(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5418790号

(P5418790)

(45) 発行日 平成26年2月19日(2014.2.19)

(24) 登録日 平成25年11月29日(2013.11.29)

|                        |                 |

|------------------------|-----------------|

| (51) Int.Cl.           | F 1             |

| HO1L 21/822 (2006.01)  | HO1L 27/04 H    |

| HO1L 27/04 (2006.01)   | HO1L 27/06 311C |

| HO1L 27/06 (2006.01)   | HO1L 27/08 321H |

| HO1L 21/8238 (2006.01) | HO3K 19/003 E   |

| HO1L 27/092 (2006.01)  |                 |

請求項の数 5 (全 10 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2010-542235 (P2010-542235)  |

| (86) (22) 出願日 | 平成20年12月10日 (2008.12.10)      |

| (65) 公表番号     | 特表2011-509528 (P2011-509528A) |

| (43) 公表日      | 平成23年3月24日 (2011.3.24)        |

| (86) 國際出願番号   | PCT/US2008/086180             |

| (87) 國際公開番号   | W02009/088622                 |

| (87) 國際公開日    | 平成21年7月16日 (2009.7.16)        |

| 審査請求日         | 平成23年12月12日 (2011.12.12)      |

| (31) 優先権主張番号  | 11/971,591                    |

| (32) 優先日      | 平成20年1月9日 (2008.1.9)          |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 テキサス州 78735<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100142907<br>弁理士 本田 淳                                                                                      |

| (72) 発明者  | カジンスキー、マイケル ジー。<br>アメリカ合衆国 78726 テキサス州<br>オースティン ブリスト ウェイ 11<br>209                                        |

最終頁に続く

(54) 【発明の名称】 ESD保護を有するMIGFET回路

## (57) 【特許請求の範囲】

## 【請求項1】

電源供給電圧線と接続された静電気放電(ESD)保護回路であって、

出力パッドと電源供給電圧線との間に接続されたソース／ドレインの経路を有する多重

独立ゲート電界効果トランジスタ(MIGFET)であって、第1のゲート端子および第

2のゲート端子を有する前記MIGFETと、

出力を有する前段駆動回路と、

前記MIGFETの第1のゲート端子に接続されたホットゲートバイアス回路と

を備え、

前記前段駆動回路の出力は、前記MIGFETの第2のゲート端子に接続され、前記ホ

ットゲートバイアス回路は、ESD現象中に、バイアス電圧を前記MIGFETの前記第

1のゲート端子に印加するように構成され、

前記MIGFETは、前記前段駆動回路の出力に応答して前記出力パッドに信号を供給

する、ESD保護回路。

## 【請求項2】

電源供給電圧線と接続された静電気放電(ESD)保護回路であって、

出力パッドと電源供給電圧線との間に接続されたソース／ドレインの経路を有する多重

独立ゲート電界効果トランジスタ(MIGFET)であって、第1のゲート端子および第

2のゲート端子を有する前記MIGFETと、

出力を有する前段駆動回路と、

10

20

前記 MIGFET の第 1 のゲート端子に接続されたホットゲートバイアス回路とを備え、

前記前段駆動回路の出力は、前記 MIGFET の第 2 のゲート端子に接続され、前記ホットゲートバイアス回路は、ESD 現象中に、バイアス電圧を前記 MIGFET の前記第 1 のゲート端子に印加するように構成され、

前記 MIGFET は、前記前段駆動回路の出力に応答して前記出力パッドに信号を供給し、

前記ホットゲートバイアス回路は、前記 ESD 現象を検出するようにさらに構成される、ESD 保護回路。

#### 【請求項 3】

電源供給電圧線と接続された静電気放電(ESD)保護回路であって、

出力パッドと電源供給電圧線との間に接続されたソース／ドレインの経路を有する多重独立ゲート電界効果トランジスタ(MIGFET)であって、第 1 のゲート端子および第 2 のゲート端子を有する前記 MIGFET と、

出力を有する前段駆動回路と、

前記 MIGFET の第 1 のゲート端子に接続されたホットゲートバイアス回路とを備え、

前記前段駆動回路の出力は、前記 MIGFET の第 2 のゲート端子に接続され、前記ホットゲートバイアス回路は、ESD 現象中に、バイアス電圧を前記 MIGFET の前記第 1 のゲート端子に印加するように構成され、

前記 MIGFET は、前記前段駆動回路の出力に応答して前記出力パッドに信号を供給し、

前記ホットゲートバイアス回路は、前記バイアス電圧を前記出力パッドの電圧と略等しくするのに十分な大きさの前記バイアス電圧を印加するように構成される、ESD 保護回路。

#### 【請求項 4】

第 1 の電力供給電圧線および第 2 の電力供給電圧線に接続された静電気放電(ESD)保護回路であって、

出力パッドと前記第 1 の電力供給電圧線との間に接続されるソース／ドレインの経路を有する第 1 の多重独立ゲート電界効果トランジスタ(MIGFET)であって、第 1 のゲート端子および第 2 のゲート端子を有する前記第 1 の MIGFET と、

前記出力パッドと前記第 2 の電力供給電圧線との間に接続されるソース／ドレインの経路を有する第 2 の多重独立ゲート電界効果トランジスタ(MIGFET)であって、第 1 のゲート端子および第 2 のゲート端子を有する前記第 2 の MIGFET と、

出力を有する前段駆動回路と、

前記第 1 の MIGFET の前記第 1 のゲート端子と、前記第 2 の MIGFET の前記第 1 のゲート端子とに接続されるゲートバイアス回路とを備え、

前記前段駆動回路は、前記第 1 の MIGFET の前記第 2 のゲート端子および前記第 2 の MIGFET の前記第 2 のゲート端子に接続され、

前記ゲートバイアス回路は、ESD 現象中に、前記第 1 の MIGFET の前記第 1 のゲート端子に第 1 のバイアス電圧を印加し、前記第 2 の MIGFET の前記第 1 のゲート端子に第 2 のバイアス電圧を印加するように構成され、

前記 MIGFET は、前記前段駆動回路の出力に応答して前記出力パッドに信号を供給する、ESD 保護回路。

#### 【請求項 5】

第 1 の電力供給電圧線および第 2 の電力供給電圧線に接続された静電気放電(ESD)保護回路であって、

出力パッドと前記第 1 の電力供給電圧線との間に接続されるソース／ドレインの経路を有する第 1 の多重独立ゲート電界効果トランジスタ(MIGFET)であって、第 1 のゲート端子および第 2 のゲート端子を有する前記第 1 の MIGFET と、

10

20

30

40

50

前記出力パッドと前記第2の電力供給電圧線との間に接続されるソース／ドレインの経路を有する第2の多重独立ゲート電界効果トランジスタ（MIGFET）であって、第1のゲート端子および第2のゲート端子を有する前記第2のMIGFETと、

出力を有する前段駆動回路と、

前記第1のMIGFETの前記第1のゲート端子と、前記第2のMIGFETの前記第1のゲート端子とに接続されるゲートバイアス回路とを備え、

前記前段駆動回路は、前記第1のMIGFETの前記第2のゲート端子および前記第2のMIGFETの前記第2のゲート端子に接続され、

前記ゲートバイアス回路は、ESD現象中に、前記第1のMIGFETの前記第1のゲート端子に第1のバイアス電圧を印加し、前記第2のMIGFETの前記第1のゲート端子に第2のバイアス電圧を印加するように構成され、10

前記MIGFETは、前記前段駆動回路の出力に応答して前記出力パッドに信号を供給し、

前記ゲートバイアス回路は、前記ESD現象を検出するようにさらに構成される、ESD保護回路。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

この開示は、概してフィン（Fin）FET型として通常動作する多重独立ゲート電界効果トランジスタ（MIGFET）に関し、また、この開示は、特にMIGFETのための静電気放電（ESD）保護に関する。20

##### 【背景技術】

##### 【0002】

フィンFET等の横型トランジスタを形成するフィンを用いることは、任意の表面領域に対して回路性能を向上するという効果を発揮する。任意の領域に対してより大きな潜在的な電流駆動が存在するように、チャネル幅が縦方向の寸法に関して決定される。しかしながら、フィンFETを用いることは、ESD保護に関する問題が取り除かないのでESD保護の必要性がある。

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0003】

このように、フィンFETのための効果的なESD保護を提供する必要がある。30

##### 【図面の簡単な説明】

##### 【0004】

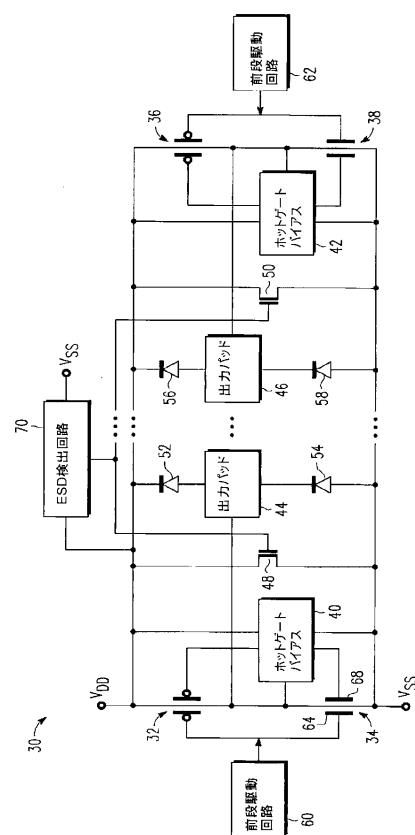

【図1】ブロック図と断面図との組合せとして示されるESD保護回路である。

【図2】図1のESD保護回路の動作を示す回路図である。

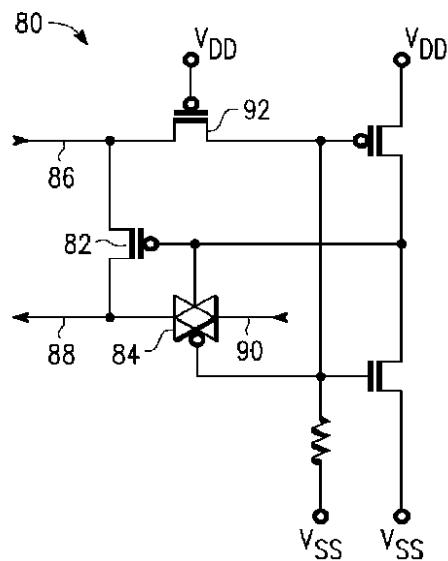

【図3】図1のオアゲートとホットゲートバイアス回路との好適な動作を示す回路図である。

##### 【発明を実施するための形態】

##### 【0005】

本発明は、例として説明され、付随する図面により制限されず、図面では、同じ参照により同様な要素を示す。図面の要素は、簡潔かつ明確に説明され、必ずしも一定の縮尺で描かれていない。40

##### 【0006】

一形態では、ESD保護回路は、出力駆動回路である多重独立ゲート電界効果トランジスタ（MIGFET）を含み、多重独立ゲート電界効果トランジスタ（MIGFET）は、入力および出力パッド（I/Oパッド）の少なくとも1つに接続され、同一チャネルを制御する第1ゲートおよび第2ゲートを有する。前段の出力駆動回路は、第1ゲートに接続され、ホットゲートバイアス回路は、第2ゲートに接続される。外部ESD現象が生じた場合、ホットゲートバイアス回路は、損傷無しでより高いドレイン・ソース間電圧に耐50

えることが可能な電圧領域にMIGFETがバイアスされるように、信号を第2ゲートに印加する。これにより、I/Oパッドに接続されるMIGFETに対する保護が強化される。このことは、以下の説明および図面から、より良く理解される。

#### 【0007】

図1に示すように、ESD保護回路10は、前段駆動回路12、NチャネルMIGFET14、ホットゲートバイアス回路16、およびオアゲート18を備える。MIGFET14は、ソースとドレインとの間のチャネルとして機能するフィン(Fin)20、フィン20の第1の側に沿ったコントロールゲート22、フィン20の第2の側にコントロールゲート24を備える。コントロールゲート22, 24の各々は、MIGFET14を導通状態にすることができる。前段駆動回路12は、コントロールゲート22およびオアゲート18の第1入力に信号を供給する。ホットゲートバイアス回路16は、オアゲート18の第2入力に接続された出力を有する。オアゲート18は、コントロールゲート24に接続された出力を有する。ESD現象が生じる場合、他のパッドに関連してMIGFET14のドレインに接続された出力パッドに比較的高い電圧が生じた状態では、ホットゲートバイアス回路16は、論理「ハイ」の出力を供給し、オアゲート18によりコントロールゲート24に論理「ハイ」を供給させ、これにより、ESD現象中に、MIGFET14のドレインとソースとの間に印加される電圧と同一電圧またはその電圧に近い電圧であるゲートとソースとの間のバイアスを有してMIGFET14を導通状態にするようとする。Nチャネルトランジスタのゲートおよびドレインがほぼ同一電圧を有する場合、ゲート電圧がドレイン電圧より著しく、例えば、2Vより低いときよりも、ドレインとソースとの間のブレークダウン電圧が高い状態にチャネルが置かれることが分かっている。通常動作で、かつESD現象がない場合に、前段駆動回路12は、信号を、コントロールゲート22に供給するとともにオアゲート18を介してコントロールゲート24に供給する。MIGFET14がPチャネルトランジスタの場合、出力パッドが他のパッドの高電圧に対して低電圧となるESD現象をホットゲートバイアス回路16により検出すことに応答して、論理「ロー」がコントロールゲート24に印加されるように、ゲート18はノアゲートとなる。通常動作中にオアゲート18に起因してわずかな遅延が生じることは、スイッチングノイズ、または、いわゆるdi/dtノイズ等のいくつかの状況において利点となる。わずかな遅延により、オアゲート18の2入力は、時差状態となって、di/dtが減少する。代替的に、オアゲート18は使用されなくてもよい。このような場合、前段駆動回路12は、単に、コントロールゲート22に接続され、ホットゲートバイアス16は、オアゲート18を介してコントロールゲート24に接続されるのではなく、直接的にコントロールゲート24に接続される。MIGFET14がPチャネルの場合、ホットゲートバイアス回路16は、論理「ロー」の出力をコントロールゲート24に直接的に供給する。このように、ホットゲートバイアス回路16は、ESD現象中に、MIGFET14が最大ブレークダウン電圧およびその電圧に略等しい電圧を示すように、コントロールゲート24に電圧を供給する。このような方式では、MIGFETの出力駆動回路が損傷からより良好に保護される。

#### 【0008】

図2に示すように、ESD保護回路30は、PチャネルMIGFET32、NチャネルMIGFET34、PチャネルMIGFET36、NチャネルMIGFET38、ホットゲートバイアス回路40、ホットゲートバイアス回路42、出力パッド44, 出力パッド46、Nチャネルトランジスタ48、Nチャネルトランジスタ50、ダイオード52、ダイオード54、ダイオード56、ダイオード58、ESD検出回路70、前段駆動回路60、および前段駆動回路62を備える。このような構成により、単体の前段駆動回路60は、NチャネルMIGFET34およびPチャネルMIGFET32の両方のゲートを制御する。代替的には、2つの別個の前段駆動回路は、NチャネルMIGFET34およびPチャネルMIGFET32のために用いられてもよい。また、MIGFET34は、第1コントロールゲート64および第2コントロールゲート68を用いて示す。MIGFET32, 36, 38は、単体のチャネルと、そのチャネルを独立的にそれぞれ制御する

10

20

30

40

50

つのコントロールゲートを同様に有する。MIGFET32は、正の電力供給端子VDD、出力パッド44に接続されたドレイン、前段駆動回路60の出力に接続された第1コントロールゲート64、およびホットゲートバイアス回路40の第1出力に接続された第2コントロールゲート68を有する。MIGFET34は、共通的なグランドである負の電力供給端子VSSに接続されたソース、出力パッド44に接続されたドレイン、前段駆動回路60の出力に接続された第1コントロールゲート、およびホットゲートバイアス回路40の第2出力に接続された第2コントロールゲートを有する。また、ホットゲートバイアス回路40は、VDD、VSS、およびMIGFET32, 34のドレインに接続される。ホットゲートバイアス回路40は、出力パッド46等の他のパッドと比較して高電圧が出力パッド44に供給されるESD現象の検出に応答して、MIGFET34のドレインにコントロールゲート68を接続する。10

ホットゲートバイアス回路40は、出力パッド44と比較して高電圧が出力パッド46に供給されるESD現象の検出に応答して、MIGFET32のドレインにMIGFET32の第2コントロールゲートを接続する。通常の電力が供給される動作中に、ホットゲートバイアス回路40は、論理「ロー」をMIGFET34に供給し、論理「ハイ」をMIGFET32に供給する。トランジスタ48は、VDDに接続されたドレイン、VSSに接続されたソース、およびESD検出回路70の出力に接続されたゲートを有する。トランジスタ50は、VDDに接続されたドレイン、VSSに接続されたソース、ESD検出回路70の出力に接続されたゲートを有する。ダイオード52では、出力パッド44とVDDとの間でアノードとカソードとが接続される。ダイオード54では、VSSと出力パッド44との間でアノードとカソードとが接続される。ダイオード56では、出力パッド46とVDDとの間でアノードとカソードとが接続される。ダイオード58では、VSSと出力パッド46との間でアノードとカソードとが接続される。MIGFET36は、正の電力供給端子VDDに接続されたソースと、出力パッド46に接続されたドレインと、前段駆動回路62の出力に接続された第1コントロールゲートと、ホットゲートバイアス回路42の第1出力に接続された第2コントロールゲートとを有する。MIGFET38は、負の電力供給端子VSSに接続されたソースと、出力パッド46に接続されたドレインと、前段駆動回路62の出力に接続された第1コントロールゲートと、ホットゲートバイアス回路42の第2出力に接続された第2コントロールゲートとを有する。また、ホットゲートバイアス回路42は、VDD、VSS、およびMIGFET36, 38のドレインに接続される。ホットゲートバイアス回路は、ホットゲートバイアス回路40が出力パッド44およびMIGFET32, 34に関連して動作するのと同様のやり方で、出力パッド46およびMIGFET36, 38に関連して動作する。通常の電力が供給される動作中に、ホットゲートバイアス回路42は、論理「ロー」をMIGFET38に供給し、論理「ハイ」をMIGFET36に供給する。20

出力パッド44, 46およびこれらに関係する回路のみを示すが、結び( ...)で示すように、追加の出力パッドおよび通常の集積回路上に追加の出力パッドに接続する回路が形成され得る。30

#### 【0009】

出力パッド46と比較して高電圧が出力パッド44に生じるESD現象の場合、ダイオード52は、ESD検出回路70およびホットゲートバイアス回路40, 42がESD現象を検出するように、出力パッドに生じる高電圧をVDDに供給する。ESD検出回路70は、論理「ハイ」の信号を生成することにより応答して、トランジスタ48, 50を導通状態にする。ホットゲートバイアス回路40は、コントロールゲート68をMIGFET34のドレインに接続することにより応答する。ESD現象の低電圧側に対応するホットゲートバイアス回路42は、MIGFET36の第2コントロールゲートをMIGFET36のドレインに接続することにより応答する。このように、電流は、出力パッド44からVDDにダイオード52を介して流れ、VDDからVSSにトランジスタ48, 50を介して流れ、VSSから出力パッド46にダイオード58を介して流れ。この電流の流れによりESD現象を軽減するが、MIGFET34は、MIGFET34のドレインに接続されたコントロールゲート68を有することにより高ドレイン・ソース間ブレーク4050

ダウン領域を維持し、MIGFET36は、トランジスタ36の第2コントロールゲートがMIGFET36のドレインに接続されることにより高ドレイン・ソース間ブレークダウン領域を維持する。また、ESD現象は、電流が出力パッド44からVSSにMIGFET34を介して流れることにより、かつ電流がVDDから出力パッド46にMIGFET36を介して流れることにより部分的に低減される。

#### 【0010】

典型的には、ホットゲートバイアス回路40, 42がMIGFET32, 36の第2コントロールゲートとこれらに対応するドレインとの間の接続を提供する必要性がないよう10に、Pチャネルトランジスタは、Nチャネルトランジスタよりも高ドレイン・ソース間ブレークダウン電圧を有する。このように、例えば、出力パッド46と比較して高電圧が出力パッド44に印加されるESD現象に対して、ホットゲートバイアス回路42は、MIGFET36の第2コントロールゲートをMIGFET36のドレインに接続する必要性がない。ホットゲートバイアス回路40, 42は、対応するNチャネルMIGFET34, 38に出力を供給するのみである。他の代替的な構成では、別個のホットゲートバイアス回路が、各NチャネルプルダウンMIGFETのために提供され、別個のホットゲートバイアス回路が、各PチャネルプルアップMIGFETのために提供されてもよい。さらに他の代替的な構成では、図1に示す構成と同様に、ホットゲートバイアス回路は、オアゲートを介して出力駆動回路のMIGFETと接続され得る。この構成の利点は、前段駆動回路がMIGFETの両方のコントロールゲートに接続可能であることがある。また代替として、ESD検出回路70は、ESD現象の検出に応答してホットゲートバイアス回路40, 42にトリガー信号を供給するように構成され得る。この場合、ホットゲートバイアス回路40, 42は、トリガー信号に応答して、バイアス電圧を各MIGFITのゲート端子に印加する。

#### 【0011】

図3に示すように、回路80は、図1のオアゲート18の機能およびホットゲートバイアス16の実施例である。図3では、Pチャネルトランジスタ82は、ESD現象中にコントロールゲート24によりMIGFET14のドレイン接続を提供する。入力端子86は、MIGFET14のドレインと接続され、出力端子88は、MIGFET14のゲートと接続される。トランスマッショングート84は、通常動作中に、前段駆動回路12の出力に対応する入力端子90と、コントロールゲート24に対応する出力端子88とを接続する。説明すると、図3の回路では、ESD現象は、MIGFET14のドレインがPチャネルMOSFET92の閾値電圧だけVDDを超えた時には常に検出される。MIGFET14のドレインが常にVDD以下に維持される全ての通常電力動作中には、前段駆動回路12のみがMIGFET14のゲートに接続される。

#### 【0012】

ここまででは、多重独立ゲート電界効果トランジスタ(MIGFET)、出力を有する前段駆動回路、およびホットゲートバイアス回路を含む、電力供給電圧線に接続された静電気放電(ESD)保護回路についての説明であることを理解されたい。MIGFETは、出力パッドと電力供給電圧線との間に接続するソース/ドレインの経路を有し、かつ第1ゲート端子および第2ゲート端子を有する。ホットゲートバイアス回路は、MIGFETの第1ゲート端子に接続され、前段駆動回路の出力は、MIGFETの第2ゲート端子に接続される。ホットゲートバイアス回路は、ESD現象中に、バイアス電圧をMIGFETの第1ゲート端子に印加するように構成される。さらに、ホットゲートバイアス回路は、静電気放電現象を検出するように構成される。ホットゲートバイアス回路は、バイアス電圧を出力パッドの電圧と略等しくするのに十分な大きさのバイアス電圧を印加するように構成され得る。ホットゲートバイアス回路は、MIGFETに関連するブレークダウン電圧を上昇するのに十分な大きさのバイアス電圧を印加するように構成され得る。さらに、保護回路は、静電気放電現象を検出するように構成される静電気放電(ESD)検出回路をさらに含んでもよく、ESD検出回路は、ホットゲートバイアス回路に接続される。ESD検出回路は、静電気放電現象の検出に応答してホットゲートバイアス回路にトリガ40

10

20

30

40

50

一信号を供給するように構成されてもよく、ホットゲートバイアス回路は、トリガー信号に応答してバイアス電圧をMIGFETの第1ゲート端子に印加する。前段駆動回路およびホットゲートバイアス回路は、論理ゲートを介してMIGFETの第1ゲート端子に接続され得る。

#### 【0013】

また、第1電力供給電圧線および第2電力供給電圧線に接続された静電気放電(ESD)保護回路について説明する。ESD回路は、出力パッドと第1電力供給電圧線との間に接続されるソース／ドレインの経路を有する第1多重独立ゲート電界効果トランジスタ(MIGFET)を含み、第1MIGFETは、第1ゲート端子および第2ゲート端子を有する。ESD回路は、出力パッドと第2電力供給電圧線との間に接続されるソース／ドレインの経路を有する第2MIGFETを含み、第2MIGFETは、第1ゲート端子および第2ゲート端子を有する。ESD回路は、出力を有する前段駆動回路を含む。ESD回路は、第1MIGFETの第1ゲート端子および第2MIGFETの第1ゲート端子に接続されるホットゲートバイアス回路、および第1MIGFETの第2ゲート端子および第2MIGFETの第2ゲート端子に接続される前段駆動回路を含み、ホットゲートバイアス回路は、ESD現象中に、第1バイアス電圧を第1MIGFETの第1ゲート端子に印加し、第2バイアス電圧を第2MIGFETの第1ゲート端子に印加するように構成される。ホットゲートバイアス回路は、第1バイアス電圧を出力パッドの電圧と略等しくするのに十分な大きさの第1バイアス電圧を印加するように構成され得る。さらに、ホットゲートバイアス回路は、ESD現象を検出するように構成され得る。ホットゲートバイアス回路は、第1MIGFETに関連するブレークダウン電圧が上昇するのに十分な大きさの第1バイアス電圧を印加し、第2MIGFETに関連するブレークダウン電圧が上昇するのに十分な大きさの第2バイアス電圧を印加するように構成され得る。ESD保護回路は、静電気放電現象を検出するように構成されるESD検出回路をさらに含み、ESD検出回路は、ホットゲートバイアス回路に接続される。ESD検出回路は、ホットゲートバイアス回路がトリガー信号に応答して第1バイアス電圧を第1MIGFETの第1ゲート端子に印加し、第2バイアス電圧を第2MIGFETの第1ゲート端子に印加するように、静電気放電の検出に応答してトリガー信号をホットゲートバイアス回路に印加するように構成され得る。通常動作中に、ホットゲートバイアス回路は、第1バイアス電圧を第1電力供給電圧線と略等しくするのに十分な大きさの第1バイアス電圧を第1MIGFETの第1ゲート端子に印加するように構成され得る。第1MIGFETは、Nチャネルトランジスタでもよく、第2MIGFETは、Pチャネルトランジスタでもよい。

#### 【0014】

さらにまた、静電気放電(ESD)保護回路に関する方法について説明する。ESD保護回路は、第1電力供給電圧線と第2電力供給電圧線との間に接続され、出力パッドと第2電力供給電圧線との間に接続されるソース／ドレインの経路を有する多重独立ゲート電界効果トランジスタ(MIGFET)を含む。MIGFETは、第1ゲート端子および第2ゲート端子を有する。その方法は、通常動作中に、第1バイアス電圧を第2電力供給電圧線と略等しくするのに十分な大きさの第1バイアス電圧をMIGFETの第1ゲート端子に印加することを含む。また、その方法は、ESD現象中に、第2バイアス電圧を出力パッドの電圧と略等しくするのに十分な大きさの第2バイアス電圧をMIGFETの第1ゲート端子に印加することを含む。この印加するステップは、第1および第2バイアス電圧を印加するためにバイアス回路を用いるような特徴をさらに有しても良く、その方法は、ESD現象を検出するためにバイアス回路を用いることをさらに含んでもよい。その方法は、MIGFETに関連するブレークダウン電圧を上昇するように第2バイアス電圧を選択することをさらに含んでもよい。その方法は、静電気放電の検出に応答してトリガー信号をホットゲートバイアス回路に印加して、ホットゲートバイアス回路がトリガー信号に応答して第1ゲート端子に第2バイアス電圧を印加することをさらに備えてもよい。

#### 【0015】

本発明を具体化する装置の大部分は当業者に知られた電子部品および回路にて構成され

10

20

30

40

50

るため、回路の詳細は、本発明の根本的なコンセプトの理解および認識に対する、および本発明の教示から不明瞭または混乱しないために必要であると思われる図示した内容よりも広い範囲について説明しない。

【 0 0 1 6 】

特定の導電性タイプまたは電位の極性を参照しながら本発明を説明してきたが、当業者であれば、導電性タイプおよび電位の極性を逆にすることができる理解することができるだろう。

【 0 0 1 7 】

さらに、上記説明および特許請求の範囲内に「前部」、「後部」、「頂部」、「底部」、「上」、「下」等の用語がもし使用してある場合には、これらの用語は説明のためだけのものであって、必ずしも、恒久的な相対位置を示すものではない。このような用語は、適当な状況の下では互換性を有し、従って本明細書に記載する本発明の実施形態は、例えば図示の方向または本明細書に記載する方向以外の方向でも動作することができることを理解されたい。10

【 0 0 1 8 】

特定の実施形態を参照しながら本発明を説明してきたが、添付の特許請求の範囲に記載する本発明の範囲から逸脱することなしに、本発明を種々に修正および変更することができる。例えば、トランジスタ 48, 50 は、N チャネルトランジスタとして説明されたが、ある他のクランプ動作が用いられてもよい。また、ダイオード 52, 54, 56, 58 は、ダイオード接続されたトランジスタでもよく、かつ有効的である。従って、本明細書および図面は制限的な意味ではなく例示として捉えられるべきであり、全てのこのような変形は本発明の範囲に包含されるべきものである。特定の実施形態に関して本明細書において説明されるいずれの効果、利点、または問題解決法も、いずれかの請求項または全ての請求項の必須の、必要な、または基本的な特徴または要素であると解釈されるべきではない。20

【 0 0 1 9 】

本明細書において用いられた「接続される」という用語は、直接的な接続または機械的な接続に制限されるべきではない。

特に記載がある場合以外は、「第 1」、「第 2」という用語は、こうした用語によって説明される要素を任意に区別するために使用されている。したがって、これらの用語がこうした要素の一時的あるいはその他の優先順位を必ずしも意味するとは限らない。30

【図1】

【図2】

【図3】

***FIG. 3***

---

フロントページの続き

(51)Int.Cl. F I

H 03K 19/003 (2006.01)

(72)発明者 マシュー、レオ

アメリカ合衆国 78717 テキサス州 オースティン ガリソン サークル 15844

(72)発明者 ミラー、ジェームズ ダブリュ.

アメリカ合衆国 78705 テキサス州 オースティン ダブリュ. サーティサード ストリー

ト 209

審査官 小田 浩

(56)参考文献 特表2004-523130 (JP, A)

特開2001-274342 (JP, A)

特開2007-053387 (JP, A)

特開2005-327766 (JP, A)

特表2007-511090 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 21/822

H 01L 21/8238

H 01L 27/04

H 01L 27/06

H 01L 27/092

H 03K 19/003