(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-541050

(P2016-541050A)

(43) 公表日 平成28年12月28日(2016.12.28)

(51) Int.Cl.

G06F 12/00 (2006.01)

G11C 11/406 (2006.01)

F 1

G 06 F 12/00

G 11 C 11/34

G 11 C 11/34

テーマコード(参考)

550B

363K

363L5B060

5MO24

審査請求 未請求 予備審査請求 有 (全 38 頁)

(21) 出願番号 特願2016-528885 (P2016-528885)

(86) (22) 出願日 平成26年10月30日 (2014.10.30)

(85) 翻訳文提出日 平成28年5月9日 (2016.5.9)

(86) 国際出願番号 PCT/US2014/063040

(87) 国際公開番号 WO2015/069530

(87) 国際公開日 平成27年5月14日 (2015.5.14)

(31) 優先権主張番号 61/902,550

(32) 優先日 平成25年11月11日 (2013.11.11)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 14/244,173

(32) 優先日 平成26年4月3日 (2014.4.3)

(33) 優先権主張国 米国(US)

(71) 出願人 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サン デイエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ディープティ・ヴィジャヤラクシミ・シュ

リラマギリ

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

最終頁に続く

(54) 【発明の名称】メモリセルをリフレッシュするための方法および装置

## (57) 【要約】

方法は、第1の信号をメモリデバイスからメモリコントローラに送るステップを含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す。

**【特許請求の範囲】****【請求項 1】**

第1の信号をメモリデバイスからメモリコントローラに送るステップであって、前記第1の信号は、前記メモリデバイスの特定のメモリセルが前記メモリデバイスによってリフレッシュされるべきであることを前記メモリコントローラに示す、ステップを含む、方法。

**【請求項 2】**

前記第1の信号が、専用バスを介して送られる、請求項1に記載の方法。

**【請求項 3】**

コマンドバスを介して確認応答信号を前記メモリコントローラから受け取るステップをさらに含む、請求項1に記載の方法。 10

**【請求項 4】**

前記メモリコントローラが、前記確認応答信号を送ることに応答してリフレッシュ時間期間の間に前記特定のメモリセルに関連付けられたコマンドの実行を中止する、請求項3に記載の方法。

**【請求項 5】**

前記確認応答信号を受け取ることに応答して、前記特定のメモリセルをリフレッシュするステップをさらに含む、請求項3に記載の方法。

**【請求項 6】**

前記第1の信号を送ることに応答して固定時間期間の間に前記特定のメモリセルに関連付けられたりフレッシュ動作を一時停止するステップと、 20

前記固定時間期間の満了に応答して前記特定のメモリセルをリフレッシュするステップと

をさらに含む、請求項1に記載の方法。

**【請求項 7】**

前記メモリコントローラが、前記固定時間期間の間に前記特定のメモリセルに関連付けられたコマンドを実行することを許される、請求項6に記載の方法。

**【請求項 8】**

前記メモリコントローラが、前記固定時間期間の間に前記特定のメモリセルに関連付けられたコマンドを実行する、請求項6に記載の方法。 30

**【請求項 9】**

前記メモリコントローラが、前記固定時間期間の前記満了に応答して前記特定のメモリセルに関連付けられたコマンドの実行を中止する、請求項6に記載の方法。

**【請求項 10】**

前記メモリデバイスは、揮発性メモリデバイスである、請求項1に記載の方法。

**【請求項 11】**

前記メモリデバイスが、ダイナミックランダムアクセスメモリ(DRAM)デバイスである、請求項1に記載の方法。

**【請求項 12】**

前記第1の信号を前記メモリコントローラに送るステップが、前記メモリデバイスに組み込まれたプロセッサによって始動される、請求項1に記載の方法。 40

**【請求項 13】**

メモリコントローラにおいて、第1の信号をメモリデバイスから受け取るステップであって、前記第1の信号は、前記メモリデバイスの特定のメモリセルが前記メモリデバイスによってリフレッシュされるべきであることを前記メモリコントローラに示す、ステップを含む、方法。

**【請求項 14】**

前記第1の信号が、専用バスを介して受け取られる、請求項13に記載の方法。

**【請求項 15】**

特定の時間期間の間に前記特定のメモリセルに関連付けられたコマンドを実行するステ 50

ップと、

前記特定の時間期間の満了に応答して、

前記特定のメモリセルに関連付けられた前記コマンドの実行を中止するステップと、

確認応答信号を前記メモリデバイスに送るステップであって、前記確認応答信号は、前記特定のメモリセルに関連付けられた前記コマンドの実行が中止されたことを前記メモリデバイスに示す、ステップと

をさらに含む、請求項13に記載の方法。

【請求項 16】

第2の信号を第2のメモリデバイスから受け取るステップであって、前記第2の信号は、前記第2のメモリデバイスの特定のメモリセルが前記第2のメモリデバイスによってリフレッシュされるべきであることを前記メモリコントローラに示す、ステップと、

前記確認応答信号を前記メモリデバイスに送った後、第2の確認応答信号を前記第2のメモリデバイスに送るステップであって、前記第2の確認応答信号は、前記第2のメモリデバイスの前記特定のメモリセルに関連付けられたコマンドの実行が中止されたことを前記第2のメモリデバイスに示す、ステップと

をさらに含む、請求項15に記載の方法。

【請求項 17】

前記メモリデバイスの第1のダイの第1の保持時間を、前記メモリデバイスの第2のダイの第2の保持時間と比較するステップと、

前記第2の保持時間が前記第1の保持時間よりも大きいという判定に応答して前記第1のダイをマスタダイとして選択するステップと、

前記第1の保持時間が前記第2の保持時間よりも大きいという判定に応答して前記第2のダイをマスタダイとして選択するステップと

をさらに含み、

前記第1の信号が前記マスタダイに関連付けられる、

請求項13に記載の方法。

【請求項 18】

前記第1の信号を受け取ることに応答して固定時間期間の後に前記特定のメモリセルに関連付けられたコマンドの実行を中止するステップをさらに含む方法であって、前記特定のメモリセルが前記固定時間期間の後に前記メモリデバイスによってリフレッシュされる、請求項13に記載の方法。

【請求項 19】

第1の信号をメモリコントローラに送ることであって、前記第1の信号は、メモリデバイスの特定のメモリセルが前記メモリデバイスによってリフレッシュされるべきであることを前記メモリコントローラに示す、送ることと、

前記特定のメモリセルをリフレッシュすることと

を行うように動作可能な前記メモリデバイス

を含む、装置。

【請求項 20】

前記第1の信号が、専用バスを介して送られる、請求項19に記載の装置。

【請求項 21】

前記メモリデバイスが、コマンドバスを介して確認応答信号を前記メモリコントローラから受け取る、請求項19に記載の装置。

【請求項 22】

前記メモリデバイスが、前記確認応答信号を受け取ることに応答して、前記特定のメモリセルをリフレッシュする、請求項21に記載の装置。

【請求項 23】

前記メモリデバイスが、

前記第1の信号を送ることに応答して固定時間期間の間に前記特定のメモリセルに関連付けられたリフレッシュ動作を一時停止することと、

10

20

30

40

50

前記固定時間期間の満了に応答して前記特定のメモリセルをリフレッシュすることとを行いうようにさらに動作可能な、請求項19に記載の装置。

**【請求項 2 4】**

前記メモリデバイスが、少なくとも1つの半導体ダイに組み込まれる、請求項19に記載の装置。

**【請求項 2 5】**

前記メモリデバイスが組み込まれた、通信デバイス、タブレット、ラップトップ、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータからなるグループから選択されるデバイスをさらに含む、請求項19に記載の装置。 10

**【請求項 2 6】**

第1の信号をメモリデバイスから受け取ることであって、前記第1の信号は、前記メモリデバイスの特定のメモリセルが前記メモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す、受け取ることと、

リフレッシュ動作を可能にするために前記特定のメモリセルに関連付けられたコマンドの実行を中止することと

を行うように動作可能な前記メモリコントローラを含む、装置。

**【請求項 2 7】**

前記第1の信号が、専用バスを介して受け取られる、請求項26に記載の装置。 20

**【請求項 2 8】**

前記メモリコントローラが、

特定の時間期間の間に前記特定のメモリセルに関連付けられた特定のコマンドを実行することと、

前記特定の時間期間の満了に応答して、

前記特定のメモリセルに関連付けられた前記特定のコマンドの実行を中止することと、

確認応答信号を前記メモリデバイスに送ることであって、前記確認応答信号は、前記特定のメモリセルに関連付けられた前記特定のコマンドの実行が中止されたことを前記メモリデバイスに示す、受け取ることと

を行うようにさらに動作可能な、請求項26に記載の装置。 30

**【請求項 2 9】**

前記メモリコントローラが、少なくとも1つの半導体ダイに組み込まれる、請求項26に記載の装置。

**【請求項 3 0】**

前記メモリコントローラが組み込まれた、通信デバイス、タブレット、ラップトップ、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータからなるグループから選択されるデバイスをさらに含む、請求項26に記載の装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

関連出願の相互参照

本出願は、その内容全体が参照により本明細書に明示的に組み込まれる、同一出願人が所有する、2013年11月11日に出願された米国仮特許出願第61/902,550号および2014年4月3日に出願された米国非仮特許出願第14/244,173号の優先権を主張するものである。

**【0 0 0 2】**

本開示は、一般に、メモリセルをリフレッシュすることに関する。

**【背景技術】**

**【0 0 0 3】**

10

20

30

40

50

技術の進歩は、より小さくより強力なコンピューティングデバイスをもたらした。たとえば、小型で、軽量で、ユーザによって容易に運ばれるポータブルワイヤレス電話、携帯情報端末(PDA)、およびページングデバイスなどのワイヤレスコンピューティングデバイスを含む様々なポータブルパーソナルコンピューティングデバイスが現在存在する。より具体的には、セルラー電話、インターネットプロトコル(IP)電話などのポータブルワイヤレス電話は、ワイヤレスネットワークを介して音声およびデータパケットを通信し得る。さらに、多くのそのようなワイヤレス電話には、内部に他のタイプのデバイスが組み込まれている。たとえば、ワイヤレス電話は、デジタルスチールカメラ、デジタルビデオカメラ、デジタルレコーダ、およびオーディオファイルプレーヤも含み得る。

#### 【0004】

10

ワイヤレス電話は、データの完全性を維持するために周期的にリフレッシュされるメモリセルを含む揮発性メモリデバイスを含み得る。揮発性メモリデバイスは、内部回路を使用してメモリセルを「自己リフレッシュする」場合があるが、自己リフレッシュプロセスは、各メモリデバイスがそれ自体のスケジュールに従ってリフレッシュすることにより、様々な時刻に様々なメモリデバイスにアクセスできなくなる場合がある。あるいは、メモリコントローラが、「自己リフレッシュ」プロセスを使用したメモリセルのリフレッシュを制御し得る。しかしながら、自己リフレッシュプロセスは、データの完全性を維持するためにリフレッシュ動作をどのくらいの頻度で実行すべきかに影響を及ぼし得る、揮発性メモリデバイスの特定の特性(たとえば、温度)を無視する場合がある。データの完全性を確保するために、自己リフレッシュプロセスは、大きいガードバンド(たとえば、実際のリフレッシュプロセスと揮発性メモリデバイスの温度に基づいたリフレッシュプロセスとの間の時間間隔)をもたらす業界規格に基づいてメモリセルをリフレッシュする場合があり、これは、必要以上の頻度でメモリデバイスがリフレッシュされるので、電力消費量を増加させる。

20

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0005】

30

DRAMデバイスによってメモリセルをリフレッシュするためのシステムおよび方法を示す。揮発性メモリデバイス(たとえば、ダイナミックランダムアクセスメモリ(DRAM)デバイス)は、保持プロファイル情報を記憶するためのモードレジスタを含み得る。保持プロファイル情報は、揮発性メモリデバイス内の特定のメモリセルのプロセス変動および温度に基づく特定のメモリセルのリフレッシュ速度に対応し得る。たとえば、揮発性メモリデバイスのメモリセルの第1のバンクは、メモリセルの第1のバンクの第1のリフレッシュ速度に関連付けられる場合があり、揮発性メモリデバイスのメモリセルの第2のバンクは、メモリセルの第2のバンクの第2のリフレッシュ速度に関連付けられる場合がある。メモリコントローラは、最も短い保持時間(たとえば、必要とされる/推奨される最速のリフレッシュ速度)を有する(たとえば、特定のダイ内の)メモリセルの特定のバンクを決定するためにモードレジスタにポーリングする場合があり、メモリコントローラは、メモリセルの特定のバンクを特定の揮発性メモリデバイスの「マスター」ダイに指定する場合がある。各揮発性メモリデバイスは、揮発性メモリデバイスのマスターダイに関連付けられたリフレッシュ速度に基づいて内部メモリセル上でリフレッシュ動作を実行し得る。

40

#### 【0006】

揮発性メモリデバイスは、リフレッシュ動作を実行する前に、側波帯シグナリングチャネル(たとえば、リフレッシュアヘッド(RFA)バス)を介してメモリコントローラにRFA信号を送り得る。たとえば、RFA信号は、内部DRAMリフレッシュ動作が実行されようとしていることをメモリコントローラに示し得る。各揮発性メモリデバイスの内部DRAMリフレッシュ動作は、各揮発性メモリデバイスのマスターダイに関連付けられた速度で実行され得る。一実施形態では、メモリコントローラは、リフレッシュ動作を実行しようとしている揮発性メモリデバイスに確認応答信号を送り得る。確認応答信号は、メモリコントローラが揮発性メモリデバイスに関連付けられたコマンドの発出/実行を中止したことと、揮発性メ

50

モリデバイスが確認応答信号を受け取ることに応答してリフレッシュ動作を実行し得ることとを示す。別の実施形態では、メモリコントローラは、RFA信号を受け取った後、固定時間期間の間に揮発性メモリデバイスに関連付けられたコマンドを発出/実行し得る。メモリコントローラは、固定時間期間が満了した後、揮発性メモリデバイスに関連付けられたコマンドの発出/実行を中止する場合があり、次いで、揮発性メモリデバイスは、リフレッシュ動作を実行する場合がある。

#### 【0007】

特定の実施形態では、装置は、第1の信号をメモリコントローラに送るように動作可能なメモリデバイスを含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す。

10

#### 【0008】

別の特定の実施形態では、方法は、第1の信号をメモリデバイスからメモリコントローラに送るステップを含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す。

#### 【0009】

別の特定の実施形態では、装置は、第1の信号をメモリデバイスからメモリコントローラに送るための手段を含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す。本装置は、特定のメモリセルをリフレッシュするための手段も含む。

#### 【0010】

別の特定の実施形態では、非一時的コンピュータ可読媒体は、メモリデバイス内のプロセッサによって実行されるとき、プロセッサに、第1の信号をメモリデバイスからメモリコントローラに送らせる命令を含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す。本命令はまた、プロセッサに、特定のメモリセルのリフレッシュ動作を始動させるように実行可能である。

20

#### 【0011】

別の特定の実施形態では、装置は、第1の信号をメモリデバイスから受け取るように動作可能なメモリコントローラを含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す。

30

#### 【0012】

別の特定の実施形態では、方法は、メモリコントローラにおいて、第1の信号をメモリデバイスから受け取るステップを含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す。

#### 【0013】

別の特定の実施形態では、装置は、第1の信号をメモリデバイスから受け取るための手段を含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることを、前記受け取るための手段に示す。本装置は、リフレッシュ動作を可能にするために特定のメモリセルに関連付けられたコマンドの実行を中止するための手段も含む。

40

#### 【0014】

別の特定の実施形態では、非一時的コンピュータ可読媒体は、メモリデバイス内のプロセッサによって実行されるとき、プロセッサに、第1の信号をメモリデバイスから受け取らせる命令を含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す。本命令はまた、プロセッサに、リフレッシュ動作を可能にするために特定のメモリセルに関連付けられたコマンドの実行を中止させるように実行可能である。

#### 【0015】

50

開示する実施形態のうちの少なくとも1つによって提供される特定の利点は、「最悪の場合」のリフレッシュ時間に従ってすべてのメモリデバイスをリフレッシュするのではなく、揮発性メモリデバイスの保持プロファイルおよび温度に基づいてメモリセルをリフレッシュすることによって揮発性メモリデバイスの電力消費量を低減する能力を含む。本開示の他の様、利点、および特徴は、以下のセクション、すなわち、図面の簡単な説明、発明を実施するための形態、および特許請求の範囲を含む本出願全体を検討した後に明らかとなろう。

【図面の簡単な説明】

【0016】

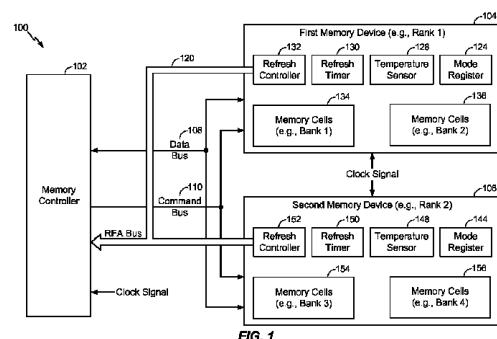

【図1】メモリセルをリフレッシュするように動作可能なシステムの特定の実施形態を示す図である。10

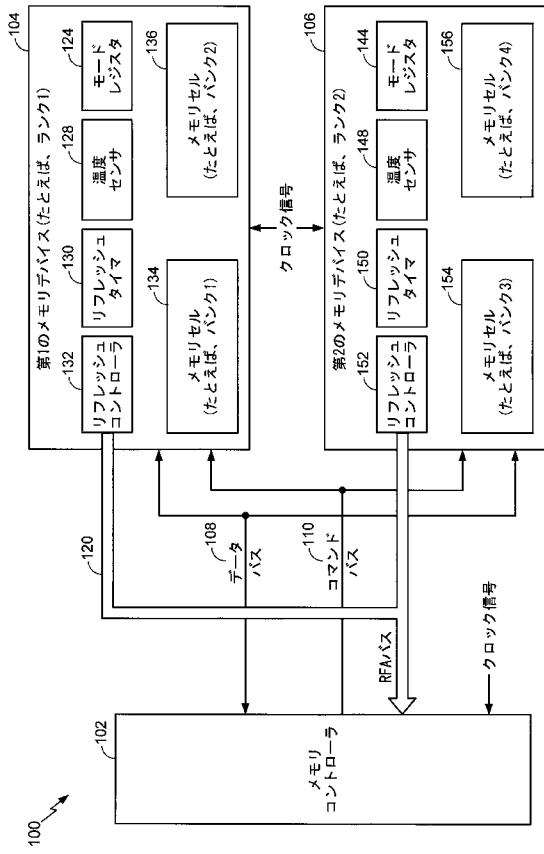

【図2】メモリセルをリフレッシュするように動作可能なシステムの別の特定の実施形態を示す図である。

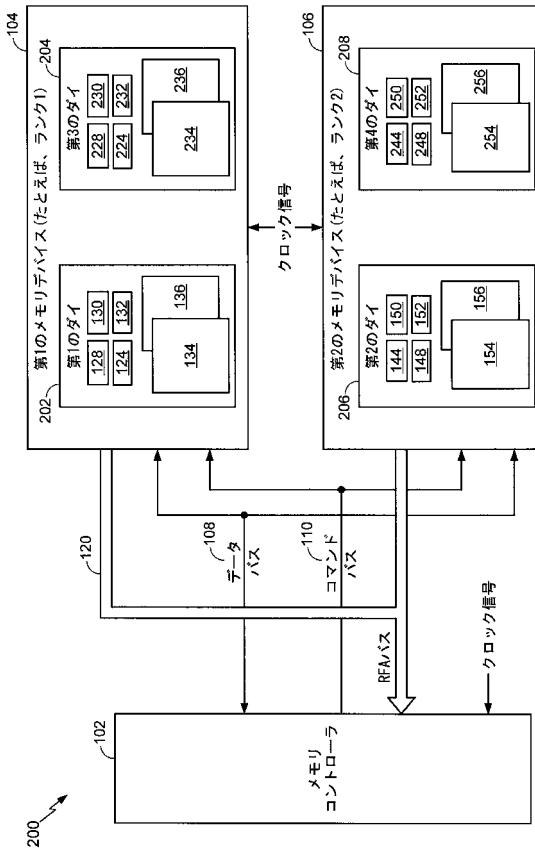

【図3】確認応答信号を使用する特定のリフレッシュ方式のタイミング図である。

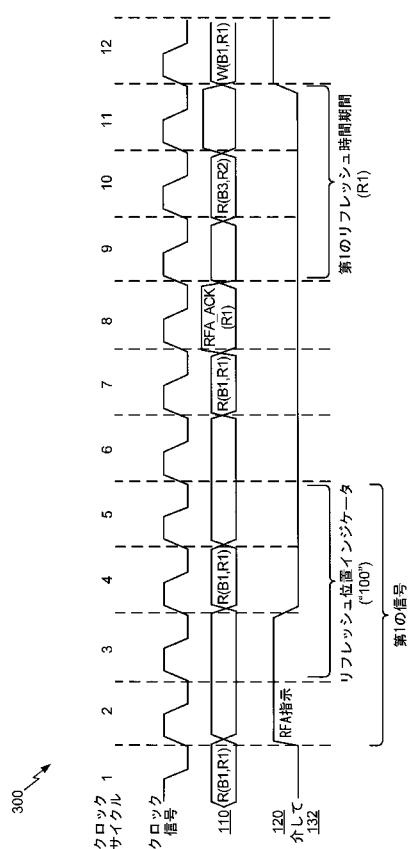

【図4】確認応答信号を使用する別の特定のリフレッシュ方式のタイミング図である。

【図5】固定タイマを使用する特定のリフレッシュ方式のタイミング図である。

【図6】固定タイマを使用する別の特定のリフレッシュ方式のタイミング図である。

【図7】メモリセルをリフレッシュするための方法の特定の実施形態を示すフローチャートである。

【図8】図1～図7のシステム、リフレッシュ方式、および方法による、メモリセルリフレッシュ動作を実行するように動作可能なワイヤレスデバイスのブロック図である。20

【図9】メモリセルをリフレッシュするように動作可能な構成要素を含む電子デバイスを製造するための製造プロセスの特定の例示的な実施形態のデータフロー図である。

【発明を実施するための形態】

【0017】

図1を参照すると、メモリセルをリフレッシュするように動作可能なシステム100の特定の実施形態が示されている。システム100は、メモリコントローラ102、第1のメモリデバイス104(たとえば、第1のランク)、および第2のメモリデバイス106(たとえば、第2のランク)を含む。第1のメモリデバイス104および第2のメモリデバイス106は、揮発性メモリデバイスであり得る。たとえば、第1のメモリデバイス104および第2のメモリデバイス106は、ダイナミックランダムアクセスメモリ(DRAM)デバイスであり得る。メモリコントローラ102は、データバス108およびコマンドバス110を介してメモリデバイス104、106に結合され得る。30

【0018】

第1のメモリデバイス104は、第1のデータを記憶するメモリセル134の第1のバンクと、第2のデータを記憶するメモリセル136の第2のバンクとを含み得る。特定の実施形態では、メモリセル134の第1のバンクおよびメモリセル136の第2のバンクは、DRAMセルに対応し得る。メモリセル134、136の各バンク内の特定のメモリセルは、行および列によって識別され得る。各メモリセルは、データの完全性を維持する(たとえば、記憶されたデータ値を保持する)ために特定の速度で周期的にリフレッシュ、または再通電され得る。たとえば、メモリセル134、136の第1および第2のバンクは、時間とともに放電する場合がある電荷を保存するキャパシタに基づいて設計され得る。リフレッシュすることは、キャパシタを再充電すること、または再通電することを含み得る。40

【0019】

第1のメモリデバイス104は、第1のメモリデバイス104の保持時間プロファイル情報を生成するように構成された第1のリフレッシュコントローラ132も含み得る。保持時間プロファイル情報は、メモリセル134の第1のバンクの第1の保持時間と、メモリセル136の第2のバンクの第2の保持時間とを示すデータを含む。たとえば、保持時間プロファイル情報は、メモリセル134の第1のバンクが再充電(たとえば、リフレッシュ)される必要なしにデータの完全性を維持し得る時間量に対応するデータを含み得る。保持プロファイル情報は、50

メモリセル136の第2のバンクが再充電される必要なしにデータの完全性を維持し得る時間量に対応するデータも含み得る。第1のタイマ130は、メモリセル134、136の特定のバンクが保持時間プロファイル情報に基づいてリフレッシュされる必要がある時を第1のリフレッシュコントローラ132に示すように構成され得る。

#### 【0020】

第1のメモリデバイス104は、第1の温度センサ128も含み得る。第1の温度センサ128は、メモリセル134の第1のバンクおよびメモリセル136の第2のバンクの第1の温度を監視し得る。第1の保持時間は、メモリセル134、136の第1の温度、および/またはメモリセル134、136に関連付けられたプロセス変動に少なくとも部分的に基づいている。たとえば、第1の保持時間は、第1の温度が増加するにつれて、減少し得る。

10

#### 【0021】

第1のメモリデバイス104は、保持時間プロファイル情報を記憶するための第1の専用データ記憶域も含み得る。特定の実施形態では、第1の専用データ記憶域は、第1のモードレジスタ124であり得る。別の特定の実施形態では、第1の専用データ記憶域は、直列プレゼンス検出(SPD)チップであり得る。本明細書で使用する「専用データ記憶域」および「モードレジスタ」という用語は、互換的に使用され得る。「モードレジスタ」は、保持時間プロファイル情報をおよび/または温度情報を記憶するように構成された任意のチップ、デバイス、および/またはレジスタを指す場合がある。

#### 【0022】

メモリセル134、136のバンクの保持時間に関連付けられた初期(たとえば、デフォルト)データは、製造中に第1のモードレジスタ124に書き込まれ得る。非限定的な例として、第1のモードレジスタ124は、メモリセル134、136の第1および第2のバンクが華氏75度の温度において32ミリ秒(たとえば、保持時間)の間にデータの完全性を維持し得ることを示し得る。第1のリフレッシュコントローラ132は、第1の温度センサ128によって検出された温度変化に応答してメモリセル134、136のバンクの保持時間を調整し得る。たとえば、第1の温度センサ128は、第1の温度の変化を検出する場合があり、第1のリフレッシュコントローラ132は、検出された変化に基づいて第1の保持時間を調整し得る。調整された保持時間は、第1のモードレジスタ124に書き込まれ得る。図2に関してより詳細に説明するように、メモリコントローラ102は、第1のメモリデバイス104の「マスター」ダイを決定するために第1のモードレジスタ124に周期的にポーリングする場合がある。たとえば、図1に示す実施形態は、(たとえば、第1のモードレジスタ124、第1の温度センサ128、第1のリフレッシュタイマ130、第1のリフレッシュコントローラ132、およびメモリセル134、136を含む)単一のダイを有する第1のメモリデバイス104を示す。しかしながら、他の実施形態(図2に示す実施形態など)では、メモリデバイスは、複数のダイを含み得る。

20

30

#### 【0023】

第2のメモリデバイス106は、第3のデータを記憶するメモリセル154の第3のバンクと、第4のデータを記憶するメモリセル156の第4のバンクとを含み得る。特定の実施形態では、メモリセル154の第3のバンクおよびメモリセル156の第4のバンクは、DRAMセルに対応し得る。第2のメモリデバイス106は、第2のリフレッシュコントローラ152、第2のリフレッシュタイマ150、第2の温度センサ148、および第2のモードレジスタ144も含み得る。第2のリフレッシュコントローラ152、第2のリフレッシュタイマ150、第2の温度センサ148、および第2のモードレジスタ144は、それぞれ、第1のリフレッシュコントローラ132、第1のリフレッシュタイマ130、第1の温度センサ128、および第1のモードレジスタ124に関して説明したのとほぼ同様に動作し得る。

40

#### 【0024】

第1のリフレッシュコントローラ132は、第1の信号(たとえば、「リフレッシュアヘッド(RFA)情報」)を第1のメモリデバイス104からメモリコントローラ102に送るように構成され得る。第1の信号は、第1のメモリデバイス104の特定のメモリセルが第1のリフレッシュコントローラ132によってリフレッシュされるべきであることをメモリコントローラ102に示し得る。たとえば、第1のリフレッシュコントローラ132は、メモリセル134の第1のバン

50

クがリフレッシュされる必要があるか、メモリセル136の第2のバンクがリフレッシュされる必要があるか、またはそれらの組合せであるかの指示を、第1のリフレッシュタイム130の満了に基づいて第1のメモリデバイス104から受け取り得る。第1の信号は、メモリセル134、136のどのバンクがリフレッシュされるべきであるかをメモリコントローラ102に示し得る。以下に説明する例として、第1の信号は、メモリセル134の第1のバンクがリフレッシュされるべきであることを示し得る。第1の信号は、専用バス(たとえば、側波帯チャネル)を介してメモリコントローラ102に送られ得る。たとえば、第1の信号は、RFAバス120を介してメモリコントローラ102に送られ得る。

#### 【0025】

メモリコントローラ102は、RFAバス120を介して第1の信号を受け取り得る。一実施形態では、メモリコントローラ102は、メモリセル134の第1のバンクに関連付けられたコマンドのセットの実行を完了し得る。メモリコントローラ102は、コマンドのセットの実行を完了した後、リフレッシュ時間期間の間にメモリセル134の第1のバンクに関連付けられたコマンドの実行を中止するように構成され得る。たとえば、メモリコントローラ102は、メモリセル134の第1のバンクに関連付けられたコマンドの実行が中止されたことを第1のリフレッシュコントローラ132に示すためにコマンドバス110を介して確認応答信号を第1のリフレッシュコントローラ132に送るように構成され得る。第1のリフレッシュコントローラ132は、確認応答信号をメモリコントローラ102から受け取ると、メモリセル134の第1のバンクをリフレッシュし得る。たとえば、第1のリフレッシュコントローラ132は、確認応答信号を受け取ることに応答してメモリセル134の第1のバンクのキャパシタを充電するために電圧信号を生成し得る。キャパシタを充電することによって、メモリセル134の第1のバンクがリフレッシュされる。

10

20

30

#### 【0026】

別の実施形態では、第1のリフレッシュコントローラ132は、第1の信号を送ることに応答して固定時間期間の間にメモリセル134の第1のバンクに関連付けられたリフレッシュ動作を一時停止するように構成され得る。固定時間期間は、メモリコントローラ102内にプログラミングされ、メモリデバイス104、106内にプログラミングされ(たとえば、製造業者によってプログラミングされ、および/または業界規格によって規定され)得る。メモリコントローラ102は、固定時間期間の間にメモリセル134の第1のバンクに関連付けられたコマンドを実行することを許され得る。たとえば、メモリコントローラ102は、第1の信号を受け取った後、固定時間期間の間にメモリセル134の第1のバンクに関連付けられたコマンドのセットを実行し得る。特定の実施形態では、メモリコントローラ102は、固定時間期間の満了を決定するためのタイマを含み得る。別の実施形態では、メモリコントローラ102は、固定時間期間に関連付けられたクロックサイクルの特定の数をカウントするためのカウンタを含み得る。メモリコントローラ102は、固定時間期間の満了に応答して、メモリセル134の第1のバンクに関連付けられたコマンドの実行を中止し、第1のリフレッシュコントローラ132は、メモリセル134の第1のバンクをリフレッシュする。

#### 【0027】

図1のシステム100は、リフレッシュ動作が実行される必要があるとき、特定のメモリデバイスがメモリコントローラ102にシグナリングすることを可能にする場合があり、メモリコントローラ102は、リフレッシュ動作中に特定のメモリデバイスに関連付けられたコマンドの実行を中止する場合がある。メモリコントローラ102は、特定のメモリデバイスにおいてリフレッシュ動作が行われる間に、他のメモリデバイスに関連付けられたコマンドを実行し得る。したがって、システム100は、標準的な「自己リフレッシュ」モードと比較して処理効率を改善することもできる。たとえば、システム100は、メモリコントローラ102が、アクティブ状態を維持し、他のメモリセルがリフレッシュ動作を受けている間にリフレッシュ動作を受けていないメモリセルにコマンドを送ることを可能にし得る。

40

#### 【0028】

図2を参照すると、メモリセルをリフレッシュするように動作可能なシステム200の別の特定の実施形態が示されている。システム200は、メモリコントローラ102、第1のメモリ

50

デバイス104、および第2のメモリデバイス106を含む。メモリコントローラ102は、データバス108およびコマンドバス110を介してメモリデバイス104、106に結合され得る。

#### 【0029】

第1のメモリデバイス104は、第1のダイ202および第3のダイ204を含み得る。図示の実施形態では、第1のメモリデバイス104は2つのダイ202、204を含むが、他の実施形態では、第1のメモリデバイス104は、追加のダイを含み得る。たとえば、第1のメモリデバイスは、K個のダイを含む場合があり、ここにおいて、Kは1以上の任意の整数である。

#### 【0030】

第1のダイ202は、第1のモードレジスタ124、第1の温度センサ128、第1のリフレッシュタイム130、および第1のリフレッシュコントローラ132を含み得る。第1のダイ202は、メモリセル134の第1のバンクとメモリセル136の第2のバンクとを含む場合もある。図示の実施形態では、第1のダイ202は、メモリセル134、136の2つのバンクを含むが、他の実施形態では、第1のダイ202は、メモリセルの追加のバンクを含み得る。たとえば、第1のメモリデバイス104は、メモリセルのP個のバンクを含む場合があり、ここにおいて、Pは1以上の任意の整数である。第3のダイ204は、第3のモードレジスタ224、第3の温度センサ228、第3のリフレッシュタイム230、および第3のリフレッシュコントローラ232を含み得る。第3のダイ204は、メモリセル234、236の複数のバンクも含み得る。第3のモードレジスタ224、第3の温度センサ228、第3のリフレッシュタイム230、および第3のリフレッシュコントローラ232は、第1のモードレジスタ124、第1の温度センサ128、第1のリフレッシュタイム130、および第1のリフレッシュコントローラ132に関して図1を参照しながら説明したのとほぼ同様に、第3のダイ204に関して動作し得る。

10

20

20

30

40

#### 【0031】

第1の温度センサ128は、第1のダイ202上のメモリセル134、136の第1および第2のバンクの第1の温度を監視し得る。メモリセル134、136の第1および第2のバンクの第1の保持時間は、メモリセル134、136の第1および第2のバンクに関連付けられた第1の温度および/またはプロセス変動に少なくとも部分的に基づいている場合がある。図1に関して上記で説明したように、第1のリフレッシュコントローラ132は、第1の保持時間を含む保持時間プロファイル情報を生成するように構成され得る。第1の保持時間は、第1の温度が増加するにつれて、減少し得る。加えて、プロセス変動(たとえば、キャパシタサイズなど)は、第1の保持時間に影響を及ぼし得る。たとえば、保持時間は、メモリセル134、136の第1および第2のバンク内のキャパシタのサイズ(たとえば、キャパシタのキャパシタンス)が増加するにつれて、増加し得る。第1の保持時間は、第1のモードレジスタ124に記憶され得る。同様に、第3の温度センサ228は、第3のダイ204上のメモリセル234、236のバンクの第3の温度を監視し得る。メモリセル234、236のバンクの第3の保持時間は、メモリセル234、236のバンクに関連付けられた第3の温度および/またはプロセス変動に少なくとも部分的に基づいている。第3のリフレッシュコントローラ232は、第3の保持時間を含む保持時間プロファイル情報を生成するように構成され得る。第3の保持時間は、第3の温度が増加するにつれて、減少し得る。加えて、プロセス変動(たとえば、キャパシタサイズなど)は、上記で説明したのとほぼ同様に、第3の保持時間に影響を及ぼし得る。第3の保持時間は、第3のモードレジスタ224に記憶され得る。

#### 【0032】

第2のメモリデバイス106は、第2のダイ206および第4のダイ208を含み得る。図示の実施形態では、第2のメモリデバイス106は2つのダイ206、208を含むが、他の実施形態では、第2のメモリデバイス106は、追加のダイを含み得る。たとえば、第2のメモリデバイス106は、N個のダイを含む場合があり、ここにおいて、Nは1以上の任意の整数である。

#### 【0033】

第2のダイ206は、第2のモードレジスタ144、第2の温度センサ148、第2のリフレッシュタイム150、および第2のリフレッシュコントローラ152を含み得る。第2のダイ206は、メモリセル154の第3のバンクとメモリセル156の第4のバンクとを含む場合もある。図示の実施形態では、第2のダイ206は、メモリセル154、156の2つのバンクを含むが、他の実施形

50

態では、第2のダイ206は、メモリセルの追加のバンクを含み得る。たとえば、第2のダイ206は、メモリセルのQ個のバンクを含む場合があり、ここにおいて、Qは1以上の任意の整数である。第4のダイ208は、第4のモードレジスタ244、第4の温度センサ248、第4のリフレッシュタイム250、および第4のリフレッシュコントローラ252を含み得る。第4のダイ208は、メモリセル254、256の複数のバンクも含み得る。第4のモードレジスタ244、第4の温度センサ248、第4のリフレッシュタイム250、および第4のリフレッシュコントローラ252は、第2のモードレジスタ244、第2の温度センサ148、第2のリフレッシュタイム150、および第2のリフレッシュコントローラ152に関して図1を参照しながら説明したのとほぼ同様に、第4のダイ208に関して動作し得る。

#### 【0034】

第2の温度センサ148は、第2のダイ206上のメモリセル154、156の第3および第4のバンクの第2の温度を監視し得る。メモリセル154、156の第3および第4のバンクの第2の保持時間は、メモリセル154、156の第3および第4のバンクに関連付けられた第2の温度および/またはプロセス変動に少なくとも部分的に基づいている場合がある。第2のリフレッシュコントローラ152は、第2の保持時間を含む保持時間プロファイル情報を生成するように構成され得る。第2の保持時間は、第2の温度が増加するにつれて、減少し得る。加えて、プロセス変動(たとえば、キャパシタサイズなど)は、上記で説明したのとほぼ同様に、第2の保持時間に影響を及ぼし得る。同様に、第4の温度センサ248は、第4のダイ208上のメモリセル254、256のバンクの第4の保持時間は、メモリセル254、256のバンクに関連付けられた第4の温度および/またはプロセス変動に少なくとも部分的に基づいている。第4のリフレッシュコントローラ252は、第4の保持時間を含む保持時間プロファイル情報を生成するように構成され得る。第4の保持時間は、第4の温度が増加するにつれて、減少し得る。加えて、プロセス変動(たとえば、キャパシタサイズなど)は、上記で説明したのとほぼ同様に、第4の保持時間に影響を及ぼし得る。第4の保持時間は、第4のモードレジスタ244に記憶され得る。

#### 【0035】

メモリコントローラ102は、データバス108を介してモードレジスタ124、144、224、244に記憶されたデータにアクセスするように構成され得る。特定の実施形態では、データバス108は、各モードレジスタ124および224または144および244から8ビットのデータを通信するように構成された32ビットバスであり得る。メモリコントローラ102は、第1のダイ202の第1の保持時間と、第3のダイ204の第3の保持時間とを、それぞれ、第1のモードレジスタ124および第3のモードレジスタ224から周期的に読み取るように構成され得る。たとえば、メモリコントローラ102は、第1のダイ202と第3のダイ204との間の保持時間変動を経時的に追跡し得る。メモリコントローラ102は、第1の保持時間を第3の保持時間と比較し、この比較に基づいて「マスター」ダイを選択し得る。本明細書で使用するマスタダイは、最も小さい保持時間を有する特定のメモリデバイスのダイに対応する。たとえば、第3の保持時間が第1の保持時間よりも大きいという判定に応答して、メモリコントローラ102は、第1のダイ202を第1のメモリデバイス104のマスタダイとして選択し得る。あるいは、メモリコントローラ102は、第1の保持時間が第3の保持時間よりも大きいという判定に応答して、第3のダイ204を第1のメモリデバイス104のマスタダイとして選択し得る。

#### 【0036】

同様に、メモリコントローラ102は、第2のダイ206の第2の保持時間と、第4のダイ208の第4の保持時間とを、それぞれ、第2のモードレジスタ144および第4のモードレジスタ244から周期的に読み取るように構成され得る。たとえば、メモリコントローラ102は、第2のダイ206と第4のダイ208との間の保持時間変動を経時的に追跡し得る。メモリコントローラ102は、第2の保持時間を第4の保持時間と比較し、この比較に基づいてマスタダイを選択し得る。たとえば、第4の保持時間が第2の保持時間よりも大きいという判定に応答して、メモリコントローラ102は、第2のダイ206を第2のメモリデバイス106のマスタダイとして選択し得る。あるいは、メモリコントローラ102は、第4の保持時間が第2の保持時間よりも大きいという判定に応答して、第4のダイ208を第2のメモリデバイス106のマスタダイ

10

20

30

40

50

として選択し得る。

【0037】

マスタダイは、リフレッシュアヘッド(RFA)側波帯シグナリングを駆動し得る。たとえば、第1のリフレッシュコントローラ132は、第1のダイ202が第1のメモリデバイス104のマスタダイである場合、RFAバス120を介してRFA信号(たとえば、第1の信号)をメモリコントローラ102に送り得る。同様に、第3のリフレッシュコントローラ232は、第3のダイ204が第1のメモリデバイス104のマスタダイである場合、RFAバス120を介してRFA信号をメモリコントローラ102に送り得る。RFA信号は、第1のメモリデバイス104のメモリセル134、136、234、236をリフレッシュするように求める要求をメモリコントローラ102に示し得る。RFA信号は、第1のメモリデバイス104のマスタダイのリフレッシュ速度(たとえば、保持時間)に基づいて時々メモリコントローラ102に送られ得る。メモリデバイス104の残りのダイ(たとえば、最も短い保持時間を有しないダイ)は、マスタダイと同じ速度で(または、ほぼ同じ速度で)リフレッシュされる。10

【0038】

同様に、第2のリフレッシュコントローラ152は、第2のダイ206が第2のメモリデバイス106のマスタダイである場合、RFAバス120を介して第2のRFA信号をメモリコントローラ102に送り得る。第4のリフレッシュコントローラ252は、第4のダイ208が第2のメモリデバイス106のマスタダイである場合、RFAバス120を介して第2のRFA信号をメモリコントローラ102に送り得る。第2のRFA信号は、第2のメモリデバイス106のメモリセル154、156、254、256をリフレッシュするように求める要求をメモリコントローラ102に示し得る。20

【0039】

図2のシステム200は、第1および第2のメモリデバイス104、106が、第1のメモリデバイス104のマスタダイおよび第2のメモリデバイス106のマスタダイの保持時間に基づくりフレッシュ速度で内部リフレッシュ動作を実行することを可能にし得る。たとえば、システム200は、メモリデバイス104、106の各マスタダイの保持時間を判定するためにメモリデバイス104、106上に位置する温度センサ128、148、228、248を利用し得る。したがって、保持時間は、メモリセルの特定の特性(たとえば、温度およびプロセス変動)に基づいている場合があり、電子デバイス技術合同協議会(JEDEC)規格によって指定されるような、規格化された、または「最悪の場合」の保持時間(たとえば、32ミリ秒リフレッシュ時間)よりも長い場合がある。特定のメモリデバイスは、リフレッシュ動作が実行されるように要求するためにメモリコントローラ102にシグナリングする場合があり、メモリコントローラ102は、リフレッシュ動作中に特定のメモリデバイスに関連付けられたコマンドの実行を中止する場合がある。メモリコントローラ102は、特定のメモリデバイスにおいてリフレッシュ動作が行われる間に他のメモリデバイスに関連付けられたコマンドを実行し得る。したがって、システム200は、標準的な「自己リフレッシュ」モードと比較して処理効率を改善し得る。たとえば、システム200は、メモリコントローラ102が、アクティブ状態を維持し、他のメモリセルがリフレッシュ動作を受けている間にリフレッシュ動作を受けていないメモリセルにコマンドを送ることを可能にし得る。30

【0040】

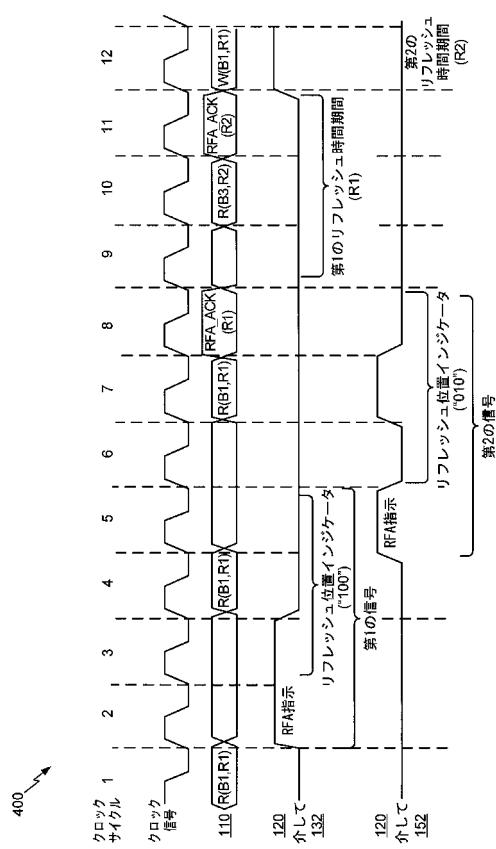

図3を参照すると、確認応答信号を使用するリフレッシュ方式のタイミング図300の特定の例示的な実施形態が示されている。タイミング図300は、図1のシステム100の構成要素に関して説明される。たとえば、タイミング図300は、12個のクロックサイクルの期間の間の、図1のシステム100のコマンドバス110上およびRFAバス120上のシグナリング活動を示す。40

【0041】

メモリコントローラ102は、第1のクロックサイクル中に、第1のメモリデバイス104(たとえば、第1のランク(R1))のメモリセル134の第1のバンク(B1)に記憶されたデータを読み取るためにコマンドバス110を介してリードコマンドR(B1,R1)を発出/実行し得る。第1のリフレッシュコントローラ132は、第2のクロックサイクル中に、RFAバス120を介して第1の信号(たとえば、RFA信号)をメモリコントローラ102に送るか、またはメモリコントロー50

ラ102に対して第1の信号をアサートし得る。たとえば、論理高電圧レベル信号(たとえば、「論理「1」)は、特定のメモリセルがリフレッシュされる必要があることを示す(たとえば、「RFA指示」)ために、第2のクロックサイクル中にRFAバス120を介してメモリコントローラ102に伝送され得る。どのメモリセルがリフレッシュされる必要があるかを識別する情報は、初期論理高電圧レベル信号の後にRFAバス120上で直列に伝送され得る。たとえば、「リフレッシュ位置インジケータ」は、第3、第4、および第5のクロックサイクルにわたってRFAバス120を介してメモリコントローラ102に直列に伝送され得る。例示的な実施形態では、リフレッシュ位置インジケータ(「100」)は、リフレッシュされる必要があるメモリセルが第1のランク(R1)内のメモリセル134の第1のバンク(B1)であることを示し得る。

10

## 【0042】

たとえば、メモリコントローラ102は、RFAバス120上で第1の信号を受け取った後、特定の時間期間の間にメモリセル134の第1のバンクに関連付けられたコマンドを実行し続ける場合がある。たとえば、メモリコントローラ102は、第3～第7のクロックサイクル中に、メモリセル134の第1のバンクに記憶されたデータを読み取るためにコマンドバス110を介して1つまたは複数のリードコマンドR(B1,R1)を発出/実行し得る。しかしながら、メモリコントローラ102は、メモリセル134の第1のバンクに関連付けられたすべてのコマンドの実行を完了することに応答して、メモリセル134の第1のバンク上のコマンドの実行を中止する場合があり、確認応答信号を第1のリフレッシュコントローラ132に発出する場合がある。たとえば、例示的な実施形態では、メモリコントローラ102は、第8のクロックサイクル中にコマンドバス110を介して第1の確認応答信号RFA\_ACK(R1)を第1のリフレッシュコントローラ132に発出する場合がある。第1の確認応答信号RFA\_ACK(R1)は、(メモリセル134の第1のバンクを含む)第1のランク(R1)に関連付けられたコマンドの実行が第1のリフレッシュ時間期間(たとえば、第9、第10、および第11のクロックサイクル)の間に中止されたことを第1のリフレッシュコントローラ132に示し得る。

20

## 【0043】

第1のリフレッシュコントローラ132は、第1のリフレッシュ時間期間の間に、メモリセル134の第1のバンクおよびメモリセル136の第2のバンクをリフレッシュする。さらに、メモリコントローラ102は、第1のリフレッシュ時間期間の間に他のランク(たとえば、第2のメモリデバイス106)に関連付けられた他のコマンドを実行し得る。たとえば、メモリコントローラ102は、第10のクロックサイクル中に第2のランク(R2)(たとえば、第2のメモリデバイス106)内のメモリセル154の第3のバンク(B3)に位置するデータを読み取るためにリードコマンドR(B3,R2)を実行し得る。

30

## 【0044】

メモリコントローラ102は、第1のリフレッシュ時間期間が満了した後(たとえば、第11のクロックサイクルの後)、(いまリフレッシュされた)第1のメモリデバイス104内のメモリセルに関連付けられたコマンドの発出/実行を再開し得る。たとえば、メモリコントローラ102は、第1のメモリデバイス104のメモリセル134の第1のバンクにデータを書き込むためにライトコマンドW(B1,R1)を実行し得る。

40

## 【0045】

図3のタイミング図300によって示されるリフレッシュ方式を実装することにより、第1のメモリデバイス104がリフレッシュ動作を受けている間に、メモリコントローラ102が、第2のメモリデバイス106に対するコマンドを実行することが可能になる。たとえば、メモリコントローラ102は、第1のランクの第1のリフレッシュ時間期間の間に、アクティブ状態を維持し、コマンド(たとえば、R(B3,R2))を第2のメモリデバイス106に発出し得る。したがって、第1のメモリデバイス104内のメモリセル134、136および第2のメモリデバイス106内のメモリセル154、156が異なる保持時間を有するシナリオでは、メモリコントローラ102は、他方のメモリデバイスがリフレッシュされている間に一方のメモリデバイスに対するコマンドを実行し得る。

## 【0046】

50

図4を参照すると、確認応答信号を使用するリフレッシュ方式のタイミング図400の別の特定の例示的な実施形態が示されている。タイミング図400は、図1のシステム100の構成要素に関して説明される。タイミング図400は、図3に関して説明したように、コマンドバス110およびRFAバス120上のシグナリング活動を組み込む。

#### 【0047】

RFAバス120上の活動は、第1～第4のクロックサイクル中に、図3に関して説明したように、第1のリフレッシュコントローラ132に関連付けられ得る。第2のリフレッシュコントローラ152は、第5のクロックサイクル中に、RFAバス120を介して第2の信号(たとえば、RF A信号)をメモリコントローラ102に送り得る。たとえば、論理高電圧レベル信号は、特定のメモリセルがリフレッシュされる必要があることを示す(たとえば、「RFA指示」)ために、第5のクロックサイクル中にRFAバス120を介してメモリコントローラ102に伝送され得る。どのメモリセルがリフレッシュされる必要があるかを識別する情報は、初期論理高電圧レベル信号の後にRFAバス120上で直列に伝送され得る。たとえば、「リフレッシュ位置インジケータ(「(001)」)」は、第6、第7、および第8のクロックサイクルにわたってRFAバス120を介してメモリコントローラ102に直列に伝送され得る。例示的な実施形態では、リフレッシュ位置インジケータ(「001」)は、リフレッシュされる必要があるメモリセルが第2のランク(R2)(第2のメモリデバイス106)内のメモリセル156の第4のバンク(B4)であることを示し得る。

10

#### 【0048】

例示的な実施形態では、第1のリフレッシュコントローラ132からの第1のRFA信号および第2のリフレッシュコントローラ152からの第2のRFA信号は、重複し得る。たとえば、第1のRFA信号は、図3に関して説明したように、第2、第3、第4、および第5のクロックサイクルにわたって伝送される4ビット信号であり得る。第2のRFA信号は、第5、第6、第7、および第8のクロックサイクルにわたって伝送される4ビット信号であり得る。このシナリオでは、メモリコントローラ102は、第1のメモリデバイス104と第2のメモリデバイス106との間でリフレッシュ動作を交互交替するために(第2のRFA信号に関連付けられた)第2の確認応答信号を第2のリフレッシュコントローラ152に送ることを遅延させ得る。たとえば、メモリコントローラ102は、第11のクロックサイクル(たとえば、第1のリフレッシュ時間期間の最後のクロックサイクル)中にコマンドバス110を介して第2の確認応答信号RFA\_ACK(R2)を第2のリフレッシュコントローラ152に発出する場合がある。第2の確認応答信号RFA\_A CK(R2)は、(メモリセル156の第4のバンクを含む)第2のランク(R2)に関連付けられたコマンドの実行が第2のリフレッシュ時間期間の間に中止されたことを第2のリフレッシュコントローラ152に示す。第2のランク(R2)の第2のリフレッシュ時間期間は、第1のリフレッシュ時間期間が終了した後(たとえば、第11のクロックサイクルの後)に開始し得る。第2のリフレッシュコントローラ152は、第2のリフレッシュ時間期間の間に、メモリセル134、136の第1および第2のバンクが読み取り/書き込み動作に利用可能である間にメモリセル154の第3のバンクおよびメモリセル156の第4のバンクをリフレッシュし得る。

20

30

#### 【0049】

図4のタイミング図400によって示されるリフレッシュ方式を実装することにより、システム性能の向上が可能になり得る。たとえば、第1のメモリデバイス104および第2のメモリデバイス106のリフレッシュ動作を交互交替することにより、他方のメモリデバイス104、106がリフレッシュ動作を受けている間に、メモリコントローラ102が、一方のメモリデバイス104、106に対するコマンドを継続的に実行することが可能になる。

40

#### 【0050】

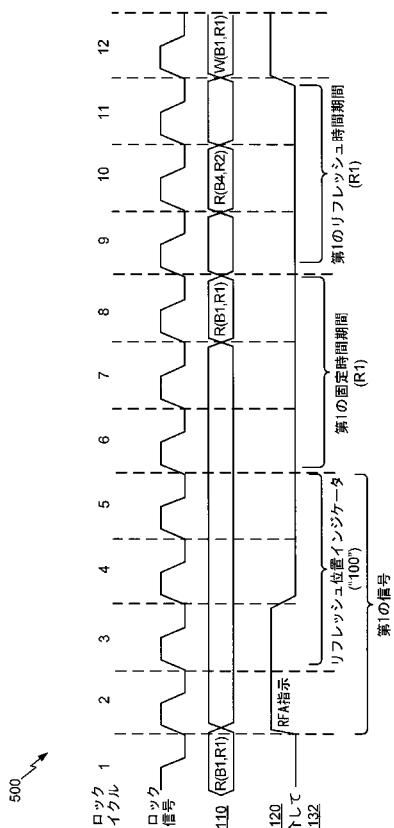

図5を参照すると、固定タイマを使用するリフレッシュ方式のタイミング図500の特定の例示的な実施形態が示されている。タイミング図500は、図1のシステム100の構成要素に関して説明される。たとえば、タイミング図500は、12個のクロックサイクルの期間の間の、図1のシステム100のコマンドバス110およびRFAバス120上のシグナリング活動を示す。

#### 【0051】

50

第1～第5のクロックサイクルの動作は、図3を参照しながら説明したように進行し得る。図3では、リフレッシュを実行する前に第1のリフレッシュコントローラ132が確認応答信号を待つが、図5では、第1のリフレッシュコントローラ132は、第1の信号を送ることに応答して第1の固定時間期間の間にリフレッシュ動作を一時停止するように構成され、第1の固定時間期間の後にリフレッシュを開始する。たとえば、第1のリフレッシュコントローラ132は、第6、第7、および第8のクロックサイクル中はリフレッシュ動作を一時停止し得る。第1の固定時間期間は、製造中に、メモリコントローラ102内にプログラミングされ、第1のメモリデバイス104内にプログラミングされ得る。図5の例示的な実施形態では、第1の固定時間期間は、3つのクロックサイクルである。メモリコントローラ102は、第1の固定時間期間の間に、メモリセル134の第1のバンクに関連付けられたコマンドを発出/実行し得る。たとえば、例示的な実施形態では、メモリコントローラ102は、第8のクロックサイクル中(たとえば、第1の固定時間期間の間)に、メモリセル134の第1のバンクに記憶されたデータを読み取るためにコマンドバス110を介してリードコマンドR(B1,R1)を発出/実行し得る。第1のメモリデバイス104は、第1の固定時間期間の間に、メモリセル134の第1のバンクに関連付けられたコマンドを実行することもできる。

10

## 【0052】

メモリコントローラ102は、第1の固定時間期間の満了において、メモリセル134の第1のバンクに関連付けられたコマンドの実行を自動的に中止するように構成される場合があり、第1のリフレッシュコントローラ132は、メモリセル134の第1のバンクとメモリセル136の第2のバンクとを自動的にリフレッシュし始めるように構成される場合がある。たとえば、メモリコントローラ102は、第8のクロックサイクルの終了時に、第1のリフレッシュ時間期間の間に第1のランク(たとえば、第1のメモリデバイス104)に対するコマンドの実行を中止し得る。第1のリフレッシュコントローラ132は、第1のリフレッシュ時間期間(たとえば、第9、第10、第11のクロックサイクル)の間に、メモリセル134の第1のバンクをリフレッシュする場合があり、メモリコントローラ102は、他のランクに対するコマンドを発出/実行する場合がある。たとえば、メモリコントローラ102は、第10のクロックサイクル中に第2のメモリデバイス106のメモリセル156の第4のバンク内のデータを読み取るためにリードコマンドR(B4,R2)を発出し得る。

20

## 【0053】

メモリコントローラ102は、第1のリフレッシュ時間期間が満了した後(たとえば、第11のクロックサイクルの後)、他のコマンドを第1のメモリデバイス104に発出し得る。たとえば、メモリコントローラ102は、第1のメモリデバイス104のメモリセル134の第1のバンクにデータを書き込むためにライトコマンドW(B1,R1)を実行し得る。第1のリフレッシュコントローラ132は、第1のリフレッシュ時間期間の後、RFAバス120を介してメモリコントローラ102に対して別のRFA信号をアサートし得る。

30

## 【0054】

図5のタイミング図500によって示されたリフレッシュ方式を実装することは、第1のリフレッシュコントローラ132への確認応答信号の通信を控えることによってコマンドバス110上のトラフィックを低減する。たとえば、リフレッシュ動作を開始するために第1の固定時間期間を利用することにより、図3に関して説明した、第8のクロックサイクル中に確認応答信号を発出するのとは反対に、メモリコントローラ102が、第8のクロックサイクル中にコマンド(たとえば、R(B1,R1))をメモリセル134の第1のバンクに発出することが可能になる。

40

## 【0055】

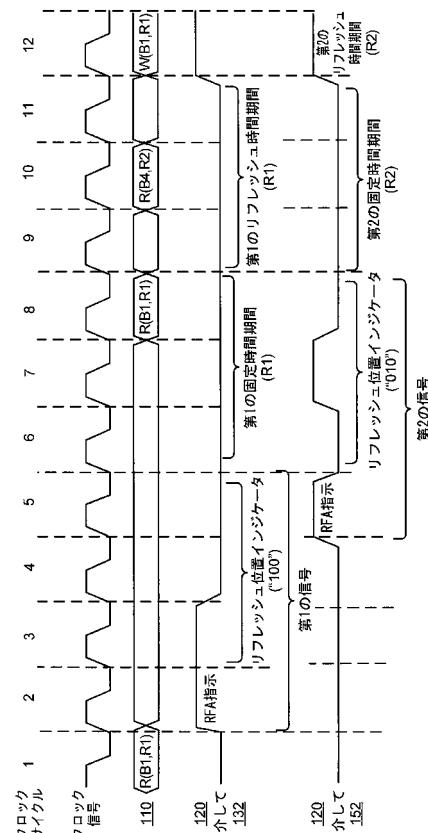

図6を参照すると、固定タイマを使用するリフレッシュ方式のタイミング図600の別の特定の例示的な実施形態が示されている。タイミング図600は、図1のシステム100の構成要素に関して説明される。タイミング図600は、図5に関して説明したように、コマンドバス110およびRFAバス120上のシグナリング活動を組み込む。

## 【0056】

RFAバス120上の活動は、第1～第4のクロックサイクル中に、図5に関して説明したよう

50

に、第1のリフレッシュコントローラ132に関連付けられ得る。第2のリフレッシュコントローラ152は、第5のクロックサイクル中に、RFAバス120を介して第2の信号(たとえば、RFA信号)をメモリコントローラ102に送り得る。たとえば、論理高電圧レベル信号は、特定のメモリセルがリフレッシュされる必要があることを示すために、第5のクロックサイクル中にRFAバス120を介してメモリコントローラ102に伝送され得る。どのメモリセルがリフレッシュされる必要があるかを識別する情報は、初期論理高電圧レベル信号の後にRFAバス120上で直列に伝送され得る。たとえば、「リフレッシュ位置インジケータ((「001」))」は、第6、第7、および第8のクロックサイクルにわたってRFAバス120を介してメモリコントローラ102に直列に伝送され得る。例示的な実施形態では、リフレッシュ位置インジケータ(「001」)は、リフレッシュされる必要があるメモリセルが第2のランク(R2)内のメモリセル156の第4のバンク(B4)であることを示し得る。10

#### 【0057】

第2のリフレッシュコントローラ152は、第2の信号を送ることに応答して第2の固定時間期間の間にリフレッシュ動作を一時停止するように構成され得る。たとえば、第2のリフレッシュコントローラ152は、第9、第10、および第11のクロックサイクル中(たとえば、第1のリフレッシュ時間期間の間)はリフレッシュ動作を一時停止し得る。第2の固定時間期間は、製造中に、メモリコントローラ102内にプログラミングされ、第2のメモリデバイス106内にプログラミングされ得る。メモリコントローラ102は、第2の固定時間期間の間に、メモリセル156の第4のバンクに関連付けられたコマンドを発出/実行し得る。たとえば、例示的な実施形態では、メモリコントローラ102は、第10のクロックサイクル中に、メモリセル156の第4のバンク(B4)に記憶されたデータを読み取るためにコマンドバス110を介してリードコマンドR(B4,R2)を発出/実行し得る。第2のメモリデバイス106は、第2の固定時間期間の間に、メモリセル156の第4のバンクに関連付けられたコマンドを実行することもできる。20

#### 【0058】

メモリコントローラ102は、第2の固定時間期間の満了において、メモリセル156の第4のバンクに関連付けられたコマンドの実行を中止するように構成され、第2のリフレッシュコントローラ152は、メモリセル156の第4のバンクをリフレッシュするように構成される。たとえば、メモリコントローラ102は、第11のクロックサイクルの終了時に、第2のリフレッシュ時間期間の間に第2のランク(たとえば、第2のメモリデバイス106)に対するコマンドの実行を中止し得る。第2のリフレッシュコントローラ152は、第2のリフレッシュ時間期間の間に、メモリセル156の第4のバンクをリフレッシュする場合があり、メモリコントローラ102は、他のランクに対するコマンドを発出/実行する場合がある。たとえば、メモリコントローラ102は、第1のメモリデバイス104のメモリセル134の第1のバンクにデータを書き込むためにライトコマンドW(B1,R1)を発出し得る。30

#### 【0059】

図6のタイミング図600によって示されるリフレッシュ方式を実装することにより、システム性能の向上が可能になり得る。たとえば、第1のメモリデバイス104および第2のメモリデバイス106のリフレッシュ動作を交互交替することにより、他方のメモリデバイス104、106がリフレッシュ動作を受けている間に、メモリコントローラ102が、一方のメモリデバイス104、106に対するコマンドを継続的に実行することが可能になる。40

#### 【0060】

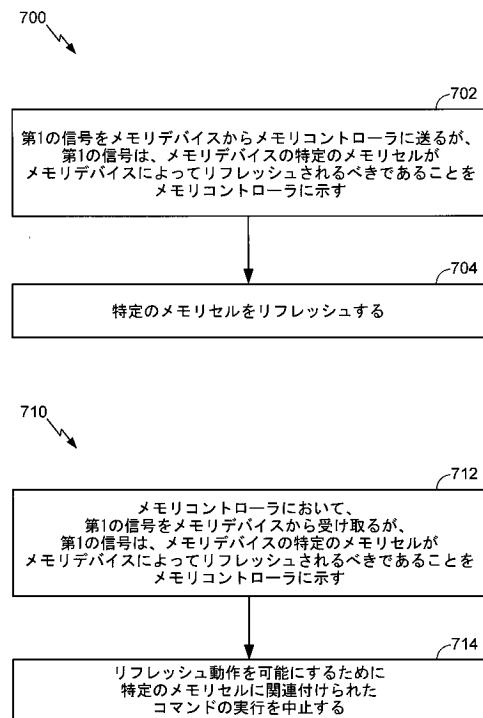

図7を参照すると、メモリセルをリフレッシュするための方法700、710の特定の実施形態を示すフローチャートが示されている。図7の第1の方法700は、図1の第1のメモリデバイス104、および/または図1の第2のメモリデバイス106などのメモリデバイスによって実行され得る。図7の第2の方法710は、図1～図2のメモリコントローラ102などのメモリコントローラによって実行され得る。

#### 【0061】

第1の方法700は、702において、第1の信号をメモリデバイスからメモリコントローラに送るステップを含み得る。たとえば、図1の第1のリフレッシュコントローラ132は、第1の50

信号(たとえば、RFA情報)を第1のメモリデバイス104からメモリコントローラ102に送り得る。第1の信号は、第1のメモリデバイス106の特定のメモリセルが第1のリフレッシュコントローラ132によってリフレッシュされるべきであることをメモリコントローラ102に示し得る。たとえば、第1の信号は、メモリセル134、136のどのバンクがリフレッシュされるべきであるかをメモリコントローラ102に示し得る。図3～図6に関して説明したように、第1の信号は、リフレッシュされる必要があるメモリセルが第1のランク(R1)内のメモリセル134の第1のバンク(B1)であることを示すためにリフレッシュ位置インジケータ(「100」)を含み得る。

#### 【0062】

第1の方法700は、704において、特定のメモリセルをリフレッシュするステップをさらに含む。たとえば、特定の実施形態では、第1のリフレッシュコントローラ132は、確認応答信号をメモリコントローラ102から受け取ることに応答して、メモリセル134の第1のバンクをリフレッシュし得る。たとえば、図2および図3に関して説明したように、メモリコントローラ102は、第8のクロックサイクル中にコマンドバス110を介して第1の確認応答信号RFA\_ACK(R1)を第1のリフレッシュコントローラ132に発出する。第1の確認応答信号RFA\_ACK(R1)は、(メモリセル134の第1のバンクを含む)第1のランク(R1)に関連付けられたコマンドの実行が第1のリフレッシュ時間期間(たとえば、第9、第10、および第11のクロックサイクル)の間に中止されたことを第1のリフレッシュコントローラ132に示す。第1のリフレッシュコントローラ132は、第1のリフレッシュ時間期間の間に、メモリセル134の第1のバンクをリフレッシュし得る。

10

20

30

40

50

#### 【0063】

別の特定の実施形態では、第1のリフレッシュコントローラ132は、固定時間期間の満了に応答して、メモリセル134の第1のバンクをリフレッシュし得る。たとえば、図5および図6に関して説明したように、メモリコントローラ102は、第1の固定時間期間の満了時に、メモリセル134の第1のバンクに関連付けられたコマンドの実行を中止し、第1のリフレッシュコントローラ132は、メモリセル134の第1のバンクをリフレッシュする。たとえば、メモリコントローラ102は、第8のクロックサイクルの終了時に、第1のリフレッシュ時間期間の間に第1のランク(たとえば、第1のメモリデバイス104)に対するコマンドの実行を中止する。第1のリフレッシュコントローラ132は、第1のリフレッシュ時間期間(たとえば、第9、第10、第11のクロックサイクル)の間に、メモリセル134の第1のバンクをリフレッシュし、メモリコントローラ102は、他のランクに対するコマンドを発出/実行する場合がある。

#### 【0064】

第1の方法700は図1のメモリデバイス104、106のうちの少なくとも1つによって実行され得るが、第2の方法710は、図1のメモリコントローラ102によって実行され得る。第2の方法710は、712で、メモリコントローラにおいて、第1の信号をメモリデバイスから受け取るステップを含み得る。たとえば、図1では、メモリコントローラ102は、RFAバス120を介して第1の信号(たとえば、RFA信号)を受け取る場合がある。第1の信号は、第1のメモリデバイス106の特定のメモリセルが第1のリフレッシュコントローラ132によってリフレッシュされるべきであることをメモリコントローラ102に示し得る。たとえば、第1の信号は、メモリセル134、136のどのバンクがリフレッシュされるべきであるかをメモリコントローラ102に示し得る。図2～図5に関して説明したように、第1の信号は、リフレッシュされる必要があるメモリセルが第1のランク(R1)内のメモリセル134の第1のバンク(B1)であることを示すためにリフレッシュ位置インジケータ(「100」)を含み得る。

#### 【0065】

714において、リフレッシュ動作を可能にするために、特定のメモリセルに関連付けられたコマンドの実行が中止され得る。たとえば、メモリコントローラ102は、特定のメモリセルがリフレッシュ動作を受けているときにコマンドを実行しないように、特定のメモリセルに関連付けられたコマンドの実行を、特定のメモリセルに関連付けられたリフレッシュ動作と調整し得る。特定の実施形態では、メモリコントローラ102は、第1のメモリデ

バイス104に対するコマンドがリフレッシュ時間期間の間に中止されたことを示すために、確認応答信号を第1のメモリデバイス104に送り得る。図2に関して説明したように、メモリコントローラ102は、第8のクロックサイクル中にコマンドバス110を介して第1の確認応答信号RFA\_ACK(R1)を第1のリフレッシュコントローラ132に発出する。第1の確認応答信号RFA\_ACK(R1)は、(メモリセル134の第1のバンクを含む)第1のランク(R1)に関連付けられたコマンドの実行が第1のリフレッシュ時間期間(たとえば、第9、第10、および第11のクロックサイクル)の間に中止されたことを第1のリフレッシュコントローラ132に示す。第1のリフレッシュコントローラ132は、第1のリフレッシュ時間期間の間に、メモリセル134の第1のバンクをリフレッシュし得る。

## 【0066】

別の特定の実施形態では、メモリコントローラ102は、第1の信号を受け取った後、固定時間期間の間に特定のメモリセルに関連付けられたコマンドを実行し、固定時間期間の満了に応答して実行を中止し得る。図5に関して説明したように、メモリコントローラ102は、第1の固定時間期間の間に、メモリセル134の第1のバンクに関連付けられたコマンドを発出/実行し得る。たとえば、メモリコントローラ102は、第8のクロックサイクル中(たとえば、第1の固定時間期間の間)に、メモリセル134の第1のバンクに記憶されたデータを読み取るためにコマンドバス110を介してリードコマンドR(B1,R1)を発出し得る。メモリコントローラ102は、第1の固定時間期間の満了時に、メモリセル134の第1のバンクに関連付けられたコマンドの実行を中止し、第1のリフレッシュコントローラ132は、メモリセル134の第1のバンクをリフレッシュする。

## 【0067】

図7の方法700、710は、標準的な「自己リフレッシュ」モードと比較して処理効率を改善し得る。たとえば、方法700、710は、メモリコントローラ102が、アクティブ状態を維持し、特定のメモリセルがリフレッシュ動作を受けている間にリフレッシュ動作を受けていないメモリセルにコマンドを送ることを可能にする。

## 【0068】

特定の実施形態では、図7の方法700、710は、中央処理装置(CPU)、デジタル信号プロセッサ(DSP)、もしくはコントローラなどの処理ユニットのハードウェア(たとえば、フィールドプログラマブルゲートアレイ(FPGA)デバイス、特定用途向け集積回路(ASIC)など)を介して、ファームウェアデバイスを介して、またはこれらの任意の組合せによって実装され得る。例として、方法700、710は、命令を実行するプロセッサによって実行され得る。したがって、図1～図7は、メモリデバイスのメモリセルをリフレッシュするシステム、リフレッシュ方式、および方法を含む例を示す。

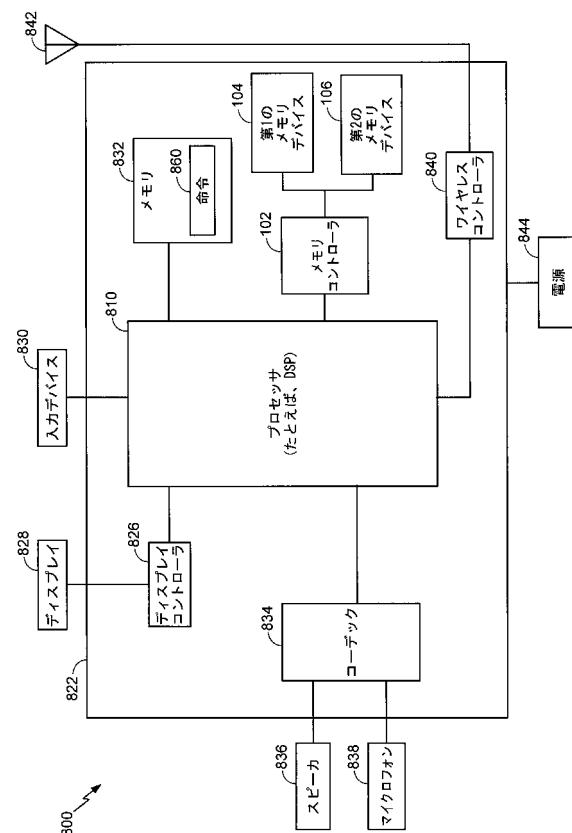

## 【0069】

図8を参照すると、ワイヤレス通信デバイスの特定の例示的な実施形態のブロック図が示され、全体が800と表される。デバイス800は、メモリ832に結合されたプロセッサ810(たとえば、中央処理装置(CPU)、デジタル信号プロセッサ(DSP)など)を含む。メモリ832は、図7の方法および図3～図6に開示したリフレッシュ方式などの、本明細書で開示する方法および処理を実行するために、プロセッサ810および/または図1～図2のメモリコントローラ102によって実行可能な命令860を含み得る。

## 【0070】

メモリ832は、ランダムアクセスメモリ(RAM)、磁気抵抗ランダムアクセスメモリ(MRAM)、スピントルクトランスファーMRAM(STT-MRAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、プログラマブル読み取り専用メモリ(PROM)、消去可能プログラマブル読み取り専用メモリ(EPROM)、電気的消去可能プログラマブル読み取り専用メモリ(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、またはコンパクトディスク読み取り専用メモリ(CD-ROM)などのメモリデバイスであり得る。メモリデバイスは、コンピュータ(たとえば、メモリコントローラ120および/またはプロセッサ810)によって実行されるとき、図7の方法700、710の少なくとも一部分をコンピュータに実行させ得る命令(たとえば、命令860)を含み得る。図1および図2の第1のメモリデバイス104、および図1および図2の第2のメモリデバ

10

20

30

40

50

イス106は、メモリコントローラ102に結合され得る。2つのメモリデバイス104、106が示されているが、他の実施形態では、追加のメモリデバイスが、メモリコントローラ102に結合され得る。非限定的な例として、7つの追加のメモリデバイスが、メモリコントローラ102に結合され得る。

#### 【0071】

図8は、プロセッサ810およびディスプレイ828に結合されたディスプレイコントローラ826も示す。図示するように、エンコーダ/デコーダ(コードック)834が、プロセッサ810に結合され得る。スピーカ836およびマイクロフォン838が、コードック834に結合され得る。図8は、プロセッサ810およびアンテナ842に結合されたワイヤレスコントローラ840も示す。特定の実施形態では、プロセッサ810、ディスプレイコントローラ826、メモリ832、コードック834、およびワイヤレスコントローラ840は、システムインパッケージデバイスまたはシステムオンチップデバイス(たとえば、移動局モデム(MSM))822に含まれる。特定の実施形態では、タッチスクリーンおよび/またはキーパッドなどの入力デバイス830ならびに電源844が、システムオンチップデバイス822に結合される。その上、特定の実施形態では、図8に示されるように、ディスプレイ828、入力デバイス830、スピーカ836、マイクロフォン838、アンテナ842、および電源844は、システムオンチップデバイス822の外部に存在している。しかしながら、ディスプレイ828、入力デバイス830、スピーカ836、マイクロフォン838、アンテナ842、および電源844の各々は、インターフェースまたはコントローラなどのシステムオンチップデバイス822の構成要素に結合され得る。

10

#### 【0072】

説明した実施形態と併せて、第1の装置は、第1の信号(たとえば、RFA信号)をメモリデバイスからメモリコントローラに送るための手段を含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す。たとえば、第1の信号を送るための手段は、図1および図2の第1のリフレッシュコントローラ132、図1および図2の第2のリフレッシュコントローラ152、図2の第3のリフレッシュコントローラ232、図2の第4のリフレッシュコントローラ252、図1および図2の第1のメモリデバイス104、図1および図2の第2のメモリデバイス106、図1および図2のRFAバス、第1の信号を送るための1つもしくは複数の他のデバイス、回路、モジュール、または命令、あるいはそれらの任意の組合せを含み得る。

20

#### 【0073】

第1の装置は、特定のメモリセルをリフレッシュするための手段も含み得る。たとえば、特定のメモリセルをリフレッシュするための手段は、図1および図2の第1のリフレッシュコントローラ132、図1および図2の第1のリフレッシュタイム130、図1および図2の第2のリフレッシュコントローラ152、図1および図2の第2のリフレッシュタイム150、図2の第3のリフレッシュコントローラ232、図2の第3のリフレッシュタイム230、図2の第4のリフレッシュコントローラ252、図2の第4のリフレッシュタイム550、図1および図2の第1のメモリデバイス104、図1および図2の第2のメモリデバイス106、特定のメモリセルをリフレッシュするための1つもしくは複数の他のデバイス、回路、モジュール、または命令、あるいはそれらの任意の組合せを含み得る。

30

#### 【0074】

説明した実施形態と併せて、第2の装置は、第1の信号(たとえば、RFA信号)をメモリデバイスから受け取るための手段を含む。第1の信号は、メモリデバイスの特定のメモリセルがメモリデバイスによってリフレッシュされるべきであることを、前記受け取るための手段に示す。第1の信号を受け取るための手段は、図1および図2のメモリコントローラ102、図1および図2のRFAバス120、第1の信号を受け取るための1つもしくは複数の他のデバイス、回路、モジュール、または命令、あるいはそれらの任意の組合せを含み得る。

40

#### 【0075】

第2の装置は、リフレッシュ動作を可能にするために特定のメモリセルに関連付けられたコマンドの実行を中止するための手段も含み得る。たとえば、特定のメモリセルに関連付けられたコマンドの実行を中止するための手段は、図1および図2のメモリコントローラ

50

102、図1および図2のコマンドバス110、特定のメモリセルに関連付けられたコマンドの実行を中止するための1つもしくは複数の他のデバイス、回路、モジュール、または命令、あるいはそれらの任意の組合せを含み得る。

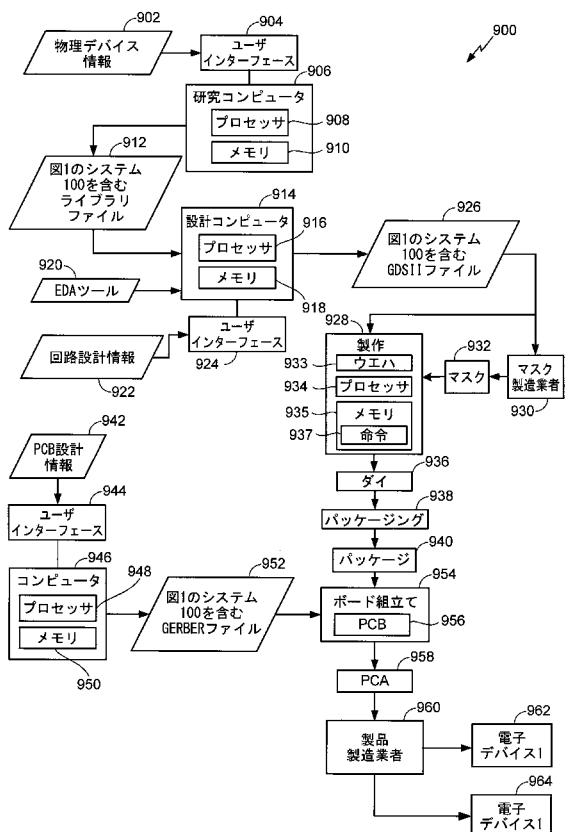

【0076】

上記の開示されるデバイスおよび機能は、コンピュータ可読媒体上に格納されたコンピュータファイル(たとえばRTL、GDSII、GERBERなど)内に設計および構成され得る。いくつかの、またはすべてのそのようなファイルが、そのようなファイルに基づいてデバイスを製作する製作ハンドラに提供され得る。得られる製品は半導体ウエハを含み、次いで半導体ウエハが半導体ダイに切断され、半導体チップ内にパッケージングされる。次いで、チップは、通信デバイス(たとえば、モバイルフォン)、タブレット、ラップトップ、携帯情報端末(PDA)、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、固定位置データユニット、またはコンピュータなどのデバイス内に採用され得る。図9は、電子デバイス製造プロセス900の特定の例示的実施形態を示す。

10

【0077】

物理デバイス情報902が、研究コンピュータ906などの製造プロセス900において受信される。物理的なデバイス情報902は、図1のシステム100、図2のシステム200、またはこれらの任意の組合せを含むデバイスなどの、半導体デバイスの少なくとも1つの物理的な特性を表す設計情報を含み得る。たとえば、物理デバイス情報902は、研究コンピュータ906に結合されたユーザインターフェース904を介して入力される物理パラメータ、材料特性、および構造情報を含み得る。研究コンピュータ906は、メモリ910などのコンピュータ可読媒体に結合された、1つまたは複数の処理コアなどのプロセッサ908を含む。メモリ910は、プロセッサ908に、物理デバイス情報902をファイルフォーマットに準拠するように変換させ、ライプラリファイル912を生成させるように実行可能なコンピュータ可読命令を格納し得る。

20

【0078】

特定の実施形態では、ライプラリファイル912は、変換された設計情報を含む少なくとも1つのデータファイルを含む。たとえば、ライプラリファイル912は、図1のシステム100、図2のシステム200、またはこれらの任意の組合せを含む半導体デバイスのライプラリを含んでもよく、このライプラリは、電子設計オートメーション(EDA)ツール920とともに使用するために提供される。

30

【0079】

ライプラリファイル912は、メモリ918に結合された、1つまたは複数の処理コアなどのプロセッサ916を含む設計コンピュータ914において、EDAツール920とともに使用され得る。EDAツール920は、設計コンピュータ914のユーザがライプラリファイル912のうちの、図1のシステム100、図2のシステム200、またはこれらの任意の組合せを含むデバイスを設計できるようにするために、プロセッサ実行可能命令としてメモリ918に記憶され得る。たとえば、設計コンピュータ914のユーザは、設計コンピュータ914に結合されたユーザインターフェース924を介して回路設計情報を922を入力することができる。回路設計情報922は、図1のシステム100、図2のシステム200、またはこれらの任意の組合せを含む半導体デバイスの少なくとも1つの物理的な特性を表す設計情報を含み得る。例示のために、回路設計特性は、特定の回路の識別および回路設計内の他の要素に対する関係、位置決め情報、フィーチャサイズ情報、相互接続情報、または半導体デバイスの物理的性質を表す他の情報を含み得る。

40

【0080】

設計コンピュータ914は、回路設計情報を922を含む設計情報をファイルフォーマットに準拠するように変換するように構成することができる。例示のために、ファイル形成は、回路レイアウトについての平面幾何形状、テキストラベル、および他の情報をグラフィックデータシステム(GDSII)ファイルフォーマットなどの階層フォーマットで表すデータベースバイナリファイルフォーマットを含み得る。設計コンピュータ914は、図1のシステム10

50

0、図2のシステム200、またはこれらの任意の組合せを含むデバイスについて説明する情報を含む、GDSIIファイル926などの変換された設計情報を含むデータファイルを生成するように構成され得る。例示のために、データファイルは、図1のシステム100、図2のシステム200、またはこれらの任意の組合せを含み、内部に追加の電子回路および構成要素をさらに含むシステムオンチップ(SOC)に対応する情報が含み得る。

#### 【0081】

GDSIIファイル926は、図1のシステム100、図2のシステム200、またはこれらの任意の組合せを含む半導体デバイスをGDSIIファイル926内の変換された情報に従って製造する製作プロセス928において受け取られ得る。たとえば、デバイス製造プロセスは、代表的なマスク932として示された、フォトリソグラフィプロセスとともに使用されるマスクなどの、1つまたは複数のマスクを作製するために、マスク製造業者930にGDSIIファイル926を提供することを含み得る。マスク932は、試験されて代表的なダイ936などのダイに分離され得る1つまたは複数のウエハ933を生成するために製作プロセスの間に使用してもよい。ダイ936は、図1のシステム100、図2のシステム200、またはこれらの任意の組合せを含む回路を含む。

10

#### 【0082】

特定の実施形態では、製造プロセス928は、プロセッサ934によって開始されるか、またはプロセッサ934によって制御され得る。プロセッサ934は、コンピュータ可読命令またはプロセッサ可読命令などの実行可能命令937を含むメモリ935にアクセスすることができる。実行可能命令は、プロセッサ934などのコンピュータによって実行可能な1つまたは複数の命令を含むことができる。製造プロセス928は、完全に自動化された、または部分的に自動化された製造システムによって実施され得る。たとえば、製造プロセス928は、自動化されてもよく、スケジュールに従って処理ステップを実行することができる。製造システムは、電子デバイスを形成するために1つまたは複数の動作を実行するための製造機器(たとえば、処理ツール)を含むことができる。

20

#### 【0083】

製造システムは、分散型アーキテクチャ(たとえば、階層)を有することができる。たとえば、製造システムは、分散型アーキテクチャに従って分散された、プロセッサ934などの1つもしくは複数のプロセッサ、メモリ935などの1つもしくは複数のメモリ、および/またはコントローラを含むことができる。分散型アーキテクチャは、1つまたは複数の低レベルシステムの動作を制御および/または開始する高レベルプロセッサを含むことができる。たとえば、製造プロセス928の高レベル部分は、プロセッサ934などの1つまたは複数のプロセッサを含むことができ、低レベルシステムは、各々、1つもしくは複数の対応するコントローラを含むことができ、または、1つもしくは複数の対応するコントローラによって制御され得る。特定の低レベルシステムの特定のコントローラは、高レベルシステムから1つまたは複数の命令(たとえば、コマンド)を受信することができ、サブコマンドを下位のモジュールまたはプロセスツールに発行することができ、高レベルシステムに状態データを通信し戻すことができる。1つまたは複数の低レベルシステムの各々は、製造機器の1つまたは複数の対応する部分(たとえば、処理ツール)に関連付けられ得る。特定の実施形態では、製造システムは、製造システム内に分散された複数のプロセッサを含むことができる。たとえば、製造システムの低レベルシステム構成要素のコントローラは、プロセッサ934などのプロセッサを含み得る。

30

#### 【0084】

代替的には、プロセッサ934は、製造システムの高レベルシステム、サブシステム、または構成要素の一部であり得る。別の実施形態では、プロセッサ934は、製造システムの様々なレベルおよび構成要素での分散処理を含む。

40

#### 【0085】

ダイ936は、パッケージングプロセス938に提供される場合があり、ここにおいて、ダイ936は、代表的なパッケージ940に組み込まれる。たとえば、パッケージ940は、システムインパッケージ(SiP)配置などの、単一のダイ936または複数のダイを含むことができる。

50

パッケージ940は、電子デバイスエンジニアリング連合評議会(JEDEC)規格などの1つまたは複数の規格または仕様に準拠するように構成され得る。

#### 【0086】

パッケージ940に関する情報が、コンピュータ946に格納される構成要素ライブラリなどを介して、様々な製品設計者に配布され得る。コンピュータ946は、メモリ950に結合された1つまたは複数の処理コアなどのプロセッサ948を含み得る。プリント回路板(PCB)ツールが、ユーザインターフェース944を介してコンピュータ946のユーザから受信されたPCB設計情報942を処理するために、プロセッサ実行可能命令としてメモリ950に格納され得る。PCB設計情報942は、回路基板上のパッケージングされた半導体デバイスの物理的位置決め情報を含む場合があり、パッケージングされた半導体デバイスは、図1のシステム100、図2のシステム200、またはこれらの任意の組合せを含むデバイスを含むパッケージ940に相当する。

10

#### 【0087】

コンピュータ946は、PCB設計情報942を変換して、パッケージングされた半導体デバイスの回路基板上での物理的な位置情報とともに、配線およびビアのような電気的な接続のレイアウトを含む、GERBERファイル952などのデータファイルを生成するように構成される場合があり、パッケージングされた半導体デバイスは、図1のシステム100、図2のシステム200、またはこれらの任意の組合せを含む、パッケージ940に対応する。別の実施形態では、変換されたPCB設計情報によって生成されるデータファイルは、GERBERフォーマット以外のフォーマットを有し得る。

20

#### 【0088】

GERBERファイル952は、ボード組立てプロセス954において受信され、GERBERファイル952内に格納される設計情報に従って製造される、代表的なPCB556などのPCBを作製するのに使用され得る。たとえば、GERBERファイル952は、PCB生産プロセスの様々なステップを実行するために、1つまたは複数の機械にアップロードされ得る。PCB556には、パッケージ940を含む電子構成要素が実装され、代表的なプリント回路アセンブリ(PCA)958が形成され得る。

30

#### 【0089】

PCA558が製品製造プロセス960において受信され、第1の代表的な電子デバイス962および第2の代表的な電子デバイス964などの1つまたは複数の電子デバイス内に統合され得る。例示的な非限定的な例として、第1の代表的な電子デバイス962、第2の代表的な電子デバイス964、またはその両方は、図1のシステム100、図2のシステム200、またはこれらの任意の組合せが統合される通信デバイス(たとえば、モバイルフォン)、タブレット、ラップトップ、携帯情報端末(PDA)、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、固定位置データユニット、およびコンピュータのグループから選択され得る。別の例示的な非限定的な例として、電子デバイス962および964のうちの1つまたは複数は、モバイルフォン、ハンドヘルドパソコン通信システム(PCS)ユニット、携帯情報端末などのポータブルデータユニット、全球測位システム(GPS)対応デバイス、ナビゲーションデバイス、メータ検針機器などの固定位置データユニット、または、データもしくはコンピュータ命令を記憶するもしくは引き出す任意の他のデバイス、またはそれらの任意の組合せなどの、遠隔ユニットであり得る。本開示の教示による遠隔ユニットに加えて、本開示の実施形態は、メモリおよびオンチップ回路を含む能動的な集積回路を含む、任意のデバイスにおいて適切に利用され得る。

40

#### 【0090】

図1のシステム100、図2のシステム200、またはこれらの任意の組合せを含むデバイスが、例示的なプロセス900において説明したように、製作され、処理され、かつ電子デバイスに組み込まれてもよい。たとえば、図1のメモリコントローラ102、図1の第1のメモリデバイス104、図1の第2のメモリデバイス106、またはこれらの任意の組合せは、電子デバイス内のダイに組み込まれ得る。電子デバイスは、通信デバイス、タブレット、ラップトッ

50

10

プ、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、携帯情報端末(PDA)、固定位置データユニット、またはコンピュータも含み得る。図1～図8に関して開示される実施形態の1つまたは複数の態様は、ライブラリファイル912、GDSIIファイル926、およびGERBERファイル952内など、様々な処理ステージにおいて含まれ、ならびに、調査コンピュータ906のメモリ910、設計コンピュータ914のメモリ918、コンピュータ946のメモリ950、基板アセンブリプロセス954においてなど様々なステージにおいて使用される1つまたは複数の他のコンピュータまたはプロセッサ(図示せず)のメモリにおいて格納され、また、マスク932、ダイ936、パッケージ940、PCA 958、プロトタイプ回路もしくはデバイス(図示せず)などの他の製品、またはその任意の組合せなどの1つまたは複数の他の物理実施形態に組み込まれ得る。物理デバイス設計から最終的製品までの製造の様々な代表的段階が示されるが、別の実施形態では、より少ない段階が使用されるか、または追加の段階が含まれる場合がある。同様に、プロセス900は、プロセス900の様々な段階を実行する単一のエンティティあるいは1つまたは複数のエンティティによって実行され得る。

#### 【0091】

20

本明細書で開示される実施形態とともに説明される様々な例示的な論理ロック、構成、モジュール、回路、およびアルゴリズムのステップは、電子的なハードウェア、ハードウェアプロセッサ等の処理デバイスにより実行されるコンピュータソフトウェア、またはこれら両方の組合せとして実装され得ることが、当業者にはさらに理解されよう。上記に、様々な例示的な構成要素、ロック、構成、モジュール、回路、およびステップについて、それらの機能に関して概略的に説明した。そのような機能をハードウェアとして実装するか、実行可能ソフトウェアとして実装するかは、特定の適用例および全体的なシステムに課される設計制約に依存する。当業者は、説明された機能を各々の特定の応用分野について様々な方式で実装し得るが、そのような実装形態は、本開示の範囲からの逸脱を引き起こすと解釈されるべきではない。

#### 【0092】

30

本明細書に開示する実施形態との関連で述べた方法またはアルゴリズムのステップは、ハードウェアにおいて直接に、または、プロセッサによって実行されるソフトウェアモジュールにおいて、またはこの2つの組合せにおいて具体化される場合がある。ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、磁気抵抗ランダムアクセスメモリ(MRAM)、スピントルクトランスファー-MRAM(STT-MRAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、プログラマブル読み取り専用メモリ(PROM)、消去可能プログラマブル読み取り専用メモリ(EPROM)、電気的消去可能プログラマブル読み取り専用メモリ(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、またはコンパクトディスク読み取り専用メモリ(CD-ROM)などのメモリデバイス内に常駐し得る。プロセッサがメモリデバイスから情報を読み取り、メモリデバイスに情報を書き込むことができるよう、例示的なメモリデバイスがプロセッサに結合される。代替として、メモリデバイスは、プロセッサに一体化され得る。プロセッサおよび記憶媒体は、特定用途向け集積回路(ASIC)内にあり得る。ASICは、コンピューティングデバイスまたはユーザ端末内にあり得る。代替として、プロセッサおよび記憶媒体は、コンピューティングデバイスまたはユーザ端末内に別個の構成要素として存在し得る。

#### 【0093】

40

開示される実施形態の前の説明は、開示される実施形態を当業者が作成または使用することを可能にするために提供される。これらの実施形態に対する様々な修正は、当業者には容易に明らかであり、本明細書で定義された原理は、本開示の範囲から逸脱することなく、他の実施形態に適用され得る。したがって、本開示は、本明細書に示す実施形態に限定するように意図されるものではなく、以下の特許請求の範囲によって定義される原理および新規な特徴と一致する可能な最も広い範囲を与えられるべきである。

#### 【符号の説明】

#### 【0094】

|     |                 |    |

|-----|-----------------|----|

| 100 | システム            |    |

| 102 | メモリコントローラ       |    |

| 104 | 第1のメモリデバイス      |    |

| 106 | 第2のメモリデバイス      |    |

| 108 | データバス           |    |

| 110 | コマンドバス          |    |

| 120 | RFAバス           |    |

| 124 | 第1のモードレジスタ      | 10 |

| 128 | 第1の温度センサ        |    |

| 130 | 第1のリフレッシュタイム    |    |

| 132 | 第1のリフレッシュコントローラ |    |

| 134 | メモリセル           |    |

| 136 | メモリセル           |    |

| 144 | 第2のモードレジスタ      |    |

| 148 | 第2の温度センサ        |    |

| 150 | 第2のリフレッシュタイム    |    |

| 152 | 第2のリフレッシュコントローラ |    |

| 154 | メモリセル           |    |

| 156 | メモリセル           |    |

| 200 | システム            | 20 |

| 202 | 第1のダイ           |    |

| 204 | 第3のダイ           |    |

| 206 | 第2のダイ           |    |

| 208 | 第4のダイ           |    |

| 224 | 第3のモードレジスタ      |    |

| 228 | 第3の温度センサ        |    |

| 230 | 第3のリフレッシュタイム    |    |

| 232 | 第3のリフレッシュコントローラ |    |

| 234 | メモリセル           |    |

| 236 | メモリセル           | 30 |

| 244 | 第4のモードレジスタ      |    |

| 248 | 第4の温度センサ        |    |

| 250 | 第4のリフレッシュタイム    |    |

| 252 | 第4のリフレッシュコントローラ |    |

| 254 | メモリセル           |    |

| 256 | メモリセル           |    |

| 800 | ワイヤレス通信デバイス     |    |

| 810 | プロセッサ           |    |

| 822 | システムオンチップデバイス   |    |

| 826 | ディスプレイコントローラ    | 40 |

| 828 | ディスプレイ          |    |

| 830 | 入力デバイス          |    |

| 832 | メモリ             |    |

| 834 | コーデック           |    |

| 836 | スピーカ            |    |

| 838 | マイクロフォン         |    |

| 840 | ワイヤレスコントローラ     |    |

| 842 | アンテナ            |    |

| 844 | 電源              |    |

| 860 | 命令              | 50 |

|     |                 |    |

|-----|-----------------|----|

| 900 | 電子デバイス製造プロセス    |    |

| 904 | ユーザインターフェース     |    |

| 906 | 研究コンピュータ        |    |

| 908 | プロセッサ           |    |

| 910 | メモリ             |    |

| 914 | 設計コンピュータ        |    |

| 916 | プロセッサ           |    |

| 918 | メモリ             |    |

| 924 | ユーザインターフェース     | 10 |

| 930 | マスク製造業者         |    |

| 932 | マスク             |    |

| 933 | ウエハ             |    |

| 934 | プロセッサ           |    |

| 935 | メモリ             |    |

| 937 | 命令              |    |

| 936 | ダイ              |    |

| 938 | パッケージング         |    |

| 940 | パッケージ           |    |

| 944 | ユーザインターフェース     |    |

| 946 | コンピュータ          | 20 |

| 948 | プロセッサ           |    |

| 950 | メモリ             |    |

| 956 | PCB             |    |

| 958 | プリント回路アセンブリ、PCA |    |

| 960 | 製品製造プロセス        |    |

| 962 | 電子デバイス1         |    |

| 964 | 電子デバイス1         |    |

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

## 【手続補正書】

【提出日】平成28年5月12日(2016.5.12)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

## 【特許請求の範囲】

## 【請求項1】

第1の信号をメモリデバイスからメモリコントローラに送るステップであって、前記第1の信号は、前記メモリデバイスの特定のメモリセルが前記メモリデバイスによってリフレッシュされるべきであることを前記メモリコントローラに示す、ステップを含む、方法であって、

前記メモリコントローラが、前記特定のメモリセルのリフレッシュ中に第2の信号を第2のメモリデバイスに送る、方法。

## 【請求項2】

前記第1の信号が、専用バスを介して送られる、請求項1に記載の方法。

## 【請求項3】

コマンドバスを介して確認応答信号を前記メモリコントローラから受け取るステップをさらに含む、請求項1に記載の方法。

## 【請求項4】

前記メモリコントローラが、前記確認応答信号を送ることに応答してリフレッシュ時間期間の間に前記特定のメモリセルに関連付けられたコマンドの実行を中止する、請求項3に記載の方法。

**【請求項 5】**

前記確認応答信号を受け取ることに応答して、前記特定のメモリセルをリフレッシュするステップをさらに含む、請求項3に記載の方法。

**【請求項 6】**

前記第1の信号を送ることに応答して固定時間期間の間に前記特定のメモリセルに関連付けられたリフレッシュ動作を一時停止するステップと、

前記固定時間期間の満了に応答して前記特定のメモリセルをリフレッシュするステップと

をさらに含む、請求項1に記載の方法。

**【請求項 7】**

前記メモリコントローラが、前記固定時間期間の間に前記特定のメモリセルに関連付けられたコマンドを実行することを許される、請求項6に記載の方法。

**【請求項 8】**

前記メモリコントローラが、前記固定時間期間の間に前記特定のメモリセルに関連付けられたコマンドを実行する、請求項6に記載の方法。

**【請求項 9】**

前記メモリコントローラが、前記固定時間期間の前記満了に応答して前記特定のメモリセルに関連付けられたコマンドの実行を中止する、請求項6に記載の方法。

**【請求項 10】**

前記メモリデバイスは、揮発性メモリデバイスである、請求項1に記載の方法。

**【請求項 11】**

前記メモリデバイスが、ダイナミックランダムアクセスメモリ(DRAM)デバイスである、請求項1に記載の方法。

**【請求項 12】**

前記第1の信号を前記メモリコントローラに送るステップが、前記メモリデバイスに組み込まれたプロセッサによって始動される、請求項1に記載の方法。

**【請求項 13】**

メモリコントローラにおいて、第1の信号をメモリデバイスから受け取るステップであって、前記第1の信号は、前記メモリデバイスの特定のメモリセルが前記メモリデバイスによってリフレッシュされるべきであることを前記メモリコントローラに示す、ステップと、

前記メモリデバイスの前記特定のメモリセルのリフレッシュ中に第2の信号を前記メモリコントローラから第2のメモリデバイスに送るステップと

を含む、方法。

**【請求項 14】**

前記第1の信号が、専用バスを介して受け取られる、請求項13に記載の方法。

**【請求項 15】**

特定の時間期間の間に前記特定のメモリセルに関連付けられたコマンドを実行するステップと、

前記特定の時間期間の満了に応答して、

前記特定のメモリセルに関連付けられた前記コマンドの実行を中止するステップと、

確認応答信号を前記メモリデバイスに送るステップであって、前記確認応答信号は、前記特定のメモリセルに関連付けられた前記コマンドの実行が中止されたことを前記メモリデバイスに示す、ステップと

をさらに含む、請求項13に記載の方法。

**【請求項 16】**

第3の信号を第3のメモリデバイスから受け取るステップであって、前記第3の信号は、前記第3のメモリデバイスの特定のメモリセルが前記第3のメモリデバイスによってリフレッシュされるべきであることを前記メモリコントローラに示す、ステップと、

前記確認応答信号を前記メモリデバイスに送った後、第2の確認応答信号を前記第3のメ

モリデバイスに送るステップであって、前記第2の確認応答信号は、前記第3のメモリデバイスの前記特定のメモリセルに関連付けられたコマンドの実行が中止されたことを前記第3のメモリデバイスに示す、ステップと

をさらに含む、請求項15に記載の方法。

【請求項 17】

前記メモリデバイスの第1のダイの第1の保持時間を、前記メモリデバイスの第2のダイの第2の保持時間と比較するステップと、

前記第2の保持時間が前記第1の保持時間よりも大きいという判定に応答して前記第1のダイをマスタダイとし選択するステップと、

前記第1の保持時間が前記第2の保持時間よりも大きいという判定に応答して前記第2のダイをマスタダイとし選択するステップと

をさらに含み、

前記第1の信号が前記マスタダイに関連付けられる、

請求項13に記載の方法。

【請求項 18】

前記第1の信号を受け取ることに応答して固定時間期間の後に前記特定のメモリセルに関連付けられたコマンドの実行を中止するステップをさらに含む方法であって、前記特定のメモリセルが前記固定時間期間の後に前記メモリデバイスによってリフレッシュされる、請求項13に記載の方法。

【請求項 19】

第1の信号をメモリコントローラに送ることであって、前記第1の信号は、メモリデバイスの特定のメモリセルが前記メモリデバイスによってリフレッシュされるべきであることを前記メモリコントローラに示す、送ることと、

前記特定のメモリセルをリフレッシュすることと

を行うように動作可能な前記メモリデバイス

を含む、装置であって、

前記メモリコントローラが、前記特定のメモリセルのリフレッシュ中に第2の信号を第2のメモリデバイスに送る、

装置。

【請求項 20】

前記第1の信号が、専用バスを介して送られる、請求項19に記載の装置。

【請求項 21】

前記メモリデバイスが、コマンドバスを介して確認応答信号を前記メモリコントローラから受け取る、請求項19に記載の装置。

【請求項 22】

前記メモリデバイスが、前記確認応答信号を受け取ることに応答して、前記特定のメモリセルをリフレッシュする、請求項21に記載の装置。

【請求項 23】

前記メモリデバイスが、

前記第1の信号を送った後、固定時間期間の間に前記特定のメモリセルに関連付けられたリフレッシュ動作を一時停止することと、

前記固定時間期間の満了に応答して前記特定のメモリセルをリフレッシュすることと

を行うようにさらに動作可能な、請求項19に記載の装置。

【請求項 24】

前記メモリデバイスが、少なくとも1つの半導体ダイに組み込まれる、請求項19に記載の装置。

【請求項 25】

前記メモリデバイスが組み込まれた、通信デバイス、タブレット、ラップトップ、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュ

ータからなるグループから選択されるデバイスをさらに含む、請求項19に記載の装置。

【請求項 26】

第1の信号をメモリデバイスから受け取ることであって、前記第1の信号は、前記メモリデバイスの特定のメモリセルが前記メモリデバイスによってリフレッシュされるべきであることをメモリコントローラに示す、受け取ることと、

リフレッシュ動作を可能にするために前記特定のメモリセルに関連付けられたコマンドの実行を中止することと、

前記メモリデバイスの前記特定のメモリセルの前記リフレッシュ中に他のメモリデバイスに関連付けられた他の信号を送ることと

を行うように動作可能な前記メモリコントローラ

を含む、装置。

【請求項 27】

前記第1の信号が、専用バスを介して受け取られる、請求項26に記載の装置。

【請求項 28】

前記メモリコントローラが、

特定の時間期間の間に前記特定のメモリセルに関連付けられた特定のコマンドを実行することと、

前記特定の時間期間の満了に応答して、

前記特定のメモリセルに関連付けられた前記特定のコマンドの実行を中止することと、

確認応答信号を前記メモリデバイスに送ることであって、前記確認応答信号は、前記特定のメモリセルに関連付けられた前記特定のコマンドの実行が中止されたことを前記メモリデバイスに示す、受け取ることと

を行うようにさらに動作可能な、請求項26に記載の装置。

【請求項 29】

前記メモリコントローラが、少なくとも1つの半導体ダイに組み込まれる、請求項26に記載の装置。

【請求項 30】

前記メモリコントローラが組み込まれた、通信デバイス、タブレット、ラップトップ、

セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、

ナビゲーションデバイス、携帯情報端末(PDA)、固定位置データユニット、およびコンピュータからなるグループから選択されるデバイスをさらに含む、請求項26に記載の装置。

。

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2014/063040 |

|---------------------------------------------------|

|                                                                          |

|--------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>INV. G11C11/406 G06F13/16<br>ADD. |

|--------------------------------------------------------------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| According to International Patent Classification (IPC) or to both national classification and IPC |

|---------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| B. FIELDS SEARCHED |

|--------------------|

|                                                                                                        |

|--------------------------------------------------------------------------------------------------------|

| Minimum documentation searched (classification system followed by classification symbols)<br>G11C G06F |

|--------------------------------------------------------------------------------------------------------|

|                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------|

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |

|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) |

|------------------------------------------------------------------------------------------------------------------------------|

|                        |

|------------------------|

| EPO-Internal, WPI Data |

|------------------------|

|                                        |

|----------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT |

|----------------------------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                      | Relevant to claim No.                   |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| X         | US 6 735 139 B2 (TANG ROBIN [US])<br>11 May 2004 (2004-05-11)<br>paragraph [0023] - paragraph [0039];<br>figure 2<br>-----                                                                              | 1,13,19,<br>26                          |

| X         | US 2013/279283 A1 (SEO EUN-SUNG [KR] ET<br>AL) 24 October 2013 (2013-10-24)<br><br>paragraph [0115] - paragraph [0123];<br>figures 2,3A<br>paragraph [0127] - paragraph [0146];<br>figures 4,5<br>----- | 1-5,<br>10-16,<br>18-22,<br>24-30<br>17 |

| Y         | US 2012/099389 A1 (PARK CHUL-WOO [KR] ET<br>AL) 26 April 2012 (2012-04-26)<br>paragraph [0008] - paragraph [0009];<br>figure 1<br>-----                                                                 | 17                                      |

|           |                                                                                                                                                                                                         | -/-                                     |

|                                                                                                |                                                              |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C. | <input checked="" type="checkbox"/> See patent family annex. |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|                                           |

|-------------------------------------------|

| * Special categories of cited documents : |

|-------------------------------------------|

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

|                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               |

|-----------------------------------------------|

| "&" document member of the same patent family |

|-----------------------------------------------|

|                                                           |

|-----------------------------------------------------------|

| Date of the actual completion of the international search |

|-----------------------------------------------------------|

|                                                    |

|----------------------------------------------------|

| Date of mailing of the international search report |

|----------------------------------------------------|

|              |

|--------------|

| 10 June 2015 |

|--------------|

|            |

|------------|

| 16/06/2015 |

|------------|

|                                      |

|--------------------------------------|

| Name and mailing address of the ISA/ |

|--------------------------------------|

|                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|

| European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 |

|------------------------------------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| Authorized officer |

|--------------------|

|                |

|----------------|

| Wolff, Norbert |

|----------------|

**INTERNATIONAL SEARCH REPORT**

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2014/063040 |

|---------------------------------------------------|

**C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                         | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 4 366 538 A (JOHNSON ROBERT B ET AL)<br>28 December 1982 (1982-12-28)<br>column 2, line 33 - line 51; figure 1<br>----- | 15,16                 |

**INTERNATIONAL SEARCH REPORT**

International application No.

PCT/US2014/063040

**Box No. II Observations where certain claims were found unsearchable (Continuation of item 2 of first sheet)**

This international search report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.: because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.: 6-9, 23 because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically:

see FURTHER INFORMATION sheet PCT/ISA/210

3.  Claims Nos.: because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

**Box No. III Observations where unity of invention is lacking (Continuation of item 3 of first sheet)**

This International Searching Authority found multiple inventions in this international application, as follows:

see additional sheet

1.  As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fees, this Authority did not invite payment of additional fees.

3.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:

4.  No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:

**Remark on Protest**

- The additional search fees were accompanied by the applicant's protest and, where applicable, the payment of a protest fee.

- The additional search fees were accompanied by the applicant's protest but the applicable protest fee was not paid within the time limit specified in the invitation.

- No protest accompanied the payment of additional search fees.

International Application No. PCT/ US2014/ 063040

**FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210**

This International Searching Authority found multiple (groups of) inventions in this international application, as follows:

1. claims: 1-5, 10-15, 18-22, 24-30

Different alternatives related to the scheduling of the execution of commands by a controller and refresh of memory cells whereon the commands are to be executed and associated signals transmitted between memory device and controller

---

2. claims: 16, 17

Refresh control of a plurality of memory devices in accordance with their retention times

---

International Application No. PCT/ US2014/ 063040

**FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210**

Continuation of Box II.2

Claims Nos.: 6-9, 23

The subject-matter of independent method claim 1 defines a method step wherein a first signal send from a memory device to a memory controller indicates to the memory controller that particular memory cells of the memory device "are to be refreshed" by the memory device. The wording "are to be refreshed" is unambiguously understood in the sense of "are about to be refreshed", or even more explicit, that memory cells are to be refreshed upon sending the signal, and not before sending the signal. The method step of dependent claim 6 defines however "suspending refresh operations ... in response to sending the first signal" and contradicts thus to the wording of claim 1 to which it refers.

A corresponding contradiction is defined in independent device claim 19 in combination with dependent claim 23 .

The subject-matter of dependent claims 6, 23 and dependent claims 7 - 9, which depends on claim 6, in combination with the subject-matter of independent claims 1 and 19 to which they refer is therefore neither understandable nor searchable.

The applicant's attention is drawn to the fact that claims relating to inventions in respect of which no international search report has been established need not be the subject of an international preliminary examination (Rule 66.1(e) PCT). The applicant is advised that the EPO policy when acting as an International Preliminary Examining Authority is normally not to carry out a preliminary examination on matter which has not been searched. This is the case irrespective of whether or not the claims are amended following receipt of the search report or during any Chapter II procedure. If the application proceeds into the regional phase before the EPO, the applicant is reminded that a search may be carried out during examination before the EPO (see EPO Guidelines C-IV, 7.2), should the problems which led to the Article 17(2) declaration be overcome.

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2014/063040

| Patent document cited in search report | Publication date | Patent family member(s) |                                                                                             | Publication date                                                   |

|----------------------------------------|------------------|-------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| US 6735139                             | B2               | 11-05-2004              | NONE                                                                                        |                                                                    |

| US 2013279283                          | A1               | 24-10-2013              | CN 103377695 A<br>KR 20130119545 A<br>US 2013279283 A1                                      | 30-10-2013<br>01-11-2013<br>24-10-2013                             |

| US 2012099389                          | A1               | 26-04-2012              | CN 102456394 A<br>JP 2012089137 A<br>KR 20120040974 A<br>TW 201225079 A<br>US 2012099389 A1 | 16-05-2012<br>10-05-2012<br>30-04-2012<br>16-06-2012<br>26-04-2012 |

| US 4366538                             | A                | 28-12-1982              | NONE                                                                                        |                                                                    |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,ST,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,R0,RS,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,D0,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(72)発明者 ジュン・ピル・キム

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライブ・5775

(72)発明者 ジュンウォン・スー

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライブ・5775

(72)発明者 シャンユ・ドン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライブ・5775

F ターム(参考) 5B060 CA10

5M024 AA04 AA92 BB22 BB39 EE09 EE26 KK35 PP01 PP07