(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-516176

(P2006-516176A)

(43) 公表日 平成18年6月22日(2006.6.22)

(51) Int.C1.

HO1L 29/78

(2006.01)

F1

HO1L 29/78

301D

テーマコード(参考)

5F14O

審査請求 未請求 予備審査請求 有 (全9頁)

(21) 出願番号 特願2004-555528 (P2004-555528)

(86) (22) 出願日 平成15年11月19日 (2003.11.19)

(85) 翻訳文提出日 平成17年7月25日 (2005.7.25)

(86) 國際出願番号 PCT/US2003/037210

(87) 國際公開番号 WO2004/049399

(87) 國際公開日 平成16年6月10日 (2004.6.10)

(31) 優先権主張番号 10/302,639

(32) 優先日 平成14年11月21日 (2002.11.21)

(33) 優先権主張国 米国(US)

(71) 出願人 501087593

クリー マイクロウエイブ リミテッド

ライアビリティ カンパニー

アメリカ合衆国 カリフォルニア州 94

089 サニーベイル ジブラルター

コート 160

(74) 代理人 100082005

弁理士 熊倉 賴男

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100074228

弁理士 今城 俊夫

(74) 代理人 100086771

弁理士 西島 孝喜

最終頁に続く

(54) 【発明の名称】水平拡散MOSトランジスタ(LDMOS)及びその製造方法

## (57) 【要約】

改善された水平拡散MOSトランジスタ(LDMOS)構造は、ゲート構造上に窒化物キャップを利用し、前記ゲート構造のまわりにスペーサを形成することによって提供され、ソース及びドレインドーパント注入に対して、及びシリサイドである全てのソース及びドレイン領域を有するシリサイド構成物に対して、同じマスクを用いることによってゲートとのソース接触及びドレイン接触を自己整列する。低減されたソース及びドレインの抵抗(R<sub>ds on</sub>)は、チャネルからソース接触までの距離が短いほど、ゲート酸化物の品質は、動作の線形性をより良く改善し、F<sub>t</sub>及びG<sub>M</sub>を上昇させ、I<sub>d q</sub>及びR<sub>ds on</sub>のドリフトを低減させる。

## 【特許請求の範囲】

## 【請求項 1】

- シリコン基板上での水平拡散MOS (LDMOS) トランジスタの製作において、

a) ゲート酸化物、該ゲート酸化物上に添加多結晶シリコン体、及び該添加多結晶シリコン体上に窒化物キャップ層を含むゲート構造を形成するステップと、

b) 前記ゲート構造のまわりにスペーサ酸化物を形成するステップと、

c) 露出されるシリコンの酸化によってシール酸化物を形成するステップと、

d) 前記窒化物キャップ層を取り除くステップと、を備える製作方法。

## 【請求項 2】

- e) 前記スペーサ酸化物に接触するソース領域に対して、及び前記スペーサ酸化物から間隔をあけて配置されるドレイン領域に対して、フォトレジストマスクを用いてドーパントを注入するステップと、

f) 前記ソース領域及び前記ドレイン領域に対して前記フォトレジストマスクを用いてシリサイド接触を形成するステップと、をさらに含む請求項 1 に記載の製作方法。

## 【請求項 3】

- ステップ e) は、前記シリサイド接触を形成する前に前記ソース領域上及び前記ドレイン上から酸化物を取り除くために前記フォトレジストマスクを用い、ソースシリサイドは前記ゲートに対して自己整列できるようにすることを含む請求項 2 に記載の製作方法。

## 【請求項 4】

- g) 前記ソース領域、前記ゲート構造、及び前記ドレイン領域の上に第 1 の層間絶縁膜を形成するステップと、

h) 前記第 2 の層間絶縁膜から前記シリサイド接触に対して第 2 の導電性バイアスを形成するステップと、をさらに含む請求項 3 に記載の制作方法。

## 【請求項 5】

- i) 前記第 1 の層間絶縁膜の上に第 2 の層間絶縁膜を形成するステップと、

j) 前記第 1 の導電性バイアスに対して第 2 の導電性バイアスを形成するステップと、

k) 導電性パターンを前記第 2 の層間絶縁膜に形成し、前記第 2 の導電性バイアスに接触させるステップと、をさらに含む請求項 4 に記載の製作方法。

## 【請求項 6】

- ステップ k) は、最初にシード金属層を形成し、その後、前記シード金属層の上に前記導電性パターンを形成することを含む請求項 5 に記載の製作方法。

## 【請求項 7】

- 1) 前記第 2 の層間絶縁膜の上に不活性化層を形成するステップをさらに含む請求項 6 に記載の製作方法。

## 【請求項 8】

- 水平拡散MOS (LDMOS) トランジスタの製作方法であって、

a) ドープされたシンカー及びチャネル接触領域を有する素子領域を取り囲むフィールド酸化膜をシリコン基板の表面に形成するステップと、

b) 前記表面の上にゲート酸化物層を形成するステップと、

c) 添加多結晶シリコンを前記ゲート酸化物層の上に形成するステップと、

d) 窒化物層を前記多結晶シリコンの上に形成するステップと、

e) フォトレジストマスクでゲート構造をマスクし、露出される窒化物及び多結晶シリコン、及びゲート酸化物層を取り除くステップと、

f) 前記ゲート構造の一部と接触し基礎をなす基板上にチャネル注入を形成し、前記チャネル接触領域に対して広げるステップと、

g) 前記ゲート構造のまわりにスペーサ酸化物を形成するステップと、

h) 露出されるシリコンの酸化によってシール酸化物を形成するステップと、

i) 前記窒化物キャップ層を前記ゲート構造から取り除くステップと、

j) 前記スペーサ酸化物に接触するソース領域に対して、及び前記スペーサ酸化物から間隔を空けて配置されるドレイン領域に対して、フォトレジストマスクを用いてドーパントを注入するステップと、

k) 前記第 2 の層間絶縁膜から前記シリサイド接触に対して第 2 の導電性バイアスを形成するステップと、

l) 導電性パターンを前記第 2 の層間絶縁膜に形成し、前記第 2 の導電性バイアスに接触させるステップと、

m) 前記シード金属層を形成するステップと、

n) 前記シード金属層の上に導電性パターンを形成するステップと、

o) 前記導電性パターンを前記第 2 の層間絶縁膜に形成するステップと、

p) 前記導電性パターンに対して第 2 の導電性バイアスを形成するステップと、

q) 前記導電性パターンを前記第 2 の層間絶縁膜に形成するステップと、

r) 前記導電性パターンに対して第 2 の導電性バイアスを形成するステップと、

s) 前記導電性パターンを前記第 2 の層間絶縁膜に形成するステップと、

t) 前記導電性パターンに対して第 2 の導電性バイアスを形成するステップと、

u) 前記導電性パターンを前記第 2 の層間絶縁膜に形成するステップと、

v) 前記導電性パターンに対して第 2 の導電性バイアスを形成するステップと、

w) 前記導電性パターンを前記第 2 の層間絶縁膜に形成するステップと、

x) 前記導電性パターンに対して第 2 の導電性バイアスを形成するステップと、

y) 前記導電性パターンを前記第 2 の層間絶縁膜に形成するステップと、

z) 前記導電性パターンに対して第 2 の導電性バイアスを形成するステップと、

トを注入するステップと、

k) 前記ソース領域及び前記ドレイン領域に対して前記フォトレジストマスクを用いてシリサイド接触を形成するステップと、を備える製作方法。

【請求項 9】

1) 前記ソース領域、前記ゲート構造、及び前記ドレイン領域の上に第1の層間絶縁膜を形成するステップと、

m) 前記第1の層間絶縁膜から前記シリサイド接触に対して第1の導電性バイアスを形成するステップと、をさらに含む請求項8に記載の製作方法。

【請求項 10】

n) 前記第1の層間絶縁膜の上に第2の層間絶縁膜を形成するステップと、

o) 前記第2の層間絶縁膜から前記第1の導電性バイアスに対して第2の導電性バイアスを形成するステップと、

p) 前記第2の層間絶縁膜の上に導電性パターンを形成し、前記第2の導電性バイアスに接触させるステップと、をさらに含む請求項9に記載の製作方法。

【請求項 11】

ステップp)は、最初にシード金属層を形成し、その後、前記シード金属層の上に前記導電性パターンを形成することを含む請求項10に記載の製作方法。

【請求項 12】

q) 前記第2の層間絶縁膜の上に不活性化層を形成するステップをさらに含む請求項1に記載の製作方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、概してRFパワートランジスタに関し、より詳細には、本発明は、水平拡散MOSトランジスタ(LDMOS)及びその製造方法に関する。

【背景技術】

【0002】

LDMOSトランジスタは、パワーアンプとしてRFアプリケーションに用いられている。高周波は、ミクロンより短い小さなゲート長、500よりも小さい薄いゲート酸化膜、10GHzよりも大きなカットオフ周波数( $F_T$ )に対する短チャネル、低減されたソースドレイン抵抗( $R_{ds(on)}$ )、及び低不純物濃度ドレイン拡張の利用による高い逆方向電圧を必要とする。

【0003】

従来の製造は、これらの特徴を実現するには制約がある。さらに、ゲート接触に対するスパッタされたタンクステンシリサイドの利用は、ゲート酸化膜の品質を高めたり低めたりすることを引き起こす厳しい収縮を結果として生じさせ、ゲートドレインを制限するホットキャリア注入改善を制限する。さらに、タンクステンシリサイド及び多結晶シリコンゲート構造は、エッチングするのが難しい。平面でないフィールド酸化膜及び厚い相互接続配線をしばしば結果として生じさせる。

【発明の開示】

【発明が解決しようとする課題】

【0004】

本発明は、LDMOSトランジスタに対する製造過程を改善すること、及び改善されたLDMOSトランジスタを提供することに関する。

【課題を解決するための手段】

【0005】

本発明によると、処理フローは、側壁スペーサ構成物に対してゲート構造をマスクする窒化物を利用すること、及びドーパント注入及びシリサイド接触構成物に対してソース及びドレインマスクを二重に利用することを含んでいる。

【0006】

10

20

30

40

50

本発明の特徴によると、チタン又はコバルトのいずれか一方はシリサイド接觸のために用いられ、それによって、タングステンシリサイドゲートと協働する収縮を排除する。

【0007】

本発明及びその対象及び特徴は、図面を参照して、以下の詳細な説明及び添付の請求項からより容易に明らかになる。

【発明を実施するための最良の形態】

【0008】

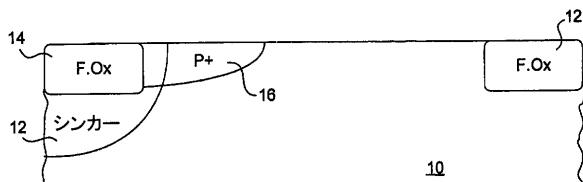

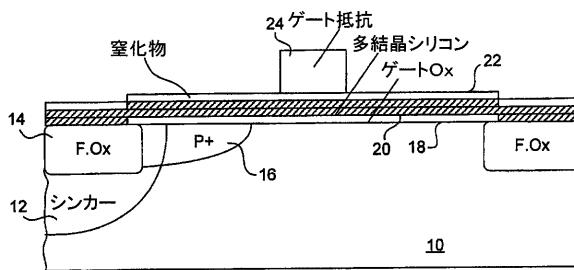

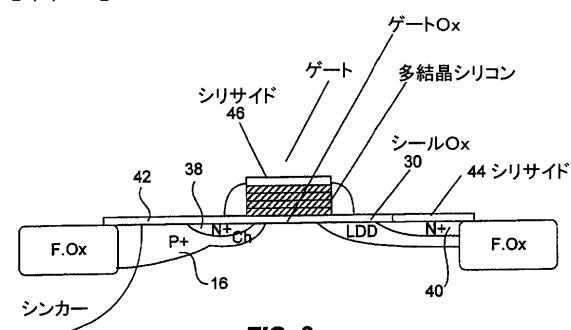

図1-13は、本発明の一実施例に従うLDMOSトランジスタの製造を例証する断面図である。図1に示されているように、前記構造は、典型的には上面にエピタキシャル層を含むシリコン基板10の上に形成される。従来の処理(LPCVD)窒化物及びサーマルパッド酸化物、第1のマスク、及びエッチングを用いることは、(ソース伝導領域になる)P+ドープされたシンカー領域12を形成するのに使用され、減圧化学蒸着法(LPCVD)窒化物及びサーマルパッド酸化物が形成され、その後、第2のマスク及びエッチングがシリコン表面を露出し、フィールド酸化物14を成長させるのに使用される。典型的には、N型フィールドの注入は、埋設領域に作られ、その後、フィールド酸化物14を成長させる。その後、フィールド酸化物は、例えば、化学的機械研磨(CMP)を用いて平坦化され、その後にチャネル領域に接觸するP+注入16が続けられる。

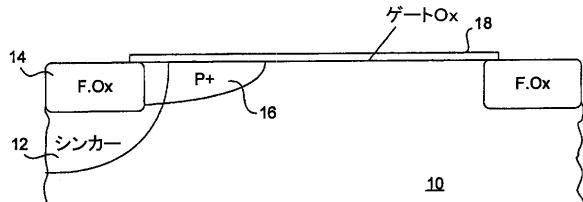

【0009】

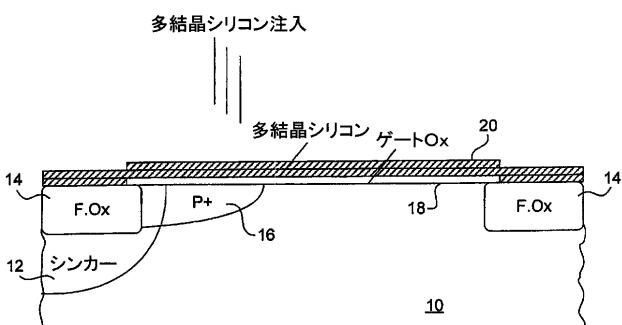

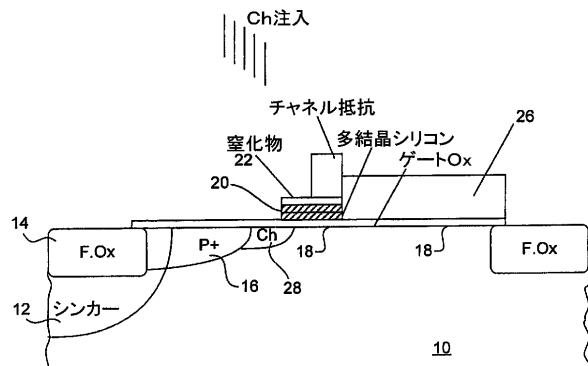

次に、図2に示すように、活性領域の表面は、窒化物/酸化物の層が取り除かれ、熱酸化は、トランジスタに対してゲート酸化膜になるシリコン酸化物層18を形成する。図3では、多結晶シリコン層20は、酸化物層18の上に蒸着され、その後、多結晶シリコン層は、N+(例えば $10^{20}$ atoms/cc)多結晶シリコン層を形成するためにN型ドーパントを注入することによってドープされる。

【0010】

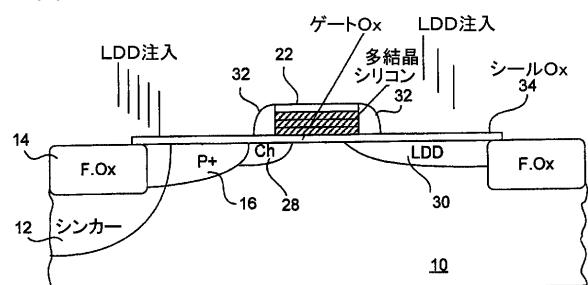

図4では、シリコン窒化物層22が約1000の厚さで減圧化学蒸着法によって形成され、その後、ゲートフォトレジストマスク24が窒化物層22の上に形成される。露出される窒化物22、多結晶シリコン20、及び(ゲート領域を含む)酸化物18は、その後、エッチングによって取り除かれる。有利なことに、多結晶シリコンは窒化物がエッチングされる時のエッチング停止部として機能し、シリコン酸化物は多結晶シリコンをエッチングする際のエッチング停止部として機能し、シリコン基板はシリコン酸化物をエッチングする際のエッチング停止部として機能する。

【0011】

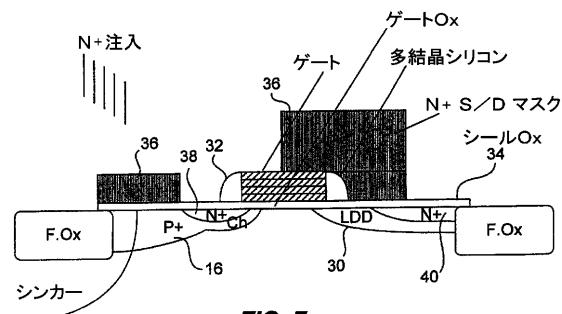

次に、図5に示すように、窒化物層22、多結晶シリコン20、及びゲート酸化物18を含んでいるゲート構造は、フォトレジスト26によってマスクされ、図6では、P型ドーパントが低不純物(例えば $10^{17}$ atoms/cc)チャネル領域28を形成するように注入される。マスク26は、その後、取り除かれ、N型ドーパントがゲート構造の片側に低不純物(例えば $10^{17}$ atoms/cc)ドレイン(LDD)30を形成するように注入される。シリコン酸化物蒸着は、およそ2000のシリコン酸化物層を形成し、その後、酸化物層は、選択性エッチングを用いて裏側にエッチングされ、それによってゲート構造のまわりの側壁スペーサ32を残す。露出された基板10の表面は、その後、およそ350から500の厚さで酸化(シール酸化)される。この酸化は、保護窒化物キャップ22により多結晶シリコンゲートの上部を酸化することはない。それゆえ、窒化物キャップ22は、シール酸化物34がおよそ300の厚さを残した状態で、リン酸などの適切なエッチング液によって取り除かれる。図7に示されるようなN+ソース/ドレイン注入マスク36は、その後、N型ドーパントを注入するのに使用され、ソース領域38及びN+(例えば $10^{19-20}$ atoms/cc)ドレイン領域40を形成する。N+ドレイン領域40がLDD領域30によってスペーサ32から間隔をあけられる一方で、ソース領域はスペーサ32と接することに注目すべきである。

【0012】

フォトレジストマスク36を用いると、酸化物34はソース38及びN+ドレイン40

10

20

30

40

50

上から取り除かれ、その後、フォトレジスト 36 が取り除かれる。チタン又はコバルトは、その後、P+（例えば  $10^{19}$  atoms/cc より大きい）領域 16 及びソース領域 38 と接触して、また図 8 に示されるような N+（例えば  $10^{19}$  atoms/cc より大きい）ドレイン領域 40 と接触して表面にスパッタされる。前記構造は、ソースに対してシリサイド接触 42、N+ ドレイン 40 に対してシリサイド接触 44、及びゲートに対してシリサイド接触 46 を形成するように加熱される。残りの化学反応を起こしていない金属は取り除かれ、シリサイドはその後、シリサイドシート抵抗を低下させるように再度アニールされる。

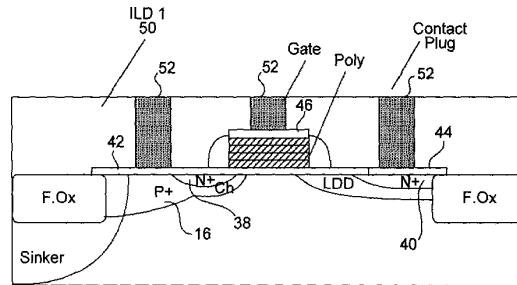

#### 【0013】

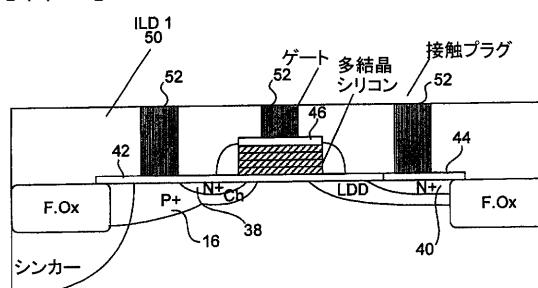

その後は、図 9 に示されるように、層間絶縁膜 50（PECVD）が、前記構造の表面に蒸着され、接触マスク及び絶縁体 50 を介したエッチングの後、バリア金属が蒸着される。シリサイド接触 42、44、及び 46 を、ソース、ドレイン、及びゲートのそれぞれに接触させる化学蒸着タンゲステン又はタンゲステン合成プラグ 52 が、その後、形成される。

#### 【0014】

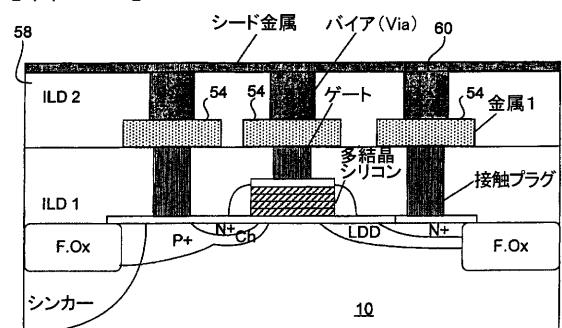

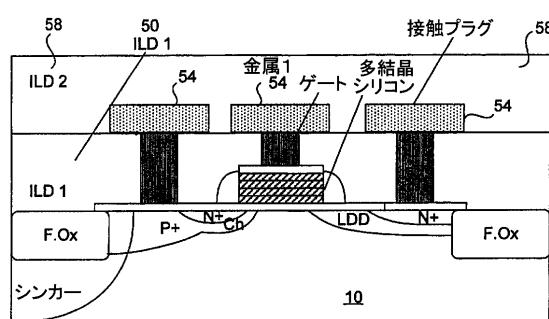

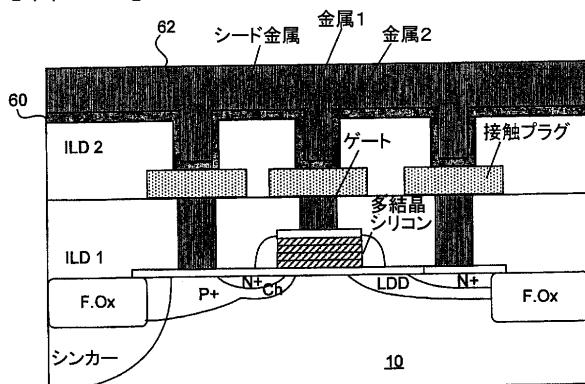

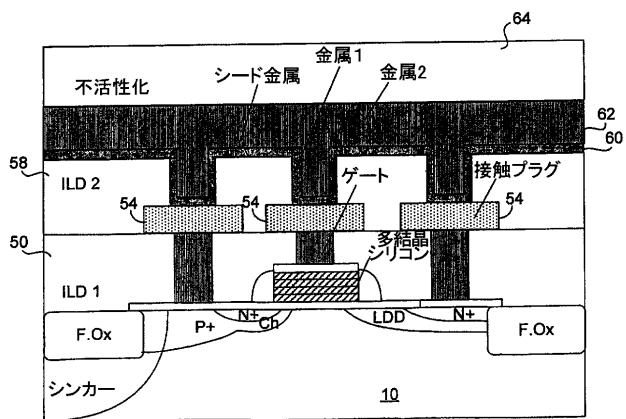

図 10 では、第 1 の金属層が、層間絶縁膜 50 にスパッタされ、選択的に接触部 54 を形成するようにエッチングされ、その後、第 2 の絶縁層 58 が金属接触部 54 及び第 1 の層間絶縁膜 50 の上に蒸着される。最終的に、図 11 に示されるように、第 2 の中間絶縁体層 58 の平坦化後、バイア（Via）マスク及びエッチングが接触部 54 を露出するのに使用され、シード / 接着剤金属層 60 が第 2 の中間絶縁体層 58 の表面に形成され、接触部 54 に対して広がる。図 12 に示されるように、第 2 の金属層 62 は、必要であれば、その後、相互接続線のためのシード金属 60 の上に形成される。

#### 【0015】

最後に、図 13 に示されるように、金属層 62 は、相互接続構造を形成するためにエッチングされ、シリコン窒化物及びシリコン酸化物の不活性化層 64 が蒸着される。

#### 【0016】

本発明に従って製作している LD MOS トランジスタは、350 から 450 のゲート酸化物の厚さで 0.5 から 0.6  $\mu$  のゲート長を有し得る。前記トランジスタは、抵抗を低減されたドレイン - ソースのため高い線形性を有し、より高い  $F_t$  はより短いチャネル長のため実現される。より高い相互コンダクタンス (Gm) は、低減されたゲート酸化物の厚さ、より短いゲート、及び低減された  $R_{ds(on)}$  によって提供される。

#### 【0017】

本発明は一実施例を参照して説明されてきた一方で、その説明は、本発明を例示するものであり、本発明を限定するものとして構成されるものではない。様々な変更及び応用は、添付される請求の範囲によって画定される本発明の本来の意図及び範囲から逸脱することなく当業者には思い浮かぶものあり得る。

#### 【図面の簡単な説明】

#### 【0018】

【図 1】本発明の実施例に従う LD MOS トランジスタを製造する際のステップを例証する断面図である。

【図 2】本発明の実施例に従う LD MOS トランジスタを製造する際のステップを例証する断面図である。

【図 3】本発明の実施例に従う LD MOS トランジスタを製造する際のステップを例証する断面図である。

【図 4】本発明の実施例に従う LD MOS トランジスタを製造する際のステップを例証する断面図である。

【図 5】本発明の実施例に従う LD MOS トランジスタを製造する際のステップを例証する断面図である。

【図 6】本発明の実施例に従う LD MOS トランジスタを製造する際のステップを例証する断面図である。

【図 7】本発明の実施例に従う LD MOS トランジスタを製造する際のステップを例証す

10

20

30

40

50

る断面図である。

【図8】本発明の実施例に従うLDMOSトランジスタを製造する際のステップを例証する断面図である。

【図9】本発明の実施例に従うLDMOSトランジスタを製造する際のステップを例証する断面図である。

【図10】本発明の実施例に従うLDMOSトランジスタを製造する際のステップを例証する断面図である。

【図11】本発明の実施例に従うLDMOSトランジスタを製造する際のステップを例証する断面図である。

【図12】本発明の実施例に従うLDMOSトランジスタを製造する際のステップを例証する断面図である。 10

【図13】本発明の実施例に従うLDMOSトランジスタを製造する際のステップを例証する断面図である。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図11】

FIG. 11

【図10】

FIG. 10

【図12】

FIG. 12

【図13】

FIG. 13

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 ダーマワン ジョハーン

アメリカ合衆国 カリフォルニア州 95014 クーパーティノ アルコールド ロード 22

650

(72)発明者 メイソン ジョン

アメリカ合衆国 94087 サニーヴェイル サウス セイジ コート 1136

F ターム(参考) 5F140 AA01 AA05 AA30 AA40 AC21 BA01 BA16 BC06 BE07 BF04

BF11 BF18 BG08 BG12 BG22 BG30 BG32 BG34 BG37 BG44

BG51 BG53 BH15 BH30 BH49 BJ08 BJ11 BJ17 BJ27 BK02

BK29 BK34 BK38 BK39 CA02 CA06 CC13 CE07 CE08 CF04

CF05