(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-306799

(P2008-306799A)

(43) 公開日 平成20年12月18日(2008.12.18)

(51) Int.Cl.

H02J 1/00 (2006.01)

G05F 1/10 (2006.01)

F 1

H02J 1/00

H02J 1/00

G05F 1/10

G05F 1/10

テーマコード(参考)

5G065

5H410

審査請求 未請求 請求項の数 8 O.L. (全 9 頁)

(21) 出願番号

特願2007-149643 (P2007-149643)

(22) 出願日

平成19年6月5日(2007.6.5)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】電源装置、電源装置の制御方法、プログラム、及び記憶媒体

## (57) 【要約】

【課題】電源投入時に異常電流が流れ続ける不具合を回避することができる電源装置を提供する。

【解決手段】回路全体を遮断する第1のスイッチ回路と、電流制限抵抗と並列接続された第2のスイッチ回路により、電源投入時の異常動作を保護する電源装置を構成する。これにより電流制限抵抗を使用した異常電流判別手段の判別結果に応じて、第1及び第2のスイッチ回路の状態を制御することでより安全性の高い電源装置を提供する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

直流電圧を出力する電源部と、

前記電源部から出力される直流電圧が入力され、接続される負荷に必要な直流電圧を供給する電源回路と、

前記電源部の出力電流を制限する電流制限手段と、

前記電流制限手段に対して直列接続される第1のスイッチ回路と、

前記電流制限手段に対して並列接続される第2のスイッチ回路と、

前記電流制限手段に対して直列接続され、前記電源部の出力電流を検知する電流検知手段と、

前記電流検知手段によって検知した電流が異常電流であるかどうかを判定し、異常電流である場合には異常電流判別信号を出力する異常電流判別手段と、

前記電流検知手段が電流を検知した場合に前記第1のスイッチ回路をオンするとともに、前記第1のスイッチ回路をオンした後、前記異常電流判別手段から前記異常電流判別信号が出力されない場合には、前記第2のスイッチ回路をオンし、前記異常電流判別手段から前記異常電流判別信号が出力された場合には、前記第1のスイッチ回路をオフとする制御手段とを有することを特徴とする電源装置。

**【請求項 2】**

前記制御手段及び前記異常電流判別手段は、前記電源部と前記電流検知手段との間から、動作電源が供給されることを特徴とする請求項1に記載の電源装置。

**【請求項 3】**

前記制御手段は、前記第1のスイッチ回路をオンとする場合には、前記電源回路も動作状態に制御することを特徴とする請求項1又は2に記載の電源装置。

**【請求項 4】**

前記第2のスイッチ回路をオンとした後、前記異常電流判別手段から前記異常電流判別信号が出力された場合に、前記制御手段は、前記第2のスイッチをオフした後、前記第1のスイッチ回路をオフとすることを特徴とする請求項1又は2に記載の電源装置。

**【請求項 5】**

前記第1のスイッチ回路及び第2のスイッチ回路は、FET素子を含むことを特徴とする請求項1乃至3のいずれか1項に記載の電源装置。

**【請求項 6】**

直流電圧を出力する電源部と、前記電源部から出力される直流電圧が入力され、接続される負荷に必要な直流電圧を供給する電源回路と、前記電源部の出力電流を制限する電流制限手段と、前記電流制限手段に対して直列接続される第1のスイッチ回路と、前記電流制限手段に対して並列接続される第2のスイッチ回路と、前記電流制限手段に対して直列接続され、前記電源部の出力電流を検知する電流検知手段と、前記電流検知手段によって検知した電流が異常電流であるかどうかを判定し、異常電流である場合には異常電流判別信号を出力する異常電流判別手段とを有する電源装置の制御方法であって、

前記電流検知手段が電流を検知した場合に前記第1のスイッチ回路をオンするとともに、前記第1のスイッチ回路をオンした後、前記異常電流判別手段から前記異常電流判別信号が出力されない場合には、前記第2のスイッチ回路をオンし、前記異常電流判別手段から前記異常電流判別信号が出力された場合には、前記第1のスイッチ回路をオフとすることを特徴とする電源装置の制御方法。

**【請求項 7】**

請求項6に記載の電源装置の制御方法を、コンピュータに実行させるためのプログラム。

**【請求項 8】**

請求項6に記載の電源装置の制御方法を、コンピュータに実行させるためのプログラムが記憶されたコンピュータで読み取り可能な記憶媒体。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、回路の異常電流に対する保護機能を備える電源装置、電源装置の制御方法、プログラム、及び記憶媒体に関する。

**【背景技術】****【0002】**

従来の技術には、たとえば特許文献1で開示された発明のように、電源回路から複数の負荷回路に対し、直流電圧である電源の供給を行う電源線上に遮断素子を配置する技術が知られている。この場合、負荷回路やDC-D Cコンバータ等で短絡障害が発生して電源線上に過電流が流れた場合、制御回路が遮断素子をオフし、他の負荷回路へ電圧変動等の影響を与えることなく、電源ラインの遮断ができるように構成されている。10

**【0003】**

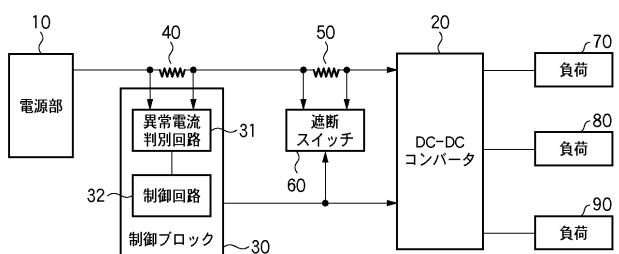

さらに、図3に示すような従来の電源回路も知られている。図3において、10は、たとえば電池よりなる電源部であり、20は、DC-D Cコンバータである。DC-D Cコンバータ20からの直流電圧出力が各負荷70乃至90に、動作のための直流電源として印加される。また、電源部10とDC-D Cコンバータ20との間には、電流検知抵抗40及び電流制限抵抗50が直列に接続されている。

**【0004】**

電流検知抵抗40の両端は、制御ブロック30に含まれる異常電流判別回路31に接続される。また制御ブロック30には、異常電流判別回路31及び異常電流判別回路31の出力が印加される制御回路32が設けられる。また、電源制限抵抗50と並列に遮断スイッチ回路60が設けられ、遮断スイッチ回路60は、制御回路32からの制御信号で制御される構成とされている。制御回路32からの制御信号は、またDC-D Cコンバータ20に供給され、DC-D Cコンバータ20を動作状態とする制御に使用される。制御ブロック30の動作電源は、電源部10から直接供給される。20

**【特許文献1】特開平7-288930号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

上記した構成を備える図3に示す従来の電源保護回路において、電源部10の投入時、すなわち電池を装着したときに、DC-D Cコンバータ20もしくは負荷70乃至90のいずれかに短絡障害などが発生しているとする。その場合当然異常電流が流れることになる。このように、電源部10の挿入時に異常電流が流れた場合、電流検知抵抗40の両端に接続された異常電流判別回路31で異常が判別される。それが制御回路に伝えられて制御回路32からの出力で、遮断スイッチ回路60がオフとされる。しかしながら、遮断スイッチ回路60がオフとなっても電流制限抵抗50があるので、それなりに電源部10より電流が流れ続けてしまう。これが原因となり、電流制限抵抗50の不要な発熱、電源部10の不要な放電や、電源部10が2次電池であった場合、過放電による性能の劣化を招く恐れがある。30

**【0006】**

電流制限抵抗50による上記した不具合を回避するために、電流制限抵抗50をなくしたとする。すると電源部10の投入時に、DC-D Cコンバータ20以降が短絡している時には、電源部10の端子電圧が下がり、制御ブロック30に対する動作電源を確保できずに短絡状態が継続してしまい、結局は保護回路の役割を果たさないことになる。また、電流制限抵抗50の抵抗値を大きくするという案も考えられるが、異常電流判別回路31が異常電流を検知するのに、少なくとも数100mA以上の電流を要するため、電流制限抵抗50の抵抗値は、感度の問題であまり大きく出来ない。40

**【0007】**

したがって、本発明の目的は、電源投入時に異常電流が流れ続ける不具合を回避することができる電源装置を提供することを目的とする。

10

20

30

40

50

## 【課題を解決するための手段】

## 【0008】

上記の目的を達成するため、本発明の実施形態に係る電源装置は、

直流電圧を出力する電源部と、

前記電源部から出力される直流電圧が入力され、接続される負荷に必要な直流電圧を供給する電源回路と、

前記電源部の出力電流を制限する電流制限手段と、

前記電流制限手段に対して直列接続される第1のスイッチ回路と、

前記電流制限手段に対して並列接続される第2のスイッチ回路と、

前記電流制限手段に対して直列接続され、前記電源部の出力電流を検知する電流検知手段と、

前記電流検知手段によって検知した電流が異常電流であるかどうかを判定し、異常電流である場合には異常電流判別信号を出力する異常電流判別手段と、

前記電流検知手段が電流を検知した場合に前記第1のスイッチ回路をオンするとともに、前記第1のスイッチ回路をオンした後、前記異常電流判別手段から前記異常電流判別信号が出力されない場合には、前記第2のスイッチ回路をオンし、前記異常電流判別手段から前記異常電流判別信号が出力された場合には、前記第1のスイッチ回路をオフとする制御手段とを有することを特徴とする。

## 【0009】

上記の目的を達成するため、本発明の実施形態に係る電源装置の制御方法は、

直流電圧を出力する電源部と、前記電源部から出力される直流電圧が入力され、接続される負荷に必要な直流電圧を供給する電源回路と、前記電源部の出力電流を制限する電流制限手段と、前記電流制限手段に対して直列接続される第1のスイッチ回路と、前記電流制限手段に対して並列接続される第2のスイッチ回路と、前記電流制限手段に対して直列接続され、前記電源部の出力電流を検知する電流検知手段と、前記電流検知手段によって検知した電流が異常電流であるかどうかを判定し、異常電流である場合には異常電流判別信号を出力する異常電流判別手段とを有する電源装置の制御方法であって、

前記電流検知手段が電流を検知した場合に前記第1のスイッチ回路をオンするとともに、前記第1のスイッチ回路をオンした後、前記異常電流判別手段から前記異常電流判別信号が出力されない場合には、前記第2のスイッチ回路をオンし、前記異常電流判別手段から前記異常電流判別信号が出力された場合には、前記第1のスイッチ回路をオフとすることを特徴とする。

## 【発明の効果】

## 【0010】

本発明によれば、電源投入時に異常電流が流れ続ける不具合を回避することが可能となる。

## 【発明を実施するための最良の形態】

## 【0011】

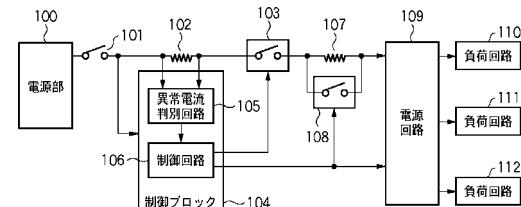

以下、本発明の実施形態に係る電源装置について、図1及び図2を参照して説明する。図1は本発明の実施形態に実施形態に係る電源装置の要部の1例を、概念的に例示するブロック図である。

## 【0012】

100は電源部であり、一般的な電池、ACアダプタ等で構成されて直流電圧を出力する。電源部100からの直流電圧の出力の端子は、主スイッチ回路101と電流検知抵抗102の直列回路の端子を介して第1のスイッチ回路103の一方の端子に接続される。尚、この主スイッチ回路101は、必ずしも必要ではなく、たとえば、電池を装着することで電流検知抵抗102、制御ブロック104に電圧が印加されるように構成することで、主スイッチ回路101は省略することが可能である。

## 【0013】

次に、電流検知抵抗102に関連して異常電流判別回路105が設けられる。すなわち

10

20

30

40

50

、電流検知抵抗 102 の両方の端子は、制御ブロック 104 に含まれる異常電流判別回路 105 の一方の端子に接続され、同じく制御ブロック 104 に含まれる制御回路 106 に、異常動作を示す異常電流の時に、異常電流判別信号を与える。制御ブロック 104 の動作電源は、主スイッチ回路 101 と電流検知抵抗 102 との端子の接続中点から供給される。更に、第 1 のスイッチ回路 103 の他方の端子は、電流制限抵抗 107 の一方の端子を介して、電源回路 109 に接続される。

#### 【0014】

電源回路 109 は、たとえば DC - DC コンバータ等で構成され、複数の負荷回路 110、111 及び 112 に、適宜仕様に応じた必要な動作電源となる直流電圧を入力する。尚、第 1 のスイッチ回路 103 と直列回路を構成する電流制限抵抗 107 の両端には、第 2 のスイッチ回路 108 が並列に接続されている。10

#### 【0015】

尚、異常電流判別回路 105 は、電流検知抵抗 102 の両端の電圧を監視し、そこに流れる電流値を算出し、予め定めた閾値以上の電流が流れた場合、これは異常電流であり、異常動作と判別して異常電流判別信号を出力して制御回路 106 に与える。電流検知抵抗 102 は、基本的に、電源部 100 の直後に配置されるので、回路全体の電流値が監視できるように構成されている。

#### 【0016】

制御回路 106 は、異常電流判別回路 105 よりの判別結果に応じて、第 1 のスイッチ回路 103 及び第 2 のスイッチ回路 108 のオン / オフを制御する。また、制御回路 106 からの制御信号は、第 2 のスイッチ回路 108 のみならず、電源回路 109 にも供給され、電源回路 109 の動作が制御される。20

#### 【0017】

すなわち、電源部 100 から電源回路 109 に対して、電流検知抵抗 102 と、第 1 のスイッチ回路 103 と、第 2 のスイッチ回路 108 が並列接続された電流制限抵抗 107 と、をこの順で直列接続して構成する。

#### 【0018】

整理して説明すると、第 1 のスイッチ回路 103 は、回路全体を遮断することを目的に、電流検知抵抗 102 の直後に配置される。最初の状態においては、第 1 のスイッチ回路 103 及び第 2 のスイッチ回路 108 はオフの状態となっている。30

#### 【0019】

そして主スイッチ回路 101 投入時に、又は電池の装着時に、制御回路 106 からの信号で第 1 のスイッチ回路 103 はオンとされる。また、異常電流判別回路 105 の判別結果により、異常電流が流れると判定されて異常動作として異常電流判別信号が出力された場合には、制御回路 106 からの信号で第 1 のスイッチ回路 103 がオフとされる。

#### 【0020】

また、第 2 のスイッチ回路 108 は、電流制限抵抗 107 と並列に接続され、第 1 のスイッチ回路 103 と電源回路 109 を接続する電源線に配置される。第 2 のスイッチ回路 108 は、主スイッチ回路 101 の投入時、或いは電池の装着時にはオフとされている。したがって、制御回路 106 の信号により第 2 のスイッチ回路 108 がオンとされるまでは、電源回路 109 への直流電圧の供給は、電流制限抵抗 107 を介して行われる。40

#### 【0021】

電流制限抵抗 107 は、電源回路 109 又は負荷回路 110 乃至 112 のいずれかが短絡障害を起こした場合に、出力電流を制限するとともに、異常電流判別回路 105 や、制御回路 106 などの制御ブロック 104 の動作電圧を確保する役割を果たす。

#### 【0022】

異常電流判別回路 105 の判別の結果により、電流値が正常動作であると判定された場合、制御回路 106 からの制御信号により第 2 のスイッチ回路 108 はオンにされる。さらに電源回路 109 も動作状態とされ、正常動作の場合における電源回路 109 への直流電圧の供給は、電流制限抵抗 107 をバイパスして行われることになる。したがって、電50

流制限抵抗 107 によるロスを防ぐことが可能となる。

【0023】

尚、第1のスイッチ回路 103 は、電源回路 109 と電流制限抵抗 107 と第2のスイッチ回路 108 との並列回路との間に挿入してもよい。

【0024】

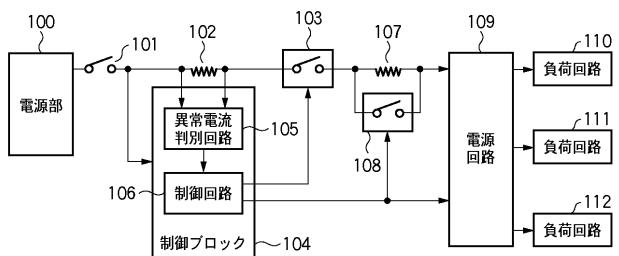

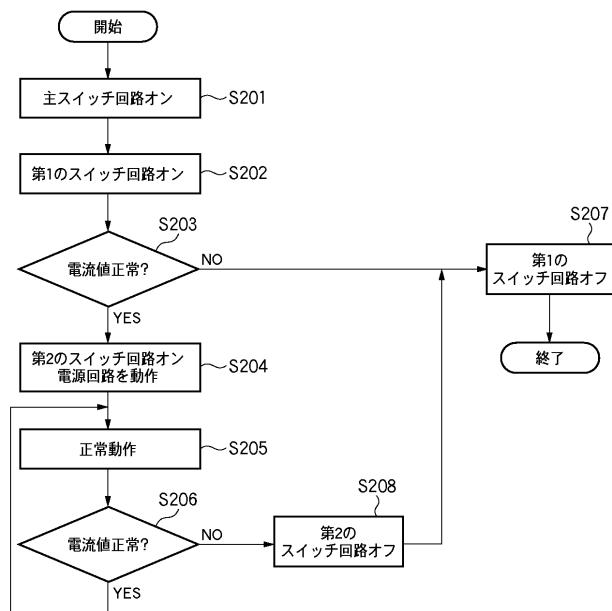

図2は本実施形態に係る電源装置の動作を説明するフローチャートである。図において、処理の開始後においては、主スイッチ回路 101、第1のスイッチ回路 103 及び第2のスイッチ回路 108 はオフの状態にある。その後まずステップ S201 で主スイッチ回路 101 がオン、または電池が装着されたとされる。するとステップ S202 に進み、制御回路 106 により第1のスイッチ回路 103 がオンとされ、ステップ S203 へ進む。

10

【0025】

次にステップ S203 では、異常電流判別回路 105 によって、電流検知抵抗 102 に流れる電流値の判別を行う。そして電流が正常動作であると判定された時はステップ S204 へ進み、異常動作として異常電流が流れていると判定された時は、異常電流判別信号が出力されてステップ S207 へと進む。

【0026】

ステップ S207 では、異常動作であるので、第1のスイッチ回路 103 をオフとし、電源回路 109 への電源の供給を遮断して、処理を終了する。

【0027】

ステップ S204 は、ステップ S203 において異常電流判別回路 105 によって電流値が正常動作であると判定された場合に実行され、制御回路 106 より、第2のスイッチ回路 108 がオンとされ、それと同時に電源回路 109 も動作状態とされる。これにより、ステップ S205 に示すように、回路が正常動作することになる。

20

【0028】

したがって、正常動作中は第2のスイッチ 108 がオンとされるので、電流制限抵抗 107 による無駄な電力消費を避けることができる。正常動作時においては、ステップ S206 で常に電源検知抵抗 102 の電流値の異常を監視する。そして、ステップ S206 において異常電流判別回路 105 によって、電源検知抵抗 102 の電流値が異常動作になったと判定された場合に、ステップ S208 に進む。

30

【0029】

ステップ S208 では、制御回路 106 により最初に第2のスイッチ回路 108 がオフとされ、次にステップ S207 に進み、制御回路 106 により第1のスイッチ回路 103 がオフとされ、処理の終了となる。

【0030】

すなわち、ステップ S206 でもステップ S203 と同様に、異常電流判別回路 105 によって、電流検知抵抗 102 に流れる電流値の判別を行う。そして電流が正常動作であると判定された時はステップ S205 へ進み、正常動作が維持され、異常電流が流れていると判定された時は、異常電流判別信号が出力されてステップ S208 へと進むこととなる。

40

【0031】

尚、第1のスイッチ回路 103 及び第2のスイッチ回路 108 には、機械的なソレノイドを使用するスイッチ素子に限ることなく、FET 素子等の半導体素子のスイッチが使用可能である。

【0032】

以上説明したように、本発明の実施形態に係る電源装置によれば、電源の投入時に、電源回路もしくは負荷回路が短絡している場合において、第1のスイッチ回路をオフとするまでに、常に電流制限抵抗 102 に電流が流れている。したがって、その間は、制御ブロック 104 の動作電源が確保できる。その後、第1のスイッチ回路 103 をオフとするので、電流制限抵抗 107 の不要な発熱、電源部 100 の不要な放電を防ぐことができる。さらに電源部 100 が2次電池であった場合には、過放電による性能劣化を回避する可能

50

性を高めることが出来る。

【0033】

また、本発明は、前述した実施形態の各工程の機能を実現するソフトウェアのプログラムコードを記録した記憶媒体を、システムあるいは装置に供給することによっても実施可能である。すなわち本発明の目的は、そのシステムあるいは装置のコンピュータ（またはCPUやMPU）が記憶媒体に格納されたプログラムコードを読み取りを実行することによっても達成される。この場合、記憶媒体から読出されたプログラムコード自身が前述した実施形態の機能を実現することになり、そのプログラムコードを記憶した記憶媒体は本発明を構成することになる。プログラムコードを供給するための記憶媒体としては、例えばフレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM、CD-R、磁気テープ、不揮発性のメモリカード、ROMなどを用いることができる。10

【0034】

また、コンピュータが読出したプログラムコードを実行することで、前述した実施形態の機能が実現されるだけでなく、そのプログラムコードの指示に基づき、コンピュータ上で稼働しているOSなどが実際の処理の一部または全部を行うこともありうる。それにより、本発明は、その処理によって前述した実施形態の機能が実現される場合も含まれる。

【0035】

さらに本発明においては、記憶媒体から読出されたプログラムコードが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書込まれて実施することも可能である。したがって、書込まれプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部または全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれる。20

【図面の簡単な説明】

【0036】

【図1】本発明の実施形態に係る電源装置の要部の構成を示すブロック図である。

【図2】本発明の実施形態に係る電源装置の動作の説明を示したフローチャートである。

【図3】従来の電源保護回路のブロック図である。

【符号の説明】

【0037】

- 100 電源部

- 101 主スイッチ回路

- 102 電流検知抵抗

- 103 第1のスイッチ回路

- 104 制御ブロック

- 105 異常電流判別回路

- 106 制御回路

- 107 電流制限抵抗

- 108 第2のスイッチ回路

- 109 電源回路

- 110 乃至 112 負荷回路

- 30

40

【図1】

【図2】

【図3】

---

フロントページの続き

(72)発明者 千島 悠輝

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

Fターム(参考) 5G065 BA04 BA07 EA01 FA01 GA04 JA02 KA05 LA02 MA10 NA05

5H410 CC02 CC08 DD01 DD02 DD05 FF05 FF22 KK01 LL06