(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-114376

(P2015-114376A)

(43) 公開日 平成27年6月22日(2015.6.22)

|                                |             |             |

|--------------------------------|-------------|-------------|

| (51) Int.Cl.                   | F 1         | テーマコード (参考) |

| <b>G09G 3/36 (2006.01)</b>     | G09G 3/36   | 2 H 19 2    |

| <b>G02F 1/1368 (2006.01)</b>   | G02F 1/1368 | 2 H 19 3    |

| <b>G02F 1/133 (2006.01)</b>    | G02F 1/133  | 3 K 10 7    |

| <b>G09G 3/20 (2006.01)</b>     | G09G 3/20   | 5 C 00 6    |

| <b>G09G 3/30 (2006.01)</b>     | G09G 3/30   | 5 C 08 0    |

| 審査請求 未請求 請求項の数 16 O L (全 11 頁) |             | 最終頁に続く      |

|           |                              |          |                                                |

|-----------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号 | 特願2013-254207 (P2013-254207) | (71) 出願人 | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号 |

| (22) 出願日  | 平成25年12月9日 (2013.12.9)       | (74) 代理人 | 110000350<br>ポレール特許業務法人                        |

|           |                              | (72) 発明者 | 中尾 健次<br>東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内       |

|           |                              | (72) 発明者 | 田中 幸生<br>東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内       |

|           |                              | (72) 発明者 | 鈴木 大一<br>東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内       |

|           |                              |          | 最終頁に続く                                         |

(54) 【発明の名称】表示装置

## (57) 【要約】

## 【課題】

表示装置において、リーク電流を抑制し、低消費電力で高精細な表示装置を提供する。

## 【解決手段】

基板上に配置された画素に対し、第一の薄膜トランジスタを介して画素電位を供給するソース電源と、

前記第一の薄膜トランジスタの導通と非導通を制御するゲート電源と、を有する表示装置であって、

前記第一の薄膜トランジスタと前記ゲート電源の間に、前記第一の薄膜トランジスタと独立して制御可能な第二の薄膜トランジスタを備えることを特徴とする表示装置。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

基板上に配置された画素に対し、第一の薄膜トランジスタを介して画素電位を供給するソース電源と、

前記第一の薄膜トランジスタの導通と非導通を制御するゲート電源と、を有する表示装置であって、

前記第一の薄膜トランジスタと前記ゲート電源の間に、前記第一の薄膜トランジスタと独立して制御可能な第二の薄膜トランジスタを備えることを特徴とする表示装置。

**【請求項 2】**

前記基板は、ガラス基板上に成膜されたアモルファスシリコン膜をレーザーアニールにより多結晶化して形成される低温ポリシリコン基板であることを特徴とする請求項 1 に記載の表示装置。 10

**【請求項 3】**

前記表示装置は、前記第一の薄膜トランジスタを周期的に駆動させ、いずれかの画素を書き込む書き込み期間と前記画素の電位を保持する保持期間からなる間欠駆動型の表示装置であることを特徴とする請求項 1 または 2 に記載の表示装置。

**【請求項 4】**

前記表示装置は、フリンジ電界を利用して液晶分子を駆動させる FFS (フリンジ・フィールド・スイッチング) 方式の液晶表示装置であることを特徴とする請求項 1 から 3 のいずれかに記載の表示装置。 20

**【請求項 5】**

前記画素は、有機化合物を含む有機発光ダイオードであることを特徴とする請求項 1 から 3 のいずれかに記載の表示装置。

**【請求項 6】**

基板上にマトリクス状に配置された複数の画素に対し、第一の薄膜トランジスタを介して画素電位を供給するソース電源群と、

前記第一の薄膜トランジスタの導通と非導通を制御するゲート電源群と、を有する表示装置であって、

前記第一の薄膜トランジスタと前記ゲート電源の間に、前記第一の薄膜トランジスタと独立して制御可能な第二の薄膜トランジスタを備えることを特徴とする表示装置。 30

**【請求項 7】**

前記基板は、ガラス基板上に成膜されたアモルファスシリコン膜をレーザーアニールにより多結晶化して形成される低温ポリシリコン基板であることを特徴とする請求項 6 に記載の表示装置。

**【請求項 8】**

前記表示装置は、前記第一の薄膜トランジスタを周期的に駆動させ、いずれかの画素を書き込む書き込み期間と前記画素の電位を保持する保持期間からなる間欠駆動型の表示装置であることを特徴とする請求項 6 または 7 に記載の表示装置。

**【請求項 9】**

前記ソース電源は、複数の異なる電圧を印加することが可能な電源であることを特徴とする請求項 6 から 8 のいずれかに記載の表示装置。 40

**【請求項 10】**

前記表示装置は、フリンジ電界を利用して液晶分子を駆動させる FFS (フリンジ・フィールド・スイッチング) 方式の液晶表示装置であることを特徴とする請求項 6 から 9 のいずれかに記載の表示装置。

**【請求項 11】**

前記画素は、有機化合物を含む有機発光ダイオードであることを特徴とする請求項 6 から 9 のいずれかに記載の表示装置。

**【請求項 12】**

基板上に一定の間隔を空けて画素を配置した第一の画素群に対し、複数の第一の薄膜ト 50

ランジスタを介して画素電位を供給する第一のソース電源群と、

前記基板上の前記第一の画素群と異なる領域に、一定の間隔を空けて画素を配置した第二の画素群に対し、複数の第二の薄膜トランジスタを介して前記画素電位と異なる極性の電位を供給する第二のソース電源群と、

前記第一の薄膜トランジスタの導通と非導通を制御する第一のゲート電源群と、

前記第二の薄膜トランジスタの導通と非導通を制御する第二のゲート電源群と、を有する表示装置であって、

前記第一の薄膜トランジスタと前記第一のゲート電源群の間に、独立して制御可能な第三の薄膜トランジスタと、

前記第二の薄膜トランジスタと前記第二のゲート電源群の間に、独立して制御可能な第四の薄膜トランジスタと、を備えることを特徴とする表示装置。 10

【請求項 1 3】

前記基板は、ガラス基板上に成膜されたアモルファスシリコン膜をレーザーアニールにより多結晶化して形成される低温ポリシリコン基板であることを特徴とする請求項 1 2 に記載の表示装置。

【請求項 1 4】

前記表示装置は、前記第一、第二の薄膜トランジスタを周期的に駆動させ、いずれかの画素を書き込む書き込み期間と前記画素の電位を保持する保持期間からなる間欠駆動型の表示装置であることを特徴とする請求項 1 2 または 1 3 に記載の表示装置。 20

【請求項 1 5】

前記表示装置は、フリンジ電界を利用して液晶分子を駆動させる FFS ( フリンジ・フィールド・スイッチング ) 方式の液晶表示装置であることを特徴とする請求項 1 2 から 1 4 のいずれかに記載の表示装置。

【請求項 1 6】

前記画素は、有機化合物を含む有機発光ダイオードであることを特徴とする請求項 1 2 から 1 4 のいずれかに記載の表示装置。 30

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、表示装置に係り、特にアクティブマトリクス方式の表示装置に関する。 30

【背景技術】

【0 0 0 2】

液晶表示装置は、マトリクス状に形成された画素に対し、それぞれの画素に薄膜トランジスタ ( Thin - Film - Transistor ; 以下、TFT ) からなる画素トランジスタを有し、書き込み時以外は TFT 画素トランジスタを OPEN 状態すなわち電気的解放状態にして表示電荷を保持する、アクティブマトリクス液晶表示装置が一般的である。

【0 0 0 3】

携帯電話やスマートフォンを長時間利用するため、低電力の液晶パネルが求められる。通常の液晶パネルは、毎秒 60 回もの書き込みを行っているが、この駆動電力が無視できない。メールやウェブページの表示などの場合、静止画表示が多く、毎秒 60 回の書き込みは必須ではない。動画主体のテレビとは異なる。また、毎秒 60 コマの表示を行う動画モードと間欠的に駆動しその間は前の画面を保持する静止画モードを切り替えるデバイスも想定できる。駆動電力を下げるためには、たとえば 1 秒に一回だけ書き込むように、駆動周波数を下げるのが効果的である。しかし、人間の目は、低周波の輝度変化に対して敏感に反応するため、書き込みの前後で輝度が変化しないようにしなければ、ちらつきが発生して利用者に不快感を与えててしまう。一般に、人間の目は 60 Hz 以上の周波数ではちらつきは認識できないので輝度変化があっても問題ないが、その周波数以下では輝度変化は認識限界以下でなければならない。 40

【0 0 0 4】

10

20

30

40

50

前述したとおり、アクティブマトリクス液晶表示装置では、データ書き込み後の保持期間では、各画素に形成されたTFTトランジスタをOPEN状態すなわち電気的解放状態にして画素電極のチャージを保持させる。もし、このTFT画素トランジスタのOFF特性が悪ければ、保持期間中にチャージが抜けてしまい、保持期間後の電圧値が初期値と異なり輝度が変化してしまう。こうなると、再度書き込んだ時に輝度が変化する現象として現れてしまう。このOFF特性すなわち保持期間中のチャージをいかに確実に長時間保持できるかが重要なパラメータになる。

#### 【0005】

また、近年、酸化物半導体を用い、このOFF電流の小ささを特徴としたアクティブマトリクス液晶表示素子も発表されている。しかし、一般にスマートフォンなどの高精細なTFTアクティブマトリクス液晶表示素子では、低温ポリシリコンTFTを用いる場合が多い。これはTFTサイズを小さくできるメリットや、走査回路などのロジック回路も形成できるメリットによるものであり、今後もこの低温ポリシリコンTFTが主流であると思われる。ただし、本願発明者の検討では、この低温ポリシリコンTFTを用いて低周波での間欠駆動を行うと、輝度変化が大きく、表示のちらつき（フリッカ）として認識されやすいとの課題があることが判った。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

#### 【特許文献1】特許第3402909号公報

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

特許文献1では、ゲートを容量接続することでリーク電流を小さくする方式が開示されている。この方式では、中間的な電極を形成していることで、実効的な容量は、容量の直列接続となるため、ゲート容量を小さくすることは可能である。しかし、低温ポリシリコンTFTを用いる場合、間欠駆動において、リーク電流を抑制するには不十分であった。

#### 【0008】

本発明の目的は、低温ポリシリコンTFTを用いる表示装置において、間欠駆動する際のリーク電流を抑制し、低消費電力で高精細な表示装置を提供することにある。

30

#### 【課題を解決するための手段】

#### 【0009】

上記の課題を解決するために、本発明の一態様は、基板上に配置された画素に対し、第一の薄膜トランジスタを介して画素電位を供給するソース電源と、

前記第一の薄膜トランジスタの導通と非導通を制御するゲート電源と、を有する表示装置であって、

前記第一の薄膜トランジスタと前記ゲート電源の間に、前記第一の薄膜トランジスタと独立して制御可能な第二の薄膜トランジスタを備えることを特徴とする表示装置である。

#### 【0010】

さらに、他の一態様として、基板上にマトリクス状に配置された複数の画素に対し、第一の薄膜トランジスタを介して画素電位を供給するソース電源群と、

前記第一の薄膜トランジスタの導通と非導通を制御するゲート電源群と、を有する表示装置であって、

前記第一の薄膜トランジスタと前記ゲート電源の間に、前記第一の薄膜トランジスタと独立して制御可能な第二の薄膜トランジスタを備える特徴を有していても良い。

#### 【図面の簡単な説明】

#### 【0011】

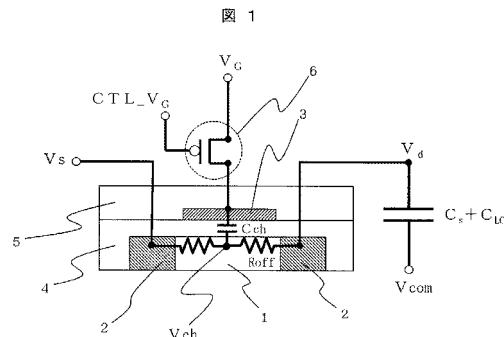

#### 【図1】本発明の一実施形態に係る表示装置の構成を模式的に示す図である。

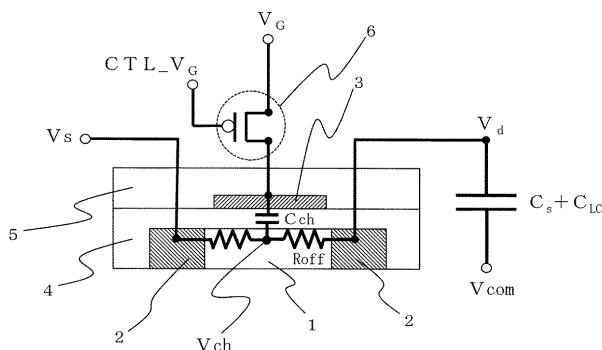

#### 【図2】本発明の一実施形態に係る表示装置の一部回路構成を概略的に示す図である。

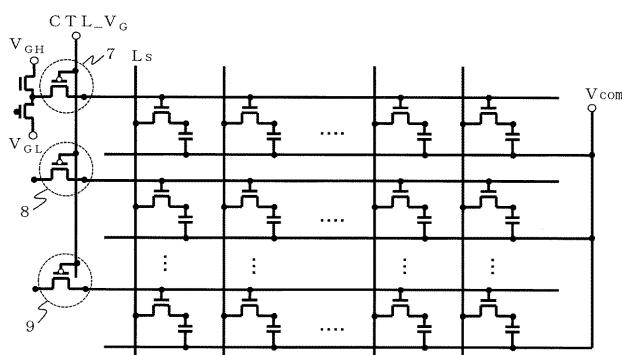

#### 【図3】本発明の一実施形態に係る表示装置の作用を概略的に示すタイムチャートである

40

50

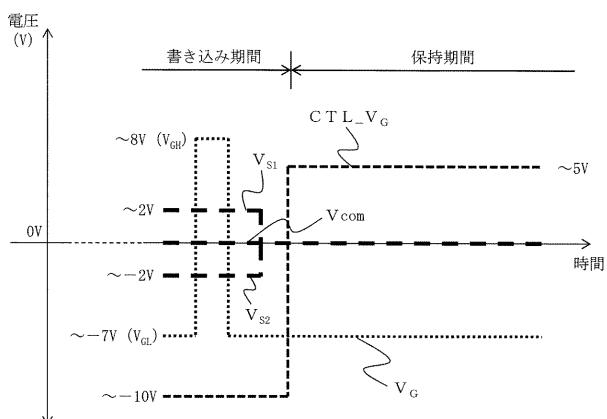

【図4】本発明の一実施形態に係る表示装置の一部回路構成を概略的に示す図である。

【図5】代表的な液晶表示装置の構成を模式的に示す図である。

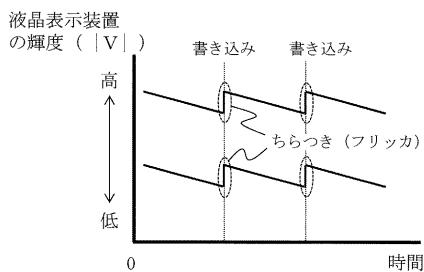

【図6】代表的な液晶表示装置における課題を模式的に示す図である。

【図7】代表的な液晶表示装置における課題を模式的に示す図である。

【図8】代表的な液晶表示装置における課題を模式的に示す図である。

【図9】従来の液晶表示装置の構成を模式的に示す図である。

【発明を実施するための形態】

【0012】

以下に、本発明の各実施の形態について、図面を参照しつつ説明する。なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするために、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号を付して、詳細な説明を適宜省略することがある。

10

【実施例1】

【0013】

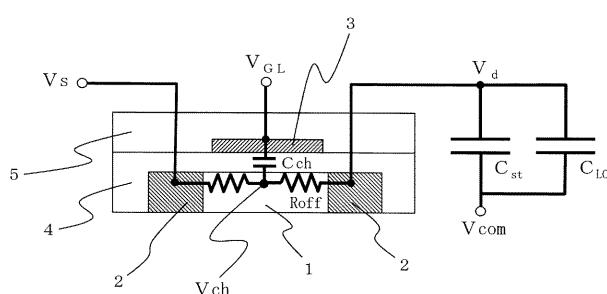

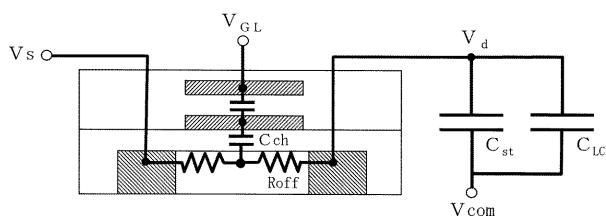

図5は、本発明の原理を説明するために、低温ポリシリコンを用いた代表的なアクティブマトリクス型液晶表示装置のひとつの画素の構造を模式的に示したものである。代表的な液晶表示装置の画素構造では画素容量（主に補助容量  $C_{st}$  と液晶容量  $C_{Lc}$  とで形成される）にチャージを蓄積し、番号1-5からなる画素 TFT でこの画素容量への充電、保持を制御する。 $V_{GL}$  にはこの TFT の ON-OFF を制御するゲート線を接続し、 $V_s$  には画素電極に充電する電位を供給するソース電圧を印加する。なお、画素容量の反対側には共通電極  $V_{com}$  に接続するものとする。

20

【0014】

画素 TFT は、チャネル形成領域1とその両側にチャネル形成領域1を挟むように形成されたソース・ドレイン領域2、ゲート絶縁膜4を介してチャネル形成領域1の上に形成されたゲート電極3、およびこれらを覆う絶縁膜5から構成されている。一方のソース・ドレイン領域は画素と電気的に接続され、他方のソース・ドレイン領域は信号線電位  $V_s$  を供給する部位へ電気的に接続されている。後述するが、説明の便宜上、ゲート電極3とチャネル形成領域1の間の容量を、ゲート電極-チャネル間容量  $C_{ch}$  とする。また、当該画素 TFT が OPEN 状態すなわち電気的解放状態にある場合、チャネル-ソース・ドレイン領域間の抵抗値を、OFF 抵抗、 $R_{ff}$  と定義する。

30

【0015】

図6、図7、図8に上記の代表的な液晶表示装置における課題を模式的に示す。アクティブマトリクスディスプレイの場合、画素に書き込んだ後で、TFTをOPENにすることで画素電位を保持する。通常のデバイスではこの保持期間が60分の1秒が多いが、間欠駆動の場合はこの期間をどこまで伸ばせるかがポイントになる。

40

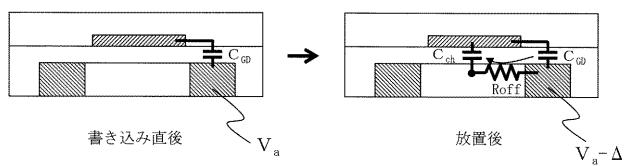

図6に示すように、TFT画素トランジスタをCLOSE状態すなわち電気的接続状態にして画素に電荷をチャージした後、TFTをOPEN状態にする。ここで、低温ポリシリコン TFT を用いて間欠駆動を実施すると、輝度変化が発生する問題が生じる。これは、OFF電流によるリーク電流で画素チャージが減少することに起因する。ポリシリコンは、アモルファスシリコンよりも結晶性が高いため、OFF特性が悪く、リークしやすい欠点がある。

つまり、図6のように、画素に電荷をチャージし、書き込みを行った後、一定時間放置すると、 $R_{ff}$  を介してゲート電極-チャネル間容量  $C_{ch}$  側へチャージが抜けた結果、画素電位は、 $V_a$  から  $V_a - \Delta V$  へと低下してしまう。問題は画素電極のチャージがリークすることにあり、最も基本的なモードは、この画素電極からソース電極に抜ける抵抗を介してリークするモードであり、これはデュアルゲート構

50

造の採用やゲート線幅設計、半導体材料の精製で調整、設計可能である。但し、この画素からソースへのリークが十分に高抵抗を実現できたとしても、ゲート電極 - チャネル間容量  $C_{c_h}$  へのリークが問題になる場合がある。これは、ゲート電極とポリシリコンのチャネル間に容量  $C_{ch}$  が存在し、この充電電流が無視できないことに起因する。放置期間中にポリシリコン中にチャージが発生すると、このチャージによって徐々にゲート電極 - チャネル間容量  $C_{c_h}$  を充電していく。概念的には  $C_{c_h}$  と  $R_{off}$  による CR 時定数で充電されるようなものである。

#### 【0016】

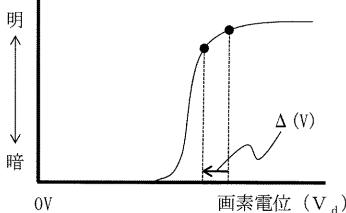

画素に電荷をチャージし、書き込みを行い、一定時間放置後に  $R_{off}$  を介してゲート電極 - チャネル間容量  $C_{c_h}$  側へチャージが抜けてしまうと、図 7 に示すように、画素電位が低下した分、すなわち  $V$  分、液晶表示装置の輝度が低下する。アクティブマトリックス方式の表示装置では、図 8 のように周期的に書き込み動作を行うが、この画素電位の低下分、すなわち  $V$  分の輝度低下が表示のちらつき（フリッカ）となって認識されてしまう。

10

#### 【0017】

ところで、代表的な液晶表示装置では、外部光による誤動作を防ぐため遮光層が形成される場合があるが、遮光層によりポリシリコンへの光照射を小さくすればこの時定数がさらに長くなることが判った。この時定数は1秒程度であった。間欠駆動の周波数が1 Hz 程度であれば、非常に大きな問題となるレベルである。補助容量  $C_{st}$  を含む画素容量が 190 fF に対し、ゲート容量が 6 fF と 3 % 程度になる。この程度の容量でも、光学的な変化としては輝度の 20 % の変化となって現れるため、高精細な液晶表示装置では大きな問題となる。輝度変化が認識されないためには、輝度変化を 1.4 % 以下に抑えなければならない。この輝度変化を抑える方法として、例えば、ゲート電極 - チャネル間容量  $C_{c_h}$  を小さくすればこの  $C_{c_h}$  へのリーク電流が小さくできるので、低減効果は期待できるが、ゲート電極 - チャネル間容量  $C_{c_h}$  はゲート線幅の最小値、ゲート酸化膜の厚みに依存するため、極端に小さくすることは困難である。

20

#### 【0018】

ゲート電極 - チャネル間容量  $C_{c_h}$  を低減する手段として、上述の特許文献 1 のような容量結合のゲートを用いた例（図 9）もあるが、表示装置の開口率を大きく低下させるデメリットがある。

30

#### 【0019】

そこで本実施の形態における液晶表示装置は、図 1 に示すように、基板上に配置された画素に対し、第一の薄膜トランジスタを介して画素電位を供給するソース電源と、前記第一の薄膜トランジスタの導通と非導通を制御するゲート電源と、を有する表示装置であって、前記第一の薄膜トランジスタと前記ゲート電源の間に、前記第一の薄膜トランジスタと独立して制御可能な第二の薄膜トランジスタを備えることを特徴としている。

#### 【0020】

図 1 について、図 5 の説明と重複する部分を省略して説明する。図 1 に示すように、ゲート電源  $V_G$  および TFT 画素トランジスタを構成するゲート電極 3 の間に、TFT 画素トランジスタとは独立して制御することが可能な TFT すなわち薄膜トランジスタ A6 が設けられている。画素への電荷のチャージ後、すなわち書き込み後、放置期間中にこの薄膜トランジスタ A6 のコントロールゲート電源  $CTL\_V_G$  に電圧を印加し、薄膜トランジスタ A6 を OPEN 状態つまり電気的解放状態とすることにより、画素に保持された電荷が、チャネル - ソース・ドレイン領域間抵抗すなわち  $R_{off}$  を介してゲート電極 - チャネル間容量  $C_{c_h}$  へ再充電されるのを抑制することができる。解放状態の容量では、その電荷は保持されるためである。これにより、駆動周波数を低減させることができ、たとえば 1 Hz の駆動周波数を実現した場合に、駆動電力は約 60 分の 1 にすることができる。また、画素にチャージされた電荷が保持期間中にリークしてしまうのを抑制できるため、一定時間放置後に画素電位が低下するのを防止することができ、液晶表示装置のちらつき、いわゆるフリッカ現象を低減することができる。これにより、低消費電力で、高精細

40

50

な液晶表示装置を実現することが可能となる。

【0021】

上記で説明した薄膜トランジスタA6、ゲート電源 $V_G$ 、対向電極電位すなわち共通電位 $V_{com}$ の状態を表すタイムチャートを図3に示す。書き込み期間において、 $V_G$ を-7V程度( $V_{GL}$ )から8V程度( $V_{GH}$ )へ昇圧し、画素に電荷をチャージする。このとき、薄膜トランジスタA6のコントロールゲート電源 $CTL_{VG}$ は-10V程度に保持し、薄膜トランジスタA6をCLOSE状態すなわち電気的接続状態としている。その後の保持期間において、薄膜トランジスタA6のコントロールゲート電源 $CTL_{VG}$ を5V程度まで昇圧し、薄膜トランジスタA6をOPEN状態すなわち電気的解放状態とし、画素に保持された電荷が、チャネル-ソース・ドレイン領域間抵抗すなわち $R_{off}$ を介してゲート電極-チャネル間容量 $C_{ch}$ へ再充電されるのを抑制する。

10

【0022】

本実施の形態における液晶表示装置においては、基板を、ガラス基板上に成膜されたアモルファスシリコン膜をレーザーアニールにより多結晶化して形成される低温ポリシリコン基板いわゆるLTPS-TFT(Low-Temperature-Poly-Silicon-TFT:低温ポリシリコンTFT)で製造しても良い。低温ポリシリコンはオフ電流が大きいため、この発明によるリーク電流を低減する効果が大きく、液晶表示装置のちらつき(フリッカ)を抑制することができる。

【0023】

また、本実施の形態における液晶表示装置は、第一の薄膜トランジスタを周期的に駆動させる間欠駆動型の表示装置に用いることができる。間欠駆動型の表示装置では、画素への電荷のチャージ後の放置期間に電荷が放電されやすいため本発明が、液晶表示装置のちらつき(フリッカ)防止には有効な解決手段となる。

20

【0024】

また、本実施の形態における液晶表示装置は、フリンジ電界を利用して液晶分子を駆動させるFFS(Fringe-Field-Switching)方式や液晶分子を基板と平行な面内で回転させ、複屈折の変化で光をスイッチングするIPS(Plane-Switching)方式、初期状態で液晶を垂直に配向させ、電圧を印加させて液晶を倒すことにより変化する複屈折を利用して、透過状態(白)と非透過状態(黒)を表現するVA(Vertical-Alignment)方式、捻じれネマティック液晶いわゆるTN(Twisted-Nematic)方式等の液晶表示装置に用いることができる。特に、FFS方式の液晶表示装置では、補助容量 $C_{st}$ が大きいため、本発明によるリーク電流が多少あってもフリッカ抑制に効果が高い。

30

【0025】

また、本実施の形態における液晶表示装置は、画素を有機化合物を含む有機発光ダイオードで形成する、いわゆる有機EL(Organic-Electroluminescence)表示装置に適用することもできる。発光期間中の電流量変化が表示に影響を与えるため、有機ELでもフリッカの抑制、低消費電力化、高精細化に有効な手段となる。

【実施例2】

【0026】

本発明における他の実施例を図2に示す。図2は、本実施例に係る液晶表示装置の一部回路構成を概略的に示している。この液晶表示装置は、基板上にマトリクス状に形成された画素に対し、それぞれの画素にTFT画素トランジスタを個別に有し、書き込み時以外はTFT画素トランジスタをOPEN状態すなわち電気的解放状態にして表示電荷を保持する、いわゆるアクティブマトリクス液晶表示装置となっている。画素と同様に基板上にマトリクス状に配置された複数のTFT画素トランジスタのゲート端子を一列毎に1つのゲート線に接続し、ゲート線の末端に電源供給部が接続されている。この電源供給部は、ゲート低電圧 $V_{GL}$ とゲート高電圧 $V_{GH}$ に接続され、どちらかに切り替える構造になっている。本実施の形態において、電源供給部はゲート低電圧 $V_{GL}$ とゲート高電圧 $V_{GH}$ のいずれかに切り替える構造の例を説明しているが、任意の電圧値が供給可能な電源すな

40

わち複数の異なる電圧を印加できる電源を設けても良い。また、マトリクス状に配置された複数のTFT画素トランジスタのそれぞれのソース・ドレイン領域は、容量すなわち液晶容量および補助容量を介して1つの共通電位線に接続され、一列毎に纏めて対向電極電位すなわち共通電位 $V_{com}$ 供給部へ接続されている。本実施例では、上記のようにマトリクス状に配置された複数のTFT画素トランジスタのゲート端子を一列毎に纏めて接続する1つのゲート線および電源供給部との間に、ゲート線毎に薄膜トランジスタB7、薄膜トランジスタC8、薄膜トランジスタD9が設けられている。これにより、実施例1と同様に、画素への電荷のチャージ後すなわち書き込み後の保持期間に、これらの薄膜トランジスタB～DをOPEN状態すなわち電気的解放状態とすることで、画素にチャージされた電荷が、保持期間中にチャネル-ソース・ドレイン領域間抵抗すなわち $R_{off}$ を介してゲート電極-チャネル間容量 $C_{ch}$ へ再充電されるのを抑制することができ、液晶表示装置の低消費電力化、高精細化が可能となる。本実施例では、1秒間の保持期間後も輝度変化が1%以下であり、良好な間欠駆動特性を得ることができた。

10

20

30

40

#### 【0027】

なお、本実施例における液晶表示装置において、実施例1と同様に、基板を、ガラス基板上に成膜されたアモルファスシリコン膜をレーザーアニールにより多結晶化して形成される低温ポリシリコン基板で製造しても良い。また、同様に間欠駆動型の表示装置に用いることもできる。さらには、FSS方式、IPS方式、VA方式、TN方式等の液晶表示装置や、いわゆる有機EL表示装置に採用しても良い。いずれの表示装置においても、低消費電力化、高精細化に有効な手段となる。

20

#### 【実施例3】

#### 【0028】

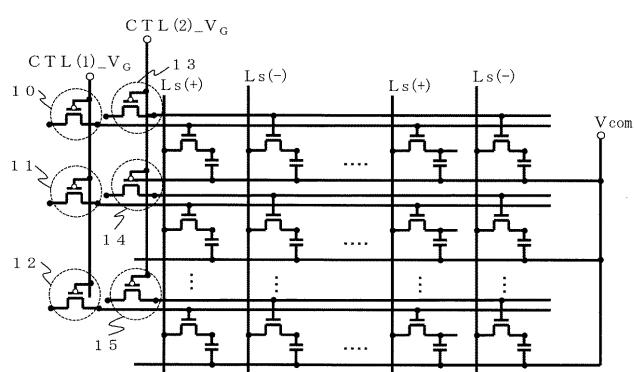

本発明に係る別の実施例を図4に示す。図4は、本実施例における液晶表示装置の一部回路構成を概略的に示している。スマートフォン等では、カラム反転駆動と呼ばれる、ソース線の奇数番目と偶数番目で書き込み信号の符号をえてちらつきを抑制する駆動法が要求される場合がある。このカラム反転駆動は、極性が同じ画素毎にゲート線を束ねて結合させることで、保持特性を向上することができる。本実施例では図4のように、極性が同じ画素毎にゲート線を束ねて結合させることで、カラム反転駆動が可能となっている。また、本実施例においては、極性毎に束ねたゲート線毎にそれぞれ個別に、薄膜トランジスタE10、薄膜トランジスタF11、薄膜トランジスタG12、薄膜トランジスタH13、薄膜トランジスタI14、薄膜トランジスタJ15を設けることにより、実施例1と同様に、画素にチャージされた電荷が、保持期間中にチャネル-ソース・ドレイン領域間抵抗すなわち $R_{off}$ を介してゲート電極-チャネル間容量 $C_{ch}$ へ再充電されるのを抑制することができ、液晶表示装置の低消費電力化、高精細化が可能となる。

30

#### 【0029】

画素をマトリクス状に配置したアクティブマトリクス方式の表示装置においては、複数の画素間でリークチャージの移動が発生する場合がある。これは個々の画素の電荷のチャージ量が大きく異なると電荷の移動が起きやすくなるためである。そこで、本実施例のようにプラス極性とマイナス極性を別々に束ねた構成とすることで、各画素における電荷の保持特性が改善される。但し、ゲート線が各行に2本づつになるため、開口率が低下する点ではデメリットとなる。

40

#### 【0030】

なお、本実施例における液晶表示装置において、実施例1と同様に、基板を、ガラス基板上に成膜されたアモルファスシリコン膜をレーザーアニールにより多結晶化して形成される低温ポリシリコン基板で製造しても良い。また、同様に間欠駆動型の表示装置に用いることもできる。さらには、FSS方式、IPS方式、VA方式、TN方式等の液晶表示装置や、いわゆる有機EL表示装置に採用しても良い。いずれの表示装置においても、低消費電力化、高精細化に有効な手段となる。

50

#### 【0031】

以上の各実施例においては、画素に電荷をチャージ後、すなわち書き込み後の保持期間

50

中にゲート線すなわちゲート電源をOPENすなわち電気的解放状態にすることで、ゲート容量の変動を抑える例について説明しているが、原理的にはソース線においても同様の効果があり、保持期間中にソース線もOPEN状態にした場合は、なお一層の効果を得ることができる。

### 【0032】

また、以上の各実施形態においては、開示例として液晶表示装置の場合を主に例示したが、その他の適用例として、有機EL表示装置、その他の自発光型表示装置、あるいは電気泳動素子等を有する電子ペーパー型表示装置等、あらゆるフラットパネル型の表示装置が挙げられる。また、中小型から大型まで、特に限定することなく適用が可能であることは言うまでもない。

10

### 【符号の説明】

### 【0033】

1 ... チャネル形成領域、2 ... ソース・ドレイン領域、3 ... ゲート電極、4 ... ゲート絶縁膜、5 ... 絶縁膜、6 ... 薄膜トランジスタA、7 ... 薄膜トランジスタB、8 ... 薄膜トランジスタC、9 ... 薄膜トランジスタD、10 ... 薄膜トランジスタE、11 ... 薄膜トランジスタF、12 ... 薄膜トランジスタG、13 ... 薄膜トランジスタH、14 ... 薄膜トランジスタI、15 ... 薄膜トランジスタJ。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

液晶表示装置

の輝度

【図8】

図8

【図9】

図9

## フロントページの続き

| (51) Int.Cl.            | F I          | テーマコード(参考) |

|-------------------------|--------------|------------|

| H 01 L 21/336 (2006.01) | G 09 G 3/20  | 624B 5C094 |

| H 01 L 29/786 (2006.01) | G 09 G 3/20  | 611A 5C380 |

| H 01 L 51/50 (2006.01)  | G 09 G 3/30  | J 5F110    |

| H 05 B 33/02 (2006.01)  | H 01 L 29/78 | 627G       |

| G 09 F 9/30 (2006.01)   | H 01 L 29/78 | 612Z       |

|                         | H 01 L 29/78 | 613Z       |

|                         | H 05 B 33/14 | A          |

|                         | H 05 B 33/02 |            |

|                         | G 09 F 9/30  | 338        |

F ターム(参考) 2H192 AA24 CB02 CB11 GD03 GD61 JA33

2H193 ZA04 ZC07 ZF21 ZF31 ZQ16

3K107 AA01 BB01 CC14 CC33 CC35 DD14 EE04 HH05

5C006 AA16 AF42 BB16 BC06 BC13 FA23 FA36 FA47

5C080 AA06 AA10 DD06 DD10

5C094 AA22 AA25 BA03 BA27 BA43 BA75 DA13 DB01 FB14 GA10

5C380 AA01 AB06 AB23 AC11 AC12 BA01 BA10 BA11 BB08 BB09

CA08 CA57 CB01 CB37 DA33 DA41 DA42 DA58

5F110 BB01 CC02 DD02 GG02 GG13 NN71 NN72 PP03