(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6370044号

(P6370044)

(45) 発行日 平成30年8月8日(2018.8.8)

(24) 登録日 平成30年7月20日(2018.7.20)

|                      |            |

|----------------------|------------|

| (51) Int.Cl.         | F 1        |

| HO4N 5/361 (2011.01) | HO4N 5/361 |

| HO4N 5/357 (2011.01) | HO4N 5/357 |

| HO4N 5/374 (2011.01) | HO4N 5/374 |

請求項の数 7 (全 20 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-267144 (P2013-267144)  |

| (22) 出願日  | 平成25年12月25日 (2013.12.25)      |

| (65) 公開番号 | 特開2015-126239 (P2015-126239A) |

| (43) 公開日  | 平成27年7月6日 (2015.7.6)          |

| 審査請求日     | 平成28年12月16日 (2016.12.16)      |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (72) 発明者  | 大西 智也<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

| (72) 発明者  | 菊池 伸<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内     |

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】撮像装置、撮像システム、撮像装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

行列状に配され、各々が光電変換部と増幅トランジスタを有する複数の画素と、第1の入力ノードと第2の入力ノードを有する差動アンプと、

第1の画素の前記増幅トランジスタと接続する第1の信号線と、

前記第1の画素が配されている列とは異なる列に配されている第2の画素の前記増幅トランジスタと接続する第2の信号線と、

前記第1の入力ノードと前記第1の信号線とを接続する第1のスイッチと、

前記第2の入力ノードと前記第1の信号線とを接続する第2のスイッチと、

前記第1の入力ノードと前記第2の信号線とを接続する第3のスイッチと、

前記第2の入力ノードと前記第2の信号線とを接続する第4のスイッチとを有し、前記第1のスイッチと前記第4のスイッチがオンになることにより、前記差動アンプは、前記第1の入力ノードに入力された前記第1の画素のリファレンス信号と、前記第2のノードに入力された前記第2の画素の光信号との差に基づく信号を出力し、

前記第2のスイッチと前記第3のスイッチがオンになることにより、前記差動アンプは、前記第2の入力ノードに入力された前記第2の画素のリファレンス信号と、前記第1のノードに入力された前記第1の画素の光信号との差に基づく信号を出力し、

前記第1および第2の画素のリファレンス信号は、リセット電位に基づく信号であることを特徴とする撮像装置。

## 【請求項 2】

10

20

前記第1および第2の画素の前記増幅トランジスタが、共通の電源配線に電気的に接続されていることを特徴とする請求項1に記載の撮像装置。

【請求項3】

前記撮像装置は、前記画素を走査する垂直走査回路をさらに有し、前記垂直走査回路が、前記第1および第2の画素と同じタイミングで選択することによって、前記第1の画素と前記第2の画素の一方の前記リファレンス信号が前記差信号生成部に入力される期間と、前記第1の画素と前記第2の画素の他方の前記光信号が前記差信号生成部に入力される期間との少なくとも一部同士を重ならせることを特徴とする請求項1または2に記載の撮像装置。

【請求項4】

前記第1および第2の画素は、互いに同じ行に属することを特徴とする請求項1～3のいずれかに記載の撮像装置。

【請求項5】

前記第1および第2の画素は、互いに異なる列および互いに異なる行に属することを特徴とする請求項1～3のいずれかに記載の撮像装置。

【請求項6】

前記第1の画素と前記第2の画素とに挟まれる画素の数が10以内であることを特徴とする請求項1～5のいずれかに記載の撮像装置。

【請求項7】

請求項1～6のいずれかに記載の撮像装置と、

前記撮像装置が出力する信号を処理する出力信号処理部と、

を有することを特徴とする撮像システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は撮像装置、撮像システム、撮像装置の駆動方法に関する。

【背景技術】

【0002】

特許文献1には、入射光を光電変換して電荷を生成し、浮遊拡散容量に電荷を転送し、浮遊拡散容量の保持した電荷に基づく信号を出力する有効画素を有する構成が記載されている。さらに特許文献1の撮像装置は、浮遊拡散容量に基準電圧を与えることで、基準信号を出力するリファレンス画素を有する。また、特許文献1には、光電変換部が遮光されたオプティカルブラック画素を有する撮像装置が記載されている。

【0003】

特許文献1の撮像装置は、リファレンス画素あるいはオプティカルブラック画素の一方と、有効画素が出力する信号との差の信号を出力する差信号生成部を有している。差信号生成部が出力する信号は、リファレンス画素あるいはオプティカルブラック画素の出力する信号と、有効画素の出力する信号との出力する信号とに共通して含まれるノイズ成分を差し引いた信号である。これにより、特許文献1に記載の撮像装置は、有効画素の出力する信号からノイズ成分を低減した信号を出力することができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2012-253740号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

有効画素とリファレンス画素とのそれぞれに含まれる信号では、暗電流によるノイズ成分の量が異なることがある。これにより、有効画素が出力する信号からリファレンス画素が出力する信号を差し引いても、有効画素のノイズ成分を精度よく低減することができな

10

20

30

40

50

いことがあった。また、オプティカルブラック画素では、光電変換部を遮光する遮光部と、浮遊拡散容量との間で寄生容量が存在することがある。この場合には、有効画素とオプティカルブラック画素とのそれぞれに含まれる信号では、ノイズ成分が異なる。従って、有効画素が出力する信号からオプティカルブラック画素の出力する信号を差し引いても、有効画素のノイズ成分を精度よく低減することができないことがあった。

【課題を解決するための手段】

【0006】

本発明は上記の課題を鑑みて為されたものであり、その一の態様は、光電変換部を各々が有し、各々が、リファレンス信号と、前記光電変換部で生じた電荷に基づく光信号とをそれぞれ出力する第1および第2の画素と、前記第1の画素と前記第2の画素との一方のリファレンス信号が入力される第1のノードと、前記第1の画素と前記第2の画素との他方の光信号が入力される第2のノードとを有し、入力された前記リファレンス信号と前記光信号との差に基づく信号を出力する差信号生成部とを有することを特徴とする撮像装置である。

10

【0007】

また、一の態様は、光電変換部を各々が有するとともに、各々がリファレンス信号と前記光電変換部で生じた電荷に基づく光信号とをそれぞれ出力する複数の画素を有する撮像装置の駆動方法であって、前記複数の画素のうちの第1の画素と第2の画素の一方が前記リファレンス信号を出力し、前記複数の画素のうちの前記第1の画素と前記第2の画素の他方の前記光信号を出力し、前記第1の画素と前記第2の画素との一方の前記リファレンス信号と前記第1の画素と前記第2の画素との他方の前記光信号との差の信号に基づく信号を出力することを特徴とする撮像装置の駆動方法である。

20

【発明の効果】

【0008】

本発明により、有効画素の出力する信号からノイズ成分を高精度に低減した信号を出力する撮像装置を提供することができる。

【図面の簡単な説明】

【0009】

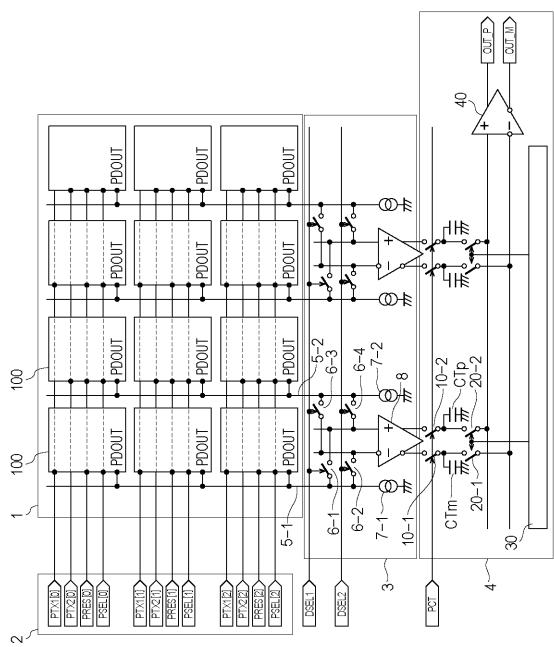

【図1】撮像装置の構成の一例を示した図

30

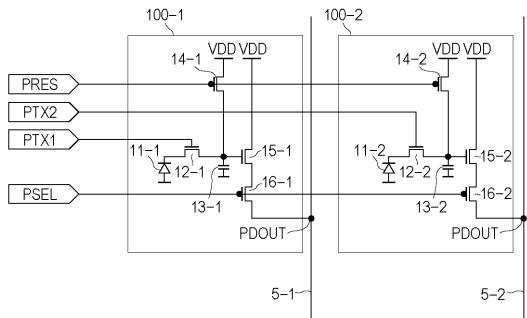

【図2】画素の構成の一例と垂直走査回路とを合わせて示した図

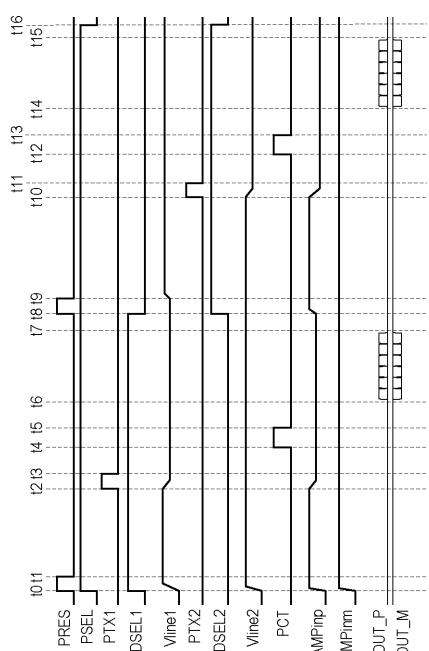

【図3】撮像装置の動作の一例を示した図

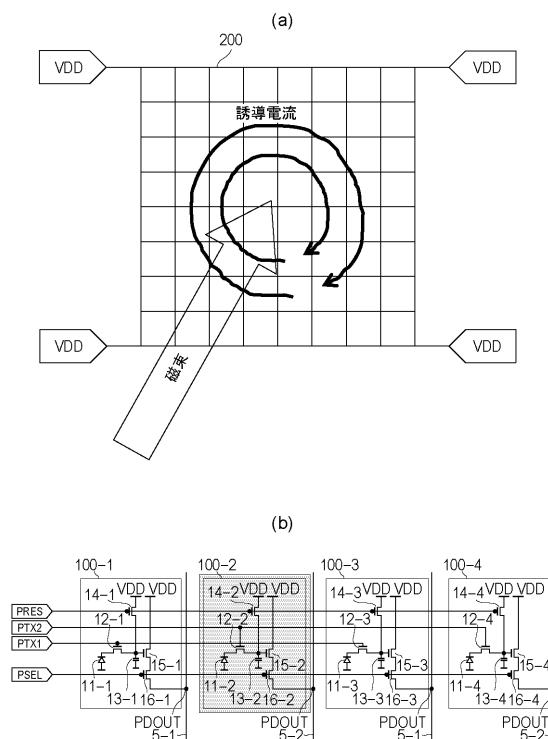

【図4】電源配線に生じる電圧変動の説明図

【図5】撮像装置の構成の一例を示した図

【図6】撮像装置の動作の一例を示した図

【図7】撮像装置の構成の一例を示した図

【図8】画素の構成の一例と垂直走査回路とを合わせて示した図

【図9】撮像装置の構成の一例を示した図

【図10】撮像装置の動作の一例を示した図

【図11】撮像システムの構成の一例を示した図

【発明を実施するための形態】

40

【0010】

以下、図面を参照しながら各実施例の撮像装置について説明する。

【0011】

(実施例1)

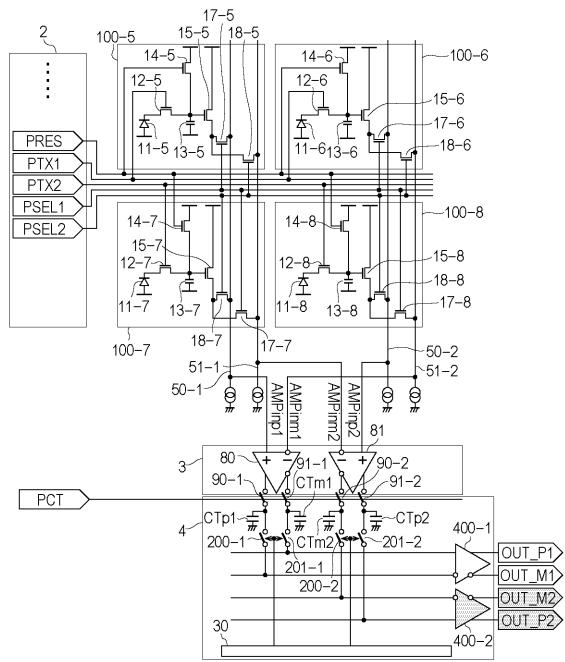

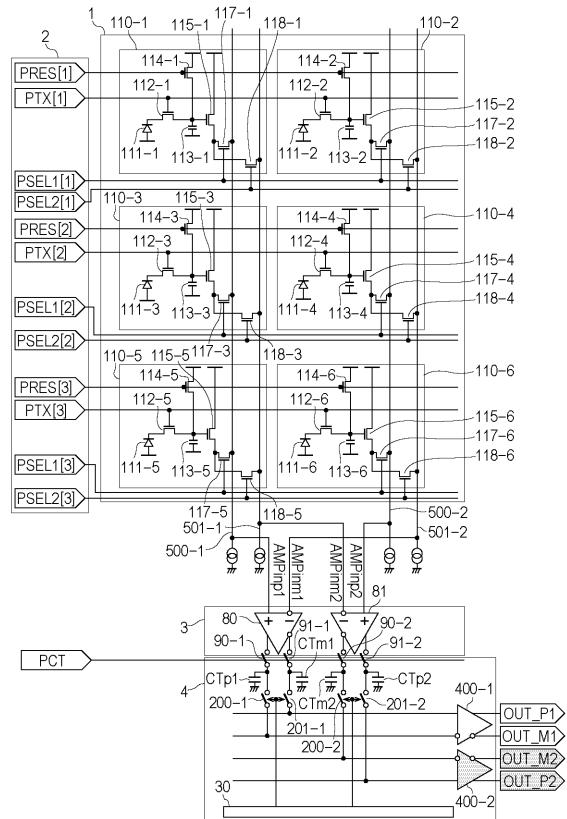

図1は、本実施例の撮像装置の一例を示したブロック図である。本実施例の撮像装置は、画素100が行列状に配された画素アレイを有する撮像領域1と、垂直走査回路2と、差信号生成部3と、水平転送部4を有する。画素100は、垂直走査回路2から信号PTX、信号PRES、信号PSELが入力される各ノードと、信号を出力するノードPDOUTを有する。以下、本明細書では、画素100について単にM行目(Mは1以上の整数)と記す時は、撮像領域1の、差信号生成部3が設けられた側に位置する端部とは逆の端

50

部から数えたものとして扱う。また、画素 100 について単に N 列目 (N は 1 以上の整数) と記す時は、撮像領域 1 の、垂直走査回路 2 が設けられた側に位置する端部から数えたものとして扱う。

【0012】

垂直走査回路 2 は、画素 100 に供給する信号 P T X 1、信号 P T X 2、信号 P R E S、信号 P S E L の信号レベルを制御することによって、撮像領域 1 の画素 100 を行単位での走査である垂直走査を行う。この垂直走査回路 2 による垂直走査によって、各画素 100 は光電変換信号とリファレンス信号のそれぞれを各々の P D O U T 端子から垂直信号線 5 - 1、垂直信号線 5 - 2 に出力する。電流源 7 - 1 は垂直信号線 5 - 1 を介して画素 100 に電流を供給する。電流源 7 - 2 は垂直信号線 5 - 2 を介して画素 100 に電流を供給する。 10

【0013】

差信号生成部 3 は、スイッチ 6 - 1、スイッチ 6 - 2、スイッチ 6 - 3、スイッチ 6 - 4、差動アンプ 8 を有する。不図示のタイミングジェネレータは、スイッチ 6 - 1、スイッチ 6 - 2、スイッチ 6 - 3、スイッチ 6 - 4 を、信号 D S E L 1、信号 D S E L 2 の信号レベルによって、導通状態、非導通状態を制御する。差信号生成部 3 は、垂直信号線 5 から入力される信号を増幅した信号を水平転送部 4 に出力する。

【0014】

水平転送部 4 は、スイッチ 10 - 1、スイッチ 10 - 2、容量素子 C T m、容量素子 C T p、スイッチ 20 - 1、スイッチ 20 - 2、水平走査回路 30、出力アンプ 40 を有する。不図示のタイミングジェネレータは、信号 P C T の信号レベルを制御することによって、スイッチ 10 - 1、スイッチ 10 - 2 の導通状態と非導通状態を制御する。 20

【0015】

水平走査回路 30 は、差動アンプ 8 が設けられた列毎に、スイッチ 20 - 1、スイッチ 20 - 2 の導通状態と非導通状態を順次制御する。これにより、水平走査回路 30 は、差動アンプ 8 の列単位の走査である水平走査を行う。

【0016】

水平走査回路 30 がスイッチ 20 - 1、スイッチ 20 - 2 を導通状態とすると、容量素子 C T m、容量素子 C T p に保持された信号が出力アンプ 40 に入力される。出力アンプ 40 は入力された信号を増幅した信号を、端子 O U T \_ P、端子 O U T \_ M を介して撮像装置の外部に出力する。 30

【0017】

尚、図 1 では、2 列の画素 100 および 1 列の差動アンプ 8 に関わる部材について符号を付している。符号を付した列に対して右隣に位置する 2 列の画素 100 および 1 列の差動アンプ 8 に関わる部材の構造はそれぞれ、左隣に位置する 2 列の画素 100 および 1 列の差動アンプ 8 に関わる部材の構造と同じである。

【0018】

図 2 は、2 列の画素 100 の構成の詳細を示した図である。図 2 では、画素 100 - 1、画素 100 - 2 はトランジスタ 12 - 1、トランジスタ 12 - 2 に垂直走査回路 2 から入力される信号が異なる点を除いて、同じである。よって、ここでは画素 100 - 1 を主に説明する。 40

【0019】

画素 100 - 1 は、フォトダイオード 11 - 1、トランジスタ 12 - 1、トランジスタ 14 - 1、トランジスタ 15 - 1、トランジスタ 16 - 1、浮遊拡散容量 13 - 1 を有している。フォトダイオード 11 - 1 は、入射光に基づく電荷を蓄積する光電変換部である。トランジスタ 12 - 1 は、垂直走査回路 2 から入力される信号 P T X 1 が H i g h レベル (以下、H レベル) となると、フォトダイオード 11 - 1 に蓄積された電荷を浮遊拡散容量 13 - 1 に転送する。トランジスタ 15 - 1 は、入力ノードが浮遊拡散容量 13 - 1 に電気的に接続されている。トランジスタ 15 - 1 は一方の主ノードに、垂直信号線 5 - 1 を介して接続される電流源 7 - 1 からバイアス電流が供給され、他方の主ノードに電源 50

電圧 V D D が供給されることでソースフォロワを構成する。トランジスタ 16 - 1 は、垂直走査回路 2 から入力される信号 P S E L が H レベルとなると、トランジスタ 15 - 1 が出力する信号を垂直信号線 5 - 1 に出力する。トランジスタ 16 - 1 が垂直信号線 5 - 1 に信号を出力するノードがノード P D O U T である。トランジスタ 15 - 1 が出力する信号は、浮遊拡散容量 13 - 1 の保持する電荷に基づく信号である。

【 0 0 2 0 】

トランジスタ 14 - 1 は、垂直走査回路 2 から入力される信号 P R E S が H レベルとなると、浮遊拡散容量 113 - 1 の電位を電源電圧 V D D に基づく電位にリセットする。

【 0 0 2 1 】

尚、垂直走査回路 2 は画素 100 - 1 のトランジスタ 12 - 1 には信号 P T X 1 を出力し、画素 100 - 2 のトランジスタ 12 - 2 には信号 P T X 2 を出力する。

【 0 0 2 2 】

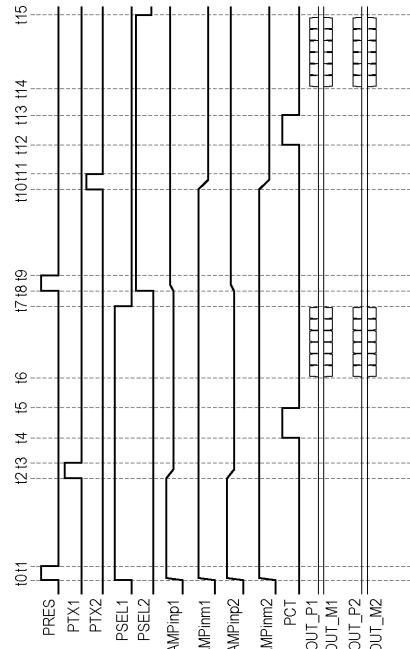

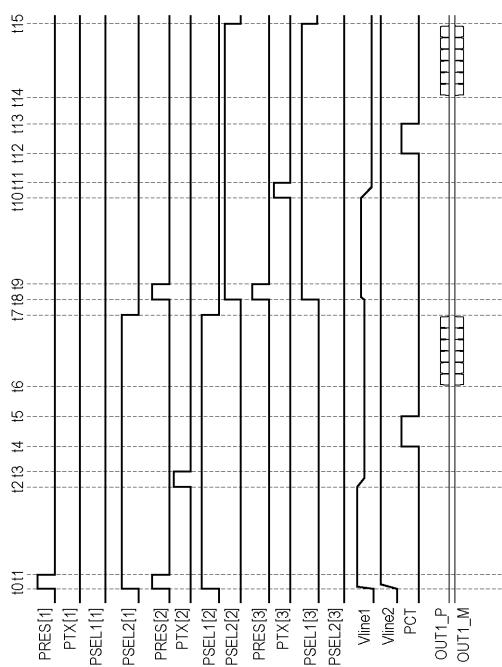

図 3 は、図 1 に示した撮像装置の動作を示したタイミング図である。図 3 に示した V 1 i n e 1 は垂直信号線 5 - 1 の電位を示している。また、図 3 に示した V 1 i n e 2 は垂直信号線 5 - 2 の電位を示している。図 3 に示した A M P i n p は、図 1 に示した差動アンプ 8 の非反転入力ノードの電位を示している。A M P i n m は、図 1 に示した差動アンプ 8 の反転入力ノードの電位を示している。以下、図 1、図 2 で付した符号を参照しながら、図 3 のタイミング図を用いて本実施例の撮像装置の動作について説明する。

【 0 0 2 3 】

時刻 t 0 において、垂直走査回路 2 は、信号 P T X 1、信号 P T X 2 を L o w レベル (以下、L レベルと表記する。) としている。

【 0 0 2 4 】

時刻 t 0 に、垂直走査回路 2 は、信号 P R E S を H レベルとする。これにより、画素 100 - 1、画素 100 - 2 の各々の浮遊拡散容量 13 - 1、浮遊拡散容量 13 - 2 の電位がリセットされる。また、垂直走査回路 2 は同時刻に信号 P S E L を H レベルとする。これにより、トランジスタ 15 - 1 が、リセットされている浮遊拡散容量 13 - 1 の電位に基づく信号を、トランジスタ 16 - 1 を介して垂直信号線 5 - 1 に出力する。同様に、トランジスタ 15 - 2 が、リセットされている浮遊拡散容量 13 - 2 の電位に基づく信号を、トランジスタ 16 - 2 を介して垂直信号線 5 - 2 に出力する。垂直走査回路 2 は信号 P S E L を H レベルとすることによって、画素 100 - 1 と画素 100 - 2 を同じタイミングで選択している。これにより、画素 100 - 1 が差動アンプ 8 にリファレンス信号を出力する期間と、画素 100 - 2 が差動アンプ 8 に光信号を出力する期間とが重なっている。

【 0 0 2 5 】

また、時刻 t 0 に不図示のタイミングジェネレータは信号 D S E L 1 を H レベルとする。これにより、図 1 に示したスイッチ 6 - 1、スイッチ 6 - 3 が導通状態となる。また、タイミングジェネレータは、信号 D S E L 2 を L レベルとしている。よって、図 1 に示したスイッチ 6 - 2、スイッチ 6 - 4 は非導通状態である。従って、信号 D S E L 1 が H レベルの期間において、差動アンプ 8 の非反転入力ノードの電位 A M P i n p は、垂直信号線 5 - 1 の電位 V 1 i n e 1 となる。同様に、信号 D S E L 1 が H レベルの期間において、差動アンプ 8 の反転入力ノードの電位 A M P i n m は、垂直信号線 5 - 2 の電位 V 1 i n e 2 となる。

【 0 0 2 6 】

時刻 t 1 に、垂直走査回路 2 は、信号 P R E S 1 を L レベルとし、画素 100 - 1、画素 100 - 2 の浮遊拡散容量 13 - 1、浮遊拡散容量 13 - 2 の電位のリセットを解除する。この時に、トランジスタ 15 - 1、トランジスタ 15 - 2 が出力している信号をリファレンス信号と表記する。

【 0 0 2 7 】

時刻 t 2 に、垂直走査回路 2 は、信号 P T X 1 を H レベルとした後、時刻 t 3 に、垂直走査回路 2 は、信号 P T X 1 を L レベルとする。これにより、図 2 に示したトランジスタ

10

20

30

40

50

12-1が、フォトダイオード11-1が蓄積した電荷を、浮遊拡散容量13-1に転送する。これにより、トランジスタ15-1が、浮遊拡散容量13-1の電位に基づく信号を、トランジスタ16-1を介して垂直信号線5-1に出力する。このトランジスタ15-1が出力する信号は、フォトダイオード11-1が蓄積した電荷に基づく信号である。このトランジスタ15-1、あるいはトランジスタ15-2がフォトダイオード11-1、あるいはフォトダイオード11-2が蓄積した電荷に基づいて出力する信号を光信号と表記する。ここでは、画素100-2は、リファレンス信号を出力する第1の画素である。一方、画素100-1は、光信号を出力する第2の画素である。ここでは垂直信号線5-2は、第1の画素である画素100-2からリファレンス信号が入力される第1の垂直信号線である。また、垂直信号線5-1は、第2の画素である画素100-1から光信号が入力される第2の垂直信号線である。トランジスタ15-1、トランジスタ15-2のそれぞれは、光信号とリファレンス信号を出力する増幅トランジスタである。

## 【0028】

差動アンプ8は、トランジスタ15-1が出力する光信号と、トランジスタ15-2が出力するリファレンス信号との差の信号を増幅した信号を出力する。

## 【0029】

時刻t4に、タイミングジェネレータは信号PCTをHレベルとする。そして、時刻t5に、タイミングジェネレータは信号PCTをLレベルとする。これにより、容量素子CTm、CTpはそれぞれ、差動アンプ8が時刻t5に出力する信号を保持する。

## 【0030】

時刻t6から、水平走査回路30はスイッチ20-1、スイッチ20-2を導通状態とする。これにより、容量素子CTm、容量素子CTpが保持した信号が、出力アンプ40に入力される。出力アンプ40は、容量素子CTm、容量素子CTpに基づく信号を、端子OUT\_P、端子OUT\_Mに出力する。水平走査回路30は時刻t6から時刻t7までの期間に、差動アンプ8が設けられた列ごとに、容量素子CTm、CTpが保持した信号を出力アンプ40に転送する。

## 【0031】

時刻t8に、垂直走査回路2は、信号PRESをHレベルにする。これにより、浮遊拡散容量13-1、浮遊拡散容量13-2の電位がリセットされる。また、時刻t8に、タイミングジェネレータが、信号DSEL1をLレベルにするとともに、信号DSEL2をHレベルにする。これにより、差動アンプ8の非反転入力ノードの電位AMPinpは、垂直信号線5-2の電位Vline2となる。同様に、差動アンプ8の反転入力ノードの電位AMPinmは、垂直信号線5-1の電位Vline1となる。

## 【0032】

時刻t9に、垂直走査回路2は、信号PRESをLレベルにする。これにより、浮遊拡散容量13-1、浮遊拡散容量13-2のリセットが解除される。よって、トランジスタ15-1はトランジスタ16-1を介して垂直信号線5-1にリファレンス信号を出力する。同様に、トランジスタ15-2はトランジスタ16-2を介して垂直信号線5-2にリファレンス信号を出力する。

## 【0033】

時刻t10に、垂直走査回路2は、信号PTX2をHレベルとした後、時刻t11に、垂直走査回路2は、信号PTX2をLレベルとする。これにより、トランジスタ12-2が、フォトダイオード11-2が蓄積した電荷を、浮遊拡散容量13-2に転送する。これにより、トランジスタ15-2は、トランジスタ16-2を介して垂直信号線5-2に光信号を出力する。ここでは、画素100-1は、リファレンス信号を出力する第1の画素である。一方、画素100-2は、光信号を出力する第2の画素である。ここでは、垂直信号線5-1は、第1の画素である画素100-1からリファレンス信号が入力される第1の垂直信号線である。また、垂直信号線5-2は、第2の画素である画素100-2から光信号が入力される第2の垂直信号線である。

## 【0034】

10

20

30

40

50

差動アンプ 8 は、トランジスタ 15 - 2 が出力する光信号と、トランジスタ 15 - 1 が出力するリファレンス信号との差の信号を増幅した信号を出力する。

【 0 0 3 5 】

時刻  $t_{12}$  に、タイミングジェネレータは信号 PCT を H レベルとする。そして、時刻  $t_{13}$  に、タイミングジェネレータは信号 PCT を L レベルとする。これにより、容量素子 C T m、C T p はそれぞれ、差動アンプ 8 - 1 が時刻  $t_{13}$  に出力する信号を保持する。

【 0 0 3 6 】

時刻  $t_{14}$  から時刻  $t_{15}$  の期間、水平走査回路 30 は、時刻  $t_6$  から時刻  $t_7$  の期間と同様に、水平走査を行う。これにより、出力アンプ 40 は、差動アンプ 8 が設けられた列に対応して設けられた各列の容量素子 C T m、C T p が保持した信号に基づく信号を順次、端子 OUT\_m、端子 OUT\_p に出力する。

【 0 0 3 7 】

このように、本実施例の撮像装置は、差動アンプ 8 - 1 が、有効画素である画素 100 - 1、画素 100 - 2 の一方の光信号と、他方のリファレンス信号との差の信号を出力する。これにより、リファレンス画素あるいはオプティカルブラック画素と、有効画素の光信号との差の信号を得る場合に比して、光信号に含まれるノイズ成分を精度よく差し引くことができる。

【 0 0 3 8 】

以下に、本実施例の撮像装置が、光信号とリファレンス信号との双方に含まれる共通のノイズ成分をさらに低減できる例を説明する。

【 0 0 3 9 】

図 4 ( a ) は、撮像装置の動作環境において、磁界が変動することによって生じるノイズを説明するための模式図である。画素 100 に電位を供給する電源電圧 VDD は電源配線 200 によって、格子状の画素 100 に対して共通に供給されている。この電源配線 200 に対し、撮像装置の外部から磁界の変動による磁束が通過したとする。磁束の変化によって起電力が電源配線 200 に生じる。これにより、電源配線 200 に渦電流が流れる。この電源配線 200 に流れる渦電流によって、電源配線 200 の電源電圧 VDD が変動する。しかし、電源配線 200 において、渦電流が流れる電気的経路の寄生抵抗と寄生容量は一様ではない。また、電源配線 200 の場所によって起電力の発生量が異なる。これらの理由により、電源配線 200 の場所によって、電源電圧 VDD の変動量のばらつきが生じる。このことから、有効画素領域外のリファレンス画素と有効画素とでは、リファレンス画素と有効画素との電源電圧 VDD の変動量がばらつく。これによって、リファレンス画素の出力する信号と、有効画素の出力する信号とに含まれるノイズ成分の量がばらつく。従って、特許文献 1 のように、有効画素領域外のリファレンス画素と有効画素との差を得る構成では、有効画素の出力する信号に含まれるノイズ成分の低減の精度が低下する。

【 0 0 4 0 】

一方、本実施例の撮像装置は、上述したように、差動アンプ 8 は光信号と、当該光信号を出力する画素 100 の近傍に位置する画素 100 のリファレンス信号との差の信号を増幅した信号を出力する。これにより、本実施例の撮像装置は、光信号との差を得るのに用いるリファレンス信号を出力する画素 100 と、当該光信号を出力する画素 100 との電源電圧 VDD の変動量が特許文献 1 に記載の構成に比して揃いやすい。よって、本実施例の撮像装置は、特許文献 1 の構成に比して、差動アンプ 8 に入力される信号同士のノイズ成分が揃いやすい。このことから、本実施例の撮像装置は、光信号に含まれるノイズ成分の低減の精度を特許文献 1 に構成に比して向上させることができる。

【 0 0 4 1 】

本実施例では、画素 100 の出力する光信号と、当該光信号を出力する画素 100 とは別の画素 100 のリファレンス信号との差を得る差信号生成部 3 の一例として差動アンプ 8 を有する例を説明した。他の例として、特許文献 1 の図 8、図 9 に記載のように、アナ

10

20

30

40

50

ログデジタル変換回路を用いるようにしても良く、前記差をデジタル信号として出力しても良い。

【0042】

尚、第1の画素と第2の画素の一方が差動アンプ8にリファレンス信号を出力する期間の全てと、第1の画素と第2の画素の他方が差動アンプ8に光信号を出力する期間の全てを重ねる必要はない。つまり、第1の画素と第2の画素の一方が差動アンプ8にリファレンス信号を出力する期間と、第1の画素と第2の画素の他方が差動アンプ8に光信号を出力する期間との少なくとも一部同士が重なっていれば良い。

【0043】

また、本実施例では、リファレンス信号を出力する第1の画素と、光信号を出力する第2の画素が互いに隣り合っている例を基に説明した。本実施例は、第1の画素と第2の画素が隣り合っている例に限定されるものではない。第1の画素と第2の画素との距離は、第1の画素と第2の画素との間に含まれる画素の数が10以内となる距離であることが好み。この第1の画素と第2の画素との間に含まれる画素の数とは、第1の画素と第2の画素のそれぞれの重心を直線で結び、その直線が通過する画素の数である。

【0044】

また、以下に本実施例の撮像装置が有する別の効果について説明する。

【0045】

図4(b)は、4列の画素である画素100-1、画素100-2、画素100-3、画素100-4を示した図である。画素100-3は画素100-1と同じ構造を有している。また、画素100-4は画素100-2と同じ構造を有している。また、図4(b)では、画素100-2に強い光が入射していることを示している。垂直走査回路2が信号PTX2をHレベルとすると、画素100-1と画素100-3とにおいて、フォトダイオード11-1、フォトダイオード11-3が蓄積した電荷が浮遊拡散容量13-1、浮遊拡散容量13-3にそれぞれ転送される。フォトダイオード11-2には強い光が入射しているため、トランジスタ15-2の入力ノードの電位が大きく変動する。このトランジスタ15-2の入力ノードの電位の大きな変動が、トランジスタ12-2の寄生容量を介して、信号PTX2を伝送する制御線(以下、PTX2線と表記する。)に伝達する。PTX2線と、信号PTX1を伝送する制御線(以下、PTX1線と表記する。)とが近傍に設けられている場合、PTX1線とPTX2線との間の配線間容量によって、PTX2線の電位変動がPTX1線に伝達される。PTX1線の電位変動によって、画素100-1のトランジスタ12-1を介してトランジスタ15-1の電位が変動することがある。このような場合、本実施例の撮像装置は、画素100-1のリファレンス信号と、画素100-2の光信号との差の信号を得ることによって、PTX1線とPTX2線との電位変動による影響を差し引くことができる。

【0046】

(実施例2)

本実施例の撮像装置について、実施例1とは異なる点を中心に説明する。

【0047】

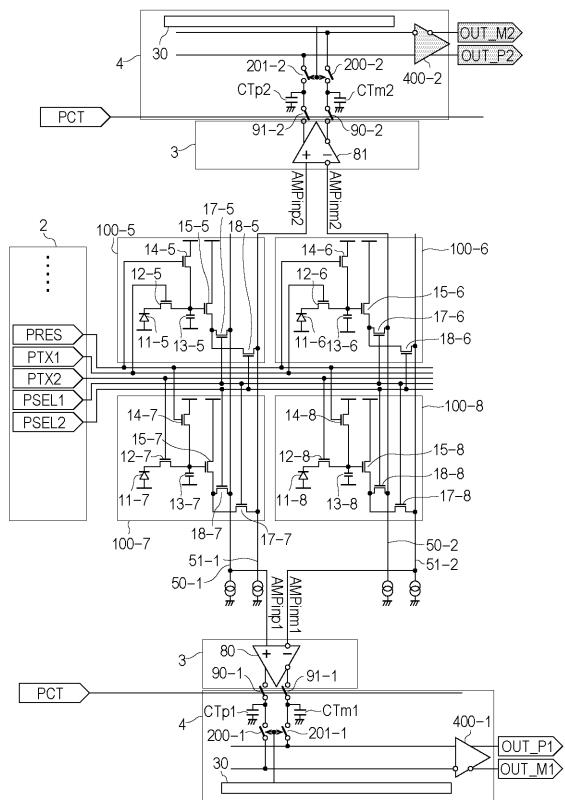

図5は、本実施例の撮像装置の構成を示した図である。図5では、2行2列に設けられた画素100-5、画素100-6、画素100-7、画素100-8を示している。図5では、図2に示した部材と同じ機能を有する部材に対して、図2に付した符号と同じ符号を付している。

【0048】

本実施例では、光信号を出力する画素100と、当該光信号との差を得るためのリファレンス信号を出力する画素100とが、斜めの位置関係にある。つまり、光信号を画素100-5が出力する場合には、この光信号との差を得るためのリファレンス信号を画素100-8が出力する。同様に、光信号を画素100-6が出力する場合には、この光信号との差を得るためのリファレンス信号を画素100-7が出力する。同様に、光信号を画素100-7が出力する場合には、この光信号との差を得るためのリファレンス信号を画

10

20

30

40

50

素 100-5 が出力する。同様に、光信号を画素 100-8 が出力する場合には、この光信号との差を得るためのリファレンス信号を画素 100-6 が出力する。本実施例では、リファレンス信号を出力する画素である第 1 の画素と、光信号を出力する第 2 の画素とが互いに異なる列および互いに異なる行に位置する関係にある。

#### 【0049】

実施例 1 では、画素 100 の各列に 1 つの垂直信号線 5 が設けられていたが、本実施例では、画素 100 の各列に対して 2 つの垂直信号線 50、51 が設けられている。垂直信号線 50-1、垂直信号線 51-1 は共に、画素 100-5、画素 100-7 が設けられた列に対応して設けられている。垂直信号線 50-2、垂直信号線 51-2 は共に、画素 100-6、画素 100-8 が設けられた列に対応して設けられている。実施例 1 では、トランジスタ 15 は、トランジスタ 16 を介して垂直信号線 5 に電気的に接続されていた。本実施例では、トランジスタ 15 は、トランジスタ 17、18 の一方を介して垂直信号線 50 に電気的に接続され、さらに、トランジスタ 17、18 の他方を介して垂直信号線 51 に電気的に接続されている。

#### 【0050】

垂直走査回路 2 が出力する信号 P R E S は、画素 100-5、画素 100-6、画素 100-7、画素 100-8 の各々が有するトランジスタ 14 に共通に入力される。垂直走査回路 2 が出力する信号 P T X 1 は、画素 100-5、画素 100-6 の各々が有するトランジスタ 12 に共通に入力される。垂直走査回路 2 が出力する信号 P T X 2 は、画素 100-7、画素 100-8 の各々が有するトランジスタ 12 に共通に入力される。垂直走査回路 2 が出力する信号 P S E L 1 は、画素 100-5、画素 100-6、画素 100-7、画素 100-8 の各々が有するトランジスタ 17 に共通に入力される。垂直走査回路 2 が出力する信号 P S E L 2 は、画素 100-5、画素 100-6、画素 100-7、画素 100-8 の各々が有するトランジスタ 18 に共通に入力される。

#### 【0051】

差動アンプ 80 の非反転入力ノードには、垂直信号線 50-1 の電位が入力される。差動アンプ 80 の反転入力ノードには、垂直信号線 51-2 の電位が入力される。差動アンプ 80 の非反転入力ノードには、垂直信号線 50-2 の電位が入力される。差動アンプ 80 の反転入力ノードには、垂直信号線 51-1 の電位が入力される。

#### 【0052】

タイミングジェネレータが信号 P C T を H レベルとすると、スイッチ 90-1、スイッチ 91-1、スイッチ 90-2、91-2 が導通状態となる。これにより、容量素子 C T p 1、容量素子 C T m 1 は差動アンプ 80 の出力する信号を保持する。同様に、容量素子 C T p 2、容量素子 C T m 2 は差動アンプ 81 の出力する信号を保持する。

#### 【0053】

水平走査回路 30 がスイッチ 200-1、スイッチ 201-1 を導通状態とすると、出力アンプ 400-1 に容量素子 C T p 1、容量素子 C T m 1 が保持した信号が入力される。出力アンプ 400-1 は、容量素子 C T p 1、容量素子 C T m 1 が保持した信号を増幅した信号を、端子 O U T \_ P 1、端子 O U T \_ M 1 に出力する。

#### 【0054】

水平走査回路 30 がスイッチ 200-2、スイッチ 201-2 を導通状態とすると、出力アンプ 400-2 に容量素子 C T p 2、容量素子 C T m 2 が保持した信号が入力される。出力アンプ 400-2 は、容量素子 C T p 2、容量素子 C T m 2 が保持した信号を増幅した信号を、端子 O U T \_ P 2、端子 O U T \_ M 2 に出力する。

#### 【0055】

図 6 は、図 5 に示した撮像装置の動作を示したタイミング図である。図 6 に示した A M P i n p 1、A M P i n m 1、A M P i n p 2、A M P i n m 2 はそれぞれ順に、差動アンプ 80 の非反転入力ノードおよび反転入力ノード、差動アンプ 81 の非反転入力ノードおよび反転入力ノードの電位である。

#### 【0056】

10

20

30

40

50

時刻  $t_0$  に、垂直走査回路 2 は、信号 P R E S を H レベルとする。これにより、浮遊拡散容量 13 - 5、浮遊拡散容量 13 - 6、浮遊拡散容量 13 - 7、浮遊拡散容量 13 - 8 の電位がリセットされる。また、垂直走査回路 2 は、信号 P S E L 1 を H レベルとする。これにより、各画素 100 のトランジスタ 17 が導通状態となる。よって、トランジスタ 15 - 5 は、トランジスタ 17 - 5 を介して垂直信号線 50 - 1 に信号を出力する。また、トランジスタ 15 - 6 は、トランジスタ 17 - 6 を介して垂直信号線 50 - 2 に信号を出力する。また、トランジスタ 15 - 7 は、トランジスタ 17 - 7 を介して垂直信号線 51 - 1 に信号を出力する。また、トランジスタ 15 - 8 は、トランジスタ 17 - 8 を介して垂直信号線 51 - 2 に信号を出力する。

【0057】

10

時刻  $t_1$  に、垂直走査回路 2 は、信号 P R E S を L レベルとする。これにより、浮遊拡散容量 13 - 5、浮遊拡散容量 13 - 6、浮遊拡散容量 13 - 7、浮遊拡散容量 13 - 8 の電位のリセットが解除される。

【0058】

時刻  $t_2$  に、垂直走査回路 2 は、信号 P T X 1 を H レベルとした後、時刻  $t_3$  に信号 P T X 1 を L レベルとする。これにより、画素 100 - 5 のトランジスタ 17 - 5 が垂直信号線 50 - 1 に光信号を出力する。また、画素 100 - 6 のトランジスタ 17 - 6 が垂直信号線 50 - 2 に光信号を出力する。ここでは、画素 100 - 7 および画素 100 - 8 は、それぞれがリファレンス信号を出力する第 1 の画素である。一方、画素 100 - 5 および画素 100 - 6 は、それぞれが光信号を出力する第 2 の画素である。ここでは、垂直信号線 51 - 1 および垂直信号線 51 - 2 のそれぞれは、第 1 の画素である画素 100 - 7 および画素 100 - 8 のそれぞれからリファレンス信号が入力される第 1 の垂直信号線である。また、垂直信号線 50 - 1 および垂直信号線 50 - 2 のそれぞれは、第 2 の画素である画素 100 - 5 および画素 100 - 6 のそれぞれから光信号が入力される第 2 の垂直信号線である。

20

【0059】

差動アンプ 80 は、画素 100 - 5 から入力される光信号と、画素 100 - 8 から入力されるリファレンス信号との差を增幅した信号を出力する。また、差動アンプ 81 は、画素 100 - 6 から入力される光信号と、画素 100 - 7 から入力されるリファレンス信号との差を增幅した信号を出力する。

30

【0060】

時刻  $t_4$  に、タイミングジェネレータは、信号 P C T を H レベルとした後、時刻  $t_5$  に信号 P T C を L レベルとする。これにより、容量素子 C T p 1、C T m 1 は差動アンプ 80 が output する信号を保持する。また、容量素子 C T p 2、C T m 2 は差動アンプ 81 が output する信号を保持する。

【0061】

時刻  $t_6$  から時刻  $t_7$  の期間、水平走査回路 30 は、各列の容量素子 C T m、容量素子 C T p を順次走査する。本実施例の撮像装置では、スイッチ 200 - 1、スイッチ 201 - 1、スイッチ 200 - 2、スイッチ 201 - 2 を同時に導通状態とする。これにより、容量素子 C T p 1、容量素子 C T m 1 が output アンプ 400 - 1 に信号を出力する期間と、容量素子 C T p 2、容量素子 C T m 2 が output アンプ 400 - 2 に信号を出力する期間とを重ねることができる。これにより、実施例 1 の撮像装置に比して、本実施例の撮像装置は、水平走査期間を短縮することができる。

40

【0062】

時刻  $t_7$  に、垂直走査回路 2 は信号 P S E L 1 を L レベルとする。

【0063】

時刻  $t_8$  に、垂直走査回路 2 は、信号 P R E S を H レベルとする。これにより、浮遊拡散容量 13 - 5、浮遊拡散容量 13 - 6、浮遊拡散容量 13 - 7、浮遊拡散容量 13 - 8 の電位がリセットされる。また、垂直走査回路 2 は、信号 P S E L 2 を H レベルとする。これにより、各画素 100 のトランジスタ 18 が導通状態となる。よって、トランジスタ

50

15-5は、トランジスタ18-5を介して垂直信号線51-1に信号を出力する。また、トランジスタ15-6は、トランジスタ18-6を介して垂直信号線51-2に信号を出力する。また、トランジスタ15-7は、トランジスタ18-7を介して垂直信号線50-1に信号を出力する。また、トランジスタ15-8は、トランジスタ18-8を介して垂直信号線50-2に信号を出力する。

【0064】

時刻t9に、垂直走査回路2は、信号PRESをLレベルとする。これにより、浮遊拡散容量13-5、浮遊拡散容量13-6、浮遊拡散容量13-7、浮遊拡散容量13-8の電位のリセットが解除される。

【0065】

時刻t10に、垂直走査回路2は、信号PTX2をHレベルとした後、時刻t11に信号PTX2をLレベルとする。これにより、画素100-7のトランジスタ17-7が垂直信号線51-1に光信号を出力する。また、画素100-8のトランジスタ17-8が垂直信号線51-2に光信号を出力する。ここでは、画素100-5および画素100-6は、それぞれがリファレンス信号を出力する第1の画素である。一方、画素100-7および画素100-8は、それぞれが光信号を出力する第2の画素である。ここでは、垂直信号線51-1および垂直信号線51-2のそれぞれは、第1の画素である画素100-5および画素100-6のそれぞれからリファレンス信号が入力される第1の垂直信号線である。また、垂直信号線50-1および垂直信号線50-2のそれぞれは、第2の画素である画素100-7および画素100-8のそれぞれから光信号が入力される第2の垂直信号線である。

【0066】

差動アンプ80は、画素100-7から入力される光信号と、画素100-6から入力されるリファレンス信号との差を増幅した信号を出力する。また、差動アンプ81は、画素100-8から入力される光信号と、画素100-5から入力されるリファレンス信号との差を増幅した信号を出力する。

【0067】

時刻t12、時刻t13の動作は、時刻t4、時刻t5の動作とそれぞれ同じである。

【0068】

時刻t14から時刻t15の動作は、時刻t6から時刻t7の動作と同じである。

【0069】

本実施例の撮像装置においても、実施例1と同じ効果を得ることができる。さらに、画素100の各列に対して2本の垂直信号線50、51を設けることによって、隣接する2列の画素100から光信号を、実施例1の撮像装置よりも高速に読み出すことができる。

【0070】

また、本実施例の撮像装置は、複数の出力アンプ400-1、400-2を有している。これにより、本実施例の撮像装置は、2列の画素100の光信号に基づく信号を外部に出力する期間を互いに重ねることができる。これにより、複数列の画素100の光信号に基づく信号を撮像装置の外部に出力する期間を短縮することができる。

【0071】

尚、本実施例では、1列の画素100に対し、2本の垂直信号線を設けていたが、さらに多くの垂直信号線を設けるようにしても良い。また、本実施例の撮像装置は、2つの出力アンプ400を有していたが、さらに多くの出力アンプ400を有するようにしても良い。

【0072】

本実施例の別の例を図7に示す。図7の撮像装置は、差動アンプ80と差動アンプ81が、画素100が設けられた撮像領域1を挟んで設けられている。図5の撮像装置では、2列の画素100に対応して、2列分の差動アンプ80、81を設ける幅が必要であった。この構成の場合、撮像装置の画素数の増大によって2列の画素100の幅が狭くなると、2列の差動アンプ80、81を設けられなくなることがある。一方で、図7の撮像装置

10

20

30

40

50

では、2列の画素100に対応して、1列分の差動アンプ80の幅に、差動アンプ80、差動アンプ81を収めることができる。これにより、図7の撮像装置は、図5の撮像装置に比して、撮像装置の画素数の増大による2列の画素100の幅の狭小化に対応しやすくなることができる。

【0073】

(実施例3)

本実施例の撮像装置について、実施例2と異なる点を中心に説明する。

【0074】

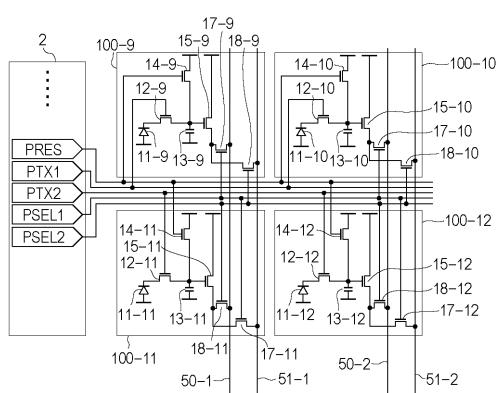

図8は、本実施例の撮像装置の構成を示した図である。

【0075】

実施例2では、信号PTX1は、同一行である画素100-5、画素100-6に共通して供給されていた。また、実施例2では、信号PTX2は、同一行である画素100-7、画素100-8に共通して供給されていた。本実施例では、信号PTX1は、同一列である画素100-9、画素100-11に共通して供給される。また、本実施例では、信号PTX2は、同一列である画素100-10、画素100-12に共通して供給される。

【0076】

図8の撮像装置では、画素100の構成は、実施例2の画素100の構成と同じである。

【0077】

本実施例の差信号生成部3、水平転送部4は実施例2の図5に記載の構成と同じである。

【0078】

本実施例では、光信号を出力する画素100と、当該光信号との差を得るためのリファレンス信号を出力する画素100とが同一行に設けられている。

【0079】

図8の撮像装置の動作は、実施例2の図6を参照しながら説明した動作と同じである。

【0080】

図6の時刻t5において、本実施例の撮像装置では、容量素子CTp1、容量素子CTm1が、画素100-9が出力する光信号と、画素100-10が出力するリファレンス信号との差の信号を差動アンプ80が増幅した信号を保持する。また、同時刻において、容量素子CTp2、容量素子CTm2が、画素100-11が出力する光信号と、画素100-12が出力するリファレンス信号との差の信号を増幅アンプ81が増幅した信号を保持する。

【0081】

また、図6の時刻t13において、本実施例の撮像装置では、容量素子CTp1、容量素子CTm1が、画素100-10が出力する光信号と、画素100-9が出力するリファレンス信号との差の信号を差動アンプ80が増幅した信号を保持する。また同時刻において、容量素子CTp2、容量素子CTm2が、画素100-12が出力する光信号と、画素100-11が出力するリファレンス信号との差の信号を差動アンプ81が増幅した信号を保持する。

【0082】

本実施例の撮像装置においても、実施例2の撮像装置と同じ効果を得ることができる。

【0083】

また、本実施例の撮像装置においても、実施例2にて図7を参照しながら説明した差信号生成部3、水平転送部4の構成としても良い。

【0084】

(実施例4)

本実施例の撮像装置について、実施例2と異なる点を中心に説明する。本実施例の撮像装置は、第1の行に属する画素100が光信号を同じタイミングで出力する。そして、光

10

20

30

40

50

信号と同じタイミングで差信号生成部3に入力されるリファレンス信号を、第1の行に先立って光信号を出力した第2の行の画素110が出力する。

【0085】

図9は、本実施例の撮像装置の構成を示した図である。撮像領域1には、複数の画素110が行列状に設けられている。図9では、複数の画素110の各々について、それぞれ枝番を付して表している。複数の画素110の各々は、フォトダイオード111、トランジスタ112、浮遊拡散容量113、トランジスタ114、トランジスタ115、トランジスタ117、トランジスタ118を有する。画素110が有する部材についても、図9では、画素110に付した枝番と対応する枝番を付している。

【0086】

また、図9では、垂直走査回路2が出力する信号について、n行目の画素行に出力する信号を、信号名称の後に[n]を付して表している。

【0087】

図9の差信号生成部3、水平転送部4は、実施例2にて図5を参照しながら説明した構成と同じ構成である。

【0088】

フォトダイオード111-1は、入射光に基づく電荷を蓄積する光電変換部である。トランジスタ112-1は、垂直走査回路2から入力される信号PTX[1]がHレベルとなると、フォトダイオード111-1に蓄積された電荷を浮遊拡散容量113-1に転送する。トランジスタ115-1は、入力ノードが浮遊拡散容量113-1に電気的に接続されている。トランジスタ115-1は、トランジスタ117-1と垂直信号線500-1を介して差動アンプ80の非反転入力ノードに電気的に接続される。

【0089】

トランジスタ117-1は、垂直走査回路2から入力される信号PSEL1[1]がHレベルとなると、トランジスタ115-1が出力する信号を垂直信号線500-1に出力する。

【0090】

トランジスタ118-1は、垂直走査回路2から入力される信号PSEL2[1]がHレベルとなると、トランジスタ115-1が出力する信号を垂直信号線501-1に出力する。

【0091】

トランジスタ114-1は、垂直走査回路2から入力される信号PRES[1]がHレベルとなると、浮遊拡散容量113-1の電位を電源電圧VDDに基づく電位にリセットする。

【0092】

尚、図9の撮像装置では、垂直走査回路2が出力する信号PRES、信号PTX、信号PSEL1、信号PSEL2のそれぞれは、同一行の画素110に対して共通の信号である。よって、画素110-2の動作は、画素110-1と同じ動作となる。

【0093】

図10は、図9の撮像装置の動作を示したタイミング図である。

【0094】

図10に示したタイミング図では、図9に示した画素110のうち、1行目に属する画素110は、既に光信号の出力を終了している。そして図10に示したタイミング図では、図9に示した画素110のうち、2行目および3行目に属する画素110が光信号を出力する。

【0095】

時刻t0に、垂直走査回路2は、信号PRES[1]をHレベルとする。これにより、1行目の画素110の浮遊拡散容量113の電位がリセットされる。また、同時刻に垂直走査回路2は、信号PRES[2]をHレベルとする。これにより、2行目の画素110の浮遊拡散容量113の電位がリセットされる。

10

20

30

40

50

## 【0096】

また、時刻  $t_0$  に、垂直走査回路 2 は、信号 PSEL2[1] を H レベルとする。これにより、1 行目の画素 110 のトランジスタ 115 が、垂直信号線 501-1、垂直信号線 501-2 に信号を出力する。また、同時に、垂直走査回路 2 は、信号 PSEL1[2] を H レベルとする。これにより、2 行目の画素 110 のトランジスタ 115 が、垂直信号線 500-1、垂直信号線 500-2 に信号を出力する。

## 【0097】

時刻  $t_1$  に、垂直走査回路 2 は、信号 PRES[1]、信号 PRES[2] を L レベルとする。これにより、1 行目の画素 110 の浮遊拡散容量 113 のリセットが解除される。1 行目の画素 110 のトランジスタ 115 は、垂直信号線 501-1、垂直信号線 501-2 にリファレンス信号を出力する。

10

## 【0098】

時刻  $t_2$  に、垂直走査回路 2 は、信号 PTX[2] を H レベルとした後、時刻  $t_3$  に L レベルとする。これにより、2 行目の画素 110 において、トランジスタ 112 が、フォトダイオード 110 に蓄積された電荷を浮遊拡散容量 113 に転送する。これにより、2 行目の画素 110 が光信号を垂直信号線 500-1、垂直信号線 500-2 に出力する。ここでは、1 行目に属する画素 110-1 および画素 110-2 は、それぞれがリファレンス信号を出力する第 1 の画素である。一方、2 行目に属する画素 110-3 および画素 110-4 は、それぞれが光信号を出力する第 2 の画素である。ここでは、垂直信号線 501-1 および垂直信号線 501-2 のそれぞれは、第 1 の画素である画素 110-1 および画素 110-2 のそれからリファレンス信号が入力される第 1 の垂直信号線である。また、垂直信号線 500-1 および垂直信号線 500-2 のそれぞれは、第 2 の画素である画素 110-3 および画素 110-4 のそれから光信号が入力される第 2 の垂直信号線である。

20

## 【0099】

差動アンプ 80 は、2 行目の画素 110 の一つである画素 110-3 から入力される光信号と、1 行目の画素 110 の一つである画素 110-1 から入力されるリファレンス信号との差を増幅した信号を出力する。また、差動アンプ 81 は、2 行目の画素 110 の一つである画素 110-4 から入力される光信号と、1 行目の画素 110 の一つである画素 110-2 から入力されるリファレンス信号との差を増幅した信号を出力する。

30

## 【0100】

時刻  $t_4$  から時刻  $t_7$  までの信号 PCT および水平転送部 4 に関する動作は、実施例 2 において図 6 を参照しながら説明した時刻  $t_4$  から時刻  $t_7$  までの動作と同じである。

## 【0101】

これにより、撮像装置は、2 行目の画素 110 の光信号と、1 行目の画素 110 のリファレンス信号との差を増幅した信号を出力することができる。

## 【0102】

時刻  $t_7$  に、垂直走査回路 2 は、信号 PSEL2[1] および信号 PSEL1[2] を L レベルとする。

## 【0103】

時刻  $t_8$  に、垂直走査回路 2 は、信号 PRES[2] を H レベルとする。これにより、2 行目の画素 110 の浮遊拡散容量 113 の電位がリセットされる。また、同時に垂直走査回路 2 は、信号 PRES[3] を H レベルとする。これにより、3 行目の画素 110 の浮遊拡散容量 113 の電位がリセットされる。

40

## 【0104】

また、時刻  $t_8$  に、垂直走査回路 2 は、信号 PSEL2[2] を H レベルとする。これにより、2 行目の画素 110 のトランジスタ 115 が、垂直信号線 501-1、垂直信号線 501-2 に信号を出力する。また、同時に、垂直走査回路 2 は、信号 PSEL1[3] を H レベルとする。これにより、3 行目の画素 110 のトランジスタ 115 が、垂直信号線 500-1、垂直信号線 500-2 に信号を出力する。

50

## 【0105】

時刻  $t_9$  に、垂直走査回路 2 は、信号 P R E S [ 2 ]、信号 P R E S [ 3 ] を L レベルとする。これにより、2 行目の画素 110 の浮遊拡散容量 113 のリセットが解除される。2 行目の画素 110 のトランジスタ 115 は、垂直信号線 501-1、垂直信号線 501-2 にリファレンス信号を出力する。

## 【0106】

時刻  $t_{10}$  に、垂直走査回路 2 は、信号 P T X [ 3 ] を H レベルとした後、時刻  $t_{11}$  に L レベルとする。これにより、3 行目の画素 110 において、トランジスタ 112 が、フォトダイオード 110 に蓄積された電荷を浮遊拡散容量 113 に転送する。これにより、3 行目の画素 110 が光信号を垂直信号線 500-1、垂直信号線 501-1 に出力する。ここでは、2 行目に属する画素 110-3 および画素 110-4 は、それぞれがリファレンス信号を出力する第 1 の画素である。一方、3 行目に属する画素 110-5 および画素 110-6 は、それぞれが光信号を出力する第 2 の画素である。ここでは、垂直信号線 501-1 および垂直信号線 501-2 のそれぞれは、第 1 の画素である画素 110-3 および画素 110-4 のそれからリファレンス信号が入力される第 1 の垂直信号線である。また、垂直信号線 500-1 および垂直信号線 500-2 のそれぞれは、第 2 の画素である画素 110-5 および画素 110-6 のそれから光信号が入力される第 2 の垂直信号線である。

## 【0107】

差動アンプ 80 は、3 行目の画素 110 の一つである画素 110-5 から入力される光信号と、2 行目の画素 110 の一つである画素 110-3 から入力されるリファレンス信号との差を増幅した信号を出力する。また、差動アンプ 81 は、3 行目の画素 110 の一つである画素 110-6 から入力される光信号と、2 行目の画素 110 の一つである画素 110-4 から入力されるリファレンス信号との差を増幅した信号を出力する。

## 【0108】

時刻  $t_{12}$  から時刻  $t_{15}$  までの信号 P C T および水平転送部 4 に関わる動作は、時刻  $t_4$  から時刻  $t_7$  までの動作と同じである。

## 【0109】

このように、本実施例の撮像装置においても、実施例 2 と同じ効果を得ることができる。

## 【0110】

また、1 行目の画素 110 が出力する光信号は、例えば、2 行目の画素 110 が出力するリファレンス信号と差を得るようにも良い。また、1 行目の画素 110 が出力する光信号は、撮像領域の外部に設けられた、フォトダイオード 110 が遮光されたオプティカルブラック画素が出力するリファレンス信号と差に基づく信号を得るようにも良い。この場合には、2 行目の画素 110 の光信号と 1 行目の画素 110 のリファレンス信号との差を得る工程に先立って、1 行目の画素 110 の光信号とオプティカルブラック画素が出力する信号との差に基づく信号を得るようにも良い。また、1 行目の画素 110 が出力する光信号は、撮像領域の外部に設けられた、フォトダイオード 110 が設けられておらず、一定の信号を出力するリファレンス画素が出力するリファレンス信号と差を得るようにも良い。この場合には、2 行目の画素 110 の光信号と 1 行目の画素 110 のリファレンス信号との差を得る工程に先立って、1 行目の画素 110 の光信号とリファレンス画素が出力するリファレンス信号との差に基づく信号を得るようにも良い。尚、オプティカルブラック画素もしくはリファレンス画素は、1 行目の画素 110 の近傍に設けられていることが好ましい。

## 【0111】

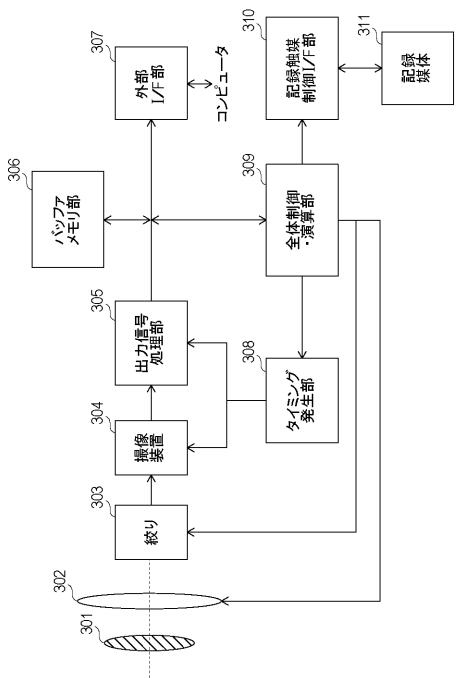

## (実施例 5)

これまで実施例 1 ~ 4 で述べた撮像装置を撮像システムに適用した場合の実施例について述べる。撮像システムとして、デジタルスチルカメラやデジタルカムコーダーや監視カメラなどがあげられる。図 11 に、撮像システムの例としてデジタルスチルカメラに撮像

10

20

30

40

50

装置を適用した場合のブロック図を示す。

【0112】

図11において、撮像システムは被写体の光学像を撮像装置304に結像させるレンズ302、レンズ302の保護のためのバリア301、レンズ302を通った光量を可変にするための絞り303を有する。また、撮像システムは撮像装置304より出力される出力信号の処理を行う出力信号処理部305を有する。

【0113】

出力信号処理部305はデジタル信号処理部を有し、撮像装置304から出力される信号を、必要に応じて各種の補正、圧縮を行って信号を出力する動作を行う。

【0114】

また、撮像システムは、画像データを一時的に記憶する為のバッファメモリ部306、記録媒体に記録または読み出しを行うための記憶媒体制御インターフェース部308を有する。さらに撮像システムは、撮像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体309を有する。さらに、撮像システムは、外部コンピュータ等と通信する為の外部インターフェース部307、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部309、撮像装置304を有する。さらに撮像システムは、出力信号処理部305に、各種タイミング信号を出力するタイミング発生部308を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システムは少なくとも撮像装置304と、撮像装置304から出力された出力信号を処理する出力信号処理部305とを有すればよい。

10

【0115】

以上のように、本実施例の撮像システムは、撮像装置304を適用して撮像動作を行うことが可能である。

【符号の説明】

【0116】

- 1 撮像領域

- 2 垂直走査回路

- 3 差信号生成部

- 4 水平転送部

- 8 差動アンプ

- 30 水平走査回路

- 100 画素

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(56)参考文献 米国特許出願公開第2009/0190005(US, A1)

米国特許出願公開第2004/0051802(US, A1)

特開2006-108889(JP, A)

特開2009-147540(JP, A)

特開2013-187744(JP, A)

特開2010-130317(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/225-5/378

H04N 9/00-9/11