(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-150283

(P2005-150283A)

(43) 公開日 平成17年6月9日(2005.6.9)

(51) Int.Cl.<sup>7</sup>

H01L 25/00

F 1

H01L 25/00

B

テーマコード(参考)

審査請求 未請求 請求項の数 5 O L (全 7 頁)

(21) 出願番号

特願2003-383617 (P2003-383617)

(22) 出願日

平成15年11月13日 (2003.11.13)

(71) 出願人 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100085187

弁理士 井島 藤治

(74) 代理人 100090424

弁理士 鮫島 信重

(72) 発明者 小林 恵子

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 福井 宏和

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(54) 【発明の名称】 BGAパッケージ

## (57) 【要約】

【課題】 内部に半導体ICを収容し、底面に他の装置との接続のための複数のパッドが設けられたBGAパッケージに関し、電気的特性の向上、小型化が図れるBGAパッケージを提供することを課題とする。

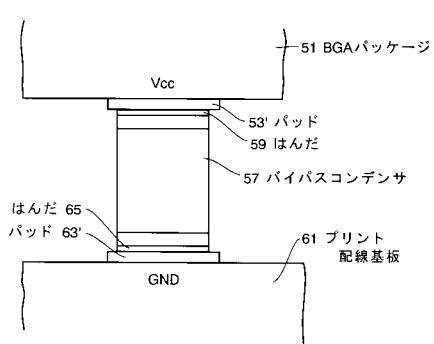

【解決手段】 BGAパッケージ51の複数のパッド53のうちの少なくとも1つのパッド53に、回路部品であるバイパスコンデンサ57を接続する。そして、バイパスコンデンサ57はプリント配線基板61のパッド63に接続される。

【選択図】

図1

第1の形態例の構成図

**【特許請求の範囲】****【請求項 1】**

内部に半導体ICを収容し、底面に他の装置との接続のための複数のパッドが設けられたBGAパッケージにおいて、

前記複数のパッドのうちの少なくとも1つに、回路部品が接続されたことを特徴とするBGAパッケージ。

**【請求項 2】**

前記回路部品の一方の端子は、前記BGAパッケージのパッドに接続され、他方の端子は前記他の装置に接続されることを特徴とする請求項1記載のBGAパッケージ。

**【請求項 3】**

前記回路部品は、前記BGAパッケージの複数のパッドのうちの隣接するパッド間に接続されることを特徴とする請求項1記載のBGAパッケージ。

**【請求項 4】**

前記回路部品は複数あることを特徴とする請求項1乃至3のいずれかに記載のBGAパッケージ。

**【請求項 5】**

前記回路部品は、バイパスコンデンサ、抵抗、コイルのうちの少なくとも1つであることを特徴とする請求項1乃至4のいずれかに記載のBGAパッケージ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、内部に半導体ICを収容し、底面に他の装置との接続のための複数のパッドが設けられたBGAパッケージに関する。

**【背景技術】****【0002】**

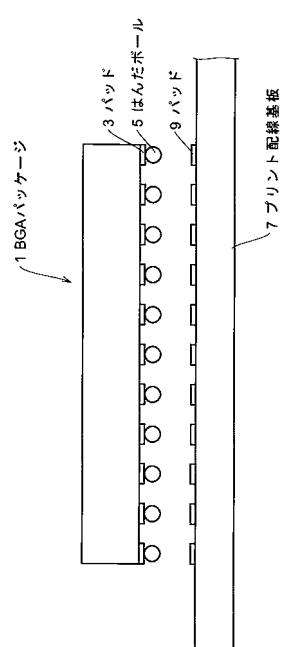

プリント配線基板にデバイスを実装するために、表面実装デバイスが用いられる。表面実装デバイスとして、図6に示すようなBGA(Ball Grid Array)パッケージの半導体デバイスがある。図において、BGAパッケージ1の下面には、パッド3が格子状に設けられ、更に、端子3には、はんだボール5が付着されている。

**【0003】**

一方、プリント配線基板(PCB)7には、BGAパッケージ1のパッド3と対応するパッド9が設けられている。そして、はんだボール5がプリント配線基板7のパッド9に接するようにBGAパッケージ1を配置し、外部から熱を加えてはんだボール5を融解し、BGAパッケージ1をプリント配線基板7に実装する。装置全体が小型化しつつある現状においては、BGAパッケージが広く使用されつつある。

**【0004】**

一方、デジタル回路や高周波回路等のような高速な動作クロックを用いて作動する半導体デバイスがプリント配線基板に実装された場合には、電源ラインに電流変動ノイズが発生し、半導体デバイスに悪影響が及ぶことがある。そのため、ノイズ除去のために、半導体デバイスの電力供給端子の近傍にバイパスコンデンサ(パスコン)を設けることがある。

**【0005】**

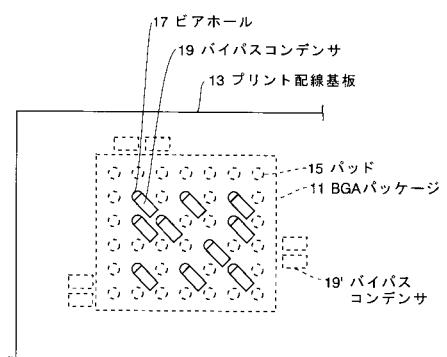

図7にその一例を示す。図はBGAパッケージ11が実装されたプリント配線基板13の裏面を示している。破線で示す15はBGAパッケージ11のパッドである。又、実線で示す17は、プリント配線基板13の表面と裏面とを配線するビアホール(Via Hole)である。このビアホール17を用いてプリント配線基板13の裏面に、バイパスコンデンサ19が接続されている。

**【0006】**

しかし、信号ラインとの関係でビアホール17によりプリント配線基板の裏面まで配線できる電源ラインには制限があり、BGAパッケージ11の周縁にもバイパスコンデンサ

10

20

30

40

50

19 を設けている。

【0007】

バイパスコンデンサは、電源ラインに可能な限り近く設けることが必要で、BGAパッケージ11の周縁に設けたバイパスコンデンサ19は、ノイズ除去効果があまり期待できない。又、プリント配線基板13も大きくなる。

【0008】

そこで、BGAパッケージの場合、以下のような方法で、バイパスコンデンサを設けることが提案されている。

(1) BGAパッケージ内にバイパスコンデンサを設ける。

【0009】

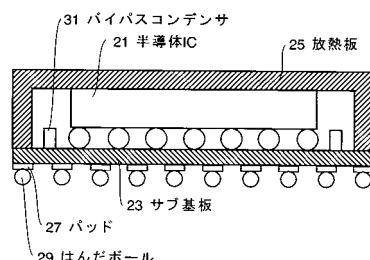

図8に示すように、半導体IC(チップ)21はサブ基板23上に設けられ、サブ基板23には、半導体IC21を覆い、半導体IC21の上面に当接する蓋状の放熱板25が設けられている。サブ基板23の下面には、他の装置との接続のための複数のパッド27が設けられ、更に、各パッド27には、はんだボール29が付着されている。そして、バイパスコンデンサ31がサブ基板23上に設けられている。

(2) BGAパッケージの上面にバイパスコンデンサを搭載する(例えば、特許文献1参照。)。

【特許文献1】特開2002-184894号公報(第4頁、図3参照)

【発明の開示】

【発明が解決しようとする課題】

【0010】

しかし、上述した(1)(2)のような方法では、以下のような問題点がある。

(1)半導体IC1の面積が大きくなると、サブ基板23にバイパスコンデンサ31を設けるスペースがなくなる。バイパスコンデンサ31をサブ基板23にどうしても設けようすると、BGAパッケージが大形化し、プリント配線基板も大形化する。

(2)BGAパッケージの上面に放熱フィンや放熱ファンを載せる場合は、バイパスコンデンサは搭載できない。

【0011】

又、バイパスコンデンサの代わりに、電気的特性の向上のために抵抗やコイル等の回路部品を用いる場合であっても、上述の(1)、(2)に示す方法が可能であるが、同様な問題点が生じる。

【0012】

本発明は、上記問題点に鑑みてなされたもので、その課題は、電気的特性の向上、小型化が図れるBGAパッケージを提供することにある。

【課題を解決するための手段】

【0013】

上記課題を解決する請求項1に係る発明は、内部に半導体ICを収容し、底面に他の装置との接続のための複数のパッドが設けられたBGAパッケージにおいて、前記複数のパッドのうちの少なくとも1つに、回路部品が接続されたことを特徴とするBGAパッケージである。

【0014】

他の装置としては、プリント配線基板等があるが限定するものではない。

【0015】

請求項2に係る発明は、前記回路部品の一方の端子は、前記BGAパッケージのパッドに接続され、他方の端子は前記他の装置に接続されることを特徴とする請求項1記載のBGAパッケージである。

【0016】

請求項3に係る発明は、前記回路部品は、前記BGAパッケージの複数のパッドのうちの隣接するパッド間に接続されることを特徴とする請求項1記載のBGAパッケージである。

10

20

30

40

50

## 【0017】

請求項4に係る発明は、前記回路部品は複数あることを特徴とする請求項1乃至3のいずれかに記載のBGAパッケージである。

## 【0018】

請求項5に係る発明は、前記回路部品は、前記回路部品は、バイパスコンデンサ、抵抗、コイルのうちの少なくとも1つであることを特徴とする請求項1乃至4のいずれかに記載のBGAパッケージである。

## 【発明の効果】

## 【0019】

請求項1に係る発明によれば、前記複数のパッドのうちの少なくとも1つに、回路部品が接続されることにより、BGAパッケージの電気的特性の向上を図れ、BGAパッケージ、及びBGAパッケージが実装される装置の小型化が図れる。10

## 【0020】

請求項2に係る発明によれば、前記回路部品の一方の端子は、前記BGAパッケージのパッドに接続され、他方の端子は前記他の装置に接続されることにより、BGAパッケージの電気的特性の向上を図れ、BGAパッケージ、及びBGAパッケージが実装される装置の小型化が図れる。

## 【0021】

請求項3に係る発明によれば、前記回路部品は、前記BGAパッケージの複数のパッドのうちの隣接するパッド間に接続されることにより、BGAパッケージの電気的特性の向上を図れ、BGAパッケージ、及びBGAパッケージが実装される装置の小型化が図れる。20

## 【0022】

請求項4に係る発明によれば、前記回路部品は複数あることにより、BGAパッケージの実装時に、はんだボールのつぶれによる実装不良を防止することができる。

## 【0023】

請求項5に係る発明によれば、前記回路部品は、前記回路部品は、バイパスコンデンサ、抵抗、コイルのうちの少なくとも1つであることにより、BGAパッケージの電気的特性の向上を図れ、BGAパッケージ、及びBGAパッケージが実装される装置の小型化が図れる。30

## 【発明を実施するための最良の形態】

## 【0024】

以下、図面を用いて本発明を実施するための最良の形態を説明する。

(第1の形態例請求項1, 2, 4, 5に対応)

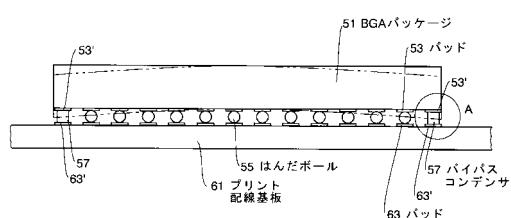

第1の形態例の構成図である図1、図1のA部分の拡大図である図2を用いて説明する。図において、BGAパッケージ51の下面には、複数のパッド53が格子状に設けられている。複数のパッド53のうちの少なくとも1つ、本形態例では、両サイドのパッド53以外のパッド53には、はんだボール55が付着されている。両サイドのパッド53(本実形態例では、電源ライン(Vcc)である)には、回路部品、本形態例では、バイパスコンデンサ57がはんだ59を用いて実装されている。40

## 【0025】

一方、プリント配線基板(PCB)61には、BGAパッケージ51のパッド53、パッド53と対応するパッド63、パッド63が設けられている。本実形態例では、パッド63は接地ライン(GND)である。又、バイパスコンデンサ57のパッド63と対向する部分には、はんだ65が付着している。

## 【0026】

そして、はんだボール55がプリント配線基板61のパッド63に接するように、又、バイパスコンデンサ57のはんだ65がプリント配線基板61のパッド63に接するようにBGAパッケージ51を配置し、外部から熱を加えてはんだボール55、はんだ65を融解することにより、BGAパッケージ51はプリント配線基板61に実装されている50

。

## 【0027】

このような構成によれば、以下のような効果を得ることができる。

(1) BGAパッケージ51の複数のパッドのうちの電源ラインであるパッド53に、バイパスコンデンサ(回路部品)57が接続されることにより、ノイズの効果的な低減(電気的特性の向上)及びBGAパッケージ51、プリント配線基板61の小型化が図れる。

(2) バイパスコンデンサ57を複数設けたことにより、BGAパッケージ51が熱により撓む場合、例えば、図1において、二点鎖線で示すように変形しても、はんだボール55より圧縮や引張に対して変形しにくいバイパスコンデンサ57を複数実装したことにより、はんだボール55が圧縮されてショートしたり、引っ張られて切断され、電気的導通がなくなったりすることが防止できる。

## 【0028】

尚、本発明は、上記形態例に限定するものではない。上記形態例では、回路部品としてバイパスコンデンサ57を用いた例で説明を行ったが、他に抵抗やコイル等の回路部品であってもよい。又、バイパスコンデンサ57を複数設けたが、1つであってもよい。

## 【0029】

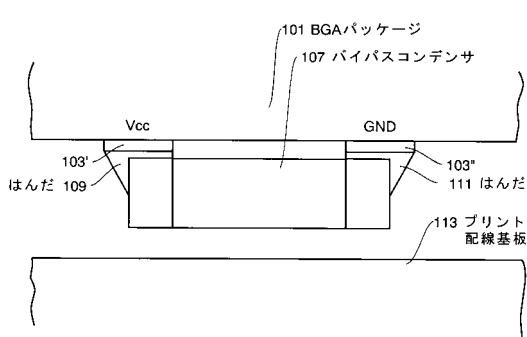

(第2の形態例請求項1,3,5に対応)

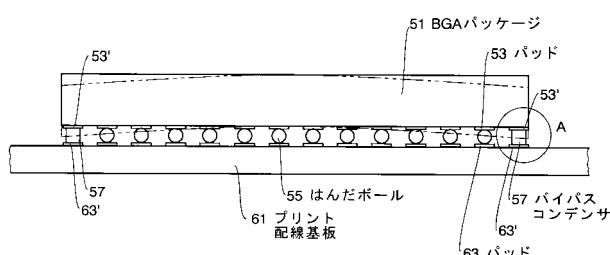

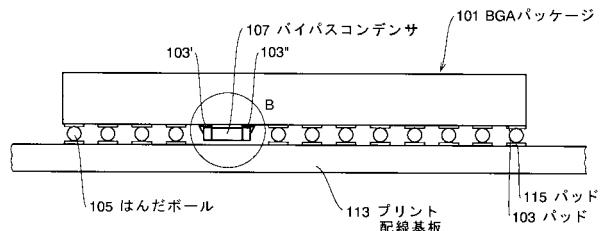

第2の形態例の構成図である図3、図3のB部分の拡大図である図4を用いて説明する。図において、BGAパッケージ101の下面には、複数のパッド103が格子状に設けられている。複数のパッド103のうちの隣接するパッド103、パッド103以外のパッド103には、はんだボール105が付着されている。尚、本形態例では、パッド103は電源ライン(Vcc)、パッド103は接地ライン(GND)に接続されている。

## 【0030】

パッド103、パッド103間には、回路部品、本形態例では、バイパスコンデンサ107がはんだ109、はんだ111を用いて実装されている。

## 【0031】

一方、プリント配線基板(PCB)113には、BGAパッケージ101のパッド103と対応するパッド115が設けられている。

## 【0032】

そして、はんだボール105がプリント配線基板113のパッド115に接するようにBGAパッケージ101を配置し、外部から熱を加えてはんだボール105を融解することにより、BGAパッケージ101はプリント配線基板113に実装されている。

## 【0033】

このような構成によれば、以下のような効果を得ることができる。

(1) BGAパッケージ101の複数のパッドのうちの隣り合うパッド(Vcc)103、パッド(GND)103に、バイパスコンデンサ(回路部品)107が接続されることにより、ノイズの効果的な低減(電気的特性の向上)及びBGAパッケージ101、プリント配線基板113の小型化が図れる。

## 【0034】

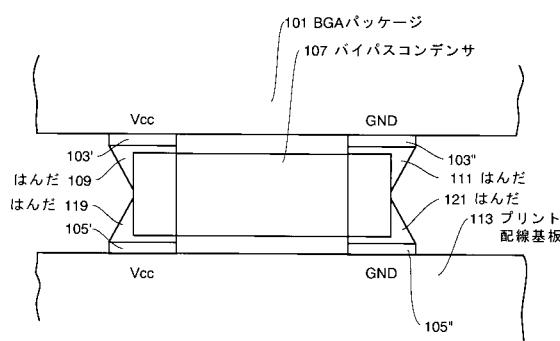

尚、本発明は、上記形態例に限定するものではない。上記実施の形態例では、バイパスコンデンサ107はBGAパッケージ101のパッド(Vcc)103、パッド(GND)103に実装したが、更に、図5に示すように、プリント配線基板113に、BGAパッケージ101のパッド(Vcc)103に対応し、プリント配線基板113の電源ラインに接続されるパッド105と、BGAパッケージ101のパッド(GND)103に対応し、プリント配線基板113の接地ラインに接続されるパッド105とを設け、パッド105とははんだ119を用いて、パッド105とははんだ121を用いてバイパスコンデンサと接続するようにしてもよい。

## 【0035】

10

20

30

40

50

又、上記形態例では、回路部品としてバイパスコンデンサ 107 を用いた例で説明を行ったが、他に抵抗やコイル等の回路部品であってもよい。又、バイパスコンデンサ 107 を複数設けてよい。

【図面の簡単な説明】

【0036】

【図1】第1の形態例の構成図である。

【図2】図1のA部分の拡大図である。

【図3】第2の形態例の構成図である。

【図4】図3のB部分の拡大図である。

【図5】他の形態例を説明する図である。

10

【図6】BGAパッケージのプリント配線基板への実装を説明する図である。

【図7】従来のバイパスコンデンサの実装を説明する図である。

【図8】従来のバイパスコンデンサの実装を説明する図である。

【符号の説明】

【0037】

51 BGAパッケージ

53, 53', 63, 63' パッド

55 はんだボール

57 バイパスコンデンサ

61 プリント配線基板

20

【図1】

第1の形態例の構成図

【図3】

第2の形態例の構成図

【図2】

図1のA部分の拡大図

【図4】

図3のB部分の拡大図

【図5】

他の形態例を説明する図

【図6】

BGAパッケージのプリント配線基板への実装を説明する図

【図7】

従来のバイパスコンデンサの実装を説明する図

【図8】

従来のバイパスコンデンサの実装を説明する図