(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-9686

(P2011-9686A)

(43) 公開日 平成23年1月13日(2011.1.13)

(51) Int.Cl.

H05K 3/46 (2006.01)

H05K 3/00 (2006.01)

F 1

H05K 3/46

H05K 3/00

テーマコード(参考)

5E346

X

審査請求 未請求 請求項の数 26 O L (全 24 頁)

(21) 出願番号 特願2009-263132 (P2009-263132)

(22) 出願日 平成21年11月18日 (2009.11.18)

(31) 優先権主張番号 098120959

(32) 優先日 平成21年6月23日 (2009.6.23)

(33) 優先権主張国 台湾(TW)

(71) 出願人 509319292

欣興電子股▲フン▼有限公司

台湾桃園縣桃園市▲亀▼山工業區興邦路3

8號

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100110364

弁理士 実広 信哉

(72) 発明者 劉 ▲謹▼銘

台湾桃園縣桃園市▲亀▼山工業區興邦路3

8號

最終頁に続く

(54) 【発明の名称】パッケージ基板及びその製造方法、並びにその基材

## (57) 【要約】

【課題】資源の無駄を省き、プロセスを簡略化できるパッケージ基板及びその製造方法、並びにその基材を提供する。

【解決手段】本発明に係るパッケージ基板の製造方法は、先ず、二つの金属層を相互にラミネートし、誘電体層で二つの金属層を覆い、次に、誘電体層の両側にビルドアップ構造をそれぞれ形成し、最後に二つの金属層の界面に沿って両側のビルドアップ構造を分離させることにより、二つのパッケージ基板を形成する。本発明は最初に誘電体層の粘着特性によって中間層である二つの金属層をビルドアップ構造の形成過程にて分離させず、最後に二つの金属層の周囲の誘電体層部分を切断することにより、二つの金属層を円滑に分離させることで、プロセスを簡略化することができる。又、中間層である二つの金属層をパターンングすることにより、回路層、金属パンプ、又は支持構造を形成することができるため、資源の無駄が生じない。

【選択図】図2 A

**【特許請求の範囲】****【請求項 1】**

一方の表面に内層回路層が設けられ、前記内層回路層に電気的に接続される複数の内層導電ビアが設けられる第1の補助誘電体層と、

前記第1の補助誘電体層の他方の表面の上に設けられ、前記内層導電ビアの各々に接続された金属バンプであって、前記内層導電ビアの、前記内層回路層に電気的に接続された一端の孔径が、前記内層導電ビアの、金属バンプに電気的に接続された一端の孔径より大きい複数の金属バンプと、

前記第1の補助誘電体層と前記内層回路層の上に設けられ、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に設けられる第1の回路層と、前記第1の誘電体層に設けられ前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を含むビルドアップ構造であって、前記ビルドアップ構造の最外層の前記第1の回路層が複数の第1の電気接触パッドを有するビルドアップ構造と、

前記ビルドアップ構造の上に設けられ、前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を有する第1の絶縁保護層と、

を含むことを特徴とするパッケージ基板。

**【請求項 2】**

前記金属バンプはソルダーバンップパッドであり、フリップチップパッケージの電気的接続に用いられることを特徴とする請求項1に記載のパッケージ基板。

**【請求項 3】**

前記金属バンプはヒートシンク及びその周囲に設けられる複数のボンディングパッドであり、前記ボンディングパッドはボンディングパッケージの電気的接続に用いられることを特徴とする請求項1に記載のパッケージ基板。

**【請求項 4】**

前記第1の補助誘電体層の上に設けられる金属支持フレームをさらに含むことを特徴とする請求項1に記載のパッケージ基板。

**【請求項 5】**

対向してラミネートされ、それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で相互に結合される二つの第1の金属層と、

前記第1の金属層の前記第2の表面の上にそれぞれ設けられ、二つの前記第1の金属層を覆う二つの第1の補助誘電体層と、

前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、

を含むことを特徴とする基材。

**【請求項 6】**

前記第1の金属層の前記第1の表面は平滑面であり、前記第2の表面は粗面であることを特徴とする請求項5に記載の基材。

**【請求項 7】**

対向してラミネートされ、対向する第1の表面と第2の表面を有し、前記第1の表面で相互に結合される二つの第1の金属層と、

前記第1の金属層の前記第2の表面の上にそれぞれ設けられ、二つの前記第1の金属層を覆う二つの第1の補助誘電体層と、

前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層と、

前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層と、

前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、

を含むことを特徴とする基材。

**【請求項 8】**

前記第1の金属層の前記第1の表面は平滑面であり、前記第2の表面は粗面であることを特徴とする請求項7に記載の基材。

10

20

30

40

50

**【請求項 9】**

それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体であって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆う基材を用意する工程と、

前記第2の金属層をパターニングすることにより内層回路層を形成する工程と、

前記第1の補助誘電体層と前記内層回路層の上にビルドアップ構造を形成することにより全体構造を形成する工程であって、前記ビルドアップ構造は、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を含む工程と、

を含むことを特徴とするパッケージ基板の製造方法。

**【請求項 10】**

前記第1の金属層の前記第1の表面は平滑面であり、前記第2の表面は粗面であることを特徴とする請求項9に記載のパッケージ基板の製造方法。

**【請求項 11】**

前記基材の製造方法は、

それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層を提供する工程と、

前記第1の金属層の前記第2の表面の上に前記第1の補助誘電体層をラミネートする工程と、

前記第1の補助誘電体層が露出した表面の上に前記第2の金属層をラミネートし、これらの前記第1の金属層、前記第1の補助誘電体層、及び前記第2の金属層を圧着させることにより、二つの前記第1の補助誘電体層を一体に結合させ、二つの前記第1の金属層を覆う工程と、

を含むことを特徴とする請求項9に記載のパッケージ基板の製造方法。

**【請求項 12】**

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断し、前記第1の金属層の各々を分離することにより、二つの基礎基板を形成する工程をさらに含むことを特徴とする請求項9に記載のパッケージ基板の製造方法。

**【請求項 13】**

前記ビルドアップ構造の最外層の前記第1の回路層はさらに複数の第1の電気接触パッドを有し、前記ビルドアップ構造の上に第1の絶縁保護層が形成され、前記第1の絶縁保護層には前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔が形成されることを特徴とする請求項12に記載のパッケージ基板の製造方法。

**【請求項 14】**

前記第1の金属層をパターニングすることにより第2の回路層を形成し、前記第1の補助誘電体層には前記内層回路層と前記第2の回路層に電気的に接続される複数の第2の導電ビアを形成する工程をさらに含み、

前記第2の回路層はさらに複数の第2の電気接触パッドを有し、前記第1の補助誘電体層の上には第2の絶縁保護層を形成し、前記第2の絶縁保護層には前記第2の電気接触パッドの各々を露出させるための複数の第2の絶縁保護層開孔が形成されることを特徴とする請求項12に記載のパッケージ基板の製造方法。

**【請求項 15】**

前記ビルドアップ構造の最外層の前記第1の回路層はさらに複数の第1の電気接触パッドを有し、

前記ビルドアップ構造の上に第1の絶縁保護層を形成し、前記第1の絶縁保護層には前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を形成する工程と、

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断する工程と、前記第1の金属層の各々を分離させることにより、二つの基礎基板を形成する工程と、をさらに含むことを特徴とする請求項9に記載のパッケージ基板の製造方法。

#### 【請求項16】

前記第1の金属層を除去することにより前記第1の補助誘電体層を露出させ、前記第1の補助誘電体層には前記内層回路層の一部を露出させる複数の開孔を形成する工程をさらに含むことを特徴とする請求項15に記載のパッケージ基板の製造方法。

#### 【請求項17】

それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体であって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆う基材を用意する工程と、

前記第2の金属層をパターニングすることにより内層回路層を形成し、前記第1の補助誘電体層には前記内層回路層と前記第1の金属層に電気的に接続される複数の内層導電ビアを形成する工程と、

前記第1の補助誘電体層と前記内層回路層の上にビルトアップ構造を形成し、前記ビルトアップ構造が、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を含み、前記ビルトアップ構造の最外層の前記第1の回路層が複数の第1の電気接触パッドを有する工程と、

前記ビルトアップ構造の上に第1の絶縁保護層を形成することにより全体構造を形成し、前記第1の絶縁保護層には前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を形成する工程と、

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断する工程と、前記第1の金属層の各々を分離させることにより、二つの基礎基板を形成する工程と、を含むことを特徴とするパッケージ基板の製造方法。

#### 【請求項18】

前記第1の金属層の前記第1の表面は平滑面であり、前記第2の表面は粗面であることを特徴とする請求項17に記載のパッケージ基板の製造方法。

#### 【請求項19】

前記基材の製造方法は、

それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面でラミネートされる二つの第1の金属層を提供する工程と、

前記第1の金属層の前記第2の表面の上に前記第1の補助誘電体層をラミネートする工程と、

前記第1の補助誘電体層が露出した表面の上に前記第2の金属層をラミネートし、これらの前記第1の金属層、前記第1の補助誘電体層、及び前記第2の金属層を圧着することにより、二つの前記第1の補助誘電体層を一体に結合させ、二つの前記第1の金属層を覆う工程と、

を含むことを特徴とする請求項17に記載のパッケージ基板の製造方法。

#### 【請求項20】

前記第1の金属層の一部を除去することにより、前記導電内層ビアの各々に接続される複数の金属バンプを形成することを特徴とする請求項17に記載のパッケージ基板の製造方法。

#### 【請求項21】

前記第1の金属層の一部を除去することにより、前記第1の補助誘電体層の上に金属支持フレームを形成することを特徴とする請求項20に記載のパッケージ基板の製造方法。

#### 【請求項22】

それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネー

10

20

30

40

50

トされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層と、前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層と、前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体であって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆い、前記コア層の両表面にはそれぞれ第1の電気接触パッドと第2の電気接触パッドを複数有し、前記第2の電気接触パッドが前記第1の補助誘電体層の上にあるようにする基材を用意する工程と、

前記第2の金属層をパターニングすることにより内層回路層を形成し、前記第2の補助誘電体層には前記内層回路層と前記第1の電気接触パッドに電気的に接続される複数の内層導電ビアを形成する工程と、10

前記第2の補助誘電体層と前記内層回路層の上にビルドアップ構造を形成することにより全体構造を形成し、前記ビルドアップ構造が、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を含む工程と、

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断する工程と、前記第1の金属層の各々を分離させることにより、二つの基礎基板を形成する工程と、を含むことを特徴とするパッケージ基板の製造方法。

#### 【請求項23】

前記第1の金属層の前記第1の表面は平滑面であり、前記第2の表面は粗面であることを特徴とする請求項22に記載のパッケージ基板の製造方法。20

#### 【請求項24】

前記基材の製造方法は、

それぞれ対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層と、前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層と、前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層を提供する工程と、30

これらの前記第1の金属層、前記第1の補助誘電体層、前記コア層、前記第2の補助誘電体層、及び前記第2の金属層を圧着することにより、二つの前記第1の補助誘電体層を一体に結合させ二つの前記第1の金属層を被覆させ、前記第2の電気接触パッドを前記第1の補助誘電体層の表面に嵌め込む工程と、

を含むことを特徴とする請求項22に記載のパッケージ基板の製造方法。

#### 【請求項25】

前記ビルドアップ構造の最外層の前記第1の回路層は、さらに複数の第1の電気接触パッドを有し、前記ビルドアップ構造の上に第1の絶縁保護層を形成し、前記第1の絶縁保護層には前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を形成する工程を含むことを特徴とする請求項22に記載のパッケージ基板の製造方法。40

#### 【請求項26】

前記第1の金属層をパターニングすることにより第2の回路層を形成し、前記第1の補助誘電体層には前記第2の電気接触パッドと前記第2の回路層に電気的に接続される複数の第2の導電ビアを形成し、前記第2の回路層が複数の第2の電気接触パッドを有し、前記第1の補助誘電体層の上に第2の絶縁保護層を形成し、前記第2の絶縁保護層に前記第2の電気接触パッドの各々を露出させるための複数の第2の絶縁保護層開孔を形成する工程を含むことを特徴とする請求項22に記載のパッケージ基板の製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

10

20

30

40

50

**【0001】**

本発明は、パッケージ基板（package substrate）及びその製造方法、並びにその基材に関し、特に、低成本のパッケージ基板及びその製造方法、並びにその基材に関するものである。

**【背景技術】****【0002】**

電子産業の急速な発展に伴い、電子製品も多機能化、高性能化が進んでいる。より多くの能動素子、受動素子、及び配線を接続することで半導体パッケージの高集積化（integration）及び小型化（miniaturization）などのパッケージの要求を満たすべく、半導体パッケージ基板は両面回路基板から多層回路基板（multi-layer board）へと革新を遂げている。これにより、限られたスペースにおいて、層間接続（Interlayer connection）技術により、半導体パッケージ基板において利用可能なレイアウト面積を増加させ、高密度レイアウトの集積回路（integrated circuit）の需要に対応し、且つパッケージ基板の厚さを低減し、パッケージの軽薄短小化、電気性能の向上などの目的を達成している。10

**【0003】**

従来の技術において、多層回路基板は、コア板及びそのコア板の両面に対称的に形成されたビルドアップ構造からなる。しかしながら、コア板を使用すると、リード線の長さ及び全体構造の厚さが増加し、電子製品の機能を向上させつつ体積を低減していくという要求を満たし難い。そこで、コアレス（coreless）構造の回路基板が開発されるに至った。これにより、リード線の長さ及び全体構造の厚さを低減することができるため、高周波化と小型化の流れに対応することが可能となっている。20

**【0004】**

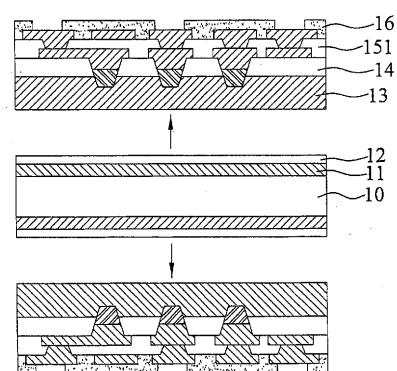

図1A乃至図1Fは従来のパッケージ基板及びその製造方法を示す断面図である。

**【0005】**

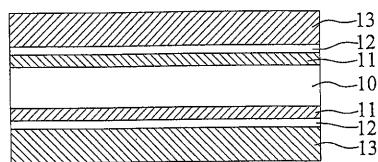

図1Aに示すように、先ず、載置基板10を用意する。この載置基板10の両面には薄膜金属層11、離型層12、及びキャリア金属層13が順に設けられる。

**【0006】**

図1Bに示すように、キャリア金属層13の上に第1の誘電体層14が形成される。

**【0007】**

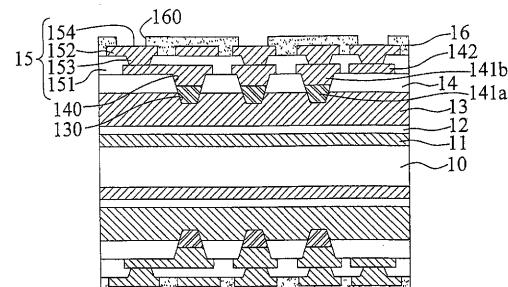

図1Cに示すように、第1の誘電体層14にはフォトリソグラフィー（photolithography）あるいはレーザアブレーション（laser ablation）のプロセスで複数のビア140が形成された後、これらのビア140に露出されたキャリア金属層13の一部の表面に、エッチングによって複数の凹部（concave）130が形成される。30

**【0008】**

図1Dに示すように、各凹部130及び各凹部130に対応するビア140の中に半田バンプ（solder bump）141aと第1の導電コンタクト141bが順に形成される。第1の誘電体層14の上には第1の導電コンタクト141bに電気的に接続される第1の回路層142が形成される。そして、第1の誘電体層14の上にビルトアップ構造15が形成される。ビルトアップ構造15は、少なくとも一つの第2の誘電体層151、第2の誘電体層151の上に設けられた第2の回路層152、及び第2の誘電体層151に設けられ第1の回路層142と第2の回路層152に電気的に接続された複数の第2の導電ビア153を含む。ビルトアップ構造15の最外層にある第2の回路層152は複数の電気接触パッド154を有する。そして、ビルトアップ構造15の最外層には絶縁保護層16が形成される。絶縁保護層16には各電気接触パッド154を露出させるための複数の絶縁保護層開孔160が形成される。40

**【0009】**

図1Eに示すように、離型層12により、キャリア金属層13から分離されることで、以降の工程で製作したパッケージ基板を載置基板10から分離させる。

10

20

30

40

50

**【0010】**

図1Fに示すように、以降の工程で半導体チップ(図示せず)を接続するために、キャリア金属層13を除去することで第1の誘電体層14の表面に突出する複数の半田バンプ141aが形成される。

**【0011】**

上述のように、従来のパッケージ基板の製造方法は、先ず、載置基板10の両側に両面の表面とも金属層が設けられる離型層12がそれぞれ形成され、次に、この構造の両側の金属層の上にビルドアップ構造15がそれぞれ形成され、最後に、離型層12とキャリア金属層13の界面に沿って両側のビルドアップ構造を分離させることで二つのパッケージ基板を形成する。

10

**【0012】**

しかしながら、従来の製造方法は両側の構造を一時的に支持するように載置基板10と薄膜金属層11を形成することが必要であるため、プロセスが複雑になり、さらに、最後には中間層である一時キャリア(載置基板10、両層の薄膜金属層11、及び両層の離型層12を含む)を除去して捨てなければならないため、材料の無駄が甚だしくなり、製造コストが増加する等の問題があった。

**【0013】**

従って、こうした状況に鑑み、従来技術のパッケージ基板の製造方法において、中間層である一時キャリアに離型層又は接着層を形成しながら最後に中間層である一時キャリアを捨てなければいけないことによるコストの無駄及びプロセスの複雑化などの問題を如何にして回避するかが、解決が待たれる極めて重要な課題となっている。

20

**【発明の概要】****【発明が解決しようとする課題】****【0014】**

本発明はこうした状況に鑑みてなされたものであり、その目的は、従来技術のパッケージ基板の製造方法における、中間層である一時キャリアに離型層又は接着層を形成しながら最後に中間層である一時キャリアを捨てなければいけないことによるコストの無駄及びプロセスの複雑化などの問題を解決することができるパッケージ基板及びその製造方法、並びにその基材を提供することにある。

30

**【課題を解決するための手段】****【0015】**

上記の目的及び他の目的を達成するために、本発明は、

一方の表面に内層回路層が設けられ、前記内層回路層に電気的に接続される複数の内層導電ビアが設けられた第1の補助誘電体層と、

前記第1の補助誘電体層の他方の表面の上に設けられ、前記内層導電ビアの各々に接続された金属バンプであって、前記内層導電ビアの電気的に接続された一端の孔径が、前記内層導電ビアの前記金属バンプが電気的に接続された一端の孔径より大きいようにする複数の金属バンプと、

前記第1の補助誘電体層と前記内層回路層の上に設けられ、少なくとも一つの第1の誘電体層、前記第1の誘電体層の上に設けられた第1の回路層と、前記第1の誘電体層に設けられ前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアと、を含むビルドアップ構造であって、このビルドアップ構造の最外層の第1の回路層が複数の第1の電気接触パッドを有するビルドアップ構造と、

40

前記ビルドアップ構造の上に設けられ、前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を有する第1の絶縁保護層と、

を備えるパッケージ基板を提供する。

**【0016】**

前記パッケージ基板において、前記金属バンプはソルダーバンプパッドであり、フリップチップパッケージ(flip chip package)の電気的接続に用いられる。あるいは、前記パッケージ基板において、前記金属バンプはヒートシンク及びその周囲に

50

設けられる複数のボンディングパッド ( bonding pad ) であり、前記ボンディングパッドはボンディングパッケージの電気的接続に用いられる。さらに金属支持フレームを含むことが好ましい。

【 0 0 1 7 】

本発明は、

対向してラミネートされ、対向する第 1 の表面と第 2 の表面を有し、前記第 1 の表面で相互に結合する二つの第 1 の金属層と、

前記第 1 の金属層の第 2 の表面の上にそれぞれ設けられ、二つの前記第 1 の金属層を覆う二つの第 1 の補助誘電体層と、

前記第 1 の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第 2 の金属層と、

を含む基材を提供する。

【 0 0 1 8 】

前記基材において、前記第 1 の金属層の前記第 1 の表面は平滑面であり、前記第 2 の表面は粗面である。

【 0 0 1 9 】

又、本発明は、

対向してラミネートされ、対向する第 1 の表面と第 2 の表面を有し、前記第 1 の表面で相互的に結合する二つの第 1 の金属層と、

前記第 1 の金属層の前記第 2 の表面の上にそれぞれ設けられ、二つの前記第 1 の金属層を覆う二つの第 1 の補助誘電体層と、

前記第 1 の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層と、

前記コア層が露出した表面の上にそれぞれ設けられる二つの第 2 の補助誘電体層と、

前記第 2 の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第 2 の金属層と、を含む基材を提供する。

【 0 0 2 0 】

前記基材において、前記第 1 の金属層の前記第 1 の表面は平滑面であり、前記第 2 の表面は粗面である。

【 0 0 2 1 】

本発明は、

対向する第 1 の表面と第 2 の表面を有し、前記第 1 の表面で対向してラミネートされる二つの第 1 の金属層と、前記第 1 の金属層の前記第 2 の表面の上にそれぞれ設けられる二つの第 1 の補助誘電体層と、前記第 1 の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第 2 の金属層と、からなるラミネート体であって、二つの前記第 1 の補助誘電体層が二つの前記第 1 の金属層を覆う基材を用意する工程と、

前記第 2 の金属層をパターニングすることにより内層回路層を形成する工程と、

前記第 1 の補助誘電体層と前記内層回路層の上にビルトアップ構造を形成することにより全体構造を形成する工程であって、前記ビルトアップ構造は、少なくとも一つの第 1 の誘電体層と、前記第 1 の誘電体層の上に形成される第 1 の回路層と、前記第 1 の誘電体層に形成され前記第 1 の回路層と前記内層回路層に電気的に接続される複数の第 1 の導電ビアと、を少なくとも含む工程と、

を含むパッケージ基板の製造方法を提供する。

【 0 0 2 2 】

前記パッケージ基板の製造方法において、前記基材の製造方法は、

対向する第 1 の表面と第 2 の表面を有し、前記第 1 の表面で対向してラミネートされる二つの第 1 の金属層を提供する工程と、

前記第 1 の金属層の前記第 2 の表面の上に前記第 1 の補助誘電体層をラミネートする工程と、

前記第 1 の補助誘電体層が露出した表面の上に前記第 2 の金属層をラミネートし、これらの前記第 1 の金属層、前記第 1 の補助誘電体層、及び前記第 2 の金属層を圧着すること

10

20

30

40

50

により、二つの前記第1の補助誘電体層を一体に結合させ、二つの前記第1の金属層を覆う工程と、

を含む。

**【0023】**

前記パッケージ基板の製造方法は、切断ラインが前記第1の金属層を通すように前記全体構造のエッジを切斷し、前記第1の金属層の各々を分離することにより、二つの基礎基板を形成する工程をさらに含む。前記パッケージ基板の製造方法において、前記ビルドアップ構造の最外層の第1の回路層はさらに複数の第1の電気接触パッドを有し、前記ビルドアップ構造の上に第1の絶縁保護層が形成され、前記第1の絶縁保護層には前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔が形成される。前記パッケージ基板の製造方法において、前記第1の金属層をパターニングすることにより第2の回路層を形成し、前記第1の補助誘電体層には前記内層回路層と前記第2の回路層に電気的に接続される複数の第2の導電ビアを形成する工程をさらに含み、前記第2の回路層はさらに複数の第2の電気接触パッドを有し、前記第1の補助誘電体層の上には第2の絶縁保護層を形成し、前記第2の絶縁保護層には前記第2の電気接触パッドの各々を露出させるための複数の第2の絶縁保護層開孔が形成される。

10

**【0024】**

前記パッケージ基板の製造方法の他の実施の態様において、前記ビルドアップ構造の最外層の第1の回路層はさらに複数の第1の電気接触パッドを有し、前記ビルドアップ構造の上に第1の絶縁保護層を形成し、前記第1の絶縁保護層には前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を形成する工程と、切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切斷する工程と、前記第1の金属層の各々を分離することにより、二つの基礎基板を形成する工程をさらに含む。前記パッケージ基板の製造方法において、前記第1の金属層を除去することにより前記第1の補助誘電体層を露出させ、前記第1の補助誘電体層に内層回路層の一部を露出させる複数の開孔を形成する工程をさらに含む。

20

**【0025】**

又、本発明は、

対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体であって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆う基材を用意する工程と、

30

前記第2の金属層をパターニングすることにより内層回路層を形成し、前記第1の補助誘電体層に前記内層回路層と前記第1の金属層に電気的に接続される複数の内層導電ビアを形成する工程と、

前記第1の補助誘電体層と前記内層回路層の上にビルドアップ構造を形成し、前記ビルドアップ構造が、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアとを含み、前記ビルドアップ構造の最外層の前記第1の回路層が複数の第1の電気接触パッドを有する工程と、

40

前記ビルドアップ構造の上に第1の絶縁保護層を形成することにより全体構造を形成し、前記第1の絶縁保護層に前記第1の電気接触パッドの各々を露出させるための複数の第1の絶縁保護層開孔を形成する工程と、

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切斷する工程と、前記第1の金属層の各々を分離することにより、二つの基礎基板を形成する工程と、を含むパッケージ基板の製造方法を提供する。

**【0026】**

前記パッケージ基板の製造方法において、前記基材の製造方法は、

50

対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートされる

二つの第1の金属層を提供する工程と、

前記第1の金属層の前記第2の表面の上に前記第1の補助誘電体層をラミネートする工程と、

前記第1の補助誘電体層が露出した表面の上に前記第2の金属層をラミネートし、これらの前記第1の金属層、前記第1の補助誘電体層、及び前記第2の金属層を圧着することにより、二つの前記第1の補助誘電体層を一体に結合させ、二つの前記第1の金属層を覆う工程と、を含む。

**【0027】**

前記パッケージ基板の製造方法において、前記第1の金属層の一部を除去することにより、前記内層ビアの各々に接続される複数の金属バンプ及び／又は金属支持フレームを形成する工程を含む。

**【0028】**

又、本発明は、

対向する第1の表面と第2の表面を有し前記第1の表面で対向してラミネートされる二つの第1の金属層と、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層と、前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層と、前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層と、からなるラミネート体であって、二つの前記第1の補助誘電体層が二つの前記第1の金属層を覆い、前記コア層の両表面には第1の電気接触パッドと第2の電気接触パッドを複数有し、前記第2の電気接触パッドが前記第1の補助誘電体層の上にあるようにする基材を用意する工程と、

前記第2の金属層をパターニングすることにより内層回路層を形成し、前記第2の補助誘電体層には前記内層回路層と前記第1の電気接触パッドに電気的に接続される複数の内層導電ビアを形成する工程と、

前記第2の補助誘電体層と前記内層回路層の上にビルドアップ構造を形成することにより全体構造を形成し、前記ビルドアップ構造が、少なくとも一つの第1の誘電体層と、前記第1の誘電体層の上に形成される第1の回路層と、前記第1の誘電体層に形成され前記第1の回路層と前記内層回路層に電気的に接続される複数の第1の導電ビアを含む工程と、

切断ラインが前記第1の金属層を通るように前記全体構造のエッジを切断する工程と、前記第1の金属層の各々を分離することにより、二つの基礎基板を形成する工程と、を含むパッケージ基板の製造方法を提供する。

**【0029】**

前記パッケージ基板の製造方法において、前記基材の製造方法は、

対向する第1の表面と第2の表面を有し、前記第1の表面で対向してラミネートする二つの第1の金属層、前記第1の金属層の前記第2の表面の上にそれぞれ設けられる二つの前記第1の補助誘電体層と、前記第1の補助誘電体層が露出した表面の上にそれぞれ設けられる二つのコア層、前記コア層が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層、及び前記第2の補助誘電体層が露出した表面の上にそれぞれ設けられる二つの第2の金属層を提供する工程と、

これらの前記第1の金属層、前記第1の補助誘電体層、前記コア層、前記第2の補助誘電体層、及び前記第2の金属層を圧着することにより、二つの前記第1の補助誘電体層を一体に結合させ二つの前記第1の金属層を覆い、前記第2の電気接触パッドを前記第1の補助誘電体層の表面に嵌め込む工程と、

を含む。

**【0030】**

前記パッケージ基板の製造方法において、前記ビルドアップ構造の最外層の第1の回路層はさらに複数の第1の電気接触パッドを有し、前記ビルドアップ構造の上に第1の絶縁保護層を形成し、前記第1の絶縁保護層に前記第1の電気接触パッドの各々を露出させる

10

20

30

40

50

ための複数の第1の絶縁保護層開孔を形成する工程を含む。

【0031】

前記パッケージ基板の製造方法は、前記第1の金属層をパターニングすることにより第2の回路層を形成し、前記第1の補助誘電体層に前記第2の電気接触パッドと前記第2の回路層に電気的に接続される複数の第2の導電ビアを形成し、前記第2の回路層が複数の第2の電気接触パッドを有し、前記第1の補助誘電体層の上に第2の絶縁保護層を形成し、前記第2の絶縁保護層に前記第2の電気接触パッドの各々を露出させるための複数の第2の絶縁保護層開孔を形成する工程を含む。

【0032】

上記三つのパッケージ基板の製造方法において、前記第1の金属層の第1の表面は平滑面であり、第2の表面は粗面である。 10

【発明の効果】

【0033】

上述のように、本発明に係るパッケージ基板は、先ず、二層の金属層をラミネートし、補助誘電体層で両層の金属層を覆い、次に、補助誘電体層の両側にビルドアップ構造をそれぞれ形成し、最後に二層の金属層の界面に沿って両側のビルドアップ構造を分離することにより二つのパッケージ基板を形成するものである。本発明は、最初に補助誘電体層の粘着特性によって中間層である二層の金属層をビルドアップ構造の形成過程にて分離せず、最後に二層の金属層の周囲の補助誘電体層の一部を切断することにより、二層の金属層を円滑に分離させ、プロセスを簡略化することができる。又、中間層である二層の金属層をパターニングすることにより、回路層、金属バンプ又は支持構造を形成することができるため、従来技術のパッケージ基板の製造方法が中間層である一時キャリアに離型層又は接着層を形成しながら最後に中間層である一時キャリアを捨てなければいけないことによるコストの無駄及びプロセスの複雑化などの問題を回避することができる。従って、本発明は無駄を省き、プロセスとコストを低減することができる。 20

【0034】

又、本発明に係るパッケージ基板は、従来技術におけるソルダーレジスト層開孔に露出される電気接触パッドの代わりに、金属バンプがパッケージ基板のチップ実装側の表面上に突出するため、ソルダーレジスト層に関するプロセスを省略できるだけでなく、ソルダーレジスト層開孔の電気接触パッドの上に半田バンプを形成することも回避できるため、さらにコストダウンと歩留まりの向上を図ることができる。 30

【図面の簡単な説明】

【0035】

【図1A】従来のパッケージ基板及びその製造方法を模式的に示す断面図である。

【図1B】従来のパッケージ基板及びその製造方法を模式的に示す断面図である。

【図1C】従来のパッケージ基板及びその製造方法を模式的に示す断面図である。

【図1D】従来のパッケージ基板及びその製造方法を模式的に示す断面図である。

【図1E】従来のパッケージ基板及びその製造方法を模式的に示す断面図である。

【図1F】従来のパッケージ基板及びその製造方法を模式的に示す断面図である。

【図2A】本発明に係るパッケージ基板及びその製造方法の第1の実施例を模式的に示す断面図である。 40

【図2B】本発明に係るパッケージ基板及びその製造方法の第1の実施例を模式的に示す断面図である。

【図2C】本発明に係るパッケージ基板及びその製造方法の第1の実施例を模式的に示す断面図である。

【図2D】本発明に係るパッケージ基板及びその製造方法の第1の実施例を模式的に示す断面図である。

【図2E】本発明に係るパッケージ基板及びその製造方法の第1の実施例を模式的に示す断面図である。

【図2F】本発明に係るパッケージ基板及びその製造方法の第1の実施例を模式的に示す

10

20

30

40

50

断面図である。

【図3A】本発明に係るパッケージ基板及びその製造方法の第2の実施例を模式的に示す断面図である。

【図3B】本発明に係るパッケージ基板及びその製造方法の第2の実施例を模式的に示す断面図である。

【図3C】本発明に係るパッケージ基板及びその製造方法の第2の実施例を模式的に示す断面図である。

【図3D】本発明に係るパッケージ基板及びその製造方法の第2の実施例を模式的に示す断面図である。

【図4A】本発明に係るパッケージ基板及びその製造方法の第3の実施例を模式的に示す断面図である。 10

【図4B】本発明に係るパッケージ基板及びその製造方法の第3の実施例を模式的に示す断面図である。

【図4C】本発明に係るパッケージ基板及びその製造方法の第3の実施例を模式的に示す断面図である。

【図4D】本発明に係るパッケージ基板及びその製造方法の第3の実施例を模式的に示す断面図である。

【図4E】本発明に係るパッケージ基板及びその製造方法の第3の実施例を模式的に示す断面図である。 20

【図4F】本発明に係るパッケージ基板及びその製造方法の第3の実施例を模式的に示す断面図である。

【図4G】本発明に係るパッケージ基板及びその製造方法の第3の実施例を模式的に示す断面図である図4Eの他の実施態様である。

【図4H】本発明に係るパッケージ基板及びその製造方法の第3の実施例を模式的に示す断面図である図4Fの他の実施態様である。

【図5A】本発明に係るパッケージ基板及びその製造方法の第4の実施例を模式的に示す断面図である。

【図5B】本発明に係るパッケージ基板及びその製造方法の第4の実施例を模式的に示す断面図である。 30

【図5C】本発明に係るパッケージ基板及びその製造方法の第4の実施例を模式的に示す断面図である。

【図5D】本発明に係るパッケージ基板及びその製造方法の第4の実施例を模式的に示す断面図である。

【図5E】本発明に係るパッケージ基板及びその製造方法の第4の実施例を模式的に示す断面図である。

【図5F】本発明に係るパッケージ基板及びその製造方法の第4の実施例を模式的に示す断面図である。

【図5G】本発明に係るパッケージ基板及びその製造方法の第4の実施例を模式的に示す断面図である。

【発明を実施するための形態】 40

【0036】

以下、具体的な実施例によって本発明の実施形態を説明する。当業者は本明細書に記載の内容から本発明のその他の利点や効果を容易に理解することができる。

【0037】

又、本発明の全ての実施例において、各回路層の製造方法は煩雑で、その具体的な実施方法も従来の技術であるため、ここではその説明を省略する。

【0038】

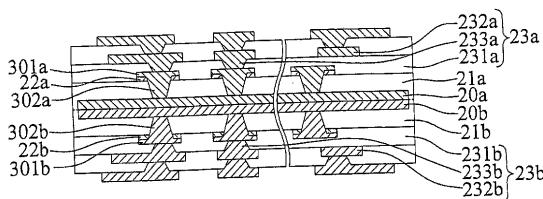

[第1の実施例]

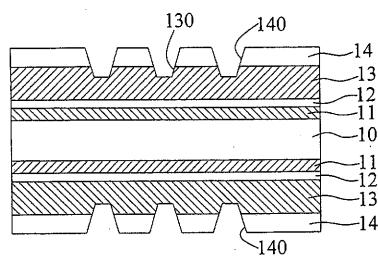

図2A乃至図2Fは、本発明に係るパッケージ基板及びその製造方法の第1の実施例を模式的に示す断面図である。 50

## 【0039】

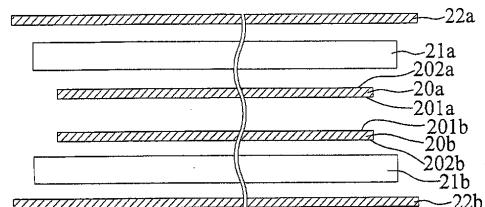

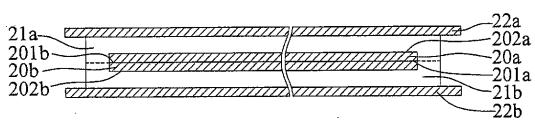

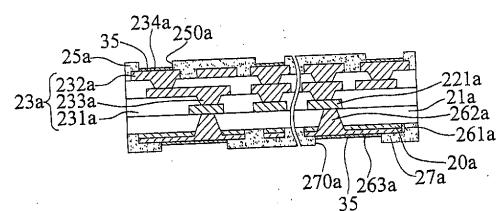

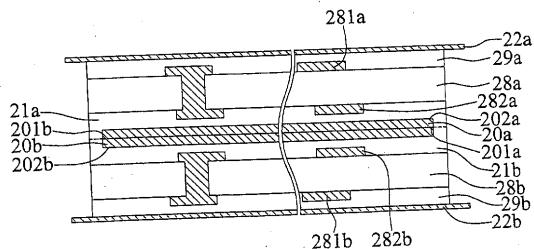

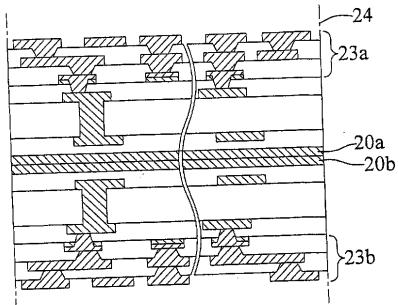

図2Aに示すように、それぞれ対向する第1の表面201a、201bと第2の表面202a、202bを有し第1の表面201a、201bで相互にラミネートされる二つの第1の金属層20a、20bと、この第1の金属層20a、20bの第2の表面202a、202bの上にそれぞれ設けられる二つの第1の補助誘電体層21a、21bと、この第1の補助誘電体層21a、21bが露出した表面の上にそれぞれ設けられる二つの第2の金属層22a、22bとを用意する。充分な剛性を提供するために、第2の金属層22a、22bの厚さを第1の金属層20a、20bより厚くする。

## 【0040】

本実施例において、第1の表面201a、201bは平滑面であり、第2の表面202a、202bは粗面である。10

## 【0041】

図2Bに示すように、これらの第1の金属層20a、20b、第1の補助誘電体層21a、21b、及び第2の金属層22a、22bを圧着することで、二つの第1の補助誘電体層21a、21bを一体に結合し最内部にある二つの第1の金属層20a、20bを覆うようにし、それにより、一つの基材を形成する。二つの第1の金属層20a、20bは第1の表面201a、201bで互いに接触する。

## 【0042】

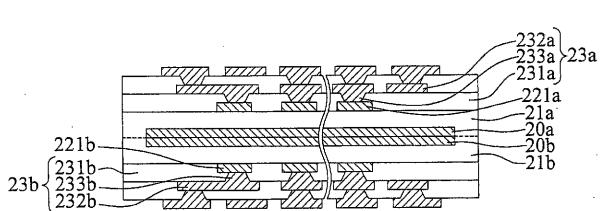

図2Cに示すように、第2の金属層22a、22bをパターニングすることにより内層回路層221a、221bを形成し、第1の補助誘電体層21a、21bと内層回路層221a、221bの上にビルドアップ構造23a、23bを形成する。ビルドアップ構造23a、23bは、少なくとも一つの第1の誘電体層231a、231bと、この第1の誘電体層231a、231bの上に形成される第1の回路層232a、232bと、第1の誘電体層231a、231bに形成され内層回路層221a、221bと第1の回路層232a、232bに電気的に接続される複数の導電ビア233a、233bとを含む。20

## 【0043】

図2Dに示すように、上述の全体構造のエッジに沿って切断し、且つ切断ライン24は第1の金属層20a、20bを通る。

## 【0044】

図2Eに示すように、二つの第1の金属層20a、20bは二つの第1の補助誘電体層21a、21bによって覆われて結合されるため、切断ライン24で切断した後、二つの第1の金属層20a、20bを互いに分離させることにより二つの基礎基板が得られる。以降の工程については基礎基板を用いて説明する。30

## 【0045】

図2Fに示すように、ビルドアップ構造23aの最外層の第1の回路層232aは複数の第1の電気接触パッド234aを有する。又、ビルドアップ構造23aの最外層の上には例えばソルダーレジスト層である第1の絶縁保護層25aを形成し、第1の絶縁保護層25aには各第1の電気接触パッド234aを露出させるための複数の第1の絶縁保護層開孔250aが形成される。又、第1の金属層20aをパターニングすることにより第1の補助誘電体層21aの上に第2の回路層261aを形成し、第1の補助誘電体層21aには内層回路層221aと第2の回路層261aに電気的に接続される複数の第2の導電ビア262aを形成する。第2の回路層261aはさらに複数の第2の電気接触パッド263aを有する。又、第1の補助誘電体層21aと第2の回路層261aの上に例えばソルダーレジスト層である第2の絶縁保護層27aを形成し、この第2の絶縁保護層27aには各第2の電気接触パッド263aを露出させるための複数の第2の絶縁保護層開孔270aを形成する。40

## 【0046】

又、第1の電気接触パッド234aと第2の電気接触パッド263aの上に表面処理層35を形成し、本発明に係るパッケージ基板を製作した。表面処理層35は、例えば、プリフラックス(OSP; organic solderability preserva50

t i v e s ) 、 無電解ニッケル / 無電解パラジウム / 置換金 ( E N E P I G ; E l e c t r o l e s s N i c k e l E l e c t r o l e s s P a l l a d i u m I m m e r s i o n G o l d ) 、 置換スズ ( I T 、 I m m e r s i o n T i n ) などであつてよい。又、各第 1 の電気接触パッド 234a は半導体チップ ( 図示せず ) を接続するためのものであり、各第 2 の電気接触パッド 263a はプリント配線基板 ( 図示なし ) を接続するためのものである。

#### 【 0047 】

又、本発明の実施例はコアレスのパッケージ基板の製作に用いられる基材を提供する。

図 2B に示すように、基材は、対向する第 1 の表面 201a、201b と第 2 の表面 202a、202b をそれぞれ有し、第 1 の表面 201a、201b で対向してラミネートされる二つの第 1 の金属層 20a、20b と、この第 1 の金属層 20a、20b の第 2 の表面 202a、202b の上にそれぞれ設けられる二つの第 1 の誘電体層 21a、21b と、この第 1 の補助誘電体層 21a、21b が露出した表面の上にそれぞれ設けられる二つの第 2 の金属層 22a、22b と、からなるラミネート体であり、二つの第 1 の補助誘電体層 21a、21b は一体に結合され、二つの第 1 の金属層 20a、20b を覆う。

#### 【 0048 】

上述の基材において、第 1 の表面 201a、201b は平滑面であり、第 2 の表面 202a、202b は粗面である。

#### 【 0049 】

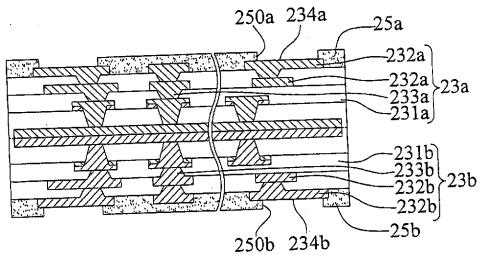

#### [ 第 2 の実施例 ]

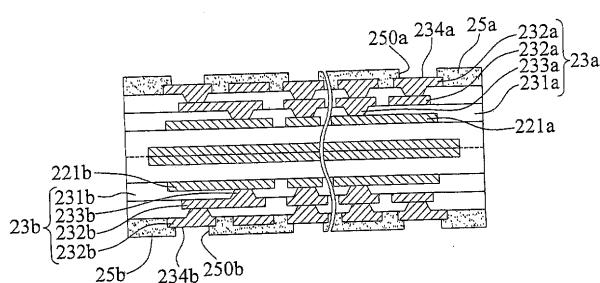

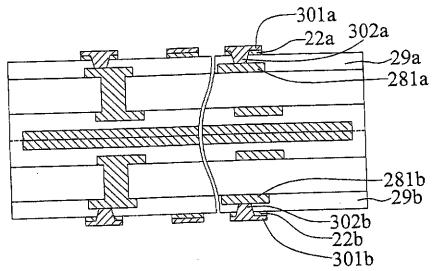

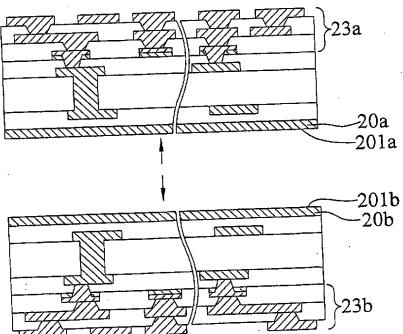

図 3A 乃至図 3D は、本発明に係るパッケージ基板及びその製造方法の第 2 の実施例を模式的に示す断面図である。

#### 【 0050 】

図 3A に示すように、図 2C の製造方法に続けて、ビルドアップ構造 23a、23b の最外層の第 1 の回路層 232a、232b は、さらに複数の第 1 の電気接触パッド 234a、234b を有する。又、ビルドアップ構造 23a、23b の最外層の上に例えばソルダーレジスト層である第 1 の絶縁保護層 25a、25b を形成し、第 1 の絶縁保護層 25a、25b には各第 1 の電気接触パッド 234a、234b を露出させるための複数の第 1 の絶縁保護層開孔 250a、250b を形成する。

#### 【 0051 】

図 3B に示すように、上述の全体構造のエッジに沿って切断し、且つ切断ライン 24 は第 1 の金属層 20a、20b を通す。

#### 【 0052 】

図 3C に示すように、二つの第 1 の金属層 20a、20b は二つの第 1 の補助誘電体層 21a、21b によって覆われて結合されるため、切断ライン 24 で切断した後、二つの第 1 の金属層 20a、20b を互いに分離されることにより、二つの基礎基板が得られる。以降の工程についてはその中の一つの基礎基板を用いて説明する。

#### 【 0053 】

図 3D に示すように、第 1 の金属層 20a を除去することにより、第 1 の補助誘電体層 21a を露出させる。第 1 の補助誘電体層 21a には内層回路層 221a の一部を露出させるための開孔 210a を形成する。露出させた内層回路層 221a は第 3 の電気接触パッド 2210 として機能する。第 1 の電気接触パッド 234a と第 3 の電気接触パッド 2210 の上に表面処理層 35 を形成する。これにより、本発明に係るパッケージ基板を製作した。又、各第 1 の電気的コンタクト 234a は半導体チップ ( 図示せず ) を接続するためのものであり、各第 3 の電気接触パッド 2210 はプリント配線基板 ( 図示せず ) を接続するためのものである。

#### 【 0054 】

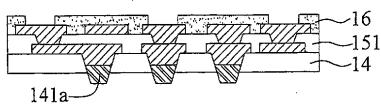

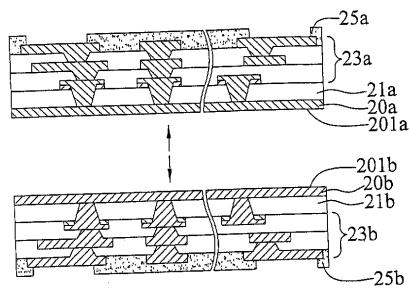

#### [ 第 3 の実施例 ]

図 4A 乃至図 4F は、本発明に係るパッケージ基板及びその製造方法の第 3 の実施例を模式的に示す断面図である。図 4G と図 4H は本実施例の他の実施態様を示す。

10

20

30

40

50

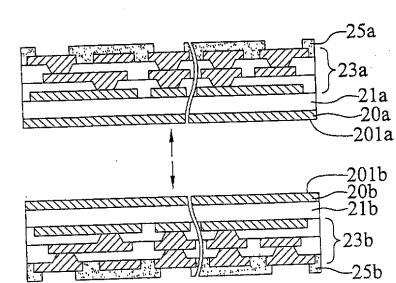

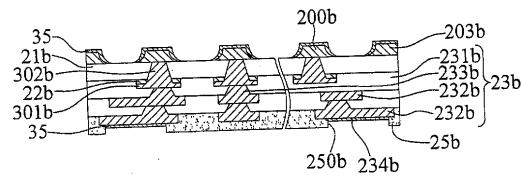

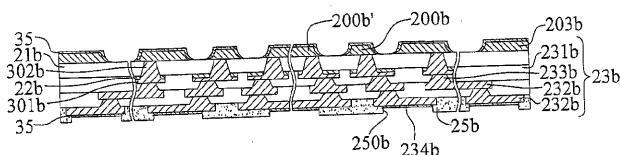

## 【0055】

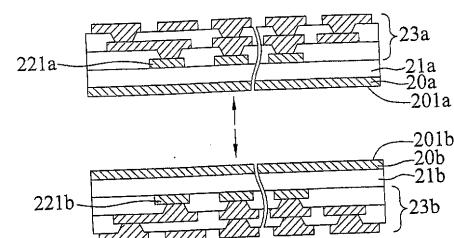

図4Aに示すように、図2Bの製造方法に続けて、第2の金属層22a、22bをパターニングすることにより、内層回路層301a、301bを形成する。第1の補助誘電体層21a、21bには内層回路層301a、301bと第1の金属層20a、20bに電気的に接続される複数の内層導電ビア302a、302bを形成する。第1の補助誘電体層21a、21bと内層回路層301a、301bの上にビルドアップ構造23a、23bを形成する。ビルドアップ構造23a、23bは、少なくとも一つの第1の誘電体層231a、231bと、この第1の誘電体層231a、231bの上に形成される第1の回路層232a、232bと、この第1の誘電体層231a、231bに形成され内装回路層301a、301bと第1の回路層232a、232bに電気的に接続される複数の第1の導電ビア233a、233bと、を含む。

10

## 【0056】

図4Bに示すように、ビルドアップ構造23a、23bの最外層の第1の回路層232a、232bは、さらに複数の第1の電気接触パッド234a、234bを有する。ビルドアップ構造23a、23bの最外層の上に例えばソルダーレジスト層である第1の絶縁保護層25a、25bを形成する。第1の絶縁保護層25a、25bには各第1の電気接触パッド234a、234bを露出させるための複数の第1の絶縁保護層開孔250a、250bをそれぞれ形成する。

## 【0057】

図4Cに示すように、上述の全体構造のエッジに沿って切断し、且つ切断ライン24は第1の金属層20a、20bを通す。

20

## 【0058】

図4Dに示すように、二つの第1の金属層20a、20bは二つの第1の補助誘電体層21a、21bによって覆われて結合するため、切断ライン24で切断した後、二つの第1の金属層20a、20bを互いに分離させることにより、二つの基礎基板が得られる。以降の工程についてはその中の一つの基礎基板を用いて説明する。

## 【0059】

図4Eに示すように、パターニングによって第1の金属層20bの一部を除去することにより、基礎基板の外周に金属支持フレーム203bを形成する。内層導電ビア302bの上には電気的に接続するための金属バンプ200bを形成する。金属支持フレーム203b、金属バンプ200b、及び第1の電気接触パッド234bの上に表面処理層35を形成する。これにより、本発明に係るパッケージ基板を製作した。

30

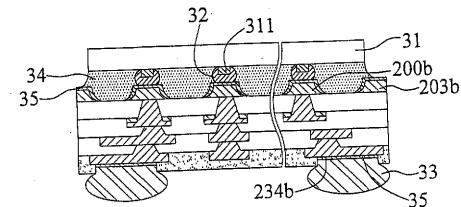

## 【0060】

図4Fに示すように、パッケージ基板の上に半導体チップ31を接着する。半導体チップ31の作用面には複数の電極パッド311を有する。これらの電極パッド311は半田バンプ32により各金属バンプ200bに電気的に接続される。半導体チップ31とパッケージ基板の間に充填材料34を形成する。各第1の電気接触パッド234aの上の表面処理層35の上に半田ボール(solder ball)33を形成する。

## 【0061】

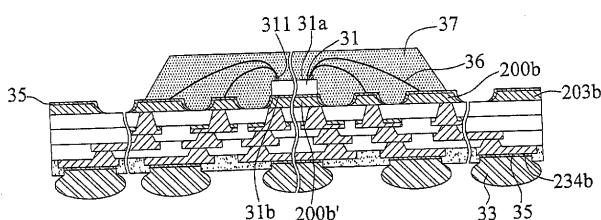

図4Gと図4Hは本実施例の他の態様を示す図である。金属バンプ200bはボンディングパッケージに用いられるボンディングパッドである。パターニングにより第1の金属層20bの一部を除去することにより、各内層導電ビア302bに接続される大面積のヒートシンク200b'を形成する。各ボンディングパッドはヒートシンク200b'の周囲にある。ヒートシンク200b'は半導体チップ31の非作用面31bに接着される。図4Hに示すように、ヒートシンク200b'は半導体チップ31の熱量を迅速に外部に伝えることで、半導体チップ31の温度の過剰な上昇を防ぐために用いられる。半導体チップ31の作用面31aは複数の電極パッド311を有する。これらの電極パッド311はボンディングワイヤ36を介してボンディングパッドとしての各金属バンプ200bに電気的に接続される。半導体チップ31とパッケージ基板の上には半導体チップ31、ボンディングワイヤ36、及び金属バンプ200bを覆うモールド化合物(molding

compound) 37 を形成する。各第1の電気接触パッド234aの上の表面処理層35の上に半田ボール33を形成する。

#### 【0062】

又、本発明の実施例はパッケージ基板を提供する。図4Eと図4Gに示すように、パッケージ基板は、第1の補助誘電体層21bと、金属バンプ200bと、ビルドアップ構造23と、例えばソルダーレジスト層である第1の絶縁保護層25bと、を含む。第1の補助誘電体層21bは、一方の表面に内層回路層301bが設けられる。第1の補助誘電体層21bには内層回路層301bに電気的に接続される複数の内層導電ビア302が設けられる。金属バンプ200bは第1の補助誘電体層21bの他方の表面に設けられ、各内層導電ビア302bに接続される。ビルドアップ構造23は第1の補助誘電体層21bと内層回路層301bの上に形成される。ビルドアップ構造23bは、少なくとも一つの第1の誘電体層231bと、この第1の誘電体層231bの上に設けられる第1の回路層232bと、第1の誘電体層231bに設けられ内層回路層301bと第1の回路層232bに電気的に接続される複数の第1の導電ビア233bと、を含む。ビルドアップ構造23bの最外層の第1の回路層232bはさらに複数の第1の電気接触パッド234bを有する。第1の絶縁保護層25bはビルドアップ構造23bの最外層に設けられる。第1の絶縁保護層25bには各第1の電気接触パッド234bを露出させるための複数の第1の絶縁保護層開孔250bが設けられる。内層導電ビア302bの内層回路層301bに電気的に接続した一端の孔径は内層導電ビア302bの金属バンプ200bに電気的に接続した他端の孔径より大きい。

10

20

30

40

50

#### 【0063】

図4Eに示すように、これらの金属バンプ200bはフリップチップパッケージに用いられるソルダーバンプパッドである。又は、図4Gに示すように、これらの金属バンプ200bはボンディングパッケージに用いられる。金属バンプ200bは大面積のヒートシンク200b'及びこのヒートシンク200b'の周囲にある複数のボンディングパッドを含む。

#### 【0064】

上述のパッケージ基板は、第1の補助誘電体層21bの上に設けられる金属支持フレーム203bをさらに含む。

#### 【0065】

図4Fは、図4Eに続けて、本発明を応用したパッケージ構造を示す。ここで、上述のパッケージ基板の上に半導体チップ31を接着する。半導体チップ31の作用面は複数の電極パッド311を有する。これらの電極パッド311は半田バンプ32により各金属バンプ200bに電気的に接続される。半導体チップ31とパッケージ基板の間に充填材料34を形成する。各第1の電気接触パッド234bの上の表面処理層35の上に半田ボール35を形成する。

#### 【0066】

図4Hは、図4Gに続けて、本発明を応用した他のパッケージ構造を示す。ここで、ヒートシンク200b'の上には作用面31aと非作用面31bを有する半導体チップ31を接着する。半導体チップ31の非作用面31bをヒートシンク200b'の上を接着する。半導体チップ31の作用面31aは複数の電極パッド311を有する。これらの電極パッド311はボンディングワイヤ36を介してボンディングパッドとしての各金属バンプ200bに電気的に接続される。半導体チップ31とパッケージ基板の上に半導体チップ31、ボンディングワイヤ36、及び金属バンプ200bを覆うためのモールド化合物37を形成する。各第1の電気接触パッド234bの上の表面処理層35の上に半田ボール33を形成する。

#### 【0067】

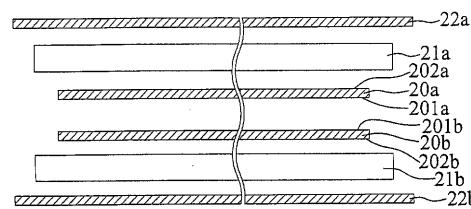

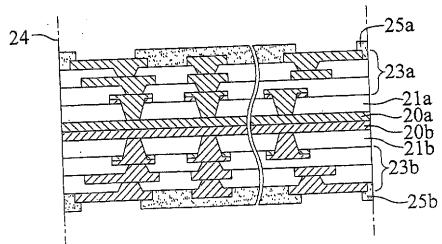

#### [第4の実施例]

図5A乃至図5Gは、本発明に係るパッケージ基板及びその製造方法の第4の実施例を模式的に示す断面図である。

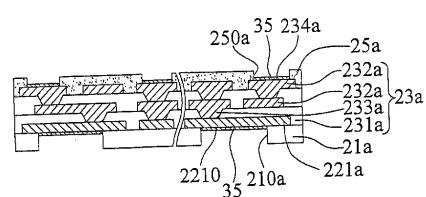

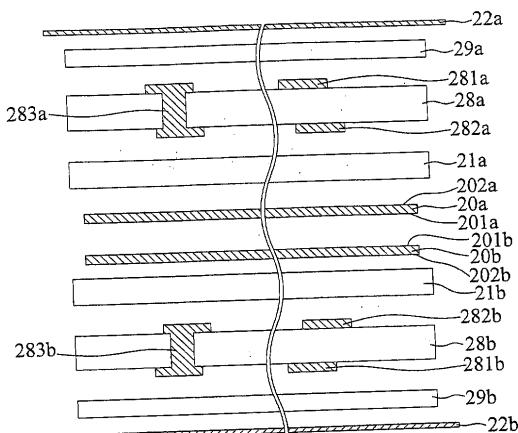

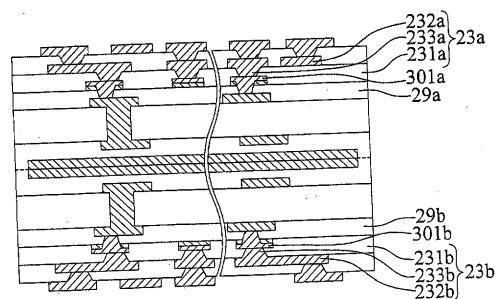

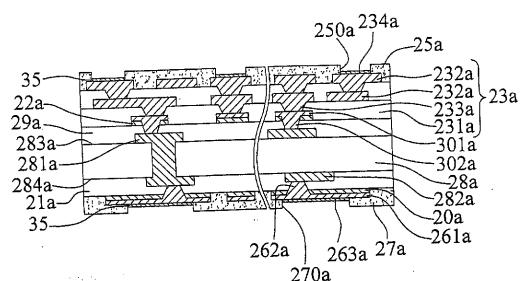

## 【0068】

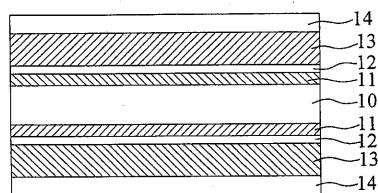

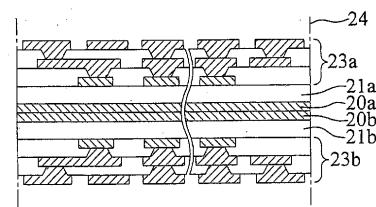

図5Aに示すように、それぞれ対向する第1の表面201a、201bと第2の表面202a、202bを有し、第1の表面201a、201bで相互にラミネートされる二つの第1の金属層20a、20bと、第1の金属層20a、20bの第2の表面202a、202bの上にそれぞれ設けられる二つの第1の補助誘電体層21a、21bと、第1の補助誘電体層21a、21bが露出した表面の上にそれぞれ設けられる二つのコア層28a、28bと、コア層28a、28bが露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層29a、29bと、第2の補助誘電体層29a、29bが露出した表面の上にそれぞれ設けられる二つの第2の金属層22a、22bと、を用意する。コア層28a、28bの対向する表面には複数の第1の電気接触パッド281a、281bと第2の電気接触パッド282a、282bをそれぞれ有する。又、コア層28a、28bには第1の電気接触パッド281a、281bと第2の電気接触パッド282a、282bに電気的に接続される導電ビア283a、283bを有する。

10

## 【0069】

本実施例において、第1の表面201a、201bは平滑面であり、第2の表面202a、202bは粗面である。

## 【0070】

図5Bに示すように、これらの第1の金属層20a、20b、第1の補助誘電体層21a、21b、コア層28a、28b、第2の補助誘電体層29a、29b、及び第2の金属層22a、22bを圧着することにより、二つの第1の補助誘電体層21a、21bを一体に結合し、最内部にある第1の金属層20a、20bを覆い、且つ二つの第1の金属層20a、20bが第1の表面で互いに接触し、第1の電気接触パッド281a、281bが第2の補助誘電体層29a、29bに嵌め込まれ、第2の電気接触パッド282a、282bが第1の補助誘電体層21a、21bに嵌め込まれる。これにより、一つの基材として形成される。

20

## 【0071】

図5Cに示すように、第2の金属層22a、22bをパターニングすることにより、内層回路層301a、301bを形成し、第2の補助誘電体層29a、29bには内層回路層301a、301bと第1の電気接触パッド281a、281bに電気的に接続される複数の内層導電ビア302a、302bを形成する。

30

## 【0072】

図5Dに示すように、第2の補助誘電体層29a、29bと内層回路層301a、301bの上にビルドアップ構造23a、23bを形成する。ビルドアップ構造23a、23bは、少なくとも一つの第1の誘電体層231a、231bと、この第1の誘電体層231a、231bの上に形成される第1の回路層232a、232bと、この第1の誘電体層231a、231bに形成され内層回路層301a、301bと第1の回路層232a、232bに電気的に接続される複数の第1の導電ビア233a、233bとを含む。

40

## 【0073】

図5Eに示すように、上述の全体構造のエッジに沿って切断し、且つ切断ライン24は第1の金属層20a、20bを通る。

40

## 【0074】

図5Fに示すように、上述のように、二つの第1の金属層20a、20bは二つの第1の補助誘電体層21a、21bによって覆われて結合されるため、切断ライン24で切断した後、二つの第1の金属層20a、20bを相互に分離させることにより、二つの基礎基板が得られる。以降の工程についてはその中の一つの基礎基板を用いて説明する。

50

## 【0075】

図5Gに示すように、ビルドアップ構造23aの最外層の第1の回路層232aはさらに複数の第1の電気接触パッド234aを有する。ビルドアップ構造23aの最外層の上には例えばソルダーレジスト層である第1の絶縁保護層25aを形成する。第1の絶縁保護層25aには各第1の電気接触パッド234aを露出させるための複数の第1の絶縁保

護層開孔 250a を形成する。

【0076】

第1の金属層 20a をさらにパターニングすることにより、第1の補助誘電体層 21a の上に第2の回路層 261a を形成し、第1の補助誘電体層 21a には第2の電気接触パッド 282a と第2の回路層 261a に電気的に接続される複数の第2の導電ビア 262a を形成する。第2の回路層 261a はさらに複数の第2の電気接触パッド 263a を有する。第1の補助誘電体層 21a の上には例えばソルダーレジスト層である第2の絶縁保護層 27a を形成する。第2の絶縁保護層 27a には各第2の電気接触パッド 263a を露出させるための複数の第2の絶縁保護層開孔 270a を形成する。

【0077】

又、第1の電気接触パッド 234a と第2の電気接触パッド 263a の上に表面処理層 35 を形成しても良い。これにより、本発明に係るパッケージ基板を製作した。又、第1の電気接触パッド 234a は半導体チップ(図示せず)を接着するためのものであり、第2の電気接触パッド 263a はプリント配線基板(図示せず)を接着するためのものである。

【0078】

又、本発明の実施例は薄コア層のパッケージ基板の製作に用いられる基材を提供する。図5Bに示すように、基材は、それぞれ対向する第1の表面 201a、201b と第2の表面 202a、202b を有し、第1の表面 201a、201b で相互にラミネートされる二つの第1の金属層 20a、20b と、この第1の金属層 20a、20b の第2の表面 202a、202b の上にそれぞれ設けられる二つの第1の誘電体層 21a、21b と、この第1の補助誘電体層 21a、21b が露出した表面の上にそれぞれ設けられる二つのコア層 28a、28b と、このコア層 28a、28b が露出した表面の上にそれぞれ設けられる二つの第2の補助誘電体層 29a、29b と、第2の補助誘電体層 29a、29b が露出した表面の上にそれぞれ設けられる第2の金属層 22a、22b と、からなるラミネート体である。又、二つの第1の金属層 20a、20b は、共に、対向する第1の表面 201a、201b と第2の表面 202a、202b を有する。第1の金属層 20a、20b は第1の表面 201a、201b で互いに接触する。二つの第1の補助誘電体層 21a、21b は一体に結合し、二つの第1の金属層 20a、20b を覆う。第1の補助誘電体層 21a、21b の表面の上にはコア層 28a、28b、第2の補助誘電体層 29a、29b、及び第2の金属層 22a、22b を順に圧着する。

【0079】

上述の基材において、第1の表面 201a、201b は平滑面であり、第2の表面 202a、202b は粗面である。

【0080】

本実施例は、薄コア層を有するパッケージ基板に適用される。薄コア層の厚さは例えば 0.2mm 以下であり、薄コア層の厚さが薄すぎたり、柔らかすぎたりすることによって、プロセスでの薬液、エアナイフの噴射圧、又は重力により基板が曲がり易く、輸送過程において基板全体が壊れたり引っかかったりし易くなり、ひいては生産ラインが止まるなどの問題が生じる恐れがあった。そのため、本発明の技術によれば、高剛性がある薄コア層を有するパッケージ基板を製作できる。

【0081】

上述のように、本発明に係るパッケージ基板は、先ず、二層の金属層をラミネートし、補助誘電体層で二層の金属層を覆い、次に、補助誘電体層の両側にビルトアップ構造をそれぞれ形成し、最後に二層の金属層の界面に沿って両側のビルトアップ構造を分離させることにより二つのパッケージ基板を形成するものである。本発明は最初に補助誘電体層によって中間層である二層の金属層を覆うため、ビルトアップ構造を形成する過程では分離せず、最後に二層の金属層の周囲を含む補助誘電体層部分を切断することにより、二層の金属層を円滑に分離させ、プロセスを簡略化することができる。又、中間層である二層の金属層をパターニングすることにより、回路層、金属バンプ、又は支持構造を形成する

10

20

30

40

50

ことができるため、従来技術のパッケージ基板の製造方法において、中間層である一時キャリアに離型層又は接着層を形成しながら最後に中間層である一時キャリアを捨てなければならぬために生じていたコストの無駄及びプロセスの複雑化の問題を回避することができる。従って、本発明は無駄を省き、プロセスとコストを低減することができる。

#### 【0082】

又、本発明の第3の実施例におけるパッケージ基板は、金属バンプがパッケージ基板のチップセット側の表面の上に突出するため、従来技術におけるソルダーレジスト層開孔に露出される電気接触パッドに取って代わり、ソルダーレジスト層に関するプロセスを省略するだけでなく、ソルダーレジスト層開孔の電気接触パッドの上に半田バンプを形成することも回避できるため、さらにコストダウンと歩留まりの向上を達成することができる。

10

#### 【0083】

上述した実施形態は本発明の原理や効果を説明するための例示に過ぎず、本発明の実施形態を限定するものではない。本発明の主旨を逸脱しない範囲において、当業者が本明細書に記載の実施形態に種々の修飾と変更が可能であることは言うまでもない。またそうした修飾や変更も本発明の特許請求の範囲に含まれる。そして、本発明の保護範囲は特許請求の範囲に記載される。

#### 【符号の説明】

#### 【0084】

|                           |           |    |

|---------------------------|-----------|----|

| 1 0                       | 載置基板      | 20 |

| 1 1                       | 薄膜金属層     |    |

| 1 2                       | 離型層       |    |

| 1 3                       | キャリア金属層   |    |

| 1 4、 2 3 1 a、 2 3 1 b     | 第1の誘電体層   |    |

| 1 5、 2 3 a、 2 3 b         | ビルドアップ構造  |    |

| 1 6                       | 絶縁保護層     |    |

| 2 0 a、 2 0 b              | 第1の金属層    |    |

| 2 1 a、 2 1 b              | 第1の補助誘電体層 |    |

| 2 2 a、 2 2 b              | 第2の金属層    |    |

| 2 4                       | 切断ライン     |    |

| 2 5 a、 2 5 b              | 第1の絶縁保護層  | 30 |

| 2 7 a                     | 第2の絶縁保護層  |    |

| 2 8 a、 2 8 b              | コア層       |    |

| 2 9 a、 2 9 b              | 第2の補助誘電体層 |    |

| 3 1                       | 半導体チップ    |    |

| 3 1 a                     | 作用面       |    |

| 3 1 b                     | 非作用面      |    |

| 3 2、 1 4 1 a              | 半田バンプ     |    |

| 3 3                       | 半田ボール     |    |

| 3 4                       | 充填材料      |    |

| 3 5                       | 表面処理層     | 40 |

| 3 6                       | ボンディングワイヤ |    |

| 3 7                       | モールド化合物   |    |

| 1 3 0                     | 凹部        |    |

| 1 4 0                     | ビア        |    |

| 1 4 1 b、 2 3 3 a、 2 3 3 b | 第1の導電ビア   |    |

| 1 4 2、 2 3 2 a、 2 3 2 b   | 第1の回路層    |    |

| 1 5 1                     | 第2の誘電体層   |    |

| 1 5 2、 2 6 1 a            | 第2の回路層    |    |

| 1 5 3、 2 6 2 a            | 第2の導電ビア   |    |

| 1 5 4                     | 電気接触パッド   | 50 |

160 絶縁保護層開孔

200b 金属バンプ

200b ヒートシンク

201a、201b 第1の表面

202a、202b 第2の表面

203b 金属支持フレーム

210a 開孔

221a、221b、301a、301b 内層回路層

234a、234b 第1の電気接触パッド

250a、250b 第1の絶縁保護層開孔

263a 第2の電気接触パッド

270a 第2の絶縁保護層開孔

281a、281b 第1の電気接触パッド

282a、282b 第2の電気接触パッド

283a、283b 導電ビア

302a、302b 内層導電ビア

311 電極パッド

2210 第3の電気接触パッド

10

【図1A】

【図1D】

【図1B】

【図1E】

【図1C】

【 図 1 F 】

【 図 2 A 】

【 図 2 B 】

【図2C】

【 図 2 D 】

【 図 2 E 】

【 図 2 F 】

( 3 A )

( 図 3 C )

【図3B】

【 図 3 D 】

【図4A】

【図 4 B】

【図 4 D】

【図 4 C】

【図 4 E】

【図 4 F】

【図 4 G】

【図 5 A】

【図 4 H】

【図 5 B】

【図 5 C】

【図 5 D】

【図 5 E】

【図 5 F】

【図 5 G】

---

フロントページの続き

F ターム(参考) 5E346 AA12 AA13 AA15 AA22 AA32 AA35 AA38 AA43 CC08 CC31

DD02 DD11 DD31 EE31 FF01 GG26 HH31 HH32 HH40