(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6644456号

(P6644456)

(45) 発行日 令和2年2月12日(2020.2.12)

(24) 登録日 令和2年1月10日(2020.1.10)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/338 | (2006.01) | HO1L 29/80 | H    |

| HO1L 29/778 | (2006.01) | HO1L 29/06 | 301F |

| HO1L 29/812 | (2006.01) | HO1L 29/78 | 301B |

| HO1L 29/06  | (2006.01) |            |      |

| HO1L 21/336 | (2006.01) |            |      |

請求項の数 25 外国語出願 (全 12 頁) 最終頁に続く

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2012-278136 (P2012-278136)  |

| (22) 出願日           | 平成24年12月20日 (2012.12.20)      |

| (65) 公開番号          | 特開2013-131758 (P2013-131758A) |

| (43) 公開日           | 平成25年7月4日 (2013.7.4)          |

| 審査請求日              | 平成27年12月18日 (2015.12.18)      |

| 審判番号               | 不服2018-7718 (P2018-7718/J1)   |

| 審判請求日              | 平成30年6月5日 (2018.6.5)          |

| (31) 優先権主張番号       | 13/333,843                    |

| (32) 優先日           | 平成23年12月21日 (2011.12.21)      |

| (33) 優先権主張国・地域又は機関 | 米国 (US)                       |

|           |                                                                                           |

|-----------|-------------------------------------------------------------------------------------------|

| (73) 特許権者 | 501315784<br>パワー・インテグレーションズ・インコーポレーテッド<br>アメリカ合衆国、95138・カリフォルニア州・サンホゼ・ヘリヤー・アベニュー<br>・5245 |

| (74) 代理人  | 110001195<br>特許業務法人深見特許事務所                                                                |

| (72) 発明者  | アレクセイ・コウディモフ<br>アメリカ合衆国、12180・ニュー・ヨーク州、トロイ、グラニット・レーン、3                                    |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体装置であって、

ソース電極とドレイン電極との間の半導体膜に活性領域を有するヘテロ構造電界効果トランジスタ(HFET)を備え、ゲート電極は前記活性領域の一部分の上にあり、前記活性領域の伝導チャネルを変調するように構成され、さらに、

前記ゲート電極の上の第1のパッシベーション膜と、

前記第1のパッシベーション膜上の第1のゲートフィールドプレートとを備え、前記第1のゲートフィールドプレートは前記ゲート電極の上方にあり、前記第1のゲートフィールドプレートは前記ゲート電極から分離しており、前記第1のパッシベーション膜は、前記ゲート電極と前記第1のゲートフィールドプレートとの間に配置され、さらに、

前記第1のゲートフィールドプレートの上の第2のパッシベーション膜と、

前記第2のパッシベーション膜上の第2のゲートフィールドプレートとを備え、前記第2のパッシベーション膜は、前記第1のゲートフィールドプレートと前記第2のゲートフィールドプレートとの間に配置され、さらに、

前記第2のゲートフィールドプレートの上のカプセル膜とを備え、前記カプセル膜は0.5 μm ~ 5 μmの厚みであり、さらに、

前記カプセル膜上の第1の金属パターンとを備え、

前記第1の金属パターンは、前記金属パターンから前記ソース電極へと伸びる1つ以上のバイアを介して前記ソース電極に電気的に接続される単層のシールドラップを含み、

10

20

前記シールドラップは、前記活性領域の大部分を被覆し、前記第1のゲートフィールドプレートおよび前記第2のゲートフィールドプレートは各々、前記ソース電極に近接した第1の端縁と、前記ドレイン電極に近接した第2の端縁とを含み、

前記シールドラップは、前記第1のゲートフィールドプレートおよび前記第2のゲートフィールドプレートの各々の前記第1の端縁および前記第2の端縁と重なる、半導体装置。

**【請求項2】**

前記第1の金属パターンにギャップが規定され、前記ギャップは、前記ドレイン電極に接続される前記第1の金属パターンの一部分から前記シールドラップを分離する、請求項1に記載の半導体装置。 10

**【請求項3】**

前記ドレイン電極から前記ソース電極までの距離は、前記ギャップの幅より5～6倍大きい、請求項2に記載の半導体装置。

**【請求項4】**

前記第1のゲートフィールドプレートは、前記第1のパッシベーション膜上の第2の金属パターンによって規定される、請求項1に記載の半導体装置。

**【請求項5】**

前記第2のゲートフィールドプレートは、前記第2のパッシベーション膜上の第3の金属パターンによって規定される、請求項4に記載の半導体装置。 20

**【請求項6】**

前記シールドラップは前記活性領域の少なくとも75%を被覆する、請求項1に記載の半導体装置。

**【請求項7】**

前記シールドラップは前記活性領域全体を被覆する、請求項6に記載の半導体装置。

**【請求項8】**

前記活性領域の少なくとも75%は、前記シールドラップまたは前記第2の金属パターンによって、個々にまたは組合せて被覆される、請求項4に記載の半導体装置。

**【請求項9】**

前記活性領域全体は、前記シールドラップまたは前記第2の金属パターンによって、個々にまたは組合せて被覆される、請求項8に記載の半導体装置。 30

**【請求項10】**

前記ゲート電極は複数のパッシベーション膜の上にある、請求項1に記載の半導体装置。

**【請求項11】**

ヘテロ構造電界効果トランジスタ(HFET)半導体装置であって、基板と、

前記基板上のバッファ層と、

前記バッファ層の活性領域にチャネルを作成するように構成された、前記バッファ層上の半導体膜と、 40

前記半導体膜に接触するソース電極と、

前記半導体膜に接触するドレイン電極とを備え、前記バッファ層内の前記活性領域は前記ソース電極と前記ドレイン電極との間にあり、さらに、

前記活性領域のチャネルを変調するように構成されたゲート電極と、

前記ゲート電極の上の第1のパッシベーション膜と、

前記第1のパッシベーション膜上の第1のゲートフィールドプレートとを備え、前記第1のゲートフィールドプレートは前記ゲート電極の上方にあり、前記第1のゲートフィールドプレートは前記ゲート電極から分離しており、前記第1のパッシベーション膜は、前記ゲート電極と前記第1のゲートフィールドプレートとの間に配置され、さらに、

前記第1のゲートフィールドプレートの上の第2のパッシベーション膜と、

50

前記第2のパッシベーション膜上の第2のゲートフィールドプレートとを備え、前記第2のパッシベーション膜は、前記第1のゲートフィールドプレートと前記第2のゲートフィールドプレートとの間に配置され、さらに、

前記第2のゲートフィールドプレートの上のカプセル膜とを備え、前記カプセル膜は0.5 μm ~ 5 μmの厚みであり、さらに、

単層のシールドラップから前記ソース電極へと伸びる1つ以上のバイアを介して前記ソース電極に電気的に接続された前記カプセル膜上の単層のシールドラップとを備え、

前記シールドラップは、前記活性領域の大部分を被覆し、

前記第1のゲートフィールドプレートおよび前記第2のゲートフィールドプレートは各々、前記ソース電極に近接した第1の端縁と、前記ドレイン電極に近接した第2の端縁とを含み、

前記シールドラップは、前記第1のゲートフィールドプレートおよび前記第2のゲートフィールドプレートの各々の前記第1の端縁および前記第2の端縁と重なる、H F E T半導体装置。

【請求項12】

前記シールドラップは前記活性領域の少なくとも75%を被覆する、請求項11に記載のH F E T半導体装置。

【請求項13】

前記シールドラップは、第1の金属パターンに形成され、

前記第1の金属パターンはさらに、前記カプセル膜上にドレイン接続を含み、前記ドレイン接続は、前記カプセル膜を通過するバイアを介して前記ドレイン電極と電気接觸する、請求項11に記載のH F E T半導体装置。

【請求項14】

前記シールドラップと前記ドレイン接続との間の前記第1の金属パターンにギャップが規定され、前記ギャップは誘電体で充填される、請求項13に記載のH F E T半導体装置。

【請求項15】

前記ギャップは窒化ケイ素で充填される、請求項14に記載のH F E T半導体装置。

【請求項16】

前記半導体装置はさらに、前記カプセル膜上にドレイン接続を含み、前記ドレイン接続は、前記カプセル膜を通過するバイアを介して前記ドレイン電極と電気接觸する、請求項11に記載のH F E T半導体装置。

【請求項17】

前記シールドラップと前記ドレイン接続との間にギャップが規定され、前記ギャップは誘電体で充填される、請求項16に記載のH F E T半導体装置。

【請求項18】

前記ギャップは窒化ケイ素で充填される、請求項17に記載のH F E T半導体装置。

【請求項19】

半導体装置であって、

ソース電極とドレイン電極との間の半導体膜に活性領域を有するヘテロ構造電界効果トランジスタ(H F E T)を備え、ゲート電極は前記活性領域の一部分の上にあり、前記活性領域の伝導チャネルを変調するように構成され、さらに、

前記ゲート電極の上の第1のパッシベーション膜と、

前記第1のパッシベーション膜上の第1のゲートフィールドプレートとを備え、前記第1のゲートフィールドプレートは前記ゲート電極の上方にあり、前記第1のゲートフィールドプレートは前記ゲート電極から分離しており、前記第1のパッシベーション膜は、前記ゲート電極と前記第1のゲートフィールドプレートとの間に配置され、さらに、

前記第1のゲートフィールドプレートの上の第2のパッシベーション膜と、

前記第2のパッシベーション膜上の第2のゲートフィールドプレートとを備え、前記第2のパッシベーション膜は、前記第1のゲートフィールドプレートと前記第2のゲートフ

10

20

30

40

50

イールドプレートとの間に配置され、さらに、

前記第2のゲートフィールドプレートの上のカプセル膜とを備え、前記カプセル膜は0.5 μm ~ 5 μmの厚みであり、さらに、

前記カプセル膜上の第1の金属パターンとを備え、

前記第1の金属パターンは、前記金属パターンから前記ドレイン電極へと伸びる1つ以上のバイアを介して前記ドレイン電極に電気的に接続される単層のシールドラップを含み、

前記シールドラップは、前記活性領域の大部分を被覆し、

前記第1のゲートフィールドプレートおよび前記第2のゲートフィールドプレートは各々、前記ソース電極に近接した第1の端縁と、前記ドレイン電極に近接した第2の端縁とを含み、

前記シールドラップは、前記第2のゲートフィールドプレートの前記第2の端縁と重なる、半導体装置。

【請求項20】

前記第1の金属パターンにギャップが規定され、前記ギャップは、前記ソース電極に接続される前記第1の金属パターンの一部分から前記シールドラップを分離する、請求項19に記載の半導体装置。

【請求項21】

前記第1の金属パターンはさらに、前記カプセル膜上にドレイン接続を含み、前記ドレイン接続は、前記カプセル膜を通過するバイアを介して前記ドレイン電極と電気接觸する、請求項19に記載の半導体装置。

【請求項22】

前記シールドラップと前記カプセル膜を通過するバイアを介して前記ソース電極と電気接觸するソース接続との間の前記第1の金属パターンにギャップが規定され、前記ギャップは誘電体で充填される、請求項21に記載の半導体装置。

【請求項23】

ヘテロ構造電界効果トランジスタ(HFET)半導体装置であって、

基板と、

前記基板上のバッファ層と、

前記バッファ層の活性領域にチャネルを作成するように構成された、前記バッファ層上の半導体膜と、

前記半導体膜に接觸するソース電極と、

前記半導体膜に接觸するドレイン電極とを備え、前記バッファ層内の前記活性領域は前記ソース電極と前記ドレイン電極との間にあり、さらに、

前記活性領域のチャネルを変調するように構成されたゲート電極と、

前記ゲート電極の上の第1のパッシベーション膜と、前記第1のパッシベーション膜上の第1のゲートフィールドプレートとを備え、前記第1のゲートフィールドプレートは前記ゲート電極の上方にあり、前記第1のゲートフィールドプレートは前記ゲート電極から分離しており、前記第1のパッシベーション膜は、前記ゲート電極と前記第1のゲートフィールドプレートとの間に配置され、さらに、

前記第1のゲートフィールドプレートの上の第2のパッシベーション膜と、

前記第2のパッシベーション膜上の第2のゲートフィールドプレートとを備え、前記第2のパッシベーション膜は、前記第1のゲートフィールドプレートと前記第2のゲートフィールドプレートとの間に配置され、さらに、

前記第2のゲートフィールドプレートの上のカプセル膜とを備え、前記カプセル膜は0.5 μm ~ 5 μmの厚みであり、さらに、

単層のシールドラップから前記ドレイン電極へと伸びる1つ以上のバイアを介して、前記ドレイン電極に電気的に接続された前記カプセル膜上の単層のシールドラップとを備え、

前記シールドラップは、前記活性領域の大部分を被覆し、

10

20

30

40

50

前記第1のゲートフィールドプレートおよび前記第2のゲートフィールドプレートは各々、前記ソース電極に近接した第1の端縁と、前記ドレイン電極に近接した第2の端縁とを含み、

前記シールドラップは、前記第2のゲートフィールドプレートの前記第2の端縁と重なる、H F E T半導体装置。

【請求項24】

前記シールドラップは、前記カプセル膜を通過するバイアを介して前記ドレイン電極と電気接觸し、

前記半導体装置はさらに、前記カプセル膜上にソース接続を含み、前記ソース接続は、前記カプセル膜を通過するバイアを介して前記ソース電極と電気接觸する、請求項23に記載のH F E T半導体装置。 10

【請求項25】

前記シールドラップと前記ソース接続との間にギャップが規定され、前記ギャップは誘電体で充填される、請求項24に記載のH F E T半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

発明の詳細な説明

1. 分野

本開示は、概してヘテロ構造電界効果トランジスタ(H F E T)に関し、より具体的には、本開示はH F E Tのためのシールドラップに関する。 20

【背景技術】

【0002】

2. 背景

携帯電話、携帯情報端末(P D A)、ラップトップなどといった多くの電気機器は、電力を利用して動作する。電力は一般に高圧交流(A C)としてコンセントを介して送られるため、典型的に電力変換装置と称される装置を利用して、高圧A C入力をエネルギー伝達要素によって正常な直流(D C)出力に変形することができる。スイッチドモード電力変換装置は、効率および寸法を向上させ、かつ今日の電子機器の多くの構成要素数を減少させるために一般に使用される。スイッチドモード電力変換装置は、閉位置(オン状態)と開位置(オフ状態)との間で切り替わって、電力変換装置の入力から出力にエネルギーを伝達する電源スイッチを使用し得る。典型的に、電源スイッチは、A C入力電圧より実質的に大きい電圧に抵抗するために必要とされる高圧装置である。 30

【0003】

スイッチドモード電力変換装置において使用される高圧電界効果トランジスタ(F E T)の一種は、高電子移動度トランジスタ(H E M T)とも称されるH F E Tである。H F E Tは、電力変換装置などの高圧出力電子機器のためのスイッチング装置においてスイッチとして使用され得る。ある用途では、バンドギャップが高くなると高い温度での性能が向上し得るため、広バンドギャップ半導体をベースとするH F E Tが有用であり得る。他の材料も使用され得るが、高圧H F E Tにおいて使用される広バンドギャップ半導体の例は、炭化けい素(S i C)、窒化ガリウム(G a N)、およびダイヤモンドといった材料である。 40

【0004】

本発明のいくつかの実施例の様々な局面、特徴、および利点は、添付の図面と合わせて示される以下のより特定的な説明から、より明白となるであろう。

【0005】

限定的でなく包括的でない本発明の実施例を添付の図面を参照して説明する。特に明記しない限り、同じ参照数字は様々な図にわたって同じ部分を指す。

【図面の簡単な説明】

【0006】

【図1】本発明の実施例に係るシールドラップを備えた典型的なH F E Tを例示する図である。

【図2】シールドラップを備えた別の典型的なH F E Tを例示する図である。

【図3】本発明の実施例に係るシールドラップを備えたH F E Tを作成するための典型的なプロセスのためのフローチャートを例示する図である。

【図4】本発明の実施例に係るシールドラップのない典型的なH F E Tについての電気的な結果を例示する図である。

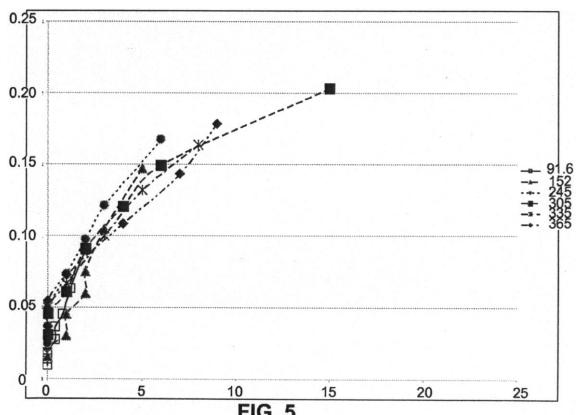

【図5】本発明の実施例に係るシールドラップを備えた典型的なH F E Tについての電気的な結果を例示する図である。

【発明を実施するための形態】

10

【0 0 0 7】

#### 詳細な説明

以下の説明では、本発明についての完全な理解を提供するために多数の具体的な詳細について述べる。しかし、当業者にとっては、本発明を実行するのに具体的な詳細を採用する必要はないことが明白であろう。他の例では、本発明を不明瞭にしないようにするために、周知の材料または方法については詳細に説明されていない。

【0 0 0 8】

20

本明細書全体にわたる「一実施例」、「実施例」、「一例」または「例」との言及は、実施例または例に関して説明される特定の特徴、構造または特性が本発明の少なくとも一実施例に含まれることを意味する。したがって、本明細書全体にわたる様々な箇所における「一実施例」、「実施例」、「一例」または「例」は、必ずしもすべて同じ実施例または例を指すとは限らない。さらに、特定の特徴、構造または特性は、1つ以上の実施例または例におけるいずれかの好適な組合せおよび／またはサブコンビネーションで組み合わせられ得る。特定の特徴、構造または特性は、説明される機能性をもたらす集積回路、電子回路、組合せ論理回路、または他の好適な構成要素に含まれ得る。また、ここに示される図は当業者への説明のためのものであり、図面は必ずしも縮尺通りではないと理解される。

【0 0 0 9】

30

以下の説明では、典型的なF E Tは説明の目的で使用される。典型的なF E Tは、ゲート誘電体を有するF E TにかかわらずH F E Tと称される。この点で、典型的なF E Tを金属絶縁体半導体F E T（M I S F E T）と呼ぶこともできる。代替的に、典型的なF E TをH E M Tと呼ぶこともできる。しかし、説明を簡単にするために、H F E Tという用語を使用する。以下のこれらの用語の使用は、請求項に対する限定ではないと理解されるべきである。

【0 0 1 0】

本願で使用される限りにおいて、電気接続はオーミック接続である。たとえば、金属を介してのみ互いに接触する2つの金属パターンが電気的に接続される。対照的に、ドレインおよびソース電極は電気的に接続されない。なぜなら、これらの電極間のいずれの接続も、半導体のチャネルを介し、ゲート電極によって制御されるためである。同様に、ゲート誘電体を用いてゲート電極を下の半導体から絶縁すると、ゲート電極は、ゲート電極の下の半導体に電気的に接続されない。

40

【0 0 1 1】

高圧スイッチであるH F E Tの動作は、数百ボルトの電圧の超高速（サブマイクロ秒）スイッチングを伴う。そのような高速スイッチングは、装置の活性領域の付近と遠方との両方において大きな電磁界を生成し得る。これらの電界の周波数は、H F E Tの動作周波数付近（たとえばk H z～M H zの範囲）であり得る。しかし、H F E Tのチャネルは、チャネル不均一性によって周波数がはるかに高い局所的な電磁界を経験し得る。これらの高い周波数の局所的な電界は、接点、パッドおよびメタライゼーションと相互作用して、G H z～T H zの範囲で放射し得る。これらの大きな電界のうちいずれかが有害である場合があり、かつ／または周囲の回路および付近の電子装置にまで干渉を引き起こす場合が

50

ある。電界は、電界に露出したパッケージング材料、相互接続、および誘電体層の長期劣化および寿命の低下にも繋がり得る。

#### 【0012】

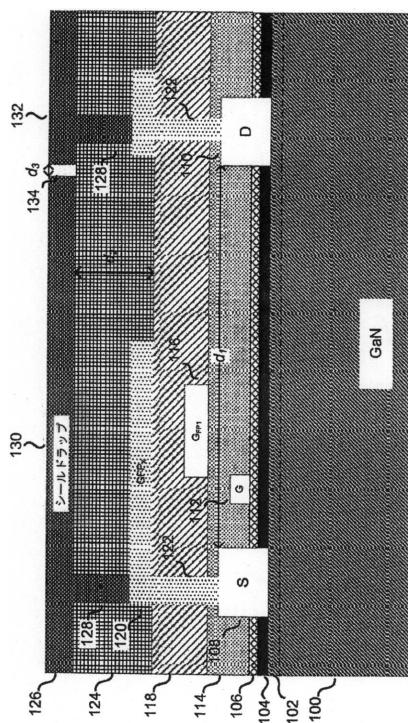

図1は、本発明の実施例に係る典型的なシールドラップを用いた典型的なH F E Tを含む典型的な半導体装置を例示する。典型的なH F E Tは、基板(図1では簡単にするために省略されている)上に形成される。基板上には、バッファ層100がGaN膜として形成される。別の半導体膜102をバッファ層100の表面上に配置して、バッファ層100を備えたヘテロ構造を形成する。半導体膜102は、バッファ層100の頂部部分に伝導チャネルを生成する。たとえば、半導体膜102はAlGaNであり得る。他の典型的なF E T(図示せず、非ヘテロ構造F E Tを含む)では、半導体膜102は他の材料であり得るか、または省略され得るか、またはバッファ層100と同じ材料であり得る。同様に、他の典型的なF E T(図示せず)では、バッファ層100は、シリコン、ガリウム砒素(GaAs)、りん化インジウム(InP)、SiCなどといった他の材料からなり得る。ある場合には、バッファ層100および/または半導体膜102は複数膜の層からなる複合膜であり得る。

#### 【0013】

パッシベーション膜104が半導体膜102上に形成される。パッシベーション膜104は、ゲート誘電体の一部分を形成し得、高品質の絶縁材料として成長し得る。たとえば、パッシベーション膜104は、Al<sub>2</sub>O<sub>3</sub>、酸化ジルコニウム(ZrO<sub>2</sub>)、窒化アルミニウム(AlN)、酸化ハフニウム(HfO<sub>2</sub>)、二酸化けい素(SiO<sub>2</sub>)、窒化ケイ素(Si<sub>3</sub>N<sub>4</sub>)などの材料、または他の好適なゲート誘電体材料からなり得る。パッシベーション膜104は半導体膜102と高品質界面も形成し得、これは信頼性を向上させ電子の表面移動度を増加させ得、それにより装置性能を向上させる。

#### 【0014】

パッシベーション膜104は、低欠陥/低トラップ密度膜として形成され得、ホットキャリアがパッシベーション膜104に注入されかつ/または捕獲され得る確率を最小化することによって、ゲート誘電体の信頼性の向上をもたらす。たとえば、原子層堆積(ALD)を用いて、パッシベーション膜104として機能する高品質の材料を形成し得る。

#### 【0015】

パッシベーション膜106がパッシベーション膜104上に形成される。パッシベーション膜104のように、パッシベーション膜106もゲート誘電体の一部分を形成し得る。パッシベーション膜106は、パッシベーション膜104と同様のやり方で同様の材料によって形成され得る。たとえば、現場でのALDプロセスを用いて、同じALDツールでパッシベーション膜104および106の両方を、ツールの外部環境に基板を露出させることなく形成し得る。パッシベーション膜104および106の組み合わせた厚さは、たとえば5nm~20nmであり得る。これらの膜を形成するためのプロセスについてのより詳細な説明については、2011年12月12日に提出され、本願と同じ譲受人に譲渡され、あらゆる目的でその全体がここに引用により援用される「現場で成長されるゲート誘電体およびフィールドプレート誘電体(IN SITU GROWN GATE DIELECTRIC AND FIELD PLATE DIELECTRIC)」と題された米国特許出願番号第13/323,672号を参照のこと。本発明の実施例に係るシールドラップは、本願で開示されるF E Tに均等に広がり得る。他の典型的なF E Tでは、単一のパッシベーション膜(たとえばパッシベーション膜104)のみが使用される。

#### 【0016】

ソース電極108およびドレイン電極110が半導体膜102上に形成される。他の典型的なH F E Tでは、これらの電極は半導体膜102の下のバッファ層100とも接触し得る。ソース電極108とドレイン電極110との間の領域は、伝導チャネルが生じ得、かつパッシベーション膜106の上に形成されるゲート電極112によって制御され得る活性領域を形成する。他の典型的なF E Tでは、ゲート電極112は半導体膜102上に直接形成され得る。ゲート電極112は、活性領域の伝導チャネルを変調するように構成

10

20

30

40

50

される。言いかえれば、ゲート電極 112 への電圧を変化させることによって、活性領域のチャネルを通る伝導が制御され得る。これらの電極のための金属積層は、たとえば Al、Ni、Ti、TiW、TiN、TiAu、TiAlMoAu、TiAlNiAu、TiAlPtAu 等を含み得る。金属以外に他の導電材料も使用され得る。

#### 【0017】

パッシベーション膜 114 がソース電極 108、ドレイン電極 110 およびゲート電極 112 上に形成され、電極、1つ以上のフィールドプレート（使用される場合）、およびシールドラップへの相互接続の形成をもたらす。パッシベーション膜 114 は、窒化ケイ素、酸化ケイ素などといった絶縁材料からなり得る。ある場合には、パッシベーション膜 114 は複数層の異なる膜の複合膜であり得る。

10

#### 【0018】

ゲートフィールドプレート 116 がパッシベーション膜 114 の上に形成される。ゲートフィールドプレート 116 は、ドレイン電極 110 に最も近いゲート電極 116 の端縁上に電界を広げるように設計される。H F E T のこの領域において電界を広げることは、ゲート誘電体（パッシベーション層 104 および 106）にキャリアが注入され得る確率を低下させ、H F E T の信頼性を向上させるのを助け得る。他の典型的な H F E T では、ゲートフィールドプレートは省略され得る。ゲートフィールドプレート 116 は、ソース、ドレインまたはゲート電極と同様の材料からなり得る。

#### 【0019】

パッシベーション膜 118 がゲートフィールドプレート 116 上に形成される。金属パターン 120 がパッシベーション膜 118 上に形成され得る。金属パターン 120 は、電極に電気接觸するために別のゲートフィールドプレートおよびバイア 122 を含み得る。他の典型的な H F E T では、ゲートフィールドプレートを1つだけ使用してもよいし、3つ以上のゲートフィールドプレートを使用してもよい。

20

#### 【0020】

カプセル膜 124 が金属パターン 120 上に形成される。カプセル膜 124 は、カプセル膜 124 の欠陥 / トラップ密度が、半導体膜 102 により近いパッシベーション膜ほど重要ではない点で、パッシベーション膜 104, 106, 114 および 118 とは異なり得る。これにより、パッシベーション膜には好適ではないかもしれない材料でカプセル膜 124 を作製することが可能となる。しかし、カプセル膜 124 は、パッシベーション膜のうち1つ以上に使用されるのと同じ材料で作製され得る。たとえば、カプセル膜 124 は、酸化ケイ素、窒化ケイ素、ガラス（たとえばフリット・オン・ガラス）、有機誘電体（たとえばポリイミドまたはベンゾシクロブテンベースの誘電体）等であり得る。ある場合には、カプセル膜 124 は、複数膜の層からなる複合膜であり得る。カプセル膜 124 は、たとえば約 0.5 μm ~ 5 μm 厚さであり得る。一例では、カプセル膜 124 は 1 μm 厚さである。

30

#### 【0021】

金属パターン 126 がカプセル膜 124 上に形成される。金属パターン 126 は、シールドラップ 130、ドレイン接続 132 およびバイア 128 を含む。ドレイン接続 132 は、1つ以上のバイア 128 を介してドレイン電極 110 と電気接觸する。シールドラップ 130 は、1つ以上のバイア 128 を介してソース電極 108 と電気接觸する。上記のフィールドプレートとは対照的に、シールドラップ 130 は、電界を広げるように設計されなくてもよい。代わりに、シールドラップ 130 は、H F E T によって生成される電磁放射を含み得る。言いかえれば、シールドラップ 130 は、シールドラップ 130 が H F E T をできるだけ被覆する点で、ゲートフィールドプレートとは異なる。したがって、シールドラップ 130 の形状は、ドレイン電極 110 に最も近いゲート電極 112 の端縁上に電界を広げるように最適化されなくてもよい。一例では、シールドラップ 130 は、ソース電極 108 とドレイン電極 110 との間の直流電気経路を作成することなく、H F E T の表面をできるだけ覆うように延在し得る。H F E T のすべてまたは一部分を覆うことによって、シールドラップ 130 は、H F E T の外部で伝達された電磁放射と、H F E T

40

50

から反射し返される電磁放射とを減少させ得る。シールドラップ 130 とシールドラップ 130 の下の金属および半導体層との間の容量結合を減少させるために、カプセル化層 124 の厚さ  $d_2$  を増大させててもよい。

【0022】

金属パターン 126 に規定されるギャップ 134 は、シールドラップ 130 が高圧でドレイン接続 132 に短絡しないように十分広い幅  $d_3$  で設計され得る。たとえば、ソース電極 108 とドレイン電極 110 との間の活性領域は、H F E T のスイッチング電圧 100 V 当たり約 1  $\mu$ m である幅  $d_1$  を有し得る（たとえば 500 V の H F E T の  $d_1$  は約 5  $\mu$ m となる）。対照的に、（スイッチング電圧の 500 ~ 600 V 当たり約 1  $\mu$ m の SiN のみを必要とし得る）窒化ケイ素（SiN）がギャップ 134 に充填される場合、ギャップ 134 の幅  $d_3$  は  $d_1$  の 5 ~ 6 分の 1 であり得る（たとえば 500 V の H F E T の  $d_3$  は約 1  $\mu$ m となる）。ある場合には、 $d_3$  は  $d_1$  の 15 ~ 20 % である。金属パターン 126 は、たとえば約 0.7  $\mu$ m ~ 2  $\mu$ m 厚さであり得る。

【0023】

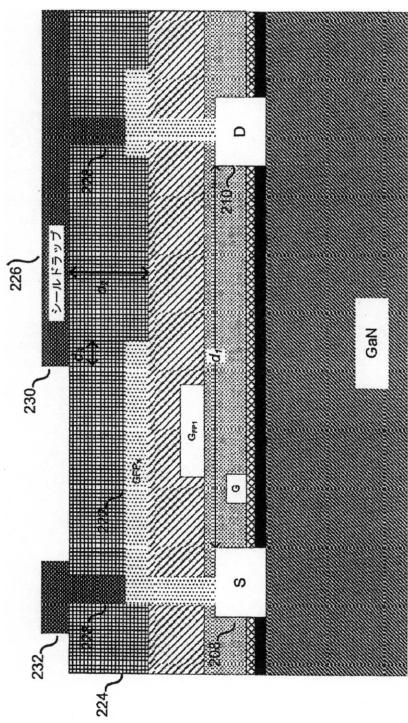

図 2 は、本発明の実施例に係る典型的なシールドラップを使用した典型的な H F E T を含む別の典型的な半導体装置を例示する。図示されるように、金属パターン 226 がカプセル膜 224 上に形成される。金属パターン 226 は、シールドラップ 230、ソース接続 232 およびバイア 228 を含む。ソース接続 232 は、1 つ以上のバイア 228 を介してドレイン電極 210 と電気接觸する。シールドラップ 230 は、1 つ以上のバイア 228 を介してソース電極 208 と電気接觸する。図示されるように、シールドプレート 230 は、ゲートフィールドプレート 222 を越えて距離  $d_3$  延在し得る。一例では、ゲートフィールドプレート 222 は、シールドラップ 230 の一部分として機能して、装置表面の適用範囲を最大化し得る。

【0024】

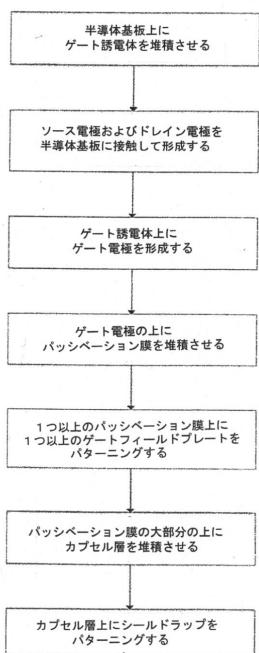

図 3 は、本発明の実施例に係る典型的なシールドラップを有する典型的な H F E T を作製するための典型的なプロセスのためのフローチャートを例示する。様々な処理工程がフローチャートに含まれるが、本発明の実施例に係る典型的なシールドラップを備えた典型的な H F E T を製作するためには他の処理工程が必要とされ得ると理解されるべきである。他の典型的なプロセスでは、図 3 に示された工程を異なる順に行なってもよいし、工程を組み合わせてもよい。たとえば、ゲート電極およびゲートフィールドプレートが同時に形成され得る。さらに他の典型的なプロセスでは、いくつかの工程を省略してもよい。たとえば、ゲートフィールドプレートのない H F E T が所望の場合、典型的なプロセスは、ゲートフィールドプレートの形成を省略することができる。

【0025】

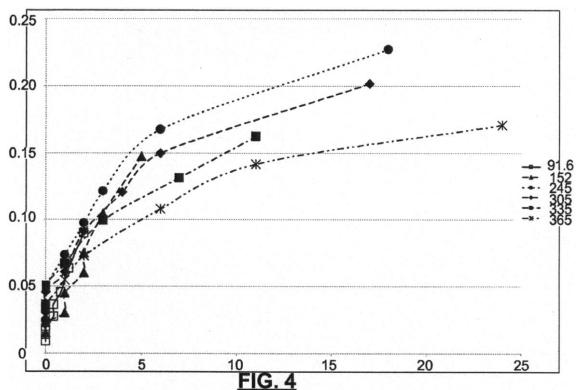

図 4 および図 5 は、本発明の実施例に係るシールドラップのない H F E T (図 4) およびシールドラップのある典型的な H F E T (図 5) の実験結果を図示する。特に、図 4 および図 5 は、シールドラップがある H F E T およびシールドラップがない H F E T の I-V 特性を図示する。オフ状態 (ゲートバイアス = -10 V) とオン状態 (ゲートバイアス = 0 V) との間で H E M T をパルス化することによって結果が得られた。ドレインバイアスは、図 4 および図 5 の表示を示す様々な値に設定された。パルス化は、10 ミリ秒の期間および 0.1 % の負荷サイクルで行なわれた。総ゲート幅は約 450  $\mu$ m であった。図 4 および図 5 の x 軸は、y 軸上の瞬間ドレイン電流での瞬間ドレイン電圧である。

【0026】

(シールドラップのない H F E T に対応する) 図 4 の結果を (本発明の実施例に係るシールドラップを備えた H F E T に対応する) 図 5 の結果と比較することにより明らかにように、瞬間ドレイン電流の分布は、シールドラップを備えた H F E T の方がより制限される。より制限された分布は、ドレイン電圧が高くなると劣化が少なく性能が向上する H F E T に相当する。具体的には、図 4 は、シールドラップのない典型的な H F E T について 335 V 未満でドレイン電圧に歪みがないことを示し、図 5 は、本発明の実施例に係るシールドラップを備えた典型的な H F E T について 365 V 未満でドレイン電圧に歪みがな

いことを示している。

【0027】

要約書に記載されるものを含む、例示した本発明の例についての上記の説明は、包括的なものまたは開示されている形態そのものへの限定とは意図されていない。発明の特定の実施例および例が説明の目的でここに説明されるが、本発明のより広い精神および範囲から逸脱することなく様々な等価な修正が可能である。実際は、厚さ、材料、処理動作等の特定の例は説明の目的で示されており、他の厚さ、材料、処理動作等も本発明の教示に係る他の実施例、例およびプロセスにおいて採用され得ると解釈される。

【0028】

これらの修正は、上記の詳細な説明に照らして発明の例に合わせて行うことができる。添付の請求項において使用される用語は、明細書および請求項に開示されている特定の実施例に発明を限定するものと解釈されるべきではない。むしろ当該範囲は、請求項解釈の既定の原理に従って解釈されるべき以下の請求項によって全体的に判断されるべきである。本明細書および図は、したがって限定的ではなく例示的なものと見なされるべきである。

10

【符号の説明】

【0029】

100 パッファ層、102 半導体膜、104, 106, 114, 118 パッシブーション膜、108 ソース電極、110 ドレイン電極、112 ゲート電極、116 ゲートフィールドプレート、120, 126 金属パターン、122, 128 バイア、124 カプセル膜、130 シールドラップ、132 ドレイン接続、134 ギャップ、 $d_1$ ,  $d_3$  幅、 $d_2$  厚さ。

20

【図1】

FIG.1

【図2】

FIG.2

【図3】

300

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/78 (2006.01)

合議体

審判長 恩田 春香

審判官 加藤 浩一

審判官 小田 浩

(56)参考文献 特表2007-537594 (JP, A)

特開平5-152291 (JP, A)

特開平8-330519 (JP, A)

特開平5-55380 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L21/336-21/338

H01L27/095-27/098

H01L29/775-29/778

H01L29/78

H01L29/80-29/812

H01L27/04