(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5759581号

(P5759581)

(45) 発行日 平成27年8月5日(2015.8.5)

(24) 登録日 平成27年6月12日(2015.6.12)

(51) Int.Cl.

H03M 1/12 (2006.01)

H03F 3/70 (2006.01)

F 1

H03M 1/12

H03F 3/70

A

請求項の数 24 外国語出願 (全 26 頁)

(21) 出願番号 特願2014-45581 (P2014-45581)

(22) 出願日 平成26年3月7日 (2014.3.7)

(65) 公開番号 特開2014-176096 (P2014-176096A)

(43) 公開日 平成26年9月22日 (2014.9.22)

審査請求日 平成26年10月24日 (2014.10.24)

(31) 優先権主張番号 61/774,432

(32) 優先日 平成25年3月7日 (2013.3.7)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 13/975,291

(32) 優先日 平成25年8月24日 (2013.8.24)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 501144003

アナログ・デバイシズ・インコーポレーテッド

アメリカ合衆国マサチューセッツ州ノーウッド, ワン・テクノロジー・ウェイ (番地なし)

(74) 代理人 100102842

弁理士 葛和 清司

(72) 発明者 シンガー, ローレンス エー.

アメリカ合衆国 マサチューセッツ州 O

1984、ウェナム、ジュニパー ストリート 19

最終頁に続く

(54) 【発明の名称】サンプリング回路のタイミング不整合を減少させるための装置および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

多重アナログ信号チャネルのサンプリングに対するタイミング不整合を減少させるために互いに対しても同期された複数のサンプリングクロックを生成するための回路であって、複数の入力信号を受信し、かつ前記複数のサンプリングクロックのそれぞれのサンプリングクロックを第1の出力状態に選択的に設定するように構成される第1の回路であって、前記複数のサンプリングクロックの選択されるサンプリングクロックが、前記複数の入力信号の選択される入力が第1の入力状態に設定されるときに、前記第1の出力状態に設定される、前記第1の回路と、

入力クロック信号を受信し、かつ前記複数のサンプリングクロックのそれを、共通路を通して第2の出力状態に遷移させるように構成される第2の回路であって、前記選択されるサンプリングクロックが、前記入力クロック信号の第1のクロック状態から第2のクロック状態への遷移に応答して、前記共通路を通して前記第1の出力状態から前記第2の出力状態に遷移される、前記第2の回路と、を含む、前記回路。

## 【請求項 2】

サンプリングクロックのそれぞれの第1の出力状態が、電圧レベルを有し、第1の回路が、サンプリングクロックのそれぞれの前記第1の出力状態の前記電圧レベルを上昇させるように構成される少なくとも1つの昇圧回路を含む、請求項1に記載の回路。

## 【請求項 3】

前記複数のサンプリングクロックを受信する複数のサンプリングチャネルを含み、前記

10

20

選択されるサンプリングクロックが前記第1の出力状態から前記第2の出力状態に遷移されるときに、前記複数のチャネルの選択されるチャネルからサンプルを生成するように構成される、サンプリング回路をさらに含む、請求項1に記載の回路。

**【請求項4】**

前記複数のサンプリングクロックのそれぞれの前記第1の出力状態が電圧レベルを有し、前記第1の回路が、前記サンプリング回路の少なくとも1つのスイッチをオン状態に駆動するために、前記複数のサンプリングクロックのそれぞれの前記第1の出力状態の前記電圧レベルを上昇させるように構成される、少なくとも1つの昇圧回路を含む、請求項3に記載の回路。

**【請求項5】**

前記選択される入力が、前記第1および第2の回路で受信される選択される入力を含み、前記第2の回路が、前記複数のサンプリングクロックのうちの1つにそれぞれ対応し、かつ前記複数の入力信号の選択される入力が前記第1の入力状態に設定されるときにその対応するスイッチを通してそれぞれのサンプリングクロックを第1のノードに選択的に接続し、前記入力クロック信号が前記第2のクロック状態に設定されるときに、前記選択されるサンプリングクロックが前記共通路を通して前記第2の出力状態に遷移されるようにそれぞれ構成される、複数のスイッチをさらに含む、請求項1に記載の回路。

**【請求項6】**

前記第1の回路で受信される前記選択される入力および前記第2の回路で受信される前記選択される入力が、それぞれ、前記複数の入力信号の同じ入力を含む、請求項5に記載の回路。

**【請求項7】**

前記複数のスイッチが、複数の第1のスイッチを含み、前記共通路が、前記第1のノードと前記第2の出力状態で保持される第2のノードとの間に連結され、前記第1のクロック状態から前記第2のクロック状態への前記入力クロック信号の遷移に応答して、前記第1のノードを前記第2のノードに接続するように構成される第2のスイッチを含む、請求項5に記載の回路。

**【請求項8】**

前記複数のサンプリングクロックのそれぞれの前記第1の出力状態が、電圧レベルを有し、前記第1の回路が、前記複数のサンプリングクロックのうちの対応する1つの前記第1の出力状態の前記電圧レベルを昇圧電圧レベルに設定するようにそれぞれ構成される複数のプルアップ昇圧回路を含み、前記第1の回路が、前記複数の第1のスイッチのースイッチにそれぞれ関連付けられる複数のプルダウン経路をさらに含み、前記選択されるサンプリングクロックが、前記第2の回路で受信される前記複数の入力の前記選択される入力が前記第1の入力状態に設定されるとき、選択されるプルダウン経路を通して前記第1のノードおよび選択される第1のスイッチに並列で接続される請求項7に記載の回路。

**【請求項9】**

前記第1の回路が、前記選択される入力が前記第1の入力状態に設定され、前記入力クロック信号が前記第1のクロック状態にあるとき、前記複数のサンプリングクロックの前記選択されるサンプリングクロックを前記第1の出力状態に設定するプルアップ回路をさらに含む、請求項1に記載の回路。

**【請求項10】**

選択されるサンプリングクロックが、第1のサンプリングクロックを含み、前記第2の回路が、

第1のノードに連結される第1の端子、前記複数のサンプリングクロックの前記第1のサンプリングクロックに連結される第2の端子、および第3の端子を有する、第1のスイッチであって、前記第1のスイッチの前記第3の端子で受信される前記複数の入力信号の入力信号が第1の入力状態にあり、前記第1のノードを前記第1のサンプリングクロックと接続するときに、前記オン状態にあるように構成される前記第1のスイッチと、

第1のノードに連結される第1の端子、前記複数のサンプリングクロックの第2のサンプ

10

20

30

40

50

リングクロックに連結される第2の端子、および第3の端子を有する、第2のスイッチであって、前記第2のスイッチの前記第3の端子で受信される前記複数の入力の入力信号が前記第1の入力状態にあり、前記第1のノードを前記第2のサンプリングクロックと接続するときに、前記オン状態にあるように構成される前記第2のスイッチと、

前記第2の出力状態で保持される第2のノードに連結される第1の端子、前記第1のノードに連結される第2の端子、および前記入力クロック信号を受信するための第3の端子を有する第3のスイッチであって、前記入力クロック信号が前記第2のクロック状態にあり、前記第1のノードを前記第2の出力状態に設定するときに、前記オン状態にあるように構成される前記第3のスイッチと、を含む、請求項1に記載の回路。

**【請求項11】**

10

前記第1の回路が、第1のサンプリングクロック上に昇圧電圧レベルを提供するように構成される第1の昇圧回路と、第2のサンプリングクロック上に昇圧電圧レベルを提供するように構成される第2の昇圧回路と、を含む、請求項1に記載の回路。

**【請求項12】**

サンプリングするための方法であって、

複数の入力信号を受信することと、

複数のサンプリングクロックの選択されるサンプリングクロックを、前記複数の入力信号の1つ以上の選択される入力が第1の入力状態に設定されるとき、第1の出力状態に設定することと、

前記1つ以上の選択される入力が前記第1の入力状態にあるときに生じる第1のクロック状態と第2のクロック状態との間の連続的遷移を有する入力クロックを受信することと、前記選択されるサンプリングクロックを、共通路を通して前記第2の出力状態において設定されるノードに接続することによって、前記第1の出力状態にある前記選択されるサンプリングクロックを第2の出力状態に設定することであって、前記複数のサンプリングクロックのそれぞれが同じ共通路を通して前記第2の出力状態に設定される、前記設定することと、を含む、方法。

**【請求項13】**

20

前記設定することが、昇圧電圧を有する前記第1の出力状態を提供するように、所定の電圧によって前記第1の出力状態を上昇させることを含む、請求項12に記載の方法。

**【請求項14】**

30

複数のサンプリングチャネルにおいて前記複数のサンプリングクロックを受信することであって、前記複数のサンプリングクロックのそれぞれが前記複数のサンプリングチャネルのうちの対応する1つのサンプリングスイッチに連結される、前記受信することと、前記選択されるサンプリングクロックが前記第1の出力状態から前記第2の出力状態に設定されるとき、前記複数のサンプリングチャネルの選択されるチャネル上のサンプリングを開始することと、をさらに含む、請求項12に記載の方法。

**【請求項15】**

前記共通路が、共通ノードを前記第2の出力状態で保持される前記ノードに連結するように構成されるスイッチを含み、前記スイッチが、前記第1のクロック状態から前記第2のクロック状態へのそれぞれの入力クロック遷移によって切り替えられる、請求項12に記載の方法。

40

**【請求項16】**

前記スイッチが、第1のスイッチを含み、前記共通ノードが、複数の第2のスイッチのうちの1つを通して前記複数のサンプリングクロックのそれぞれに連結され、前記設定することが、

前記1つ以上の入力が前記第1の入力状態にあるとき、前記第2の複数のスイッチの選択されるスイッチを通して前記選択されるサンプリングクロックを前記共通ノードに接続することと、

前記第1のクロック状態から前記第2のクロック状態へのそれぞれのクロック遷移上で、前記選択されるサンプリングクロックを前記第1のスイッチを通して前記第2の出力状態

50

で保持される前記ノードに接続することによって、前記選択されるサンプリングクロックを前記第2の出力状態に設定することと、を含む、請求項15に記載の方法。

**【請求項17】**

前記選択されるサンプリングクロックの前記共通ノードへの前記接続は、前記1つ以上の入力が前記第1の入力状態にあるとき、前記第2の複数のスイッチの選択されるスイッチおよび並列プルダウン経路を通して、前記選択されるサンプリングクロックを前記共通ノードに接続することを含む、請求項16に記載の方法。

**【請求項18】**

サンプリングするための回路であって、

複数の入力信号を受信するための手段と、

10

複数のサンプリングクロックの選択されるサンプリングクロックを、前記複数の入力信号の1つ以上の選択される入力が第1の入力状態に設定されるとき、第1の出力状態に設定するための手段と、

前記1つ以上の選択される入力が前記第1の入力状態にあるときに生じる、第1のクロック状態と第2のクロック状態との間の連続的遷移を有する入力クロックを受信するための手段と、

前記第1の出力状態にある前記選択されるサンプリングクロックを、前記選択されるサンプリングクロックを前記第2の出力状態で設定されるノードに接続することによって共通路を通して第2の出力状態に設定することであって、前記複数のサンプリングクロックのそれぞれが同じ共通路を通して前記第2の出力状態に設定される、設定するための手段と、を含む、前記回路。

20

**【請求項19】**

複数のサンプリングクロックの選択されるサンプリングクロックを第1の出力状態に設定するための前記手段は、昇圧電圧を有する前記第1の出力状態を提供するように、所定の電圧によって前記第1の出力状態を上昇させる手段を含む、請求項18に記載の回路。

**【請求項20】**

複数のサンプリングクロックを複数のサンプリングチャネルで受信するための手段であって、前記複数のサンプリングクロックのそれぞれが前記複数のサンプリングチャネルのうちの対応する1つのサンプリングスイッチと連結される、前記受信するための手段と、前記選択されるサンプリングクロックが前記第1の出力状態から前記第2の出力状態に設定されるとき、前記複数のサンプリングチャネルの選択されるチャネル上でサンプルを開始するための手段と、をさらに含む、請求項18に記載の回路。

30

**【請求項21】**

前記共通路が、共通ノードを前記第2の出力状態で保持される前記ノードに連結するように構成されるスイッチ手段を含み、前記スイッチ手段が、前記第1のクロック状態から前記第2のクロック状態へのそれぞれの入力クロック遷移によって切り替えられる、請求項18に記載の回路。

**【請求項22】**

前記スイッチ手段が、第1のスイッチを含み、前記共通ノードが、複数の第2のスイッチのうちの1つを通して前記複数のサンプリングクロックのそれぞれに連結され、前記設定するための手段が、

40

前記1つ以上の入力が前記第1の入力状態にあるとき、前記第2の複数のスイッチの選択されるスイッチを通して前記選択されるサンプリングクロックを前記共通ノードに接続する手段と、

前記第1のクロック状態から前記第2のクロック状態へのそれぞれのクロック遷移上で、前記選択されるサンプリングクロックを前記第1のスイッチを通して前記第2の出力状態で保持される前記ノードに接続することによって、前記選択されるサンプリングクロックを前記第2の出力状態に設定するための手段と、を含む、請求項21に記載の回路。

**【請求項23】**

前記選択されるサンプリングクロックを前記共通ノードへ接続する手段が、前記1つ以

50

上の入力が前記第1の入力状態にあるとき、前記第2の複数のスイッチの選択されるスイッチおよび並列プルダウン経路を通して、前記選択されるサンプリングクロックを前記共通ノードに接続するための手段を含む、請求項18に記載の回路。

**【請求項24】**

前記第1の回路が、前記複数の第1のスイッチのースイッチにそれぞれ関連付けられる複数のプルダウン経路をさらに含み、前記選択されるサンプリングクロックが、前記第2の回路で受信される前記複数の入力の前記選択される入力が前記第1の入力状態に設定されるとき、選択されるプルダウン経路を通して前記第1のノードおよび選択される第1のスイッチに並列で接続される請求項5に記載の回路。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

**優先権に関する事項**

本出願は、2013年3月7日に出願された仮特許出願第61/774,432号への優先権を主張するものであり、そのすべての内容は参照により本明細書に組み込まれる。

**【0002】**

本開示は、概して、サンプリング回路に関し、より具体的には、減少されたタイミング不整合を有するサンプリングクロック信号を生成するための装置、システム、回路、および関連する方法に関する。

**【背景技術】**

20

**【0003】**

アナログ・デジタル変換器（A D C）は、複数の時点でアナログ入力信号をサンプリングし、次いで、そのサンプルを、デジタル信号を作成するためにデジタル値に変換するサンプリング回路を利用する。A D Cの使用は、アナログ信号で表される入力信号または入力データを受信し、次いで、デジタル形式でのさらなる処理のためにアナログ信号をデジタル信号に変換する用途において一般的である。アナログ入力信号を正確に変換するために、サンプリング回路によって実施される入力信号のサンプリングは、適切である限りの最高の正確さを有するアナログ入力信号を表すサンプルを変換器に提供するように達成されなければならない。変換されるアナログ入力信号の周波数（F i n）が上昇するにつれて、サンプリングの必要周波数もまた上昇する。A D Cが使用される用途の種類の数が増加しているため、次第に高速になる動作において動作可能なA D Cの必要性もまた増大している。

**【0004】**

時間インターリープ方式でアナログ入力信号を処理するために多重チャネルを利用する時間インターリープA D Cは、高速用途、高速実装等のために開発されたA D Cの一種である。インターリープはまた、所与の分解能に対する電力消費を低下することができる。これは、単一チャネルA D Cのサンプリングレートが使用される技術の限界に近づくにつれて、単一チャネルA D Cの速度／入力電圧のトレードオフが非直線性になるためであり、インターリープを魅力的な代替手段にする。十分な数のA D Cチャネルがインターリープされる場合、それぞれが線形速度／入力電圧のトレードオフを有することになり、結果として、最適な構成を実現する。インターリープに関連付けられるオーバーヘッドはまた、任意のシステムの全性能の評価において、考慮されなければならない。さらに、およそ8ビット以上の分解能に関して、チャネルの内の不整合、例えば、インターリープチャネルのそれぞれにおけるサンプル間のタイミング不整合が除去されなければならない。これは、例えば、フォアグラウンドまたはバックグラウンド較正を介して完了され得る。

**【0005】**

時間インターリープA D Cは、変換速度がチャネルの数に比例して上昇するため、単一チャネルA D Cを上回るデジタルからアナログへの変換のサンプリングレートにおける速さの利点を効果的に提供する。時間インターリープA D Cにおいて、それぞれのチャネルは、アナログ入力信号を順々にサンプリングできる。Nチャネルは並列で動作するため、

50

サンプリングレートは、単一チャネル A D C の N 倍に上昇する。サンプルが一つのチャネルから得られる時間中に、他の複数のチャネルからのサンプルが処理され得る。したがって、時間インターリーブ A D C は、単一チャネルシステムよりも速い速度でデジタル符号語を生成する。しかしながら、時間インターリーブ A D C の欠点は、異なるチャネル間の不整合によって、エラーが生じる可能性があることである。インターリーブ技術は、チャネル間のタイミング不整合の影響を受けやすい。

#### 【 0 0 0 6 】

したがって、インターリーブはまた、変換速度の上昇に加えて、メタスタビリティ割合を減少させ、A D C をより安定させる。それぞれのチャネルに変換のためのより長い時間が与えられると、メタスタビリティの確率は急激に低下する。一般的に、インターリーブ A D C の性能は、典型的にチャネルの内の不整合により制限される。ゲイン、オフセット、およびタイミング不整合は、8 ビット以上の分解能における全体の信号対（ノイズ + 歪み）比率（S N D R ）に大きな影響を与える。多くの場合、タイミング不整合は、検出または訂正に容易に適さないため、較正するのが最も困難である。10

#### 【 0 0 0 7 】

典型的な時間インターリーブサンプリング A D C では、サンプリング信号を使用して、A D C のインターリーブチャネルのそれれにおいてサンプリングのタイミングを制御する。追跡およびホールド回路を使用して、サンプリング信号がある状態から別の状態へ変化するとき、つまりアナログ入力信号のサンプルを保持するようにスイッチをトリガし、チャネルからのアナログ入力信号のサンプルを追跡する（次いで得る）。スイッチ間のいかなる不整合およびサンプリング信号のエッジの間のいかなるタイミング不整合も、インターリーブチャネルからの連続したインターリーブサンプルの不均一な時間的離間を引き起こす。サンプルの不均一な離間は、サンプリングシステムの出力系列中に望ましくないスペクトル成分の出現をもたらす。これらのスペクトル成分は、典型的に所望のサンプル信号の画像を生成し、頻繁に、出力スペクトル内の所望されない場所に生じる。例えば、単純双方向インターリーブシステムにおいて、サンプルクロック中のタイミング不整合は、 $F_s / 2 + / - F_{in}$ において出現する所望の信号の画像中に生じ得、式中、 $F_s$  はシステムのサンプリング周波数であり、 $F_{in}$  はシステムへの入力信号の周波数である。画像の大きさは、サンプリングチャネル間の時間差に比例し、また入力信号の周波数にも比例する。これらのエラーは、特により高い入力周波数において、サンプリングシステムの最大達成可能ス皮アスフリー・ダイナミックレンジ（spurious-free dynamic range）（S F D R ）を低下させる。20

#### 【 0 0 0 8 】

タイミング不整合によって生じるスペクトルアーチファクト（spectral artefact）の効果の除去には費用がかかる。かなりの電力を消費する大きなデジタルフィルターが使用され得る。別的方法として低電力アナログ回路を使用して、タイミングエラーを小さい値に「削減」することができる。しかしながら、いずれの場合においても、エラーが許容レベル [供給される環境、温度、故障応力（die stress）等の変化によらない] を下回るまで低減され、その許容 レベルで維持されるまでの度合いは、初めのエラーがどの程度少ないのでかに左右され得る。少ない初期エラーは少ないままである傾向がある一方、多い初期エラーは削減によって減少され得るが環境変化が生じるほどに著しくドリフトする傾向がある。30

#### 【 0 0 0 9 】

タイミングエラーを除去することが非常に困難であるため、システムはしばしば、追加のネットワークを使用することにより、サンプリングネットワークの何らかの形式のランダム化を利用する。これは、タイミングエラーの影響を除去しない。ランダム化は、単に、エラーを固定パターンではなく時間内により不規則に分布させる。これは、エラーをシステムのノイズフロア全体に広げる傾向がある。この作用は、システムのノイズフロアを上昇させ、さらに、サンプリングシステムが達成することができる最大の信号対ノイズ比（S N R ）を低下させる。タイミングエラーの最小化は、したがって、システムが達成し4050

得る潜在的な信号対ノイズ比（S N R）を最大化する。これは、たとえランダム化が使用される場合であっても同じである。少ない初期タイミングエラーを有するシステムは、いかなる時間インターリーブA D Cシステムにおいても利益を提供する。したがって、時間インターリーブA D Cにおけるタイミング不整合を最小化し、実装するために低減された複雑性しか必要とせず、実装することが比較的単純であり、ならびにそれ自体によってまたは他の技術と組み合わせて使用され得る解決策を有することが望ましい。

### 概要

#### 【0010】

本開示は、概して、サンプリングシステムを制御するためのサンプリング信号を生成するための装置、システム、回路、および方法に関する。一実施形態例において、方法、システム、および装置は、多重インターリーブサンプリングチャネルを有する時間インターリーブサンプリング回路にサンプリングクロックとしての出力を生成する回路を含み得る。回路は、共通回路が多重インターリーブチャネルのそれぞれのサンプリングクロック回路で共有されるように実装され得る。共通回路の利用は、互いに対するサンプリングクロック間のタイミング関係の制御を均一化することを可能にする。そのような手法は、サンプリングクロック間のタイミングスキューを減少させることができる。本実施形態の実装例において、多重インターリーブサンプリングチャネルは、アナログ・デジタル変換器（A D C）回路のインターリーブサンプリングチャネルを含み得る。

10

#### 【0011】

一実施形態において、入力クロック信号を含む複数の入力信号を受信し、複数のサンプリングクロックを生成するための回路が提供される。回路は、複数のサンプリングクロックのそれぞれのサンプリングクロックを第1の出力状態に選択的に設定するように構成される第1の回路を含み、複数のサンプリングクロックの選択されるサンプリングクロックは、複数の入力信号の選択される入力が第1の入力状態に設定されるとき、第1の出力状態に設定される。回路はまた、複数のサンプリングクロックのそれぞれを、共通路を通して第2の出力状態に遷移させるように構成される第2の回路を含み、選択されるサンプリングクロックは、第1のクロック状態から第2のクロック状態への入力クロック信号の遷移に応答して、第1の出力状態から第2の出力状態に共通路を通して遷移される。

20

#### 【0012】

別の実施形態において、回路は、時間インターリーブサンプリング回路にサンプリングクロックとして昇圧出力を生成する昇圧回路を含み得る。昇圧サンプリングクロックは、サンプリングクロック出力によって駆動されるスイッチを作動させるためのより高い信号レベルを提供する。回路は、共通回路が多重インターリーブチャネルのそれぞれのサンプリングクロック回路間で共有されるように実装され得る。共通回路の利用は、昇圧サンプリングクロック間のタイミング関係の制御の均一化を可能にする。

30

#### 【0013】

さらに別の実施形態において、回路は、複数のサンプリングクロックのうちの1つに対応する第1の回路の出力にそれぞれ連結される複数のサンプリングチャネルを含むサンプリング回路を含み得る。サンプリング回路は、選択されるサンプリングクロックが第1の出力状態から第2の出力状態に遷移されるとき、複数のチャネルの選択されるチャネルからサンプルを生成するように構成され得る。

40

#### 【0014】

別の実施形態例において、方法、システム、および装置は、多重インターリーブチャネルのそれぞれのサンプリングクロック回路間で共有され得るプルアップ／ホールドダウン回路を制御する共通クロック信号を利用することによってサンプリングクロック間のタイミングスキューを最小化する構造を含む時間インターリーブサンプリング回路に、サンプリングクロックとしての出力を生成する回路を含む。共通プルアップ／ホールドダウン回路の利用は、クロックスキューを最小化するための、互いに対する多重インターリーブチャネルのサンプリングクロックのエッジ間のタイミング関係の制御を可能にする。このプルアップ／ホールドダウン回路の実装において、サンプリングクロックが上昇させられ得

50

る。

**【0015】**

他の実施形態例において、方法、システム、および装置は、共通クロック信号を利用することによってサンプリングクロック間のタイミングスキーを最小化する構造を含み得る時間インターリープサンプリング回路にサンプリングクロックとしての出力を生成する回路を含む。共通クロック信号は、多重インターリープチャネルのそれぞれのサンプリングクロック回路間で共有され得るプルアップ／ホールドダウン回路およびプルダウン回路を制御する。共通プルアップ／ホールドダウン回路およびプルダウン回路の利用は、クロックスキーを最小化するための、多重インターリープチャネル（互いに対する）のサンプリングクロックのエッジ間のタイミング関係の制御を可能にする。プルアップ／ホールドダウン回路およびプルダウン回路の実施形態の一実装例において、サンプリングクロックが上昇させられ得る。10

**【図面の簡単な説明】**

**【0016】**

本開示のより完全な理解ならびに特徴およびそれらの利益を提供するために、添付の図面とともに得られる以下の説明が参照され、図中、同様の符号は同様の部分を表す。

**【0017】**

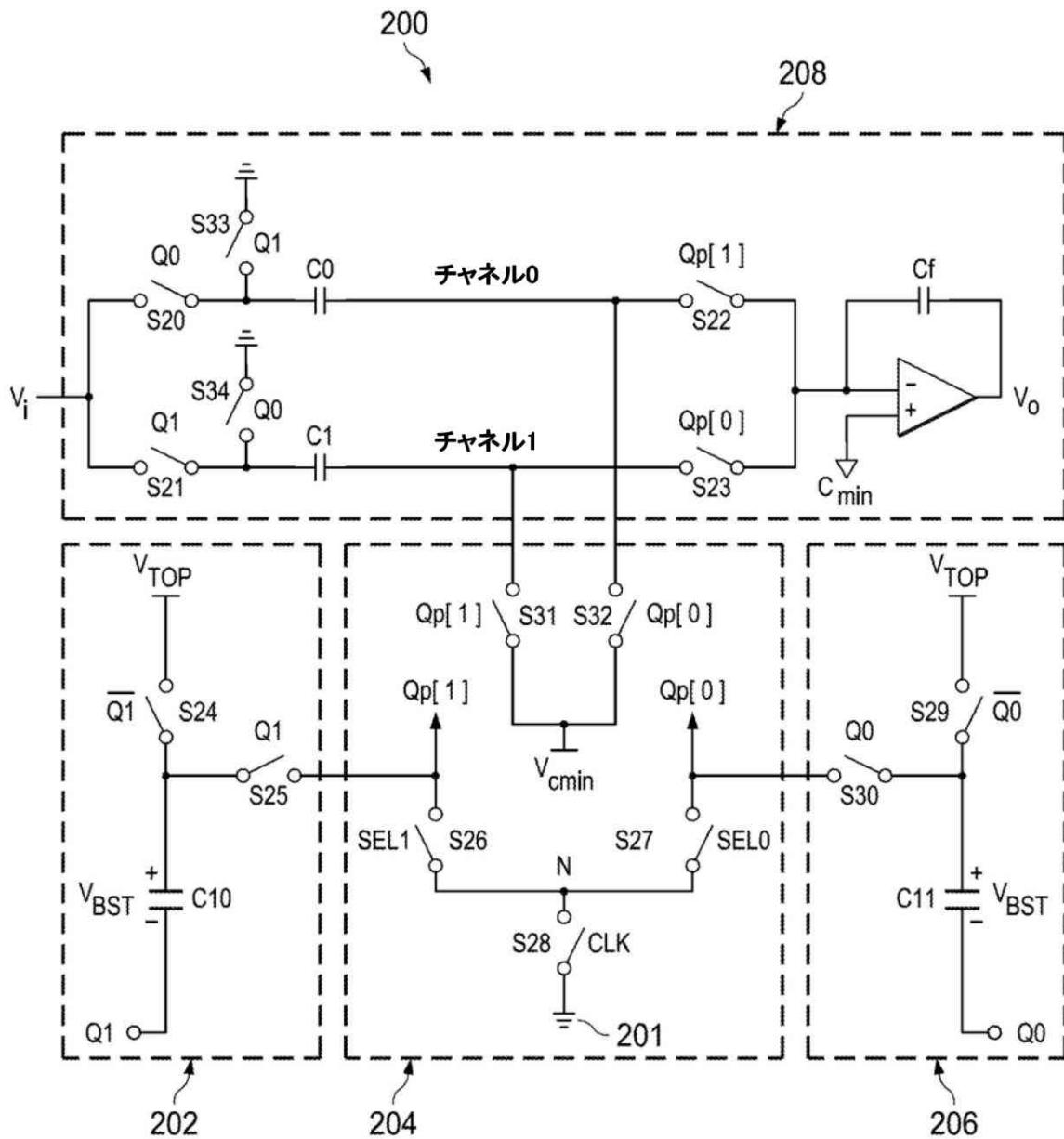

**【図1A】**図1Aは、本開示の一実施形態のスイッチレベル図の例を図示する。

**【0018】**

**【図1B】**図1Bは、図1Aの実施形態に関するタイミング波形の例を図示する。20

**【0019】**

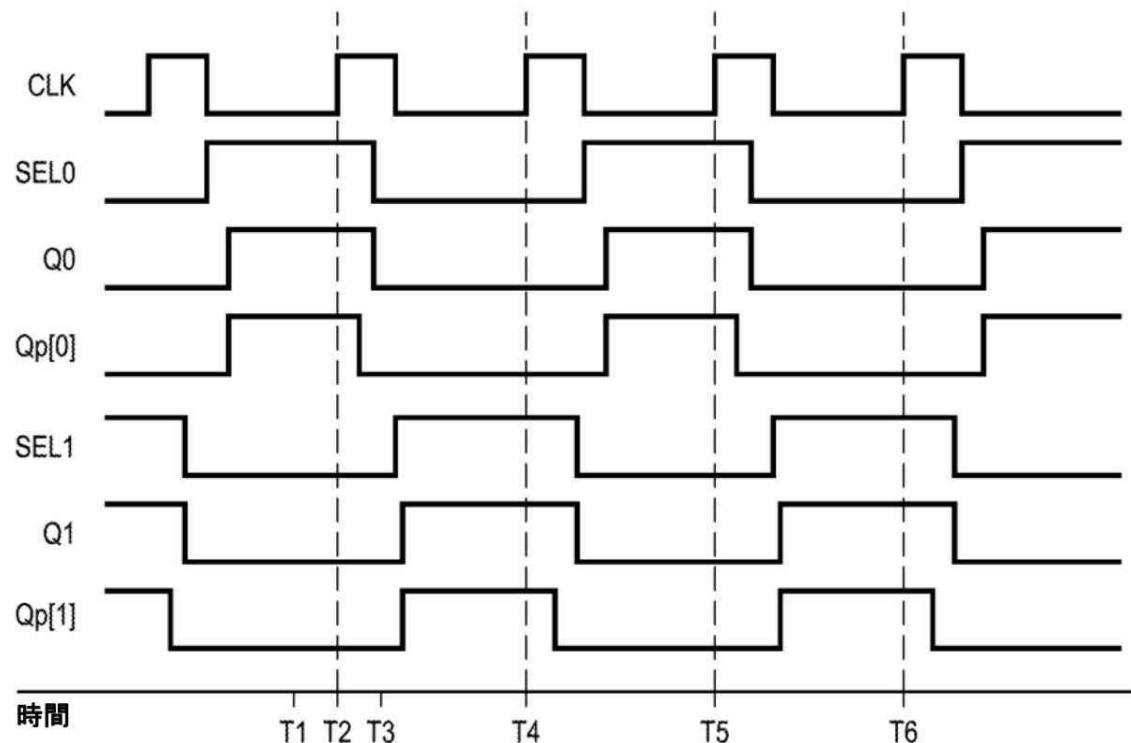

**【図2】**図2は、図1の実施形態のプルダウン回路の一実装例を図示する。

**【0020】**

**【図3A】**図3Aは、本開示の別の実施形態に従うサンプリング回路を図示する。

**【0021】**

**【図3B】**図3Bは、図3Aの実施形態のプルアップ／ホールドダウン回路の一実装例を図示する。

**【0022】**

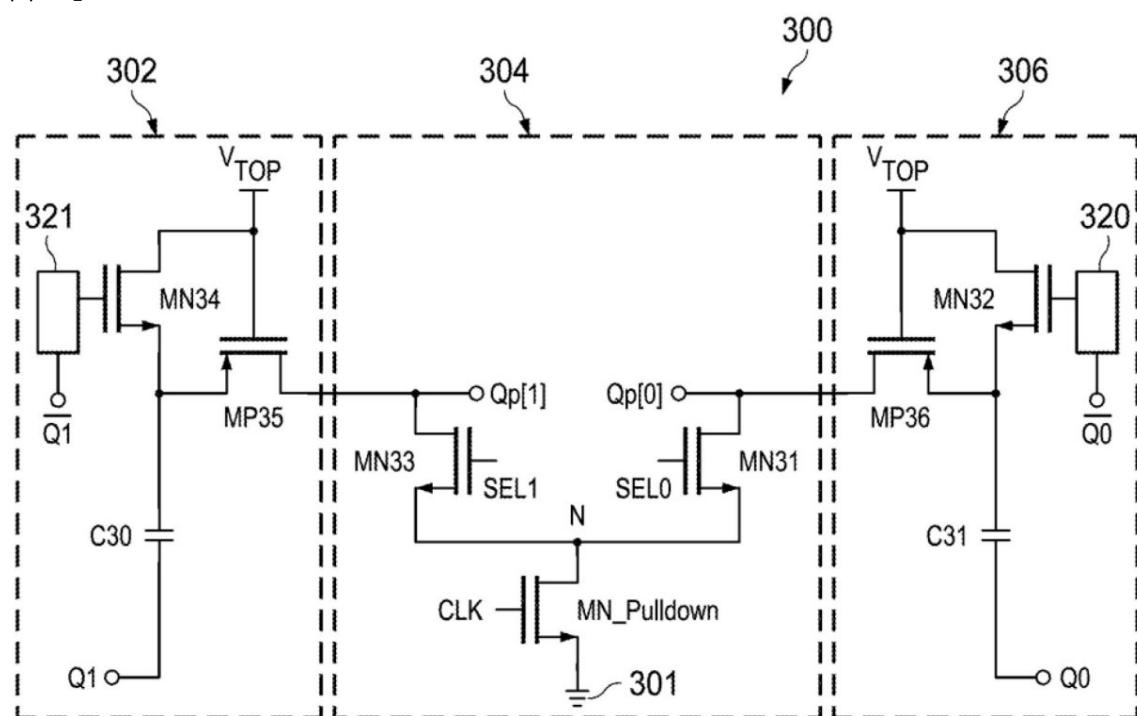

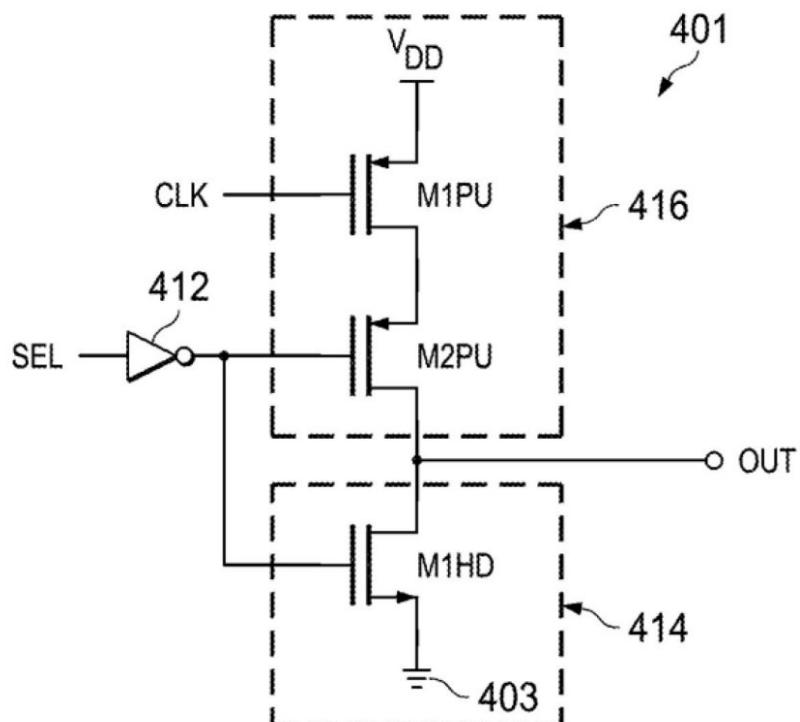

**【図4A】**図4Aは、本開示のさらなる実施形態に従うサンプリング回路を図示する。

**【0023】**

**【図4B】**図4Bは、図4Aの実施形態に関するプルアップ昇圧／ホールドダウン回路の一実装例を図示する。30

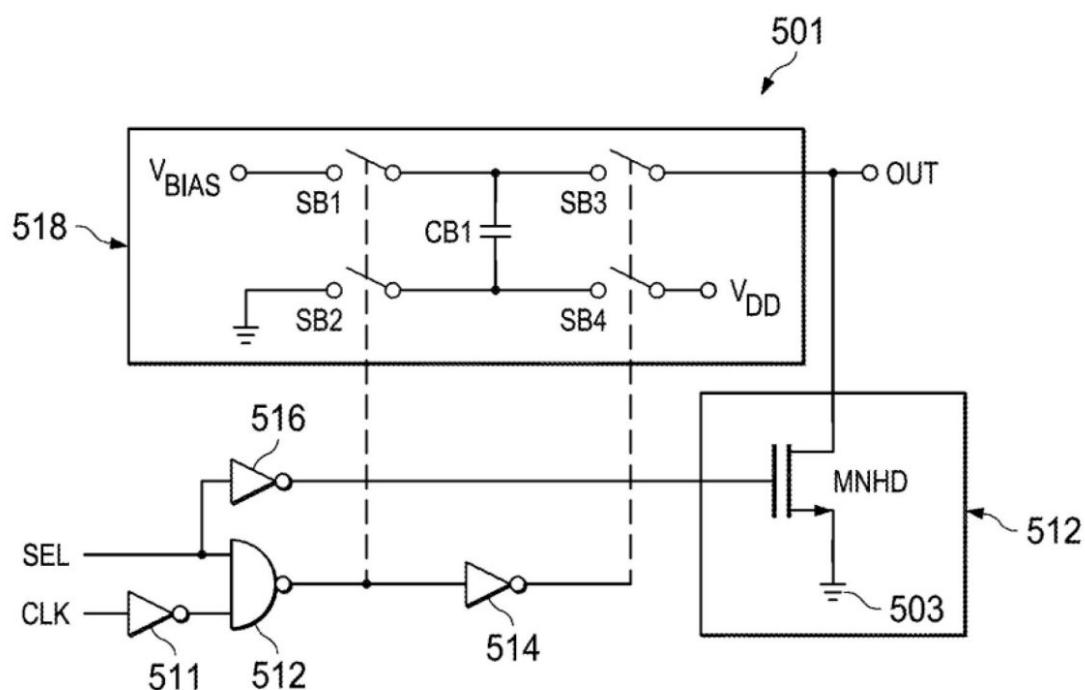

**【0024】**

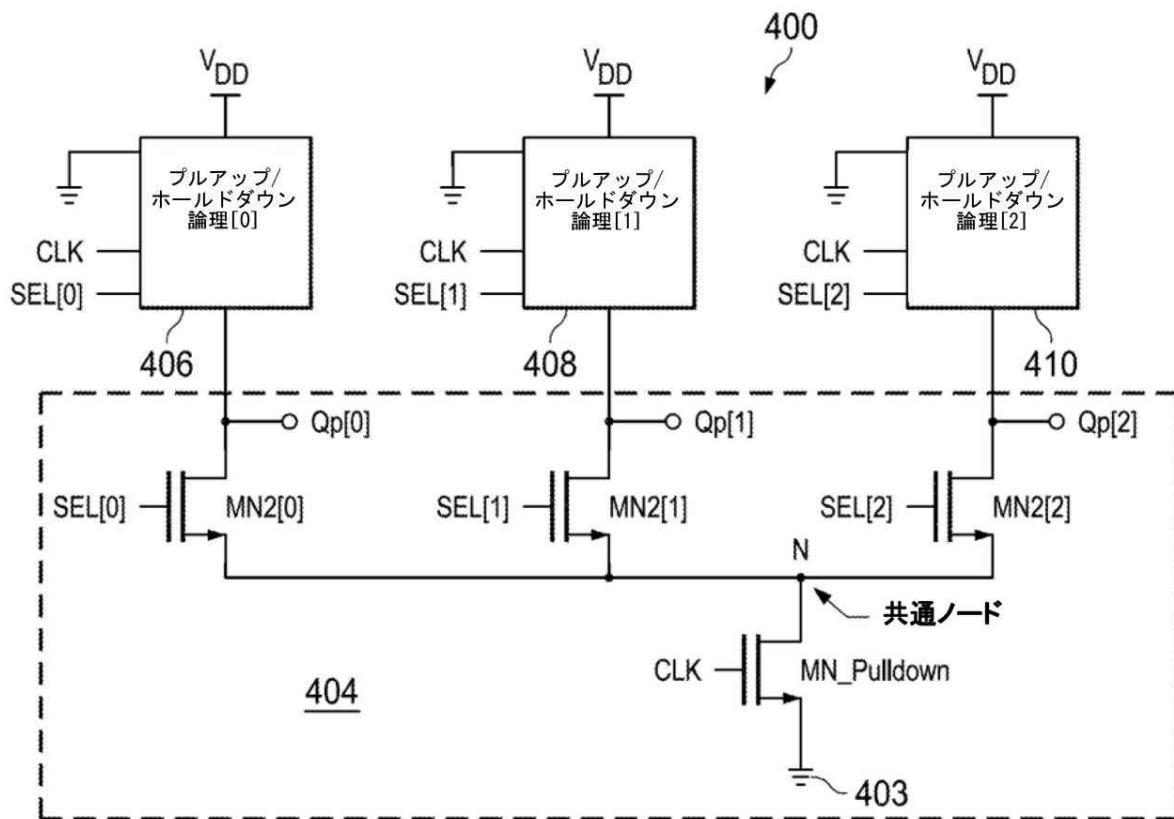

**【図5】**図5は、本開示の別の実施形態に従うプルアップ昇圧／ホールドダウン、およびプルダウンサンプリング回路の一実装例を図示する。

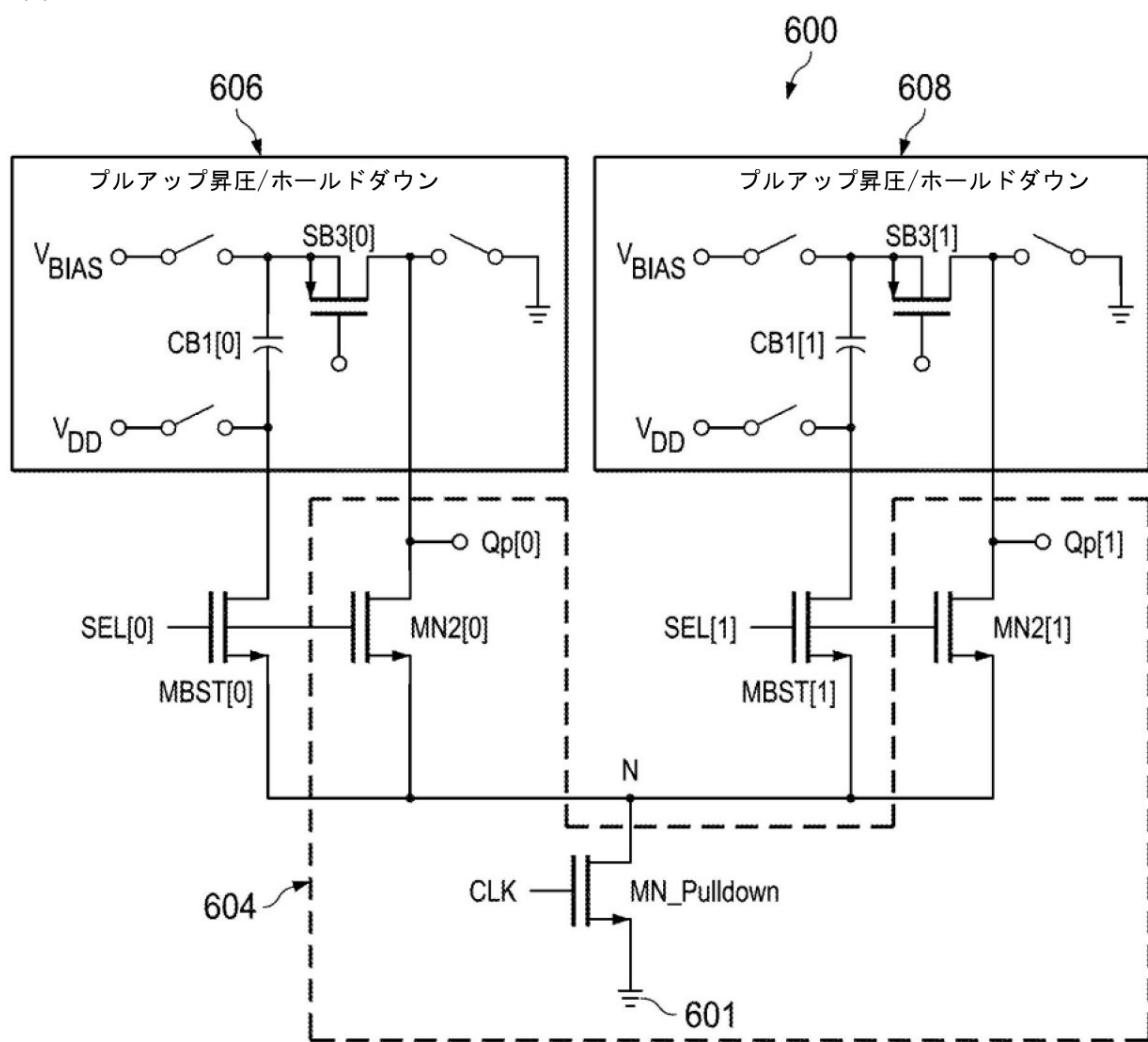

**【0025】**

**【図6A】**図6Aは、本開示のさらなる実施形態に従うプルアップおよびプルダウンサンプリング回路の一実装例を図示する。

**【0026】**

**【図6B】**図6Bは、図6Aの実施形態に関するタイミング波形の例を図示する。40

**【発明を実施するための形態】**

**【0027】**

本開示は、概して、サンプリングシステムを制御するためのサンプリング信号を生成するための装置、システム、および方法に関する。より具体的には、本装置、システム、および方法は、インターリープサンプリング回路の多重チャネルのサンプリングクロック間の不整合およびタイミングスキーを最小化するインターリープサンプリング回路にサンプリングクロックを生成するための実施形態を提供する。

**【0028】**

ここで図1Aを参照すると、インターリープアナログ・デジタル変換器（ADC）においてサンプリングクロックを生成するように構成される本開示の一実施形態例のスイッチ50

レベル図がある。図1Aは、インターリープADCチャネル回路208、サンプリングクロックを生成するための、プルダウン回路204、電圧回路202、および電圧回路206を含む回路を含むADCサンプリング回路200を図示する。ADC回路208は、入力Viにおいてアナログ入力信号を受信し、出力Voにおいてアナログ入力信号のサンプルを生成する。Voにおけるサンプル出力は、次いで、さらなる処理のためにデジタル値に変換され得る。

#### 【0029】

図1Aのスイッチレベル実装は、サンプリング回路200の様々な部分内で示されるスイッチS20～S34を図示する。個々のスイッチS20～S34のそれぞれは、図1Aの実施形態例において、2つのノードをともに連結するように構成される論理レベルスイッチを表す。それぞれのスイッチは、スイッチ入力信号がロー状態またはロー論理状態にあるときはオフにされており、それぞれのスイッチは、スイッチ上の各信号名ラベルで示されるスイッチ入力信号がハイ信号レベルまたはハイ論理状態に動くときは接続を閉じる。例えば、信号Q0がハイに動くとき、ViをC0に連結するように構成されるスイッチS20が起動し、ViとC0との間の接続を閉じる。図1Aは、特定の論理スイッチレベル実装として本実施形態例を図示するが、図1Aのスイッチ機能は、多くの異なる構成のスイッチング回路で実装されてもよいことに留意されたい。例えば、他の実装において、スイッチのうちの1つ以上が、スイッチ入力上でハイ論理状態ではなくロー論理状態によって起動されてもよい。さらに、本開示の様々な実施形態の回路は、異なる部品を使用する異なる種類の技術で実装され得る。回路は、例えば、NMOSまたはPMOS論理を使用するMOSFET実装切り替え論理を含み得る。また、図1Aの実施形態は、特定の入力信号および出力信号ならびにこれらの信号間のタイミング相関を図示するが、本実施形態の利益は、異なる論理状態およびこれらの信号間の異なるタイミング相関を有する入力および出力信号の異なる配置を利用して実現されてもよいことに留意されたい。さらに、図1Aは2つのインターリープチャネルを図示するが、図1Aの実装は、3つ以上の任意の数のインターリープチャネルにサンプリングクロックを生成するように拡張されてもよいことに留意されたい。

#### 【0030】

図1Aの実施形態において、サンプリング回路200の動作は、入力SEL0、SEL1、Q0、Q1、およびCLKで受信される入力信号により制御され得る。互いに対するこれらの入力信号の論理状態およびタイミングは、各々チャネル0およびチャネル1上でサンプリングをトリガするサンプリングクロック出力Qp[0]およびQp[1]でのサンプリング信号の生成を制御する。プルアップ昇圧電圧回路202、206に加えてプルダウン回路204で生成されるサンプリングクロック出力Qp[0]およびQp[1]は、いつ入力Viにおけるアナログ信号入力のサンプルが各々チャネル0およびチャネル1上で得られるのかを制御する。本実施形態は、（電圧回路202および206とともに機能する）プルダウン回路204が、共通ノードNおよびCLK入力信号を使用する共通スイッチS28を通る出力Qp[0]およびQp[1]における信号のタイミングの制御を可能にするという点において利益を提供する。共通ノードN、共通スイッチS28、ならびにスイッチS26およびS27を通る出力Qp[0]およびQp[1]における信号のタイミングの制御は、ADC上でのクロックスキュー効果およびタイミング不整合効果を最小化する。この利益は、追加の出力をノードNに連結するために、そこでサンプリングクロックが生成されるそれぞれの追加の出力のためのスイッチS26およびS27を含む複数のスイッチに追加することによって、3つ以上の任意の数のインターリープチャネルにサンプリングクロックを生成するように拡張されてもよい。

#### 【0031】

ここで図1Bを参照すると、図1Aの実施形態のタイミング回路の入力信号に対するタイミング波形の例が示される。図1Bは、CLK、SEL0、Qp[0]、Q0、SEL1、Q1、およびQp[1]信号のタイミング波形の例を図示する。入力SEL0およびSEL1がプルダウン回路204に入力され、サンプリングの全体のシステムタイミング

10

20

30

40

50

を制御する。図 1 A の実施形態において、SEL0、Q0、SEL1、およびQ1は、インターリープサンプリングチャネル回路208に直接入力されないが、プルダウン回路204ならびにブースター回路202および206に入力される。プルダウン回路204ならびに電圧回路202および206は、次いで、インターリープサンプリング回路208でサンプリングをトリガするための出力Qp[0]およびQp[1]を生成する。入力Q0は、SEL0に基づいて生成され得、Qp[0]の立ち下がりエッジに続く立ち下がりエッジを有するように時間決めされ得る。入力Q1は、SEL1に基づいて生成され得、Q[1]の立ち下がりエッジに続く立ち下がりエッジを有するように時間決めされ得る。CLK信号は、次いで、プルダウン回路204に入力され得、Qp[0]およびQp[1]によって駆動されるサンプリングの相対的なタイミングの制御に使用され得る。本実施形態において、図1Bは、反対極性の周期波形としてSEL0およびSEL1を示し、CLK信号は、CLKハイ論理状態がSEL0およびSEL1の立ち下がりエッジを包含するように時間決めされ得る周期パルスとして入力され得る。

10

### 【0032】

図1Aおよび1Bを参照して、説明として、時間T1においてSEL0がハイであり、SEL1がローであるとき、ロー論理状態にあるQ1およびSEL1によって、スイッチS25およびS26が開き、Qp[1]がロー論理状態にあるその前の状態で留まる。また時間T1において、入力Q1はローであり、Viは開いているS21によってインターリープチャネル1からオフに切り替えられ、ハイの入力SEL0およびQ0によってS30およびS27は閉じられ、S29は開けられる。これより前、入力Q0がその前にローであったときは、S29は閉じられており、VTOPはコンデンサC11の上板に接続されていた。Q0がハイになるとき、S29は開き、コンデンサC11の上板の上のVTOPをサンプリングする。このため、C11の上でサンプリングされた電圧VBSTは、VTOPとローレベル論理信号Q0の実際の電圧レベルとの間の差異と等しい。Q0がハイになるとき、S30は閉じ、Qp[0]は、VBSTに加えてハイ論理状態入力Q0の電圧レベルと等しい実際の電圧レベルでハイ論理状態にある。ハイ論理状態になるQp[0]は、S32をオンに切り替え、チャネル0を電圧Vcminに接続する。ローであるQp[1]は、S22を開いたまま保ち、ハイであるQ0はS20を閉じ、コンデンサC0が入力信号Viを追跡することを可能にする。CLK入力は、SEL0が、時間T2で図1Bにおいて示されるように依然ハイであるとき、ハイ状態になるように時間決めされる。CLKが、SEL0がハイであるT2でハイに動くとき、スイッチS28は閉じ、Qp[0]を、例えば、S27を通してグランドで保持され得るノード201の電圧レベルに引く。ローになるQp[0]は、スイッチS32をオフにし、Qp[0]がローに動きS32をオフにするように切り替える時点で、チャネル0上で得られるべきVinの値のサンプルをトリガする。時間T3において、SEL0が続いてローに動き、SEL1がハイに動くとき、スイッチS20が開き、スイッチS22およびS33が閉じ、インターリープADCチャネル回路208の出力Voで出力されるべき入力Viでのアナログ入力信号のサンプルを可能にする。Q1がロー状態にあるT3の前の時間の間、S24は閉じられ、VTOPはコンデンサC10の上板に接続される。これは、C10を入力Q1ロー状態とVTOPとの間の電圧差異と等しい電圧に充電し、それはVBSTと等しい。時間T3の後、Q1がハイになるとき、S24は開いてS25は閉じ、VTOPはコンデンサC10の上板の上でサンプル化され得る。

20

30

40

### 【0033】

SEL0がT3においてローに動くとき、SEL1はハイに動き、インターリープサンプリングチャネル0のQp[0]でサンプリングクロックを生成するための前述のプロセスは、記載のプロセス中において、各々SEL0、Q0、およびQp[0]で置き換えられるSEL1、Q1、およびQp[1]信号、コンデンサC11で置き換えられるコンデンサC10、ならびに各々スイッチS20、S22、S29、S30、S27、およびS33で置き換えられるスイッチS21、S23、S24、S25、S26、およびS34を有するインターリープサンプリングチャネル1のQp[1]でサンプリングクロックを

50

生成するために同様に起こる。T 2 でハイになる C L K によって Q p [ 0 ] がローに引かれたときのチャネル 0 上と同様に、チャネル 1 上のサンプルは、Q p [ 1 ] が、S E L 1 がハイである T 4 で C L K 信号がハイになることにより、S 2 6 および S 2 8 を通る V B S T に加えてハイ論理状態入力 Q 1 の電圧レベルからローに引かれるときに得られる。図 1 A の 2 つのチャネル実施形態において、サンプリングクロック Q p [ 0 ] および Q p [ 1 ] は、ロー状態からハイ状態への C L K 入力の続く遷移上においてチャネル 0 およびチャネル 1 でサンプリングを交互にトリガすることによって継続される。例えば、図 1 Bにおいて、サンプルは、チャネル 0 で時間 T 5 においてロー状態からハイ状態に遷移させる C L K 入力によってトリガされ、ならびにサンプルは、チャネル 1 で時間 T 6 においてロー状態からハイ状態に遷移させる C L K 入力によって生成される。3 つ以上の数のインターリーブチャネル、例えば、複数の N 個のインターリーブサンプリングチャネルを有する図 1 A の回路の一実施形態において、アナログ信号のサンプリングは、N 個のサンプリングチャネルのそれぞれで独立して交互に行われ得る。これは、C L K 入力がローからハイ状態へ遷移するとき、チャネル上のサンプリングをトリガする入力が 1 つずつハイ状態に交互に設定されるように、入力 S E L [ 0 ] . . . . . S E L [ N ] および Q 0 . . . . . Q N 上で適切に時間決めされる入力信号を生成することによって完了され得る。

#### 【 0 0 3 4 】

図 1 A の実施形態におけるインターリーブチャネルのためのサンプリングクロック Q p [ 0 ] および Q p [ 1 ] は、したがって、1 つの共通スイッチ S 2 8 によって作成される共通路を通るノード 2 0 1 の状態に引かれる共通ノード N によって、C L K 信号の立ち上がりエッジに同期される。これは、S E L 0 と S E L 1 との間のタイミング不整合、または、さもなければチャネルをサンプリングするためのサンプリングクロックとして使用されることになる他のサンプリングクロック信号の効果を減少させる。3 つ以上の複数のインターリーブサンプリングチャネルを有する一実施形態において、共通路の使用は、サンプリングクロック Q p [ 0 ] . . . . Q p [ N ] のそれぞれを同じ手法で同期することになる。本実施形態は、スイッチ S 2 8 が単一のトランジスタを使用して実装されることができ、それにより、両方の信号がスイッチ S 2 8 を通る同じ進路を通してローに引き下げられるために、C L K 入力の立ち上がりエッジから Q p [ 0 ] の立ち下がりエッジまで、および C L K の立ち上がりエッジから Q p [ 1 ] の立ち下がりエッジまでの伝播遅延路における差異を最小化するという点において利益を提供する。Q p [ 0 ] および Q p [ 1 ] をローに設定するために、それぞれ別々のトランジスタから成る別々の論理ゲートが使用される場合、論理ゲートがどのように作成されるかにかかわらず、製造上の誤差のため、C L K の立ち上がりエッジから Q p [ 0 ] の立ち下がりエッジまでの、および C L K の立ち上がりエッジから Q p [ 1 ] の立ち下がりエッジまでのゲートのそれぞれを通る伝播遅延における差異が存在する。サンプリングクロック Q 1 p [ 0 ] および Q 1 [ 1 ] の立ち下がりエッジの均一化した離間、つまり、サンプルスイッチのターンオフ時を制御するエッジは、均一に離間された入力サンプルの保存において重要である。立ち上がりエッジの均一化した離間は、本実施形態においては極めて重要とはいえないであろう。

#### 【 0 0 3 5 】

さらに、図 1 A の実施形態は、Q p [ 0 ] および Q p [ 1 ] によって切り替えられるスイッチ S 2 3 、 S 3 2 、および S 2 2 、 S 3 1 が各々完全におよびきれいにオンとなるように駆動されるように、Q p [ 0 ] および Q p [ 1 ] 信号を上昇させる電圧回路 2 0 2 および 2 0 6 を有するという、追加される利益を提供する。

#### 【 0 0 3 6 】

ここで図 2 を参照すると、トランジスタレベル回路、つまり、図 1 A の昇圧電圧回路 2 0 2 および 2 0 6 ならびにプルダウン回路 2 0 4 の一実装例が示される。図 2 の実装は、各々同じ機能を有する図 1 A の昇圧電圧回路 2 0 2 および 2 0 6 、ならびにプルダウン回路 2 0 4 との相互関係を示すブースター回路 3 0 2 および 3 0 6 、ならびにプルダウン回路 3 0 4 を含む。図 2 の実装の回路は、図 1 A および図 1 B の実施形態に関して記載され

10

20

30

40

50

たように、入力 S E L 0、S E L 1、Q 0、Q 1、および C L K を受信し、出力 Q p [ 0 ] および Q p [ 1 ] を生成する。プルダウン回路 3 0 4 は、M O S トランジスタ M N \_ P u 1 1 d o w n、M N 3 1、および M N 3 3 を含む。M N 3 1 および M N 3 3 は、各々対応する回路出力 Q p [ 0 ] および Q p [ 1 ] を共通ノード N に連結するようにそれぞれ構成される。M N 3 3 のドレイン端子は、Q p [ 1 ] サンプリングクロック出力に接続され得、M N 3 1 のドレインは、Q p [ 0 ] サンプリングクロック出力に接続され得る。M N 3 1 および M N 3 3 両方のソース端子は、共通ノード N で M N - プルダウンのドレイン端子に接続される。M N \_ P u 1 1 d o w n のソース端子は、ノード 3 0 1 に接続され得、共通ノード N を、M N \_ P u 1 1 d o w n を通してノード 3 0 1 に連結する。本実施形態において、ノード 3 0 1 は、0 の電圧レベルで保持され得るか、またはグランド S E L 0 10 、S E L 1、および C L K は、各々 M N 3 1、M N 3 3、および M N \_ P u 1 1 d o w n のゲート端子に入力される。ブースター回路 3 0 2 のゲート制御回路 3 2 1 は、Q 1 がローであるとき、M N 3 4 をオンにする。これは、(ロー論理状態にある) Q 1 の電圧と V T O P との間のコンデンサ C 3 0 を充電する。ブースター回路 3 0 6 のゲート制御回路 3 2 0 は同様に、Q 0 がローであるとき、M N 3 2 をオンにする。これは、(ロー論理状態にある) Q 0 の電圧と V T O P との間のコンデンサ C 3 1 を充電する。

#### 【 0 0 3 7 】

ブースター回路 3 0 2 の目的の 1 つは、Q p [ 0 ] および Q p [ 1 ] によって駆動されるサンプリングスイッチを、供給電圧が、制限されるかまたは入力信号をサンプリングするために使用されるトランジスタの閾値電圧と比較して小さいときであっても、大きいゲート - ソース間電圧 (V G S) を使用してオンにすることである。多くのロー電圧 C M O S サンプリング回路において、クロック昇圧の使用は、スイッチをオンにするために重要であることに留意されたい。 20

#### 【 0 0 3 8 】

図 2 の回路が、図 1 A のスイッチ - レベル実装に関して記載されるように、S E L 0、S E L 1、Q 0、Q 1、および C L K 上の同じ入力を提供されるとき、図 3 の回路 3 0 0 は、図 1 B に示される同じ関係を有する Q p [ 0 ] および Q p [ 1 ] 上に出力信号波形を提供する。図 2 は、N M O S トランジスタを使用して図 1 A の部分の特定のトランジスタレベル実装を図示するが、同じ機能を有する多くの異なるトランジスタおよび部品レベルの実装が、本開示の広範囲から逸脱することなく容易に構成され得ることに留意されたい。 30 例えれば、P M O S トランジスタを使用して、本実施形態の実装が作成されてもよい。

#### 【 0 0 3 9 】

ここで図 3 A を参照すると、本開示のさらなる実施形態に従うサンプリング回路 4 0 0 が示される。図 3 A の実施形態は、プルダウン論理 4 0 4、ならびにプルアップ / ホールドダウン論理 4 0 6、4 0 8、および 4 1 0 を含む。図 3 A の実施形態は、3 チャネルインターリーブ A D C のサンプリングクロックを生成するように構成され示されるが、回路は任意の数のサンプリングチャネルで作動するように縮小または拡張されてもよい。それぞれのプルアップ / ホールドダウン論理区分 4 0 6、4 0 8、4 1 0 は、3 サンプリングチャネルのうちの 1 つを用いて作動する。図 3 A の実施形態において、プルアップ / ホールドダウン論理区分 4 0 6、4 0 8、4 1 0 は、図 3 B に示される実施形態のトランジスタ実装例 (すなわち、プルアップ / ホールドダウン論理 4 0 1) としてそれぞれ実装され得る。 40

#### 【 0 0 4 0 】

図 3 B を参照して、プルアップ / ホールドダウン論理 4 0 1 は、インバーター 4 1 2 ならびに M O S トランジスタ M 1 P U、M 2 P U、および M 1 H D を含む。プルアップ区分 4 1 6 は、V D D を出力 O U T に連結するように構成される M 1 P U および M 2 P U を含む。プルアップ区分 4 1 6 は、C L K 入力がローであり、S E L 入力がハイのとき、M 1 P U および M 1 P U を通る V D D に応じて出力 O U T を引き出す。ホールドダウン区分 4 1 4 は、出力 O U T をノード 4 0 3 に連結するように構成されるトランジスタ M 1 H D を含む。S E L がローのとき、M 1 H D はオンであり、O U T をロー状態のノード 4 0 3 で 50

保持する。図3Aの実施形態に従うそれぞれのチャネルに関するプルアップ／ホールドダウン論理406、408、および410は、それぞれのチャネルの適切なサンプリング入力SEL[0]、SEL[1]、またはSEL[2]を、プルアップ／ホールドダウン論理401としてそれぞれのチャネルに対して別々に実装される回路のSEL入力に接続することによって、それぞれのプルアップ／ホールドダウン論理406、408、および410のCLK入力をプルアップ／ホールドダウン論理401として実装される回路のCLK入力に接続することによって、ならびにそれぞれのチャネルに対するプルアップ／ホールドダウン論理401として実装されるそれぞれのプルアップ／ホールドダウン論理406、408、および410のOUT端子を、Qp[0]、Qp[1]、またはQp[2]の適切な出力に接続することによって実装されてもよい。プルアップ／ホールドダウン論理回路、406、408、および410は、各々Qp[0]、Qp[1]、またはQp[2]で、順々にプルダウン回路404とともに3つのインターリーブチャネル上でサンプリングをトリガするための適切なサンプリングクロック信号を生成する。

10

#### 【0041】

再び図3Aを参照して、プルダウン回路404は、MOSトランジスタMN\_Pu11down、MN2[0]、MN2[1]、およびMN2[2]を含む。プルダウン回路404は、図3Aの実施形態におけるプルダウン回路404が、2つのチャネルではなく3つのチャネルをサンプリングするために出力サンプリングクロック信号Qp[0]、Qp[1]、およびQp[2]を生成するように構成され得ることを除いて、図1Aおよび2のプルダウン回路204およびプルダウン回路304と同様に機能する。図3Aのサンプリング回路400の実施形態について、CLK信号の追加のサイクルが第3のチャネルに追加される。それぞれの信号Qp[0]、Qp[1]、またはQp[2]は、各々、適切なプルアップ／ホールドダウン論理区分406、408、または410によってハイに設定され、次いで、入力信号SEL0、SEL1、SEL2、およびCLKの回路400への適用を通してプルダウン回路404によって引き下げられることを介して順々にまたはランダムにサイクルされ得る。それぞれのサンプリングクロックQp[n]は、その各プルアップネットワークによって独立してハイに設定されてもよい。この状態において、対応する選択ラインがハイ状態にあってもよく、一方CLKはロー状態にある。一例として、Qp[0]は、SEL[0]がハイであり、CLKがローであるとき、ハイに設定され得る。この場合において、すべての他のQp[n]チャネルがローであり、それらの各SEL[n]入力はロー状態に設定される。

20

30

#### 【0042】

サンプリング時間において、CLK入力がロー状態からハイ状態に遷移するとき、プルダウン回路404を使用して、各々MN2[0]、MN2[1]、またはMN2[2]を通るQp[0]、Qp[1]、またはQp[2]を、ハイに上昇しMN\_Pu11downをオンにするCLK信号によって、MN\_Pu11downを通る共通ノードNを介してロー状態のノード403に引き下げることができる。例えば、SEL[0]がハイ状態にあり、CLK入力がロー状態からハイ状態に遷移するとき、Qp[0]は、MN\_Pu11downおよびMN2[0]を通して引き下げられる。Qp[0]が下がり始める瞬間は、主にロー状態からハイ状態に遷移する入力信号CLKに応答するMN\_Pu11downのターンオン特性によって、MN2[0]の閾値電圧よりもはるかに小さい程度まで決定される。同様の方式において、適切なSEL[n]入力がハイであるとき、他のサンプリングクロックQp[n]のそれぞれは、主にロー状態からハイ状態に遷移するCLK信号に応答するMN\_Pu11downによって決定される時間に下がり始める。その時間もまた、各MN2[n]トランジスタの閾値電圧によりもはるかに小さい程度まで決定される。本実施形態の一つの利益は、本開示におけるすべてのサンプリングクロック出力Qp[n]のハイ-ロー間遷移の開始が、主に1つの单ートランジスタによって制御されることである。MN2[n]に例示されるバス-ゲートトランジスタの2つ目の効果は、立ち下がりエッジの開始において相当減少された効果を有する。

40

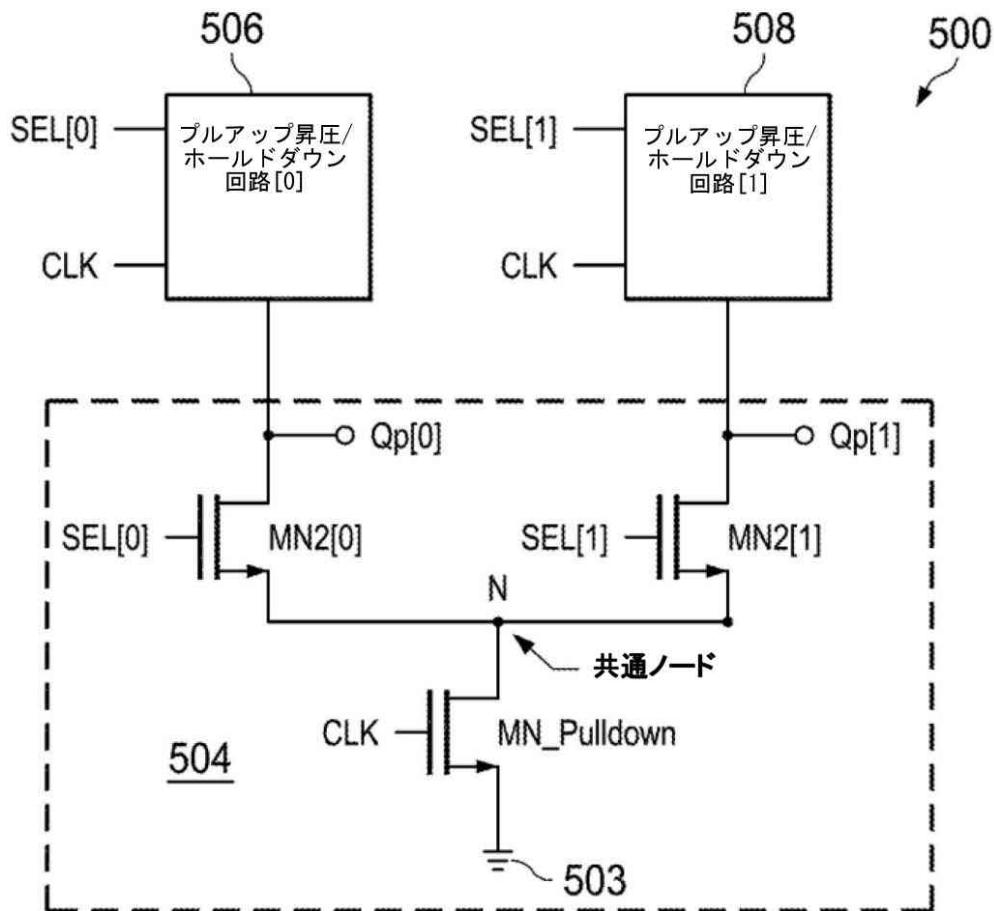

#### 【0043】

ここで図4Aを参照すると、本開示のさらなる実施形態に従うサンプリング回路500が示される。サンプリング回路500は、プルダウン回路504ならびにプルアップ昇圧/ホールドダウン回路506および508を含む。図4Aの実施形態は、2チャネルインターリーブADCのサンプリングクロックを生成するように構成され示されるが、回路は、任意の数のインターリーブチャネルで作動するように拡張されてもよい。サンプリング回路500は、それぞれのサンプリングチャネルに対するプルアップ昇圧/ホールドダウン論理区分506および508を含む。図4Aの実施形態において、プルアップ昇圧/ホールドダウン論理区分506および508は、図4Bに示される実装例に従ってそれぞれ実装され得る。

## 【0044】

10

図4Bを参照すると、図4Aの実施形態のプルアップ昇圧/ホールドダウン回路506および508の一実装例がある。プルアップ昇圧/ホールドダウン回路501は、NANDゲート512、インバーター511、514、および516、MOSトランジスタMNHD、スイッチSB1、SB2、SB3、およびSB4、ならびにコンデンサCB1を含む。論理的に、プルアップ昇圧/ホールドダウン回路501は、OUT出力における電圧が、SELがハイであり、CLKがローであるとき、電圧Vbiasによって供給電圧Vddより上に上昇されるようにプルアップ昇圧回路518に対する制御を生成する。SELがローであるか、またはCLKがハイであるかのいずれかであるとき、プルアップ昇圧回路518は出力OUTから切断され、代わりにコンデンサCB1を電圧VBIASに付勢するように充電する。プルアップ昇圧回路518の目的の1つは、Qp[0]およびQp[1]によって駆動されるサンプリングスイッチを、電圧Vbiasによって供給電圧Vddより上に上昇されたOUT出力における大きいゲート-ソース間電圧(VGS)を使用してオンにすることである。これは、供給電圧が、制限されるかまたは入力信号をサンプリングするために使用されるトランジスタの閾値電圧と比較して小さいときであっても、サンプリングスイッチを駆動する。出力OUTをノード503に連結するように構成されるMNHDを含むホールドダウン回路512は、SELがローであり、MNHDがオンであるときはいつでも出力ノードOUTをロー状態のノード503で保持するように作動され得る。スイッチSB1～SB4の制御信号を作成するために使用される論理は、例示としてのみ示され、ならびに他の機能的に同等のスイッチの制御信号を生成する方法は、本開示の範囲から逸脱することなく使用されてもよいことを理解されたい。

20

## 【0045】

30

図4Aの実施形態において、プルアップ昇圧/ホールドダウン論理506および508は、それぞれのチャネルの適切なサンプリング入力SEL[0]またはSEL[1]をプルアップ昇圧/ホールドダウン回路部分506および508のそれれにおいて、図4Bのプルアップ昇圧/ホールドダウン回路501と同様に実装される回路のSEL入力に接続することによって実装され得る。サンプリング回路500のCLK入力信号は、次いで、それぞれのプルアップ昇圧/ホールドダウン回路部分506および508のCLK入力に接続され得、それぞれのチャネルQp[0]またはQp[1]のサンプリング出力は、プルアップ昇圧/ホールドダウン回路501として実装されるプルアップ昇圧/ホールドダウン回路506または508の適切なOUT端子に接続され得る。そのように実装されるプルアップ昇圧/ホールドダウン回路506および508は、プルダウン回路504とともに、各々サンプリングクロック出力Qp[0]およびQp[1]において、インターリーブチャネル上で順々にサンプリングをトリガするための適切な信号を生成する。

40

## 【0046】

再び図4Aを参照すると、プルダウン回路504は、MOSトランジスタMN\_Pu1down、MN2[0]、およびMN2[1]を含む。プルダウン回路504は、図1Aおよび2のプルダウン回路204およびプルダウン回路304と同様に機能する。図4Aのサンプリング回路500の実施形態に関して、それぞれの信号Qp[0]およびQp[1]は、各々プルアップ昇圧/ホールドダウン論理区分506および508、ならびに入力信号SEL[0]、SEL[1]、およびCLKのサンプリング回路500への適用

50

を通してプルダウン回路 504 によってハイ状態に設定されるように、順々にサイクルされ得る。それぞれのサンプリングクロック Qp[n] は、その各プルアップネットワークによって独立してハイ状態に設定され得る。Qp[n] がハイ状態にあるとき、対応する選択ライン SEL[n] は、ハイレベルであってもよく、一方 CLK はローレベルである。一例として、Qp[0] は、SEL[0] がハイであり、CLK がローであるとき、ハイに設定されてもよい。すべての他のサンプリングクロック出力 Qp[n] は、ロー状態にあってもよく、それらの対応する SEL[n] 入力は、ロー状態に設定される。

#### 【0047】

CLK 入力がロー状態からハイ状態に遷移するとき、プルダウン回路 504 は、MN\_Pull down を通る共通路を通る共通ノード N を介して、MN2[0] または MN2[1] を通して、各々 Qp[0] または Qp[1] をロー状態のノード 503 に引き下げる。例えば、SEL0 がハイ状態にあり、CLK がロー状態からハイ状態に遷移するとき、MN\_Pull down および MN2[0] を通して Qp[0] をロー状態に引き下げる。Qp[0] が下がり始める瞬間は、主にロー状態からハイ状態への CLK の遷移に応答する MN\_Pull down のターンオン特性によって、MN2[0] の閾値電圧よりもはるかに小さい程度までされ得る。同様の方式において、SEL[1] 入力がハイであるとき、Qp[1] は、主にロー状態からハイ状態に遷移する CLK 信号に応答する MN プルダウンによって決定される時間に下がり始める。その時間もまた、MN2[1] トランジスタの閾値電圧よりもはるかに小さい程度まで決定される。これは、すべてのサンプリングクロック出力 Qp[0] または Qp[1] のハイ - ロー間遷移の開始が、主に 1 つの单一トランジスタ MN\_Pull down によって制御されるという点において、本開示の実施形態によって提供される利益を有する。バス - ゲートトランジスタ MN2[0] および MN[1] の 2 つ目の効果は、立ち下がりエッジの開始において相当減少された効果を有する。

#### 【0048】

Qp[0] および Qp[1] によって駆動されるサンプリングスイッチを所定の電圧 Vbias によって、基準電圧、例えば、供給電圧 Vdd より上に上昇される大きいゲート - ソース間電圧 (VGS) を使用してオンにするための図 4A のものといった、実施形態例のいくつかにおける昇圧回路の使用は、供給電圧が制限されるかまたは小さいときであっても、サンプリングスイッチが昇圧電圧によって駆動されるという利益を提供することに留意されたい。供給電圧が制限されるかまたは入力信号のサンプリングに使用されるトランジスタの閾値電圧と比較して小さいとき、これはサンプリングスイッチが駆動され、それぞれのチャネルからサンプルが得られるとき、正確なサンプルを提供することを確実にする。

#### 【0049】

ここで図 5 を参照すると、本開示の別の実施形態例が示される。図 5 は、プルダウン回路 604 ならびにプルアップ昇圧 / ホールドダウン回路 606 および 608 を含むサンプリング回路 600 を図示する。サンプリング回路 600 の実施形態において、プルアップ昇圧 / ホールドダウン回路 608 は、昇圧コンデンサ CB1[1] およびスイッチ SB3[1] を含み、プルアップ昇圧 / ホールドダウン回路 606 は、昇圧コンデンサ CB1[0] およびスイッチ SB3[0] を含む。それぞれの昇圧コンデンサ CB1[0] および CB1[1] の下板は、プルダウン回路 604 と並列で作動するプルダウンネットワークに接続され得る。図 5 のそれぞれのチャネルサンプリングクロック出力 Qp[n] (n = 0, 1) の並列プルダウン回路は、SEL[n] に接続されるそのゲートおよび共通プルダウンノード N に接続されるそのソースを有する NMOS トランジスタ MBS T[n] を含む。MBS T[n] のドレインは、昇圧コンデンサ CB1[n] の下板に接続され得る。この並列プルダウン構成は、サンプルクロック Qp[n] の立ち下がりエッジが、主要プルダウントランジスタ MN\_Pull down によってのみ決定される時間に開始することを確実にする。共通ノード N とそれぞれの Qp[n] との間に 2 つの伝播経路が存在する。直接 MN2[n] を通り、Qp[n] を共通ノード N に連結するように構成される

10

20

30

40

50

もの、およびM B S T [ n ]、昇圧コンデンサC B 1 [ n ]を通り、最終的には、プルアップ昇圧／ホールドダウン区分606または608内のスイッチS B 3 [ n ]を通るもの。両方の経路は、C L K信号を用いてM N \_ P u l l d o w nをオンにすることによって同時に起動される。M N \_ P u l l d o w nは、共通ノードNをノード601に連結するように構成される。共通ノードNは、M N \_ P u l l d o w nがハイ状態にあるC L Kによってオンにされるとき、ロー状態のノード601に設定される。

#### 【0050】

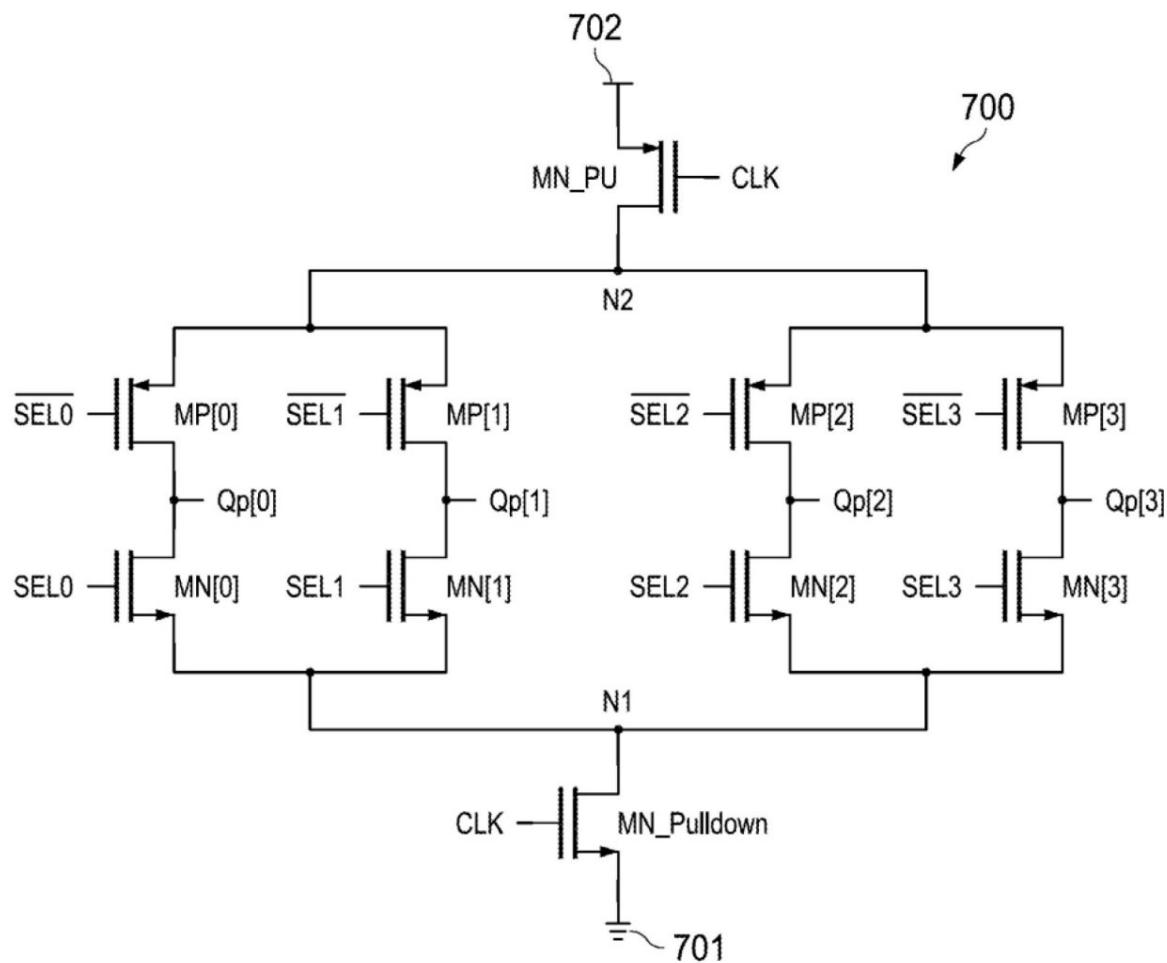

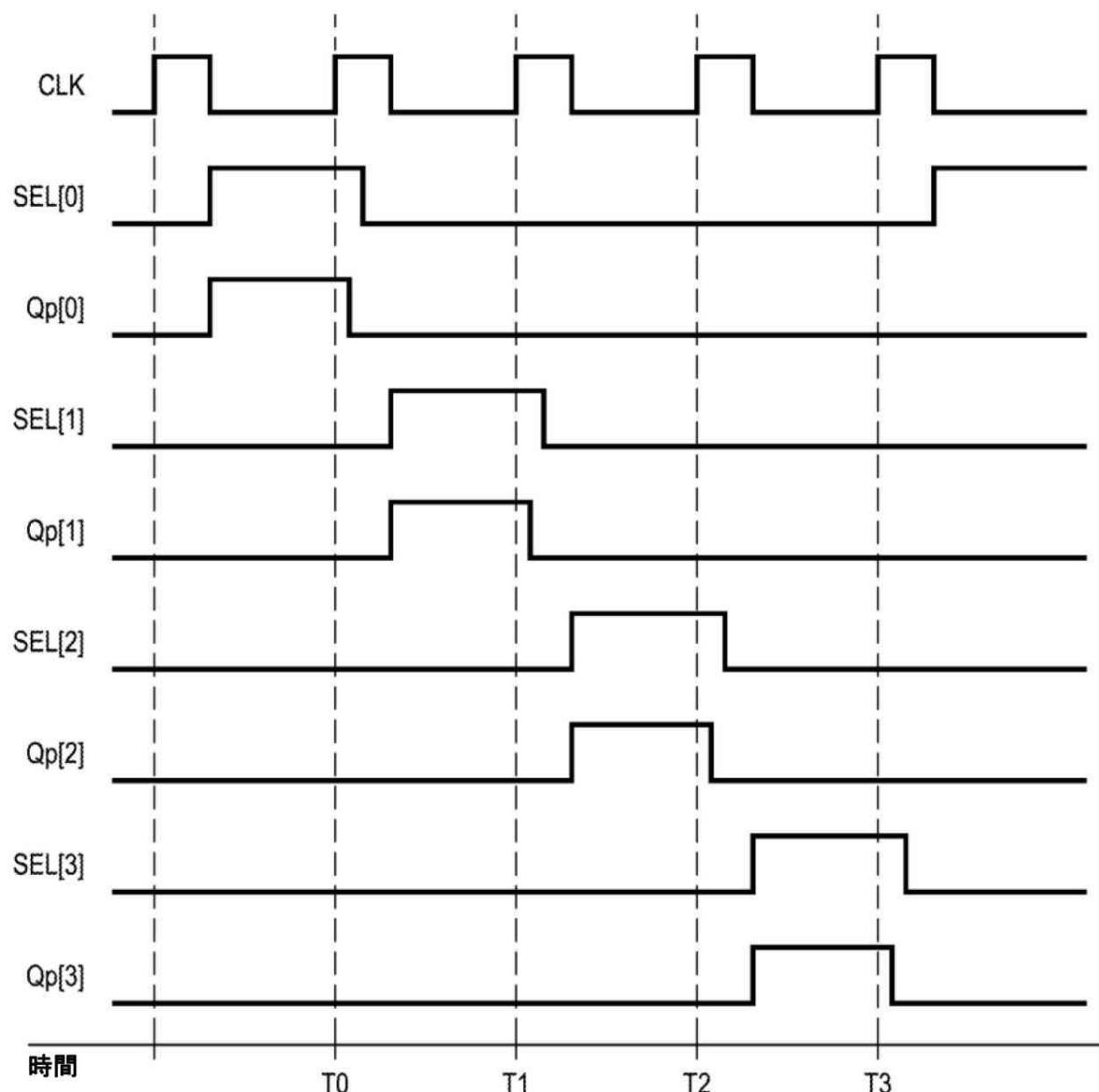

ここで図6Aおよび6Bを参照すると、図6Aは、本開示の別の実施形態に従うサンプリング回路700を図示し、図6Bは、サンプリング回路700の入力および出力信号として使用され得る波形の例を図示する。サンプリング回路700は、4つのサンプリングクロックQ p [ 0 ] ~ Q p [ 3 ]を生成する。一実施形態において、サンプリング回路700は、4チャネルインターリープA D Cのサンプリングクロック信号を生成し得る。サンプリング回路700は、M O SトランジスタM N [ 0 ]、M N [ 1 ]、M N [ 2 ]、M N [ 3 ]、およびM P [ 0 ]、M P [ 1 ]、M P [ 2 ]、M P [ 3 ]、M N \_ P U、ならびにM N \_ P u l l d o w nを含む。入力信号S E L 0、S E L 1、S E L 2、およびS E L 3は、サンプリング入力であり、そこから回路700は、インターリープチャネルA D CのQ p [ 0 ]、Q p [ 1 ]、Q p [ 2 ]、およびQ p [ 3 ]を生成する。サンプリング回路700の入力波形の例は、図6Bに示される。Q p [ 0 ]、Q p [ 1 ]、Q p [ 2 ]、およびQ p [ 3 ]のそれぞれに出力が、S E L 0、S E L 1、S E L 2、およびS E L 3のそれぞれが各々順々にハイ状態に動くとき、時間インターリープA D Cの4つの各チャネルのうちの1つの上でサンプリングできるように、それぞれハイ状態に駆動されることが、図6Bから分かる。ロー状態からハイ状態へのC L K信号入力の遷移は、先の実施形態に関して記載されたように、出力サンプリングクロックQ p [ 0 ]、Q p [ 1 ]、Q p [ 2 ]、およびQ p [ 3 ]のそれぞれがハイ状態からロー状態に遷移するとき、Q p [ 0 ]、Q p [ 1 ]、Q p [ 2 ]、およびQ p [ 3 ]の立ち下がりエッジを制御し、得られるサンプルをトリガする。例えば、S E L 0がハイ状態にあり、C L KがT 0でハイ状態に遷移するとき、M N \_ P u l l d o w nをオンにするC L K立ち上がりエッジの作用によって、M N [ 0 ]、共通ノードN 1、およびM N \_ P u l l d o w nを通してQ p [ 0 ]をロー状態のノード701に引く。このロー状態への引き下げはまた、S E L 1、S E L 2、およびS E L 3としてのQ p [ 1 ]、Q p [ 2 ]、およびQ p [ 3 ]の立ち下がりエッジのそれぞれが、それぞれ順々にハイに設定され、C L Kパルスがサンプリング回路700に入力され、時間T 1、T 2、およびT 3でロー状態からハイ状態に遷移することによっても起こる。Q p [ 0 ]、Q p [ 1 ]、Q p [ 2 ]、およびQ p [ 3 ]の立ち下がりエッジ間のタイミング不整合は、次いで最小化される。図6Aの出力Q p [ n ]のそれぞれについて、トランジスタM P [ n ]およびM N \_ P U、ならびに共通ノードN 2のそれぞれを含むプルアップ回路を使用して、M N \_ P u l l d o w nをオンにするC L Kによってサンプリングがトリガされる前に、M P [ n ]、共通ノードN 2、およびM N \_ P Uを通して、Q p [ n ]をハイ状態のノード702に引く。

#### 【0051】

上記の実施形態の考察において、例えば、N M O Sトランジスタの場合のように、スイッチおよびトランジスタは、制御信号がハイであるときはオンであると見なされ、制御信号がローであるときはオフであると見なされる。しかしながら、補助的スイッチおよび補助的駆動レベルの使用が、スイッチを実装するための同様に実行可能な選択肢であることに留意されたい。つまり、P M O Sトランジスタは、補助的ゲート駆動回路を有するN M O Sトランジスタで置き換えられてもよく、N M O SおよびP M O Sトランジスタの両方は、制御信号の両極を使用して並列で使用され得る。また本実施形態は特定の数のサンプリングチャネルを用いてそれぞれ示されたが、当業者は、本実施形態が任意の数のインターリープチャネルへの応用を有することを理解するであろう。

#### 【0052】

図を参照して上記で考察される作業は、信号処理を含む任意の集積回路、特にそれらの

10

20

30

40

50

一部がデジタル化リアルタイムデータの処理に関連付けられる専門ソフトウェアプログラム、またはアルゴリズムを実行するものに応用可能であることに留意せよ。ある特定の実施形態は、マルチDSP信号処理、浮動小数点処理、信号／制御処理、固定機能処理、マイクロコントローラ用途等に関するものよい。

#### 【0053】

ある特定の状況において、本明細書で考察される機能は、医療システム、科学装置、無線および優先通信、レーダー、産業用プロセス制御、音響および映像機器、電流検出、計測（それは高精度であり得る）、ならびに他のデジタル処理ベースのシステムに応用可能である。

#### 【0054】

さらに、上記で考察されるある特定の実施形態は、医用画像、患者の監視、医療機器、および在宅医療に関するデジタル信号処理技術において供給され得る。これは、肺用モニター、加速度計、心拍数モニター、ペースメーカー等を含み得る。他の用途には、安全システム（例えば、安定制御システム、運転者支援システム、ブレーキシステム、インフォテインメント、および任意の種類の内装用途）のための自動車用技術を含む。さらに、パワートレインシステム（例えば、ハイブリッドおよび電気自動車における）は、電池監視、制御システム、報告制御、維持作業等における高精度データ変換製品を使用することができる。

#### 【0055】

さらに他のシナリオ例において、本開示の教示は、生産性、エネルギー効率、および信頼性を高めることを補助するプロセス制御システムを含む産業市場において応用可能である。消費者用途において、上記で考察される信号処理回路の教示は、（例えば、デジタルスチルカメラ、カムコーダー等の）画像処理、自動焦点、画像安定化に使用されてもよい。他の消費者用途には、ホームシアターシステム、DVDレコーダー、および高解像度テレビのための音声および映像プロセッサを含み得る。さらに他の消費者用途には、（例えば、任意の種類の携帯用媒体装置のための）先進タッチスクリーンコントローラを含む。したがって、そのような技術は、容易にスマートフォン、タブレット、セキュリティーシステム、PC、ゲーム技術、仮想現実、シミュレーション訓練等の部分となり得る。

#### 【0056】

一実施形態例において、図の任意の数の電気回路は、関連する電子機器のマザーボード上に実装され得る。マザーボードは、電子機器の内部電子システムの種々の部品を保持し得る一般的な回路基板であってもよく、さらに、他の周辺機器のコネクタを提供する。より具体的には、マザーボードは、電気的接続を提供することができ、それによりシステムの他の部品が電気的に通信することができる。任意の好適なプロセッサ（デジタル信号プロセッサ、マイクロプロセッサ、サポートチップセット等を含む）、記憶素子等は、特定の構成の必要性、処理要求、コンピュータ設計等に基づくマザーボードに好適に連結され得る。外部記憶装置、追加センサ、音響／映像ディスプレイ用のコントローラ、および周辺機器等の他の部品は、ケーブルを介して、プラグインカードとしてマザーボードに取り付けられるか、またはマザーボード自体に一体化され得る。

#### 【0057】

別の実施形態例において、図の電気回路は、独立型モジュール（例えば、特定の用途または機能を実施するように構成される関連する部品および／または回路を有する装置）として実装され得るか、またはプラグインモジュールとして電子機器の特定用途向けハードウェア内に実装され得る。本開示の特定の実施形態は、システムオンチップ（SOC）パッケージ中に、部分的または全体的に容易に含まれ得ることに留意せよ。SOCは、コンピュータまたは他の電子システムの部品を单一チップに一体化するICを表す。それは、デジタル、アナログ、混合信号、およびしばしばラジオ周波数機能を含み、それらのすべては、单一チップ基板上に提供され得る。他の実施形態は、単一の電子パッケージ内に位置し、電子パッケージを通して互いに密接に相互に作用する構成される複数の独立したICを有するマルチチップモジュール（MCM）を含み得る。様々な他の実施形態において

10

20

30

40

50

、増幅機能性は、特定用途向け集積回路（A S I C）、フィールドプログラマブルゲートアレイ（F P G A）、および他の半導体チップ中の1つ以上のシリコンコア内に実装され得る。

#### 【 0 0 5 8 】

本明細書に概説される仕様、寸法、および関係（例えば、プロセッサおよび記憶素子の数、論理動作等）のすべては、例および教示のみを目的として提供されたに過ぎないことに留意することがまた肝要である。そのような情報は、本開示の趣旨または添付される特許請求の範囲から逸脱することなく、大幅に変化されてもよい。本明細書は、非限定的な一つの例にのみ適用され、したがって、それらはそのように解釈されるべきである。前述の説明において、実施形態例は、特定のプロセッサおよび／または部品配置を参照して記載された。種々の改良および変更が、添付の特許請求の範囲から逸脱することなく、そのような実施形態に行われてもよい。説明および図面は、したがって、限定的な意味ではなく、例示であると見なされるべきものである。10

#### 【 0 0 5 9 】

本明細書に提供される多数の例を参照して、相互作用は、2つ、3つ、4つ以上の電気部品について記載されることに留意せよ。しかしながら、これは明確さおよび例示の目的でのみ行われたものである。システムは、いかなる好適な手段で統合されてもよいことを理解されたい。類似の設計の代替案に沿って、図の例示される部品、モジュール、および要素のいずれかは、種々の可能な構成において組み合わせられてもよく、それらのすべては、明らかに本明細書の広範囲内である。ある特定の場合において、限定された数の電気素子を参照することによってのみ、流れの所与の設定の機能性の1つ以上を説明することはより容易であり得る。図の電気回路およびその教示は、容易に拡張可能であり、多数の部品、ならびにより複雑な／高機能の配置および構成に適応できることを理解されたい。したがって、提供される例は、無数の他のアーキテクチャに潜在的に適用される電気回路の範囲を制限するべきではなく、またはその教示の範囲を阻害するべきではない。20

#### 【 0 0 6 0 】

本明細書において、「一つの実施形態」、「実施形態例」、「一実施形態」、「別の実施形態」、「一部の実施形態」、「種々の実施形態」、「他の実施形態」、「代替的実施形態」等に含まれる様々な特徴（例えば、要素、構造、モジュール、部品、ステップ、動作、特性等）の参照は、任意のそのような特徴は、本開示の1つ以上の実施形態に含まれるが、同じ実施形態において必ず組み合わせられてもよく、またはそうでなくてもよいことを意味することが意図されることに留意する。30

#### 【 0 0 6 1 】

多数の他の変更、置換え、変形、修正、および改良は、当業者に理解され、本開示が、添付の特許請求の範囲の範囲内であるとしてすべてのそのような変更、置換え、変形、修正、および改良を包含することが意図される。本明細書に添付される特許請求の範囲の解釈について、米国特許商標局（U S P T O）、加えて、本出願において交付された任意の特許の任意の読者を援助するために、出願人は、出願人が、（a）添付される特許請求の範囲のいずれかが、用語「のための手段」または「のためのステップ」が特定の特許請求の範囲内で具体的に使用されない限り、本明細書の出願日に存在した米国特許法第112節の第6項を発動することを意図せず、および（b）本明細書中のいかなる記載によっても、添付される特許請求の範囲に反映されない限り、決して本開示を制限することを意図しないことを留意することを望む。40

【図 1 A】

【図 1 B】

【図 2】

【図3A】

【図3B】

【図4A】

【図4B】

【図5】

【図 6 A】

【図 6 B】

---

フロントページの続き

(72)発明者 デヴァラジヤン, シッダース

アメリカ合衆国 マサチューセッツ州 02474、アーリントン、ビーコン ストリート 53

審査官 柳下 勝幸

(56)参考文献 特表2002-500461(JP, A)

特開2002-135117(JP, A)

米国特許出願公開第2010/0207792(US, A1)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00 - 1/88

H03F 3/70