(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3848620号

(P3848620)

(45) 発行日 平成18年11月22日(2006.11.22)

(24) 登録日 平成18年9月1日(2006.9.1)

(51) Int.C1.

F 1

|                |                |                  |         |       |         |

|----------------|----------------|------------------|---------|-------|---------|

| <b>G 1 1 C</b> | <b>11/22</b>   | <b>(2006.01)</b> | G 1 1 C | 11/22 | 5 0 1 A |

| <b>H 0 1 L</b> | <b>27/105</b>  | <b>(2006.01)</b> | G 1 1 C | 11/22 | 5 0 1 F |

| <b>H 0 1 L</b> | <b>21/8246</b> | <b>(2006.01)</b> | G 1 1 C | 11/22 | 5 0 1 K |

|                |                |                  | HO 1 L  | 27/10 | 4 4 4 C |

請求項の数 13 (全 16 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2002-529782 (P2002-529782)  |

| (86) (22) 出願日 | 平成13年8月24日 (2001.8.24)        |

| (65) 公表番号     | 特表2004-510283 (P2004-510283A) |

| (43) 公表日      | 平成16年4月2日 (2004.4.2)          |

| (86) 國際出願番号   | PCT/N02001/000348             |

| (87) 國際公開番号   | W02002/025665                 |

| (87) 國際公開日    | 平成14年3月28日 (2002.3.28)        |

| 審査請求日         | 平成15年2月21日 (2003.2.21)        |

| (31) 優先権主張番号  | 2000 4236                     |

| (32) 優先日      | 平成12年8月24日 (2000.8.24)        |

| (33) 優先権主張国   | ノルウェー (NO)                    |

|           |                                                                                |

|-----------|--------------------------------------------------------------------------------|

| (73) 特許権者 | 500034413<br>シン フィルム エレクトロニクス エイ<br>エスエイ<br>ノルウェー国、オスロ、バイカ、ビー、<br>オー、ボックス 1872 |

| (74) 代理人  | 100066692<br>弁理士 浅村 皓                                                          |

| (74) 代理人  | 100072040<br>弁理士 浅村 肇                                                          |

| (74) 代理人  | 100118821<br>弁理士 祖父江 栄一                                                        |

| (74) 代理人  | 100094673<br>弁理士 林 銀三                                                          |

最終頁に続く

(54) 【発明の名称】不揮発性受動マトリックス装置および同装置の読み出し方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ヒステリシスを呈している電気的に分極可能な誘電記憶材料(12)、特に強誘電性材料を含む不揮発性受動マトリックス記憶装置(10)であって、前記記憶材料(12)が、並列なアドレッシング電極の対応する第1の組と第2の組(14、15)の間の層に挟まれ、前記第1の組(14)の電極が前記記憶装置のワード線(WL<sub>1</sub>からWL<sub>m</sub>)を構成し、前記第2の組(15)の電極と実質的に直交する関係に置かれ、前記第2の組が、前記記憶装置のビット線(BL<sub>1</sub>からBL<sub>n</sub>)を構成し、蓄電器のような構造をした記憶セル(13)が前記ワード線と前記ビット線の交点において前記記憶材料(12)において定義され、前記記憶装置の前記記憶セル(13)が受動マトリックス(11)の構成要素を構成し、各前記記憶セル(13)を前記ワード線(WL)と前記ビット線(BL)を通して、書き込み/読み取り操作のために選択的にアドレスすることができ、前記記憶セルへの書き込み操作が、前記記憶セルを定義している対応する前記ワード線(WL)および前記ビット線(BL)を通して前記記憶セルに適用される電圧により前記記憶セル内に好ましい分極状態を確立することによって実行され、前記電圧が、前記記憶セルにおける分極状態を決定するかあるいは前記記憶セルの分極状態を交互に切り換えることができ、読み取り操作が、強制電圧V<sub>c</sub>より大きい電圧を前記記憶セルに適用し、前記ビット線(BL)上の出力電流の少なくともひとつを検知することにより実行される、不揮発性受動マトリックス記憶装置(10)であって、前記ワード線(WL)が複数のセグメント(S)に分割され、当該各セグメントが前記マトリックス(11)における隣接

する複数の前記ビット線 (B L) を有しまたそれらによって定義され、前記セグメント (S) に割り当てられた各前記ビット線 (B L) を対応する感知手段 (26) に接続する手段 (25) が備えられ、そのことにより前記セグメント (S) 上の前記ワード線 (W L) に割り当てられた全ての前記記憶セル (13) を前記セグメント (S) の対応する前記ビット線 (B L) を通して読み出すために同時に接続することができ、各前記感知手段 (26) が当該感知手段に接続するビット線 (B L) における電荷の流れを感知するように適合され、前記ビット線によって定義された前記記憶セル (13) に記憶された論理値を決定することを特徴とする、不揮発性受動マトリックス記憶装置。

【請求項 2】

請求項 1 に記載の不揮発性受動マトリックス記憶装置 (10) であって、アドレス中に上記セグメント (S) の各上記ビット線 (B L) を関連する上記感知手段 (26) に同時に接続する上記手段 (25) が、マルチブレクサであることを特徴とする、不揮発性受動マトリックス記憶装置。 10

【請求項 3】

請求項 2 に記載の不揮発性受動マトリックス記憶装置 (10) であって、上記マルチブレクサ (25) の数が上記セグメント (S) を定義している上記ビット線 (B L) の最大数に対応し、上記セグメントの各上記ビット線が特定の上記マルチブレクサに接続していることを特徴とする、不揮発性受動マトリックス記憶装置。

【請求項 4】

請求項 3 に記載の不揮発性受動マトリックス記憶装置 (10) であって、各上記マルチブレクサの出力が、ひとつの上記感知手段 (26) に接続していることを特徴とする、不揮発性受動マトリックス記憶装置。 20

【請求項 5】

請求項 4 に記載の不揮発性受動マトリックス記憶装置 (10) であって、ひとつの上記感知手段 (26) が、感知増幅器であることを特徴とする、不揮発性受動マトリックス記憶装置。

【請求項 6】

請求項 1 に記載の不揮発性受動マトリックス記憶装置 (10) であって、アドレス中に、上記セグメント (S) の各上記ビット線 (B L) を関連する上記感知手段 (26) に同時に接続する上記手段 (25) が、ゲート手段であることを特徴とする、不揮発性受動マトリックス記憶装置。 30

【請求項 7】

請求項 6 に記載の不揮発性受動マトリックス記憶装置 (10) であって、上記セグメント (S) の全ての上記ビット線 (B L<sub>1</sub> から B L<sub>n</sub>) が特定の上記ゲート手段に接続され、各上記ゲート手段がそれぞれの上記セグメント (S) における上記ビット線 (B L) の数に対応する数の出力を有し、各上記ゲート手段 (25) の各前記出力が出力データ・バス (28) の特定のバス線 (27) に接続し、前記バス線 (27) の数が上記セグメント (S) における上記ビット線 (B L) の最大数に対応し、各前記バス線 (27) がひとつの上記感知手段 (26) に接続していることを特徴とする、不揮発性受動マトリックス記憶装置。 40

【請求項 8】

請求項 6 に記載の不揮発性受動マトリックス記憶装置 (10) であって、上記ゲート手段 (25) が通過ゲートを含むことを特徴とする、不揮発性受動マトリックス記憶装置。

【請求項 9】

請求項 6 に記載の不揮発性受動マトリックス記憶装置 (10) であって、上記感知手段 (26) が感知増幅器であることを特徴とする、不揮発性受動マトリックス記憶装置。

【請求項 10】

ヒステリシスを呈している電気的に分極可能な誘電記憶材料 (12) 、特に強誘電性材料を含む不揮発性受動マトリックス記憶装置 (10) であって、前記記憶材料 (12) が、並列なアドレッシング電極の対応する第 1 の組と第 2 の組 (14、15) の間の層に挟 50

まれ、前記第1の組(14)の電極が前記記憶装置(10)のワード線(WL)を構成し、前記第2の組(15)の電極と実質的に直交する関係に置かれ、前記第2の組が、前記記憶装置(10)のビット線(BL<sub>1</sub>からBL<sub>n</sub>)を構成し、蓄電器のような構造をした記憶セル(13)が前記ワード線と前記ビット線(BL)の交点において前記記憶材料(12)において定義され、前記記憶装置(10)の前記記憶セル(13)が受動マトリックス(11)の構成要素を構成し、各前記記憶セル(13)を前記ワード線(WL)と前記ビット線(BL)を通して、書き込み/読み取り操作のために選択的にアドレスすることができ、前記記憶セルへの書き込み操作が、前記記憶セルを定義している対応する前記ワード線(WL)および前記ビット線(BL)を通して前記記憶セルに適用される電圧により前記記憶セル内に好ましい分極状態を確立することによって実行され、前記電圧が、前記記憶セルにおける分極状態を決定するかあるいは前記記憶セルの分極状態を交互に切り換えることができ、読み取り操作が、強制電圧V<sub>c</sub>より大きい切り換え電圧V<sub>s</sub>を前記記憶セルに適用し、前記ビット線(BL)上の出力電流の少なくともひとつを電気パラメータを検知することにより実行される不揮発性受動マトリックス記憶装置のための読み出し方法であって、当該方法が、全ての前記ワード線および前記ビット線のための電気タイミング順序を有するプロトコルに従った時間調整により全ての前記ワード線(WL)および全ての前記ビット線(BL)における電位を制御するステップと、前記プロトコルが読み取りサイクルを含むよう調整するステップと、前記読み取りサイクル間前記感知手段が前記ビット線における電位の流れを感知するよう調整するステップと、を含み、前記ワード線(WL)が複数のセグメント(S<sub>1</sub>からS<sub>q</sub>)に分割され、当該各セグメントが前記マトリックス(11)における隣接する複数の前記ビット線(BL)を有しましたそれらによって定義され、前記ワード線セグメント(S)内の各前記ビット線(BL)を対応する感知手段(26)に接続し、前記プロトコルに従って、一時にひとつの前記ワード線(WL)を、前記セグメント(S)の当該ひとつのワード線の電位を前記読み取りサイクルの少なくともある時間切り換え電圧V<sub>s</sub>に設定することによって活性化し、その間前記セグメントの全ての前記ビット線をゼロ電位に保持し、前記読み取りサイクルの間に前記感知手段(26)によって感知された前記個々の記憶セル(13)に記憶された論理値を決定することを特徴とする、読み出し方法。

10

20

30

#### 【請求項11】

請求項10に記載の読み出し方法であって、全ての上記ワード線(WL)および上記ビット線(BL)を、どの上記記憶セル(13)も読み書きされていないとき、切り換え電圧V<sub>s</sub>の約3分の1の静止電圧に保持し、上記プロトコルに従って、一時にひとつの上記ワード線(WL)を、上記セグメント(S)の当該ひとつのワード線の電位を上記読み取りサイクルの少なくともある時間切り換え電圧V<sub>s</sub>に設定することによって活性化し、その間上記セグメントの全ての上記ビット線(BL)をゼロ電位に保持し、上記読み取りサイクルの間に上記感知手段(26)によって感知された上記個々の記憶セル(13)に記憶された論理値を決定することを特徴とする、読み出し方法。

30

#### 【請求項12】

複数のスタック層(P<sub>1</sub>, P<sub>2</sub>...)を有し、当該各層(P)が、請求項1に記載の不揮発性受動マトリックス記憶装置(10)のひとつを有する立体的データ記憶装置。

40

#### 【請求項13】

複数のスタック層(P<sub>1</sub>, P<sub>2</sub>...)を有し、当該各層(P)が、請求項10に記載の読み出し方法を使用した不揮発性受動マトリックス記憶装置(10)のひとつを有する立体的データ記憶装置の読み出し方法。

50

#### 【発明の詳細な説明】

#### 【0001】

本発明は、不揮発性受動マトリックス記憶装置に関する。この記憶装置は、ヒステリシスを呈している、電気的に分極可能な誘電記憶材料、特に強誘電性材料、を含んでいる。この記憶材料は、並列なアドレッシング電極の対応する第1の組と第2の組の間の層に挟まれている。第1の組の電極は、記憶装置のワード線を構成し、第2の組の電極と実質的

に直交する関係に置かれている。第2の組は、記憶装置のビット線を構成している。蓄電器のような構造をした記憶セルは、ワード線およびビット線の交点において記憶材料において定義される。記憶装置の記憶セルは、受動マトリックスの構成要素を構成し、各記憶セルは、ワード線とビット線を通して、書き込み／読み取り操作のために選択的にアドレスされることができる。記憶セルへの書き込み操作は、セルを特定する、対応するワード線およびビット線を通してセルに与えられる電圧によりセル内に好ましい分極状態を確立することによって、実行される。この電圧は、記憶セルにおける分極状態を決定するか、あるいは、記憶セルの分極状態を交互に切り換えることができる。読み取り操作は、強制電圧  $V_c$  より大きい切り換え電圧  $V_s$  を記憶セルに適用し、ビット線上の出力電流の少なくともひとつの電気パラメータを検知することにより、実行される。

10

また、本願発明はこの種のメモリデバイスを読み出すための方法に関する。

#### 【0002】

本発明は、また、立体的(volumetric)データ記憶装置における、不揮発性受動マトリックス記憶装置の使用に関する。

#### 【0003】

強誘電集積回路は、従来の技術に比較して、革命的な特質を持っている。不揮発性情報記憶装置、特にマトリックス・メモリを含む応用は、スピードが速く、実質的に耐久性に限度がなく、書き込み速度が速い。これらの特質は、近年希望されたが実現できなかったものである。

#### 【0004】

強誘電マトリックス・メモリは、ふたつの型に分けることができる。ひとつの型は、記憶セルにリンクされた活動的な要素を有し、他の型は活動的な要素を有しない。これらのふたつの型を以下に説明する。

20

#### 【0005】

アクセス・トランジスタのような活動的なアクセス要素を持たない、強誘電蓄電器の形の記憶セルを有する強誘電マトリックス記憶装置は、片側に配置された1組の並列な導電電極（“ワード線”）と、他の側に配置された実質的に直交する1組の導電電極（“ビット線”）を有する薄い強誘電フィルムを有している。この構成は、以下に“受動マトリックス・メモリ”と呼ぶ。受動マトリックス・メモリにおいて、各強誘電記憶セルは、記憶セルを有する記憶マトリックスを構成している相反する電極の交点において形成される。記憶マトリックスは記憶セルを有し、記憶セルは、マトリックスの端からの適当な電極の選択的な駆動によって個別的にアクセスすることができる。

30

#### 【0006】

マトリックス・メモリを形成する他の方法として、各強誘電記憶セルを、通常強誘電蓄電器と直列に活動的要素、通常はアクセス・トランジスタを含ませることによって、変更することである。アクセス・トランジスタは、蓄電器へのアクセスを制御し、例えば近接する記憶セルからの、望ましくない妨害信号を遮る。記憶セルは、通常、強誘電蓄電器、およびワード線にゲートを接続したnチャネル金属酸化膜半導体電界効果トランジスタ（以下において、簡略化のためn型あるいはp型を示さずに単に“MOSFET”と呼ぶ）を含む。MOSFETのソース／ドレイン領域は、ビット線に接続している。強誘電蓄電器のひとつの電極は、MOSFETのソース／ドレイン領域に接続し、蓄電器の他の電極は、いわゆる“ドライブ線”に接続している。これは、従来の概念であり、しばしばひとつのトランジスタ、ひとつの蓄電器（1T-1C）記憶セルとして提供されている。2つ以上のトランジスタを含む他の概念も周知である。しかし、これらの概念は、受動マトリックス・メモリと比較してトランジスタの数が多くなり、複雑さや消費電流が増し、一定の領域における記憶セルの数が少なくなるなどの、多くの欠点がある。以下に、これらの型の装置を、“活動的”要素、つまり各記憶セルにあるトランジスタのために、“活動的”マトリックス・メモリと呼ぶ。

40

#### 【0007】

本発明は、しかし、記憶セルに局所的に関連するダイオードあるいはトランジスタのよう

50

な活動的要素を持たない、受動マトリックス・メモリにのみに関する。

【0008】

受動マトリックス・メモリにおける読み書き操作は、いわゆる“部分的ワード・アドレッシング”という方法によって実行することができる。この方法では、ある部分のみ、通常所定のワード線上の記憶セルのひとつが読み書きされる。このような部分的読み書き操作を実行するために、活性化されていないワード線あるいはビット線上のアドレスされていないセルは、アドレスされていないセルの部分的切り換えを防ぐために、いわゆる“パルシング・プロトコル”に従って、電圧バイアスされる。パルシング・プロトコルの選択は多くの要素に依存し、ヒステリシスを呈している強誘電性記憶材料を含む応用に関する様々な構成が文献において発表されている。このことは、例えば、本出願と関連する、2000年7月7日出願のノルウェー特許出願第20003508号に記述されている。この出願は、受動マトリックス・メモリのためのプロトコルを記述している。一方、アドレスされていないセルのバイアスは、通常、妨害電圧を発生させ、そのため記憶内容が喪失し、あるいは、ここでは“スニーカー(sneak)電流”と呼ぶ、漏洩電流および他の寄生電流が発生することがある。スニーカー電流は、アドレスされた記憶セルの電流を、読み書き操作中にマスクすることができ、それにより、読み取り操作中にデータ内容をマスクすることができる。問題となっている装置の型によって、スニーカー電流を取り消す方法のような、アドレスされていない記憶セルの妨害を防ぐ、あるいは少なくとも減少させる基準を定義することができる。他の方法として、マトリックス内の各セルの小信号妨害に対する感度を下げる方法がある。この方法は、閾値処理、整流あるいは様々な形式のヒステリシスを含む、非線形電圧電流反応を呈するセルによって実現することができる。

【0009】

活動的および受動的強誘電記憶装置の双方の性能を改善するため、例えば電力要求を減らすために、記憶マトリックスは内部的に、小さなブロック、いわゆる“セグメント”に、分割すなわち“セグメンテーション”することができる。通常このセグメンテーションは、利用者には意識されない。セグメンテーションを行う他の理由は、強誘電蓄電器がいわゆる“疲労”を起こす問題があることである。“疲労”とは、強誘電蓄電器が、何回も例えば何百万回も切り換えられると、残留する分極を維持することができず、機能を停止してしまうことである。この特定の問題の解決策は、蓄電器の1列が全部切り換わるのを防ぐために、マトリックスのセグメントをより小さくすることである。このことは、例えば、米国特許第5,567,636号に開示されている。セグメントされた記憶マトリックスを記述した他の文献として、コロラド・スプリングスのセリス・セミコンダクタ・コーポレーション、ゲイリー・F・ダーベンウィックその他のによる“宇宙応用のための不揮発性強誘電性メモリ”がある。この文献は、ひとつのトランジスタおよびひとつの蓄電器記憶セル構造(1T、1C)を使用した活動的マトリックスにおける電力要求を減少させることができる、セグメントされたメモリ・マトリックスを記述している。

【0010】

強誘電性記憶材料を使用している受動マトリックス・メモリの例は、40年から50年前の文献に遡って見つけることができる。例えば、W. J. マーツおよびJ. R. アンダーソンは1955年に、バリウム・チタンエステルに基づくメモリを記述している(W. J. マーツおよびJ. R. アンダーソンによる“強誘電記憶装置”ベル・ラブ・レコード1、335-342ページ(1955))。また、同様な技術がその後すぐに報告されている(例えば、C. F. プルバリによる“強誘電およびそれらの記憶装置への応用”、IREトランザクションCP-3、3-11ページ(1956)、およびD. S. キャンベルによる“バリウム・チタンエステルおよび記憶装置としてのその使用”、J. ブリット・IRE 17(7)、385-395ページ(1957))。受動マトリックス・メモリの他の例は、IBMテクニカル・ディスクロージャ・ブルテン、Vol. 37、No. 11、1994年11月号に見ることができる。しかし、これらの文献のいずれも、アドレスされていないセルの妨害問題に対する解決策を記述していない。

【0011】

この問題に対する他の対処法は、正方形をしたヒステリシス・ループを形成するように強誘電性材料を調整することである。しかし、この方法も詳細に記述されたことがない。

#### 【0012】

従って、アドレスされていないセルの妨害問題のような、上記の否定的特徴を持たない、受動マトリックス・メモリの必要がある。

#### 【0013】

上記記述に照らして、本発明の目的は、アドレスされていない記憶セルの妨害に関する問題を解決する、受動マトリックス記憶装置を提供することである。本発明の他の目的は、記憶されたデータを読み取る間の、アドレスされていないセルからの累積する信号の影響を最小にする、受動マトリックス記憶装置を提供することである。さらに、上記目的とも10両立する受動マトリックス記憶装置における読み出し方法を提供することも、本発明の目的である。

#### 【0014】

上記目的およびさらなる有利な点および特徴は、本発明による不揮発性受動メモリ・マトリックス装置によって実現される。本メモリ・マトリックス装置は、ワード線が複数のセグメントに分割されていることを特徴とする。各セグメントはマトリックス内の複数の隣接するビット線を有し、それらによって定義されている。セグメントに割り当てられた各ビット線を関連する感知手段に接続する手段が提供され、それによって、セグメントの対応するビット線を通して読み出すため、セグメントにおけるワード線に割り当てられた全ての記憶セルを同時に接続することが可能となる。各感知手段は、ビット線によって定義された記憶セルに記憶された論理価値を決定するために、感知手段に接続されたビット線における電位の流れを感知するよう適合されている。20

#### 【0015】

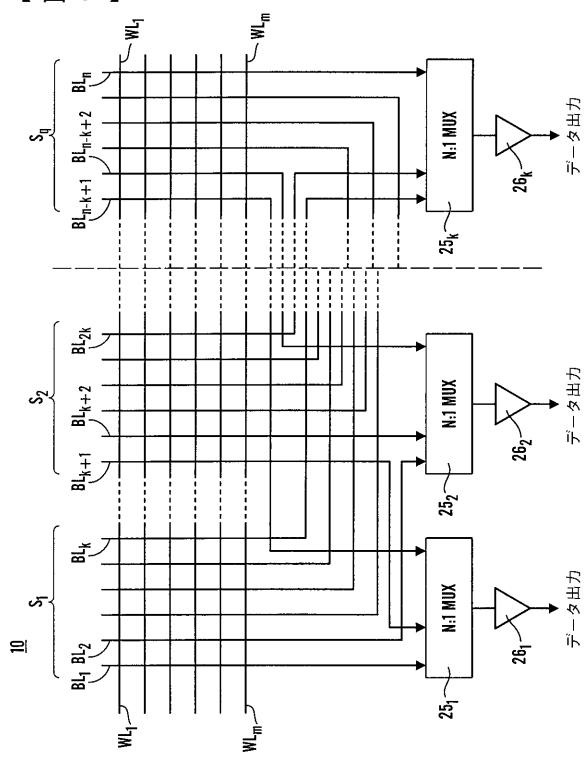

本発明による記憶装置の第1の好ましい実施例において、アドレス中にセグメントの各ビット線を関連する感知手段に同時に接続する手段は、マルチプレクサである。この場合、マルチプレクサの数は、セグメントを定義しているビット線の最大数に対応し、セグメントの各ビット線は特定のマルチプレクサに接続している。各マルチプレクサの出力は、ひとつ感知手段に接続していることが望ましく、特に、そのひとつ感知手段は感知増幅器であってもよい。

#### 【0016】

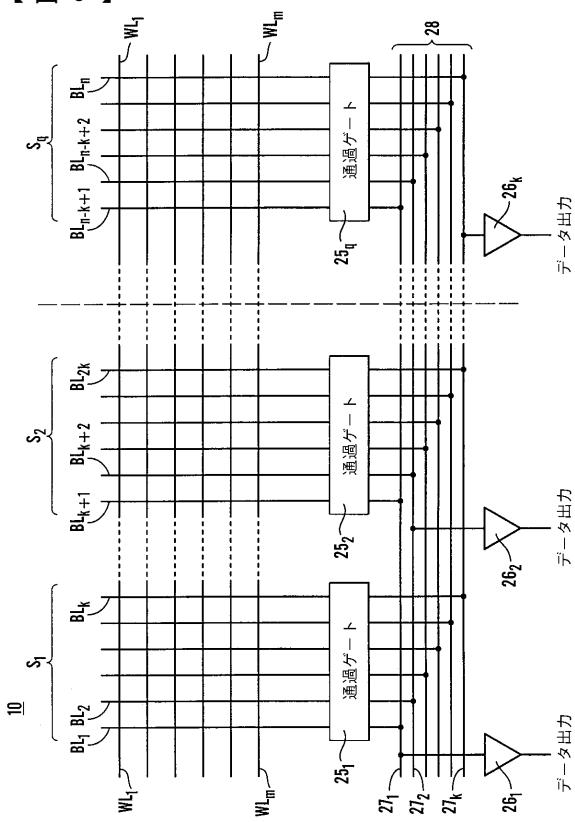

本発明による記憶装置の第2の好ましい実施例において、アドレス中にセグメントの各ビット線を関連する感知手段に同時に接続する手段は、ゲート手段である。この場合、セグメントの全てのビット線は、特定のゲート手段に接続することができる。各ゲート手段は、それぞれのセグメントにおけるビット線の数に対応した数の出力を有し、各ゲート手段の各出力は、出力データ・バスの特定のバス線に接続している。バス線の数は、従って、セグメントのビット線の最大数に対応し、各バス線はひとつの感知手段に接続している。30

#### 【0017】

ゲート手段は通過ゲートを有することが望ましく、感知手段は感知増幅器であることが望ましい。

#### 【0018】

上記目的および他の有利な点および特徴は、本発明による記憶装置のための読み出し方法によっても実現される。本方法は、以下のことを特徴とする。ワード線を複数のセグメントに分割する。各セグメントはマトリックス内の複数の隣接するビット線を有し、それらによって定義されている。ワード線セグメント内の各ビット線は関連する感知手段に接続される。プロトコルに従って、読み取りサイクルの間の少なくともある時間、セグメントのひとつのワード線の電位を切り換え電圧  $V_s$  に設定することによって、一度にひとつのワード線が活性化される。その間セグメントの全てのビット線はゼロ電位に保たれる。読み取りサイクルの間感知手段によって感知された各記憶セルに記憶された論理価値を決定する。

#### 【0019】

10

20

30

40

50

本発明による読み出し方法の好ましい実施例において、どの記憶セルも読み書きされていないとき、すべてのワード線およびビット線は、スイッチング電圧  $V_s$  の約 3 分の 1 の静止電圧に保たれている。読みサイクルの間の少なくともある時間、プロトコルに従って、セグメントのひとつのワード線の電位を切り替え電圧  $V_s$  に設定することによって、一度にひとつのワード線が、活性化される。その間、セグメントの全てのビット線はゼロ電位に保たれる。読みサイクル中に感知手段によって感知された各記憶セルに記憶された論理価値が、決定される。

#### 【0020】

最後に、上記の目的、他の特徴、および有利な点は、本発明に係る不揮発性受動記憶装置を使用し、複数のスタック層を有し、各層が不揮発性受動マトリックス記憶装置のひとつを有する立体的データ記憶装置における読み出しのために本発明による方法を使用することによって、実現される。

10

#### 【0021】

本発明は、その一般的な背景および好ましい実施例と図面の説明と共に、以下に詳しく説明される。

#### 【0022】

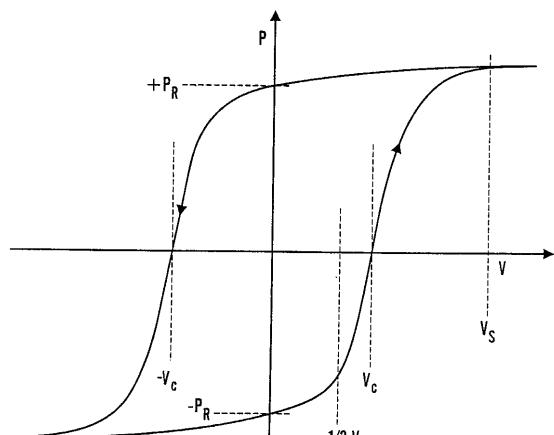

好ましい実施例の詳細について説明をする前に、受動マトリックス・メモリあるいはこのような記憶装置内の単一の記憶セルがどのように機能しているかをよりよく理解できるように、本発明の一般的な背景を説明する。この点に関し、図 1 を参照されたい。図 1 は、強誘電性材料の、典型的ないわゆる“ヒステリシス・ループ”を示している。強誘電性材料の極性  $P$  は 電位差  $V$  に対して描かれている。極性値は、示される方向に従ってループに沿って変化する。図 1 に示されるようなヒステリシス・ループを持つ強誘電性材料は、電圧  $V_s$  がいわゆる強制電圧  $V_c$  を超えると、そのネット極性方向を変化させ（“切り替え”）、極性  $P$  は、突然大きな陽性値  $+P$  に変化する（ゼロ電圧における陰性極性から始まると仮定する）。この陽性極性  $+P$  は、対応する陰性の電圧  $-V_s$  が陰性の強制電圧  $-V_c$  を超え、極性を再び陰性の極性に変化させるまで続く。このように、強誘電性材料を含む蓄電器を有する記憶装置は、外部から適用される電場がない場合に記憶効果を発揮し、分極反応を引き起こす電位差を強誘電性材料にわたって適用することにより、不揮発性データを記憶することが可能となる。従って、その方向（および規模）を好ましい状態に設定し、そのまま保つことができる。同様に、分極状態を決定することもできる。データの記憶および決定を以下にさらに詳しく説明する。

20

#### 【0023】

必要な切り替え速度その他によって、強誘電性材料の分極状態を駆動するために使用される名目電圧  $V_s$  は、通常、強制電圧  $E_c$  よりかなり大きく選択される。電圧  $V_s$  は、図 1 において点線で表されているが、この特定の値に限定されているわけではない。他の値を適用することもできる。

30

#### 【0024】

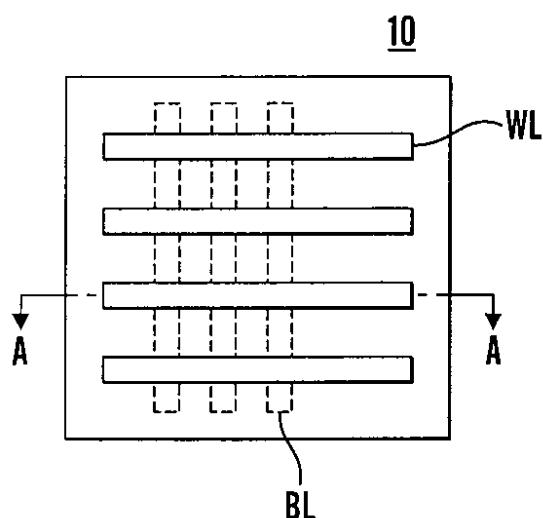

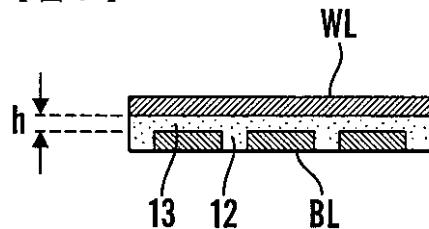

図 2 は、受動マトリックス・メモリ 10 の  $m \cdot n$  記憶マトリックス 11 の一部を示し、並列な電極の互いに反する 2 つの組、つまり、ワード線電極  $W_L$  およびビット線電極  $B_L$  を示している。ワード線とビット線電極  $W_L$ 、 $B_L$  は、互いに垂直になるように配置され、それによって、それらは、交差する領域において、絶縁強誘電性材料の特定の量的要素の側面の壁を定義し（以下にさらに詳しく説明する）、記憶マトリックス 11 における蓄電器に似た記憶セルの容量を定義する。図 3 は、図 2 における線 A に沿った断面図である。各“蓄電器”の絶縁体は、強誘電性材料層 12 における強誘電性材料であり、その材料の厚さが、容量要素の高さ  $h$  を定義し、容量要素が記憶セル 13 を定義する。簡略化のため、図 2 において、ワード線とビット線電極  $W_L$ 、 $B_L$  の交点が 3 つだけ示されている。

40

#### 【0025】

電位差  $V_s$  を、ふたつの相反する電極、セル 13 におけるワード線  $W_L$  およびビット線  $B_L$  の間に与えることによって、セル 13 における強誘電性材料は、電場  $E$  がかけられ、分極反応が引き起こされる。分極反応は、図 1 に示されるような法則に従って、ふたつの安

50

定した状態、陽性あるいは陰性分極のうちのどちらかの状態に設定されそのままの状態におかれる、方向を持っている。このふたつの状態は、2進数の状態“1”および“0”を表す。同様に、セル13の分極状態は、セル13をアドレスしているふたつの相反する電極WLおよびBLの間に電位差を再び適用することによって、変化あるいは減少する。電位差の適用は、電位差が取り除かれた後に、分極をそのままにするか、あるいは反対の方向に転換する。前記の場合適用された電圧に対応して小さな電流が流れ、後記の場合分極の変化により大きな電流が流れる。電流は、様々な方法で提供される参照（図示されていない）と比較され、“0”あるいは“1”的状態が存在するかどうか決定される。読みが破壊的な読みであった場合、いくつかのセルにおける分極状態は、反対の状態に切り換えられる。例えば、読まれたものが状態“1”であっても状態“0”であっても、セルの分極は“0”に切り換えされることもある。最初の状態は、情報つまり読み出し値をメモリ内に保存するために、メモリ内のセルに書き戻されなければならない。受動マトリックス・メモリがどのように動作するかに関するさらに詳しい説明は、以下に、本発明の好ましい実施例を記述する際に行う。

#### 【0026】

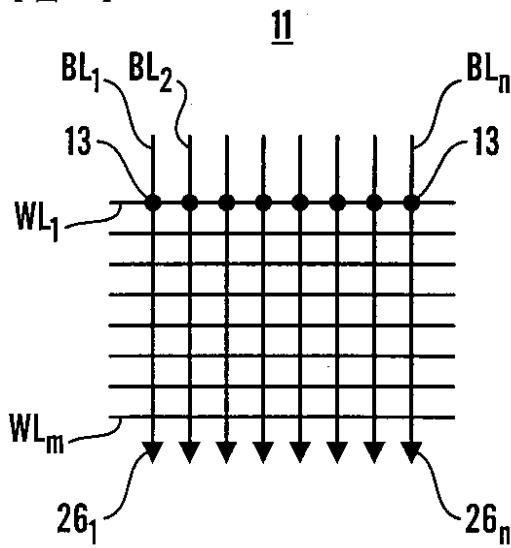

本発明の理解を高めるために、以下に“全ワード読み取り”と呼ぶ、受動マトリックス・メモリのための他の読み出し方法を示している図4を参照されたい。この方法において、活動的ワード線、ここにおいては、求められる記憶セル13を有する第1のワード線WL<sub>1</sub>が、その全ワードの長さ、つまりビット線BL<sub>1</sub>からBL<sub>n</sub>によって定義されるセル13において感知される。全ワード読み取りそのものは、例えば米国特許第6,157,578号に記述されるように、周知の概念である。本文献においては、しかし、解決策は活動的マトリックス記憶装置に向けられていて、記憶マトリックスの比較的大きなブロックに記憶されたデータの転送速度を増すことを目的としている。本発明は、反対に、受動マトリックス・メモリに関するものであり、米国特許第6,157,578号に記述されるような活動的マトリックスに関する従来技術の知識は、活動的装置にはアドレスされていないセルの妨害に関する問題は無いので、適切ではない。

#### 【0027】

受動マトリックス・メモリにおける全ワード読み取りのためのパルシング(pulsing)・プロトコルに従って、使用されていないワード線、この場合ワード線WL<sub>2</sub>からWL<sub>m</sub>は、同じ電位すなわちビット線BL<sub>1</sub>からBL<sub>n</sub>と本質的に同じ電位に保つことができることに注目することが重要である。その結果、記憶マトリックス(10)のどのアドレスされていないセルにおいても、妨害信号が発生しない。データの読み出し(感知)のために、活動的なワード線、この場合最初のワード線WL<sub>1</sub>は、交差するビット線BL<sub>1</sub>からBL<sub>n</sub>上をセルを通って流れる電流Iを発生させる電位に置かれる。電流Iの大きさは、各セル13の分極状態により、感知手段26によって決定される。感知手段26は、図4に示されるように、各ビット線BLにつきひとつ存在する。感知手段は、例えば感知増幅器であってよい。

#### 【0028】

全ワード読み取り方法にはいくつかの有利な点がある。例えば、アドレスされていないセルにおける部分的切り換えを被ることなく、読み出し電圧を強制電圧よりかなり高く選択することができる。またこの方法は、大規模なマトリックスに使用することもできる。

#### 【0029】

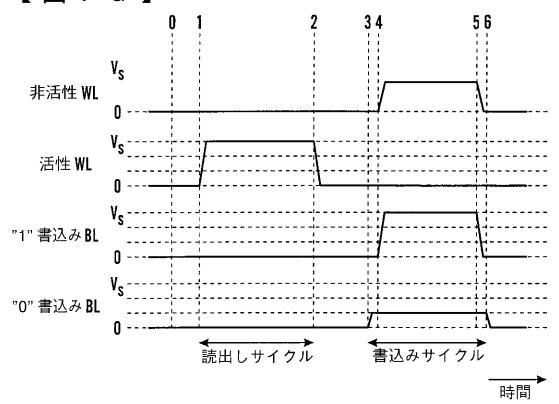

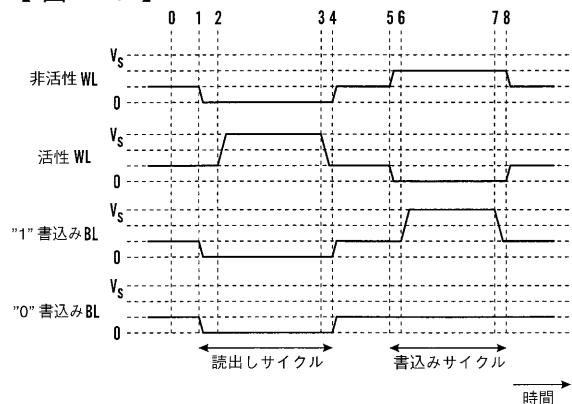

本発明の好ましい実施例が、図5から図7に示されている。付随するタイミング図は、活動中のセグメントにおける全てのセルを読む間、活動中のワード線WL<sub>1</sub>の全てのセル上に切り換え電圧V<sub>s</sub>を適用する一方、アドレスされていない記憶セルの妨害信号がゼロボルトであることを示している。好ましいタイミング図が図7aに示されている。また、他の好ましいタイミング図が図7bに示されている。

#### 【0030】

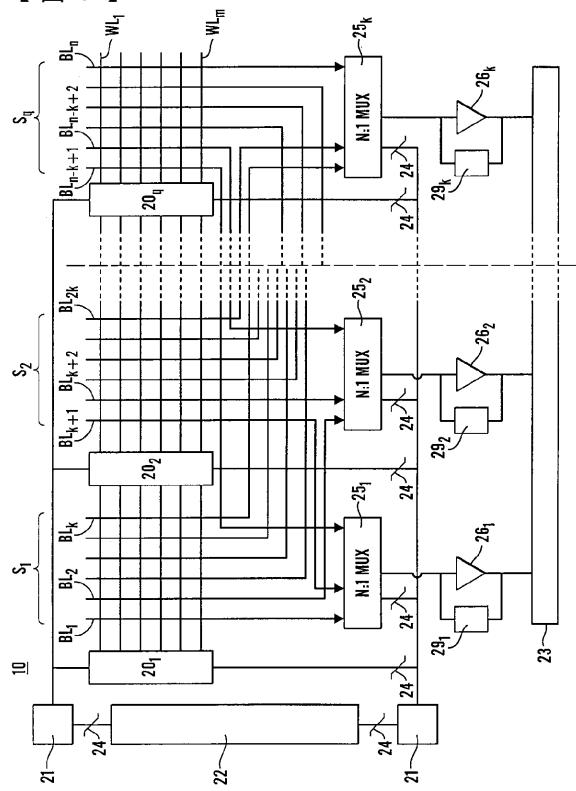

本発明による受動マトリックス・メモリの好ましい実施例を示す図5に関して、マトリックスの特性は、m本のワード線WL<sub>1</sub>からWL<sub>m</sub>およびn本のビット線BL<sub>1</sub>からBL<sub>n</sub>から

10

20

30

40

50

なる  $m \cdot n$  マトリックスとして構成されている。ワード線は、 $q$  個のセグメント  $S$  に分割され、各セグメント  $S$  は、マトリックス  $BL$  における隣接するビット線  $BL$  の数  $k$  によって定義されている。 $k$  は、 $q \cdot k = n$  となるように、各セグメントに対して同じであることが好ましい。各セグメント  $S$  における第 1 のビット線を読み出すために、セグメントは第 1 のマルチプレクサ  $25_1$  によって第 1 の感知手段  $26_1$  に接続される。各セグメントにおける第 2 のビット線は、他のマルチプレクサ  $25_2$  に接続され、同様に、各セグメントの  $k$  番目の線は残りのマルチプレクサ  $25_k$  に接続される。つまり、マルチプレクサ ( $MUX$ )  $25$  の数は、セグメントを定義しているビット線の数と等しくなる。もちろん、各セグメント  $S$  におけるビット線の数は異なるものであってもよいが、セグメントにおけるビット線の記憶セルが同じ長さのデータ・ワードを有する場合、 $k$  は全てのセグメントに対して同じとなる。各マルチプレクサ  $25$  は、データの読み出しのための感知手段  $26$  に接続され、感知手段  $26$  の数もまた、セグメントを定義しているビット線の最大数  $k$  と等しくなる。部分的にワードを読み取る従来の受動マトリックス・メモリと異なり、ワード線セグメント  $n$  における全ての記憶セル  $13$  は、ワード線セグメント上の全てのビット・スポットを平行して読み出すことができるよう、感知手段  $26$  に同時に接続される。特に、感知手段は、感知増幅器であってもよい。簡略化のために、図 5において、最初の 2 つのセグメント  $S_1, S_2$  および最後のセグメント  $S_q$  のみが示されている。関連するマルチプレクサ  $25$  および感知増幅器  $26$  に関しても同様である。記憶マトリックス  $11$  に記憶されている、あるいはこれから記憶されるデータは、図 5 には示されていないが、関連する列デコーダおよび行デコーダによってアクセスすることができる。記憶マトリックス  $11$  における記憶セル  $13$  に記憶されたデータは、パルス・プロトコルによって、例えば図 7 a に関して説明されるように、マルチプレクサ  $25$  を経由してビット線に接続される感知増幅器  $26$  を通して、読み出すことができる。ワード線セグメント  $S$  を定義する全てのビット線  $BL$  はマルチプレクサ  $25$  に方向付けられ、このセグメントの一定のワード線  $WL$  が活動的であるときにのみ選択される。このように、セグメント  $S$  の活動的ワード線  $WL$  における全てのビット線は、“全ワード構成”において平行して読み出され、全てのビット線は感知増幅器  $26$  間に分配される。

#### 【0031】

具体的な実施例において、受動記憶装置は、例えば、8つのセグメント  $S$  に分割された 16 ビット・メモリであってもよい。すなわち  $q = 8$  であり、それぞれ 64 ビットの  $25_6, 000$  本のワード線  $WL$  を有する記憶装置である。従って、各セグメント  $S$  に 8 本のビット線  $BL$  があり、 $k = 8$  となる。もちろん他の構成も可能であり、例えば各セグメントに 9、16 あるいは 32 本のビット線があってもよい。

#### 【0032】

本発明の他の好ましい実施例において、少なくとも 256 個の記憶セル  $13$  が各セグメント  $S$  において使用される。これは、32:1 のマルチプレクサ  $25$  を使用して、ワード線ドライバが 32 重複しない 8192 ビット幅メモリを形成する。各ワード線は、もちろん、提供された感知増幅器  $26$  の数に従って分割される。

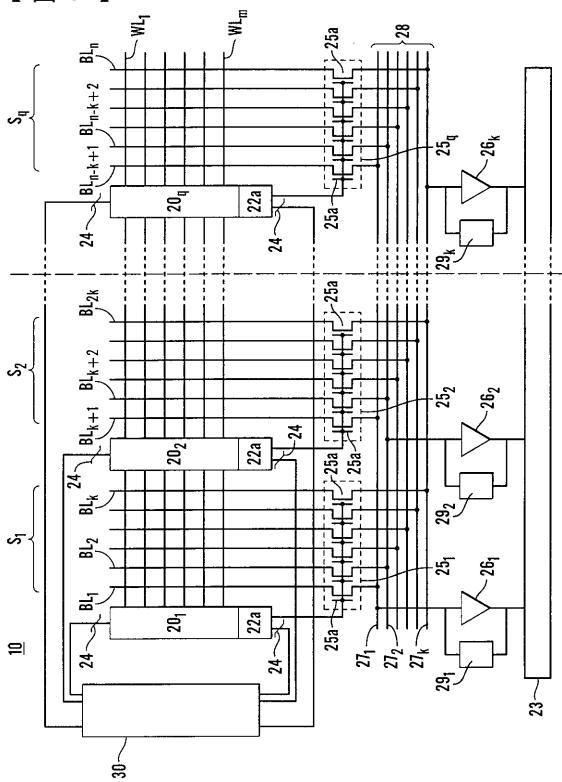

#### 【0033】

図 6において、本発明による記憶装置の他の実施例が示されている。ここでは、マルチプレクサの代わりにゲート手段  $25$  が使用されている。ゲート手段  $25$  は、マルチプレクサと同様の方法でビット線  $BL$  を活性化する。

#### 【0034】

ゲート手段  $25$  は、セグメント  $S$  の各ビット線  $BL$  に接続した通過ゲートであることが望ましい。図 5 におけるマルチプレクサ  $25$  の数は、セグメント  $S$  におけるビット線  $BL$  の数、すなわち  $k$ 、と等しいが、図 6 の実施例における通過ゲートの数は、セグメント  $S$  の数  $q$  に対応する。各通過ゲート  $25$  における出力の数は、それぞれのセグメント  $S$  におけるビット線  $BL$  の数に対応する。セグメント  $S$  の活動的ワード線の記憶セル  $13$  を平行して読み続けるために、セグメント  $S$  の各ビット線  $BL$  に対して感知増幅器  $26$  が使用される。各感知増幅器  $26$  は、データ・バス  $28$  上の線  $27$  のひとつに接続している。通過ゲ

10

20

30

40

50

ートの第1の出力は第1のバス線 $27_1$ に、第2の出力は第2のバス線 $27_2$ に接続し、以下同様に接続される。バス線 $27$ および感知増幅器の数は、もちろん、セグメント $S$ を定義するビット線 $BL$ の最大数と一致する。

【0035】

図7aおよび図7bは、全ワード読み取りサイクルにおけるタイミング図を示している。

【0036】

図7aは、ワード線セグメントのための、以下の書き込み／読み取りサイクル（“リフレッシュ”、“書き戻し”）を持つ全ワード読み取りのタイミングを表す図である。このタイミング図は、4レベル電圧プロトコルに基づいている。このタイミング図によると、全てのワード線および全てのビット線は、マトリックス内のどのセルも読み書きされていないとき、ゼロボルトの静止電圧に保たれている。全ての記憶セルは、読まれる予定のこのセグメント内の全てのビット線 $BL$ および活性化されたワード線 $WL$ によって形成された交点を表すアドレスを持っている。

10

【0037】

不活性のワード線 $WL$ および全てのビット線 $BL$ は、リード・サイクルの間同じ電位曲線に従う。リード・サイクルの間、読まれるセルと接触しているワード線は、切り換え電圧 $V_s$ に設定される。同じ時間間隔で、全てのビット線がゼロ電圧に保たれる。ここに示されるタイミング図において、切り換え電圧 $V_s$ をセルのワード線側に適用し、同じセルのビット線側をゼロ電圧にすることによって、セルには“0”が書き込まれることを示している。このことに従って、双方のタイミング図において、活動的なワード線上の全てのセルは、読み取り操作が実行された後、ゼロ状態に設定されていることが示されている。従って、メモリ中に記憶されたデータを復元するために、“1”を含むべきセルを持つビット線上にのみ“1”を書き戻すことが必要である。このことは図7aおよび図7bにおける例において示され、反対の極性を持つ電圧が、読み取りサイクル間に“1”を書かれるべきセルに適用される。

20

【0038】

図7bは、4レベル電圧プロトコルに基づく他のタイミング図を示している。この実施例によると、全てのワード線およびビット線は、マトリックス内のどのセルも読み書きされていないときは、静止電圧 $V_s/3$ に保たれている。

30

【0039】

図7aおよび図7bに示されるような例におけるすべてのタイミング・ポイントの正確な値は、記憶セルの材料および設計の詳細による。

【0040】

図5および図6における実施例において、ワード線は、原則的に中断されることはない。つまり、ワード線は別々のセグメントに連続して伸び、セグメントは対応するビット線によってのみ定義される。読み書きのためのマルチプレクサおよびプロトコルは、そこに適合されなければならない。しかし、ワード線が長くなりすぎると不利である。セグメントの数と、各セグメントのビット線の数を制限することにより、ワード線が長くなりすぎることを防ぐことができる。上記の例においては、256,000本のワード線およびそれぞれ8本のビット線を持つ8個のセグメントが使用されている。そしてメモリは、上記のように、16Mビットの記憶容量を持つ。しかし、ワード線が連続していることによる他の不利な点がある。セグメント $S$ の記憶セルのビット・スポットが、活動的なワード線上にかけられ、アドレスされたセグメントにおけるビット線のみが接続されていても、静電容量連結およびスニーケ電流が形成され、例えばセグメント内の隣接する活動的でないワード線における記憶セルに影響を与えることがある。このことは、偽の読み出しあるいは雑音を起こすことがある。本発明による記憶装置の具体的な実施例において、アドレスされたセグメント内の活動的ワード線のみがドライバに電気的に接続され、残りのセグメントの対応するワード線セグメントが接続されないように、ワード線を電気的に分割することができるようになることが適切である。このことは、図7におけるプロトコルが、原則的

40

50

に図 5 の実施例に対応する、図 8 に示される記憶装置の実施例において使用され実現される場合に、特に適切である。図示されていないが、ドライバ群 20 におけるひとつのドライバが、セグメント選択器 22 によって選択される。セグメント選択器 22 は、例えば、選択バスのようなものであり、選択されたセグメント S におけるワード線 WL が読み書きサイクルのために活性化される。セグメント選択手段 22 によって制御されるマルチブレクサ 25 は、スイッチ 24 を通してドライバ群 20 の選択されたドライバと接続することができ、切り換え可能キャッシュ・メモリ 21 を経由して選択手段 22 を通して制御される。特定のマルチブレクサ 25 が、アドレスされたセグメントにおけるビット線 BL を感知増幅器 26 に接続するために、同時にアドレスされる。具体的に言うと、セグメント内の各ワード線 WL は、例えば CMOS 論理ゲートのような AND ゲート、即ち通過ゲートに接続することができ、セグメントはワード線あるいはアドレス・デコーダからアドレスすることができる。例えば、ワード線 WL<sub>1</sub> が、セグメント S<sub>1</sub> において選択され、セグメント S<sub>1</sub> 内のこのビット線上にのみ電圧がかけられる。破壊的読み出しの場合、セグメント S<sub>1</sub> における全ての記憶セルおよびワード線 WL<sub>1</sub> がゼロ状態に切り換えられ、マルチブレクサ 25 は、セグメント S<sub>1</sub> 内の全てのビット線を対応する感知増幅器 26<sub>1</sub> から 26<sub>k</sub> に接続する。そして、活性化されたワード線上の全てのセルを読み出すことができる。つまり、セグメントのワード線がデータ・ワードを含むよう定義されていれば、全ワード読み取りが実現される。選択されたワード線 WL<sub>1</sub> 上の全てのセルの状態が検知されると、残りのワード線 WL<sub>2</sub> から WL<sub>m</sub> およびビット線 BL<sub>1</sub> から BL<sub>k</sub> は、感知増幅器 26 のバイアス・ポイントに近い静止電圧に保たれる。そして、原則として、セグメントの残りのセルからの妨害信号はない。また、感知増幅器 26 の入力への妨害信号が生成されるようない、ビット線のセル上のバイアス電圧もない。感知増幅器 26 のデータ出力は、2 方向データ・バス 23 に伝達され、書き込み論理 29 がセグメント内の活動的なワード線上のセルのビット・スポットへデータを書くために、マルチブレクサの出力に並列に接続される。セグメント内のワード線は、読み出しの場合と同様に、選択手段 22 を通して対応する方法で選択されている。選択手段 22 の切り換え可能出力上にバッファ・メモリ 21 があり、選択手段 22 が、選択手段 22 によって制御される複数の線スイッチ 24 を通してドライバとマルチブレクサ 25 を接続することが望ましい。

#### 【0041】

図 9 は、図 8 における実施例と機能的に同様な実施例を示しているが、マルチブレクサが通過ゲート 25 に置き換えられている図 6 の実施例にも対応するものである。各通過手段 25 は、例えば、通過ゲートとして機能する切り換えトランジスタ 25a を各線にひとつ有し、通過手段 25 において合計 k 個の切り換えトランジスタ 25a が存在する。図 8 における実施例の場合、各セグメントにひとつのドライバ群 20 が提供されているが、ここでは、選択手段 22 の代わりにドライバ群選択器 22a が提供されている。別々のワード線 WL のアドレッシングは、群選択器 22a による制御のもとワード線アドレス・バス 30 における出力を通して行われる。読み出しにおいて、ビット線 25a はデータ・バス 28 におけるバス線 27 に接続し、感知増幅器のデータ出力は、双方向データ・バス 23 に接続している。図 8 と同様に、書き込み論理 29 は感知増幅器 26 と並列に提供されている。書き込み操作が行われているとき、ワード線セグメントは群選択器 22a を通して選択され、ワード線アドレス・バス 30 を通してアドレスされる。

#### 【0042】

基本的に、選択、デコードおよびアドレスのために必要な装置および手段は、ここには示されていないタイミング論理同様、従来技術において周知であり、活動的あるいは受動的なマトリックス・アドレス可能なメモリにおいて一般的に使用されている。従って、ここでは詳細に記述しない。

#### 【0043】

パルシング・プロトコルにおける電圧レベルの数および電圧レベルそのものは、全ワード読み取りを実行するための必要条件が満たされる限り、任意に選択することができる。さらに、ここに示されるプロトコルに従った電圧の分極は、反転することができる。

10

20

30

40

50

## 【0044】

本発明による記憶装置を実現するための具体的な回路技術において、記憶マトリックスを基板上に装備し、記憶装置の全領域が大きくなないように、ワード線ドライバをそこに一体化することができる。

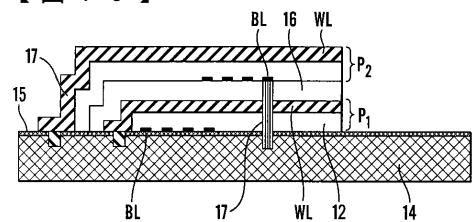

## 【0045】

分割されたワード線もまた、スタック・メモリ面上に実現することができ、この場合、ビット線  $B_L$  は、マルチブレクサあるいはゲート手段 25 に垂直に接続する。このことは図 10 に示されている。図 10 において、本発明による記憶装置 10 がスタック・メモリとして提供されている実施例を、概要的に断面図として示している。このことは、各層あるいは記憶面  $P$  がひとつの記憶装置 10 を有する立体的データ記憶装置を実現する。記憶装置を互い違いに配置することによって、それぞれのワード線  $W_L$  およびビット線  $B_L$  は、いわゆる互い違いバイア 17、つまり交互に水平および垂直の“端越え”接続、を通して基板 14 内の（図示されていない）ドライバおよび制御回路に接続することができる。基板 14 は、無機性つまりシリコン基板であってもよく、従って、回路は例えば両立する CMOS 技術において実現することができる。図 10 には、ふたつの記憶面  $P_1$ 、 $P_2$  のみが示されているが（限られた数のビット線のみが図示されていることに注意されたい）、実際には、容積測定データ記憶装置は多数、8 から 100 以上の記憶面を有することができ、各記憶面が約  $1\mu m$  あるいはそれ以下の薄さであっても、大容量および高記憶密度の記憶装置を実現することができる。

## 【0046】

上記の受動マトリックス記憶装置の利点には、製造が簡便化されることと、セルが高密度となることも含まれる。さらなる利点は、

a) ワード線が電気的に分割され、図 7 a に示されるプロトコルが使用されると、アドレスされていない記憶セルは、読み取りサイクルの間ゼロボルト電位（あるいは小さな電位）に保たれる。このことにより、記憶内容の喪失を起こす可能性のある妨害信号の数を減少させることができ、同様に、スニーケ電流を引き起こす、読み取り操作中の全ての妨害信号を除去することができる。

b) データ転送速度が、セグメント内のビット線の数が可能にする限りの最高速度となる。

c) 読み出し電圧  $V_s$  は、アドレスされていないセルにおける部分的切り換えを起こすことなく、強制電圧よりかなり高く選択することができる。このことにより、切り換え速度は、セルにおける分極可能材料の可能な限りの最高速度に近づくことができる。

d) 本読み出し方法は、大規模マトリックスに適用することができる。

## 【0047】

加えて、本発明による記憶装置は、少ない数の感知増幅器を使用しても実現することができる。このことは、記憶装置が大規模であるときに有利であり、感知増幅器の電力消費に関しても有利である。感知増幅器の電力消費は高いものであるが、ドライブおよびアドレス回路の電力を適切に管理することによって、ある程度減少させることができる。さらに、感知増幅器の数を減らすことによって、感知手段のための場所の均衡をとり、記憶装置における全体的な領域の最適化を達成することができる。最後に、ワード線を分割することによって、ひとつのワード線が障害を起こした場合、読み出しあるいはアドレス中のエラーの位置をひとつのワードにおいて特定することができる。

## 【図面の簡単な説明】

【図 1】 強誘電性記憶材料のヒステリシス曲線の法則を表す図である。

【図 2】 交差する電極線を有し、記憶セルがこれらの電極が重なったその間に置かれた強誘電性材料を有する、受動メモリ・マトリックスの一部を表す概要図である。

【図 3】 図 2 の A 線に沿った断面の拡大図である。

【図 4】 強誘電性マトリックス・メモリにおける全ワード読み取りを示す機能プロック図である。

【図 5】 本発明の好ましい実施例による、分割されたワード線を有する受動マトリック

10

20

30

40

50

ス・メモリを示す機能ブロック図である。

【図6】 本発明の好ましい実施例による、分割されたワード線を有する受動マトリックス・メモリを示す機能ブロック図である。

【図7a】 “全ワード読み取り”におけるメモリ・マトリックスのセグメントのワード線をアドレスするために後に続く書き込み／書き直し周期がある、単純な全ワード読み取りのタイミングを示す図である。

【図7b】 図7aにおけるタイミング図の別形を示す図である。

【図8】 図5に示される実施例と同様の実施例であるが、ワード線が電気的に分割されている実施例を示す図である。

【図9】 図6に示される実施例と同様の実施例であるが、ワード線が電気的に分割されている実施例を示す図である。 10

【図10】 図5および図6における記憶マトリックスが、容積測定記憶装置においてどのように実現されるかを示す図である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7 a】

【図7 b】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 トンプソン、マイケル

アメリカ合衆国 ニューヨーク、イサカ、コーネル ユニヴァーシティ、バード ホール 32

9

(72)発明者 ウォマック、リチャード

アメリカ合衆国 ニューメキシコ、アルバカーキ、アカデミー ロード エヌイー 6733

- エイ、シン フィルム エレクトロニクス インコーポレイテッド内

(72)発明者 グスタフソン、ゲーラン

スウェーデン国 リンケピング、トルムスラガレガタン 33

(72)発明者 カールソン、ヨハン

スウェーデン国 リンケピング、エクホルムスヴェーゲン 219

審査官 高野 芳徳

(56)参考文献 国際公開第99/012170 (WO, A1)

特開平06-314494 (JP, A)

特開2002-026283 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/22