(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5039130号

(P5039130)

(45) 発行日 平成24年10月3日(2012.10.3)

(24) 登録日 平成24年7月13日(2012.7.13)

(51) Int.Cl.

G06F 17/50 (2006.01)

F 1

G06F 17/50 672Z

G06F 17/50 664Z

請求項の数 6 (全 25 頁)

(21) 出願番号 特願2009-508341 (P2009-508341)

(86) (22) 出願日 平成19年5月2日 (2007.5.2)

(65) 公表番号 特表2009-535726 (P2009-535726A)

(43) 公表日 平成21年10月1日 (2009.10.1)

(86) 國際出願番号 PCT/EP2007/054255

(87) 國際公開番号 WO2007/128753

(87) 國際公開日 平成19年11月15日 (2007.11.15)

審査請求日 平成22年2月18日 (2010.2.18)

(31) 優先権主張番号 11/381,437

(32) 優先日 平成18年5月3日 (2006.5.3)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】シミュレーション結果を表示するための信号の仕様をサポートする方法、システム、およびプログラム製品

## (57) 【特許請求の範囲】

## 【請求項1】

データ処理システムにおけるデータ処理の方法であって、データ処理システムが、

信号グループ名によって信号グループを指定する少なくとも1つのエントリを含むデータ・セットを入力として受け取るステップと、

前記データ・セットの受け取りに応答して、

前記データ・セット内の前記少なくとも1つのエントリを処理して、前記信号グループ名を識別するステップと、

前記識別された信号グループ名に対応する信号グループに含まれる信号の信号名を、

シミュレーション結果を含むイベント・トレース・ファイルに関連付けられた信号グループ情報から決定するステップと、

前記複数の信号のインスタンスに関連付けられた前記イベント・トレース・ファイルからの1以上のシミュレーション結果を、プレゼンテーションに含めるステップと、

リネームから関連する信号名が保護されることになる特定の信号を識別する保護指示を受け取るステップと、

前記保護指示に応答して、前記プレゼンテーションにおいて前記関連する信号名によつて前記信号を識別するステップと

を実行することを含む、前記方法。

## 【請求項2】

前記信号グループが第1の信号グループを備えており、

10

20

前記第1の信号グループが、前記複数の信号をメンバとして集合的に有する第2および第3の信号グループを備えている、

請求項1に記載の方法。

【請求項3】

前記データ・セットは、信号インスタンス化識別子、信号グループ・インスタンス化識別子、及び、参照有効範囲コマンドを含み、

前記データ処理システムが、

前記データ・セット内の参照有効範囲コマンドを解釈して、前記インスタンス化識別子又は信号グループ・インスタンス化識別子の中からユーザに提示する識別子を選択するステップ

10

をさらに実行することを含む、請求項1又は2に記載の方法。

【請求項4】

データ処理システムに、請求項1～3のいずれか一項に記載の方法の各ステップを実行させるコンピュータ・プログラム。

【請求項5】

データ処理システムに、請求項1～3のいずれか一項に記載の方法の各ステップを実行させるコンピュータ・プログラムを記録したコンピュータ読み取り可能な記録媒体。

【請求項6】

データ処理システムであって、

プロセッサと、

前記プロセッサに結合されたデータ・ストレージと

を備えており、

前記データ・ストレージが、

前記データ処理システムに、請求項1～3のいずれか一項に記載の方法の各ステップを実行させるプログラム・コード

20

を含む、前記データ処理システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、デジタル・デバイス、モジュール、およびシステムのシミュレートに関し、具体的には、デジタル・デバイス、モジュール、およびシステムのコンピュータ・シミュレーションに関する。

30

【背景技術】

【0002】

デジタル設計の論理的正確さの検証、および、必要であれば設計のデバッグは、ほとんどのデジタル設計プロセスにおいて非常に重要なステップである。論理ネットワークは、実際にネットワークを構築すること、またはコンピュータ上でネットワークをシミュレートすることの、いずれかによってテストされる。論理ネットワークが非常に複雑になるにつれて、設計が実際に構築される前に設計をシミュレートすることが必要になってきている。これは特に、集積回路の製造にかなりの時間を必要とし、ミスの訂正にかなりのコストがかかることから、設計が集積回路として実装される場合に当てはまる。デジタル設計シミュレーションの目的は、設計の論理的正確さの検証である。

40

【0003】

従来の電子コンピュータ支援設計（E C A D）システムによってサポートされる典型的な自動設計プロセスでは、設計者は、V H D Lなどのハードウェア記述言語（H D L）を使用して高水準の記述を入力し、様々な回路ブロックおよびそれらの相互接続の表現を生成する。E C A Dシステムは、設計記述を、シミュレーションに最適なフォーマットにコンパイルする。次にシミュレータを使用して、回路レイアウトを展開するのに先立って設計の論理的正確さを検証する。

【0004】

50

シミュレータとは、典型的には、デジタル表現、または回路のシミュレーション・モデル、およびデジタル・システムの入力を表現する入力刺激 (input stimuli) のリスト (すなわちテストケース) で動作する、ソフトウェア・ツールである。シミュレータは、回路の応答の数値表現を生成し、これが、値のリストとしてディスプレイ画面上に表示されるか、または、しばしば別のソフトウェア・プログラムによってさらに解釈され、グラフの形でディスプレイ画面上に提示される可能性がある。シミュレータは、シミュレーション用に特別に設計された、汎用コンピュータまたは通常は汎用コンピュータに接続された他の電子装置上で、実行可能である。全体として汎用コンピュータ上のソフトウェア内で実行するシミュレータを、以下では「ソフトウェア・シミュレータ」と呼ぶ。特別に設計された電子装置の支援を受けて実行されるシミュレータを、以下では「ハードウェア・シミュレータ」と呼ぶ。

10

#### 【0005】

通常、ソフトウェア・シミュレータは非常に多くの計算を実行し、ユーザの観点からゆっくりと動作する。性能を最適化するために、シミュレーション・モデルのフォーマットは、シミュレータが非常に効率良く使用するように設計される。ハードウェア・シミュレータは、本質的に、回路記述を備えるシミュレーション・モデルが特別に設計されたフォーマットで通信されることを必要とする。いずれの場合も、以下ではシミュレーション実行可能モデルと呼ばれる、HDL記述からシミュレーション・フォーマットへの変換が必要である。

20

#### 【0006】

シミュレータによるシミュレーション実行可能モデルへのテストケースの適用の結果は、本明細書では「全イベント・トレース」(AET)と呼ばれる。AETは、シミュレーション実行可能モデル内の信号あるいはストレージ要素またはその両方の論理値を含む。AETビューアは、再検討および分析のためにAETのコンテンツによってユーザに提示するために使用することができる。

#### 【0007】

大規模なシミュレーション実行可能モデルの場合、莫大な量のデータがAETに存在することになり、それらのすべてがユーザに関係する訳ではないことを理解されよう。したがって従来のAETビューアでは、ユーザは、ユーザが表示したいシミュレーション実行可能モデル内の信号を指定する入力/出力(I/O)リストを入力することができる。これに応答して、従来のAETビューアは、I/Oリスト内で識別されたシミュレーション実行可能モデル内の信号のみをユーザに提示する。

30

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0008】

本発明は、特に複雑なシミュレーション実行可能モデルの場合、I/Oリストの(たとえばキーボードを利用した)ユーザ入力が退屈で時間のかかるものであることを理解している。したがって本発明は、シミュレーション処理のための方法、システム、およびプログラム製品を提供する。

#### 【課題を解決するための手段】

40

#### 【0009】

本発明は、データ処理システムにおけるデータ処理の方法であって、データ処理システムが、

信号グループ名によって信号グループを指定する少なくとも1つのエントリを含むデータ・セットを入力として受け取るステップと、

前記データ・セットの受け取りに応答して、

前記データ・セット内の前記少なくとも1つのエントリを処理して、前記信号グループ名を識別するステップと、

前記識別された信号グループ名に対応する信号グループに含まれる信号の信号名を、シミュレーション結果を含むイベント・トレース・ファイルに関連付けられた信号グル

50

情報から決定するステップと、前記複数の信号のインスタンスに関連付けられた前記イベント・トレース・ファイルからの1以上のシミュレーション結果を、プレゼンテーションに含めるステップと、リネームから関連する信号名が保護されることになる特定の信号を識別する保護指示を受け取るステップと、前記保護指示に応答して、前記プレゼンテーションにおいて前記関連する信号名によって前記信号を識別するステップとを実行することを含む、前記方法を提供する。**【0010】**

例示的方法によれば、所定の信号グループ名によって信号グループを指定する少なくとも1つのエントリを含むデータ・セットが、データ処理システムによって受け取られる。このデータ・セットの受け取りに応答して、信号グループ名を識別するためにデータ・セット内のエントリが処理される。信号グループのメンバである複数の信号の信号名を特定するために、シミュレーション結果を含むイベント・トレース・ファイルに関連付けられた信号グループ情報にアクセスする。その後、当該複数の信号のインスタンスに関連付けられたイベント・トレース・ファイルからのシミュレーション結果が、シミュレーション結果のプレゼンテーションに含められる。

10

本発明のすべての目的、特徴、および利点は、以下の詳細な説明で明らかになろう。

**【0011】**

本発明の新規な機能であるとみなされる特徴は、添付の特許請求の範囲に示される。しかしながら、本発明それ自体、ならびに好ましい使用モード、それらの他の目的および利点は、添付の図面に関して例示的実施形態の以下の詳細な説明を参照することによって、最も良く理解されるであろう。

20

**【発明を実施するための最良の形態】****【0012】**

次に図面を参照すると、また特に図1を参照すると、これによって本発明が有利に使用できる、データ処理システム10の絵画図が示されている。図に示されるように、データ処理システム10は、1つまたは複数のノード13が接続されたワークステーション12を備える。ワークステーション12は、好ましくは、ニューヨーク州アーモンクのインターナショナル・ビジネス・マシーンズ(IBM)(登録商標)コーポレーションから入手可能なPOWERライン・コンピュータ・システムのうちの1つなどの、高性能マルチプロセッサ・コンピュータを備える。ワークステーション12は、好ましくは、本発明の方法およびシステムに従ってデジタル回路設計を開発および検証するために使用可能なECA/Dシステムを備えるソフトウェア・アプリケーションを格納するための、不揮発性および揮発性の内部ストレージを含む。図に示されるように、ノード13は、ディスプレイ・デバイス14、キーボード16、およびマウス20を含む。ワークステーション12内で実行されるECA/Dソフトウェア・アプリケーションは、好ましくは、デジタル回路設計者がキーボード16およびマウス20を使用して対話することが可能なグラフィック・ユーザ・インターフェース(GUI)を、ディスプレイ・デバイス14のディスプレイ画面22内に表示する。したがって、キーボード16およびマウス20を利用して適切な入力を実行することによって、デジタル回路設計者は、以下により詳細に説明する方法に従ってデジタル回路設計を開発および検証することができる。

30

**【0013】**

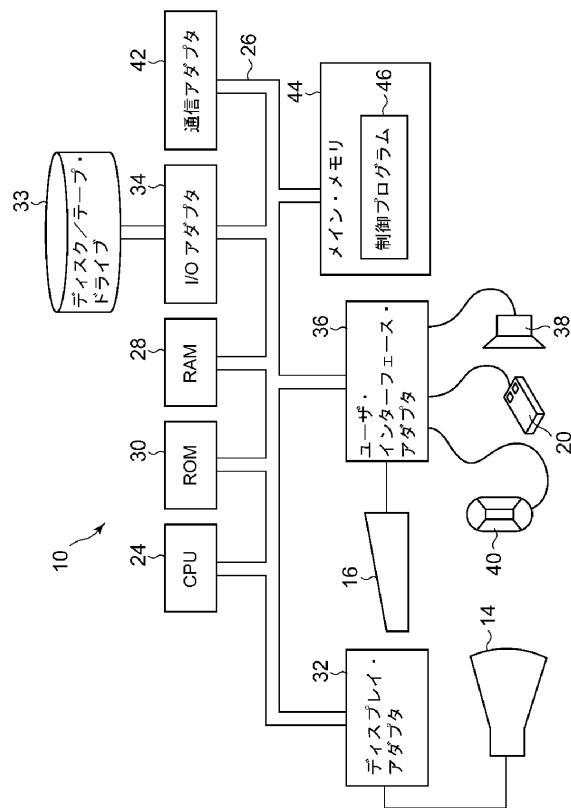

図2は、データ処理システム10を示すより詳細なブロック図である。図に示されるように、データ処理システム10は、従来のマイクロプロセッサなどの1つまたは複数の中央処理ユニット(CPU)、および、システム相互接続26を介して相互接続された、いくつかの他の構成要素を含む。図2には示されていないが、CPU24などのCPUは、通常、コンピュータ・メモリ内のデータおよびプログラム・ストレージを編成し、このデータおよび他の情報をコンピュータ・システムの様々な部分間で転送する、制御ユニットを含む。CPUは一般に、加算、比較、乗算などの算術的および論理的演算を実行する

40

50

、1つまたは複数の演算論理ユニットも含む。

【0014】

データ処理システム10は、ランダム・アクセス・メモリ(RAM)28、読み取り専用メモリ(ROM)30、ディスプレイ・デバイス14の接続をサポートするディスプレイ・アダプタ32、および周辺デバイス(たとえばディスクおよびテープ・ドライブ33)を接続するためのI/Oアダプタ34を、さらに含む。データ処理システム10は、データ処理システム10を通信ネットワークに接続するための通信アダプタ42と、キーボード16、マウス20、スピーカ38、マイクロフォン40、あるいは他のユーザ・インターフェース・デバイスまたはそれらすべてを、システム相互接続26に接続するための、ユーザ・インターフェース・アダプタ36とを、さらに含む。

10

【0015】

当業者であれば理解されるように、データ処理システム10は、RAM 28、ROM 30、磁気ディスク、磁気テープ、または光ディスク(最後の3つはディスクおよびテープ・ドライブ33内に配置される)などの、任意の好適なコンピュータ読み取り可能媒体に常駐可能な、オペレーティング・システム(たとえばAIX)および1つまたは複数の他のプログラムの制御の下で動作する。

【0016】

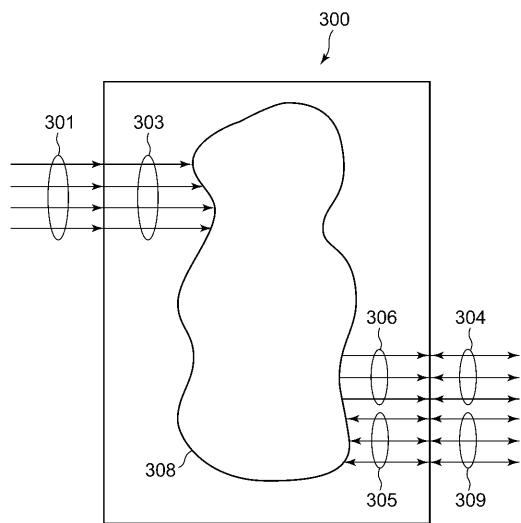

シミュレートされたデジタル回路設計モデルは、以下で設計エンティティと呼ばれる、少なくとも1つ、通常は多くの、サブユニットからなる。図3は、その内部に本発明の方法およびシステムが実装可能な、例示的設計エンティティ300のブロック図である。設計エンティティ300は、エンティティ名、エンティティ・ポート、および設計エンティティ300によって実行される機能の表現という、いくつかの構成要素によって定義される。所与のモデル内の各エンティティは、各エンティティのHDL記述で宣言された固有名(図3には明示的に図示せず)を有する。さらに各エンティティは、通常、ポートと呼ばれる、エンティティ外部の信号へのいくつかの信号相互接続を含む。これらの外部信号は、全体設計内の他のエンティティに接続している全体設計または信号の主入力/出力(I/O)とすることができます。

20

【0017】

通常、ポートは、入力ポート、出力ポート、および双方向ポートという、3つの別個のタイプのうちの1つに属するものと分類される。設計エンティティ300は、設計エンティティ300内に信号を搬送するいくつかの入力ポート303を有するものとして示される。入力ポート303は入力信号301に接続される。加えて、設計エンティティ300は、設計エンティティ300外部へ信号を搬送するいくつかの出力ポート306を含む。出力ポート306は出力信号304のセットに接続される。双方向ポート305は、設計ポート300の内部および外部へ信号を搬送するために使用される。双方向ポート305は、双方向信号309のセットに接続される。設計エンティティ300などのエンティティは、3つすべてのタイプのポートを含む必要がなく、悪くすると、まったくポートを含まない。エンティティ・ポートの外部信号への接続を実施するために、「ポート・マップ」と呼ばれるマッピング技法が使用される。ポート・マップ(図3には明示的に図示せず)は、エンティティ・ポート名とエンティティが接続された外部信号との間の指定された対応関係からなる。シミュレーション・モデルを構築する場合、E CADソフトウェアを使用し、ポート・マップ指定に従って、外部信号をエンティティの適切なポートに接続する。

30

【0018】

最後に、設計エンティティ300は、設計エンティティ300によって実行される1つまたは複数の機能を記述した本体部分308を含む。デジタル設計の場合、本体部分308は、他のエンティティのインスタンス化に加えて、論理ゲート、ストレージ要素などの相互接続を含む。他のエンティティ内にエンティティをインスタンス化することによって、全体設計の階層記述が達成される。たとえばマイクロプロセッサは、同一機能ユニットの複数インスタンスを含む場合がある。したがって、マイクロプロセッサそれ自体は、し

40

50

ばしば單一エンティティとしてモデル化されることになる。マイクロプロセッサ・エンティティ内では、任意の重複する機能エンティティの複数のインスタンス化が存在することになる。

【0019】

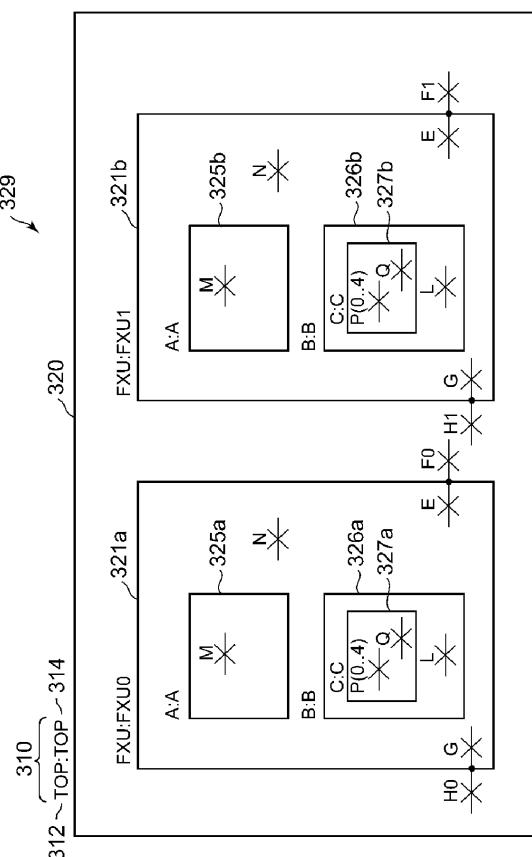

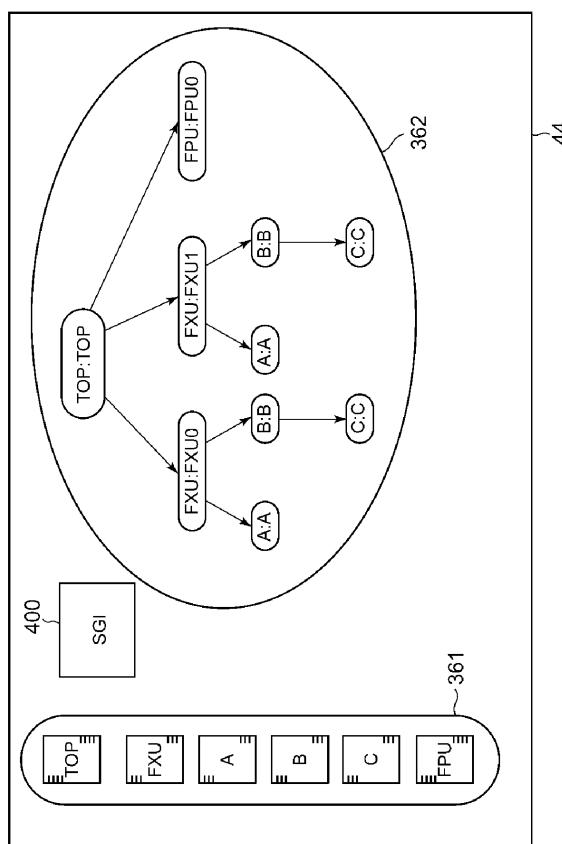

次に図4を参照すると、本発明の好ましい実施形態で使用可能な例示的シミュレーション・モデル329の概略図が示されている。シミュレーション・モデル329は、複数の階層的な設計エンティティを含む。視覚的に単純かつ明瞭にするために、シミュレーション・モデル329内のエンティティを相互接続するポートおよび信号の多くは明示的に示されていない。いかなるモデルにおいても、唯一のエンティティがいわゆる「最上位エンティティ」である。最上位エンティティ320は、シミュレーション・モデル329内のすべての他のエンティティを包含するエンティティである。すなわち、最上位エンティティ320は、設計内のすべての下位(descendant)エンティティを直接または間接的にインスタンス化する。シミュレーション・モデル329は、FXUエンティティ321の2つのインスタンスである321aおよび321bを直接インスタンス化する、最上位エンティティ320からなる。各インスタンス化は、エンティティ名および固有のインスタンス化名を含む関連記述を有する。最上位エンティティ320の場合、記述310は「TOP:TOP」とラベル表示される。記述310は、コロンに先行する「TOP」としてラベル表示されたエンティティ名312を含み、コロンに続く「TOP」としてラベル表示されたインスタンス化名314も含む。

【0020】

FXUエンティティ321のインスタンス化321aおよび321bで示されるように、特定のエンティティを複数回インスタンス化することが可能である。インスタンス化321aおよび321bは、それぞれ、インスタンス化名FXU0およびFXU1を備えた、FXUエンティティ321の別個のインスタンス化である。最上位エンティティ320は、シミュレーション・モデル329の階層内の最高レベルにある。下位エンティティをインスタンス化するエンティティは、以下では、下位エンティティの「上位(ancestor)」と呼ばれる。したがって、最上位エンティティ320は、FXUエンティティ・インスタンス化321aおよび321bを直接インスタンス化する上位である。シミュレーション・モデル階層の任意の所与のレベルで、すべてのインスタンス化のインスタンス化名が固有でなければならない。

【0021】

FXUエンティティ321のインスタンス化321a内では、エンティティA 325およびエンティティB 326の單一インスタンス・エンティティ325aおよび326aが、それぞれ直接インスタンス化される。同様に、同じFXUエンティティのインスタンス化321bは、それぞれエンティティA 325およびエンティティB 326のインスタンス化325bおよび326bを含む。同様に、インスタンス化326aおよびインスタンス化326bはそれぞれ、エンティティC 327の單一インスタンスを、それぞれエンティティ327aおよび327bとして直接インスタンス化する。

【0022】

インスタンス化されたすべてのエンティティが、別個または複合的にかかわらず固有のエンティティ名を有し、任意の所与のレベルの階層のインスタンス化名が互いに固有であると想定すると、他のエンティティ内にエンティティをネストすることは、任意レベルの複雑さまで続行することができる。各エンティティは、エンティティを記述するために必要な情報を含む1つまたは複数のHDLファイルから構築される。

【0023】

各エンティティのインスタンス化との関連付けが、いわゆる「インスタンス化識別子」である。所与のインスタンス化のインスタンス化識別子は、最上位エンティティ・インスタンス化名から始まるエンクロージング・エンティティ・インスタンス化名からなる文字列である。たとえば、FXUエンティティ321のインスタンス化321a内にあるエンティティC 327のインスタンス化327aのインスタンス化識別子は、「TOP.F

10

20

30

40

50

X U 0 . B . C 」である。この識別子は、シミュレーション・モデル内の各インスタンス化を固有に識別する働きをする。

【 0 0 2 4 】

例示的シミュレーション・モデル 3 2 9 内では、様々な信号がインスタンス化される（たとえば信号 E、F 0、F 1、G、H 0、H 1、L、M、N、P、および Q）。各信号は、関連する信号名（たとえば「M」）と、好ましい実施形態では最上位レベル・エンティティ・インスタンス化名から始まり信号名で終わる、エンクロージング・エンティティ・インスタンス化名からなる文字列である、信号インスタンス化識別子とを有する。したがって、F X U エンティティ 3 2 1 のインスタンス化 3 2 1 a 内にある信号 M のインスタンス化識別子は「T O P . F X U 0 . A . M」である。このインスタンス化識別子は、シミュレーション・モデル内の各信号インスタンス化を固有に識別する働きをする。たとえば信号 P ( 0 . . 4 ) などの信号は、マルチビット信号ベクトルとすることができるに留意されたい。また、いくつかの信号（たとえば信号 T O P . F X U 0 . E、T O P . F X U 1 . E、T O P . F X U 0 . G、T O P . F X U 1 . G）は、設計エンティティの境界線を越えると（それぞれ、信号 T O P . F X U 0 . F 0、T O P . F X U 1 . F 1、T O P . F X U 0 . H 0、T O P . F X U 1 . H 1 として）リネームされることにも留意されたい。

10

【 0 0 2 5 】

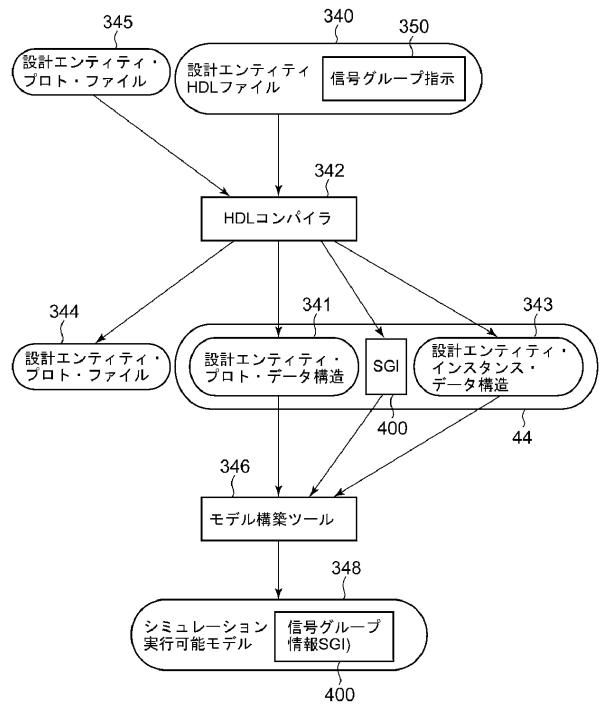

次に図 5 を参照すると、本発明の好ましい実施形態で実装可能なモデル構築プロセスの流れ図が示されている。このプロセスは、1 つまたは複数の設計エンティティ HD L ソース・コード・ファイル 3 4 0、および、潜在的には、H D L コンパイラ 3 4 2 の以前のランから入手可能な、以下では「プロト・ファイル」3 4 5 と呼ばれる 1 つまたは複数の設計エンティティ 中間フォーマット・ファイル 3 4 5 で始まる。H D L コンパイラ 3 4 2 は、シミュレーション・モデルの最上位エンティティで始まり、完全なシミュレーション・モデルを記述するすべての H D L またはプロト・ファイルを介して再帰的に進行する、H D L ファイル 3 4 0 を処理する。

20

【 0 0 2 6 】

コンパイル・プロセス中の各 H D L ファイル 3 4 0 について、H D L コンパイラ 3 4 2 は、以前にコンパイルされたプロト・ファイルが使用可能であり整合性を持つかどうかを判別するために、プロト・ファイル 3 4 5 を検査する。こうしたファイルが使用可能であり整合性を持つ場合、H D L コンパイラ 3 4 2 はその特定のファイルを再コンパイルせず、むしろ現存のプロト・ファイルを参照することになる。使用可能なこうしたプロト・ファイルがなく、プロト・ファイルが整合性を持たない場合、H D L コンパイラ 3 4 2 は当該の H D L ファイル 3 4 0 を明示的に再コンパイルし、その後のコンパイルで使用するためにプロト・ファイル 3 4 4 を作成する。こうしたプロセスは、以下では「増分コンパイル」と呼ばれ、シミュレーション実行可能モデル 3 4 8 を作成するプロセスを大幅にスピードアップすることができる。H D L コンパイラ 3 4 2 によっていったん作成されると、プロト・ファイル 3 4 4 は、その後のコンパイルでプロト・ファイル 3 4 5 として働くように使用可能である。

30

【 0 0 2 7 】

プロト・ファイル 3 4 4 に加えて、H D L コンパイラ 3 4 2 は、コンピュータ・システム 1 0 のメモリ 4 4 内に、設計エンティティ・プロト・データ構造 3 4 1 および設計エンティティ・インスタンス・データ構造 3 4 3 という、2 つのデータ構造セットも作成する。設計エンティティ・プロト・データ構造 3 4 1 および設計エンティティ・インスタンス・データ構造 3 4 3 は、シミュレーション実行可能モデル 3 4 8 のコンテンツのメモリ・イメージとして働く。データ構造 3 4 1 および 3 4 3 は、メモリ 4 4 を介して、データ構造 3 4 1 および 3 4 3 をシミュレーション実行可能モデル 3 4 8 に処理するモデル構築ツール 3 4 6 へと渡される。

40

【 0 0 2 8 】

以下では、各エンティティが单一の H D L ファイルによって記述されるものと想定され

50

る。本発明が実施される規則または特定のHDLに応じて、この制約が必要な可能性がある。しかしながら、特定の環境では、または特定のHDLについては、複数のHDLファイルを使用することによってエンティティを記述することができる。当業者であれば、エントリが複数のHDLファイルによって記述できる場合に、本発明を実施するために必要な拡張を理解されよう。さらに、各エンティティについて、エンティティ名と、エンティティを表すHDLファイルの名前およびそのエンティティのプロト・ファイルの名前の両方との間に、直接の対応関係があるものと想定される。

#### 【0029】

以下の説明では、所与のエンティティに対応するHDLソース・コード・ファイルは、エンティティ名の後に「.vhd1」を付けて呼ばれることになる。たとえば、最上位エンティティ320を記述するHDLソース・コード・ファイルは、TOP.vhd1と呼ばれることになる。このラベル表示規則は、単なる表記上の便宜として働くものであり、本発明の適用可能性をVHDL以外のHDLに限定するものと解釈すべきではない。

#### 【0030】

図4に戻ると、各エンティティが、1つまたは複数の他のエンティティを直接または間接的にインスタンス化できることがわかる。たとえば、FXUエンティティは、Aエンティティ325およびBエンティティ326を直接インスタンス化する。さらにBエンティティ326はCエンティティ327を直接インスタンス化する。したがって、FXUエンティティ321は、Aエンティティ325、Bエンティティ326、およびCエンティティ327を、直接または間接的にインスタンス化する。他のエンティティによって直接または間接的にインスタンス化されるそうしたエンティティを、以下では「下位」と呼ぶ。最上位エンティティ320の下位は、FXUエンティティ321、Aエンティティ325、Bエンティティ326、およびCエンティティ327である。各エンティティが下位の固有セットを有すること、ならびに、エンティティがインスタンス化されるごとに、エンティティの固有インスタンスおよびその下位が作成されることがわかる。シミュレーション・モデル329内では、FXUエンティティ321は、最上位エンティティ320によって、FXU:FXU0\_321aおよびFXU:FXU1\_321bの2回インスタンス化される。FXUエンティティ321の各インスタンス化は、FXU、A、B、およびCエンティティのインスタンスの固有セットを作成する。

#### 【0031】

各エンティティについて、「部品表」またはBOMと呼ばれるものを定義することができる。BOMは、エンティティそれ自体およびエンティティの下位の日付および時刻スタンプを有する、HDLファイルのリストである。再度図5を参照すると、エンティティのコンパイル後、エンティティのBOMはプロト・ファイル344に格納される。したがって、HDLコンパイラ342がHDLファイル340の中の特定のHDLソース・コード・ファイルをコンパイルする場合、もしもあれば、エンティティおよびエンティティの下位を構成するHDLファイル340をリスト表示するBOMを含むプロト・ファイル344が生成される。BOMは、HDLファイルがコンパイルされていたときにコンピュータ・システム10のディスク/テープ33上に出現するたびに参照された、HDLファイルのそれについての日付および時刻スタンプも含む。

#### 【0032】

エンティティまたはエンティティの下位を構成するいずれかのHDLファイルが後に変更された場合、プロト・ファイル344は不整合としてフラグが立てられ、以下でより詳細に説明するように、HDLコンパイラ342は後続の再コンパイルでHDLファイル340を再コンパイルすることになる。たとえば図4に戻ると、FXUエンティティ321のBOMによって参照されるHDLファイルは、それぞれ適切な日付および時刻スタンプを備えた、FXU.vhd1、A.vhd1、B.vhd1、およびC.vhd1である。最上位エンティティ320のBOMによって参照されるファイルは、適切な日付および時刻スタンプを備えた、TOP.vhd1、FXU.vhd1、A.vhd1、B.vhd1、C.vhd1、およびFPU.vhd1である。

10

20

30

40

50

〔 0 0 3 3 〕

図 5 に戻ると、HDL コンパイラ 342 は、コンピュータ・システム 10 のメイン・メモリ 44 内にシミュレーション・モデルの構造のイメージを作成する。このメモリ・イメージは、「プロト」データ構造 341 および「インスタンス」データ構造 343 という構成要素からなる。プロトとは、モデル内の各エンティティについて、エンティティのポートに関する情報、エンティティの本体コンテンツ、およびエンティティによって直接インスタンス化された他のエンティティへの参照のリストを含む、データ構造のことである（以下では、「プロト」という用語は、前述のメモリ内データ構造を言い表すために利用され、「プロト・ファイル」という用語は、中間フォーマット・ファイル 344 を記述するために利用される）。したがってプロト・ファイル 344 は、HDL コンパイラ 342 によって生成されるメモリ内プロト・データ構造のディスク上表現である。

〔 0 0 3 4 〕

インスタンス・データ構造とは、モデル内のエンティティの各インスタンスについて、インスタンスのインスタンス名、インスタンスが参照するエンティティの名前、および、エンティティを外部信号と相互接続するために必要なポート・マップ情報を含む、データ構造のことである。コンパイル時に、各エンティティはプロト・データ構造を1つだけ有することになるが、エンティティの複数のインスタンス化の場合、各エンティティは1つまたは複数のインスタンス・データ構造を有することができる。

〔 0 0 3 5 〕

モデルを効率よく増分的にコンパイルするために、HDLコンパイラ342は、プロト・ファイル345が使用可能であり、それらのエンティティおよびそれらの下位を構成するHDLソース・ファイルと整合性を持つ場合、モデルの連続エンティティがこうしたファイルから考慮およびロードされる、再帰的コンパイル方法に従う。既存のプロト・ファイル345からロードできない各エンティティの場合、HDLコンパイラ342はエンティティの下位を再帰的に検査し、プロト・ファイル345から使用可能なそれらの下位エンティティをロードし、プロト・ファイル345と不整合なそれらの下位について、必要に応じてプロト・ファイル344を作成する。HDLコンパイラ342のメイン制御ループに関する擬似コードが、以下に示される（擬似コードの右側のライン番号は擬似コードの一部ではなく、単に表記上の便宜としての働きをする）。

【数1】

```

process_HDL_file(file)          5

{

if (NOT proto_loaded(file)) { 10

if (exists_proto_file(file) AND check_bom(file)) { 15

load_proto(file); 20

} else { 30

parse_HDL_file(file) 35

for (all instances in file) { 40

process_HDL_file(instance); 45

}

create_proto(file); 55

write_proto_file(file); 60

}

}

create_instance(file); 70

}

create_instance(file); 75

}

```

【 0 0 3 6 】

コンパイラ 342 が初期に呼び出された場合、プロト・データ構造 341 またはインスタンス・データ構造 343 がコンピュータ・システム 10 のメモリ 44 内に存在する。メイン制御ループである、ルーチン `process_HDL_file()` ( ライン 5 ) が呼び出され、パラメータ「`file`」によって、最上位エンティティの名前が渡される。アルゴリズムは第 1 に、現在のエンティティに関するプロト・データ構造がメモリ 44 内に存在するかどうかを、ルーチン `proto_loaded()` ( ライン 15 ) を使用して判別する。いかなるプロト・データ構造もメモリ 44 にロードされることなくプロセス 50

が開始されるため、最上位エンティティに関するプロト・データ構造は、決してメモリ内に存在しないことに留意されたい。メモリ44内に合致するプロト・データ構造が存在する場合、現在のエンティティおよび現在のエンティティの下位に関するインスタンス・データ構造があれば、必要に応じて、ルーチン `create_instance()` (ライン75) によって、メモリ44内に作成される。

#### 【0037】

しかしながら、合致するプロト・データ構造がメモリ44内に存在しない場合、制御はライン20に渡され、ここでルーチン `exists_proto_file()` は、エンティティに関するプロト・ファイルが存在するかどうかを判別するために、プロト・ファイル345を検査する。合致するプロト・ファイルが存在する場合、および存在する場合にのみ、プロト・ファイル345が整合性を持つかどうかを判別するために、ルーチン `check_bom()` が呼び出される。プロト・ファイルが整合性を持つかどうかを判別するために、プロト・ファイルに関するBOMが検査される。ルーチン `check_bom()` は、HDLソース・コード・ファイルに関する日付または時刻スタンプが変更されたかどうか、あるいは、HDLソース・コード・ファイルが削除されたかどうかを判別するために、BOM内にリスト表示された各HDLソース・コード・ファイルを検査する。BOM内の任意のファイルに対しても、その状態が発声した場合、プロト・ファイルは不整合であり、ルーチン `check_bom()` は失敗する。しかしながら、`check_bom()` が成功した場合、制御はライン25に渡され、ここでルーチン `load_proto()` はプロト・ファイルおよび任意の下位プロト・ファイルをメモリ44内にロードし、現在のエンティティおよび、あれば現在のエンティティの下位に関するプロト・データ構造341を作成する。`process_HDL_file()` の構造は、いったんプロト・ファイルが整合性を持つとして検証されると、その下位プロト・ファイルもすべて整合性を持つことを保証する。

#### 【0038】

プロト・ファイルが実在しないか、または不整合である場合、制御はライン35に渡され、ここでルーチン `parse_HDL_file()` は、現在のエンティティに関するHDLソース・コード・ファイルをロードする。ルーチン `parse_HDL_file()` (ライン35) は、構文上の正確さについてHDLソース・コード・ファイルを検査し、もしもあれば、どちらの下位エンティティが現在のエンティティによってインスタンス化されるかを決定する。ライン40、45、および50は、現在のエンティティによって呼び出される下位エンティティを処理するために、ルーチン `process_HDL_file()` が再帰的に呼び出されるループを構成する。このプロセスでは、現在のエンティティのすべての下位のプロト・データ構造341およびプロト・データ・ファイル344を作成する縦型様式 (depth-first fashion) で、現在のエンティティのすべての下位のトラバースを再帰的に繰り返す。下位エンティティが処理されると、制御はライン55に渡され、ここでルーチン `create_proto()` によって、メモリ44内に現在のエンティティに対して新しいプロト・データ構造が作成される。次に、制御はライン60に渡され、ここで、関連するBOMを含む新しいプロト・ファイル344がルーチン `write_proto_file()` によってディスク33に書き込まれる。最終的に、制御はライン75に渡され、ここでルーチン `create_instance()` は、現在のエンティティおよび必要に応じて任意の下位エンティティに対してインスタンス・データ構造343を作成する。このようにして、`process_HDL_file()` (ライン5) は、プロト・データ構造341およびインスタンス・データ構造343からなるモデルのメモリ内イメージを作成するシミュレーション・モデル全体を、再帰的に処理する。

#### 【0039】

さらに図5に示されるように、さらに本発明は、シミュレーション実行可能モデル348のシミュレートの結果を表示する際に注目される可能性が高い特定の信号を識別する、1つまたは複数の信号グループ指示350を、設計者が設計エンティティHDLファイル

10

20

30

40

50

340内に含められるようにする。信号グループ指示350に対する例示的なセマンティクスについて、図12～図13を参照しながら以下で説明する。前述の処理に加えて、HDLコンパイラ342は、任意の便利なデータ構造（たとえばリンク付きリスト、テーブルなど）を使用する注目される信号の信号インスタンス化識別子を表す信号グループ情報（SGI）400を生成するために、好ましくは信号グループ指示350を処理する。モデル構築ツール346は、次に、オプションで何らかのフォーマットの追加変換を使用して、信号グループ情報（SGI）400をシミュレーション実行可能モデル348内に配置する。

#### 【0040】

ここで図6を参照すると、本発明の好ましい実施形態で実装可能な、コンパイル済みデータ構造を表すブロック図が示されている。メモリ44は、シミュレーション・モデル329内で参照されるエンティティそれぞれについて1つの、プロト・データ構造361を含む。加えて、シミュレーション・モデル329におけるインスタンス化はインスタンス・データ構造362によって示される。インスタンス・データ構造362は、シミュレーション・モデル329内のエンティティのインスタンス化の階層的性質を示すポインタによって接続される。最終的に、メモリ44はSGI400を含む。図5のモード構築ツール346は、シミュレーション実行可能モデル348を生成するために、メモリ44のコンテンツをメモリ・データ構造に処理する。

#### 【0041】

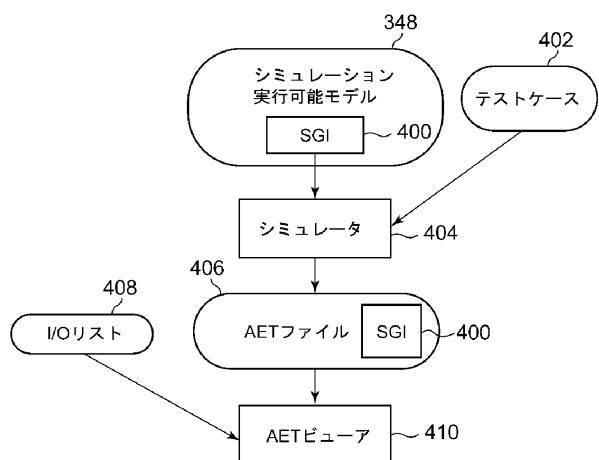

次に図7を参照すると、本発明に従って設計をシミュレートし、シミュレーション結果を表示するためのプロセスの流れ図が示されている。図に示されるように、図5のプロセスによってシミュレーション実行可能モデル348が取得されると、デジタル設計の動作をシミュレートするためのテストケース402を利用してシミュレーション実行可能モデル348をシミュレートするために、ソフトウェアあるいはハードウェアまたはその両方のシミュレータ404が使用される。シミュレーション時には、全イベント・トレース（AET）ファイル406が、テストケース402に対するシミュレーション実行可能モデル348の応答を表すデータを記録する。AETファイル406内のデータは、経時にシミュレーション実行可能モデル348ならびにSGI400内の様々な信号あるいはストレージ要素またはその両方の値を含む。

#### 【0042】

AETファイル406のコンテンツを再検討するために、ユーザは一般に、本明細書ではAETビューア410と呼ばれる、別個のまたは一体化されたビューア・プログラムを採用する。たとえばユーザは、AETファイル406からのデータを、ディスプレイ画面22内にグラフィカル・フォーマットで、またはハードコピー・フォーマットで提示するように、AETビューア410に要求することができる。前述のようにユーザは、データ・セット（本明細書ではI/Oリスト408と呼ばれる）内に注目する信号を指定することによって、AETビューア410によるデータのプレゼンテーションを、注目する特定の信号に有利に限定することができる。

#### 【0043】

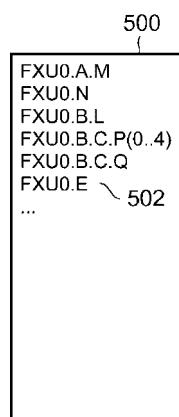

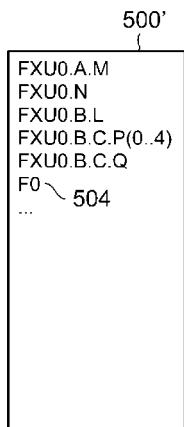

図8に示されるように、従来技術に従った従来のI/Oリスト500は、それぞれが注目する信号のうちの1つの信号インスタンス化識別子を示す大量のエントリを含むリストであり、この場合は図4のFXUインスタンス化321a内のすべての信号を備える。したがって、図8で与えられた簡略化された例から理解されるように、従来技術では、ユーザは、潜在的に大量の信号インスタンス化識別子のそれぞれを、キーボード16を使用して入力しなければならない。信号インスタンス化識別子を手動でキー入力するこの従来の技法は、退屈でエラーの起こりやすいものである。

#### 【0044】

加えて、一部のシミュレータ404は、設計エンティティの境界線をより高水準の設計エンティティへと越境する下位設計エンティティ内の信号の信号名を保護しない。その代わりに、AETファイルにおける信号の重複をなくすために、こうしたシミュレータ40

10

20

30

40

50

4は、その内部に出現する最高位設計エンティティ内のその信号名によってのみ、A E T ファイル内の信号を識別する。したがって、信号名を保護しないシミュレータ404が採用される場合、ユーザは、信号が出現する最高水準設計エンティティからの信号の信号名を採用する信号インスタンス化識別子を利用して、I / Oリスト500内に信号を指定しなければならない。たとえば、図8のエントリ502と図9のI / Oリスト500'の対応するエントリ504とを比較することでわかるように、信号名を保護しないシミュレータ404のユーザは、参照番号502で示されるような信号インスタンス化識別子F X U . E ではなく、参照番号504で示されるような信号インスタンス化識別子F 0 を利用しなければならない。理解されるように、作業が主に下位設計エンティティに関連するA E Tビューア410のユーザは、ユーザが精通している低水準設計エンティティをインスタンス化する、より高水準の設計エンティティ内で使用される信号名を決定すること、または容易に想起することが、困難な可能性がある。

10

#### 【0045】

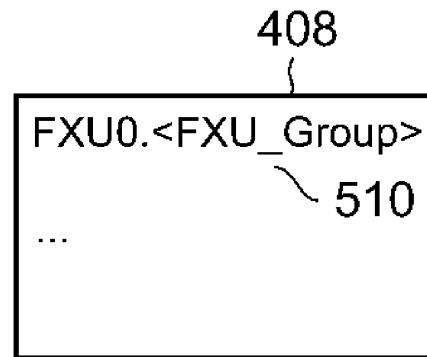

従来のI / Oリスト500または500'の代わりに、本発明は、A E Tビューア410のユーザが、図10に従って、1つまたは複数の改良されたI / Oリスト408を利用してA E Tファイル406からのデータのプレゼンテーションを代わりにフィルタリングできるようにする。図10に示されるように、I / Oリスト408は、1つまたは複数のエントリを含むリストである。図8または図9に示されるような従来の信号インスタンス化識別子を含むゼロまたはそれ以上のエントリに加えて、エントリ510などのI / Oリスト408のエントリは、S G I 400内の情報に対応する信号グループ・インスタンス化識別子によって、注目する1つまたは複数の信号のグループを識別することができる。

20

#### 【0046】

図に示されるように、信号グループ・インスタンス化識別子は、信号インスタンス化識別子と同様に形成され、最高位エンティティ・インスタンス化名から始まり、括弧付きコンテンツが別の信号グループ名前空間のメンバであることを示す1対の山括弧（「<」および「>」）によって囲まれた信号グループ名で終わる、エンクロージング・エンティティ・インスタンス化名の文字列からなる。したがって、F X Uエンティティ・インスタンス化321a内で注目する6つの信号は、信号インスタンス化識別子をI / Oリスト408内に個々に入力するのではなく、單一エントリ「F X U 0 . < F X U \_ G r o u p >」によって簡単に識別することができる。前述のように、信号グループF X U \_ G r o u p を備える個々の信号は、設計エンティティH D Lファイル340内の信号グループ指示350を利用して指定される。

30

#### 【0047】

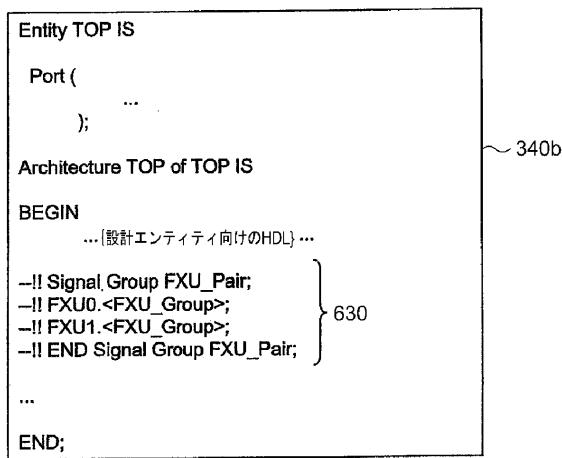

次に、図12を参照すると、本発明に従った設計エンティティH D Lファイル340aの例示的実施形態が示される。当業者であれば理解されるように、設計エンティティH D Lファイル340aは、この場合は設計エンティティF X U \_ 321である、設計エンティティを記述する従来のH D Lソース・コードを含む。従来のH D Lソース・コードは、ポート・マップ600および信号割り当てステートメント602を含む。加えて、設計エンティティH D Lファイル340aは、本発明に従った信号グループ指示350（図5）を含む従来のH D Lコメントを含む。

40

#### 【0048】

設計エンティティH D Lファイル340aでは、信号グループ指示350は、信号グループ宣言610および信号保護指示620という、2つの異なるタイプの信号グループ指示を含む。信号グループ宣言610は「- - ! ! S i g n a l \_ G r o u p \_ s i g n a l \_ g r o u p \_ n a m e ;」の形のH D Lコメントで始まり、「- - ! ! E N D \_ S i g n a l \_ G r o u p \_ s i g n a l \_ g r o u p \_ n a m e ;」の形のH D Lコメントで終わるが、ここでs i g n a l \_ g r o u p \_ n a m e は所与のターゲット設計エンティティに対して固有の信号グループ名（この例ではF X U \_ G r o u p ）である。信号グループ宣言610の最初と最後の間に、注目する1つまたは複数の信号の信号名が、A E Tビューア410によって所望のプレゼンテーション順にリスト表示される。この実施形

50

態では、信号名はターゲット設計エンティティ（たとえばFXU設計エンティティ321）に関して指定される。本発明の少なくとも一部の実施形態は、設計エンティティ階層内で、次に高位の階層を示すために、慣用構文「..」を利用して、ターゲット設計エンティティに関してより上位の信号名を指定することができる。

#### 【0049】

ユーザは、好ましくは、信号グループ宣言610内の信号のプレゼンテーションに関して、追加の属性をさらに指定することができる。たとえば、ユーザは、信号の所望の色、波形またはバイナリ信号表現のデフォルト、非整列ビット・ベクトルの所望の位置合わせなどを指定することができる。したがって、信号グループ宣言610のステートメント612では、ユーザは5ビット信号ベクトルB.C.P(0..4)の左位置合わせを指定している。

10

#### 【0050】

さらに図13の設計エンティティHDLファイル340bに示されるように、信号グループ宣言630などの信号グループ宣言も、好ましくは、ユーザが任意の正当な深さまでネストされた信号グループを指定できるようにする。より大規模な信号グループの一部を含むネストされた信号グループを指定するために、ユーザは、山括弧（すなわち「<」および「>」）に囲まれた信号グループを備えたネストされた信号グループのインスタンス化識別子を参照する信号グループ宣言内に、ステートメントを含めるだけである。山括弧を使用することで、HDLコンパイラ342は、信号の名前空間と信号グループ名との間を区別することができる。

20

#### 【0051】

再度図12を参照すると、信号保護指示620を利用して、特定のリネームされた信号（たとえば信号G）を保存するために、デフォルトでは、リネームされた信号より低位の信号名を保存しないことをシミュレータ404に指示する。したがって、シミュレータ404がデフォルトではリネームされた信号の低位の名前を保護しないものと想定すると、AETファイル406は、信号インスタンス化識別子TOP.FXU0.GおよびTOP.FXU1.Gに関するデータを含むことになる。図9に関して上記で述べたように、精通した信号名を保護するための機能により、ユーザが、保護された信号Gの信号データを表示するために、精通していない可能性のある信号インスタンス化識別子TOP.FXU1.H0およびTOP.FXU1.H1をI/Oリストに入力する必要がなくなる。

30

#### 【0052】

次に図14～図16を参照すると、本発明に従った、AETビューア410がI/Oリスト408を処理する際に使用する例示的プロセスの高水準論理流れ図が示される。論理流れ図として、動作は順番ではなく論理的に示され、示された動作の多くは並行して、または代替順で実行することができる。

#### 【0053】

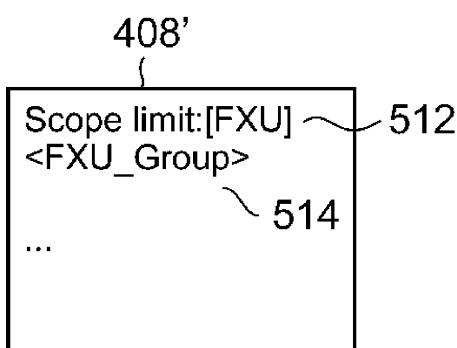

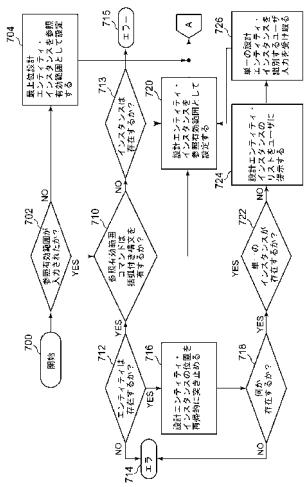

図に示されるように、プロセスは図14のブロック700で始まり、その後、ユーザがI/Oリスト408の参照有効範囲、すなわち、参照によりすべての他のI/Oリスト・エントリが解析されるシミュレーション実行可能モデル348の有効範囲に入ったか否かの判別を示す、ブロック702へと進む。デフォルトでは、参照有効範囲は、シミュレーション実行可能モデル348内の最上位設計エンティティ・インスタンス、たとえば図4の最上位設計エンティティ・インスタンスである。一実施形態では、ユーザは「Scope limit: instance\_string0.[design\_entity].instance\_string1」の形の参照有効範囲をさらに限定するコマンドを入力することが可能であり、ここでinstance\_string0およびinstance\_string1はオプションの設計エンティティ・インスタンス文字列であり（instance\_string0は最上位設計エンティティ・インスタンスで始まる）、角括弧で囲まれたdesign\_entityはオプションの設計エンティティ名である。正当な参照有効範囲コマンドは、3つのオプション・フィールド、instance\_string0、[design\_entity]、およびinstance\_st

40

50

ing 1 のうちの少なくとも 1 つを含む。参照有効範囲コマンドは、たとえばコマンド行を介して A E T ビューア 4 1 0 に、または I / O リスト 4 0 8 内に送ることができる。I / O リスト 4 0 8 に挿入された場合、参照有効範囲コマンドは、好ましくはその I / O リスト 4 0 8 内のすべてのエントリに適用される。

#### 【 0 0 5 4 】

ブロック 7 0 2 で示されるように、ユーザが異なる参照有効範囲を入力していない場合、ブロック 7 0 4 で示されるように、A E T ビューア 4 1 0 はデフォルトで、参照有効範囲をシミュレーション実行可能モデル 3 4 8 の最上位設計エンティティ・インスタンスに設定する。その後、プロセスはページ連結子 A を通って図 1 5 へと進む。A E T ビューア 4 1 0 がブロック 7 0 2 で、ユーザが異なる参照有効範囲を入力したものと判別した場合、A E T ビューア 4 1 0 は、ブロック 7 1 0 で、参照有効範囲コマンドが括弧付き構文(たとえば [ design\_entity ]) を含むか否かを判別するために参照有効範囲コマンドをさらに解析する。含まない場合、プロセスは、参照有効範囲コマンドによって指定された設計エンティティ・インスタンスがシミュレーション実行可能モデル 3 4 8 内に存在するか否かを、A E T ビューア 4 1 0 が判別することを示す、ブロック 7 1 3 に進む。存在しない場合、プロセスはブロック 7 1 5 でエラー終了する。存在する場合、プロセスはブロック 7 1 3 からブロック 7 2 0 へと渡され、ここで A E T ビューア 4 1 0 は、参照有効範囲を、参照有効範囲コマンドの instance\_string 0 フィールド内に指定された特定の設計エンティティ・インスタンスに設定する。たとえば、図 4 のシミュレーション実行可能モデル 3 2 9 を想定すると、参照有効範囲コマンド「Scope 10 limit : TOP . FXU0」は、参照有効範囲を FXU 設計エンティティ 3 2 1 のインスタンス 3 2 1 a に設定する。この参照有効範囲の場合、図 1 0 の I / O リスト 4 0 8 のエントリ 5 1 0 は <FXU\_Group> として簡略化することができる。その後、プロセスはページ連結子 A を通って図 1 5 へと進む。

#### 【 0 0 5 5 】

ブロック 7 1 0 に戻ると、参照有効範囲コマンドが括弧付き構文を採用しているとの決定に応答して、A E T ビューア 4 1 0 は次に、ブロック 7 1 2 で、名前付き設計エンティティがシミュレーション実行可能モデル 3 4 8 内に存在するか否かを判別する。存在しない場合、プロセスはブロック 7 1 4 でエラー終了する。しかしながら、指定された設計エンティティがシミュレーション実行可能モデル 3 4 8 内に存在する場合、A E T ビューア 4 1 0 は、存在する場合は instance\_string 0 で定義されるシミュレーション実行可能モデル 3 4 8 の一部分に存在する設計エンティティのすべてのインスタンスを識別するために、シミュレーション実行可能モデル 3 4 8 を再帰的に検索する。ブロック 7 1 8 で示されるように、指定された設計エンティティのインスタンスが指定された有効範囲内に存在しない場合、プロセスはブロック 7 1 4 でエラー終了する。A E T ビューア 4 1 0 がブロック 7 1 8 で、指定された有効範囲内に、指定された設計エンティティの少なくとも 1 つのインスタンスの位置が突き止められたものと判別した場合、さらに A E T ビューア 4 1 0 は、ブロック 7 2 2 で、指定された有効範囲内に設計エンティティの単一のインスタンスのみが見つけられたかどうかを判別する。見つけられた場合、プロセスはブロック 7 2 0 へと渡され、ここで A E T ビューア 4 1 0 は、設計エンティティの単一のインスタンスを参照有効範囲として設定する。その後、プロセスはページ連結子 A を通って図 1 5 へと進む。

#### 【 0 0 5 6 】

A E T ビューア 4 1 0 が、ブロック 7 2 2 で、指定された有効範囲内に指定された設計エンティティの複数のインスタンスが見つけられたものと判別した場合、A E T ビューア 4 1 0 は、たとえばディスプレイ画面 2 2 内に表示されるグラフィカル・メニューを介して選択するために、設計エンティティ・インスタンスのリストをユーザに提示する(ブロック 7 2 4)。その後 A E T ビューア 4 1 0 は、ブロック 7 2 6 で示されるように、所望の参照範囲を定義する複数の設計エンティティ・インスタンスのうちの 1 つを指定するユーザ入力を受け取る。たとえば、図 4 のシミュレーション実行可能モデル 3 2 9 および図 10

11のI/Oリスト408'を想定すると、図11の参照番号512で与えられた参照有効範囲コマンド「Scope limit: [FXU]」は、AETビューア410に、シミュレーション実行可能モデル329内でFXUインスタンス321aおよび321bの位置を突き止めさせ、インスタンス321aおよび321bのインスタンス識別子を選択のためにユーザに提示させる。有利なことに、FXUインスタンス321aおよび321bのどちらが注目される、ユーザによって選択されるかに関わらず、信号グループは、図11のI/Oリスト408'のエントリ512に示されるように<FXU\_Group>として指定することができる。その後プロセスは、これまでに説明したブロック720に渡される。

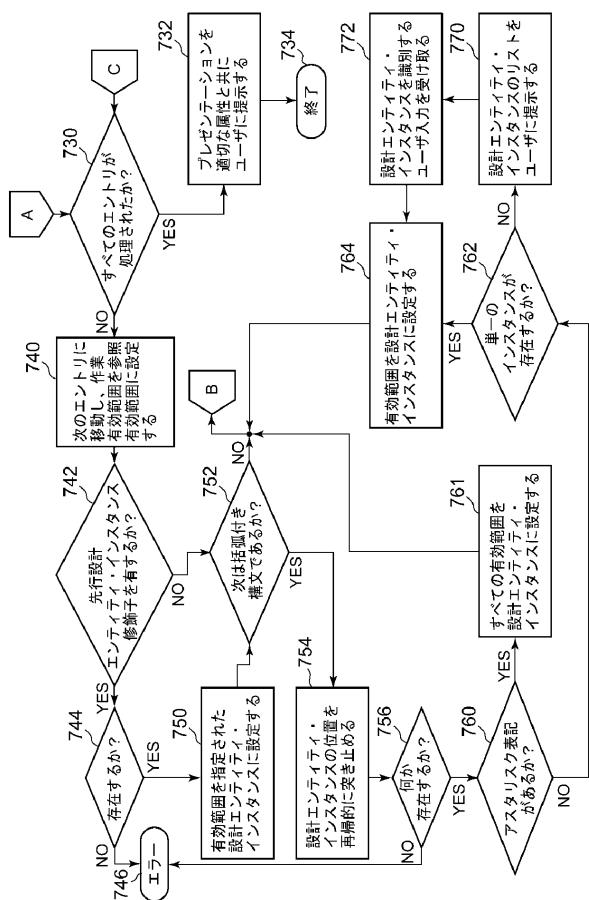

## 【0057】

10

次に図15を参照すると、プロセスはページ連結子Aで始まり、その後ブロック730へと進んで、AETファイル406のプレゼンテーションを構築するために、AETビューア410が1つまたは複数のI/Oリスト408内の各エントリを処理する、処理ループを提示する。ブロック730でAETビューア410が、I/Oリスト内のすべてのエントリが処理されたものと決定した場合、プロセスは以下で説明するブロック732へと渡される。しかしながら、I/Oリスト408内に、処理されるべき少なくとも1つのエントリが残っている場合、プロセスはブロック740へと進み、ここでAETビューア410は第1または次の信号識別エントリへと移動して、エントリの作業有効範囲を参照有効範囲へと初期化する。I/Oリスト408内の信号識別エントリは、参照有効範囲に関して処理され（すなわち参照有効範囲によって暗に限定され）、以下の形を取り、

```

instance_string2.[design_entity*].instance_string3.signals

```

上式で、instance\_string2およびinstance\_string3はオプションの設計エンティティ・インスタンス文字列であり、

角括弧（すなわち「[」および「]」）で囲まれたdesign\_entityはオプションの設計エンティティ名であり、

\*は、指定された有効範囲内のすべてのdesign\_entityインスタンスを示すオプションのユニバーサル演算子であり、

signalsは、信号名、山括弧（すなわち「<」および「>」）で囲まれた信号グループ名、または指定された有効範囲内のすべての信号グループを示す空の山括弧を指定する、必須パラメータである。

## 【0058】

30

図15に示されるプロセスは、ブロック740からブロック742へと進み、ここでAETビューア410は、現在の信号識別エントリが先行設計エンティティ・インスタンス修飾子（たとえばinstance\_string2）を有するかどうかを判別する。有さない場合、プロセスは以下で説明するブロック752へと渡される。有する場合、プロセスはブロック742からブロック744へと進み、ここでAETビューア410は、シミュレーション実行可能モデル348の参照有効範囲内に指定された設計エンティティ・インスタンスが存在するか否かを判別する。存在しない場合、プロセスはブロック746でエラー終了する。存在する場合、プロセスはブロック750へ進む。ブロック750は、現在の有効範囲を、設計エンティティ・インスタンス修飾子によって定義された有効範囲を参照有効範囲に追加することによって形成された有効範囲に設定する。次に、AETビューア410は、ブロック752で、I/Oリスト408の信号識別エントリ内の次のフィールドが、角括弧に囲まれたdesign\_entity修飾子であるか否かを判別する。括弧付き修飾子でない場合、プロセスはページ連結子Bを通って図16へと進む。括弧付き修飾子である場合、信号識別エントリの処理はブロック754へと続く。

## 【0059】

40

ブロック754は、AETビューア410が、指定された設計エンティティ名に合致するエンティティ名を有する現在の有効範囲内で、すべての設計エンティティ・インスタンスの位置を突き止めるために、シミュレーション実行可能モデル348を再帰的に検索す

50

ることを示す。その後 A E T ビューア 410 は、ブロック 756 で、何らかのこうした設計エンティティ・インスタンスが存在するか否かを判別する。存在しない場合、処理はブロック 746 でエラー状態で終了する。存在する場合、さらに A E T ビューア 410 は、ブロック 760 で、括弧付き構文が、指定された有効範囲内へのすべての設計エンティティ・インスタンスの包含を示すアスタリスクを含むか否かを判別する。含む場合、A E T ビューア 410 は、エントリの作業有効範囲を、ブロック 754 で突き止められた 1 つまたは複数の設計エンティティ・インスタンスまで狭める（ブロック 761）。その後プロセスは、ページ連結子 B を通って図 16 へと進む。

#### 【0060】

ブロック 760 に戻ると、否定の決定に応答して、プロセスはブロック 762 へと進み、ここで A E T ビューア 410 は、単一の設計エンティティ・インスタンスがブロック 754 で発見されたかどうかを判別する。発見された場合、ブロック 764 で、作業有効範囲は単一の設計エンティティ・インスタンスに設定される。その後プロセスは、ページ連結子 B を通って図 16 へと進む。これに対して、ブロック 762 で A E T ビューア 410 が、ブロック 754 で複数の設計エンティティ・インスタンスが発見されたものと決定した場合、A E T ビューア 410 は、たとえばディスプレイ画面 22 内に表示されるグラフィカル・メニューを介して選択するために、設計エンティティ・インスタンスのリストをユーザに提示する（ブロック 770）。その後、A E T ビューア 410 は、ブロック 772 で示されるように、所望の作業有効範囲を定義する複数の設計エンティティ・インスタンスのうちの 1 つまたは複数を指定するユーザ入力を受け取る。その後、プロセスはブロック 764 に渡され、ここで A E T ビューア 410 は、ユーザの選択に従って 1 つまたは複数の作業有効範囲を確立する。その後プロセスは、ページ連結子 B を通って図 16 へと進む。

10

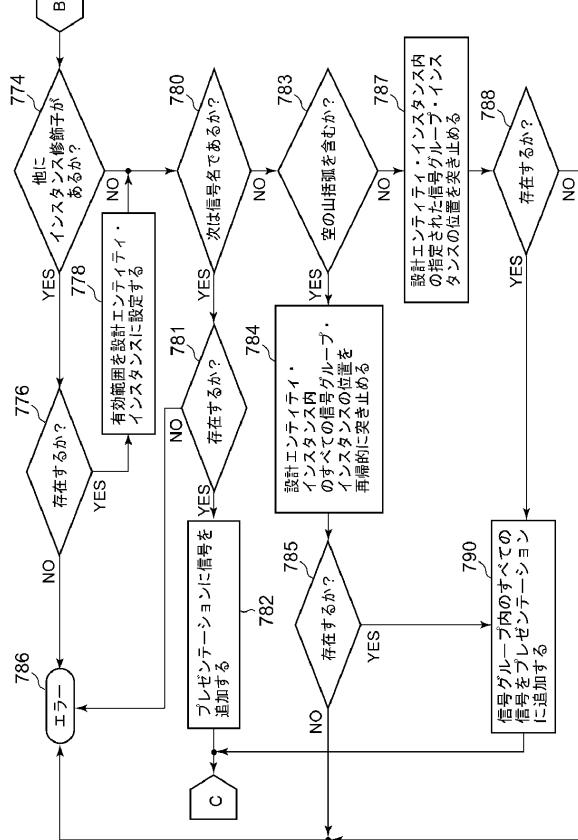

#### 【0061】

次に図 16 を参照すると、プロセスはページ連結子 B で開始され、その後ブロック 774 へ進み、ここでさらに A E T ビューア 410 は、エントリが作業有効範囲を制限するための他のインスタンス修飾子（たとえば `instance_string3`）を含むかどうかを判別するために、信号識別エントリを解析する。含まない場合、プロセスは以下で説明するブロック 780 へ渡される。含む場合、A E T ビューア 410 は、ブロック 776 で、指定された設計エンティティ・インスタンスが存在するか否かを判別する。存在しない場合、プロセスはブロック 786 でエラー終了する。指定された設計エンティティ・インスタンスが存在する場合、A E T ビューア 410 は、現在の信号識別エントリの作業有効範囲を、第 2 のインスタンス修飾子によって示された設計エンティティ・インスタンスまで狭める（ブロック 778）。その後、プロセスはブロック 780 に渡される。

20

#### 【0062】

ブロック 780 で、さらに A E T ビューア 410 は、エントリの終端 `signals` フィールドが単一の信号名または信号グループ名を含むかどうかを判別するために、I/O リスト 408 の信号識別エントリを解析する。`signals` フィールドが信号名を含む場合、次に A E T ビューア 410 は、ブロック 781 で、指定された信号が作業有効範囲内に存在するかどうかを判別する。存在しない場合、プロセスはブロック 786 でエラー状態で終了する。存在する場合、A E T ビューア 410 は、指定された信号を A E T ファイル 406 のプレゼンテーションに追加する（ブロック 782）。その後プロセスは、ページ連結子 C を介して図 15 のブロック 730 に戻る。

30

#### 【0063】

再度ブロック 780 を参照すると、信号識別エントリの `signals` フィールドが信号名を含まないとの決定に応答して、プロセスはブロック 783 へ渡され、ここで A E T ビューア 410 は、`signals` フィールドが空の山括弧を含むかどうかを判別する。含む場合、A E T ビューア 410 は、ブロック 784 に示されるように、作業有効範囲内にある設計エンティティ・インスタンス内のすべての信号グループ・インスタンスの位置を再帰的に突き止める。A E T ビューアがブロック 785 で、何も存在しないと決定した

40

50

場合、プロセスはブロック 786 でエラー終了する。これに対して、AET ビューア 410 がブロック 785 で、1つまたは複数の信号グループが存在すると決定した場合、AET ビューア 410 は、個々の信号が SGI 400 からの信号グループを備えることを決定し、ブロック 790 で、すべてのこうした信号をプレゼンテーションに追加する。その後プロセスは、ページ連結子 C を通じて図 15 に戻る。

#### 【0064】

ブロック 783 に戻り、AET ビューア 410 が、I/O リスト 408 の信号識別エントリの `signals` フィールドが空の山括弧を含まないが、その代わりに山括弧内に信号グループ名を指定するものと決定した場合、プロセスはブロック 787 に渡される。ブロック 787 で、AET ビューア 410 は、作業有効範囲内にある設計エンティティ・インスタンス内の指定された信号グループ・インスタンスのインスタンスの位置を再帰的に突き止める。ブロック 788 によって表されるように、信号グループ・インスタンスの位置が突き止められない場合、プロセスはブロック 786 でエラー状態で終了する。別の方 10 法として、名前付き信号グループの少なくとも 1 つのインスタンスの位置が突き止められた場合、プロセスはブロック 790 へと進み、以前に説明したブロックへと続く。

#### 【0065】

以上説明してきたように、本発明は、シミュレーション結果をプレゼンテーション用に処理するための方法、システム、およびプログラム製品を提供する。本発明によれば、シミュレーション結果のプレゼンテーションをフィルタリングするために必要なユーザ入力の量は、所定の信号グループの使用、およびオプションで有効範囲コマンドの使用によって、大幅に削減される。加えて、信号 リネーム が存在する中で信号名が 保護 されることになる信号を設計者が指定できるようにする信号 保護 指示のサポートを通じて、シミュレーション結果の理解しやすさが向上する。 20

#### 【0066】

以上、本発明について、好ましい実施形態を参照しながら具体的に説明してきたが、当業者であれば、本発明の趣旨および範囲を逸脱することなく、形式および細部における様々な変更が実行可能であることを理解されよう。たとえば、本発明の諸実施形態のうちの 1 つは、図 1 および図 2 で説明されたように全体として構成される 1 つまたは複数のコンピュータ・システムの、ランダム・アクセス・メモリ 28 または不揮発性ストレージ内に常駐するプログラム・コードを使用して、実装可能である。プログラム・コードのセットは、ユーザによって所望された場合、コンピュータ・システム 10 によって要求されるまで、ディスク・ドライブ 33 または CD-ROM などの他のコンピュータ読み取り可能ストレージ・デバイス内、あるいは他のコンピュータのデータ・ストレージ内に格納すること、および、ローカル・エリア・ネットワークまたはインターネットなどのワイド・エリア・ネットワークを介して伝送することが可能である。コンピュータ使用可能媒体内で具体化されたプログラム・コードは、コンピュータ・プログラム製品と呼ぶことができる。 30

#### 【0067】

(1) データ処理システムにおけるデータ処理の方法であって、

所定の信号グループ名によって信号グループを指定する少なくとも 1 つのエントリを含むデータ・セットを入力として受け取るステップと、 40

前記データ・セットの受け取りに応答して、

前記信号グループ名を識別するために、前記データ・セット内の前記エントリを処理するステップと、

前記信号グループのメンバである複数の信号の信号名を決定するために、シミュレーション結果を含むイベント・トレース・ファイルに関連付けられた信号グループ情報にアクセスするステップと、

前記複数の信号のインスタンスに関連付けられた前記イベント・トレース・ファイルからのそれらのシミュレーション結果を、プレゼンテーションに含めるステップと、

を有する、方法。

#### (2) シミュレーション実行可能モデル内でインスタンス化された設計エンティティを記

10

20

30

40

50

述するHDLソース・コード・ファイルを参照して前記信号グループ内の前記信号名のメンバシップを確立するステップをさらに有する、(1)に記載の方法。

(3) 前記信号グループが第1の信号グループを備え、前記第1の信号グループが、前記複数の信号をメンバとして集合的に有する第2および第3の信号グループを備える、(1)または(2)に記載の方法。

(4) リネームから関連する信号名が保護されることになる特定の信号を識別する保護指示を受け取るステップと、

前記保持指示に応答して、プレゼンテーションにおいて前記関連する信号名によって前記信号を識別するステップと、

をさらに有する、(1)、(2)、または(3)に記載の方法。 10

(5) 前記シミュレーション実行可能モデル内の設計エンティティ・インスタンスについて、参照有効範囲を示す有効範囲コマンドを入力として受け取るステップと、

前記有効範囲コマンドの受け取りに応答して、前記参照有効範囲に関する前記データ・セット内の前記少なくとも1つのエントリを解釈するステップと、

をさらに有する、(1)から(4)のいずれか一つに記載の方法。

(6) 前記シミュレーション実行可能モデル内に複数の設計エンティティ・インスタンスを有する設計エンティティ名を、エントリ内で識別するために、前記データ・セット内の前記エントリを処理するステップと、

前記設計エンティティ名の識別に応答して、ユーザの選択のために、前記複数の設計エンティティ・インスタンスのインスタンス識別子を提示するステップと、 20

前記インスタンス識別子のうちの1つのユーザ選択に応答して、前記信号グループに属する信号のインスタンスが位置する有効範囲を狭めるステップと、

をさらに有する、(1)から(5)のいずれか一つに記載の方法。

(7) コンピュータ読み取り可能媒体と、

前記コンピュータ読み取り可能媒体内のプログラム・コードと、を備えるプログラムであって、前記プログラム・コードがデータ処理システムに、

所定の信号グループ名によって信号グループを指定する少なくとも1つのエントリを含むデータ・セットを入力として受け取るステップと、

前記データ・セットの受け取りに応答して、

前記信号グループ名を識別するために、前記データ・セット内の前記エントリを処理するステップと、 30

前記信号グループのメンバである複数の信号の信号名を決定するために、シミュレーション結果を含むイベント・トレース・ファイルに関連付けられた信号グループ情報にアクセスするステップと、

前記複数の信号のインスタンスに関連付けられた前記イベント・トレース・ファイルからのそれらのシミュレーション結果を、プレゼンテーションに含めるステップと、

を含む方法を実行させる、プログラム。

(8) 前記方法が、シミュレーション実行可能モデル内でインスタンス化された設計エンティティを記述するHDLソース・コード・ファイルを参照して前記信号グループ内の前記信号名のメンバシップを確立するステップをさらに含む、(7)に記載のプログラム。 40

(9) 前記信号グループが第1の信号グループを備え、前記第1の信号グループが、前記複数の信号をメンバとして集合的に有する第2および第3の信号グループを備える、(7)または(8)に記載のプログラム。

(10) 前記方法が、

リネームから関連する信号名が保護されることになる特定の信号を識別する保護指示を受け取るステップと、

前記保持指示に応答して、プレゼンテーションにおいて前記関連する信号名によって前記信号を識別するステップと、

をさらに含む、(7)、(8)、または(9)に記載のプログラム。

(11) 前記方法が、

前記シミュレーション実行可能モデル内の設計エンティティ・インスタンスについて、

参照有効範囲を示す有効範囲コマンドを入力として受け取るステップと、

前記有効範囲コマンドの受け取りに応答して、前記参照有効範囲に関する前記データ・

セット内の前記少なくとも1つのエントリを解釈するステップと、

をさらに含む、(7)から(10)のいずれか一つに記載のプログラム。

(12)前記方法が、

前記シミュレーション実行可能モデル内に複数の設計エンティティ・インスタンスを有する

設計エンティティ名を、エントリ内で識別するために、前記データ・セット内の前記

エントリを処理するステップと、

前記設計エンティティ名の識別に応答して、ユーザの選択のために、前記複数の設計エンティティ・

インスタンスのインスタンス識別子を提示するステップと、

前記インスタンス識別子のうちの1つのユーザ選択に応答して、前記信号グループに属する

信号のインスタンスが位置する有効範囲を狭めるステップと、

をさらに含む、(7)から(11)のいずれか一つに記載のプログラム。

(13)プロセッサと、

前記プロセッサに結合されたデータ・ストレージと、を備える、データ処理システムであって、

前記データ・ストレージが、前記データ処理システムに、

所定の信号グループ名によって信号グループを指定する少なくとも1つのエントリを含む

データ・セットを入力として受け取るステップと、

前記データ・セットの受け取りに応答して、

前記信号グループ名を識別するために、前記データ・セット内の前記エントリを処理する

ステップと、

前記信号グループのメンバである複数の信号の信号名を決定するために、シミュレーション

結果を含むイベント・トレース・ファイルに関連付けられた信号グループ情報にアクセスする

ステップと、

前記複数の信号のインスタンスに関連付けられた前記イベント・トレース・ファイル

からのそれらのシミュレーション結果を、プレゼンテーションに含めるステップと、

を含む方法を実行させる、プログラム・コードを含む、データ処理システム。

(14)前記方法が、シミュレーション実行可能モデル内でインスタンス化された設計エンティティを記述するHDLソース・コード・ファイルを参照して前記信号グループ内の

前記信号名のメンバシップを確立するステップをさらに含む、(13)に記載のデータ処理

システム。

(15)前記信号グループが第1の信号グループを備え、前記第1の信号グループが、前記複数の信号をメンバとして集合的に有する第2および第3の信号グループを備える、(13)または(14)に記載のデータ処理システム。

(16)前記方法が、

リネームから関連する信号名が保護されることになる特定の信号を識別する保護指示を

受け取るステップと、

前記保持指示に応答して、プレゼンテーションにおいて前記関連する信号名によって前記

信号を識別するステップと、

をさらに含む、(13)、(14)、または(15)に記載のデータ処理システム。

(17)前記方法が、

前記シミュレーション実行可能モデル内の設計エンティティ・インスタンスについて、

参照有効範囲を示す有効範囲コマンドを入力として受け取るステップと、

前記有効範囲コマンドの受け取りに応答して、前記参照有効範囲に関する前記データ・

セット内の前記少なくとも1つのエントリを解釈するステップと、

をさらに含む、(13)から(16)のいずれか一つに記載のデータ処理システム。

(18)前記方法が、

前記シミュレーション実行可能モデル内に複数の設計エンティティ・インスタンスを有する

設計エンティティ名を、エントリ内で識別するために、前記データ・セット内の前記

10

20

30

40

50

エントリを処理するステップと、

前記設計エンティティ名の識別に応答して、ユーザの選択のために、前記複数の設計エンティティ・インスタンスのインスタンス識別子を提示するステップと、

前記インスタンス識別子のうちの1つのユーザ選択に応答して、前記信号グループに属する信号のインスタンスが位置する有効範囲を狭めるステップと、

をさらに含む、(13)から(17)のいずれか一つに記載のデータ処理システム。

【図面の簡単な説明】

【0068】

【図1】本発明に従ったデータ処理システムを示す絵画図である。

【図2】図1に示されたデータ処理システムの代表的なハードウェア環境を示す図である

10

。

【図3】本発明の教示に従ったデジタル設計エンティティを示す簡易ブロック図である。

【図4】本発明の教示に従ったシミュレーション・モデルを示す概略図である。

【図5】本発明の教示に従ったモデル構築プロセスを示す流れ図である。

【図6】本発明の教示に従った設計を表すシミュレーション・モデル・データ構造を示すブロック図である。

【図7】シミュレーション実行可能モデルのシミュレーションおよびシミュレーションの結果をユーザに提示することを示す流れ図である。

【図8】従来技術に従った第1の従来のI/Oリストを示す図である。

【図9】従来技術に従った第2の従来のI/Oリストを示す図である。

20

【図10】本発明に従った例示的I/Oリストを示す図である。

【図11】本発明に従った例示的I/Oリストを示す図である。

【図12】本発明に従った、信号グループ記述子を含む例示的設計エンティティHDLファイルを示す図である。

【図13】本発明に従った、ネストされた信号グループ記述子を含む例示的設計エンティティHDLファイルを示す図である。

【図14】本発明に従った、AETビューアがAETファイルのプレゼンテーションを生成するためにI/Oリストを処理する際に使用する例示的プロセスを示す、高水準論理流れ図の一部である。

【図15】本発明に従った、AETビューアがAETファイルのプレゼンテーションを生成するためにI/Oリストを処理する際に使用する例示的プロセスを示す、高水準論理流れ図の一部である。

30

【図16】本発明に従った、AETビューアがAETファイルのプレゼンテーションを生成するためにI/Oリストを処理する際に使用する例示的プロセスを示す、高水準論理流れ図の一部である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

Entity FXU IS

Port ( ...

E: OUT STD\_ULOGIC;

G: OUT STD\_ULOGIC;

...

); } 600

Architecture FXU of FXU IS

BEGIN

...[設計エンティティ向けのHDLソース・コード]...

E <= ...;

G <= ...; } 602

-!! Signal Group FXU\_Group;

-!! N

-!! B.L

-!! B.C.P(0..4) LEFT\_JUSTIFY

-!! B.C.Q

-!! E

-!! END Signal Group FXU\_Group; } 610

-!! Signal Preserve G; } 620

...

END } 340a

【 図 1 3 】

【図14】

【 図 1 5 】

### 【図16】

---

フロントページの続き

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 ボボク、ガボール

アメリカ合衆国12309 ニューヨーク州ニスカユナ ホーソーン・ロード 1345

(72)発明者 レスナー、ウォルフガング

アメリカ合衆国78726 テキサス州オースティン チェストナット・リッジ・ロード 107

17

(72)発明者 ウィリアムズ、デレク、エドワード

アメリカ合衆国78717 テキサス州オースティン スレイト・クリーク・トレイル 9406

審査官 松浦 功

(56)参考文献 特開平11-066114 (JP, A)

特開平03-116276 (JP, A)

特開平05-151304 (JP, A)

特開平05-342296 (JP, A)

小林優, Verilog - HDLによるFPGA回路設計の実際, Interface, CQ出版株式会社, 1996年 5月 1日, 第22巻, 第4号, pp. 128-137

藤谷つぐみ, パソコン上で動作するVerilog HDL - SILOSIII, インターフェース, CQ出版株式会社, 1993年12月 1日, 第19巻, 第12号, pp. 184-188

(58)調査した分野(Int.Cl., DB名)

G06F 17/50

Google Scholar