(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6650737号

(P6650737)

(45) 発行日 令和2年2月19日(2020.2.19)

(24) 登録日 令和2年1月23日(2020.1.23)

(51) Int.Cl.

F 1

|              |           |      |        |      |

|--------------|-----------|------|--------|------|

| HO1L 21/822  | (2006.01) | HO1L | 27/04  | C    |

| HO1L 27/04   | (2006.01) | HO1L | 29/78  | 613B |

| HO1L 29/786  | (2006.01) | HO1L | 29/78  | 612Z |

| HO1L 21/336  | (2006.01) | HO1L | 27/108 | 321  |

| HO1L 21/8242 | (2006.01) | HO1L | 27/108 | 621B |

請求項の数 3 (全 53 頁) 最終頁に続く

(21) 出願番号

特願2015-226511 (P2015-226511)

(22) 出願日

平成27年11月19日(2015.11.19)

(65) 公開番号

特開2016-105473 (P2016-105473A)

(43) 公開日

平成28年6月9日(2016.6.9)

審査請求日

平成30年11月13日(2018.11.13)

(31) 優先権主張番号

特願2014-236230 (P2014-236230)

(32) 優先日

平成26年11月21日(2014.11.21)

(33) 優先権主張国・地域又は機関

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 野田 耕生

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 市川 武宜

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の容量素子と、前記第1の容量素子の上方に位置する第2の容量素子と、を有し、

前記第1の容量素子は、

凸部を有する第1の電極と、

前記凸部上の第1の絶縁体と、

前記第1の電極及び前記第1の絶縁体を覆う第2の絶縁体と、

前記第2の絶縁体上の第2の電極と、を有し、

前記第2の容量素子は、

凸部を有する第3の電極と、

前記凸部を有する第3の絶縁体と、

前記第3の電極及び前記第3の絶縁体を覆う第4の絶縁体と、

前記第4の絶縁体上の第4の電極と、を有し、

前記第2の電極の側周辺は、前記第1の絶縁体及び前記第2の絶縁体を介して、前記第1の電極と重なる領域を有し、

前記第4の電極の側周辺は、前記第3の絶縁体及び前記第4の絶縁体を介して、前記第3の電極と重なる領域を有し、

前記第2の容量素子は、前記第1の容量素子と重なる領域を有し、

前記第4の電極は、前記第2の電極と電気的に接続されている、半導体装置。

## 【請求項 2】

10

20

第1の容量素子と、前記第1の容量素子の上方に位置する第2の容量素子と、を有し、

前記第1の容量素子は、

凸部を有する第1の電極と、

前記凸部上の第1の絶縁体と、

前記第1の電極及び前記第1の絶縁体を覆う第2の絶縁体と、

前記第2の絶縁体上の第2の電極と、を有し、

前記第2の容量素子は、

凸部を有する第3の電極と、

前記凸部を有する第3の絶縁体と、

前記第3の電極及び前記第3の絶縁体を覆う第4の絶縁体と、

前記第4の絶縁体上の第4の電極と、を有し、

前記第2の電極の側周辺は、前記第1の絶縁体及び前記第2の絶縁体を介して、前記第1の電極と重なる領域を有し、

前記第4の電極の側周辺は、前記第3の絶縁体及び前記第4の絶縁体を介して、前記第3の電極と重なる領域を有し、

前記第2の容量素子は、前記第1の容量素子と重なる領域を有し、

前記第3の電極は、前記第2の電極と電気的に接続されている、半導体装置。

### 【請求項3】

請求項1または請求項2において、

前記第1の電極は、トランジスタと電気的に接続されている半導体装置。 20

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明の一態様は、容量素子、及び容量素子を有する半導体装置に関する。

#### 【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、液晶表示装置、発光装置、照明装置、蓄電装置、記憶装置、撮像装置、それらの駆動方法、または、それらの製造方法、を一例として挙げることができる。 30

#### 【0003】

なお、本明細書等において、半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。撮像装置、表示装置、液晶表示装置、発光装置、電気光学装置、発電装置（薄膜太陽電池、有機薄膜太陽電池等を含む）、及び電子機器は、半導体装置を有している場合がある。

#### 【背景技術】

#### 【0004】

半導体材料を用いてトランジスタを構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（単に表示装置とも表記する）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体材料としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。 40

#### 【0005】

例えば、酸化物半導体として酸化亜鉛、またはIn-Ga-Zn系酸化物半導体を用いてトランジスタを作製する技術が開示されている（特許文献1及び特許文献2参照）。

#### 【0006】

また、近年では電子機器の高性能化、小型化、または軽量化に伴い、微細化されたトランジスタなどの半導体素子を高密度に集積した集積回路の要求が高まっている。例えば、T 50

ri-GateトランジスタとCOB (capacitor over bitline)構造のMIM容量素子が紹介されている(非特許文献1)。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

【非特許文献】

【0008】

【非特許文献1】R. Brain et al., "A 22nm High Performance Embedded DRAM SoC Technology Featuring Tri-gate Transistors and MIMCAP COB", 2013 SYMPOSIUM ON VLSI TECHNOLOGY 2-1

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明の一態様は、微細化・高密度化に適した半導体装置を提供することを課題の一とする。

【0010】

または、半導体装置に良好な電気特性を付与することを課題の一とする。または、信頼性の高い半導体装置を提供することを課題の一とする。または、新規な構成の半導体装置を提供することを課題の一とする。

【0011】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0012】

本発明の一態様は、凸部を有する第1の電極と、凸部上の第1の絶縁体と、第1の電極及び第1の絶縁体を覆う第2の絶縁体と、第2の絶縁体上の第2の電極と、を有し、第2の電極の側周辺は、第1の絶縁体及び第2の絶縁体を介して、第1の電極と重なる領域を有している。

【0013】

なお、側周辺とは、その形状の側面に沿った端部からなる領域である。特に本明細書中における容量素子を形成する構造に対して用いる場合、構造の端部におけるリーク電流(エッジリークともいう)が起こりうる領域のことである。例えば、第2の電極の側周辺とは、第1の電極とリーク電流が生じる可能性がある第2の電極の端部を含む周辺部のことである。

【0014】

本発明の一態様は、凸部を有する第1の電極と、凸部上の第1の絶縁体と、第1の電極及び第1の絶縁体を覆う第2の絶縁体と、第2の絶縁体上の第2の電極と、を有し、第2の電極は、第1の絶縁体及び第2の絶縁体を介して第1の電極と重なる第1の領域と、第2の絶縁体を介して第1の電極と重なる第2の領域と、を有し、第2の電極の側周辺は、第1の領域にある。

【0015】

また、上記構成において、第1の電極は、トランジスタと電気的に接続されている。

【0016】

また、上記構成において、トランジスタは、第3の電極を有し、第3の電極は、第1の電

10

20

30

40

50

極と共に導電体に設けられている。

**【0017】**

また、本発明の一態様は、上記構成と、表示装置、マイクロフォン、スピーカー、操作キー、タッチパネル、または、アンテナの少なくともいずれかと、を有する電子機器である。

**【発明の効果】**

**【0018】**

本発明の一態様によれば、微細化・高密度化に適した半導体装置を提供することができる。

**【0019】**

または、半導体装置に良好な電気特性を付与することができる。または、信頼性の高い半導体装置を提供することができる。または、新規な構成の半導体装置等を提供することができる。なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

**【図面の簡単な説明】**

**【0020】**

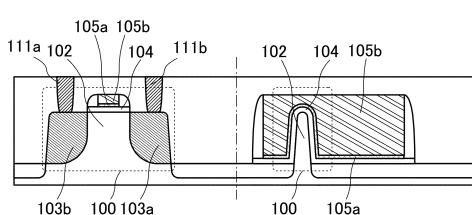

【図1】実施の形態に係る、容量素子の上面図及び積層構造を説明する図。

【図2】実施の形態に係る、容量素子の積層構造を説明する図。

20

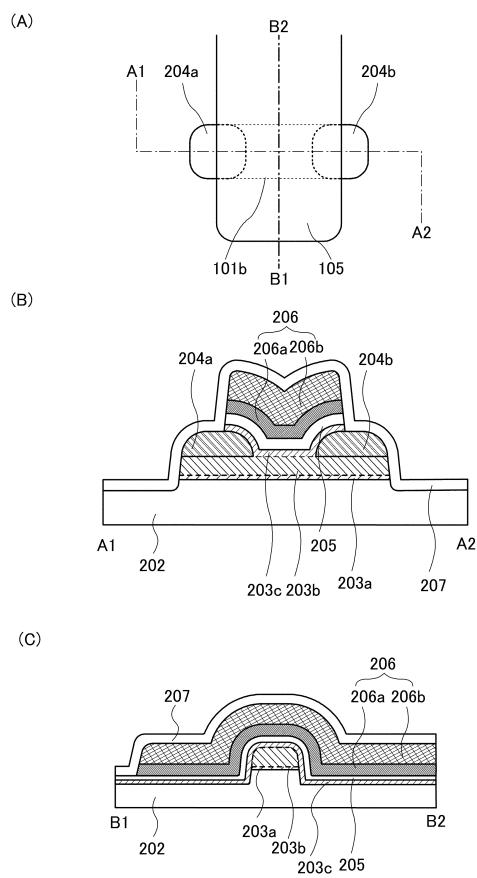

【図3】実施の形態に係る、容量素子の上面図及び積層構造を説明する図。

【図4】実施の形態に係る、容量素子の作製方法例を説明する図。

【図5】実施の形態に係る、容量素子の作製方法例を説明する図。

【図6】実施の形態に係る、容量素子の作製方法例を説明する図。

【図7】実施の形態に係る、半導体装置の構成例及び回路図。

【図8】実施の形態に係る、トランジスタの構成例。

【図9】実施の形態に係る、トランジスタの上面図及び積層構造を説明する図。

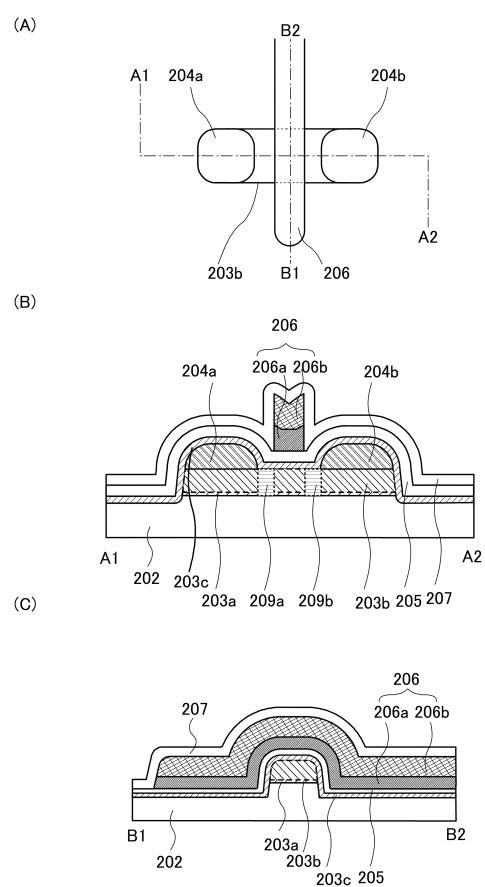

【図10】実施の形態に係る、トランジスタの上面図及び積層構造を説明する図。

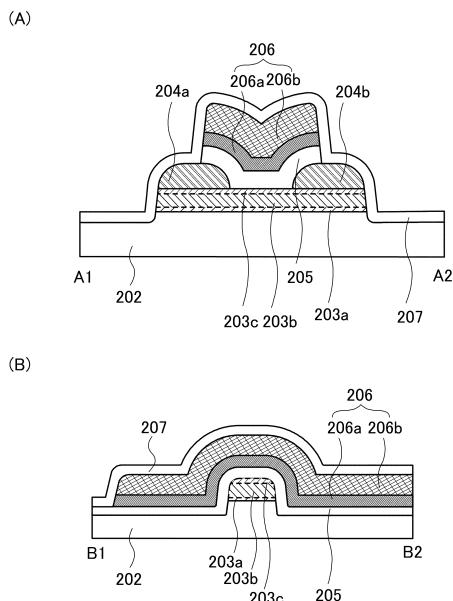

【図11】実施の形態に係る、トランジスタの構成例。

【図12】実施の形態に係る、トランジスタの構成例。

30

【図13】実施の形態に係る、半導体装置の作製方法例を説明する図。

【図14】実施の形態に係る、半導体装置の作製方法例を説明する図。

【図15】実施の形態に係る、半導体装置の構成例。

【図16】実施の形態に係る、半導体装置の構成例。

【図17】C A A C - O S の断面におけるC s 補正高分解能T E M像、およびC A A C - O S の断面模式図。

【図18】C A A C - O S の平面におけるC s 補正高分解能T E M像。

【図19】C A A C - O S および単結晶酸化物半導体のX R Dによる構造解析を説明する図。

【図20】C A A C - O S の電子回折パターンを示す図。

40

【図21】I n - G a - Z n 酸化物の電子照射による結晶部の変化を示す図。

【図22】半導体装置の一態様を示す断面図及び回路図。

【図23】半導体装置の一態様を示す断面図。

【図24】半導体装置の一態様を示す断面図。

【図25】半導体装置の一態様を示す回路図。

【図26】実施の形態に係る、R F デバイスタグの構成例。

【図27】実施の形態に係る、C P Uの構成例。

【図28】実施の形態に係る、記憶素子の回路図。

【図29】実施の形態に係る、表示装置の断面図、上面図及び回路図。

【図30】実施の形態に係る、表示装置の断面図及び回路図。

50

【図31】実施の形態に係る、電子機器。

【図32】実施の形態に係る、RFデバイスタグの使用例。

【発明を実施するための形態】

【0021】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0022】

なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。 10

【0023】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0024】

なお、本明細書等における「第1」、「第2」等の序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではない。

【0025】

トランジスタは半導体素子の一種であり、電流や電圧の増幅や、導通または非導通を制御するスイッチング動作などを実現することができる。本明細書におけるトランジスタは、IGFET (I n s u l a t e d G a t e F i e l d E f f e c t T r a n s i s t o r) や薄膜トランジスタ (TFT : T h i n F i l m T r a n s i s t o r) を含む。 20

【0026】

なお、本明細書において、「平行」とは、二つの直線が - 10° 以上 10° 以下の角度で配置されている状態をいう。したがって、- 5° 以上 5° 以下の場合も含まれる。また、「略平行」とは、二つの直線が - 30° 以上 30° 以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が 80° 以上 100° 以下の角度で配置されている状態をいう。したがって、85° 以上 95° 以下の場合も含まれる。また、「略垂直」とは、二つの直線が 60° 以上 120° 以下の角度で配置されている状態をいう。 30

【0027】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

【0028】

なお、「膜」という言葉と、「層」という言葉とは、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。 40

【0029】

(実施の形態1)

[構成例]

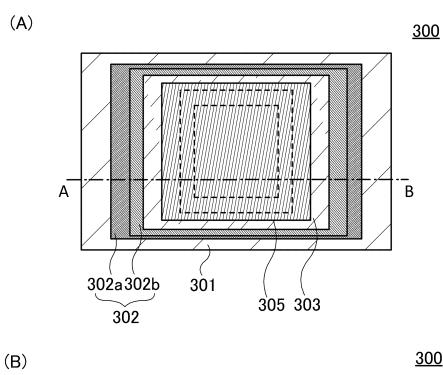

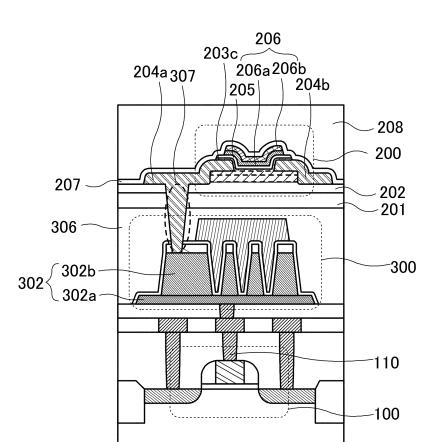

図1(A)に容量素子300の上面図の一例を示す。図1(B)は図1(A)に示す一点鎖線A-Bに対応する断面図である。

【0030】

容量素子300は、絶縁膜301上に設けられ、導電層302a及び導電層302bを含む第1の電極302と、バリア層303と、絶縁体304と、第2の電極305とを有する。

【0031】

50

20

30

40

50

導電層 302a 及び導電層 302b は、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。耐熱性と導電性を両立するタンゲステンやモリブデンなどの高融点材料を用いることが好ましく、特にタンゲステンを用いることが好ましい。なお、導電層 302a と、導電層 302b とは、異なる材料で形成しても、同じ材料を用いて形成してもよい。

#### 【0032】

また、導電層 302a 上に、導電層 302a の一部が露出するように導電層 302b を形成することで、第 1 の電極 302 は、表面に起伏を有する形状となる。なお、ここでは導電層 302a 及び導電層 302b を用いて、凹凸部を形成する場合を示したが、1 層の導電層、または 3 層以上の複数の積層された導電層を加工して、凹凸形状を有する第 1 の電極 302 を形成してもよい。また、導電層 302b の形状は、少なくとも第 2 の電極 305 の側周辺と重なる領域に設けられていればよく、適宜最適な形状を設計するとよい。例えば、図 1 では、導電層 302b が、開口部を有する四角形の島状である例を示したが、導電層 302b は、多角形でも円形でもよい。

#### 【0033】

バリア層 303 は、導電層 302b の上面に設けられる。バリア層 303 を設けることで、容量素子 300 の形状不良を低減できる。なお、バリア層 303 として、酸化シリコン膜、ガリウム酸化物膜などの絶縁膜、もしくは酸化物半導体膜などの半導体膜を用いることができる。

#### 【0034】

絶縁体 304 は、導電層 302a、導電層 302b、及びバリア層 303 を覆うように設けられる。絶縁体 304 には例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよく、積層または単層で設ける。

#### 【0035】

第 2 の電極 305 は、バリア層 303、絶縁体 304 を介して、第 1 の電極 302 上に設けられる。第 2 の電極 305 は、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。耐熱性と導電性を両立するタンゲステンやモリブデンなどの高融点材料を用いることが好ましく、特にタンゲステンを用いることが好ましい。

#### 【0036】

なお、第 2 の電極 305 は、側周辺がバリア層 303 と絶縁体 304 を介して導電層 302b に重なるように設けられる。

#### 【0037】

容量素子 300 において、第 2 の電極 305 の側周辺が、バリア層 303 を介して導電層 302b と重なる。そのため、第 2 の電極 305 は、側周辺において、少なくともバリア層 303 の厚みにより、第 1 の電極 302 との間隔が広くなる。よって、本発明の一態様に係る容量素子 300 の形状不良を抑制し、信頼性の高い容量素子を提供することができる。

#### 【0038】

容量素子 300 は、第 1 の電極 302 に起伏を有することで、立体的な容量素子を形成することができる。これにより、容量素子の投影面積当たりの容量を増加させることができると、半導体装置の小面積化、高集積化、微細化が可能となる。

#### 【0039】

以上が構成例についての説明である。

#### 【0040】

##### <応用例 1>

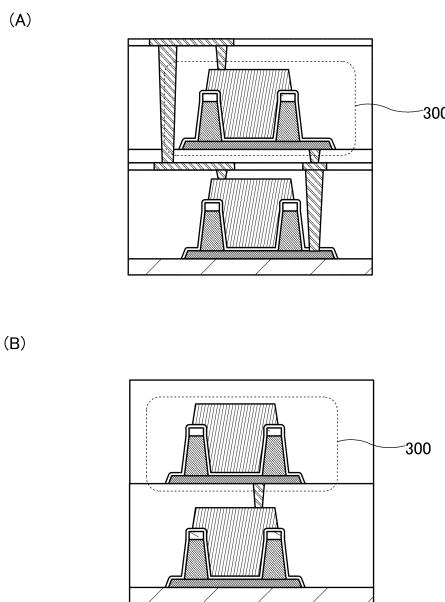

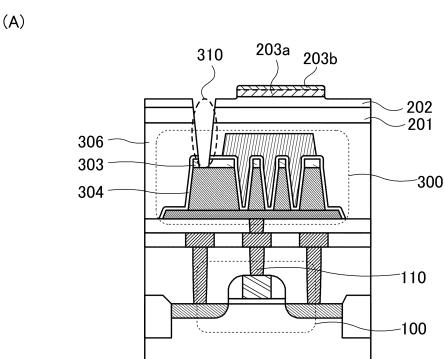

また、本実施の形態の応用例として、図 2 (A) 及び (B) に示すように容量素子 300 を複数積層して用いることができる。図 2 (A) は並列接続、図 2 (B) は直列接続となるように接続されている。なお、図 2 では、2 個の容量素子 300 を積層した場合を示しているが、必要に応じて、容量素子 300 を 3 個以上積層することも可能である。

10

20

30

40

50

**【0041】**

当該構成により、立体的な容量素子を形成することができる。これにより、容量素子の投影面積当たりの容量を増加させることができるため、半導体装置の小面積化、高集積化、微細化が可能となる。

**【0042】**

## &lt;変形例1&gt;

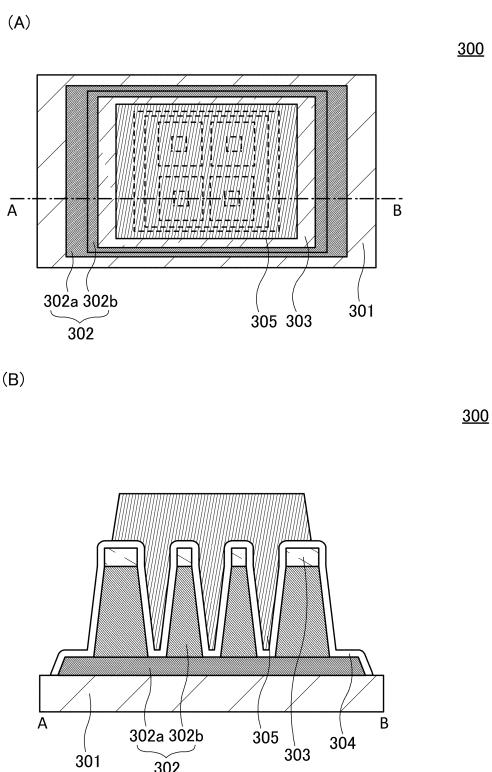

また、本実施の形態の変形例として、図3に示すように容量素子300の第1の電極302の溝部内に、導電層302bを用いて凸部を設けてよい。なお、凸部の形状は、適宜最適な形状を設計するとよい。例えば、縞(格子)状の他、島状であれば、四角錐台、多角錐台、円錐台、多角柱、円柱でもよい。また、起伏部は必ずしも整列して形成される必要はなく、不規則に形成されていてよい。10

**【0043】**

凸部を有することで、容量素子の投影面積当たりの容量をさらに増加させることができるため、半導体装置の小面積化、高集積化、微細化が可能となる。

**【0044】**

## [作製方法例]

以下では、図3で示した容量素子の作製方法の一例について、図4乃至図6を用いて説明する。

**【0045】**

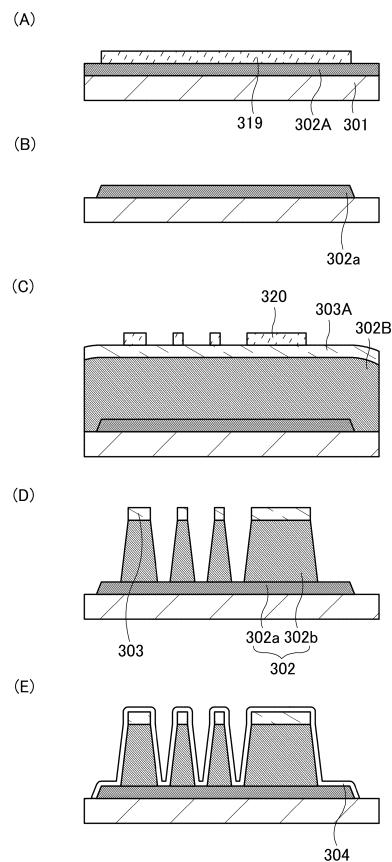

まず、絶縁膜301上に導電膜302Aを形成する(図4(A))。なお、絶縁膜301は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよく、積層または単層で設ける。絶縁膜301はスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、当該絶縁膜301をCVD法、好ましくはプラズマCVD法によって成膜すると、被覆性を向上させることができるために好ましい。またプラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。20

**【0046】**

また、導電膜302Aとしては、タンタル、タングステン、チタン、モリブデン、クロム、ニオブ等から選択された金属、またはこれらの金属を主成分とする合金材料若しくは化合物材料を用いることが好ましい。また、リン等の不純物を添加した多結晶シリコンを用いることができる。また、金属窒化物膜と上記の金属膜の積層構造を用いてよい。金属窒化物としては、窒化タングステン、窒化モリブデン、窒化チタンを用いることができる。金属窒化物膜を設けることにより、金属膜の密着性を向上させることができ、剥離を防止することができる。30

**【0047】**

導電膜302Aは、スパッタリング法、蒸着法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)などにより成膜することができる。また、プラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。40

**【0048】**

続いて、導電膜302A上にリソグラフィ法等を用いてレジストマスク319を形成し、当該導電膜302Aの不要な部分を除去する。その後、レジストマスク319を除去することにより、導電層302aを形成することができる(図4(B))。

**【0049】**

ここで、被加工膜の加工方法について説明する。被加工膜を微細に加工する場合には、様々な微細加工技術を用いることができる。例えば、リソグラフィ法等で形成したレジストマスクに対してスリミング処理を施す方法を用いてよい。また、リソグラフィ法等でダミーパターンを形成し、当該ダミーパターンにサイドウォールを形成した後にダミーパターンを除去し、残存したサイドウォールをレジストマスクとして用いて、被加工膜をエッ50

チングしてもよい。また、被加工膜のエッティングとして、高いアスペクト比を実現するために、異方向性のドライエッティングを用いることが好ましい。また、無機膜または金属膜からなるハードマスクを用いてもよい。

#### 【0050】

レジストマスクの形成に用いる光は、例えばi線（波長365nm）、g線（波長436nm）、h線（波長405nm）、またはこれらを混合させた光を用いることができる。そのほか、紫外線やKrFレーザ光、またはArFレーザ光等を用いることもできる。また、液浸露光技術により露光を行ってもよい。また、露光に用いる光として、極端紫外光（EUV：Extreme Ultra-violet）やX線を用いてもよい。また、露光に用いる光に換えて、電子ビームを用いることもできる。極端紫外光、X線または電子ビームを用いると、極めて微細な加工が可能となるため好ましい。なお、電子ビームなどのビームを走査することにより露光を行う場合には、フォトマスクは不要である。10

#### 【0051】

また、レジストマスクとなるレジスト膜を形成する前に、被加工膜とレジスト膜との密着性を改善する機能を有する有機樹脂膜を形成してもよい。当該有機樹脂膜は、例えばスピノコート法などにより、その下層の段差を被覆して表面を平坦化するように形成することができ、当該有機樹脂膜の上層に設けられるレジストマスクの厚さのばらつきを低減できる。また、特に微細な加工を行う場合には、当該有機樹脂膜として、露光に用いる光に対する反射防止膜として機能する材料を用いることが好ましい。このような機能を有する有機樹脂膜としては、例えばB A R C（Bottom Anti-Reflection Coating）膜などがある。当該有機樹脂膜は、レジストマスクの除去と同時に除去するか、レジストマスクを除去した後に除去すればよい。20

#### 【0052】

次に、導電層302a上に、導電膜302B及びバリア膜303Aを成膜する。なお、導電膜302Bは、導電膜302Aと同様に形成することができる。また、バリア膜303Aとして、酸化シリコン膜、ガリウム酸化物膜などの絶縁膜、もしくは酸化物半導体膜などの半導体膜を用いることができる（図4（C））。

#### 【0053】

バリア膜303Aは、例えばスパッタリング法、CVD法（熱CVD法、MOCVD法、PECVD法等を含む）、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、バリア膜303AをCVD法、好ましくはプラズマCVD法によって成膜すると、被覆性を向上させることができるために好ましい。また、プラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。30

#### 【0054】

その後、上記と同様の方法によりレジストマスク320を形成し、バリア膜303A及び導電膜302Bの不要な領域をエッティングにより除去する。その後、レジストマスク320を除去することで、バリア層303及び導電層302bが形成される（図4（D））。なお、導電層302bが形成されることにより、容量素子300の一方の電極となる第1の電極302を形成する。

#### 【0055】

また、バリア膜303Aと、導電膜302Bは別々にエッティングを行ってもよい。その場合、まず、バリア層303をレジストマスク320により形成した後、形成されたバリア層303をハードマスクとして導電膜302Bをエッティングするとよい。

#### 【0056】

なお、導電膜を十分に厚く成膜した上にバリア膜を成膜し、1層の導電膜から凸部を有する第1の電極302を加工してもよい。なお、加工にはハーフエッティングなどの手法を用いることもできる。例えば、図5（A）及び図5（B）に示すように、バリア膜303A、及び十分に厚く成膜した導電膜302Cにレジストマスク330を形成して、加工を行い、バリア層303B及び導電膜302cを形成する。続いて、図5（C）及び図5（D）に示すように、レジストマスク320を形成して、バリア層303B及び導電膜30240

50

c の一部を加工すればよい。導電膜 302c を更に加工する場合、導電膜 302c のエッチングレートから、所望のエッチング量に対応する処理時間を算出し、タイマーによりエッチングを途中で止める、タイマーエッチングにより加工すればよい。このようにして、第1の電極 302 に、図 5 (D) に示すような凸部を設けることができる。

#### 【0057】

また、ハーフトーン露光法とも呼ばれる半透部を備えた露光マスクを用いた露光法を用いれば、第1の電極 302 をマスク 1 枚で加工できる。また、回折格子パターンからなる光強度低減機能を有する補助パターンを設置したフォトマスク或いはレチクルを第1の電極 302 形成用のリソグラフィ工程に適用してもよい。

#### 【0058】

次に、先ほどと同様にレジストマスクを用いて、第1の電極 302 及びバリア層 303 上に絶縁体 304 を形成する。絶縁体 304 は絶縁膜 301 と同様に形成することができる(図 4 (E))。

#### 【0059】

絶縁体 304 上に導電膜 305A を形成する(図 6 (A))。導電膜 305A としては、導電膜 302A と同様に形成することができる。その後、上記と同様の方法によりレジストマスク 325 を形成し、導電膜 305A の不要な領域をエッチングにより除去することにより第2の電極 305 を形成する。この際に、導電膜 305A だけでなく、絶縁体 304 の表面が削られてしまい、絶縁体 304 は第2の電極 305 と重ならない領域の膜厚が、第2の電極 305 と重なる領域の膜厚よりも薄くなる。さらに、ドライエッチングの場合にプラズマ、またはウェットエッチングの場合に用いられる溶剤等に曝されることで、絶縁体 304 の表面にダメージが生じる。したがって、バリア層 303 がない場合、第2の電極 305 の側周辺においてリーク電流が生じやすくなる。そこで、バリア層 303 を設けることにより、第1の電極 302 と第2の電極 305 とは、適切な距離が保たれるため、高集積化、微細化が可能となった信頼性の高い容量素子 300 を形成することができる(図 6 (B))。

#### 【0060】

続いて、容量素子 300 を覆う絶縁膜 306 を成膜する。絶縁膜 306 は、絶縁膜 301 等と同様の材料及び方法により形成することができる(図 6 (C))。

#### 【0061】

また、形成された容量素子 300 を他の半導体素子を電気的に接続するための配線 308 を形成してもよい(図 6 (D))。なお配線 308 には、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。特に、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。上記のような材料を用いることで配線抵抗を低くすることができる。

#### 【0062】

以上の工程により、本発明の一態様の容量素子を作製することができる。なお、図 1 の構成についても、同様に作製することができる。

#### 【0063】

なお、本実施の形態において、本発明の一態様について述べた。または、他の実施の形態において、本発明の一態様について述べる。ただし、本発明の一態様は、これらに限定されない。つまり、本実施の形態および他の実施の形態では、様々な発明の態様が記載されているため、本発明の一態様は、特定の態様に限定されない。例えば、本発明の一態様として、容量素子の第1の電極上にバリア層を有する場合の例を示したが、本発明の一態様は、これに限定されない。場合によっては、または、状況に応じて、本発明の一態様では、容量素子の第1の電極上に、様々な層を有していてもよい。または例えば、場合によっては、または、状況に応じて、本発明の一態様では、容量素子の第1の電極上に、バリア層を有していないなくてもよい。

#### 【0064】

(実施の形態 2)

10

20

30

40

50

**[構成例]**

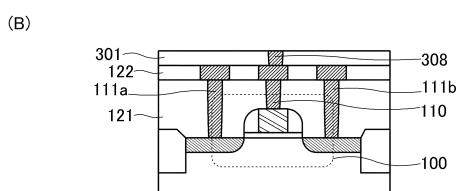

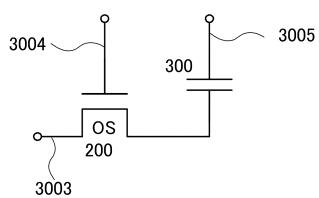

本発明の一態様である容量素子を使用した、半導体装置（記憶装置）の一例を図7に示す。なお、図7（B）は図7（A）を回路図で表したものである。

**【0065】**

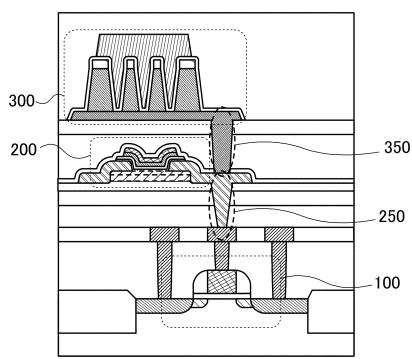

図7（A）及び図7（B）に示す半導体装置は、第1のトランジスタ100と第2のトランジスタ200、および容量素子300を有している。なお、容量素子300としては、実施の形態1で説明した容量素子を用いることができる。

**【0066】**

第2のトランジスタ200は、酸化物半導体を有する半導体層にチャネルが形成されるトランジスタである。第2のトランジスタ200は、オフ電流が小さいため、これを半導体装置（記憶装置）に用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体装置（記憶装置）とすることが可能となるため、消費電力を十分に低減することができる。

10

**【0067】**

図7（B）において、配線3001は第1のトランジスタ100のソース電極と電気的に接続され、配線3002は第1のトランジスタ100のドレイン電極と電気的に接続されている。また、配線3003は第2のトランジスタ200のソース電極およびドレイン電極の一方と電気的に接続され、配線3004は第2のトランジスタ200のゲート電極と電気的に接続されている。そして、第1のトランジスタ100のゲート電極、および第2のトランジスタ200のソース電極およびドレイン電極の他方は、容量素子300の電極の一方と電気的に接続され、配線3005は容量素子300の電極の他方と電気的に接続されている。

20

**【0068】**

また、図7（A）に示す半導体装置をマトリクス状に配置することで、記憶装置（メモリセルアレイ）を構成することができる。

**【0069】**

本発明の一態様の半導体装置は、第1の電極が凸部を有する容量素子300を有することにより、小面積化、及び高集積化を可能としている。また、容量素子300は、少なくとも、第1の電極に形成された凸部の上面と第2の電極の端部が重なる領域における電極間の距離が、第1の電極に形成された凸部の側面における電極間の距離よりも長く設けられているため、電極間の短絡を防ぐことができる。

30

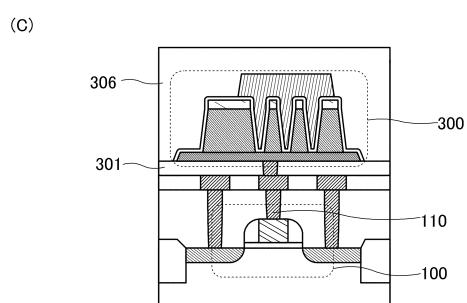

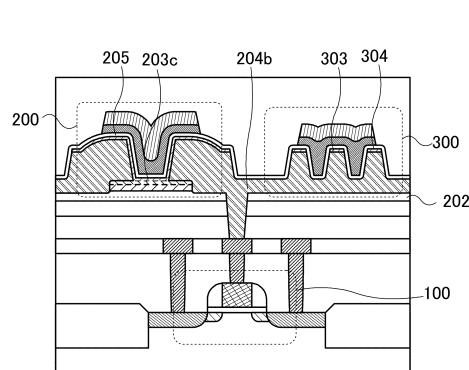

**【0070】**

半導体装置は、図7（A）に示すように第1のトランジスタ100、第2のトランジスタ200、容量素子300を有する。第2のトランジスタ200は第1のトランジスタ100の上方に設けられ、第1のトランジスタ100と第2のトランジスタ200の間には容量素子300が設けられている。

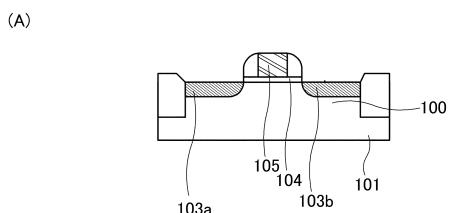

**【0071】**

第1のトランジスタ100は、半導体基板101上に設けられ、半導体基板101の一部からなる半導体膜102、ゲート絶縁膜104、ゲート電極105、及びソース領域またはドレイン領域として機能する低抵抗層103a及び低抵抗層103bを有する。

40

**【0072】**

第1のトランジスタ100は、pチャネル型、nチャネル型のいずれでもよいが、回路構成や駆動方法に応じて適切なトランジスタを用いればよい。

**【0073】**

半導体膜102のチャネルが形成される領域やその近傍の領域や、ソース領域またはドレイン領域となる低抵抗層103a及び低抵抗層103b等において、シリコン系半導体などの半導体を含むことが好ましく、単結晶シリコンを含むことが好ましい。または、Ge（ゲルマニウム）、SiGe（シリコンゲルマニウム）、GaAs（ガリウムヒ素）、GaAlAs（ガリウムアルミニウムヒ素）などを有する材料で形成してもよい。結晶格子

50

に応力を与え、格子間隔を変化させることで有効質量を制御したシリコンを用いた構成としてもよい。またはG a A sとG a A l A s等を用いることで、第1のトランジスタ100をHEMT(H i g h E l e c t r o n M o b i l i t y T r a n s i s t o r)としてもよい。

#### 【0074】

低抵抗層103a及び低抵抗層103bは、半導体膜102に適用される半導体材料に加え、ヒ素、リンなどのn型の導電性を付与する元素、またはホウ素などのp型の導電性を付与する元素を含む。

#### 【0075】

ゲート電極105は、ヒ素、リンなどのn型の導電性を付与する元素、もしくはホウ素などのp型の導電性を付与する元素を含むシリコンなどの半導体材料、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。しきい値電圧を調整するためにゲート電極を用いて仕事関数を調整することが好ましく、具体的にはゲート電極に窒化チタンや窒化タンタルなどの材料を用いることが好ましい。さらに導電性と埋め込み性を両立するためにゲート電極にタングステンやアルミニウムなどの金属材料を積層として用いることが好ましく、特にタングステンを用いることが耐熱性の点で好ましい。

#### 【0076】

ここで、第1のトランジスタ100は図8に示すようなトランジスタを用いてもよい。図8の一点鎖線より左側に第1のトランジスタ100のチャネル長方向の断面を、一点鎖線より右側にチャネル幅方向の断面を示す。図8に示す第1のトランジスタ100はチャネルが形成される半導体膜102(半導体基板101の一部)が凸形状を有する。また、半導体膜102の側面及び上面を、ゲート絶縁膜104を介して、ゲート電極105a及びゲート電極105bが覆うように設けられている。なお、ゲート電極105aは仕事関数を調整する材料を用いてもよい。このような第1のトランジスタ100は半導体基板の凸部を利用していることからF I N型トランジスタとも呼ばれる。なお、凸部の上部に接して、凸部を形成するためのマスクとして機能する絶縁膜を有していてもよい。また、ここでは半導体基板の一部を加工して凸部を形成する場合を示したが、S O I基板を加工して凸形状を有する半導体膜を形成してもよい。

#### 【0077】

第1のトランジスタ100を覆って、絶縁膜121、絶縁膜122、及び絶縁膜301が順に積層して設けられている。

#### 【0078】

絶縁膜121はその下層に設けられる第1のトランジスタ100などによって生じる段差を平坦化する平坦化膜として機能する。絶縁膜121の上面は、平坦性を高めるために化学機械研磨(C M P : C h e m i c a l M e c h a n i c a l P o l i s h i n g)法等を用いた平坦化処理により平坦化されていてもよい。

#### 【0079】

また、絶縁膜121、絶縁膜122、及び絶縁膜301には容量素子300、または、第2のトランジスタ200と電気的に接続する配線110等が埋め込まれている。なお、本明細書等において、電極と、電極と電気的に接続する配線とが一体物であってもよい。すなわち、配線の一部が電極として機能する場合や、電極の一部が配線として機能する場合もある。

#### 【0080】

各配線(配線308等)の材料としては、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。耐熱性と導電性を両立するタングステンやモリブデンなどの高融点材料を用いることが好ましく、特にタングステンを用いることが好ましい。特に、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。上記のような材料を用いることで配線抵抗を低くすることができる。

#### 【0081】

絶縁膜301の上部及び配線308の上部には、容量素子300の第1の電極302が設

10

20

30

40

50

けられている。第1の電極302は配線308と電気的に接続する。

【0082】

容量素子300の第1の電極302上にバリア層303及び絶縁体304が設けられ、絶縁体304上に容量素子300の第2の電極305が設けられている。

【0083】

また、容量素子300は、絶縁膜306に埋め込まれるように設けられ、絶縁膜306の上面は平坦化されていることが好ましい。

【0084】

絶縁膜306の上に絶縁膜を形成する。なお、本実施例では絶縁膜201及び絶縁膜202の2層を形成したが、単層でも、3層以上の積層でもよい。

10

【0085】

絶縁膜202は、加熱により一部の酸素が脱離する酸化物材料を用いることが好ましい。

【0086】

加熱により酸素を脱離する酸化物材料として、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物を用いることが好ましい。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物膜は、加熱により一部の酸素が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物膜は、昇温脱離ガス分光法(TDS: Thermal Desorption Spectroscopy)分析にて、酸素原子に換算しての酸素の脱離量が $1.0 \times 10^{18}$  atoms/cm<sup>3</sup>以上、好ましくは $3.0 \times 10^{20}$  atoms/cm<sup>3</sup>以上である酸化物膜である。なお、上記TDS分析時における膜の表面温度としては100以上700以下、または100以上500以下の範囲が好ましい。

20

【0087】

例えばこのような材料として、酸化シリコンまたは酸化窒化シリコンを含む材料を用いることが好ましい。または、金属酸化物を用いることもできる。なお、本明細書中において、酸化窒化シリコンとは、その組成として窒素よりも酸素の含有量が多い材料を指し、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多い材料を示す。

【0088】

絶縁膜202の上部には、第2のトランジスタ200が設けられている。

30

【0089】

電極204a及び電極204bは、一方がソース電極として機能し、他方がドレイン電極として機能する。

【0090】

電極204a及び電極204bは、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニアム、モリブデン、銀、タンタル、またはタングステンなどの金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、タングステン膜上にアルミニウム膜を積層する二層構造、銅-マグネシウム-アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タングステン膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。

40

【0091】

ゲート絶縁膜205は、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化ジルコニアム、チタン酸ジルコニアム( P Z T )、チタン酸ストロンチウム( S r T i O<sub>3</sub> )または( B a , S r ) T i O<sub>3</sub> ( B S T )などのいわゆる h i g h - k 材料を含む絶縁膜を単層または積層で用いる

50

ことができる。またはこれらの絶縁膜に例えば酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タンゲステン、酸化イットリウム、酸化ジルコニウムを添加してもよい。またはこれらの絶縁膜を窒化処理しても良い。上記の絶縁膜に酸化シリコン、酸化窒化シリコンまたは窒化シリコンを積層して用いてもよい。

#### 【0092】

また、ゲート絶縁膜205として、絶縁膜202と同様に、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いることが好ましい。

#### 【0093】

なお、特定の材料をゲート絶縁膜に用いると、特定の条件でゲート絶縁膜に電子を捕獲せしめて、しきい値電圧を増大させることもできる。例えば、酸化シリコンと酸化ハフニウムの積層膜のように、ゲート絶縁膜の一部に酸化ハフニウム、酸化アルミニウム、酸化タンタルのような電子捕獲準位の多い材料を用い、より高い温度（半導体装置の使用温度あるいは保管温度よりも高い温度、あるいは、125以上450以下、代表的には150以上300以下）の下で、ゲート電極の電位をソース電極やドレイン電極の電位より高い状態を、10ミリ秒以上、代表的には1分以上維持することで、半導体膜からゲート電極に向かって、電子が移動し、そのうちのいくらかは電子捕獲準位に捕獲される。

10

#### 【0094】

このように電子捕獲準位に必要な量の電子を捕獲させたトランジスタは、しきい値電圧がプラス側にシフトする。ゲート電極の電圧の制御によって電子の捕獲する量を制御することができ、それに伴ってしきい値電圧を制御することができる。また、電子を捕獲せしめる処理は、トランジスタの作製過程におこなえばよい。

20

#### 【0095】

例えば、トランジスタのソース電極あるいはドレイン電極に接続する配線の形成後、あるいは、前工程（ウェハー処理）の終了後、あるいは、ウェハーダイシング工程後、パッケージ後等、工場出荷前のいずれかの段階で行うとよい。いずれの場合にも、その後に125以上の温度に1時間以上さらされないことが好ましい。

#### 【0096】

導電体206a及び導電体206bを有するゲート電極206は、例えばアルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた金属、または上述した金属を成分とする合金か、上述した金属を組み合わせた合金等を用いて形成することができる。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属を用いてもよい。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体、ニッケルシリサイド等のシリサイドを用いてもよい。例えば、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンゲステン膜を積層する二層構造、窒化タンタル膜または窒化タンゲステン膜上にタンゲステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数の金属を組み合わせた合金膜、もしくは窒化膜を用いてもよい。

30

#### 【0097】

また、ゲート電極206は、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属の積層構造とすることもできる。

#### 【0098】

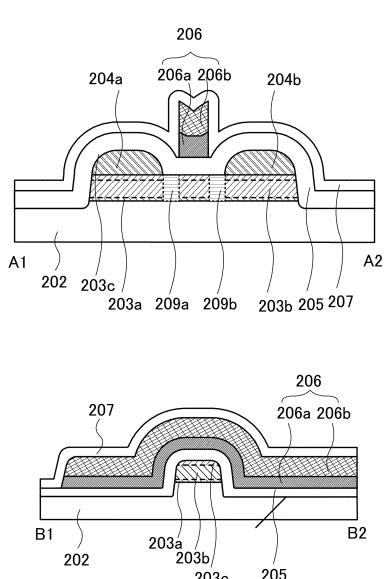

ここで、第2のトランジスタ200に適用可能なトランジスタの構成例について示す。図9(A)は以下で例示するトランジスタの上面概略図であり、図9(B)、図9(C)は

40

50

それぞれ、図9(A)中の切断線A1-A2、B1-B2で切断したときの断面概略図である。なお、図9(B)はトランジスタのチャネル長方向の断面に相当し、図9(C)はトランジスタのチャネル幅方向の断面に相当する。

#### 【0099】

図9(C)に示すように、トランジスタのチャネル幅方向の断面において、ゲート電極206が酸化物半導体層203bの上面及び側面に面して設けられることで、酸化物半導体層203bの上面近傍だけでなく側面近傍にまでチャネルが形成され、実効的なチャネル幅が増大し、オン状態における電流(オン電流)を高めることができる。特に、酸化物半導体層203bの幅が極めて小さい(例えば50nm以下、好ましくは30nm以下、より好ましくは20nm以下)場合には、酸化物半導体層203bの内部にまでチャネルが形成される領域が広がるため、微細化するほどオン電流に対する寄与が高まる。10

#### 【0100】

なお、図10(A)、図10(B)、図10(C)に示すように、ゲート電極206の幅を狭くしてもよい。その場合、例えば、電極204a及び電極204bや、ゲート電極206などをマスクとして、酸化物半導体層203bなどに、アルゴン、水素、リン、ホウ素などの不純物を導入することができる。その結果、酸化物半導体層203bなどにおいて、低抵抗領域209a、低抵抗領域209bを設けることができる。なお、低抵抗領域209a、低抵抗領域209bは、必ずしも、設けなくてもよい。なお、図9だけでなく、他の図面においても、ゲート電極206の幅を狭くすることができる。20

#### 【0101】

図11(A)、図11(B)に示すトランジスタは、図9で例示したトランジスタと比較して、酸化物半導体層203cが電極204a及び電極204bの下面に接して設けられている点で主に相違している。20

#### 【0102】

このような構成とすることで、酸化物半導体層203a、酸化物半導体層203b及び酸化物半導体層203cを構成するそれぞれの膜の成膜時において、大気に触れさせることなく連続的に成膜することができるため、各々の界面欠陥を低減することができる。

#### 【0103】

また、上記では、酸化物半導体層203bに接して酸化物半導体層203a及び酸化物半導体層203cを設ける構成を説明したが、酸化物半導体層203aまたは酸化物半導体層203cの一方、またはその両方を設けない構成としてもよい。30

#### 【0104】

なお、図11においても、図9と同様に、ゲート電極206の幅を狭くすることができる。その場合の例を、図12(A)、図12(B)に示す。なお、図9、図11だけでなく、他の図面においても、ゲート電極206の幅を狭くすることができる。

#### 【0105】

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソース(ソース領域またはソース電極)とドレイン(ドレイン領域またはドレイン電極)との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルが形成される領域における、いずれか一の値、最大値、最小値または平均値とする。40

#### 【0106】

チャネル幅とは、例えば、半導体(またはトランジスタがオン状態のときに半導体の中で電流の流れる部分)とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では50

、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

#### 【0107】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅（以下、実効的なチャネル幅と呼ぶ。）と、トランジスタの上面図において示されるチャネル幅（以下、見かけ上のチャネル幅と呼ぶ。）と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅の方が大きくなる。10

#### 【0108】

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるためにには、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

#### 【0109】

そこで、本明細書では、トランジスタの上面図において、半導体とゲート電極とが重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅（SCW：Surrounded Channel Width）」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面TEM像などを取得して、その画像を解析することなどによって、値を決定することができる。20

#### 【0110】

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。30

#### 【0111】

以上が第2のトランジスタ200についての説明である。

#### 【0112】

第2のトランジスタ200を覆う絶縁膜207、絶縁膜208は、バリア膜、またはその下層の凹凸形状を被覆する平坦化膜として機能してもよい。

#### 【0113】

以上が構成例についての説明である。

#### 【0114】

##### [作製方法例]

以下では、上記構成例で示した半導体装置の作製方法の一例について、図13乃至図15を用いて説明する。40

#### 【0115】

まず、半導体基板101を準備する。半導体基板101としては、例えば、単結晶シリコン基板（p型の半導体基板、またはn型の半導体基板を含む）、炭化シリコンや窒化ガリウムを材料とした化合物半導体基板などを用いることができる。また、半導体基板101として、SOI基板を用いてもよい。以下では、半導体基板101として単結晶シリコンを用いた場合について説明する。

#### 【0116】

続いて、半導体基板101に素子分離層を形成する。素子分離層はLOCOS（Loca50

l Oxidation of Silicon) 法または STI (Shallow Trench Isolation) 法等を用いて形成すればよい。

#### 【0117】

なお、同一基板上に p 型のトランジスタと n 型のトランジスタを形成する場合、半導体基板 101 の一部に n ウェルまたは p ウェルを形成してもよい。例えば、n 型の半導体基板 101 に p 型の導電性を付与するホウ素などの不純物元素を添加して p ウェルを形成し、同一基板上に n 型のトランジスタと p 型のトランジスタを形成してもよい。

#### 【0118】

続いて、半導体基板 101 上にゲート絶縁膜 104 となる絶縁膜を形成する。例えば、表面窒化処理後に酸化処理を行い、シリコンと窒化シリコン界面を酸化して酸化窒化シリコン膜を形成してもよい。例えば NH<sub>3</sub> 霧囲気中で 700 °C にて熱窒化シリコン膜を表面に形成後に酸素ラジカル酸化を行うことで酸化窒化シリコン膜が得られる。

#### 【0119】

当該絶縁膜は、スパッタリング法、CVD (Chemical Vapor Deposition) 法(熱 CVD 法、MOCVD (Metal Organic CVD) 法、PECVD (Plasma Enhanced CVD) 法等を含む)、MBE (Molecular Beam Epitaxy) 法、ALD (Atomic Layer Deposition) 法、または PLD (Pulsed Laser Deposition) 法等で成膜することにより形成してもよい。

#### 【0120】

続いて、ゲート電極 105 となる導電膜を成膜する。導電膜としては、タンタル、タンゲステン、チタン、モリブデン、クロム、ニオブ等から選択された金属、またはこれらの金属を主成分とする合金材料若しくは化合物材料を用いることが好ましい。また、リン等の不純物を添加した多結晶シリコンを用いることができる。また、金属窒化物膜と上記の金属膜の積層構造を用いてもよい。金属窒化物としては、窒化タンゲステン、窒化モリブデン、窒化チタンを用いることができる。金属窒化物膜を設けることにより、金属膜の密着性を向上させることができ、剥離を防止することができる。また、ゲート電極 105 の仕事関数を制御する金属膜を設けてもよい。

#### 【0121】

導電膜は、スパッタリング法、蒸着法、CVD 法(熱 CVD 法、MOCVD 法、PECVD 法等を含む)などにより成膜することができる。また、プラズマによるダメージを減らすには、熱 CVD 法、MOCVD 法あるいは ALD 法が好ましい。

#### 【0122】

続いて、当該導電膜上にリソグラフィ法等を用いてレジストマスクを形成し、当該導電膜の不要な部分を除去する。その後、レジストマスクを除去することにより、ゲート電極 105 を形成することができる。

#### 【0123】

ここで、被加工膜の加工方法について説明する。被加工膜を微細に加工する場合には、様々な微細加工技術を用いることができる。例えば、リソグラフィ法等で形成したレジストマスクに対してスリミング処理を施す方法を用いてもよい。また、リソグラフィ法等でダミーパターンを形成し、当該ダミーパターンにサイドウォールを形成した後にダミーパターンを除去し、残存したサイドウォールをレジストマスクとして用いて、被加工膜をエッチングしてもよい。また、被加工膜のエッチングとして、高いアスペクト比を実現するために、異方性のドライエッチングを用いることが好ましい。また、無機膜または金属膜からなるハードマスクを用いてもよい。

#### 【0124】

レジストマスクの形成に用いる光は、例えば i 線(波長 365 nm)、g 線(波長 436 nm)、h 線(波長 405 nm)、またはこれらを混合させた光を用いることができる。そのほか、紫外線や KrF レーザ光、または ArF レーザ光等を用いることもできる。また、液浸露光技術により露光を行ってもよい。また、露光に用いる光として、極端紫外光

10

20

30

40

50

(EUV: Extreme Ultra-violet) や X 線を用いてもよい。また、露光に用いる光に換えて、電子ビームを用いることもできる。極端紫外光、X 線または電子ビームを用いると、極めて微細な加工が可能となるため好ましい。なお、電子ビームなどのビームを走査することにより露光を行う場合には、フォトマスクは不要である。

#### 【0125】

また、レジストマスクとなるレジスト膜を形成する前に、被加工膜とレジスト膜との密着性を改善する機能を有する有機樹脂膜を形成してもよい。当該有機樹脂膜は、例えばスピニコート法などにより、その下層の段差を被覆して表面を平坦化するように形成することができ、当該有機樹脂膜の上層に設けられるレジストマスクの厚さのばらつきを低減できる。また、特に微細な加工を行う場合には、当該有機樹脂膜として、露光に用いる光に対する反射防止膜として機能する材料を用いることが好ましい。このような機能を有する有機樹脂膜としては、例えば BARC (Bottom Anti-Reflection Coating) 膜などがある。当該有機樹脂膜は、レジストマスクの除去と一緒に除去するか、レジストマスクを除去した後に除去すればよい。

10

#### 【0126】

ゲート電極 105 の形成後、ゲート電極 105 の側面を覆うサイドウォールを形成してもよい。サイドウォールは、ゲート電極 105 の厚さよりも厚い絶縁膜を成膜した後に、異方性エッチングを施し、ゲート電極 105 の側面部分のみ当該絶縁膜を残存させることにより形成できる。

20

#### 【0127】

サイドウォールの形成時にゲート絶縁膜 104 となる絶縁膜も同時にエッチングされることにより、ゲート電極 105 及びサイドウォールの下部にゲート絶縁膜 104 が形成される。または、ゲート電極 105 を形成した後にゲート電極 105 またはゲート電極 105 を加工するためのレジストマスクをエッチングマスクとして当該絶縁膜をエッチングすることによりゲート絶縁膜 104 を形成してもよい。または、当該絶縁膜に対してエッチングによる加工を行わずに、そのままゲート絶縁膜 104 として用いることもできる。

#### 【0128】

続いて、半導体基板 101 のゲート電極 105 (及びサイドウォール) が設けられていない領域にリンなどの n 型の導電性を付与する元素、またはホウ素などの p 型の導電性を付与する元素を添加する。この段階における断面概略図が図 13 (A) に相当する。

30

#### 【0129】

続いて、絶縁膜 121 を形成した後、上述した導電性を付与する元素の活性化のための第 1 の加熱処理を行う。

#### 【0130】

絶縁膜 121 は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよく、積層または単層で設ける。また、酸素と水素を含む窒化シリコン (SiN<sub>x</sub>) を用いると、加熱によって脱離する水素の量を多くするため好ましい。また、TEOS (Tetra-Ethyl-Ortho-Silicate) 若しくはシラン等と、酸素若しくは亜酸化窒素等とを反応させて形成した段差被覆性の良い酸化シリコンを用いることもできる。

40

#### 【0131】

絶縁膜 121 は、例えば、スパッタリング法、CVD 法 (熱 CVD 法、MOCVD 法、PECVD 法等を含む)、MBE 法、ALD 法または PLD 法などを用いて形成することができる。特に、当該絶縁膜を CVD 法、好ましくはプラズマ CVD 法によって成膜すると、被覆性を向上させることができるため好ましい。また、プラズマによるダメージを減らすには、熱 CVD 法、MOCVD 法あるいは ALD 法が好ましい。

#### 【0132】

第 1 の加熱処理は、希ガスや窒素ガスなどの不活性ガス雰囲気下、または減圧雰囲気下にて、例えば、400 以上でかつ基板の歪み点未満で行うことができる。

50

**【0133】**

この段階で第1のトランジスタ100が形成される。

**【0134】**

続いて絶縁膜121の上面をCMP法等を用いて平坦化する。

**【0135】**

続いて、絶縁膜121に低抵抗層103a、低抵抗層103b及びゲート電極105等に達する開口を形成する。その後、開口を埋めるように導電膜を形成し、絶縁膜121の上面が露出するように該導電膜に平坦化処理を施すことにより、配線111a、配線111b、配線110等を形成する。導電膜の形成は、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。10

**【0136】**

続いて、絶縁膜121上に導電膜を成膜する。その後上記と同様の方法によりレジストマスクを形成し、導電膜の不要な部分をエッチングにより除去する。その後レジストマスクを除去することにより、配線を形成した後、さらに、絶縁膜122を形成し、配線の上面が見えるまで、CMP法等を用いて平坦化することにより、埋め込み配線を形成する。また、ダマシン法を用いて形成してもよい。なお、絶縁膜122は絶縁膜121と同様の材料及び方法で作成することができる。

**【0137】**

次に、絶縁膜301を形成した後、絶縁膜301に配線110に接続される配線に達するコンタクトホールを形成し、配線110と同様の材料及び方法で、配線308を形成する。この段階における断面概略図が図13(B)に相当する。20

**【0138】**

続いて、配線308に接続されるように、容量素子300を形成する。作成方法は実施の形態1の作成方法例で示した。容量素子300を形成した段階における断面概略図が図13(C)に相当する。

**【0139】**

続いて、容量素子300を覆う絶縁膜306となる絶縁膜を成膜する。絶縁膜306となる絶縁膜は、絶縁膜121等と同様の材料及び方法により形成することができる。

**【0140】**

また、絶縁膜306となる絶縁膜を形成した後、その上面の平坦性を高めるためにCMP法等を用いた平坦化処理を行って絶縁膜306を形成する。30

**【0141】**

続いて、絶縁膜201および絶縁膜202となる絶縁膜を成膜する。絶縁膜201および絶縁膜202となる絶縁膜は、例えばスパッタリング法、CVD法(熱CVD法、MOCVD法、PECVD法等を含む)、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、当該絶縁膜をCVD法、好ましくはプラズマCVD法によって成膜すると、被覆性を向上させることができるため好ましい。また、プラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。

**【0142】**

また、絶縁膜202となる絶縁膜に酸素を過剰に含有させるためには、例えば酸素雰囲気下にて絶縁膜202となる絶縁膜の成膜を行えばよい。または、成膜後の絶縁膜202となる絶縁膜に酸素を導入して酸素を過剰に含有する領域を形成してもよく、双方の手段を組み合わせてもよい。40

**【0143】**

例えば、成膜後の絶縁膜202となる絶縁膜に酸素(少なくとも酸素ラジカル、酸素原子、酸素イオンのいずれかを含む)を導入して酸素を過剰に含有する領域を形成する。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理などを用いることができる。

**【0144】**

50

酸素導入処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。また、酸素導入処理において、酸素を含むガスに希ガスを含ませてもよく、例えば、二酸化炭素と水素とアルゴンの混合ガスを用いることができる。

#### 【0145】

また、絶縁膜202となる絶縁膜を形成した後、その上面の平坦性を高めるためにC M P法等を用いた平坦化処理を行って絶縁膜202を形成してもよい。

#### 【0146】

続いて、酸化物半導体層203aとなる酸化物半導体膜と、酸化物半導体層203bとなる酸化物半導体膜を順に成膜する。当該酸化物半導体膜は、大気に触れさせることなく連続して成膜することが好ましい。10

#### 【0147】

酸化物半導体層203bとなる酸化物半導体膜を成膜後、加熱処理を行うことが好ましい。加熱処理は、250以上650以下、好ましくは300以上500以下の温度で、不活性ガス雰囲気、酸化性ガスを10ppm以上含む雰囲気、または減圧状態で行えばよい。また、加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上含む雰囲気で行ってもよい。加熱処理は、酸化物半導体層203bとなる酸化物半導体膜を成膜した直後に行なってもよいし、酸化物半導体層203bとなる酸化物半導体膜を加工して島状の酸化物半導体層203bを形成した後に行なってもよい。加熱処理により、絶縁膜202から酸化物半導体層に酸素が供給され、酸化物半導体層中の酸素欠損を低減することができる。20

#### 【0148】

その後、酸化物半導体層203bとなる酸化物半導体膜上にハードマスクとなる導電膜及び上記と同様の方法によりレジストマスクを形成し、導電膜の不要な部分をエッチングにより除去する。その後、導電膜をマスクとして酸化物半導体膜の不要な部分をエッチングにより除去する。その後レジストマスクを除去することにより、島状の酸化物半導体層203aと島状の酸化物半導体層203bの積層構造を形成することができる。なお、ハードマスクとなる導電膜は、後に形成する電極204a、電極204bの一部として用いてよい。

#### 【0149】

次に、絶縁膜202、島状の酸化物半導体層203a、及び島状の酸化物半導体層203b上にレジストマスクを形成し、絶縁膜202、絶縁膜201、絶縁膜306、絶縁体304、バリア層303を貫通するコンタクトホール310を形成する（図14（A）参照）。

#### 【0150】

続いて、導電膜を形成する。導電膜の形成は、例えばスパッタリング法、CVD法（熱CVD法、MOCVD法、PECVD法等を含む）、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、当該導電膜をCVD法、好ましくはプラズマCVD法によって成膜すると、被覆性を向上させることができると好ましい。また、プラズマによるダメージを減らすには、熱CVD法、MOCVD法あるいはALD法が好ましい。40

#### 【0151】

次に、導電膜上に上記と同様の方法によりレジストマスクを形成し、導電膜の不要な部分をエッチングにより除去する。その後レジストマスクを除去することにより、電極204a、電極204b、及び電極204aと容量素子300の第1の電極302とをコンタクトホール310を介して接続する配線307を同時に形成することができる。

#### 【0152】

続いて、酸化物半導体層203cとなる酸化物半導体膜と、絶縁膜を順に成膜する。絶縁膜上に上記と同様の方法によりレジストマスクを形成し、絶縁膜及び酸化物半導体膜の不要な部分をエッチングにより除去する。その後レジストマスクを除去することにより、酸50

化物半導体層 203c、及びゲート絶縁膜 205を形成する。

【0153】

続いて、導電膜を成膜し、導電体 206a、及び導電体 206b を有するゲート電極 206を形成する。

【0154】

この段階で第 2 のトランジスタ 200 が形成される。

【0155】

続いて、絶縁膜 207、及び必要に応じて絶縁膜 208 を形成する。絶縁膜 207、絶縁膜 208 は、例えばスパッタリング法、CVD 法（熱 CVD 法、MOCVD 法、PECVD 法等を含む）、MBE 法、ALD 法または PLD 法などを用いて形成することができる。特に、当該絶縁膜を CVD 法、好ましくはプラズマ CVD 法によって成膜すると、被覆性を向上させることができるとため好ましい。また、プラズマによるダメージを減らすには、熱 CVD 法、MOCVD 法あるいは ALD 法が好ましい（図 14 (B) 参照）。10

【0156】

以上の工程により、本発明の一態様の半導体装置を作製することができる。

【0157】

<変形例 1 >

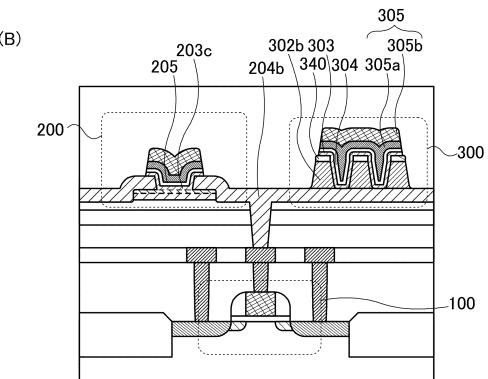

また、本実施の形態の変形例として、図 15 に示すように容量素子 300 の位置を第 2 のトランジスタ 200 より上方に設けてよい。具体的には、第 1 のトランジスタ 100 上に、第 2 のトランジスタ 200 を形成した後、容量素子 300 を形成すればよい。なお、配線 250 を介して、第 1 のトランジスタ 100 と第 2 のトランジスタ 200 を接続する。また、第 2 のトランジスタ 200 の電極 204b を延在した配線に到達するように層間絶縁膜にコンタクトホールを形成する。そして、コンタクトホールに配線 350 を形成することにより、容量素子 300、第 1 のトランジスタ 100、及び第 2 のトランジスタ 200 を電気的に接続すればよい。20

【0158】

<変形例 2 >

また、図 16 (A) 及び図 16 (B) に示すように、第 2 のトランジスタ 200 のソース電極またはドレイン電極の一方と、容量素子 300 の第 1 の電極とを、同一の導電層により設ける構成としてもよい。従って、図中に示す電極 204b は、第 2 のトランジスタ 200 のソース電極またはドレイン電極の一方、および容量素子 300 の第 1 の電極としての機能を有する。30

【0159】

図 16 (A) を具体的に説明する。電極 204b となる導電膜を十分に厚く形成する。上記と同様の方法によりレジストマスクを形成し、導電膜の不要な部分を除去する。次に、レジストマスクを除去した後、酸化物半導体層 203c、及びバリア層 303 となる酸化物半導体膜を形成する。上記と同様にレジストマスクを形成し、酸化物半導体膜の不要な部分を除去する。レジストマスクを除去することで、酸化物半導体層 203c、及びバリア層 303 を形成する。

【0160】

次に、酸化物半導体層 203c 及びバリア層 303 をマスクとして、電極 204b となる導電膜を絶縁膜 202 に到達しない程度にハーフエッチングすることにより、第 2 のトランジスタ 200 のソース電極またはドレイン電極の一方、及び容量素子 300 の第 1 の電極として機能する電極 204b を形成することができる。40

【0161】

続いて、絶縁体 304（ゲート絶縁膜 205）を形成する。絶縁体 304 上に導電膜を形成し、上記と同様にレジストマスクを形成し、導電膜の不要な部分を除去することで、第 2 のトランジスタ 200 と容量素子 300 を同時に形成することができる。

【0162】

図 16 (B) を具体的に説明する。第 2 のトランジスタ 200 のソース電極またはドレイ50

ン電極の一方、及び容量素子 300 の第 1 の電極の一部として機能する電極 204b を形成する。続いて、容量素子 300 の第一の電極の凸部となる導電層 302b、及びバリア層 303 を形成した後、酸化物半導体層 203c 及び中間層 340 となる酸化物半導体膜と、絶縁体 304 及びゲート絶縁膜 205 となる絶縁膜と、導電体 305a と導電体 305b とを有する第 2 の電極 305 及び導電体 206a と導電体 206b とを有するゲート電極 206 となる導電膜を形成する。上記と同様にレジストマスクを形成し、酸化物半導体膜、絶縁膜、及び導電膜の不要な部分を除去することで、第 2 のトランジスタ 200 と容量素子 300 を同時に形成することができる。

#### 【0163】

図 16 (A) または図 16 (B) の構造を用いることで、工程数及びマスク枚数を削減、

または増やすことなく微細化・高密度化に適した半導体装置を提供することができる。

10

#### 【0164】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【0165】

##### (実施の形態 3)

本実施の形態では、本発明の一態様の半導体装置の半導体膜に好適に用いることのできる酸化物半導体について説明する。

#### 【0166】

##### <酸化物半導体の構造>

以下では、酸化物半導体の構造について説明する。

20

#### 【0167】

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体とに分けられる。非単結晶酸化物半導体としては、 C AAC - OS ( C Axis Aligned Crystalline Oxide Semiconductor )、多結晶酸化物半導体、 nc - OS ( nanocrystalline Oxide Semiconductor )、擬似非晶質酸化物半導体 ( a - like OS : amorphous like Oxide Semiconductor )、非晶質酸化物半導体などがある。

#### 【0168】

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体とに分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、 C AAC - OS 、多結晶酸化物半導体、 nc - OS などがある。

30

#### 【0169】

非晶質構造の定義としては、一般に、準安定状態で固定化していないこと、等方的であつて不均質構造を持たないことなどが知られている。また、結合角度が柔軟であり、短距離秩序性は有するが、長距離秩序性を有さない構造と言い換えることもできる。

#### 【0170】

逆の見方をすると、本質的に安定な酸化物半導体の場合、完全な非晶質 ( complete ely amorphous ) 酸化物半導体と呼ぶことはできない。また、等方的でない ( 例えは、微小な領域において周期構造を有する ) 酸化物半導体を、完全な非晶質酸化物半導体と呼ぶことはできない。ただし、 a - like OS は、微小な領域において周期構造を有するものの、鬆 ( ボイドともいう。 ) を有し、不安定な構造である。そのため、物性的には非晶質酸化物半導体に近いといえる。

40

#### 【0171】

##### < C AAC - OS >

まずは、 C AAC - OS について説明する。

#### 【0172】

C AAC - OS は、 c 軸配向した複数の結晶部を有する酸化物半導体の一つである。

#### 【0173】

透過型電子顕微鏡 ( TEM : Transmission Electron Micro

50

s c o p e ) によって、 C A A C - O S の明視野像と回折パターンとの複合解析像（高分解能 T E M 像ともいう。）を観察すると、複数の結晶部を確認することができる。一方、高分解能 T E M 像では結晶部同士の境界、即ち結晶粒界（グレインバウンダリーともいう。）を明確に確認することができない。そのため、 C A A C - O S は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

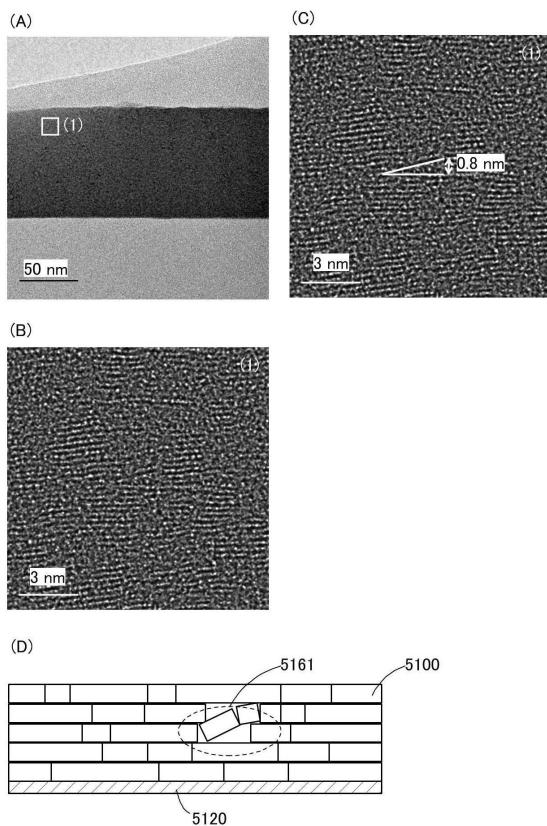

#### 【 0 1 7 4 】

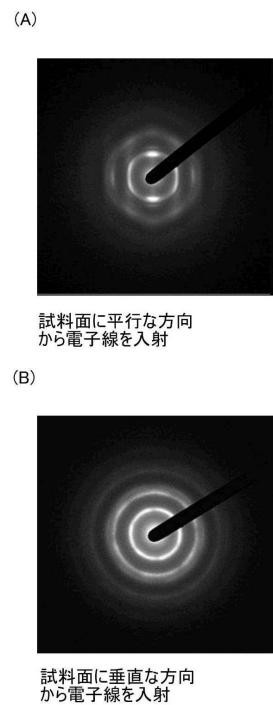

以下では、 T E M によって観察した C A A C - O S について説明する。図 17 ( A ) に、試料面と略平行な方向から観察した C A A C - O S の断面の高分解能 T E M 像を示す。高分解能 T E M 像の観察には、球面収差補正 ( Spherical Aberration Corrector ) 機能を用いた。球面収差補正機能を用いた高分解能 T E M 像を、特に Cs 補正高分解能 T E M 像と呼ぶ。Cs 補正高分解能 T E M 像の取得は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡 J E M - A R M 2 0 0 F などによって行うことができる。

10

#### 【 0 1 7 5 】

図 17 ( A ) の領域 ( 1 ) を拡大した Cs 補正高分解能 T E M 像を図 17 ( B ) に示す。図 17 ( B ) より、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層の配列は、 C A A C - O S の膜を形成する面（被形成面ともいう。）または上面の凹凸を反映しており、 C A A C - O S の被形成面または上面と平行となる。

#### 【 0 1 7 6 】

図 17 ( B ) に示すように、 C A A C - O S は特徴的な原子配列を有する。図 17 ( C ) 20 は、特徴的な原子配列を、補助線で示したものである。図 17 ( B ) および図 17 ( C ) より、結晶部一つの大きさは 1 n m 以上 3 n m 以下程度であり、結晶部と結晶部との傾きにより生じる隙間の大きさは 0 . 8 n m 程度であることがわかる。したがって、結晶部を、ナノ結晶 ( nc : nanocrystal ) と呼ぶこともできる。また、 C A A C - O S を、 C A N C ( C - A x i s A l i g n e d n a n o c r y s t a l s ) を有する酸化物半導体と呼ぶこともできる。

#### 【 0 1 7 7 】

ここで、 Cs 補正高分解能 T E M 像をもとに、基板 5 1 2 0 上の C A A C - O S の結晶部 5 1 0 0 の配置を模式的に示すと、レンガまたはブロックが積み重なったような構造となる（図 17 ( D ) 参照。）。図 17 ( C ) で観察された結晶部と結晶部との間で傾きが生じている箇所は、図 17 ( D ) に示す領域 5 1 6 1 に相当する。

30

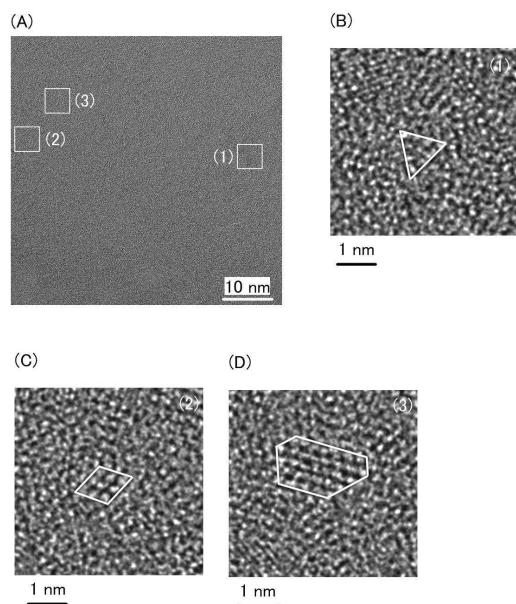

#### 【 0 1 7 8 】

また、図 18 ( A ) に、試料面と略垂直な方向から観察した C A A C - O S の平面の Cs 補正高分解能 T E M 像を示す。図 18 ( A ) の領域 ( 1 ) 、領域 ( 2 ) および領域 ( 3 ) を拡大した Cs 補正高分解能 T E M 像を、それぞれ図 18 ( B ) 、図 18 ( C ) および図 18 ( D ) に示す。図 18 ( B ) 、図 18 ( C ) および図 18 ( D ) より、結晶部は、金属原子が三角形状、四角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

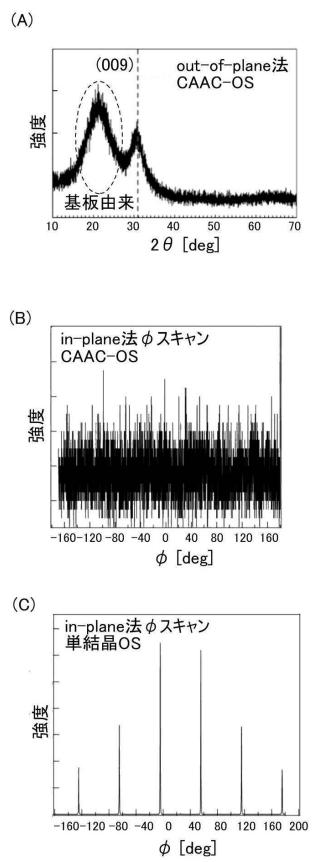

#### 【 0 1 7 9 】

次に、 X 線回折 ( X R D : X - R a y D i f f r a c t i o n ) によって解析した C A A C - O S について説明する。例えば、 I n G a Z n O<sub>4</sub> の結晶を有する C A A C - O S に対し、 o u t - o f - p l a n e 法による構造解析を行うと、図 19 ( A ) に示すように回折角 ( 2 $\theta$  ) が 31° 近傍にピークが現れる場合がある。このピークは、 I n G a Z n O<sub>4</sub> の結晶の ( 0 0 9 ) 面に帰属されることから、 C A A C - O S の結晶が c 軸配向性を有し、 c 軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

40

#### 【 0 1 8 0 】

なお、 C A A C - O S の o u t - o f - p l a n e 法による構造解析では、 2 $\theta$  が 31° 。近傍のピークの他に、 2 $\theta$  が 36° 近傍にもピークが現れる場合がある。 2 $\theta$  が 36° 近傍のピークは、 C A A C - O S 中の一部に、 c 軸配向性を有さない結晶が含まれることを示している。より好ましい C A A C - O S は、 o u t - o f - p l a n e 法による構造解

50

析では、 $2\beta$ が $31^\circ$ 近傍にピークを示し、 $2\beta$ が $36^\circ$ 近傍にピークを示さない。

#### 【0181】

一方、CAAC-OSに対し、c軸に略垂直な方向からX線を入射させるin-plane法による構造解析を行うと、 $2\beta$ が $56^\circ$ 近傍にピークが現れる。このピークは、InGaN<sub>0.4</sub>の結晶の(110)面に帰属される。CAAC-OSの場合は、 $2\beta$ を $56^\circ$ 近傍に固定し、試料面の法線ベクトルを軸(c軸)として試料を回転させながら分析(スキャン)を行っても、図19(B)に示すように明瞭なピークは現れない。これに対し、InGaN<sub>0.4</sub>の単結晶酸化物半導体であれば、 $2\beta$ を $56^\circ$ 近傍に固定してスキャンした場合、図19(C)に示すように(110)面と等価な結晶面に帰属されるピークが6本観察される。したがって、XRDを用いた構造解析から、CAAC-OSは、 $a$ 軸および $b$ 軸の配向が不規則であることが確認できる。

10

#### 【0182】

次に、電子回折によって解析したCAAC-OSについて説明する。例えば、InGaN<sub>0.4</sub>の結晶を有するCAAC-OSに対し、試料面に平行にプローブ径が $300\text{ nm}$ の電子線を入射させると、図20(A)に示すような回折パターン(制限視野透過電子回折パターンともいう。)が現れる場合がある。この回折パターンには、InGaN<sub>0.4</sub>の結晶の(009)面に起因するスポットが含まれる。したがって、電子回折によても、CAAC-OSに含まれる結晶部がc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が $300\text{ nm}$ の電子線を入射させたときの回折パターンを図20(B)に示す。図20(B)より、リング状の回折パターンが確認される。したがって、電子回折によても、CAAC-OSに含まれる結晶部のa軸およびb軸は配向性を有さないことがわかる。なお、図20(B)における第1リングは、InGaN<sub>0.4</sub>の結晶の(010)面および(100)面などに起因すると考えられる。また、図20(B)における第2リングは(110)面などに起因すると考えられる。

20

#### 【0183】

上述したように、CAAC-OSは結晶性の高い酸化物半導体である。酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、逆の見方をするとCAAC-OSは不純物や欠陥(酸素欠損など)の少ない酸化物半導体ともいえる。

#### 【0184】

なお、不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。

30

#### 【0185】

酸化物半導体が不純物や欠陥を有する場合、光や熱などによって特性が変動する場合がある。例えば、酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。また、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。

40

#### 【0186】

不純物および酸素欠損の少ないCAAC-OSは、キャリア密度の低い酸化物半導体である。具体的には、キャリア密度を $8 \times 10^{11} / \text{cm}^3$ 未満、好ましくは $1 \times 10^{11} / \text{cm}^3$ 未満、さらに好ましくは $1 \times 10^{10} / \text{cm}^3$ 未満であり、 $1 \times 10^{-9} / \text{cm}^3$ 以上とすることができます。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。CAAC-OSは、不純物濃度が低く、欠陥準位密度が低い。即ち、安定な特性を有する酸化物半導体であるといえる。

#### 【0187】

< n c - OS >

次に、n c - O Sについて説明する。

**【0188】**

n c - O Sは、高分解能TEM像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。n c - O Sに含まれる結晶部は、1 nm以上10 nm以下、または1 nm以上3 nm以下の大きさであることが多い。なお、結晶部の大きさが10 nmより大きく100 nm以下である酸化物半導体を微結晶酸化物半導体と呼ぶことがある。n c - O Sは、例えば、高分解能TEM像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、C AAC - O Sにおける結晶部と起源を同じくする可能性がある。

**【0189】**

n c - O Sは、微小な領域（例えば、1 nm以上10 nm以下の領域、特に1 nm以上3 nm以下の領域）において原子配列に周期性を有する。また、n c - O Sは、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O Sは、分析方法によっては、a - like O Sや非晶質酸化物半導体と区別が付かない場合がある。例えば、n c - O Sに対し、結晶部よりも大きい径のX線を用いた場合、out-of-plane法による解析では、結晶面を示すピークは検出されない。また、n c - O Sに対し、結晶部よりも大きいプローブ径（例えば50 nm以上）の電子線を用いる電子回折を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O Sに対し、結晶部の大きさと近いか結晶部より小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - O Sに対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。さらに、リング状の領域内に複数のスポットが観測される場合がある。

10

**【0190】**

このように、結晶部（ナノ結晶）間では結晶方位が規則性を有さないことから、n c - O Sを、R ANC (Random Aligned nanocrystals)を有する酸化物半導体、またはN ANC (Non-Aligned nanocrystals)を有する酸化物半導体と呼ぶこともできる。

**【0191】**

n c - O Sは、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、n c - O Sは、a - like O Sや非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、n c - O Sは、異なる結晶部間で結晶方位に規則性が見られない。そのため、n c - O Sは、C AAC - O Sと比べて欠陥準位密度が高くなる。

30

**【0192】**

<a - like O S>

a - like O Sは、n c - O Sと非晶質酸化物半導体との間の構造を有する酸化物半導体である。

**【0193】**

a - like O Sは、高分解能TEM像において鬆が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。

40

**【0194】**

鬆を有するため、a - like O Sは、不安定な構造である。以下では、a - like O Sが、C AAC - O Sおよびn c - O Sと比べて不安定な構造であることを示すため、電子照射による構造の変化を示す。

**【0195】**

電子照射を行う試料として、a - like O S（試料Aと表記する。）、n c - O S（試料Bと表記する。）およびC AAC - O S（試料Cと表記する。）を準備する。いずれの試料もIn - Ga - Zn酸化物である。

**【0196】**

50

まず、各試料の高分解能断面TEM像を取得する。高分解能断面TEM像により、各試料は、いずれも結晶部を有することがわかる。

#### 【0197】

なお、どの部分を一つの結晶部と見なすかの判定は、以下のように行えばよい。例えば、 $InGaZnO_4$  の結晶の単位格子は、In-O層を3層有し、またGa-Zn-O層を6層有する、計9層がc軸方向に層状に重なった構造を有することが知られている。これらの近接する層同士の間隔は、(009)面の格子面間隔(d値ともいう。)と同程度であり、結晶構造解析からその値は0.29nmと求められている。したがって、格子縞の間隔が0.28nm以上0.30nm以下の箇所を、 $InGaZnO_4$  の結晶部と見なすことができる。なお、格子縞は、 $InGaZnO_4$  の結晶のa-b面に対応する。

10

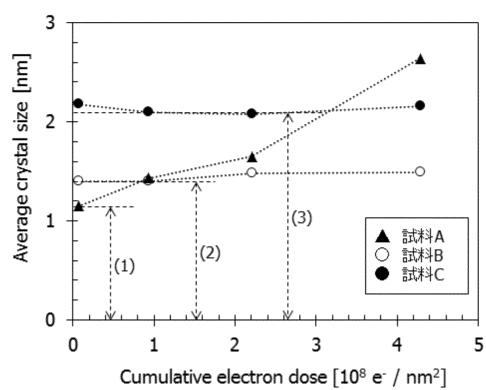

#### 【0198】

図21は、各試料の結晶部(22箇所から45箇所)の平均の大きさを調査した例である。ただし、上述した格子縞の長さを結晶部の大きさとしている。図21より、a-like OSは、電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。具体的には、図21中に(1)で示すように、TEMによる観察初期においては1.2nm程度の大きさだった結晶部(初期核ともいう。)が、累積照射量が $4.2 \times 10^8 e^- / nm^2$ においては2.6nm程度の大きさまで成長していることがわかる。一方、nc-OSおよびCAAC-OSは、電子照射開始時から電子の累積照射量が $4.2 \times 10^8 e^- / nm^2$ までの範囲で、結晶部の大きさに変化が見られないことがわかる。具体的には、図21中の(2)および(3)で示すように、電子の累積照射量によらず、nc-OSおよびCAAC-OSの結晶部の大きさは、それぞれ1.4nm程度および2.1nm程度であることがわかる。

20

#### 【0199】

このように、a-like OSは、電子照射によって結晶部の成長が見られる場合がある。一方、nc-OSおよびCAAC-OSは、電子照射による結晶部の成長がほとんど見られないことがわかる。即ち、a-like OSは、nc-OSおよびCAAC-OSと比べて、不安定な構造であることがわかる。

#### 【0200】

また、鬆を有するため、a-like OSは、nc-OSおよびCAAC-OSと比べて密度の低い構造である。具体的には、a-like OSの密度は、同じ組成の単結晶の密度の78.6%以上92.3%未満となる。また、nc-OSの密度およびCAAC-OSの密度は、同じ組成の単結晶の密度の92.3%以上100%未満となる。単結晶の密度の78%未満となる酸化物半導体は、成膜すること自体が困難である。

30

#### 【0201】

例えば、 $In : Ga : Zn = 1 : 1 : 1$  [原子数比]を満たす酸化物半導体において、菱面体晶構造を有する単結晶 $InGaZnO_4$ の密度は $6.357 g / cm^3$ となる。よって、例えば、 $In : Ga : Zn = 1 : 1 : 1$  [原子数比]を満たす酸化物半導体において、a-like OSの密度は $5.0 g / cm^3$ 以上 $5.9 g / cm^3$ 未満となる。また、例えば、 $In : Ga : Zn = 1 : 1 : 1$  [原子数比]を満たす酸化物半導体において、nc-OSの密度およびCAAC-OSの密度は $5.9 g / cm^3$ 以上 $6.3 g / cm^3$ 未満となる。

40

#### 【0202】

なお、同じ組成の単結晶が存在しない場合がある。その場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成における単結晶に相当する密度を見積もることができる。所望の組成の単結晶に相当する密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて見積もればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて見積もることが好ましい。

#### 【0203】

以上のように、酸化物半導体は、様々な構造をとり、それぞれが様々な特性を有する。なお、酸化物半導体は、例えば、非晶質酸化物半導体、a-like OS、nc-OS、

50

C A A C - O S のうち、二種以上を有する積層膜であってもよい。

【 0 2 0 4 】

(実施の形態 4 )

本実施の形態では、本発明の一態様のトランジスタを利用した半導体装置の構成の一例について図面を参照して説明する。

【 0 2 0 5 】

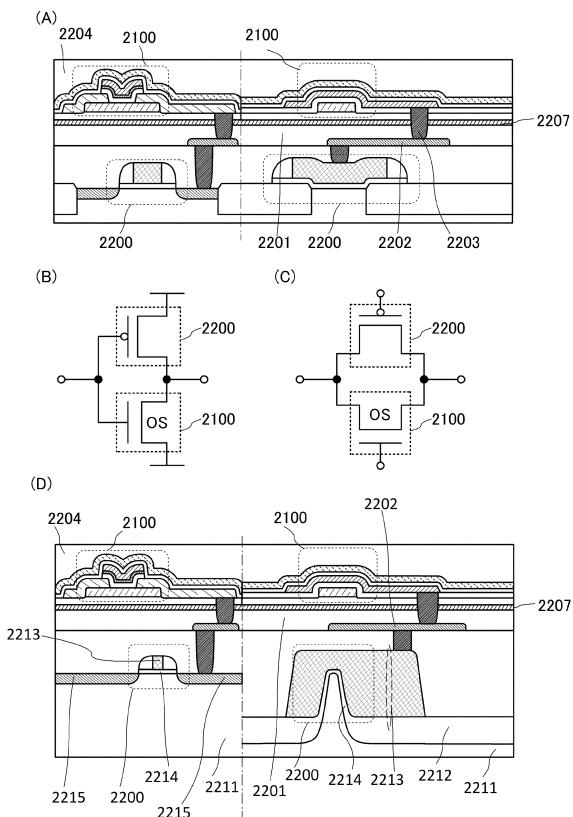

[ 断面構造 ]

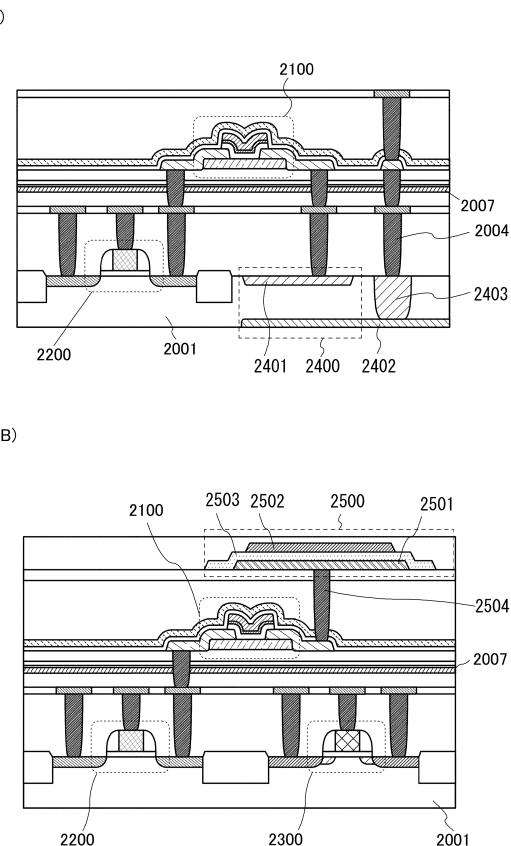

図 2 2 ( A ) に本発明の一態様の半導体装置の断面図を示す。図 2 2 ( A ) に示す半導体装置は、下部に第 1 の半導体材料を用いたトランジスタ 2 2 0 0 を有し、上部に第 2 の半導体材料を用いたトランジスタ 2 1 0 0 を有している。なお、一点鎖線より左側がトランジスタのチャネル長方向の断面、右側がチャネル幅方向の断面である。10

【 0 2 0 6 】

なお、トランジスタ 2 1 0 0 にバックゲートを設けた構成であってもよい。

【 0 2 0 7 】

第 1 の半導体材料と第 2 の半導体材料は異なるエネルギーギャップを持つ材料とすることが好ましい。例えば、第 1 の半導体材料を酸化物半導体以外の半導体材料（シリコン（歪シリコン含む）、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、ガリウムヒ素、アルミニウムガリウムヒ素、インジウムリン、窒化ガリウム、有機半導体など）とし、第 2 の半導体材料を酸化物半導体とすることができる。酸化物半導体以外の材料として単結晶シリコンなどを用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、オフ電流が低い。20

【 0 2 0 8 】

トランジスタ 2 2 0 0 は、n チャネル型のトランジスタまたは p チャネル型のトランジスタのいずれであってもよく、回路によって適切なトランジスタを用いればよい。また、酸化物半導体を用いた本発明の一態様のトランジスタを用いるほかは、用いる材料や構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

【 0 2 0 9 】

図 2 2 ( A ) に示す構成では、トランジスタ 2 2 0 0 の上部に、絶縁膜 2 2 0 1 、絶縁膜 2 2 0 7 を介してトランジスタ 2 1 0 0 が設けられている。また、トランジスタ 2 2 0 0 とトランジスタ 2 1 0 0 の間には、複数の配線 2 2 0 2 が設けられている。また、各種絶縁膜に埋め込まれた複数のプラグ 2 2 0 3 により、上層と下層にそれぞれ設けられた配線や電極が電気的に接続されている。また、トランジスタ 2 1 0 0 を覆う層間絶縁膜 2 2 0 4 が設けられている。30

【 0 2 1 0 】

このように、2 種類のトランジスタを積層することにより、回路の占有面積が低減され、より高密度に複数の回路を配置することができる。

【 0 2 1 1 】

ここで、下層に設けられるトランジスタ 2 2 0 0 にシリコン系半導体材料を用いた場合、トランジスタ 2 2 0 0 の半導体膜の近傍に設けられる絶縁膜中の水素はシリコンのダングリングボンドを終端し、トランジスタ 2 2 0 0 の信頼性を向上させる効果がある。一方、上層に設けられるトランジスタ 2 1 0 0 に酸化物半導体を用いた場合、トランジスタ 2 1 0 0 の半導体膜の近傍に設けられる絶縁膜中の水素は、酸化物半導体中にキャリアを生成する要因の一つとなるため、トランジスタ 2 1 0 0 の信頼性を低下させる要因となる場合がある。したがって、シリコン系半導体材料を用いたトランジスタ 2 2 0 0 の上層に酸化物半導体を用いたトランジスタ 2 1 0 0 を積層して設ける場合、これらの間に水素の拡散を防止する機能を有する絶縁膜 2 2 0 7 を設けることは特に効果的である。絶縁膜 2 2 0 7 により、下層に水素を閉じ込めてトランジスタ 2 2 0 0 の信頼性が向上することに加え、下層から上層に水素が拡散することが抑制されることでトランジスタ 2 1 0 0 の信頼性も同時に向上させることができる。40

【 0 2 1 2 】

絶縁膜 2207 としては、例えば、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム、イットリア安定化ジルコニア (YSZ) 等を用いることができる。

#### 【0213】

また、酸化物半導体膜を含んで構成されるトランジスタ 2100 を覆うように、トランジスタ 2100 上に水素の混入を防止する機能を有するロック膜を形成してもよい。ロック膜としては、絶縁膜 2207 と同様の材料を用いることができ、特に酸化アルミニウムを適用することが好ましい。酸化アルミニウム膜は、水素、水分などの不純物および酸素の双方に対して膜を透過させない遮断 (ブロッキング) 効果が高い。したがって、トランジスタ 2100 を覆うロック膜として酸化アルミニウム膜を用いることで、トランジスタ 2100 に含まれる酸化物半導体膜からの酸素の脱離を防止するとともに、酸化物半導体膜への水および水素の混入を防止することができる。10

#### 【0214】

なお、トランジスタ 2200 は、プレーナ型のトランジスタだけでなく、様々なタイプのトランジスタとすることができる。例えば、FIN (フィン) 型、TRI-GATE (トライゲート) 型などのトランジスタなどとすることができる。その場合の断面図の例を、図 22 (D) に示す。半導体基板 2211 の上に、絶縁膜 2212 が設けられている。半導体基板 2211 は、先端の細い凸部 (フィンともいう) を有する。なお、凸部の上には、絶縁膜が設けられていてもよい。その絶縁膜は、凸部を形成するときに、半導体基板 2211 がエッチングされないようにするためのマスクとして機能するものである。なお、凸部は、先端が細くなくてもよく、例えば、略直方体の凸部であってもよいし、先端が太い凸部であってもよい。半導体基板 2211 の凸部の上には、ゲート絶縁膜 2214 が設けられ、その上には、ゲート電極 2213 が設けられている。なお、本実施の形態では、ゲート電極 2213 は 1 層構造であるがこれに限らず、2 層以上の積層でもよい。半導体基板 2211 には、ソース領域およびドレイン領域 2215 が形成されている。なお、ここでは、半導体基板 2211 が、凸部を有する例を示したが、本発明の一態様に係る半導体装置は、これに限定されない。例えば、SOI 基板を加工して、凸部を有する半導体領域を形成しても構わない。20

#### 【0215】

##### [回路構成例]

上記構成において、トランジスタ 2100 やトランジスタ 2200 の電極の接続構成を異ならすことにより、様々な回路を構成することができる。以下では、本発明の一態様の半導体装置を用いることにより実現できる回路構成の例を説明する。30

#### 【0216】

図 22 (B) に示す回路図は、p チャネル型のトランジスタ 2200 と n チャネル型のトランジスタ 2100 を直列に接続し、且つそれぞれのゲートを接続した、いわゆる CMOS 回路の構成を示している。

#### 【0217】

また、図 22 (C) に示す回路図は、トランジスタ 2100 とトランジスタ 2200 のそれぞれのソースとドレインを接続した構成を示している。このような構成とすることで、いわゆるアナログスイッチとして機能させることができる。40

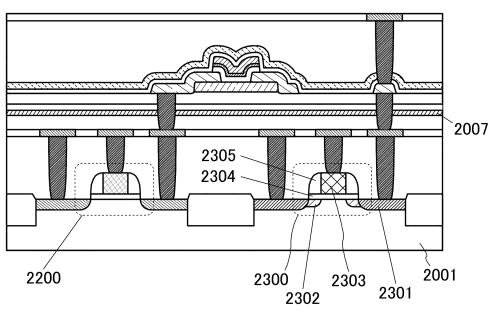

#### 【0218】

また、第 1 の半導体材料をチャネルにもつトランジスタ 2200 およびトランジスタ 2300 で、CMOS 回路を構成した場合の半導体装置の断面図を図 23 に示す。

#### 【0219】

トランジスタ 2300 は、ソース領域またはドレイン領域として機能する不純物領域 2301 と、ゲート電極 2303 と、ゲート絶縁膜 2304 と、側壁絶縁膜 2305 と、を有している。また、トランジスタ 2300 は、側壁絶縁膜 2305 の下に、LDD 領域として機能する不純物領域 2302 を設けてよい。図 23 のその他の構成要素については、図 22 (A) の説明を援用すればよい。50

## 【0220】

トランジスタ2200と、トランジスタ2300とは、互いに異なる極性のトランジスタであることが好ましい。例えば、トランジスタ2200がpチャネル型のトランジスタの場合、トランジスタ2300は、nチャネル型のトランジスタであることが好ましい。

## 【0221】

また、図22(A)および図23に示す半導体装置に、例えばフォトダイオードなどの光電変換素子を設けてもよい。

## 【0222】

フォトダイオードは、単結晶半導体や多結晶半導体を用いて形成してもよい。単結晶半導体や多結晶半導体を用いたフォトダイオードは、光の検出感度が高いため好ましい。

10

## 【0223】

図24(A)は、基板2001にフォトダイオード2400を設けた場合の断面図を示している。フォトダイオード2400は、アノードおよびカソードの一方としての機能を有する導電膜2401と、アノードおよびカソードの他方としての機能を有する導電膜2402と、導電膜2402とプラグ2004とを電気的に接続させる導電膜2403と、を有する。導電膜2401乃至導電膜2403は、基板2001に不純物を注入することで作製してもよい。

## 【0224】

図24(A)は、基板2001に対して縦方向に電流が流れるようにフォトダイオード2400を設けているが、基板2001に対して横方向に電流が流れるようにフォトダイオード2400を設けてもよい。

20

## 【0225】

図24(B)は、トランジスタ2100の上層にフォトダイオード2500を設けた場合の半導体装置の断面図である。フォトダイオード2500は、アノードおよびカソードの一方としての機能を有する導電膜2501と、アノードおよびカソードの他方としての機能を有する導電膜2502と、半導体層2503と、を有している。また、フォトダイオード2500は、プラグ2504を介して、トランジスタ2100と電気的に接続されている。

## 【0226】

図24(B)において、フォトダイオード2500をトランジスタ2100と同じ階層に設けてもよい。また、フォトダイオード2500をトランジスタ2200とトランジスタ2100の間の階層に設けてもよい。

30

## 【0227】

図24(A)および図24(B)のその他の構成要素に関する詳細は、図22(A)および図23の記載を援用すればよい。

## 【0228】

また、フォトダイオード2400またはフォトダイオード2500は、放射線を吸収して電荷を発生させることができ可能な材料を用いて形成してもよい。放射線を吸収して電荷を発生させることができ可能な材料としては、セレン、ヨウ化鉛、ヨウ化水銀、ガリウムヒ素、CdTe、CdZn等がある。

40

## 【0229】

例えば、フォトダイオード2400またはフォトダイオード2500にセレンを用いると、可視光や、紫外光に加えて、X線や、ガンマ線といった幅広い波長帯域にわたって光吸収係数を有する光電変換素子を実現できる。

## 【0230】

## &lt;記憶装置&gt;

本発明の一態様であるトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶装置)の一例を図25に示す。

## 【0231】

50

図25に示す半導体装置は、トランジスタ100を設けていない点で実施の形態1に示す記憶装置と相違している。この場合も上記と同様の動作により情報の書き込みおよび保持動作が可能である。

#### 【0232】

次に、図25に示す半導体装置の情報の読み出しについて説明する。トランジスタ200がオン状態となると、浮遊状態である配線3003と容量素子300とが導通し配線3003と容量素子300の間で電荷が再分配される。その結果、配線3003の電位が変化する。配線3003の電位の変化量は、容量素子300の電極の一方の電位（または容量素子300に蓄積された電荷）によって、異なる値をとる。

#### 【0233】

例えば、容量素子300の電極の一方の電位をV、容量素子300の容量をC、配線3003が有する容量成分をCB、電荷が再分配される前の配線3003の電位をVB0とすると、電荷が再分配された後の配線3003の電位は、 $(CB \times VB_0 + C \times V) / (CB + C)$ となる。したがって、メモリセルの状態として、容量素子300の電極の一方の電位がV1とV0 ( $V1 > V0$ ) の2状態をとるとすると、電位V1を保持している場合の配線3003の電位 ( $= (CB \times VB_0 + C \times V1) / (CB + C)$ ) は、電位V0を保持している場合の配線3003の電位 ( $= (CB \times VB_0 + C \times V0) / (CB + C)$ ) よりも高くなることがわかる。

#### 【0234】

そして、配線3003の電位を所定の電位と比較することで、情報を読み出すことができる。

#### 【0235】

この場合、メモリセルを駆動させるための駆動回路に上記第1の半導体材料が適用されたトランジスタを用い、トランジスタ200として第2の半導体材料が適用されたトランジスタを駆動回路上に積層して設ける構成とすればよい。

#### 【0236】

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合（ただし、電位は固定されていることが望ましい）であっても、長期にわたって記憶内容を保持することが可能である。

#### 【0237】

また、本実施の形態に示す半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁膜の劣化といった問題が全く生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。

#### 【0238】

本実施の形態に示す記憶装置は、例えば、CPU(Central Processing Unit)、DSP(Digital Signal Processor)、カスタムLSI、PLD(Programmable Logic Device)等のLSI、RF-ID(Radio Frequency Identification)にも応用可能である。

#### 【0239】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0240】

10

20

30

40

50

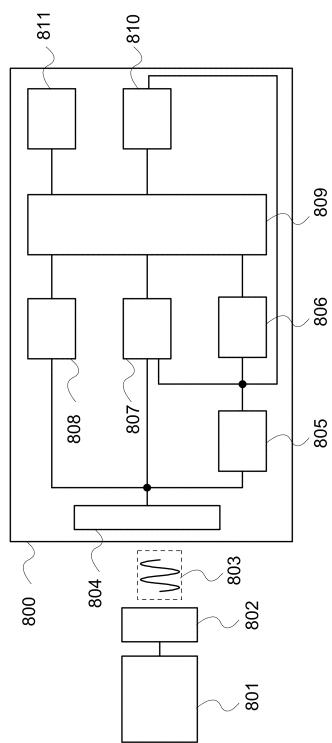

(実施の形態 5 )

本実施の形態では、上記実施の形態で例示したトランジスタ、または記憶装置を含む R F デバイスタグについて、図 2 6 を用いて説明する。

【 0 2 4 1 】

本実施の形態における R F デバイスタグは、内部に記憶回路を有し、記憶回路に必要な情報を記憶し、非接触手段、例えば無線通信を用いて外部と情報の授受を行うものである。このような特徴から、R F デバイスタグは、物品などの個体情報を読み取ることにより物品の識別を行う個体認証システムなどに用いることが可能である。なお、これらの用途に用いるためには極めて高い信頼性が要求される。

【 0 2 4 2 】

R F デバイスタグの構成について図 2 6 を用いて説明する。図 2 6 は、R F デバイスタグの構成例を示すブロック図である。

【 0 2 4 3 】

図 2 6 に示すように R F デバイスタグ 8 0 0 は、通信器 8 0 1 (質問器、リーダ / ライタなどともいう) に接続されたアンテナ 8 0 2 から送信される無線信号 8 0 3 を受信するアンテナ 8 0 4 を有する。また、R F デバイスタグ 8 0 0 は、整流回路 8 0 5 、定電圧回路 8 0 6 、復調回路 8 0 7 、変調回路 8 0 8 、論理回路 8 0 9 、記憶回路 8 1 0 、R O M 8 1 1 を有している。なお、復調回路 8 0 7 に含まれる整流作用を示すトランジスタに逆方向電流を十分に抑制することが可能な材料、例えば、酸化物半導体が用いられた構成としてもよい。これにより、逆方向電流に起因する整流作用の低下を抑制し、復調回路の出力が飽和することを防止できる。つまり、復調回路の入力に対する復調回路の出力を線形に近づけることができる。なお、データの伝送形式は、一対のコイルを対向配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の 3 つに大別される。本実施の形態に示す R F デバイスタグ 8 0 0 は、そのいずれの方式に用いることも可能である。

【 0 2 4 4 】

次に各回路の構成について説明する。アンテナ 8 0 4 は、通信器 8 0 1 に接続されたアンテナ 8 0 2 との間で無線信号 8 0 3 の送受信を行うためのものである。また、整流回路 8 0 5 は、アンテナ 8 0 4 で無線信号を受信することにより生成される入力交流信号を整流、例えば、半波 2 倍圧整流し、後段に設けられた容量素子により、整流された信号を平滑化することで入力電位を生成するための回路である。なお、整流回路 8 0 5 の入力側または出力側には、リミッタ回路を設けてもよい。リミッタ回路とは、入力交流信号の振幅が大きく、内部生成電圧が大きい場合に、ある電力以上の電力を後段の回路に入力しないよう制御するための回路である。

【 0 2 4 5 】

定電圧回路 8 0 6 は、入力電位から安定した電源電圧を生成し、各回路に供給するための回路である。なお、定電圧回路 8 0 6 は、内部にリセット信号生成回路を有していてもよい。リセット信号生成回路は、安定した電源電圧の立ち上がりを利用して、論理回路 8 0 9 のリセット信号を生成するための回路である。

【 0 2 4 6 】

復調回路 8 0 7 は、入力交流信号を包絡線検出することにより復調し、復調信号を生成するための回路である。また、変調回路 8 0 8 は、アンテナ 8 0 4 より出力するデータに応じて変調をおこなうための回路である。

【 0 2 4 7 】

論理回路 8 0 9 は復調信号を解析し、処理を行うための回路である。記憶回路 8 1 0 は、入力された情報を保持する回路であり、ロウデコーダ、カラムデコーダ、記憶領域などを有する。また、R O M 8 1 1 は、固有番号 ( I D ) などを格納し、処理に応じて出力をを行うための回路である。

【 0 2 4 8 】

なお、上述の各回路は、必要に応じて、適宜、取捨することができる。

10

20

30

40

50

**【0249】**

ここで、先の実施の形態で説明した記憶装置を、記憶回路810に用いることができる。本発明の一態様の記憶装置は、電源が遮断された状態であっても情報を保持できるため、RFデバイスタグに好適に用いることができる。さらに本発明の一態様の記憶装置は、データの書き込みに必要な電力（電圧）が従来の不揮発性メモリに比べて著しく小さいため、データの読み出し時と書き込み時の最大通信距離の差を生じさせないことも可能である。さらに、データの書き込み時に電力が不足し、誤動作または誤書き込みが生じることを抑制することができる。

**【0250】**

また、本発明の一態様の記憶装置は、不揮発性のメモリとして用いることが可能であるため、ROM811に適用することもできる。その場合には、生産者がROM811にデータを書き込むためのコマンドを別途用意し、ユーザーが自由に書き換えできないようにしておくことが好ましい。生産者が出荷前に固有番号を書込んだのちに製品を出荷することで、作製したRFデバイスタグすべてについて固有番号を付与するのではなく、出荷する良品にのみ固有番号を割り当てることが可能となり、出荷後の製品の固有番号が不連続になることがなく出荷後の製品に対応した顧客管理が容易となる。

**【0251】**

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

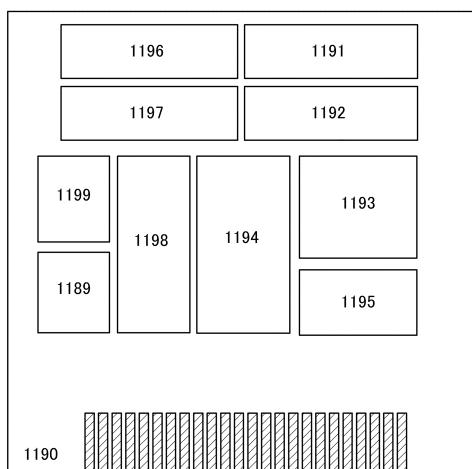

**【0252】****(実施の形態6)**

本実施の形態では、少なくとも実施の形態で説明したトランジスタを用いることができ、先の実施の形態で説明した記憶装置を含むCPUについて説明する。

**【0253】**

図27は、先の実施の形態で説明したトランジスタを少なくとも一部に用いたCPUの一例の構成を示すブロック図である。

**【0254】**

図27に示すCPUは、基板1190上に、ALU1191(ALU: Arithmetic logic unit、演算回路)、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース1198(Bus I/F)、書き換え可能なROM1199、及びROMインターフェース1189(ROM I/F)を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199及びROMインターフェース1189は、別チップに設けてもよい。もちろん、図27に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。例えば、図27に示すCPUまたは演算回路を含む構成を一つのコアとし、当該コアを複数含み、それぞれのコアが並列で動作するような構成としてもよい。また、CPUが内部演算回路やデータバスで扱えるビット数は、例えば8ビット、16ビット、32ビット、64ビットなどとすることができます。

**【0255】**

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

**【0256】**

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラ

10

20

30

40

50

ム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ 1197 は、レジスタ 1196 のアドレスを生成し、CPU の状態に応じてレジスタ 1196 の読み出しや書き込みを行なう。

#### 【0257】

また、タイミングコントローラ 1195 は、ALU1191、ALUコントローラ 1192、インストラクションデコーダ 1193、インタラプトコントローラ 1194、及びレジスタコントローラ 1197 の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ 1195 は、基準クロック信号 CLK1 を元に、内部クロック信号 CLK2 を生成する内部クロック生成部を備えており、内部クロック信号 CLK2 を上記各種回路に供給する。

10

#### 【0258】

図 27 に示す CPU では、レジスタ 1196 に、メモリセルが設けられている。レジスタ 1196 のメモリセルとして、先の実施の形態に示したトランジスタを用いることができる。

#### 【0259】

図 27 に示す CPU において、レジスタコントローラ 1197 は、ALU1191 からの指示に従い、レジスタ 1196 における保持動作の選択を行う。すなわち、レジスタ 1196 が有するメモリセルにおいて、フリップフロップによるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。フリップフロップによるデータの保持が選択されている場合、レジスタ 1196 内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ 1196 内のメモリセルへの電源電圧の供給を停止することができる。

20

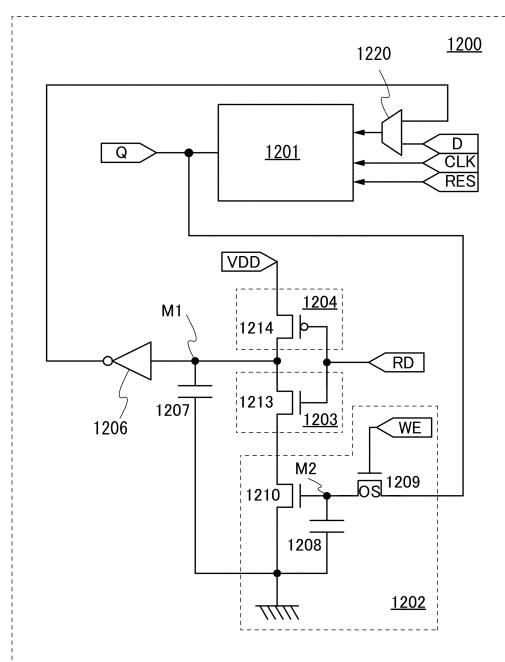

#### 【0260】

図 28 は、レジスタ 1196 として用いることのできる記憶素子の回路図の一例である。記憶素子 1200 は、電源遮断で記憶データが揮発する回路 1201 と、電源遮断で記憶データが揮発しない回路 1202 と、スイッチ 1203 と、スイッチ 1204 と、論理素子 1206 と、容量素子 1207 と、選択機能を有する回路 1220 と、を有する。回路 1202 は、容量素子 1208 と、トランジスタ 1209 と、トランジスタ 1210 と、を有する。なお、記憶素子 1200 は、必要に応じて、ダイオード、抵抗素子、インダクタなどの他の素子をさらに有していても良い。

30

#### 【0261】

ここで、回路 1202 には、先の実施の形態で説明した記憶装置を用いることができる。記憶素子 1200 への電源電圧の供給が停止した際、回路 1202 のトランジスタ 1209 のゲート電極には接地電位 (0V)、またはトランジスタ 1209 がオフする電位が入力され続ける構成とする。例えば、トランジスタ 1209 のゲート電極が抵抗等の負荷を介して接地される構成とする。

#### 【0262】

スイッチ 1203 は、一導電型（例えば、n チャネル型）のトランジスタ 1213 を用いて構成され、スイッチ 1204 は、一導電型とは逆の導電型（例えば、p チャネル型）のトランジスタ 1214 を用いて構成した例を示す。ここで、スイッチ 1203 の第 1 の端子はトランジスタ 1213 のソース電極とドレイン電極の一方に対応し、スイッチ 1203 の第 2 の端子はトランジスタ 1213 のソース電極とドレイン電極の他方に対応し、スイッチ 1203 はトランジスタ 1213 のゲート電極に入力される制御信号 RD によって、第 1 の端子と第 2 の端子の間の導通または非導通（つまり、トランジスタ 1213 のオン状態またはオフ状態）が選択される。スイッチ 1204 の第 1 の端子はトランジスタ 1214 のソース電極とドレイン電極の一方に対応し、スイッチ 1204 の第 2 の端子はトランジスタ 1214 のソース電極とドレイン電極の他方に対応し、スイッチ 1204 はトランジスタ 1214 のゲート電極に入力される制御信号 RD によって、第 1 の端子と第 2 の端子の間の導通または非導通（つまり、トランジスタ 1214 のオン状態またはオフ状態）が選択される。

40

50

態)が選択される。

**【0263】**

トランジスタ1209のソース電極とドレイン電極の一方は、容量素子1208の一対の電極のうちの一方、及びトランジスタ1210のゲート電極と電気的に接続される。ここで、接続部分をノードM2とする。トランジスタ1210のソース電極とドレイン電極の一方は、低電源電位を供給することのできる配線(例えばGND線)に電気的に接続され、他方は、スイッチ1203の第1の端子(トランジスタ1213のソース電極とドレイン電極の一方)と電気的に接続される。スイッチ1203の第2の端子(トランジスタ1213のソース電極とドレイン電極の他方)はスイッチ1204の第1の端子(トランジスタ1214のソース電極とドレイン電極の一方)と電気的に接続される。スイッチ1204の第2の端子(トランジスタ1214のソース電極とドレイン電極の他方)は電源電位VDDを供給することのできる配線と電気的に接続される。スイッチ1203の第2の端子(トランジスタ1213のソース電極とドレイン電極の他方)と、スイッチ1204の第1の端子(トランジスタ1214のソース電極とドレイン電極の一方)と、論理素子1206の入力端子と、容量素子1207の一対の電極のうちの一方と、は電気的に接続される。ここで、接続部分をノードM1とする。容量素子1207の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位(GND等)または高電源電位(VDD等)が入力される構成とすることができます。容量素子1207の一対の電極のうちの他方は、低電源電位を供給することのできる配線(例えばGND線)と電気的に接続される。容量素子1208の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位(GND等)または高電源電位(VDD等)が入力される構成とすることができます。容量素子1208の一対の電極のうちの他方は、低電源電位を供給することのできる配線(例えばGND線)と電気的に接続される。10

**【0264】**

なお、容量素子1207及び容量素子1208は、トランジスタや配線の寄生容量等を積極的に利用することによって省略することも可能である。

**【0265】**

トランジスタ1209の第1のゲート電極には、制御信号WEが入力される。スイッチ1203及びスイッチ1204は、制御信号WEとは異なる制御信号RDによって第1の端子と第2の端子の間の導通状態または非導通状態を選択され、一方のスイッチの第1の端子と第2の端子の間が導通状態のとき他方のスイッチの第1の端子と第2の端子の間は非導通状態となる。30

**【0266】**

トランジスタ1209のソース電極とドレイン電極の他方には、回路1201に保持されたデータに対応する信号が入力される。図28では、回路1201から出力された信号が、トランジスタ1209のソース電極とドレイン電極の他方に入力される例を示した。スイッチ1203の第2の端子(トランジスタ1213のソース電極とドレイン電極の他方)から出力される信号は、論理素子1206によってその論理値が反転された反転信号となり、回路1220を介して回路1201に入力される。40

**【0267】**

なお、図28では、スイッチ1203の第2の端子(トランジスタ1213のソース電極とドレイン電極の他方)から出力される信号は、論理素子1206及び回路1220を介して回路1201に入力する例を示したがこれに限定されない。スイッチ1203の第2の端子(トランジスタ1213のソース電極とドレイン電極の他方)から出力される信号が、論理値を反転させられることなく、回路1201に入力されてもよい。例えば、回路1201内に、入力端子から入力された信号の論理値が反転した信号が保持されるノードが存在する場合に、スイッチ1203の第2の端子(トランジスタ1213のソース電極とドレイン電極の他方)から出力される信号を当該ノードに入力することができます。

**【0268】**

50

20

40

50

また、図28において、記憶素子1200に用いられるトランジスタのうち、トランジスタ1209以外のトランジスタは、酸化物半導体以外の半導体でなる層または基板1190にチャネルが形成されるトランジスタとすることができる。例えば、シリコン層またはシリコン基板にチャネルが形成されるトランジスタとすることができる。また、記憶素子1200に用いられるトランジスタ全てを、チャネルが酸化物半導体膜で形成されるトランジスタとすることもできる。または、記憶素子1200は、トランジスタ1209以外にも、チャネルが酸化物半導体膜で形成されるトランジスタを含んでいてもよく、残りのトランジスタは酸化物半導体以外の半導体でなる層または基板1190にチャネルが形成されるトランジスタとすることもできる。

## 【0269】

10

図28における回路1201には、例えばフリップフロップ回路を用いることができる。また、論理素子1206としては、例えばインバータやクロックドインバータ等を用いることができる。

## 【0270】

本発明の一態様における半導体装置では、記憶素子1200に電源電圧が供給されない間は、回路1201に記憶されていたデータを、回路1202に設けられた容量素子1208によって保持することができる。

## 【0271】

また、酸化物半導体膜にチャネルが形成されるトランジスタはオフ電流が極めて小さい。例えば、酸化物半導体膜にチャネルが形成されるトランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく低い。そのため、当該トランジスタをトランジスタ1209として用いることによって、記憶素子1200に電源電圧が供給されない間も容量素子1208に保持された信号は長期間にわたり保たれる。こうして、記憶素子1200は電源電圧の供給が停止した間も記憶内容（データ）を保持することが可能である。

## 【0272】

20

また、スイッチ1203及びスイッチ1204を設けることによって、プリチャージ動作を行うことを特徴とする記憶素子であるため、電源電圧供給再開後に、回路1201が元のデータを保持しなおすまでの時間を短くすることができる。

## 【0273】

30

また、回路1202において、容量素子1208によって保持された信号はトランジスタ1210のゲート電極に入力される。そのため、記憶素子1200への電源電圧の供給が再開された後、容量素子1208によって保持された信号を、トランジスタ1210の状態（オン状態、またはオフ状態）に変換して、回路1202から読み出すことができる。それ故、容量素子1208に保持された信号に対応する電位が多少変動していても、元の信号を正確に読み出すことが可能である。

## 【0274】

40

このような記憶素子1200を、プロセッサが有するレジスタやキャッシュメモリなどの記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。よって、プロセッサ全体、もしくはプロセッサを構成する一つ、または複数の論理回路において、短い時間でも電源停止を行うため、消費電力を抑えることができる。

## 【0275】

本実施の形態では、記憶素子1200をCPUに用いる例として説明したが、記憶素子1200は、DSP(Digital Signal Processor)、カスタムLSI、PLD(Programmable Logic Device)等のLSI、RF-ID(Radio Frequency Identification)にも応用可能である。

## 【0276】

50

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0277】

(実施の形態7)

本実施の形態では、本発明の一態様に係る表示装置について、図29および図30を用いて説明する。

【0278】

表示装置に用いられる表示素子としては液晶素子（液晶表示素子ともいう。）、発光素子（発光表示素子ともいう。）などを用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL（Elec<sup>10</sup>roluminescence）、有機ELなどを含む。以下では、表示装置の一例としてEL素子を用いた表示装置（EL表示装置）および液晶素子を用いた表示装置（液晶表示装置）について説明する。

【0279】

なお、以下に示す表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むICなどを実装した状態にあるモジュールとを含む。

【0280】

また、以下に示す表示装置は画像表示デバイス、または光源（照明装置含む）を指す。また、コネクター、例えばFPC、TCPが取り付けられたモジュール、TCPの先にプリント配線板を有するモジュールまたは表示素子にCOG方式によりIC（集積回路）が直接実装されたモジュールも全て表示装置に含むものとする。<sup>20</sup>

【0281】

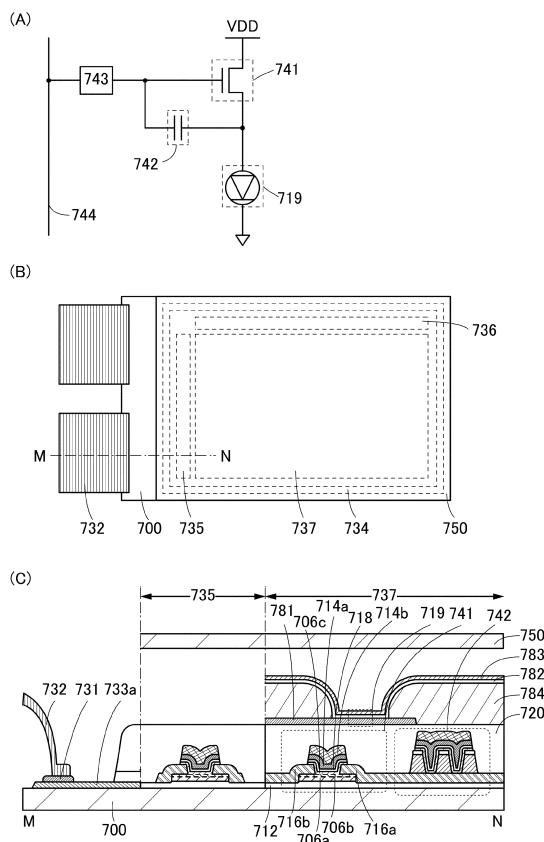

図29は、本発明の一態様に係るEL表示装置の一例である。図29(A)に、EL表示装置の画素の回路図を示す。図29(B)は、EL表示装置全体を示す上面図である。また、図29(C)は、図29(B)の一点鎖線M-Nの一部に対応するM-N断面である。

【0282】

図29(A)は、EL表示装置に用いられる画素の回路図の一例である。

【0283】

なお、本明細書等においては、能動素子（トランジスタ、ダイオードなど）、受動素子（容量素子、抵抗素子など）などが有するすべての端子について、その接続先を特定しなくても、当業者であれば、発明の一態様を構成することは可能な場合がある。つまり、接続先を特定しなくとも、発明の一態様が明確であるといえる。そして、接続先が特定された内容が、本明細書等に記載されている場合、接続先を特定しない発明の一態様が、本明細書等に記載されていると判断することが可能な場合がある。特に、端子の接続先として複数の箇所が想定される場合には、その端子の接続先を特定の箇所に限定する必要はない。したがって、能動素子（トランジスタ、ダイオードなど）、受動素子（容量素子、抵抗素子など）などが有する一部の端子についてのみ、その接続先を特定することによって、発明の一態様を構成することが可能な場合がある。<sup>30</sup>

【0284】

なお、本明細書等においては、ある回路について、少なくとも接続先を特定すれば、当業者であれば、発明を特定することが可能な場合がある。または、ある回路について、少なくとも機能を特定すれば、当業者であれば、発明を特定することが可能な場合がある。つまり、機能を特定すれば、発明の一態様が明確であるといえる。そして、機能が特定された発明の一態様が、本明細書等に記載されていると判断することが可能な場合がある。したがって、ある回路について、機能を特定しなくとも、接続先を特定すれば、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。または、ある回路について、接続先を特定しなくても、機能を特定すれば、発明の一態様として開示されているものであり、発明の一態様を構成することが可能である。<sup>40</sup>

【0285】

図29(A)に示すEL表示装置は、スイッチ素子743と、トランジスタ741と、容量素子742と、発光素子719と、を有する。

#### 【0286】

なお、図29(A)などは、回路構成の一例であるため、さらに、トランジスタを追加することが可能である。逆に、図29(A)の各ノードにおいて、トランジスタ、スイッチ、受動素子などを追加しないようにすることも可能である。

#### 【0287】

トランジスタ741のゲート電極はスイッチ素子743の第1の端子および容量素子742の一方の電極と電気的に接続される。トランジスタ741のソース電極は容量素子742の他方の電極と電気的に接続され、発光素子719の一方の電極と電気的に接続される。トランジスタ741のドレイン電極は電源電位VDDが与えられる。スイッチ素子743の第2の端子は信号線744と電気的に接続される。発光素子719の他方の電極は定電位が与えられる。なお、定電位は接地電位GNDまたはそれより小さい電位とする。

10

#### 【0288】

スイッチ素子743としては、トランジスタを用いると好ましい。トランジスタを用いることで、画素の面積を小さくでき、解像度の高いEL表示装置とすることができます。また、スイッチ素子743として、トランジスタ741と同一工程を経て作製されたトランジスタを用いると、EL表示装置の生産性を高めることができる。なお、トランジスタ741または/およびスイッチ素子743としては、例えば、上述したトランジスタを適用することができる。

20

#### 【0289】

図29(B)は、EL表示装置の上面図である。EL表示装置は、基板700と、基板750と、シール材734と、駆動回路735と、駆動回路736と、画素737と、FPC732と、を有する。シール材734は、画素737、駆動回路735および駆動回路736を囲むように基板700と基板750との間に配置される。なお、駆動回路735または/および駆動回路736をシール材734の外側に配置しても構わない。

#### 【0290】

図29(C)は、図29(B)の一点鎖線M-Nの一部に対応するEL表示装置の断面図である。

30

#### 【0291】

図29(C)には、トランジスタ741として、基板700上の絶縁体712と、絶縁体712上に半導体706a、および半導体706bと、半導体706aおよび半導体706bと接する導電体716aおよび導電体716bと、半導体706b上、導電体716a上および導電体716b上の半導体706cおよび絶縁体718と、絶縁体718上にあり半導体706cと重なる導電体714aおよび導電体714bと、を有する構造を示す。なお、トランジスタ741の構造は一例であり、図29(C)に示す構造と異なる構造であっても構わない。

#### 【0292】

したがって、図29(C)に示すトランジスタ741において、導電体714aおよび導電体714bはゲート電極としての機能を有し、絶縁体718はゲート絶縁体としての機能を有し、導電体716aはソース電極としての機能を有し、導電体716bはドレイン電極としての機能を有する。

40

#### 【0293】

図29(C)には、容量素子742として、上記実施の形態で示した容量素子300と同様の構造を有する容量素子を用いることができる。上記構成の容量素子を用いることにより、立体的な容量素子を形成することができる。これにより、容量素子の投影面積当たりの容量を増加させることができるために、EL表示装置の小面積化、高集積化、微細化が可能となる。

#### 【0294】

また、容量素子742は、トランジスタ741と共に通する膜を用いて作製することができ

50

る。また、導電体 716a および容量素子 742 の第 1 の電極を同種の導電体とすると好ましい。その場合、導電体 716a および容量素子 742 の第 1 の電極は、同一工程を経て形成することができる。また、導電体 714a および導電体 714b を、容量素子 742 の第 2 の電極と同種の導電体とすると好ましい。その場合、導電体 714a および導電体 714b と、容量素子 742 の第 2 の電極は、同一工程を経て形成することができる。

#### 【0295】

図 29 (C) に示す容量素子 742 は、占有面積当たりの容量が大きい容量素子である。したがって、図 29 (C) は表示品位の高い E L 表示装置である。

#### 【0296】

トランジスタ 741 および容量素子 742 上には、絶縁体 720 が配置される。ここで、絶縁体 720 は、トランジスタ 741 のソース電極として機能する導電体 716a に達する開口部を有してもよい。絶縁体 720 上には、導電体 781 が配置される。導電体 781 は、絶縁体 720 の開口部を介してトランジスタ 741 と電気的に接続してもよい。

#### 【0297】

導電体 781 上には、導電体 781 に達する開口部を有する隔壁 784 が配置される。隔壁 784 上には、隔壁 784 の開口部で導電体 781 と接する発光層 782 が配置される。発光層 782 上には、導電体 783 が配置される。導電体 781、発光層 782 および導電体 783 の重なる領域が、発光素子 719 となる。

#### 【0298】

ここまででは、E L 表示装置の例について説明した。次に、液晶表示装置の例について説明する。

#### 【0299】

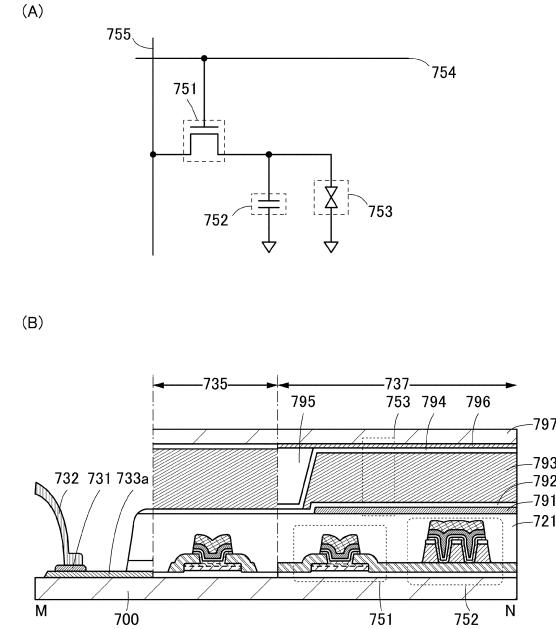

図 30 (A) は、液晶表示装置の画素の構成例を示す回路図である。図 30 に示す画素は、トランジスタ 751 と、容量素子 752 と、一対の電極間に液晶の充填された素子（液晶素子）753 とを有する。

#### 【0300】

トランジスタ 751 では、ソース電極、ドレイン電極の一方が信号線 755 に電気的に接続され、ゲート電極が走査線 754 に電気的に接続されている。

#### 【0301】

容量素子 752 では、一方の電極がトランジスタ 751 のソース電極、ドレイン電極の他方に電気的に接続され、他方の電極が共通電位を供給する配線に電気的に接続されている。

#### 【0302】

液晶素子 753 では、一方の電極がトランジスタ 751 のソース電極、ドレイン電極の他方に電気的に接続され、他方の電極が共通電位を供給する配線に電気的に接続されている。なお、上述した容量素子 752 の他方の電極が電気的に接続する配線に与えられる共通電位と、液晶素子 753 の他方の電極に与えられる共通電位とが異なる電位であってもよい。

#### 【0303】

なお、液晶表示装置も、上面図は E L 表示装置と同様として説明する。図 29 (B) の一点鎖線 M - N に対応する液晶表示装置の断面図を図 30 (B) に示す。図 30 (B) において、FPC 732 は、端子 731 を介して配線 733a と接続される。なお、配線 733a は、トランジスタ 751 を構成する導電体または半導体のいずれかと同種の導電体または半導体を用いてもよい。

#### 【0304】

トランジスタ 751 は、トランジスタ 741 についての記載を参照する。また、容量素子 752 は、容量素子 742 についての記載を参照する。なお、図 30 (B) には、図 29 (C) の容量素子 742 に対応した容量素子 752 の構造を示したが、これに限定されない。

#### 【0305】

10

20

30

40

50

なお、トランジスタ751の半導体に酸化物半導体を用いた場合、極めてオフ電流の小さいトランジスタとすることができます。したがって、容量素子752に保持された電荷がリークしにくく、長期間に渡って液晶素子753に印加される電圧を維持することができる。そのため、動きの少ない動画や静止画の表示の際に、トランジスタ751をオフ状態とすることで、トランジスタ751の動作のための電力が不要となり、消費電力の小さい液晶表示装置とすることができます。また、容量素子752の占有面積を小さくできるため、開口率の高い液晶表示装置、または高精細化した液晶表示装置を提供することができる。

#### 【0306】

トランジスタ751および容量素子752上には、絶縁体721が配置される。ここで、絶縁体721は、トランジスタ751に達する開口部を有する。絶縁体721上には、導電体791が配置される。導電体791は、絶縁体721の開口部を介してトランジスタ751と電気的に接続する。10

#### 【0307】

導電体791上には、配向膜として機能する絶縁体792が配置される。絶縁体792上には、液晶層793が配置される。液晶層793上には、配向膜として機能する絶縁体794が配置される。絶縁体794上には、スペーサ795が配置される。スペーサ795および絶縁体794上には、導電体796が配置される。導電体796上には、基板797が配置される。

#### 【0308】

上述した構造を有することで、占有面積の小さい容量素子を有する表示装置を提供することができる、または、表示品位の高い表示装置を提供することができる。または、高精細の表示装置を提供することができる。20

#### 【0309】

例えば、本明細書等において、表示素子、表示素子を有する装置である表示装置、発光素子、および発光素子を有する装置である発光装置は、様々な形態を用いること、または様々な素子を有することができる。表示素子、表示装置、発光素子または発光装置は、例えば、白色、赤色、緑色または青色などの発光ダイオード(LED: Light Emitter Diode)、トランジスタ(電流に応じて発光するトランジスタ)、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ(GLV)、プラズマディスプレイ(PDP)、MEMS(マイクロ・エレクトロ・メカニカル・システム)を用いた表示素子、デジタルマイクロミラーデバイス(DMD)、DMS(デジタル・マイクロ・シャッター)、IMOD(インターフェアレンス・モジュレーション)素子、シャッター方式のMEMS表示素子、光干渉方式のMEMS表示素子、エレクトロウェッティング素子、圧電セラミックディスプレイ、カーボンナノチューブを用いた表示素子などの少なくとも一つを有している。これらの他にも、電気的または磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有していても良い。30

#### 【0310】

EL素子を用いた表示装置の一例としては、ELディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッションディスプレイ(FED)またはSED方式平面型ディスプレイ(SED: Surface-conduction Electron-emitter Display)などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ(透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ)などがある。電子インク、電子粉流体(登録商標)、または電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。なお、半透過型液晶ディスプレイや反射型液晶ディスプレイを実現する場合には、画素電極の一部、または、全部が、反射電極としての機能を有するようにすればよい。例えば、画素電極の一部または全部が、アルミニウム、銀、などを有するようにすればよい。さらに、その場合、反射電極の下に、SRAMなどの記憶回路を設けることも可能である。これにより、さらに、消費電力を低減することができる。4050

## 【0311】

なお、LEDを用いる場合、LEDの電極や窒化物半導体の下に、グラフェンやグラファイトを配置してもよい。グラフェンやグラファイトは、複数の層を重ねて、多層膜としてもよい。このように、グラフェンやグラファイトを設けることにより、その上に、窒化物半導体、例えば、結晶を有するn型GaN半導体などを容易に成膜することができる。さらに、その上に、結晶を有するp型GaN半導体などを設けて、LEDを構成することができる。なお、グラフェンやグラファイトと、結晶を有するn型GaN半導体との間に、AlN層を設けてもよい。なお、LEDが有するGaN半導体は、MOCVDで成膜してもよい。ただし、グラフェンを設けることにより、LEDが有するGaN半導体は、スペッタリング法で成膜することも可能である。

10

## 【0312】

## (実施の形態8)

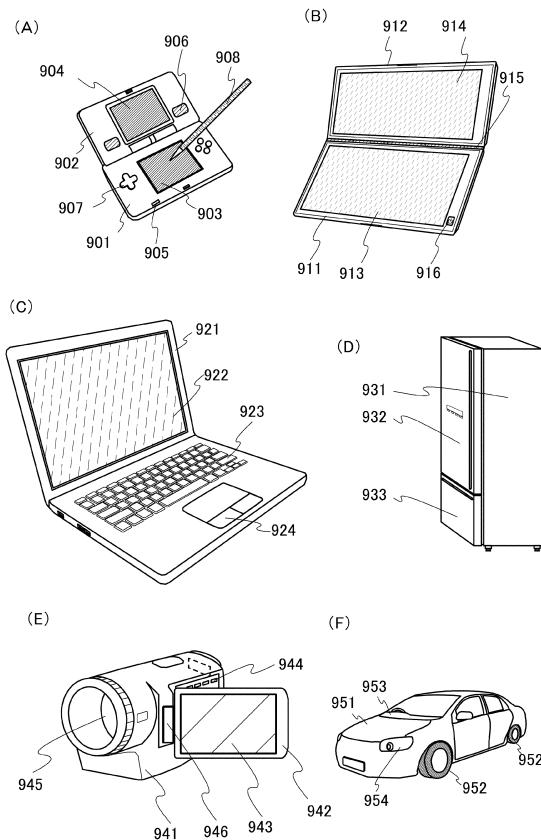

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯データ端末、電子書籍端末、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンタ、プリント複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図31に示す。

20

## 【0313】

図31(A)は携帯型ゲーム機であり、筐体901、筐体902、表示部903、表示部904、マイクロフォン905、スピーカー906、操作キー907、スタイルス908等を有する。なお、図31(A)に示した携帯型ゲーム機は、2つの表示部903と表示部904とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

## 【0314】

図31(B)は携帯データ端末であり、第1筐体911、第2筐体912、第1表示部913、第2表示部914、接続部915、操作キー916等を有する。第1表示部913は第1筐体911に設けられており、第2表示部914は第2筐体912に設けられている。そして、第1筐体911と第2筐体912とは、接続部915により接続されており、第1筐体911と第2筐体912の間の角度は、接続部915により変更が可能である。第1表示部913における映像を、接続部915における第1筐体911と第2筐体912との間の角度に従って、切り替える構成としても良い。また、第1表示部913及び第2表示部914の少なくとも一方に、位置入力装置としての機能が付加された表示装置を用いるようにしても良い。なお、位置入力装置としての機能は、表示装置にタッチパネルを設けることで付加することができる。或いは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を表示装置の画素部に設けることでも、付加することができる。

30

## 【0315】

図31(C)はノート型パーソナルコンピュータであり、筐体921、表示部922、キーボード923、ポインティングデバイス924等を有する。

40

## 【0316】

図31(D)は電気冷凍冷蔵庫であり、筐体931、冷蔵室用扉932、冷凍室用扉933等を有する。

## 【0317】

図31(E)はビデオカメラであり、第1筐体941、第2筐体942、表示部943、操作キー944、レンズ945、接続部946等を有する。操作キー944及びレンズ9

50

45は第1筐体941に設けられており、表示部943は第2筐体942に設けられている。そして、第1筐体941と第2筐体942とは、接続部946により接続されており、第1筐体941と第2筐体942の間の角度は、接続部946により変更が可能である。表示部943における映像を、接続部946における第1筐体941と第2筐体942との間の角度に従って切り替える構成としても良い。

#### 【0318】

図31(F)は乗用車であり、車体951、車輪952、ダッシュボード953、ライト954等を有する。

#### 【0319】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。 10

#### 【0320】

##### (実施の形態9)

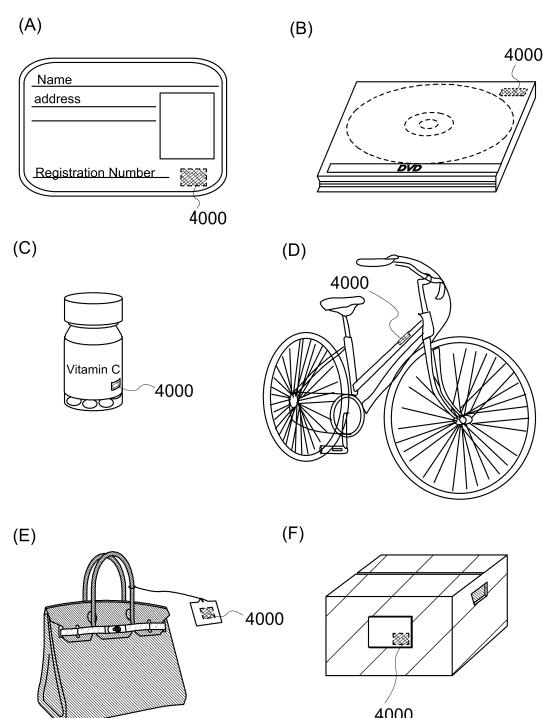

本実施の形態では、本発明の一態様に係るRFデバイスタグの使用例について図32を用いながら説明する。RFデバイスタグの用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類(運転免許証や住民票等、図32(A)参照)、記録媒体(DVDやビデオテープ等、図32(B)参照)、包装用容器類(包装紙やボトル等、図32(C)参照)、乗り物類(自転車等、図32(D)参照)、身の回り品(鞄や眼鏡等)、食品類、植物類、動物類、人体、衣類、生活用品類、薬品や薬剤を含む医療品、または電子機器(液晶表示装置、EL表示装置、テレビジョン装置、または携帯電話)等の物品、若しくは各物品に取り付ける荷札(図32(E)、図32(F)参照)等に設けて使用することができる。 20

#### 【0321】

本発明の一態様に係るRFデバイスタグ4000は、表面に貼る、または埋め込むことにより、物品に固定される。例えば、本であれば紙に埋め込み、有機樹脂からなるパッケージであれば当該有機樹脂の内部に埋め込み、各物品に固定される。本発明の一態様に係るRFデバイスタグ4000は、小型、薄型、軽量を実現するため、物品に固定した後もその物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、または証書類等に本発明の一態様に係るRFデバイスタグ4000を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、または電子機器等に本発明の一態様に係るRFデバイスタグ4000を取り付けることにより、検品システム等のシステムの効率化を図ることができる。また、乗り物類であっても、本発明の一態様に係るRFデバイスタグ4000を取り付けることにより、盗難などに対するセキュリティ性を高めることができる。 30

#### 【0322】

以上のように、本発明の一態様に係わるRFデバイスタグを本実施の形態に挙げた各用途に用いることにより、情報の書き込みや読み出しを含む動作電力を低減できるため、最大通信距離を長くとることが可能となる。また、電力が遮断された状態であっても情報を極めて長い期間保持可能であるため、書き込みや読み出しの頻度が低い用途にも好適に用いることができる。 40

#### 【0323】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【符号の説明】

#### 【0324】

- 100 トランジスタ

- 101 半導体基板

- 102 半導体膜

- 103a 低抵抗層

10

20

30

40

50

|         |          |    |

|---------|----------|----|

| 1 0 3 b | 低抵抗層     |    |

| 1 0 4   | ゲート絶縁膜   |    |

| 1 0 5   | ゲート電極    |    |

| 1 0 5 a | ゲート電極    |    |

| 1 0 5 b | ゲート電極    |    |

| 1 1 0   | 配線       |    |

| 1 1 1 a | 配線       |    |

| 1 1 1 b | 配線       |    |

| 1 2 1   | 絶縁膜      | 10 |

| 1 2 2   | 絶縁膜      |    |

| 2 0 0   | トランジスタ   |    |

| 2 0 1   | 絶縁膜      |    |

| 2 0 2   | 絶縁膜      |    |

| 2 0 3 a | 酸化物半導体層  |    |

| 2 0 3 b | 酸化物半導体層  |    |

| 2 0 3 c | 酸化物半導体層  |    |

| 2 0 4 a | 電極       |    |

| 2 0 4 b | 電極       |    |

| 2 0 5   | ゲート絶縁膜   |    |

| 2 0 6   | ゲート電極    | 20 |

| 2 0 6 a | 導電体      |    |

| 2 0 6 b | 導電体      |    |

| 2 0 7   | 絶縁膜      |    |

| 2 0 8   | 絶縁膜      |    |

| 2 0 9 a | 低抵抗領域    |    |

| 2 0 9 b | 低抵抗領域    |    |

| 2 5 0   | 配線       |    |

| 3 0 0   | 容量素子     |    |

| 3 0 1   | 絶縁膜      |    |

| 3 0 2   | 電極       | 30 |

| 3 0 2 a | 導電層      |    |

| 3 0 2 A | 導電膜      |    |

| 3 0 2 b | 導電層      |    |

| 3 0 2 B | 導電膜      |    |

| 3 0 2 C | 導電膜      |    |

| 3 0 2 c | 導電膜      |    |

| 3 0 3   | バリア層     |    |

| 3 0 3 A | バリア膜     |    |

| 3 0 3 B | バリア層     |    |

| 3 0 4   | 絶縁体      | 40 |

| 3 0 5   | 電極       |    |

| 3 0 5 A | 導電膜      |    |

| 3 0 5 a | 導電体      |    |

| 3 0 5 b | 導電体      |    |

| 3 0 6   | 絶縁膜      |    |

| 3 0 7   | 配線       |    |

| 3 0 8   | 配線       |    |

| 3 1 0   | コンタクトホール |    |

| 3 1 9   | レジストマスク  |    |

| 3 2 0   | レジストマスク  | 50 |

|         |            |    |

|---------|------------|----|

| 3 2 5   | レジストマスク    |    |

| 3 3 0   | レジストマスク    |    |

| 3 4 0   | 中間層        |    |

| 3 5 0   | 配線         |    |

| 7 0 0   | 基板         |    |

| 7 0 6 a | 半導体        | 10 |

| 7 0 6 b | 半導体        |    |

| 7 0 6 c | 半導体        |    |

| 7 1 2   | 絶縁体        |    |

| 7 1 4 a | 導電体        |    |

| 7 1 4 b | 導電体        |    |

| 7 1 6 a | 導電体        |    |

| 7 1 6 b | 導電体        |    |

| 7 1 8   | 絶縁体        |    |

| 7 1 9   | 発光素子       |    |

| 7 2 0   | 絶縁体        |    |

| 7 2 1   | 絶縁体        |    |

| 7 3 1   | 端子         |    |

| 7 3 2   | F P C      | 20 |

| 7 3 3 a | 配線         |    |

| 7 3 4   | シール材       |    |

| 7 3 5   | 駆動回路       |    |

| 7 3 6   | 駆動回路       |    |

| 7 3 7   | 画素         |    |

| 7 4 1   | トランジスタ     |    |

| 7 4 2   | 容量素子       |    |

| 7 4 3   | スイッチ素子     |    |

| 7 4 4   | 信号線        |    |

| 7 5 0   | 基板         |    |

| 7 5 1   | トランジスタ     | 30 |

| 7 5 2   | 容量素子       |    |

| 7 5 3   | 液晶素子       |    |

| 7 5 4   | 走査線        |    |

| 7 5 5   | 信号線        |    |

| 7 8 1   | 導電体        |    |

| 7 8 2   | 発光層        |    |

| 7 8 3   | 導電体        |    |

| 7 8 4   | 隔壁         |    |

| 7 9 1   | 導電体        |    |

| 7 9 2   | 絶縁体        | 40 |

| 7 9 3   | 液晶層        |    |

| 7 9 4   | 絶縁体        |    |

| 7 9 5   | スペーサ       |    |

| 7 9 6   | 導電体        |    |

| 7 9 7   | 基板         |    |

| 8 0 0   | R F デバイステグ |    |

| 8 0 1   | 通信器        |    |

| 8 0 2   | アンテナ       |    |

| 8 0 3   | 無線信号       |    |

| 8 0 4   | アンテナ       | 50 |

|         |                |    |

|---------|----------------|----|

| 8 0 5   | 整流回路           |    |

| 8 0 6   | 定電圧回路          |    |

| 8 0 7   | 復調回路           |    |

| 8 0 8   | 変調回路           |    |

| 8 0 9   | 論理回路           |    |

| 8 1 0   | 記憶回路           |    |

| 8 1 1   | R O M          |    |

| 9 0 1   | 筐体             |    |

| 9 0 2   | 筐体             |    |

| 9 0 3   | 表示部            | 10 |

| 9 0 4   | 表示部            |    |

| 9 0 5   | マイクロフォン        |    |

| 9 0 6   | スピーカー          |    |

| 9 0 7   | 操作キー           |    |

| 9 0 8   | スタイラス          |    |

| 9 1 1   | 筐体             |    |

| 9 1 2   | 筐体             |    |

| 9 1 3   | 表示部            |    |

| 9 1 4   | 表示部            |    |

| 9 1 5   | 接続部            | 20 |

| 9 1 6   | 操作キー           |    |

| 9 2 1   | 筐体             |    |

| 9 2 2   | 表示部            |    |

| 9 2 3   | キー ボード         |    |

| 9 2 4   | ポインティングデバイス    |    |

| 9 3 1   | 筐体             |    |

| 9 3 2   | 冷蔵室用扉          |    |

| 9 3 3   | 冷凍室用扉          |    |

| 9 4 1   | 筐体             |    |

| 9 4 2   | 筐体             | 30 |

| 9 4 3   | 表示部            |    |

| 9 4 4   | 操作キー           |    |

| 9 4 5   | レンズ            |    |

| 9 4 6   | 接続部            |    |

| 9 5 1   | 車体             |    |

| 9 5 2   | 車輪             |    |

| 9 5 3   | ダッシュボード        |    |

| 9 5 4   | ライト            |    |

| 1 1 8 9 | R O M インターフェース |    |

| 1 1 9 0 | 基板             | 40 |

| 1 1 9 1 | A L U          |    |

| 1 1 9 2 | A L U コントローラ   |    |

| 1 1 9 3 | インストラクションデコーダ  |    |

| 1 1 9 4 | インタラプトコントローラ   |    |

| 1 1 9 5 | タイミングコントローラ    |    |

| 1 1 9 6 | レジスタ           |    |

| 1 1 9 7 | レジスタコントローラ     |    |

| 1 1 9 8 | バスインターフェース     |    |

| 1 1 9 9 | R O M          |    |

| 1 2 0 0 | 記憶素子           | 50 |

|         |                |    |

|---------|----------------|----|

| 1 2 0 1 | 回路             |    |

| 1 2 0 2 | 回路             |    |

| 1 2 0 3 | スイッチ           |    |

| 1 2 0 4 | スイッチ           |    |

| 1 2 0 6 | 論理素子           |    |

| 1 2 0 7 | 容量素子           |    |

| 1 2 0 8 | 容量素子           |    |

| 1 2 0 9 | トランジスタ         |    |

| 1 2 1 0 | トランジスタ         |    |

| 1 2 1 3 | トランジスタ         | 10 |

| 1 2 1 4 | トランジスタ         |    |

| 1 2 2 0 | 回路             |    |

| 2 0 0 1 | 基板             |    |

| 2 0 0 4 | プラグ            |    |

| 2 1 0 0 | トランジスタ         |    |

| 2 2 0 0 | トランジスタ         |    |

| 2 2 0 1 | 絶縁膜            |    |

| 2 2 0 2 | 配線             |    |

| 2 2 0 3 | プラグ            |    |

| 2 2 0 4 | 層間絶縁膜          | 20 |

| 2 2 0 7 | 絶縁膜            |    |

| 2 2 1 1 | 半導体基板          |    |

| 2 2 1 2 | 絶縁膜            |    |

| 2 2 1 3 | ゲート電極          |    |

| 2 2 1 4 | ゲート絶縁膜         |    |

| 2 2 1 5 | ソース領域およびドレイン領域 |    |

| 2 3 0 0 | トランジスタ         |    |

| 2 3 0 1 | 不純物領域          |    |

| 2 3 0 2 | 不純物領域          |    |

| 2 3 0 3 | ゲート電極          | 30 |

| 2 3 0 4 | ゲート絶縁膜         |    |

| 2 3 0 5 | 側壁絶縁膜          |    |

| 2 4 0 0 | フォトダイオード       |    |

| 2 4 0 1 | 導電膜            |    |

| 2 4 0 2 | 導電膜            |    |

| 2 4 0 3 | 導電膜            |    |

| 2 5 0 0 | フォトダイオード       |    |

| 2 5 0 1 | 導電膜            |    |

| 2 5 0 2 | 導電膜            |    |

| 2 5 0 3 | 半導体層           | 40 |

| 2 5 0 4 | プラグ            |    |

| 3 0 0 1 | 配線             |    |

| 3 0 0 2 | 配線             |    |

| 3 0 0 3 | 配線             |    |

| 3 0 0 4 | 配線             |    |

| 3 0 0 5 | 配線             |    |

| 4 0 0 0 | R F デバイスタグ     |    |

| 5 1 0 0 | 結晶部            |    |

| 5 1 2 0 | 基板             |    |

| 5 1 6 1 | 領域             | 50 |

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【 図 7 】

(B)

【 义 8 】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

---

フロントページの続き

(51)Int.Cl.

F I

|        |         |           |        |        |         |

|--------|---------|-----------|--------|--------|---------|

| H 01 L | 27/108  | (2006.01) | H 01 L | 27/06  | 1 0 2 A |