(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6131195号

(P6131195)

(45) 発行日 平成29年5月17日(2017.5.17)

(24) 登録日 平成29年4月21日(2017.4.21)

|               |           |        |       |         |

|---------------|-----------|--------|-------|---------|

| (51) Int.Cl.  | F 1       |        |       |         |

| HO 1 L 25/07  | (2006.01) | HO 1 L | 25/04 | C       |

| HO 1 L 25/18  | (2006.01) | HO 1 L | 21/60 | 3 2 1 E |

| HO 1 L 21/60  | (2006.01) | HO 1 L | 25/08 | E       |

| HO 1 L 25/065 | (2006.01) | HO 1 L | 23/48 | H       |

| HO 1 L 23/48  | (2006.01) | HO 2 M | 3/155 | Y       |

請求項の数 19 (全 15 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-553496 (P2013-553496)  |

| (86) (22) 出願日 | 平成24年2月7日(2012.2.7)           |

| (65) 公表番号     | 特表2014-511027 (P2014-511027A) |

| (43) 公表日      | 平成26年5月1日(2014.5.1)           |

| (86) 國際出願番号   | PCT/US2012/024171             |

| (87) 國際公開番号   | W02012/109265                 |

| (87) 國際公開日    | 平成24年8月16日(2012.8.16)         |

| 審査請求日         | 平成27年2月3日(2015.2.3)           |

| (31) 優先権主張番号  | 13/021,969                    |

| (32) 優先日      | 平成23年2月7日(2011.2.7)           |

| (33) 優先権主張国   | 米国(US)                        |

|               |                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者     | 390020248<br>日本テキサス・インスツルメンツ株式会社<br>東京都新宿区西新宿六丁目24番1号                                                                 |

| (73) 特許権者     | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>-5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655<br>474 |

| (74) 上記1名の代理人 | 100098497<br>弁理士 片寄 恒三                                                                                                |

最終頁に続く

(54) 【発明の名称】スイッチノードリングが低減された3次元電源モジュール

## (57) 【特許請求の範囲】

## 【請求項1】

電気的入力端子と接地端子である少なくとも1つのリードとを有する電源モジュールであって、

ダイパッドと複数のリードとを含むリードフレームであって、前記ダイパッドが前記電気的入力端子であり、前記複数のリードの少なくとも1つが接地端子である、前記リードフレームと、

制御FETダイを含む同期降圧コンバータと、

前記制御FETダイの頂部上にスタックされる同期FETダイと、

を含み、

前記制御FETダイが、第1の物理的領域と、第1の能動領域と、前記制御FETダイの第1の面上の第1のソース端子と、前記制御FETダイの前記第1の面とは反対側の第2の面上の第1のドレイン端子とを有し、

前記同期FETダイが、前記同期FETダイの第1の面上の第2のソース端子と、前記同期FETダイの前記第1の面とは反対側の第2の面上の第2のドレイン端子とを有し、

前記制御FETダイの前記第1のドレイン端子がドレイン端子を下向きに前記ダイパッドに直接に付けられ、前記同期FETダイの前記第2のソース端子が金属クリップによって前記接地端子に接続され、前記第2のソース端子と前記接地端子との間の電気的接続が前記金属クリップを介した2つの異なる電気的経路を含む、電源モジュール。

## 【請求項2】

10

20

請求項 1 に記載の電源モジュールであって、

前記同期 F E T ダイが、前記第 1 の物理的領域よりも小さくない第 2 の物理的領域と前記第 1 の能動領域よりも小さくない第 2 の能動領域とを有し、前記第 2 のドレイン端子が前記第 1 のソース端子に取り付けられる、電源モジュール。

【請求項 3】

請求項 2 に記載の電源モジュールであって、

前記制御 F E T ダイと前記同期 F E T ダイとが n 型 M O S F E T を含む、電源モジュール。

【請求項 4】

請求項 3 に記載の電源モジュールであって、

前記複数のリードが前記ダイパッドの辺に対して一列に配置される、電源モジュール。

【請求項 5】

請求項 4 に記載の電源モジュールであって、

前記コンバータのスイッチノード端子として動作可能な第 1 の金属クリップを更に含み、前記第 1 の金属クリップが、前記第 1 のソース端子と前記第 2 のドレイン端子にハンダ付けされ、それぞれのリードに接続されるリッジを有する、電源モジュール。

【請求項 6】

請求項 1 に記載の電源モジュールであって、

前記金属クリップが、前記第 2 のソース端子にハンダ付けされ、それぞれのリードに接続される 1 つ又は複数のリッジを有する、電源モジュール。

【請求項 7】

請求項 6 に記載の電源モジュールであって、

前記制御 F E T ダイが第 1 のゲート端子を有し、前記同期 F E T ダイが第 2 のゲート端子を有する、電源モジュール。

【請求項 8】

請求項 7 に記載の電源モジュールであって、

前記第 1 及び第 2 のゲート端子をリードに接続するワイヤボンドを更に含む、電源モジュール。

【請求項 9】

請求項 8 に記載の電源モジュールであって、

前記コンバータとクリップとワイヤボンドとを封止し、外部部品への接続のために前記パッドと前記複数のリードとの表面を封止せずに残す、パッケージング化合物を更に含む、電源モジュール。

【請求項 10】

電源モジュールであって、

外部入力端子と下向きのドレイン端子を有する制御電界効果トランジスタ ( F E T ) ダイとの間の第 1 の電気的経路と、

外部接地端子と同期 F E T ダイとの間の第 2 及び第 3 の電気的経路と、

を含み、

前記第 1 の電気的経路が前記第 2 の電気的経路より電気的に抵抗性が小さく、前記第 2 及び第 3 の電気的経路が第 2 の金属クリップを含み、前記第 2 の金属クリップがその相対する側に沿った 2 つの細長いリッジを有し、前記 2 つの細長いリッジが前記外部接地端子に結合される、電源モジュール。

【請求項 11】

請求項 10 に記載の電源モジュールであって、

前記第 1 の電気的経路が、前記制御 F E T ダイに直接にハンダ付けされる金属パッドを含む、電源モジュール。

【請求項 12】

請求項 10 に記載の電源モジュールであって、

前記第 2 の金属クリップが前記外部接地端子と前記同期 F E T ダイとに接触する、電源

10

20

30

40

50

モジュール。

【請求項 1 3】

請求項 1 2 に記載の電源モジュールであって、

前記第 2 の金属クリップがソース端子において前記同期 F E T ダイに接触する、電源モジュール。

【請求項 1 4】

請求項 1 0 に記載の電源モジュールであって、

外部スイッチノード端子を更に含む、電源モジュール。

【請求項 1 5】

請求項 1 0 に記載の電源モジュールであって、

10

外部スイッチノード端子を更に含み、前記外部入力端子が前記外部スイッチノード端子と前記外部接地端子との間に配置される、電源モジュール。

【請求項 1 6】

電源モジュールであって、

外部入力端子と下向きのドレイン端子を有する制御電界効果トランジスタ ( F E T ) ダイとの間の第 1 の電気的経路と、

外部接地端子と同期 F E T ダイとの間の第 2 及び第 3 の電気的経路と、

第 1 の金属クリップに接続される外部スイッチノード端子と、

を含み、

前記第 1 の電気的経路が前記第 2 の電気的経路より電気的に抵抗性が小さく、前記第 2 及び第 3 の電気的経路が第 2 の金属クリップを含む、電源モジュール。

20

【請求項 1 7】

請求項 1 6 に記載の電源モジュールであって、

前記第 1 の金属クリップが前記制御 F E T ダイと前記同期 F E T ダイとの両方に接触する、電源モジュール。

【請求項 1 8】

請求項 1 7 に記載の電源モジュールであって、

前記制御 F E T ダイが前記第 1 の金属クリップの第 1 の表面にハンダ付けされ、前記同期 F E T ダイが前記第 1 の金属クリップの第 2 の表面にハンダ付けされる、電源モジュール。

30

【請求項 1 9】

請求項 1 8 に記載の電源モジュールであって、

前記第 1 の金属クリップが前記制御 F E T ダイのソース端子と前記同期 F E T ダイのドレイン端子とにハンダ付けされる、電源モジュール。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、概ね、半導体デバイス及びプロセスの分野に関し、より詳細には、高効率を有し、スイッチノードリニングが低減された状態で高周波数で動作する電源モジュールのシステム構造及び製作方法に関する。

40

【背景技術】

【0 0 0 2】

よく使われているパワースイッチングデバイス系列の中には、D C - D C 電源回路があり、特に、スイッチモード電源回路の範疇に入るものがある。普及しつつある電力供給要件に特に適しているものは、直列に接続され、共通のスイッチノードによって互いに結合される 2 つのパワーM O S 電界効果トランジスタ ( F E T ) を備えた同期降圧コンバータである。降圧コンバータでは、ハイ側スイッチとも呼ばれる制御 F E T ダイが、供給電圧  $V_{I N}$  と L C 出力フィルタの間に接続され、ロー側スイッチとも呼ばれる同期 F E T ダイが、L C 出力フィルタと接地の間に接続される ( 同期 F E T はフリーホイールダイオードの代わりに同期整流器として働く ) 。このコンバータは、ドライバ回路及びコントローラ

50

回路も含む。

【0003】

出力回路のインダクタは、電源回路のエネルギーストレージとして働く。定出力電圧  $V_{OUT}$  を確実に維持するために、典型的なインダクタは約 300 ~ 400 nH とすべきである。

【0004】

いくつかのパワースイッチングデバイスが、パワーMOSFET、ドライバ回路、コントローラ回路とともに別々のダイとして構築される。各ダイは、典型的には、金属リードフレームの長方形又は正方形のパッドに取り付けられ、出力端子としてのリードがパッドを囲んでいる。これらのリードは、カンチレバー延長部をもたない形状とされ得、QFN (Quad Flat No-Lead) 又はSON (Small Outline No-Lead) デバイスとして配され得る。これらのダイとの電気的接続はボンディングワイヤによって提供される。このようなアセンブリは、典型的にプラスチックパッケージ内にパッケージングされ、パッケージングされた構成要素は、電源システムのボードアセンブリ用の個別の構成ブロックとして用いられる。

10

【0005】

他のパワースイッチングデバイスにおいて、パワーMOSFET及びドライバ - コントローラダイがリードフレームパッド上に並んでアセンブリされ、デバイス出力端子として働くリードがリードフレームパッドの4辺すべてを囲む。これらのリードもQFN又はSONにならった形状にされ得る。

20

【0006】

いくつかの近年導入された先進アセンブリでは、接続ワイヤの代わりに銅クリップが用いられる。これらのクリップは幅が広く、導入される寄生インダクタンスが小さい。

【0007】

別の最近の開発では、制御FETと同期FETがスタック状に互いの頂部上に垂直にアセンブリされ、これら2つのFETのうち物理的に面積が大きいダイがリードフレームパッドに取り付けられ、クリップがスイッチノード及びスタック頂部への接続を提供する。このパッケージでは、同期FETチップはリードフレームパッド上にアセンブリされ、同期FETのソース端子がリードフレームパッドにハンダ付けされる。制御FETチップは、そのソースが同期ダイのドレインに結合されてスイッチノードが形成され、そのドレインが入力電源  $V_{IN}$  に接続される。これら2つのFET間に挿入されるクリップがスイッチノードに接続される。パッドは接地電位を有し、ヒートスプレッダとして働く。スタック頂部上の細長いクリップが、制御FETのドレイン端子を入力電源  $V_{IN}$  に接続する。

30

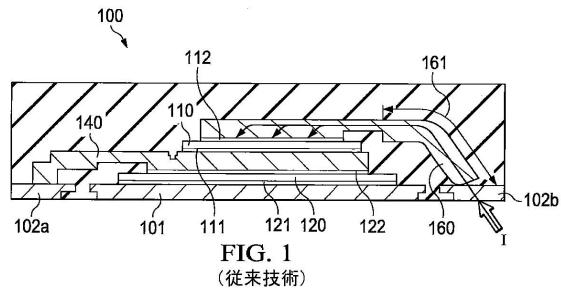

【0008】

直前の段落で説明した典型的なコンバータが図1に示され、全体的に100で表されている。制御FET110が同期FET120の上にスタックされる。制御FETダイ110は、同期FETダイ120に対して小さな面積を有する。QFN金属リードフレームが、長方形の平坦なパッド101を有する。リード102a及び102bが、パッドの相対する側の2辺に沿って一列に配置される。これらのFETダイのスタックはソースを下向きにして成される。同期FET120のソースは、ハンダ層121によってリードフレームパッド101にハンダ付けされる。ハンダ層122によって同期FET120のドレインにハンダ付けされる第1のクリップ140が、ハンダ層111によって取り付けられる制御FET110のソースを有する。そのため、第1のクリップ140は、コンバータのスイッチノード端子として働く。第2のクリップ160が、ハンダ層112によって制御FET110のドレインに接続される。第2のクリップ160は、リードフレームのリード102bに取り付けられ、そのため、入力電源  $V_{IN}$  に接続される。このコンバータは、500 kHzから1 MHzまでの周波数で効率的に動作し得る。

40

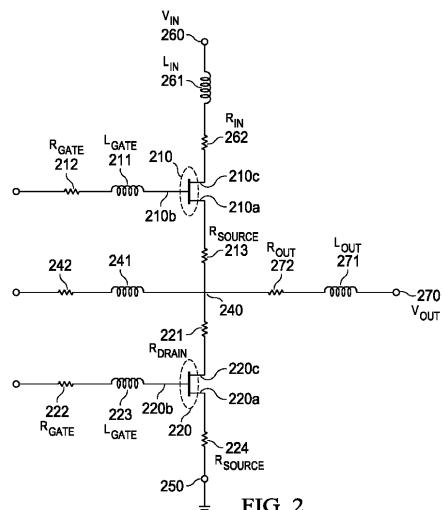

【0009】

図2は、図1の同期降圧コンバータアセンブリの電気回路図である。図2では、ゲート210bがワイヤボンドによってリードに接続されるように示されており、このワイヤボ

50

ンド接続は、約  $1.94 \text{ nH}$  の寄生インダクタンス  $L_{GATE}$  (211) 及び約  $2.6 \text{ m}$  の寄生インピーダンス  $R_{GATE}$  (212) と相互に関係している。制御 FET 210 が第1のクリップ 140 上にソースを下向きにしてアセンブリされているため、ソース 210a の寄生インピーダンス  $R_{SOURCE}$  (213) は実質的にゼロである。ソースが下向きのアセンブリのために、ソース 210a の寄生インダクタンスも小さい。

#### 【0010】

図2はさらに、リードフレームパッド 101に対する同期 FET 220 の典型的な寄生インダクタンス及びインピーダンスも示している。ハンダ付けによってソース 220a をパッドに接続するため、この接続の寄生抵抗  $R_{SOURCE}$  (224) は小さくなる(約  $0.001 \text{ m}$ )。同期 FET 220 が第1のクリップ 140 にハンダ付けされているため、ドレイン 220c の寄生インピーダンス  $R_{DRAIN}$  (221) は実質的にゼロであり、ドレイン 220c の寄生インダクタンスも小さい。ゲート 220b はワイヤボンドによってリードに接続され、そのため、約  $1.54 \text{ nH}$  の寄生インダクタンス  $L_{GATE}$  (223) 及び約  $2.2 \text{ m}$  の寄生インピーダンス  $R_{GATE}$  (222) と相互に関係している。

10

#### 【0011】

図2に示されるように、コンバータの負荷電流は、スイッチノード 240 から、リードフレームの対応するリードに取り付けられる第1のクリップ 140 を介して、出力インダクタ及び  $V_{OUT}$  (270) まで流れる。第1のクリップ 140 に沿って、寄生インピーダンス  $R_{OUT}$  (272) は約  $0.2 \text{ m}$  であり、寄生インダクタンス  $L_{OUT}$  (271) は約  $0.45 \text{ nH}$  である。図2はさらに、スイッチノード 240 からリードフレームの対応するリードに接続される制御 FET のゲートリターンを示す。この接続は、ワイヤボンドによってなされるので、約  $1.54 \text{ nH}$  の寄生インダクタンス 241 及び約  $2.2 \text{ m}$  の寄生インピーダンス 242 を与える。

20

#### 【発明の概要】

#### 【0012】

出願人により、図1に示すような典型的なシステムのオンサイクルの初期段階の間、約  $50 \text{ ns}$  の時間間隔にわたって、スイッチノード電圧に関連する最大約  $2.5 \text{ V}$  の過大なリングングがあることが観察された。このピーク電圧は、このシステムで用いられるMOSFETの絶縁破壊電圧に近くなるか、又はそれを超えることがあり、そのため、多くのアプリケーションではこのリングングの振幅及び継続時間は許容されない。

30

#### 【0013】

詳細な解析により、出願人は、この過大なリングングの根本的な原因は、コンバータの入力ノードにおける過大な寄生インピーダンス及びインダクタンスに関連しており、そのため入力ノードと出力回路要素の間でエネルギーが交換され、それが出力ノードでリングングとして出現することを見いだした。さらに、出願人は、入力ノードにおいて寄生インダクタンス及びインピーダンスが生じる大きな要因が、制御 FET のドレインをリードフレーム端子 102b において入力電源  $V_{IN}$  に接続する細長いクリップであることを見いだした。

40

#### 【0014】

出願人はさらに、この細長いクリップが銅などの高導電材料で製作されても、コンバータ内では、制御 FET のドレインとリードフレーム端子の間を流れる入力電流が、クリップをその長さ分、ネック部分 161 を含め、クリップの小さな断面を通って流れなければならないように構成されていることを見いだした。出願人は、このようなコンバータでは、クリップは典型的には入力ノードにおいて  $600 \text{ pH}$  のインダクタンス及び  $0.5 \text{ m}$  のインピーダンスを附加すると算出した。

#### 【0015】

出願人は、コンバータの入力端子をリードフレームパッドに直接接続し、それによって、コンバタ回路の入力ノードからのクリップに関連する寄生の影響を取り除くことによってこの問題を解決した。

50

## 【0016】

これは、例えば、制御FETとしてドレインが下向きのFETを備えたコンバータを構築し、外部回路ボードに取り付け可能な金属パッド上にドレイン端子を直接配置して、入力電流がVin端子から制御FETのドレインに直交しつつ垂直に流れるようにすることによって実現し得る。これにより、間に事実上何の寄生インダクタンス又はインピーダンスも生じることなく電流経路が得られる。制御ダイ上に配されるスイッチノードクリップは、電流がコンバータスタックを介して垂直に流れ続けるように、制御ダイの頂部上に同期ダイをドレインを下向きにして配置するために充分に広い面積を有するように設計される。同期ダイのソース端子は第2のクリップによって接地される。この実施形態をテストすると、スイッチノード電圧のリンクギングの振幅及び継続時間が90%よりも大きく減少する。

10

## 【0017】

関連する図面を参照して本発明の上記及び他の実施形態を下記により詳細に説明する。

## 【図面の簡単な説明】

## 【0018】

【図1】従来技術に従ってアセンブリされた同期降圧コンバータの断面図であり、大面積同期FETダイがリードフレームパッドに取り付けられ、その上に小面積制御FETダイが配置され、後者が細長いクリップによってリードに接続されている。

## 【0019】

【図2】図1に示す同期降圧コンバータの出願人による回路図である。

20

## 【0020】

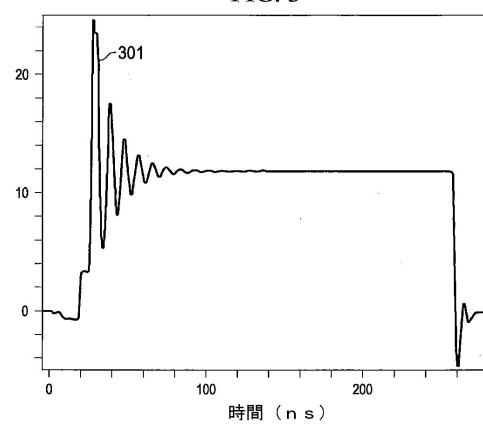

【図3】図2に示すような同期降圧コンバータの開始後のスイッチノード電圧（単位：ボルト）を時間（単位：ナノ秒）の関数として示すグラフである。

## 【0021】

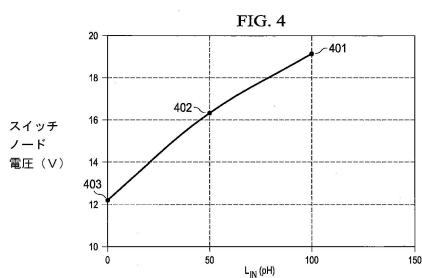

【図4】同期降圧コンバータのスイッチノード電圧のリンクギングの振幅（単位：ボルト）を寄生入力インダクタンス（単位：ピコヘンリー）の関数として示す。

## 【0022】

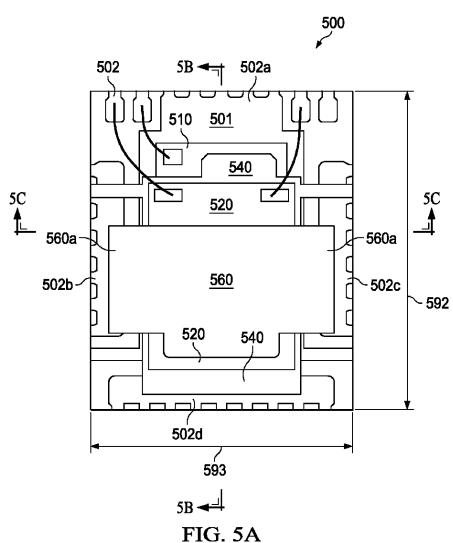

【図5A】本発明の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、モジュールの透明な封入を通して見た上面図である。

30

## 【0023】

【図5B】本発明の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、モジュールの切断線に沿った図5Aのモジュールの断面図である。

## 【0024】

【図5C】本発明の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、図5Bの切断線に直交する別の切断線に沿った図5Aのモジュールの断面図である。

## 【0025】

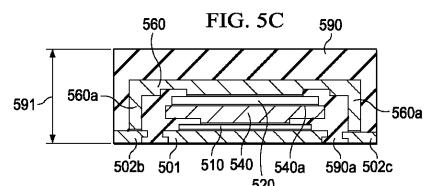

【図6】図5A、図5B、及び図5Cに示す同期降圧コンバータの出願人による回路図である。

## 【0026】

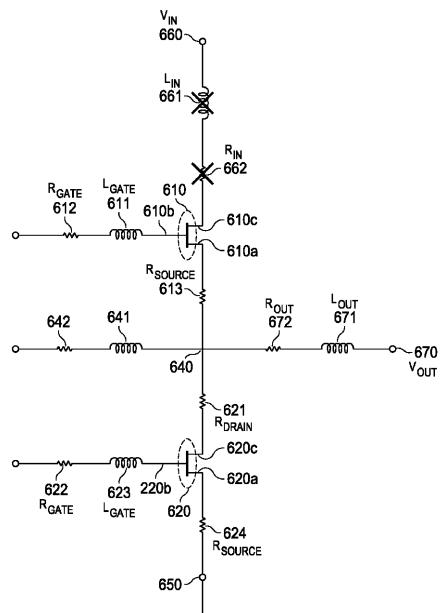

【図7】図5A、図5B、及び図5Cに示す同期降圧コンバータの開始後のスイッチノード電圧（単位：ボルト）を時間の関数（単位：ナノ秒）として示すグラフである。

40

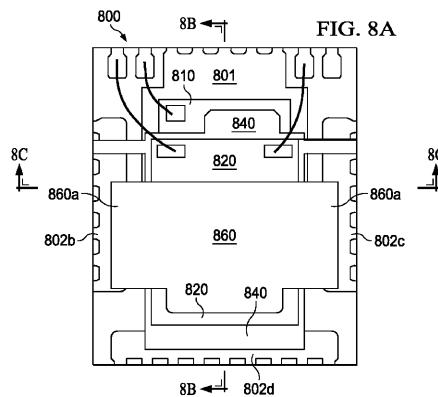

## 【0027】

【図8A】本発明の別の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、モジュールの透明な封入を通して見た上面図である。

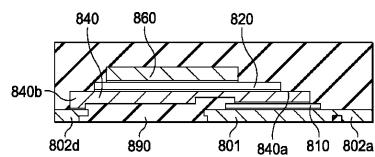

## 【0028】

【図8B】本発明の別の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、モジュールの切断線に沿った図8Aのモジュールの断面図である。

## 【0029】

【図8C】本発明の別の実施形態に従ってアセンブリされる同期降圧コンバータモジュ

50

ルの構造を示し、図 8 B の切断線に直交する別の切断線に沿った図 8 A のモジュールの断面図である。

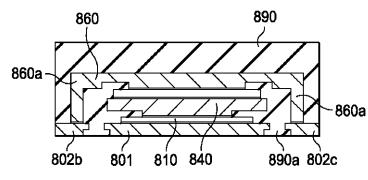

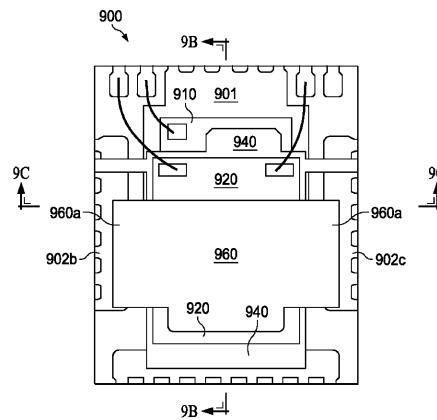

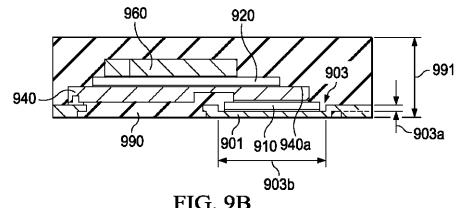

【0030】

【図 9 A】本発明の別の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、モジュールの透明な封入を通して見た上面図である。

【0031】

【図 9 B】本発明の別の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、モジュールの切断線に沿った図 9 A のモジュールの断面図である。

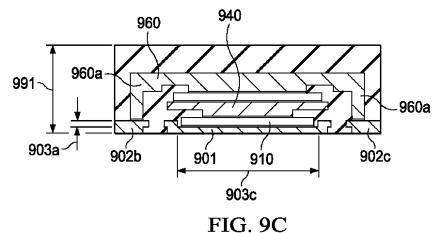

【0032】

【図 9 C】本発明の別の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、図 9 B の切断線に直交する別の切断線に沿った図 9 A のモジュールの断面図である。 10

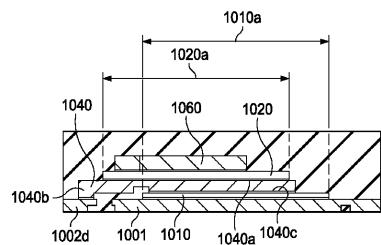

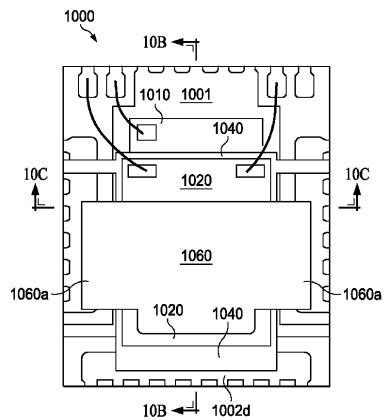

【0033】

【図 10 A】本発明のさらに別の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、モジュールの透明な封入を通して見た上面図である。

【0034】

【図 10 B】本発明のさらに別の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、モジュールの切断線に沿った図 10 A のモジュールの断面図である。

【0035】

【図 10 C】本発明のさらに別の実施形態に従ってアセンブリされる同期降圧コンバータモジュールの構造を示し、図 10 B の切断線に直交する別の切断線に沿った図 10 A のモジュールの断面図である。 20

【発明を実施するための形態】

【0036】

図 1 に示すような例示同期降圧コンバータが動作中のとき、時間の関数としてのスイッチノード電圧  $V_{SW}$  の開始が、図 3 のシミュレーション波形 301 によってグラフ化されるように観察された。スイッチノード電圧  $V_{SW}$  は、ボルト単位で測定され、時間（単位：ナノ秒）の関数として表示されている。図 3 に示すように、この電圧は、最大で 25 V までの急速な変位（振幅）を経て周期的に変動した後、その最終的な定常値 12 V まで減衰する。スイッチノード電圧のこのいわゆるリンクギング挙動は 60 ~ 80 ns の間継続する。多くのコンバータアプリケーションでは、スイッチノード電圧のこの大きく長いリンクギングは許容されない。 30

【0037】

詳細な解析において、出願人は、スイッチノード電圧のこれらの振幅の根本的な原因は、図 1 に 160 で表す細長いクリップの大きな寄生インダクタンス  $L_{IN}$  (600 pH、図 2 に 261 で表す) 及び寄生インピーダンス  $R_{IN}$  (0.5 m、図 2 に 262 で表す) であることを見いだした。このクリップは、制御入力端子を入力電源  $V_{IN}$  に接続するための細長い延長部を有する。その結果、 $V_{IN}$  から制御ダイ (110) の入力端子への電流は、寄生インダクタンス及びインピーダンスを有するクリップ 160 の長さを介して横方向に流れる。図 4 は、オンになったスイッチノード電圧  $V_{SW}$  のデータ及び補間された値を示す。これらの値は、ピコヘンリーの単位で測定される寄生インダクタンス  $L_{IN}$  の関数としてボルト単位で測定される。100 pH (測定値 401) の寄生入力インダクタンス  $L_{IN}$  で、スイッチノード電圧  $V_{SW}$  は 19 V よりも大きく変位する。先に述べたように、図 2 の回路では、寄生入力インダクタンス  $L_{IN}$  は 600 pH であり得る。これにより、スイッチノード電圧  $V_{SW}$  が変位して 25 V まで達し得る。図 4 では、 $L_{IN}$  を 50 pH (データ点 402) まで低減しても、スイッチノード電圧は依然として 16 V よりも大きく変動する。 40

【0038】

図 5 A、図 5 B、及び図 5 C は、上記の問題に対する 1 つの解決策を示す。これらの図 50

面に示されるコンバータは、その入力電流が、パッド 501 から、実質的な寄生インピーダンス又はインダクタンスを有するいかなる要素も経ることなく、制御 FET 510 のドレイン端子に垂直に流れる。制御 FET は、 $V_{IN}$  に接続されるリードフレームパッドに直接取り付けられる。このコンバータの制御 FET は、ドレインが下向きの n チャネル MOSFET である。そのため、入力電流 (I) は、パッドから垂直に制御ダイのドレイン端子に入る。ハンダ付けの場合、入力電流は、インピーダンス及びインダクタンスがない状態で制御ダイのドレインに達することができる。同期ダイは、制御ダイの頂部上に配置され、ドレインを下向きにして制御ダイのソースに取り付けられる。そのため、電流はコンバータスタックを介して垂直に流れ続ける。同期ダイのソース端子は、ヒートスプレッダとして働くように設計されるクリップによって接地される。その結果、スイッチノード電圧のリングは、継続時間が 90 % よりも大きく、振幅が 75 % よりも大きく減少する。（より詳細には図 7 を参照されたい。）

#### 【0039】

透明な封入化合物を通した上面図において、図 5A は、図 5B 及び図 5C の断面の切断線を示す。コンバータ 500 は、制御 MOSFET ダイ 510 上にスタックされる同期 MOSFET ダイ 520 を有する。オン状態の抵抗値  $R_{ON}$  は能動ダイ面積に反比例するので、同期降圧コンバータのデューティサイクルが、同期 FET に必要とされる能動領域に対する制御 FET に必要とされる能動領域の比を決定する。図 5A、図 5B、及び図 5C の例示モジュールでは、予想されるデューティサイクルはほとんどの時間で小さい ( $< 0.5$ )。したがって、制御 FET は動作の大部分の間オフになり導通せず、同期 FET はサイクルタイムの大部分で導通する。降圧コンバータの導電損失  $P_{LOSS} = I^2 R_{ON}$  を低減するために、同期 FET ダイ 520 が制御 FET ダイ 510 の能動領域と等しいか、それよりも大きい能動領域を有することが好ましい。その結果、同期ダイ 520 も制御ダイ 510 の物理的な面積に等しいかそれより大きい物理的な面積を有する。

#### 【0040】

図 5A、図 5B 及び図 5C はさらに、 $V_{IN}$  からの入力電流 (I) の入力端子になる長方形の平坦なデバイスアセンブリパッド (DAP) 501 を備えた、一般的な QFN タイプの構成を有する金属リードフレームを示す。リードフレームのリードは、長方形パッド 501 の 4 辺に平行に配置される。個別のリードは 502 で表され、他のリードは集合単位でまとめて表される。集合 502a はパッド 501 に接続され、集合 502b 及び 502c は、電気的接地への端子及び熱的エネルギー（熱）移動の経路として働き、集合 502d はスイッチノード及び出力電流への端子として働く。他の実施形態が、特に特定の熱分散が必要な場合に、異なるリード構成を有し得ることに留意されたい。

#### 【0041】

先に述べたように、図 5A、図 5B、及び図 5C の例では、制御ダイ 510 は同期ダイ 520 に等しいかそれより小さい面積を有する。n 型導電性チャネルダイの実施形態では、制御ダイがドレインを下向きにしてリードフレームパッドにアセンブリされる必要があるので、スタックされたアセンブリ内で小さな制御ダイが大きな同期ダイの垂直に下に配置される必要がある。そのため、制御ダイ 510 のソースを同期ダイ 520 のドレインに接続するスイッチクリップ 540（第 1 のクリップとも称する）が、その上側 540a のハンダ付け可能な領域を拡張して大面積同期ダイ 520 が収まるように設計され得る。スイッチクリップ 540 の好ましい製作方法が、リードフレームのリード集合 502d への第 1 のクリップ 540 の取付けを容易にするように第 1 のクリップ 540 の 1 辺から突出するビーム状リッジ（プロップ）540b（図 5B 参照）の形成を可能にするハーフエッティング技術を含む。

#### 【0042】

ドレインが下向きにスタックされた FET を備えたコンバータアセンブリでは、同期ダイ 520 のソース端子はスタックの頂部上に置かれ、そして、電気的に接地されなければならない。接続用の第 2 のクリップ 560 は、動作するコンバータによって生成される動作熱の大部分を基板内のヒートシンクに伝えるように設計される。そのため、この実施形

10

20

30

40

50

態の第2のクリップ560は、ヒートスプレッダとして働く大きな金属領域と、好ましくはクリップの相対する側に沿った2つの細長いリッジ(プロップ)560a(図5C参照)を有し、それにより、熱をリード502b及び502cに伝え、そこから基板内のヒートシンクまで伝えるようにする。リードの構成が異なる他の実施形態において、クリップ560は、コンバータからの熱除去を向上させるために3つのリッジを有するように設計され得る。さらに他の実施形態では、1つのリッジ560aで充分な場合もある。リッジ560aはこれらがパッド501の相対する側のリード集合502b及び502cにハンダ付けされ得るように充分高く形成される。リッジ560aを備えた第2のクリップ560を製作する好ましい方法は、金属シートに適用されるハーフエッチング技術である。

## 【0043】

10

スタックされたMOSFETは、好ましくは、モジュールを形成するように保護パッケージング化合物590に封入される。好ましい封入方法は成型技術である。図5B及び図5Cに示す実施形態では、成型モジュールの厚さ591は約1.5mmである。スイッチクリップ540は先に述べたように好ましくはハーフエッチング技術によって製作されるので、封入されるモジュールの堅固さを増すために、ハーフエッチング処理によって開けられる空隙590aなどのいかなる空間も封入化合物で充填することが有利である。図5Aの実施形態500では、成型されたパッケージの横方向寸法は、長さ592が約6mmであり、幅593が約5mmである。

## 【0044】

20

図6は、図5A、図5B、及び図5Cに示すような例示同期降圧コンバータの回路図である。電源 $V_{IN}$ (660)から制御FET610のドレイン610cに流れる入力電流は、リードフレームパッド(図5A、図5B、及び図5Cの501)の厚さを介して垂直に流れ、その結果、寄生インダクタンス $L_{IN}$ (661)及び寄生インピーダンス $R_{IN}$ (662)がほぼゼロになる。

## 【0045】

30

図6にさらに示すように、ゲート610bが、ワイヤボンドによってリードフレームのリードに接続され、そのため、約1.94nHの寄生インダクタンス $L_{GATE}$ (611)及び約26mの寄生インピーダンス $R_{GATE}$ (612)を有する。制御FET610のソース610aの寄生インピーダンス $R_{SOURCE}$ (613)は、スイッチノード640として機能する第1のクリップ540にソース610aが直接ハンダ付けされるので、実質的にゼロであり、ソース610aの寄生インダクタンスも同様に実質的に無視し得る。

## 【0046】

40

図6はさらに、同期FET620がドレインを下向きにしてスイッチノードに接続され、且つそのソース620aが接地650に接続されることに伴う寄生値も示す。寄生インピーダンス $R_{SOURCE}$ (624)及び第2のクリップに沿った電源電圧 $V_{IN}$ までの寄生抵抗値はゼロではないが、その入力電流に対する影響は無視し得る。ドレイン620cと第1のクリップの間の寄生インピーダンス $R_{DRAIN}$ (621)は、同期FET620が第1のクリップ540(スイッチノード640)に取り付けられているため、実質的にゼロであり、ドレイン620cの寄生インダクタンスも実質的にゼロである。

## 【0047】

ゲート620bは、ワイヤボンドによってリードフレームのリードに結合され、そのため、約1.54nHの寄生インダクタンス $L_{GATE}$ (623)及び約22mの寄生インピーダンス $R_{GATE}$ (622)を有する。図6では、コンバータの負荷電流は、スイッチノード640からリードフレームの対応するリードに取り付けられる第1のクリップ(図5A、図5B、及び図5Cの540)を介して、出力インダクタ(図6では図示せず)及び $V_{OUT}$ (670)まで流れる。第1のクリップ540に沿って、寄生インピーダンス $R_{OUT}$ (672)は約0.2mであり、寄生インダクタンス $L_{OUT}$ (671)は約0.45nHである。図6はさらに、スイッチノード640からリードフレームの対応するリードに接続される制御FETのゲートリターンを示す。この接続は、ワイヤボン

50

ドによってなされるので、約 1.54 nH の寄生インダクタンス 641 及び約 2.2 m の寄生インピーダンス 642 を与える。

【0048】

図 5 A、図 5 B、及び図 5 C に示すような例示同期降圧コンバータが動作中のとき、時間の関数としてのスイッチノード電圧  $V_{SW701}$  の開始の波形が、図 7 のようにグラフ化され得る。図 7 に示すように、この電圧は、最大 16.3 V までの 2、3 回小さな変位を経て変動した後、その最終的な定常値 12 V まで急速に減衰する。この電圧のこの種のリングング挙動は、10 ~ 15 ns の間継続し、そのため、短くかつ穏やかである。

【0049】

他のシミュレーション及びデータにより、図 5 A、図 5 B、及び図 5 C に従ってアセンブリされる同期降圧コンバータの効率は 89.5% に達し得るが、図 1 に従ってアセンブリされるコンバータの効率は 88.5% に過ぎないことが示されている。これは、効率の損失がほぼ 8% 低減されることを示している。

【0050】

本発明の別の実施形態を図 8 A、図 8 B、及び図 8 C に示し、全体的に 800 として表す。この実施形態は、制御ダイ 810 の面積に匹敵する程度に面積が小さくされたリードフレームパッド 801 によって特徴づけられる。図 8 B の図 5 B との比較が示すように、パッド金属の量が減少しているので、より多い封入化合物 890 が用いられ得る。封入化合物の量が増えると、温度変動や湿気のある雰囲気におけるモジュール 800 の堅固さが増す。これにより、化合物と金属の間の剥離の又は化合物の破壊のリスクが減少する。

【0051】

図 8 B に示すように、第 1 のクリップ 840 は、その上側 840a のハンダ付け可能領域を拡張して大面積同期ダイ 820 が収まるように設計される。第 1 のクリップ 840 の好ましい製作方法が、リードフレームのリード集合 802d への第 1 のクリップ 840 の取付けが容易になるように第 1 のクリップ 840 の 1 辺から突出するビーム状リッジ 840b の形成を可能にするハーフエッチング技術を含む。第 2 のクリップ 860 は、コンバータの動作の間生成される動作熱の大部分を基板内のヒートシンクに伝えるように設計される。そのため、この実施形態の第 2 のクリップ 860 は、ヒートスプレッダとして働く大きな金属領域と、好ましくはクリップの相対する側に沿った 2 つの細長いリッジ 860a を有し、それにより、熱をリード 802b 及び 802c に伝え、そこから基板内のヒートシンクまで伝えるようにする。他の実施形態において、クリップ 860 は、コンバータからの熱除去を向上させるために 3 つのリッジを有するように設計されるが、他の実施形態において 1 つのリッジで充分な場合もある。リッジ 860a は、これらがパッド 801 の相対する側のリード集合 802b 及び 802c にハンダ付けされ得るように充分高く形成される。リッジ 860a を備えた第 2 のクリップ 860 を製作する好ましい方法は、金属シートに適用されるハーフエッチング技術である。

【0052】

本発明のさらに別の実施形態を図 9 A、図 9 B、及び図 9 C に示し、全体的に 900 で表す。この実施形態は、図 8 の実施形態のパッド領域に類似の面積のリードフレームパッド 901 を含むが、このパッド領域には窪んだ凹部 903 がある。ハーフエッチング技術によって、長方形凹部 903 が、深さ 903a、横方向寸法 903b 及び 903c で生成され、そのため、長方形制御ダイ 910 をこの窪んだ凹部内に配置することができる。同期ダイを 920 で表す。その結果、第 1 のクリップ 940 は、リードフレームのリードに取り付けるための突出するリッジを必要とせず、実質的に平坦なプレートのままとし得、そのため、全体的なモジュールの厚さを薄くする現在の傾向に沿っている。封入化合物 990 を備えたモジュール 900 では、厚さ 991 は、図 5 の例示モジュールの厚さ 591 が 1.5 mm であるのに対し、1.3 mm に過ぎない。図 9 A 及び図 9 C では、第 2 のクリップ 960 は、動作するコンバータによって生成される熱の大部分を基板内のヒートシンクに伝えるように設計される。そのため、この実施形態の第 2 のクリップ 960 は、ヒートスプレッダとして働く大きな金属領域と、好ましくはクリップの相対する側に沿った

10

20

30

40

50

2つの細長いリッジ 960aとを有し、それにより、熱をリード 902b及び902cに伝え、そこから基板内のヒートシンクまで伝えるようとする。リードの構成が異なる他の実施形態において、クリップ 960は、コンバータからの熱除去を向上させるために3つのリッジを有するように、更に他の実施形態において1つのリッジを有するように、設計される。

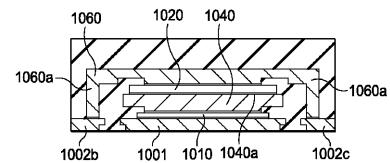

#### 【0053】

図10A、図10B、及び図10Cは、高デューティサイクル動作を意図した、さらに別の実施形態を示し、全体的に1000で表す。実施形態1000は、制御ダイ1010と同期ダイ1020の面積が実質的に等しいことによって特徴づけられる。例として、図10Bにおいて横方向寸法1010a及び1010bはそれぞれ3.5mmである。n型導電性チャネルダイはドレインを下向きにしてより容易にリードフレームパッド1001にアセンブリされるので、制御ダイ1010は、スタックされたアセンブリにおいて同期ダイ1020の垂直に下に配置され得る。そのため、制御ダイ1010のソースを同期ダイ1020のドレインと接続するスイッチクリップ(第1のクリップ)1040が、同期ダイ1020を収めるためのハンダ付け可能な表面1040a及び制御ダイ1010を収めるためのハンダ付け可能な表面1040cを有するように設計され得る。スイッチクリップ1040の好ましい製作方法が、リードフレームのリード集合1002dへの第1のクリップ1040の取付けが容易になるように第1のクリップ1040の1辺から突出するビーム状リッジ(プロップ)1040b(図10B参照)、及び適切な表面領域の形成を可能にするハーフエッチング技術を含む。ドレインを下向きにしてスタックされるFETを備えたコンバータアセンブリでは、同期ダイ1020のソース端子は、このスタックの頂部上に配置され、そして、接地電位に電気的に接続されなければならない。接続用の第2のクリップ1060は、動作するコンバータによって生じる動作熱の大部分を基板内のヒートシンクに伝えるように設計される。そのため、この実施形態の第2のクリップ1060は、ヒートスプレッダとして働く大きな金属領域とクリップの相対する側に沿って2つ(或いは3つの場合もある)の細長いリッジ1060aとを有し、熱をリード1002b及び1002cに伝え、そこから基板内のヒートシンクまで伝えるようとする。

#### 【0054】

本発明は、電界効果トランジスタだけでなく、他の適切なパワートランジスタにも適用される。さらに、第2のクリップがヒートシンクに、好ましくはハンダ付けによって、接続され得るように第2のクリップの頂部表面を封入せずに残すことによって、電源モジュールの大電流能力はさらに拡張され得、効率はさらに高められ得る。この構成では、モジュールはその熱をヒートシンクの両面から放散し得る。

#### 【0055】

本発明の特許請求の範囲から逸脱することなく、説明した実施形態に多くの他の改変をなし得ること、及び多くの他の実施形態が可能であることが当業者には理解されよう。

【図1】

FIG. 1

(従来技術)

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5A】

FIG. 5A

【図5C】

FIG. 5C

【図5B】

FIG. 5B

【図6】

FIG. 6

【図7】

FIG. 7

【図8A】

FIG. 8A

【図8B】

FIG. 8B

【図8C】

FIG. 8C

【図9A】

FIG. 9A

【図9B】

FIG. 9B

【図 9C】

FIG. 9C

【図 10B】

FIG. 10B

【図 10A】

FIG. 10A

【図 10C】

FIG. 10C

---

フロントページの続き

(51)Int.Cl. F I

H 02M 3/155 (2006.01)

(72)発明者 ファン エイ エルボソメール

アメリカ合衆国 18078 ペンシルベニア州 シュネックスビル, アロー・ヘッド ドライブ

5165

(72)発明者 オスバルド ジェイ ロペス

アメリカ合衆国 08801 ニュージャージー州 アナンデール, グランディン テラス 1

6

(72)発明者 ジョナサン エイ ノキル

アメリカ合衆国 18015 ペンシルベニア州 ベスレヘム, ソーコンピューター ドライブ 1

06

審査官 原田 貴志

(56)参考文献 特開2005-217072 (JP, A)

米国特許出願公開第2010/0090668 (US, A1)

米国特許出願公開第2010/0171543 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H 01L 25/07

H 01L 21/60

H 01L 23/48

H 01L 25/065

H 01L 25/18

H 02M 3/155