(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4942020号

(P4942020)

(45) 発行日 平成24年5月30日(2012.5.30)

(24) 登録日 平成24年3月9日(2012.3.9)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 25/065 | (2006.01) | HO1L 25/08 | Z    |

| HO1L 25/07  | (2006.01) | HO1L 21/60 | 301N |

| HO1L 25/18  | (2006.01) |            |      |

| HO1L 21/60  | (2006.01) |            |      |

請求項の数 4 (全 13 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2006-133680 (P2006-133680)  |

| (22) 出願日  | 平成18年5月12日 (2006.5.12)        |

| (65) 公開番号 | 特開2007-305848 (P2007-305848A) |

| (43) 公開日  | 平成19年11月22日 (2007.11.22)      |

| 審査請求日     | 平成21年4月30日 (2009.4.30)        |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地 |

| (74) 代理人  | 100089071<br>弁理士 玉村 静世                               |

| (72) 発明者  | 黒田 宏<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内             |

| (72) 発明者  | 橋詰 勝彦<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内            |

審査官 日比野 隆治

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

平面形状が四角形から成る主面、前記主面に形成された複数のボンディングリード、及び前記主面とは反対側の裏面を有するモジュール基板と、

平面形状が四角形から成る第1主面、前記第1主面に形成された集積された第1回路、前記第1主面に形成され、かつ前記第1回路に接続する複数の第1電極パッド、前記第1主面に形成され、かつ前記第1回路に接続する複数の第2電極パッド、及び前記第1主面とは反対側の第1裏面を有し、前記モジュール基板の前記主面に搭載された第1半導体チップと、

平面形状が四角形から成る第2主面、前記第2主面に形成された集積された第2回路、前記第2主面に形成され、かつ前記第2回路に接続する複数の第3電極パッド、前記第2主面に形成され、かつ前記第2回路に接続する複数の第4電極パッド、及び前記第2主面とは反対側の第2裏面を有し、前記第1半導体チップの前記第1主面に搭載された第2半導体チップと、

前記第1電極パッドと前記複数のボンディングリードのうちの第1ボンディングリードとを電気的に接続する第1ワイヤと、

前記第3電極パッドと前記複数のボンディングリードのうちの第2ボンディングリードとを電気的に接続する第2ワイヤと、

前記複数の第2電極パッドのうちの第5電極パッドと前記複数のボンディングリードのうちの第3ボンディングリードとを電気的に接続する第3ワイヤと、

10

20

前記複数の第4電極パッドと前記複数の第2電極パッドのうちの第6電極パッドとを電気的に接続する第4ワイヤと、

前記第1半導体チップ、前記第2半導体チップ、前記第1ワイヤ、前記第2ワイヤ、前記第3ワイヤ、及び前記第4ワイヤを封止する封止体と、を含み、

前記モジュール基板の前記主面は、第1辺と、前記第1辺と対向する第2辺を有し、

前記第1ポンディングリードは、前記第1辺に沿って配置されており、

前記第2ポンディングリードは、前記第1辺と前記第1ポンディングリードとの間に前記第1辺に沿って配置されており、

前記第3ポンディングリードは、前記第2辺に沿って配置されており、

前記第1半導体チップは、前記第1ポンディングリードと前記第3ポンディングリードとの間に配置され、10

前記第1半導体チップの前記第1主面は、前記モジュール基板の前記第1辺と並ぶ第3辺と、前記第3辺と対向する第4辺を有し、

前記複数の第1電極パッドは、前記第3辺に沿って配置され、

前記複数の第2電極パッドは、前記第4辺に沿って配置され、

前記第2半導体チップは、前記複数の第1電極パッドと前記複数の第2電極パッドとの間に配置され、

前記第2半導体チップの前記第2主面は、前記第1半導体チップの前記第3辺と並ぶ第5辺と、前記第5辺と対向する第6辺を有し、20

前記複数の第3電極パッドは、前記第5辺に沿って配置され、

前記複数の第4電極パッドは、前記第6辺に沿って配置され、

断面視において、前記モジュール基板の前記第1辺と前記第1半導体チップの前記第3辺の間隔は、前記モジュール基板の前記第2辺と前記第1半導体チップの前記第4辺の間隔よりも大きく、

前記第4電極パッドは、前記第6辺の縁辺部分に集約され、

前記第6電極パッドは、前記第4辺の縁辺部分に集約され、

前記第4ワイヤを共有する前記第4電極パッドと前記第6電極パッドは相互に一方が出力端子であり、他方が入力端子であることを特徴とする半導体装置。

#### 【請求項2】

断面視において、前記第2半導体チップの中心部は、前記モジュール基板の前記第1辺よりも前記モジュール基板の中心部から前記モジュール基板の前記第2辺に向かって偏倚していることを特徴とする請求項1記載の半導体装置。30

#### 【請求項3】

複数のボール電極が前記モジュール基板の前記裏面に形成されていることを特徴とする請求項1記載の半導体装置。

#### 【請求項4】

前記第1半導体チップは、CCDカメラの動作を制御するタイミング制御信号を生成するタイミング・コントローラであり、

前記第2半導体チップは、前記CCDカメラに駆動電圧を出力するドライバであることを特徴とする請求項1記載の半導体装置。40

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、2個の半導体チップを積み重ねて1個のパッケージに収めたスタック構造のシステム・イン・パッケージ(SIP)の半導体装置に関する。

##### 【背景技術】

##### 【0002】

2個の半導体チップをスタックしたSIPにおいてモジュール基板の裏面にはボール・グリッド・アレイ(BGA)等のモジュール端子が配置され、モジュール基板の表面にはモジュール端子に結合するポンディングリード等が形成される。ポンディングリードには50

10

スタックされた 2 個の半導体チップの対応する電極パッドがワイヤで接続される。双方の半導体チップの同じ側の辺に沿って多数の電極パッドが配置されているとき、それらが接続されるボンディングリードはモジュール基板の一辺に沿って前後 2 列に配置される。例えば下に配置された半導体チップの電極パッドに前列のボンディングリードをワイヤで接続し、上に配置された半導体チップの電極パッドに後列のボンディングリードをワイヤで接続する。特許文献 1 にはそのような接続形態として、上側の半導体チップの電極パッドを対応するボンディングリードに直接接続する場合、接続ワイヤが長くなるとそのワイヤが半導体チップや他のワイヤに接触したりして問題であるから、下側の半導体チップに中継端子を設け、上の半導体チップの電極パッドから対応するボンディングリードへの接続を、上の半導体チップの電極パッドからワイヤを中継端子に接続し、中継端子から対応するボンディングリードへ接続するようにした構造が示される。特に特許文献 1 ではスタックされた下の半導体チップの左右両側に中継端子を配置する構造では上にスタックされる半導体チップのサイズが制限されるので、一方の中継端子を無くし、中継端子を無くした側に偏倚させてその上に別半導体チップをスタックする構造を提案している。上の半導体チップを下の半導体チップの縁辺部分に近付けて偏倚することにより近付けられた側において上の半導体チップの電極パッドをモジュール基板のボンディングリードに接続するワイヤを直結可能な程度に短くすることができる。結果として、下にスタックされる半導体チップの一辺側から中継端子を省くことができ下にスタックされる半導体チップの小型化を実現することができる、とする。

20

【0003】

【特許文献 1】特開 2002-43503

【発明の開示】

【発明が解決しようとする課題】

【0004】

メモリコントローラのアドレス出力端子を構成する電極パッドと、メモリのアドレス入力端子を構成する電極パッドのように、機能上直結されてよい電極パッドに関しては、それぞれの電極パッドをボンディングリードに接続し、対応するボンディングリードをモジュール基板内配線で結合する構造を採用することができる。機能上直結されてよい電極パッドであってもその配置が互いに揃っていない場合に対処するためである。

30

【0005】

しかしながら、それではボンディングリードの数が増え、例えば 2 段に半導体チップがスタックされた場合、1 段目の半導体チップに対応するボンディングリード列と 2 段目に対応するボンディングリード列が、半導体チップの左右（又は周囲）にそれぞれ 2 列に配置されることになり、モジュール基板を小型化することが難しくなる。特許文献 1 の技術はスタックされた下の半導体チップに対して上の半導体チップを偏倚させて配置することにより下の半導体チップのサイズを小さくしようとするものであり、信号入出力機能上直結されてよい電極パッド間の相互接続の点でモジュール基板を小型化することに関する示唆は無い。

【0006】

40

1 段目の半導体チップを、その表面（電極パッド形成面）がモジュール基板の表面（ボンディングリード形成面）と対向するようにフリップチップ接続すれば、1 段目の半導体チップの電極パッドに対応した複数のボンディングリードが半導体チップの周囲ではなく、半導体チップの裏面下に配置することができるため、モジュール基板の小型化が可能である。しかしながら、フリップチップ接続を適用すると、ワイヤボンディング方式に比べ、製造コストが高くなってしまう。

【0007】

そこで、本発明者はスタックされた半導体チップ間で機能上直結されてよい電極パッドの配置がある程度揃っている場合に、そのような電極パッドを直結することについて検討した。直結することにより、モジュール基板上のボンディングリードの数を減らすことができると共に、モジュール基板内で対応するボンディングリード間を接続する配線を不要

にでき、モジュール基板の簡素化に資することができるからである。但し、ボンディングリードの数を減らすことができても、それによる空きスペースがモジュール基板上で分散していたのではモジュール基板の小型化に資することはできない。

【0008】

本発明の目的は、機能上直結されてよい電極パッド間の相互接続の点に関しモジュール基板の小型化に資することができる半導体装置を提供することにある。

【0009】

また、本発明の目的は、半導体装置の製造コストを低減することができる技術を提供することにある。

【0010】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

10

【課題を解決するための手段】

【0011】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0012】

〔1〕本発明に係る半導体装置(4)は、モジュール基板(3)、第1半導体チップ(1)及び第2半導体チップ(2)を有する。モジュール基板は、第1辺(301)に沿って配置された複数の第1ボンディングリード(303)と、前記第1ボンディングリードよりも第1辺寄りに離間して当該第1辺に沿って配置された複数の第2ボンディングリード(302)と、前記第1辺に対向する第2辺(306)に沿って配置された複数の第3ボンディングリード(307)とを有する。第1半導体チップは、集積された第1回路と、その第3辺(100)に沿って配置され前記第1回路に接続する複数の第1電極パッド(101)と、前記第3辺に対向する第4辺(104)に沿って配置され前記第1回路に接続する複数の第2電極パッド(105)とを有し、前記モジュール基板の上に搭載される。第2半導体チップは、集積された第2回路と、その第5辺(200)に沿って配置され前記第2回路に接続する複数の第3電極パッド(201)と、前記第5辺に対向する第6辺(204)に沿って配置され前記第2回路に接続する複数の第4電極パッド(205)とを有し、前記第1半導体チップの上に搭載される。それぞれ対応する前記第1ボンディングリードと前記第1電極パッドは第1ワイヤ(502)によって電気的に接続される。それぞれ対応する前記第2ボンディングリードと前記第3電極パッドは第2ワイヤ(501)によって電気的に接続される。それぞれ対応する前記第3ボンディングリードと前記第2電極パッドは第3ワイヤ(507)によって電気的に接続される。それぞれ対応する前記第4電極パッドは第4ワイヤ(500)によって電気的に接続される。前記第3辺及び前記第5辺は前記第1辺寄りに配置され、前記第4辺及び前記第6辺は前記第2辺寄りに配置され、前記第1辺と第3辺の間隔は前記第2辺と第4辺の間隔よりも大きくされる。

20

【0013】

上記した手段によれば、第4ワイヤによって直結される第2電極パッド及び第4電極パッドは第1半導体チップ及び第2半導体チップの同じ側の縁辺部分に集約され、モジュール基板の第2辺(306)に沿って配置された複数のボンディングリードからは第2電極パッドと第4電極パッドとを接続するためのボンディングリードを無くすことができる。したがってその部位に集中してボンディングリードの数を減らすことが可能になる。直結によって得られる空きスペースは分散されずモジュール基板の第2辺に集中される。この結果、第2辺に沿って配置されるボンディングリードは複数列から1列に集約することができる。その第2辺寄りに第1及び第2半導体チップを偏倚させて配置するから、モジュール基板の第1辺側にはスペース的に大きな余裕ができ、数多くのボンディングリードを配置することができになり、モジュール基板の製造容易化とモジュール基板の小型化の実現に資することができる。仮に、モジュール基板の第2辺寄りに第1及び第2半導体

30

40

50

チップを偏倚させなければ、モジュール基板の第1辺側には相対的に高密度で数多くのボンディングリードを配置し、モジュール内配線を形成しなければならず、モジュール基板の製造が難しくなり、その小型化が制限される。

#### 【0014】

また、第1及び第2半導体チップのそれぞれは、複数のボンディングワイヤを介してモジュール基板上に設けられた複数のボンディングリードと電気的に接続するため、半導体装置の製造コストを低減することができる。

#### 【0015】

本発明の一つの具体的な形態として、前記第3辺と第5辺の間隔と前記第4辺と第6辺の間隔は等しくされる。第1半導体チップと第2半導体チップのスタックについては従来手法と同様にチップ中心を合わせて容易にスタックすることができる。10

#### 【0016】

本発明の別の具体的な形態として、前記第4ワイヤを共有する前記第2電極パッドと前記第4電極パッドは相互に一方が出力端子であり、他方が入力端子である。異なる半導体チップ間における代表的な直結端子の相互関係とされる。

#### 【0017】

本発明の別の具体的な形態として、前記第3ボンディングリードの数は前記第1ボンディングリードの数よりも少ない。モジュール基板の第1辺側のスペース的な余裕を更に大きくすることができる。

#### 【0018】

〔2〕本発明に係る半導体装置(4)は、モジュール基板(3)と、前記モジュール基板との間で相互に中心位置を左右に偏倚させて当該モジュール基板の上に搭載され第1回路が集積された第1半導体チップ(1)と、前記第1半導体チップの上に搭載され第2回路が集積された第2半導体チップ(2)と、を備える。前記偏倚された前記第1半導体チップの端縁からモジュール基板の端縁までの距離が短い方では相互に対応する前記第1半導体チップ上の電極パッド(105)と前記第2半導体チップ上の電極パッド(20)がワイヤ(500)で直結される。前記偏倚された前記第1半導体チップの端縁からモジュール基板の端縁までの距離が長い方では前記第1半導体チップ上の電極パッド(101)及び前記第2半導体チップ上の電極パッド(201)が前記モジュール基板上の対応するボンディングリード(303, 302)にワイヤ(502, 501)で結合される。20

#### 【0019】

上記した手段によれば、モジュール基板上ではワイヤで直結された電極パッドが配置された側に半導体チップが偏倚されているから、半導体チップを挟んで反対側にはモジュール基板上にスペース的に大きな余裕ができ、数多くのボンディングリードを配置することが容易になり、モジュール基板の製造容易化とモジュール基板の小型化の実現に資することができる。

#### 【0020】

本発明の一つの具体的な形態として、前記偏倚された前記第1半導体チップの端縁からモジュール基板の端縁までの距離が短い方では相互に対応する前記第1半導体チップ上の電極パッドと前記モジュール基板上のボンディングリードがワイヤで結合される。前記偏倚された前記第1半導体チップの端縁からモジュール基板の端縁までの距離が短い方では全てを第1半導体チップの電極パッドと第2半導体チップの電極パッドとの直結に割り当てなくともよいという意味で自由度が増す。40

#### 【発明の効果】

#### 【0021】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

#### 【0022】

すなわち、機能上直結されてよい電極パッド間の相互接続の点に関し半導体装置のモジュール基板を小型化することができる。50

## 【0023】

また、半導体装置の製造コストを低減することができる。

## 【発明を実施するための最良の形態】

## 【0024】

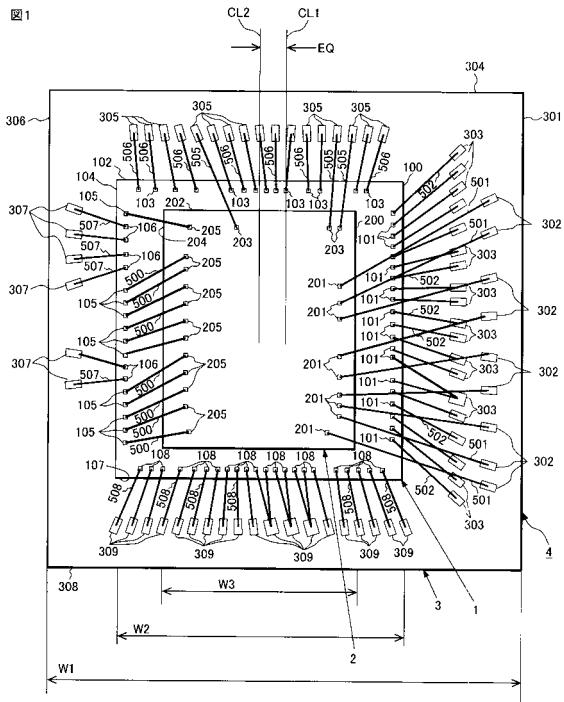

図1には本発明に係る半導体装置の一例が平面的に示される。同図に示される半導体装置4はモジュール基板(配線基板)3に第1半導体チップ1と第2半導体チップ2をスタックして構成されたSIP構造を有する。

## 【0025】

第2半導体チップ2は例えばCCDカメラに駆動電圧を出力するドライバであり、第1半導体チップ1はCCDカメラの動作を制御するタイミング制御信号等を生成するタイミングコントローラである。ドライバはタイミングコントローラが生成するタイミング制御信号の一部を入力して駆動信号をCCDカメラに供給する。

10

## 【0026】

矩形の第1半導体チップ1上にスタックされた矩形の第2半導体チップ2は辺(第5辺)200に沿って配置された複数の電極パッド(第3電極パッド)201を有し、辺202に沿って配置された複数の電極パッド203を有し、辺(第6辺)204に沿って配置された複数の電極パッド(第4電極パッド)205を有する。電極パッド205は第1の半導体チップ1とインターフェースされ、例えばタイミング制御信号を入力し或いは応答信号を出力する機能が割り当てられる。特に図示はしないが、第2半導体チップ2はその機能を実現するための内部回路(第2回路)として電圧生成回路及び出力回路等を備える。前記電極パッド201、203、及び205は半導体チップ2の内部に形成された内部回路の所定ノードに配線層を介して結合されている。

20

## 【0027】

矩形の第1半導体チップ1は辺(第3辺)100に沿って配置された複数の電極パッド(第1電極パッド)101を有し、辺102に沿って配置された複数の電極パッド103を有し、辺(第4辺)104に沿って配置された複数の電極パッド(第2電極パッド)105、106を有し、辺107に沿って複数の電極パッド108を有する。電極パッド105は第2半導体チップ2の対応する電極パッド205にボンディングワイヤ(第4ワイヤ)500で結合される。特に図示はしないが、第1半導体チップ1はその機能を実現するための内部回路(第1回路)としてタイミング制御のためのシーケンサ若しくはプログラム制御回路、並びに周辺回路等を備える。前記電極パッド101、103、105、106、及び108は半導体チップ2の内部に形成された内部回路の所定ノードに配線層を介して結合されている。特に制限されないが、第1半導体チップはアナログ信号の入出力インターフェース回路(例えばアナログ・デジタル変換回路)を有しており、当該アナログ入出力インターフェース回路に接続する電極パッドはデジタル信号との混在を極力割けるために例えば辺107に沿った電極パッド108に集約されている。

30

## 【0028】

モジュール基板3は、例えば配線層を有するガラスエポキシ樹脂製の矩形の配線基板により構成され、裏面には例えば多数のボール電極がアレイ状に配置され、表面には辺(第1辺)301に沿って外側より複数のボンディンググリード(第2ボンディンググリード)302と複数のボンディンググリード(第1ボンディンググリード)303が2列形成され、更に、辺304に沿った複数のボンディンググリード305の1列と、辺(第2辺)306に沿った複数のボンディンググリード(第3ボンディンググリード)307の1列と、辺308に沿った複数のボンディンググリード309の1列が形成される。前記ボンディンググリード302は第2半導体チップ2の電極パッド201にボンディングワイヤ(第2ワイヤ)501で結合される。前記ボンディンググリード303は第1半導体チップ1の電極パッド101にボンディングワイヤ(第1ワイヤ)502で結合される。前記ボンディンググリード305は第2半導体チップ2の対応する電極パッド203にボンディングワイヤ505で結合され、また、第1半導体チップ1の対応する電極パッド103にボンディングワイヤ506で結合される。前記ボンディンググリード307は第1半導体チップ1の電極パッド

40

50

106 にポンディングワイヤ (第3ワイヤ) 507 で結合される。前記ポンディングリード 309 は第1半導体チップ1の電極パッド 108 にポンディングワイヤ 508 で結合される。特に図示はしないが、各々のポンディングリード 302, 305, 307, 309 はスルーホールや配線を介して対応する前記ボール電極に接続されている。モジュール基板 304 の表面上において前記第1半導体チップ1、第2半導体チップ2、及びポンディングワイヤ 500, 501, 502, 505, 506, 507, 508 は樹脂で封止されて保護されている。

【0029】

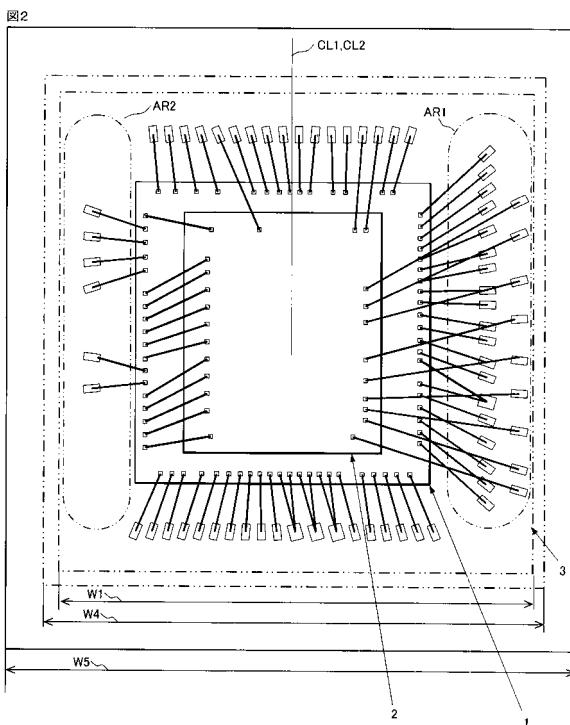

CL1 はモジュール基板 3 の中心線、CL2 は半導体チップ1, 2 の中心線である。図より明らかなように半導体チップ1, 2 はその中心線を合わせてスタックされ、スタックされた半導体チップ1, 2 はモジュール基板 4 の中心線 CL1 に対して左側に偏倚 (偏心) されてスタックされている。その偏倚量は EQ である。ワイヤポンディングにおいては隣り合うワイヤが接触しないことが必要であるから、隣接するポンディングリード間には規定の最小ピッチが確保されなければならない。したがって、スタックされた半導体チップ1, 2 をモジュール基板 4 の中心線 CL1 に対して左側に偏倚させてスタックすることにより、配置スペースが限られたモジュール基板 3 上においてポンディングリード 302, 303 を2列で配置しなければならない領域にはスペース的な余裕が生まれ、反対側でポンディングリード 307 を1列配置すればよい領域には無駄な空きスペースを生ぜず、結果として、モジュール基板 3 の小型化の実現に資することができる。図2に示される第1の比較例のように、モジュール基板 3 の中心線 CL1 と、半導体チップ1, 2 の中心線 CL2 を合わせてスタックすると。モジュール基板 3 上における半導体チップ1の左右の領域 AR1, AR2 は面積が同じになり、領域 AR1 に2列のポンディングリードを配置してモジュール基板を形成することは実質的に不可能になり、少なくとも幅 W4 (W1 < W4) でモジュール基板を形成しなければならなくなる。実際にはコスト若しくは標準化との関係で任意サイズのモジュール基板を採用することは難しい。規格化されたジユール基板サイズに W4 が無ければ、それよりも大きな寸法 W5 のモジュール基板サイズを採用しなければならなくなり、コスト的にも面積的にも大きな無駄を生ずる虞がある。図1の半導体装置4の大きさに関し、例えば前記第1半導体チップ1の幅寸法を W2 = 3.68 mm、第2半導体チップ2の幅寸法を W3 = 2.4 mm とするとき、偏倚量を EQ = 0.32 mm とすることによって、幅寸法 W1 = 6 mm のモジュール基板 3 を採用することができた。これに対し、図2の比較例の場合には例えば幅寸法 W5 = 8 mm のモジュール基板を採用することが必要になる。

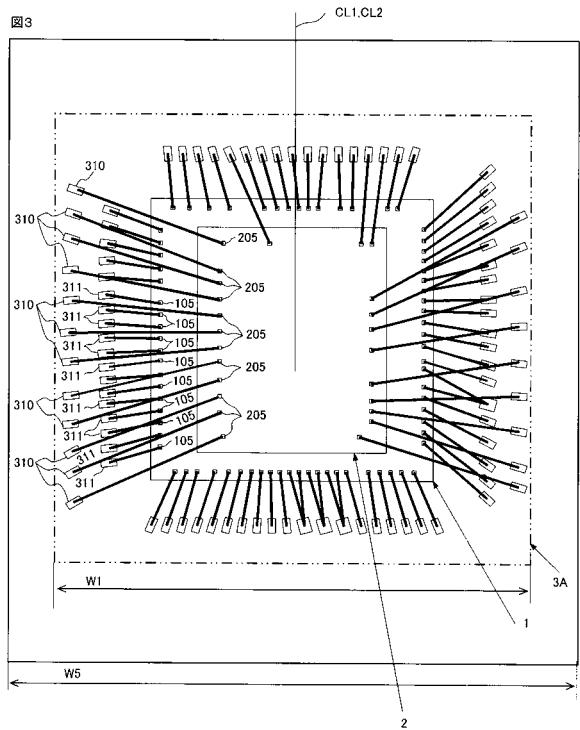

【0030】

図1の例では第1半導体チップ1の電極パッド 105 と第2半導体チップ2の電極パッド 205 は相互に一方が出力端子、他方が入力端子であり、機能上直結可能な端子である。図1ではそれぞれの半導体チップ1, 2 におけるそれら電極パッド 105, 205 を相互に同じ側の辺 (本発明では、例えばモジュール基板の第2辺側) に来るよう集約することにより、ワイヤ 500 で直結可能な配置としたものである。第1半導体チップ1の電極パッド 105 と第2半導体チップ2の電極パッド 205 を直結する考慮を払わない場合には、図3の第2の比較例に示されるように、第1半導体チップ1の電極パッド 105 と第2半導体チップ2の電極パッド 205 をそれぞれ対応するポンディングリード 311, 310 にワイヤで個別に結合しなければならない。モジュール基板にはポンディングリード 310 と 311 を対応するもの同士で接続するモジュール内配線が形成されなければならない。図3の場合にはモジュール基板 3A 内配線が複雑になるだけでなく、モジュール基板 3A の左右それぞれポンディングリードを2列ずつ配置しなければならないから、図2の比較例と同様に W5 のような大きなサイズのモジュール基板を採用しなければならなくなる。図2及び図3の比較例より明らかなように、異なる半導体チップ1, 2 間で機能上直結可能な電極パッド 105, 205 をワイヤ 500 で直結する考慮を払っただけでは図2の構成に止み、往々にしてサイズの小さなモジュール基板を採用することは難しく、更なるステップとして、モジュール基板とスタックされた半導体チップ1, 2 を相互に中

10

20

30

40

50

心位置を左右に偏倚させて積み重ねるという手段を講じて始めてサイズの小さなモジュール基板を採用することが可能になる。

#### 【0031】

次に、本発明の半導体装置4の製造方法について図4に示すフローチャートに沿って説明する。

#### 【0032】

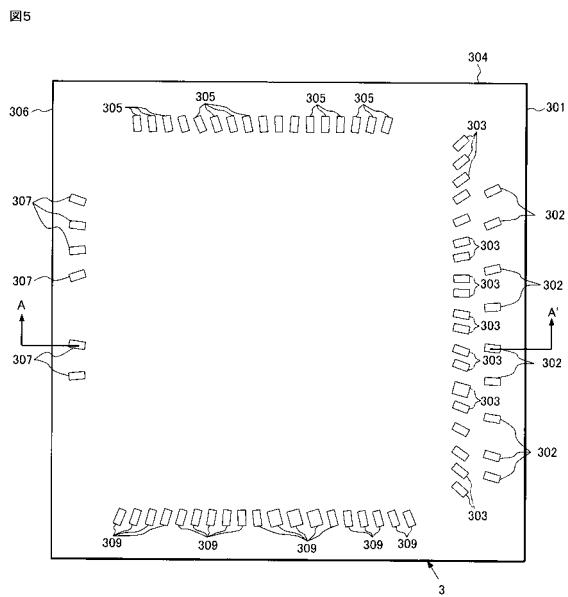

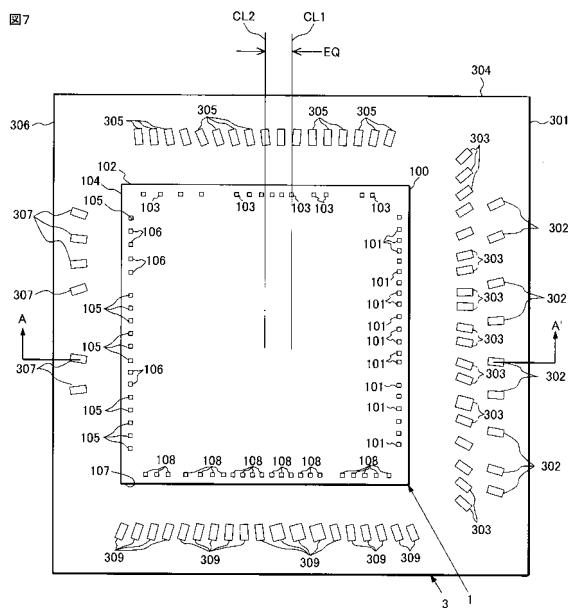

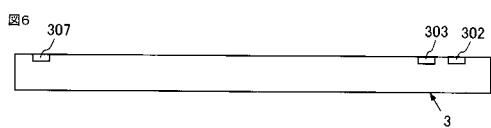

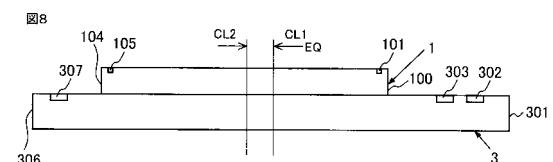

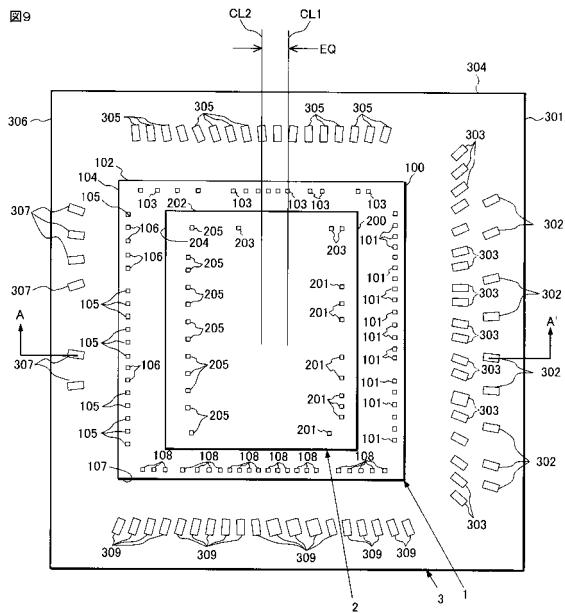

まず、図4のステップS1では、図5及び図6に示すモジュール基板3を準備する。モジュール基板3は、その表面(正面)上において複数の辺301, 304, 306, 308に沿って複数のボンディングリード302, 303, 305, 307, 309がそれぞれ形成されている。

10

#### 【0033】

次に、図4のステップS2では、図7及び図8に示すように、モジュール基板3の表面上に、接着材(図示しない)を介して第1半導体チップ1を実装する。第1半導体チップ1の正面には集積された内部回路(第1回路)が形成されている。また、配線層を介して内部回路と電気的に接続された複数の電極パッド101、103、105、106、108は、第1半導体チップ1の複数の辺100、102、104、107に沿ってそれぞれ形成されている。また、第1半導体チップ1は、その中心線CL2がモジュール基板の中心線CL1からずらした位置、すなわち、モジュール基板3の第1辺301と第1半導体チップ1の第3辺100との間隔が、モジュール基板3の第2辺306と第1半導体チップ1の第4辺104との間隔よりも大きくなるように、第1半導体チップ1の中心線CL2をモジュール基板3の第2辺側に偏倚させて実装している。

20

#### 【0034】

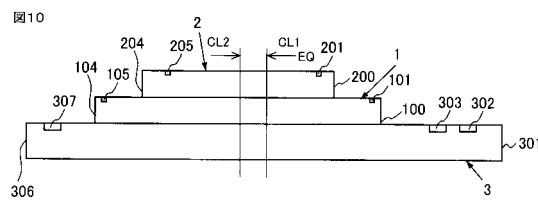

次に、図4のステップS3では、図9及び図10に示すように、第1半導体チップ1上に、接着材(図示しない)を介して第2半導体チップ2を実装する。第2半導体チップ2の正面には集積された内部回路(第2回路)が形成されている。また、配線層を介して内部回路と電気的に接続された複数の電極パッド201、203、205は、第2半導体チップ2の複数の辺200、202、204に沿ってそれぞれ形成されている。また、第2半導体チップ2は、その中心線CL2がモジュール基板の中心線CL1からずらした位置、言い換えると、第1半導体チップ1の中心線CL2と重なるように、第1半導体チップ1上に実装している。このように、2段目以降に半導体チップ2を積層する場合は、それぞれの半導体チップ1, 2の中心線を位置合わせの目印として、上段側の半導体チップの中心線が下段側の半導体チップの中心線と重なるように積層することで、組立性を容易にすることができます。

30

#### 【0035】

その後、図4のステップS4に示すように、第1及び第2半導体チップ1, 2を実装したモジュール基板3を、熱雰囲気中でベーク処理することで、上記接着剤を硬化させる。

#### 【0036】

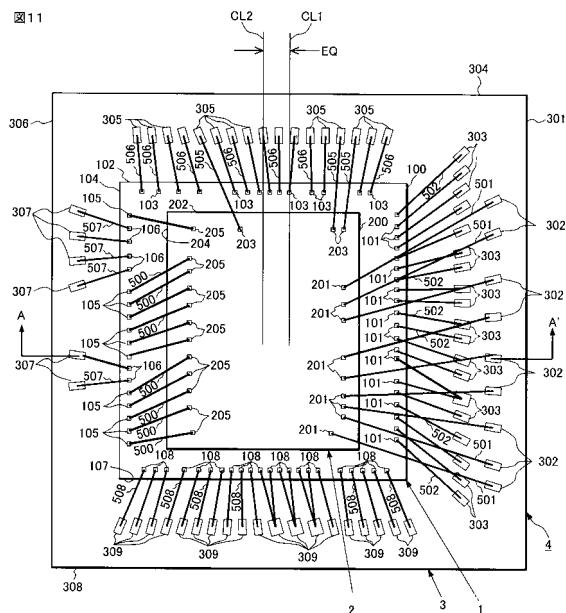

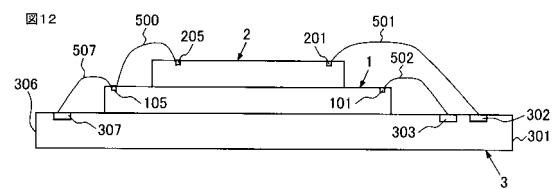

次に、図4のステップS5、ステップS6では、図11及び図12に示すように、第1半導体チップ1の複数の電極パッド101、103、105、106、108とモジュール基板3の複数のボンディングリード303、305、307、309を導電性部材からなる複数のボンディングワイヤ502, 506, 507, 508を介してそれぞれ電気的に接続する。その後、第2半導体チップ2の複数の電極パッド201、203とモジュール基板3の複数のボンディングリード302, 305を導電性部材からなる複数のボンディングワイヤ501, 505でそれぞれ電気的に接続し、また第2半導体チップ2の複数の電極パッド205と第1半導体チップ1の複数の電極パッド105を導電性部材からなる複数のボンディングワイヤ500でそれぞれ電気的に接続する。上段側の半導体チップ2とモジュール基板3とのワイヤボンディングを行ってから下段側の半導体チップ1とモジュール基板3とのワイヤボンディングを行うと、先に形成されたワイヤとワイヤボンディングツールであるキャピラリの先端が接触してしまい、断線不良を引き起こす虞がある。そこで、本発明のように、下段側の半導体チップ1とモジュール基板3とのワイヤボン

40

50

ディングを行った後に、上段側の半導体チップ2とモジュール基板3とのワイヤボンディングを行うことで、ワイヤとキャピラリの接触を抑制することができる。これは、後に形成するワイヤのループ形状が先に形成したワイヤのループ形状よりも上方に位置するためである。

【0037】

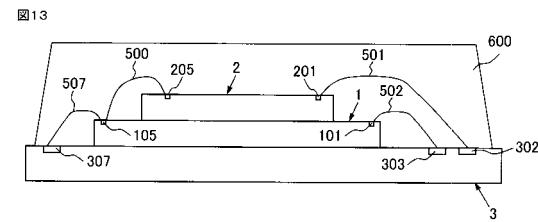

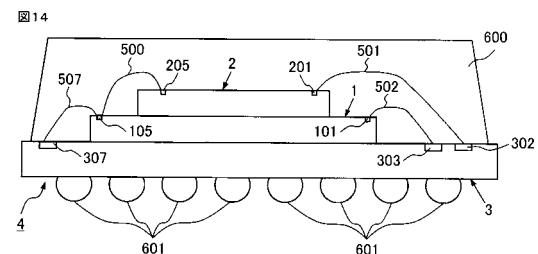

次に、図4のステップS7では図13に示すように、モジュール基板3の表面側、第1半導体チップ1、第2半導体チップ2、および複数のボンディングワイヤ500、501、502、505、506、507、508を樹脂600で封止し、封止体を形成する。

【0038】

その後、図4のステップS8では、図14に示すように、モジュール基板3の裏面側に多数のボール電極601を形成する。多数のボール電極601は、図示しないが、モジュール基板3の内層に設けられた配線層を介して表面上に形成されている複数のボンディンググリード302、303、305、307、309とそれぞれ電気的に接続されている。

【0039】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0040】

例えば第1及び第2半導体チップはCCDカメラのタイミングコントローラとドライバに限定されず、液晶ディスプレイのドライバと表示コントローラ、メモリとメモリコントローラ、マイクロコンピュータとワークメモリ等のその他の組合せであってもよい。半導体チップの内部回路は当該半導体チップの機能に応じてその回路構成が決定されればよい。

【0041】

また、例えば個別モールド方式により樹脂封止されることに限定されず、複数の製品形成領域を有するモジュール基板上に複数の半導体チップをそれぞれ実装した後、一括モールド方式(MAP)により複数の製品形成領域を一括して樹脂封止してもよい。その場合は、個片化工程において例えばダイシングブレードにより複数の製品形成領域が切断、分離されるため、取得される半導体装置の封止体の端部は、モジュール基板の端部と同じ位置に形成される。

【図面の簡単な説明】

【0042】

【図1】本発明に係る半導体装置の一例を示す平面図である。

【図2】モジュール基板に対して半導体チップを偏倚させずにスタックした第1の比較例に係る半導体装置を示す平面図である。

【図3】スタックされた半導体装間で機能上直結可能な電極パッドを個別にモジュール基板のボンディンググリードに接続し、対応するそれらボンディンググリードをモジュール基板内の配線を用いて相互に接続するようにした第2の比較例に係る半導体装置を示す平面図である。

【図4】本発明の半導体装置の製造工程を示すフローチャートである。

【図5】本発明のモジュール基板の模式的平面図である。

【図6】図5のA-A'線に沿う模式的断面図である。

【図7】第1半導体チップをモジュール基板上に実装した模式的平面図である。

【図8】図7のA-A'線に沿う模式的断面図である。

【図9】第2半導体チップを第1半導体チップ上に実装した模式的平面図である。

【図10】図9のA-A'線に沿う模式的断面図である。

【図11】第1及び第2半導体チップのそれぞれとモジュール基板をワイヤボンディングした模式的平面図である。

【図12】図11のA-A'線に沿う模式的断面図である。

【図13】モジュール基板上に封止体を形成した図11のA-A'に沿う模式的断面図で

10

20

30

40

50

ある。

【図14】モジュール基板の裏面に多数のボール電極が配置された図11のA-A'線に沿う模式的断面図である。

【符号の説明】

【0043】

1 第1半導体チップ

2 第2半導体チップ

3 モジュール基板

4 半導体装置

100、102、104、107 第1半導体チップの辺

10

101、103、105、106、108 第1半導体チップの電極パッド

200、202、204 第2半導体チップの辺

201、203、205 第2半導体チップの電極パッド

301、304、306、308 モジュール基板の辺

302、303、305、307、309 モジュール基板のボンディンググリード

500、501、502、505、506、507、508 ボンディングワイヤ

CL1 モジュール基板の中心線

CL2 半導体チップの中心線

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開2002-043503(JP,A)

特開2002-373968(JP,A)

特開2002-057270(JP,A)

特表2008-515203(JP,A)

国際公開第2006/037056(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 25/065

H01L 25/07

H01L 25/18

H01L 21/60