등록특허 10-2697457

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년08월22일

(11) 등록번호 10-2697457

(24) 등록일자 2024년08월16일

- (51) 국제특허분류(Int. Cl.)

*H10K 50/80* (2023.01) *H10K 59/00* (2023.01)

*H10K 71/00* (2023.01)

- (52) CPC특허분류

*H10K 50/84* (2023.02)

*H10K 59/12* (2023.02)

- (21) 출원번호 10-2018-0121197

- (22) 출원일자 2018년10월11일

심사청구일자 2021년10월08일

- (65) 공개번호 10-2020-0041420

- (43) 공개일자 2020년04월22일

- (56) 선행기술조사문현

JP2016219125 A\*

(뒷면에 계속)

전체 청구항 수 : 총 39 항

심사관 : 신재경

## (54) 발명의 명칭 표시 패널

**(57) 요 약**

본 발명의 일 실시예는 개구를 둘러싸는 표시영역 상에 배치되며, 화소전극, 화소전극 상의 발광층, 발광층 상의 대향전극을 각각 구비하는 복수의 표시소자들; 개구와 표시영역 사이에 위치하는 그루브;를 포함하며, 그루브는 제1층 및 제1층 위의 제2층을 포함하는 다층 막의 두께 방향을 따라 오목한 언더컷 단면을 가지며, 제2층은 그루브의 중심을 향해 돌출된 한 쌍의 텁을 포함하며, 텁 각각의 길이는  $2\mu\text{m}$  보다 작은, 표시 패널을 개시한다.

대 표 도 - 도8a

(52) CPC특허분류

*H10K 59/351* (2023.02)

*H10K 71/00* (2023.02)

(72) 발명자

**김수연**

경기도 용인시 기흥구 삼성로 1 (농서동)

**서정한**

경기도 용인시 기흥구 삼성로 1 (농서동)

**이서연**

경기도 용인시 기흥구 삼성로 1 (농서동)

**이형섭**

경기도 용인시 기흥구 삼성로 1 (농서동)

**장문원**

경기도 용인시 기흥구 삼성로 1 (농서동)

**채승근**

경기도 용인시 기흥구 삼성로 1 (농서동)

(56) 선행기술조사문헌

KR1020170059864 A\*

KR1020180002126 A\*

KR1020170115177 A

KR1020170135587 A

\*는 심사관에 의하여 인용된 문헌

## 명세서

### 청구범위

#### 청구항 1

개구를 둘러싸는 표시영역 상에 배치되며, 화소전극, 상기 화소전극 상의 발광층, 상기 발광층 상의 대향전극을 각각 구비하는 복수의 표시소자들; 및

상기 개구와 상기 표시영역 사이에 위치하는 그루브;

를 포함하며,

상기 그루브는 제1층 및 상기 제1층 위의 제2층을 포함하는 다층 막의 두께 방향을 따라 오목한 언더컷 단면을 가지고,

상기 제2층은 상기 그루브의 중심을 향해 돌출된 한 쌍의 팁을 포함하며, 상기 팁 각각의 길이는  $0.3\mu\text{m}$  이거나 그보다 크고  $2\mu\text{m}$  보다 작으며,

상기 화소전극과 상기 대향전극 사이에 개재되는 기능층은 상기 복수의 표시소자들에서 공유되며, 상기 기능층은 상기 개구와 상기 표시영역 사이에서 상기 팁 상에 배치된 제1부분 및 상기 제1부분과 분리되며 상기 그루브의 바닥면 상에 배치된 제2부분을 포함하고,

상기 대향전극은 상기 복수의 표시소자들에서 공유되며, 상기 대향전극은 상기 개구와 상기 표시영역 사이에서 상기 기능층의 상기 제1부분 상에 위치하는 제3부분 및 상기 제3부분과 분리되며 상기 그루브의 상기 바닥면과 대응하도록 상기 기능층의 상기 제2부분 상에 위치하는 제4부분을 포함하는, 표시 패널.

#### 청구항 2

삭제

#### 청구항 3

제1항에 있어서,

상기 제1층은 유기물을 포함하며, 상기 제2층은 무기물을 포함하는, 표시 패널.

#### 청구항 4

제3항에 있어서,

상기 제2층은 무기질연층 또는 금속을 포함하는, 표시 패널.

#### 청구항 5

제1항에 있어서,

상기 그루브는,

상기 제1층의 제1홀 또는 제1리세스; 및

상기 제2층의 제2홀;을 포함하며,

상기 제2홀은 상기 제1홀 또는 상기 제1리세스와 연결되는, 표시 패널.

#### 청구항 6

제5항에 있어서,

상기 한 쌍의 팁 사이의 거리는, 상기 제1홀 또는 상기 제1리세스의 깊이 보다 큰, 표시 패널.

#### 청구항 7

제5항에 있어서,

상기 제1홀 또는 상기 제1리세스의 깊이는, 상기 텁 각각의 길이 보다 큰, 표시 패널.

#### 청구항 8

제7항에 있어서,

상기 제1홀 또는 상기 제1리세스의 깊이에 대한 상기 텁 각각의 길이는,  $0.05 < (\ell / dp) < 0.50$ 인, 표시 패널.

여기서,  $\ell$ 은 상기 텁 각각의 길이를,  $dp$ 는 상기 제1홀 또는 상기 제1리세스의 깊이를 나타낸다.

#### 청구항 9

제5항에 있어서,

상기 제1홀 또는 상기 제1리세스의 깊이는, 상기 제1층의 두께와 같거나 그보다 작은, 표시 패널.

#### 청구항 10

제5항에 있어서,

상기 기능층은,

상기 화소전극과 상기 발광층 사이의 제1기능층, 및 상기 발광층과 상기 대향전극 사이의 제2기능층 중 적어도 어느 하나를 포함하고,

상기 제1홀 또는 상기 제1리세스의 깊이는, 상기 기능층의 상기 제2부분의 두께, 및 상기 대향전극의 상기 제4부분의 두께의 합 보다 큰, 표시 패널.

#### 청구항 11

제10항에 있어서,

상기 대향전극 위의 캡핑층을 더 포함하되, 상기 캡핑층은 상기 대향전극의 상기 제3부분 상의 제5부분 및 상기 제5부분과 분리되고 상기 대향전극의 상기 제4부분 상의 제6부분을 포함하고,

상기 제1홀 또는 상기 제1리세스의 깊이는,

상기 기능층의 상기 제2부분의 두께, 및 상기 대향전극의 상기 제4부분의 두께, 및 상기 캡핑층의 상기 제6부분의 두께의 합 보다 큰, 표시 패널.

#### 청구항 12

제1항에 있어서,

기판, 및 상기 기판 상에 배치되며 상기 화소전극과 전기적으로 연결된 박막트랜지스터를 구비하는 화소회로를 더 포함하는, 표시 패널.

#### 청구항 13

제12항에 있어서,

상기 기판은 상기 다층 막을 포함하는, 표시 패널.

#### 청구항 14

제12항에 있어서,

상기 다층 막은 상기 기판 위에 위치하는, 표시 패널.

#### 청구항 15

개구를 둘러싸는 표시영역에 위치하며, 각각 화소전극, 발광층 및 대향전극을 포함하는, 복수의 표시요소들; 및

상기 개구와 상기 표시영역 사이에 위치하며, 언더컷 단면을 갖는 그루브;를 포함하며,

상기 그루브는, 제1층 및 상기 제1층 위의 제2층을 포함하는 다층 막의 두께 방향을 따라 형성되며,

상기 제2층은 상기 그루브의 중심을 향해 돌출된 한 쌍의 팁을 포함하고,

상기 그루브 중 상기 제1층을 지나는 부분의 깊이는, 상기 한 쌍의 팁 각각의 길이 보다 크고,

상기 팁 각각의 길이는  $0.3\mu m$  이거나 그보다 크고  $2\mu m$  보다 작으며,

상기 화소전극과 상기 대향전극 사이에 개재되는 기능층은 상기 복수의 표시요소들에서 공유되되, 상기 한 쌍의

팁 각각의 상면 상에 배치된 제1부분 및 상기 제1부분과 분리되며 상기 그루브의 바닥면 상에 배치된 제2부분을

포함하고,

상기 대향전극은 상기 복수의 표시요소들에서 공유되되, 상기 기능층의 상기 제1부분 상에 위치하는 제3부분 및

상기 제3부분과 분리되며 상기 그루브의 상기 바닥면에 대응하도록 상기 기능층의 상기 제2부분 상에 위치하는

제4부분을 포함하는 표시 패널.

### 청구항 16

삭제

### 청구항 17

제15항에 있어서,

상기 깊이는 상기 제1층의 두께와 같거나 그보다 작은, 표시 패널.

### 청구항 18

제17항에 있어서,

상기 한 쌍의 팁 사이의 거리는 상기 깊이 보다 큰, 표시 패널.

### 청구항 19

제15항에 있어서,

상기 깊이에 대한 상기 팁 각각의 길이는,  $0.05 < (\ell / dp) < 0.50$ 인, 표시 패널.

여기서,  $\ell$ 은 상기 팁 각각의 길이를,  $dp$ 는 상기 깊이를 나타낸다.

### 청구항 20

제15항에 있어서,

상기 화소전극과 상기 발광층 사이의 제1기능층, 및 상기 발광층과 상기 대향전극 사이의 제2기능층 중 적어도

어느 하나를 더 포함하고,

상기 깊이는, 상기 기능층의 상기 제2부분의 두께, 및 상기 대향전극의 상기 제4부분의 두께의 합 보다 큰, 표

시 패널.

### 청구항 21

제20항에 있어서,

상기 대향전극 위의 캡핑층을 더 포함하고, 상기 캡핑층은 상기 대향전극의 상기 제3부분 상의 제5부분 및 상기

제5부분과 분리되고 상기 대향전극의 상기 제4부분 상의 제6부분을 포함하며,

상기 깊이는, 상기 기능층의 상기 제2부분의 두께, 및 상기 대향전극의 상기 제4부분의 두께, 및 상기 캡핑층의

상기 제6부분의 두께의 합 보다 큰, 표시 패널.

### 청구항 22

제15항에 있어서,

상기 깊이는  $2\mu m$  이거나 그보다 큰, 표시 패널.

### 청구항 23

제15항에 있어서,

기판, 및 상기 기판 상에 위치하며, 상기 화소전극과 전기적으로 연결된 박막트랜지스터를 구비하는 화소회로를 더 포함하는, 표시 패널.

### 청구항 24

제23항에 있어서,

상기 기판은 상기 다층 막을 포함하는, 표시 패널.

### 청구항 25

제23항에 있어서,

상기 다층 막은 상기 기판 위에 위치하는, 표시 패널.

### 청구항 26

개구를 포함하는 기판;

상기 개구를 둘러싸는 표시영역에 배치된 복수의 화소전극들;

상기 복수의 화소전극들 상에 배치되는 대향전극;

상기 복수의 화소전극들과 상기 대향전극 사이에 개재되는 기능층;

제1무기봉지층, 상기 제1무기봉지층 상의 유기봉지층, 및 상기 유기봉지층 상의 제2무기봉지층을 포함하고, 상기 대향전극 상에 배치되는 봉지층; 및

상기 개구와 상기 표시영역 사이에 배치된 다층 구조;를 포함하고,

상기 다층 구조는,

제1층; 및

상기 제1층 상의 제2층을 포함하고,

상기 제2층은 상기 제1층의 측면과 상기 제2층의 바닥면이 만나는 지점을 넘어 상기 기판의 상면과 평행한 수평 방향으로 돌출된 텁을 포함하고, 상기 텁의 길이는  $0.3\mu m$  이거나 그보다 크고  $2\mu m$  보다 작고, 여기서 상기 텁의 길이는 상기 지점과 상기 텁의 측면 사이의 거리를 나타내며,

상기 다층 구조는 상기 다층 구조의 두께 방향을 따라 오목한 그루브를 포함하고,

상기 개구와 상기 표시영역 사이에서, 상기 기능층은 상기 텁 상에 배치된 제1부분 및 상기 제1부분과 분리되며 상기 그루브의 바닥면 상에 배치된 제2부분을 포함하고,

상기 개구와 상기 표시영역 사이에서, 상기 대향전극은 상기 기능층의 상기 제1부분 상에 위치하는 제3부분 및 상기 제3부분과 분리되며 상기 그루브의 상기 바닥면에 대응하도록 상기 기능층의 상기 제2부분 상에 위치하는 제4부분을 포함하는, 표시 패널.

### 청구항 27

제26항에 있어서,

상기 제1층의 물질은 상기 제2층의 물질과 상이한, 표시 패널.

### 청구항 28

제27항에 있어서,

상기 제2층은 금속층을 포함하는, 표시 패널.

### 청구항 29

제26항에 있어서,

상기 제2층의 두께는 상기 제1층의 두께 보다 작은, 표시 패널.

### 청구항 30

삭제

### 청구항 31

삭제

### 청구항 32

제26항에 있어서,

상기 제1층의 두께는 상기 기능층의 상기 제2부분 및 상기 대향전극의 상기 제4부분의 두께의 합 보다 큰, 표시 패널.

### 청구항 33

제26항에 있어서,

상기 제1무기봉지층은 상기 대향전극의 상기 제3부분 및 상기 대향전극의 상기 제4부분과 연속적으로 중첩하는, 표시 패널.

### 청구항 34

제33항에 있어서,

상기 제1무기봉지층은,

상기 텁의 상기 측면 및 바닥면, 그리고 상기 제1층의 상기 측면과 연속적으로 중첩하도록 연장된, 표시 패널.

### 청구항 35

제26항에 있어서,

상기 유기봉지층은 상기 텁에 의해 분리된 상기 기능층의 상기 제1부분과 상기 제2부분 및 상기 대향전극의 상기 제3부분과 상기 제4부분 각각에 중첩하는, 표시 패널.

### 청구항 36

제26항에 있어서,

상기 기능층은,

홀수송층(HTL), 홀주입층(HIL), 전자수송층(ETL), 및 전자주입층(HIL)에서 선택된 적어도 하나를 포함하는, 표시 패널.

### 청구항 37

개구를 포함하는 기판;

상기 개구를 둘러싸는 표시영역에 배열된 복수의 화소전극들;

상기 복수의 화소전극들 상에 배치되는 대향전극;

상기 복수의 화소전극들과 상기 대향전극 사이에 개재되는 기능층;

상기 대향전극 상의 봉지층; 및

상기 개구와 상기 표시영역 사이에 배치된 다층 구조;를 포함하고,

상기 다층 구조는,

제1층; 및

상기 제1층의 두께 보다 작고, 상기 제1층 상에 배치된 제2층;을 포함하고,

상기 제2층은 상기 제1층의 측면과 상기 제2층의 바닥면이 만나는 지점을 넘어 상기 기판의 상면과 평행한 수평 방향으로 돌출된 텁을 포함하고,

상기 텁의 길이는  $0.3\mu m$  이거나 그보다 크고  $2 \mu m$  보다 작고, 여기서 상기 텁의 길이는 상기 지점과 상기 텁의 측면 사이의 거리를 나타내며,

상기 다층 구조는 상기 다층 구조의 두께 방향을 따라 오목한 그루브를 포함하고,

상기 개구와 상기 표시영역 사이에서, 상기 기능층은 상기 텁 상에 배치된 제1부분 및 상기 제1부분과 분리되며 상기 그루브의 바닥면 상에 배치된 제2부분을 포함하고,

상기 개구와 상기 표시영역 사이에서, 상기 대향전극은 상기 기능층의 상기 제1부분 상에 위치하는 제3부분 및 상기 제3부분과 분리되며 상기 그루브의 바닥면에 대응하도록 상기 기능층의 상기 제2부분 상에 위치하는 제4부분을 포함하는, 표시 패널.

### 청구항 38

제37항에 있어서,

상기 제1층의 물질은 상기 제2층의 물질과 상이하고, 상기 제2층은 금속층을 포함하는, 표시 패널.

### 청구항 39

삭제

### 청구항 40

제37항에 있어서,

상기 대향전극은 상기 기능층의 상기 제1부분 상에 배치된 제3부분, 및 상기 제3부분과 분리되며 상기 기능층의 상기 제2부분 상에 배치된 제4부분을 포함하는, 표시 패널.

### 청구항 41

제40항에 있어서,

상기 제1층의 두께는 상기 기능층의 상기 제2부분의 두께 및 상기 대향전극의 상기 제4부분의 두께의 합 보다 큼, 표시 패널.

### 청구항 42

제40항에 있어서,

상기 봉지층은,

제1무기봉지층; 및

상기 제1무기봉지층 상의 유기봉지층;을 포함하고,

상기 제1무기봉지층은 상기 제2층의 상면에 위치하는 상기 기능층의 부분 및 상기 대향전극의 부분을 덮고, 상기 텁의 상기 측면과 바닥면 및 상기 제1층의 측면을 연속적으로 커버하도록 연장되는, 표시 패널.

### 청구항 43

제42항에 있어서,

상기 유기봉지층은 상기 텁에 의해 분리된 상기 기능층의 상기 제1부분과 상기 제2부분, 및 상기 대향전극의 상기 제3부분과 상기 제4부분 각각에 중첩하는, 표시 패널.

#### 청구항 44

제37항에 있어서,

상기 기능층은,

홀수송층(HTL), 홀주입층(HIL), 전자수송층(ETL), 및 전자주입층(HIL)에서 선택된 적어도 하나를 포함하는, 표시 패널.

#### 발명의 설명

#### 기술 분야

[0001]

본 발명의 실시예들은 그루브를 포함하는 표시 패널 및 표시 패널을 포함하는 표시 장치에 관한 것이다.

#### 배경 기술

[0002]

근래에 표시 장치는 그 용도가 다양해지고 있다. 또한, 표시 장치의 두께가 얇아지고 무게가 가벼워 그 사용의 범위가 광범위해지고 있는 추세이다.

[0003]

표시 장치 중 표시영역이 차지하는 면적을 확대하면서, 표시 장치에 접목 또는 연계하는 다양한 기능들이 추가되고 있다. 면적을 확대하면서 다양한 기능을 추가하기 위한 방안으로서 표시영역에 개구가 형성된 표시 장치의 연구가 계속되고 있다.

#### 발명의 내용

#### 해결하려는 과제

[0004]

개구를 구비하는 표시 장치의 경우, 개구의 측면으로 수분 등의 이물이 침투할 수 있으며, 이 경우 개구를 둘러싸는 표시요소들을 손상시킬 수 있다. 본 발명은 상기와 같은 문제점을 포함하여 여러 문제점들을 해결하기 위한 것으로서, 개구를 통한 투습을 방지할 수 있는 구조의 표시 패널 및 이를 구비한 표시 장치를 제공한다. 그러나 이러한 과제는 예시적인 것으로, 이에 의해 본 발명의 범위가 한정되는 것은 아니다.

#### 과제의 해결 수단

[0005]

본 발명의 일 실시예는, 개구를 둘러싸는 표시영역 상에 배치되며, 화소전극, 상기 화소전극 상의 발광층, 상기 발광층 상의 대향전극을 각각 구비하는 복수의 표시소자들; 및 상기 개구와 상기 표시영역 사이에 위치하는 그루브; 를 포함하며, 기 그루브는 제1층 및 상기 제1층 위의 제2층을 포함하는 다층 막의 두께 방향을 따라 오목한 언더컷 단면을 가지며, 상기 제2층은 상기 그루브의 중심을 향해 돌출된 한 쌍의 텁을 포함하며, 상기 텁 각각의 길이는  $2\mu\text{m}$  보다 작은, 표시 패널을 개시한다.

[0006]

상기 텁 각각의 길이는  $0.3\mu\text{m}$  이거나 그보다 크고  $2\mu\text{m}$  보다 작을 수 있다. 은, 표시 패널.

[0007]

상기 제1층은 유기물을 포함하며, 상기 제2층은 무기물을 포함할 수 있다.

[0008]

상기 제2층은 무기질연층 또는 금속을 포함할 수 있다.

[0009]

상기 그루브는, 상기 제1층의 제1홀 또는 제1리세스; 및 상기 제2층의 제2홀;을 포함하며, 상기 제2홀은 상기 제1홀 또는 상기 제1리세스와 연결될 수 있다.

[0010]

상기 한 쌍의 텁 사이의 거리는, 상기 제1홀 또는 상기 제1리세스의 깊이 보다 클 수 있다,

[0011]

상기 제1홀 또는 상기 제1리세스의 깊이는, 상기 텁 각각의 길이 보다 클 수 있다.

[0012]

상기 제1홀 또는 상기 제1리세스의 깊이에 대한 상기 텁 각각의 길이는,  $0.05 < (\ell / dp) < 0.50$ 일 수 있으며, 여기서,  $\ell$  은 상기 텁 각각의 길이를,  $dp$ 는 상기 제1홀 또는 상기 제1리세스의 깊이를 나타낸다.

[0013]

상기 제1홀 또는 상기 제1리세스의 깊이는, 상기 제1층의 두께와 같거나 그보다 작을 수 있다.

- [0014] 상기 화소전극과 상기 발광층 사이의 제1기능층, 및 상기 발광층과 상기 대향전극 사이의 제2기능층 중 적어도 어느 하나를 더 포함할 수 있으며, 상기 제1기능층 및 상기 제2기능층 중 적어도 어느 하나, 및 상기 대향전극은 각각 상기 한 쌍의 텁을 중심으로 단절되고, 상기 제1홀 또는 상기 제1리세스의 깊이는, 상기 제1기능층과 상기 제2기능층 중 적어도 어느 하나의 두께, 및 상기 대향전극의 두께의 합 보다 클 수 있다.

- [0015] 상기 대향전극 위의 캡핑층을 더 포함하고, 상기 제1홀 또는 상기 제1리세스의 깊이는, 상기 제1기능층과 상기 제2기능층 중 적어도 어느 하나의 두께, 상기 대향전극의 두께, 및 상기 캡핑층의 두께의 합 보다 클 수 있다.

- [0016] 기판, 및 상기 기판 상에 배치되며 상기 화소전극과 전기적으로 연결된 박막트랜지스터를 구비하는 화소회로를 더 포함할 수 있다.

- [0017] 상기 기판은 상기 다층 막을 포함할 수 있다. 또는, 상기 다층 막은 상기 기판 위에 위치할 수 있다.

- [0018] 본 발명의 다른 실시예는, 개구를 둘러싸는 표시영역에 위치하며, 각각 화소전극, 발광층 및 대향전극을 포함하는, 복수의 표시요소들; 및 상기 개구와 상기 표시영역 사이에 위치하며, 언더컷 단면을 갖는 그루브;를 포함하며, 상기 그루브는, 제1층 및 상기 제1층 위의 제2층을 포함하는 다층 막의 두께 방향을 따라 형성되며, 상기 제2층은 상기 그루브의 중심을 향해 돌출된 한 쌍의 텁을 포함하고, 상기 그루브 중 상기 제1층을 지나는 부분의 깊이는, 상기 한 쌍의 텁 각각의 길이 보다 큰, 표시 패널을 개시한다.

- [0019] 상기 텁 각각의 길이는  $0.3\mu\text{m}$  와 같거나 그보다 크고  $2\mu\text{m}$  보다 작을 수 있다.

- [0020] 상기 깊이는 상기 제1층의 두께와 같거나 그보다 작을 수 있다.

- [0021] 상기 한 쌍의 텁 사이의 거리는 상기 깊이 보다 클 수 있다.

- [0022] 상기 깊이에 대한 상기 텁 각각의 길이는,  $0.05 < (\ell / dp) < 0.5$ 일 수 있으며, 여기서,  $\ell$  은 상기 텁 각각의 길이를,  $dp$  는 상기 깊이를 나타낸다.

- [0023] 상기 화소전극과 상기 발광층 사이의 제1기능층, 및 상기 발광층과 상기 대향전극 사이의 제2기능층 중 적어도 어느 하나를 더 포함하고, 상기 제1기능층과 상기 제2기능층 중 적어도 어느 하나, 및 상기 대향전극은 각각 상기 한 쌍의 텁을 중심으로 단절되며, 상기 깊이는, 상기 제1기능층과 상기 제2기능층 중 적어도 어느 하나의 두께, 및 상기 대향전극의 두께의 합 보다 클 수 있다.

- [0024] 상기 대향전극 위에는 캡핑층이 더 포함될 수 있으며, 상기 깊이는, 상기 제1기능층과 상기 제2기능층 중 적어도 어느 하나의 두께, 상기 대향전극의 두께, 및 상기 캡핑층의 두께의 합 보다 클 수 있다.

- [0025] 상기 깊이는  $2\mu\text{m}$  이거나 그보다 클 수 있다.

- [0026] 기판, 및 상기 기판 상에 위치하며, 상기 화소전극과 전기적으로 연결된 박막트랜지스터를 구비하는 화소회로를 더 포함할 수 있다.

- [0027] 상기 기판은 상기 다층 막을 포함할 수 있다. 또는, 상기 다층 막은 상기 기판 위에 위치할 수 있다.

- [0028] 전술한 것 외의 다른 측면, 특징, 이점이 이하의 도면, 특허청구범위 및 발명의 상세한 설명으로부터 명확해질 것이다.

### 발명의 효과

- [0029] 본 발명의 실시예들에 관한 표시 패널은 언더컷 단면의 그루브가 손상되는 것을 방지할 수 있으며, 따라서 표시 요소들이 외부의 수분과 같은 이물질에 의해 손상되는 것을 방지할 수 있다. 그러나 이러한 효과는 예시적인 것으로, 이에 의해 본 발명의 범위가 한정되는 것은 아니다.

### 도면의 간단한 설명

- [0030] 도 1은 본 발명의 일 실시예에 따른 표시 장치를 개략적으로 도시한 사시도이다.

도 2는 본 발명의 일 실시예에 따른 표시 장치를 간략하게 나타낸 단면도이다.

도 3은 본 발명의 일 실시예에 따른 표시 패널을 개략적으로 나타낸 평면도이다.

도 4는 표시 패널의 어느 한 화소를 개략적으로 나타낸 등가 회로도이다.

도 5는 본 발명의 일 실시예에 따른 표시 패널 중 제1비표시영역에 위치하는 신호라인들을 나타낸다.

도 6은 본 발명의 일 실시예에 따른 표시 패널 중 제1비표시영역에 위치하는 그루브들을 나타낸다.

도 7은 본 발명의 일 실시예에 따른 표시 패널에 구비된 어느 하나의 화소의 단면도이다.

도 8a 내지 도 8d는 본 발명의 일 실시예에 따른 표시 패널에 구비된 그루브의 단면도이다.

도 9는 본 발명의 일 실시예에 따른 표시 패널의 단면도이다.

도 10은 본 발명의 일 실시예에 따른 표시 패널 중 그루브를 발췌하여 나타낸 단면도이다.

도 11은 본 발명의 다른 실시예에 따른 표시 패널 중 그루브를 발췌하여 나타낸 단면도이다.

도 12는 본 발명의 다른 실시예에 따른 표시 패널 중 그루브를 발췌하여 나타낸 단면도이다.

도 13은 본 발명의 다른 실시예에 따른 표시 패널 중 그루브를 발췌하여 나타낸 단면도이다.

도 14는 본 발명의 다른 실시예에 따른 표시 패널 중 그루브를 발췌하여 나타낸 단면도이다.

도 15는 본 발명의 다른 실시예에 따른 표시 패널 중 제1비표시영역에 배치된 그루브들을 나타낸 단면도이다.

도 16은 본 발명의 다른 실시예에 따른 표시 패널 중 제1비표시영역에 배치된 그루브들을 나타낸 단면도이다.

도 17은 본 발명의 다른 실시예에 따른 표시 패널의 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0031]

본 발명은 다양한 변환을 가할 수 있고 여러 가지 실시예를 가질 수 있는 바, 특정 실시예들을 도면에 예시하고 상세한 설명에 상세하게 설명하고자 한다. 본 발명의 효과 및 특징, 그리고 그것들을 달성하는 방법은 도면과 함께 상세하게 후술되어 있는 실시예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 다양한 형태로 구현될 수 있다.

[0032]

이하, 첨부된 도면을 참조하여 본 발명의 실시예들을 상세히 설명하기로 하며, 도면을 참조하여 설명할 때 동일하거나 대응하는 구성 요소는 동일한 도면부호를 부여하고 이에 대한 중복되는 설명은 생략하기로 한다.

[0033]

이하의 실시예에서, 제1, 제2 등의 용어는 한정적인 의미가 아니라 하나의 구성 요소를 다른 구성 요소와 구별하는 목적으로 사용되었다.

[0034]

이하의 실시예에서, 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다.

[0035]

이하의 실시예에서, 포함하다 또는 가지다 등의 용어는 명세서상에 기재된 특징, 또는 구성요소가 존재함을 의미하는 것이고, 하나 이상의 다른 특징들 또는 구성요소가 부가될 가능성을 미리 배제하는 것은 아니다.

[0036]

이하의 실시예에서, 막, 영역, 구성 요소 등의 부분이 다른 부분 위에 또는 상에 있다고 할 때, 다른 부분의 바로 위에 있는 경우뿐만 아니라, 그 중간에 다른 막, 영역, 구성 요소 등이 개재되어 있는 경우도 포함한다.

[0037]

도면에서는 설명의 편의를 위하여 구성 요소들이 그 크기가 과장 또는 축소될 수 있다. 예컨대, 도면에서 나타난 각 구성의 크기 및 두께는 설명의 편의를 위해 임의로 나타내었으므로, 본 발명이 반드시 도시된 바에 한정되지 않는다.

[0038]

어떤 실시예가 달리 구현 가능한 경우에 특정한 공정 순서는 설명되는 순서와 다르게 수행될 수도 있다. 예를 들어, 연속하여 설명되는 두 공정이 실질적으로 동시에 수행될 수도 있고, 설명되는 순서와 반대의 순서로 진행될 수 있다.

[0039]

이하의 실시예에서, 막, 영역, 구성 요소 등이 연결되었다고 할 때, 막, 영역, 구성 요소들이 직접적으로 연결된 경우뿐만 아니라 막, 영역, 구성요소들 중간에 다른 막, 영역, 구성 요소들이 개재되어 간접적으로 연결된 경우도 포함한다. 예컨대, 본 명세서에서 막, 영역, 구성 요소 등이 전기적으로 연결되었다고 할 때, 막, 영역, 구성 요소 등이 직접 전기적으로 연결된 경우뿐만 아니라, 그 중간에 다른 막, 영역, 구성 요소 등이 개재되어 간접적으로 전기적 연결된 경우도 포함한다.

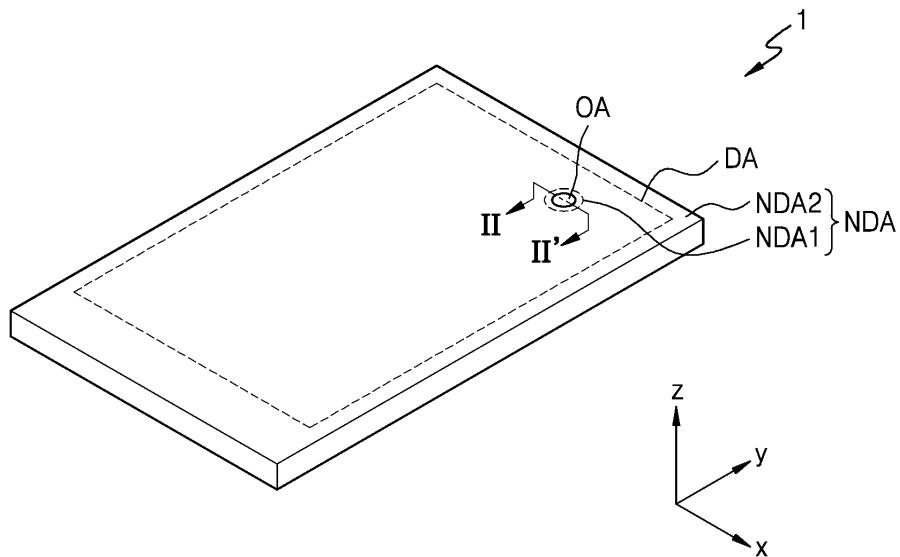

[0040]

도 1은 본 발명의 일 실시예에 따른 표시 장치를 개략적으로 도시한 사시도이다.

[0041]

도 1을 참조하면, 표시 장치(1)는 빛을 방출하는 표시영역(DA)과 빛을 방출하지 않는 비표시영역(NDA)을 포함한

다. 비표시영역(NDA)은 표시영역(DA)과 인접하게 배치된다. 표시 장치(1)는 표시영역(DA)에 배치된 복수의 화소들에서 방출되는 빛을 이용하여 소정의 이미지를 제공할 수 있다.

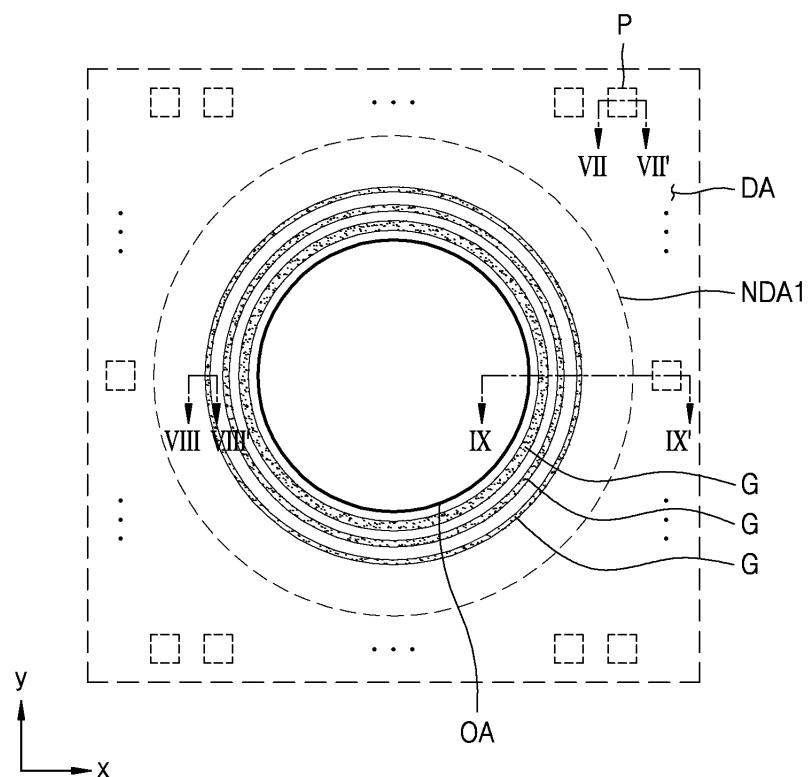

[0042] 표시 장치(1)는 표시영역(DA)에 의해 적어도 부분적으로 둘러싸인 개구영역(OA)을 포함한다. 일 실시예로, 도 1은 개구영역(OA)이 표시영역(DA)에 의해 전체적으로 둘러싸인 것을 도시한다. 비표시영역(NDA)은 개구영역(OA)을 둘러싸는 제1비표시영역(NDA1), 및 표시영역(DA)의 외곽을 둘러싸는 제2비표시영역(NDA2)을 포함할 수 있다. 제1비표시영역(NDA1)은 개구영역(OA)을 전체적으로 둘러싸고, 표시영역(DA)은 제1비표시영역(NDA1)을 전체적으로 둘러싸며, 제2비표시영역(NDA2)은 표시영역(DA)을 전체적으로 둘러쌀 수 있다.

[0043] 이하에서는, 본 발명의 일 실시예에 따른 표시 장치(1)로서, 유기 발광 표시 장치를 예로 하여 설명하지만, 본 발명의 표시 장치는 이에 제한되지 않는다. 다른 실시예로서, 무기 EL 표시 장치(Inorganic Light Emitting Display), 퀀텀닷 발광 표시 장치(Quantum dot Light Emitting Display) 등과 같이 다양한 방식의 표시 장치가 사용될 수 있다.

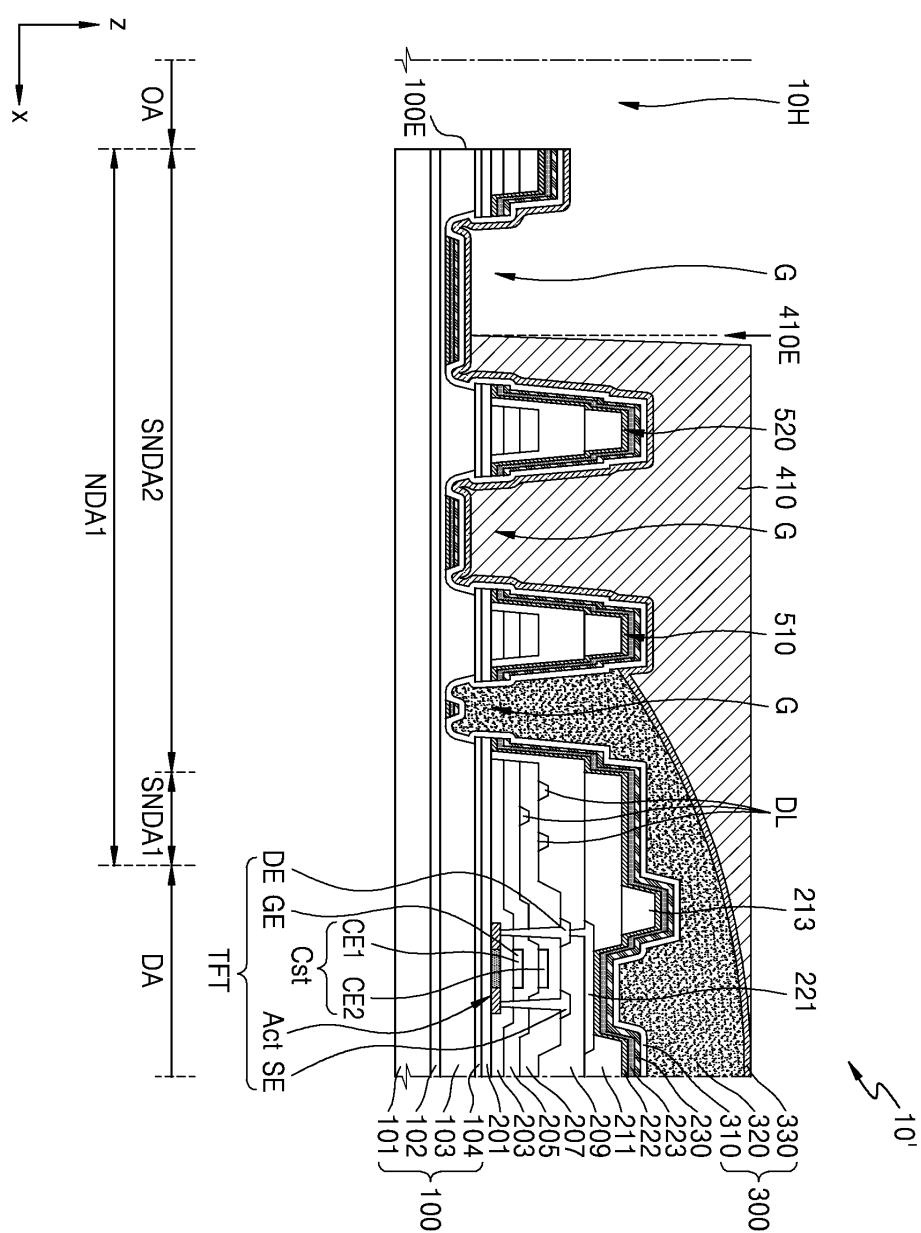

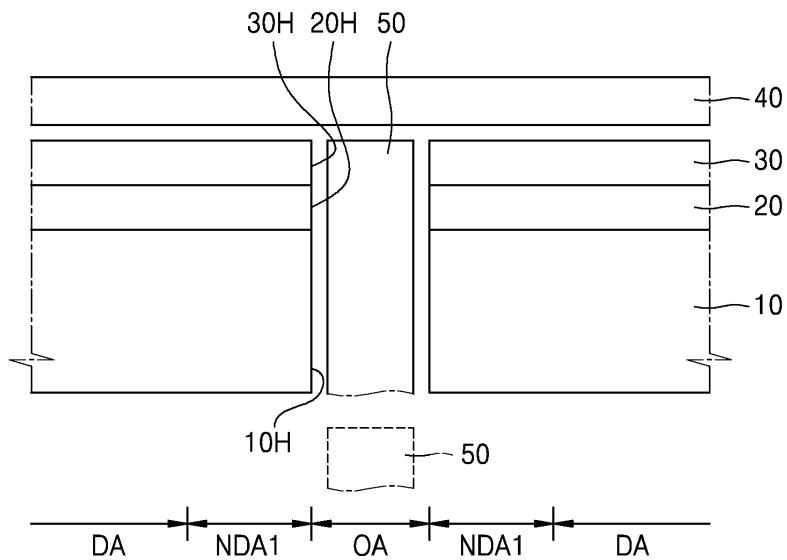

[0044] 도 2는 본 발명의 일 실시예에 따른 표시 장치를 간략하게 나타낸 단면도로서, 도 1의 II-II'선에 따른 단면에 대응할 수 있다.

[0045] 도 2를 참조하면, 표시 장치(1)는 표시 패널(10), 표시 패널(10) 상에 배치되는 입력 감지 부재(20), 및 광학적 기능 부재(30)를 포함할 수 있으며, 이들은 윈도우(40)로 커버될 수 있다. 표시 장치(1)는 휴대폰(mobile phone), 노트북, 스마트 위치와 같은 다양한 전자 기기일 수 있다.

[0046] 표시 패널(10)은 이미지를 표시할 수 있다. 표시 패널(10)은 표시영역(DA)에 배치된 화소들을 포함한다. 화소들은 표시요소 및 이와 연결된 화소회로를 포함할 수 있다. 표시요소는 유기발광 다이오드, 무기발광 다이오드, 또는 퀀텀닷 발광 다이오드 등을 포함할 수 있다.

[0047] 입력 감지 부재(20)는 외부의 입력, 예컨대 터치 이벤트에 따른 좌표정보를 획득한다. 입력 감지 부재(20)는 감지전극(sensing electrode 또는 touch electrode) 및 감지전극과 연결된 신호라인(trace line)들을 포함할 수 있다. 입력 감지 부재(20)는 표시 패널(10) 위에 배치될 수 있다.

[0048] 입력 감지 부재(20)는 표시 패널(10) 상에 직접 형성되거나, 별도로 형성된 후 광학 투명 접착제(OCA)와 같은 접착층을 통해 결합될 수 있다. 예컨대, 입력 감지 부재(20)는 표시 패널(10)을 형성하는 공정 이후에 연속적으로 이뤄질 수 있으며, 이 경우 접착층은 입력 감지 부재(20)와 표시 패널(10) 사이에 개재되지 않을 수 있다. 도 2에는 입력 감지 부재(20)가 표시 패널(10)과 광학적 기능 부재(30) 사이에 개재된 것을 도시하지만, 다른 실시예로서 입력 감지 부재(20)는 광학적 기능 부재(30) 위에 배치될 수 있다.

[0049] 광학적 기능 부재(30)는 반사 방지층을 포함할 수 있다. 반사 방지층은 윈도우(40)를 통해 외부에서 표시 패널(10)을 향해 입사하는 빛(외부 광)의 반사율을 감소시킬 수 있다. 반사 방지층은 위상지연자(retarder) 및 편광자(polarizer)를 포함할 수 있다. 위상지연자는 필름타입 또는 액정 코팅타입일 수 있고,  $\lambda/2$  위상지연자 및/ 또는  $\lambda/4$  위상지연자를 포함할 수 있다. 편광자 역시 필름타입 또는 액정 코팅타입일 수 있다. 필름타입은 연신형 합성수지 필름을 포함하고, 액정 코팅타입은 소정의 배열로 배열된 액정들을 포함할 수 있다. 위상지연자 및 편광자는 보호필름을 더 포함할 수 있다. 위상지연자 및 편광자 자체 또는 보호필름이 반사방지 층의 베이스 층으로 정의될 수 있다.

[0050] 다른 실시예로, 반사 방지층은 블랙 매트릭스와 컬러필터들을 포함할 수 있다. 컬러필터들은 표시 패널(10)의 화소들 각각에서 방출되는 빛의 색상을 고려하여 배열될 수 있다. 또 다른 실시예로, 반사 방지층은 상쇄간섭 구조물을 포함할 수 있다. 상쇄간섭 구조물은 서로 다른 층 상에 배치된 제1 반사층과 제2 반사층을 포함할 있다. 제1 반사층 및 제2 반사층에서 각각 반사된 제1 반사광과 제2 반사광은 상쇄 간섭될 수 있고, 그에 따라 외부 광 반사율이 감소될 수 있다.

[0051] 광학적 기능 부재(30)는 렌즈층을 포함할 수 있다. 렌즈층은 표시 패널(10)에서 방출되는 빛의 출광 효율을 향상시키거나, 색편차를 줄일 수 있다. 렌즈층은 오목하거나 볼록한 렌즈 형상을 가지는 층을 포함하거나, 또는/ 및 굴절률이 서로 다른 복수의 층을 포함할 수 있다. 광학적 기능 부재(30)는 전술한 반사 방지층 및 렌즈층을 모두 포함하거나, 이를 중 어느 하나를 포함할 수 있다.

[0052] 표시 패널(10), 입력 감지 부재(20), 및 광학적 기능 부재(30)는 개구를 포함할 수 있다. 이와 관련하여, 도 2에는 표시 패널(10), 입력 감지 부재(20), 및 광학적 기능 부재(30)가 각각 제1 내지 제3개구(10H, 20H, 30H)를 포함하며, 제1 내지 제3개구(10H, 20H, 30H)들이 서로 중첩되는 것을 도시한다. 제1 내지 제3개구(10H, 20H,

30H)들은 개구영역(OA)에 대응하도록 위치한다. 다른 실시예로, 표시 패널(10), 입력 감지 부재(20), 및/또는 광학적 기능 부재(30) 중 적어도 하나는 개구를 포함하지 않을 수 있다. 예컨대, 표시 패널(10), 입력 감지 부재(20), 및 광학적 기능 부재(30) 중에서 선택된 어느 하나, 또는 두 개의 구성요소는 개구를 포함하지 않을 수 있다.

[0053] 컴포넌트(50)는 개구영역(OA)에 대응할 수 있다. 컴포넌트(50)는 도 2에 실선으로 도시된 바와 같이 제1 내지 제3개구(10H, 20H, 30H) 내에 위치하거나, 점선으로 도시된 바와 같이 표시 패널(10)의 아래에 배치될 수 있다.

[0054] 컴포넌트(50)는 전자요소를 포함할 수 있다. 예컨대, 컴포넌트(50)는 빛이나 음향을 이용하는 전자요소일 수 있다. 예컨대, 전자요소는 적외선 센서와 같이 빛을 수광하여 이용하는 센서, 빛을 수광하여 이미지를 촬상하는 카메라, 빛이나 음향을 출력하고 감지하여 거리를 측정하거나 지문 등을 인식하는 센서, 빛을 출력하는 소형 램프이거나, 소리를 출력하는 스피커 등을 포함할 수 있다. 빛을 이용하는 전자요소의 경우, 가시광, 적외선광, 자외선광 등과 같이 다양한 파장 대역의 빛을 이용할 수 있다. 일부 실시예에서, 개구영역(OA)은 컴포넌트(50)로부터 외부로 출력되거나 외부로부터 전자요소를 향해 진행하는 빛 또는/및 음향이 투과할 수 있는 투과영역(transmission area)으로 이해될 수 있다.

[0055] 다른 실시예로, 표시 장치(1)가 스마트 위치나 차량용 계기판으로 이용되는 경우, 컴포넌트(50)는 시계 바늘이나 소정의 정보(예, 차량 속도 등)를 지시하는 바늘 등을 포함하는 부재일 수 있다. 표시 장치(1)가 시계 바늘이나 차량용 계기판을 포함하는 경우, 컴포넌트(50)가 윈도우(40)를 관통하여 외부로 노출될 수 있으며, 윈도우(40)는 개구영역(OA)에 대응하는 개구를 포함할 수 있다.

[0056] 컴포넌트(50)는 전술한 바와 같이 표시 패널(10)의 기능과 관계된 구성요소(들)를 포함하거나, 표시 패널(10)의 심미감을 증가시키는 액세서리와 같은 구성요소 등을 포함할 수 있다.

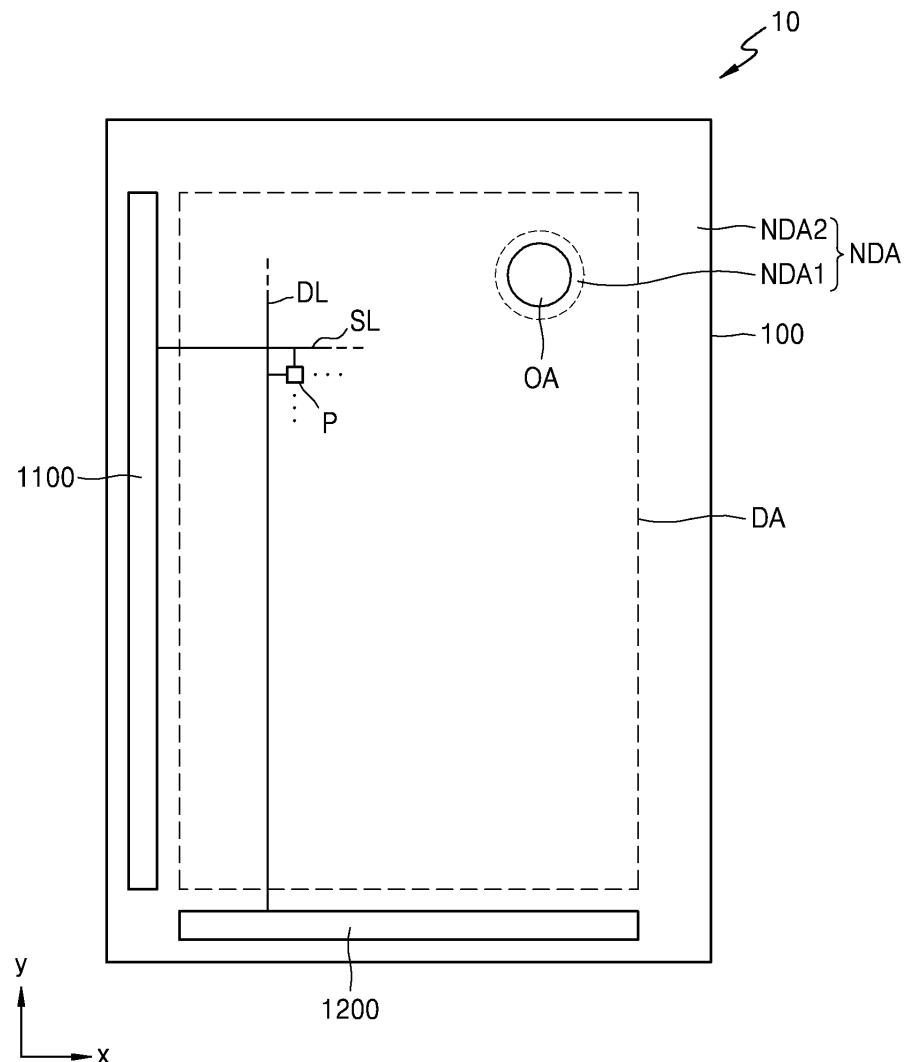

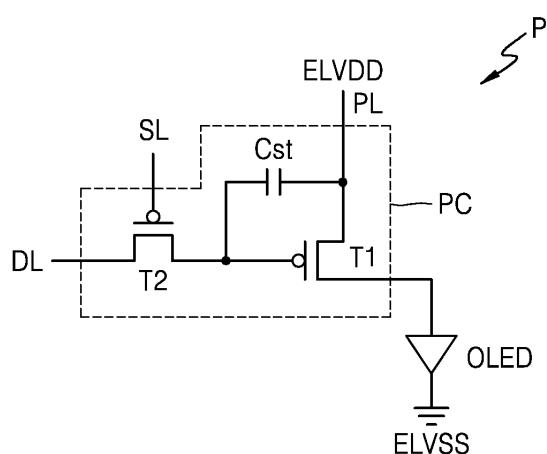

[0057] 도 3은 본 발명의 일 실시예에 따른 표시 패널을 개략적으로 나타낸 평면도이고, 도 4는 표시 패널의 어느 한 화소를 개략적으로 나타낸 등가 회로도이다.

[0058] 도 3을 참조하면, 표시 패널(10)은 표시영역(DA) 및 제1 및 제2비표시영역(NDA1, NDA2)를 포함한다. 도 3은 표시 패널(10) 중 기판(100)의 모습으로 이해될 수 있다. 예컨대, 기판(100)이 개구영역(OA), 표시영역(DA), 제1 및 제2비표시영역(NDA1, NDA2)를 갖는 것으로 이해될 수 있다.

[0059] 표시 패널(10)은 표시영역(DA)에 배치된 복수의 화소(P)들을 포함한다. 각 화소(P)는 도 4에 도시된 바와 같이 화소회로(PC), 및 화소회로(PC)에 연결된 표시요소로서, 유기발광다이오드(OLED)를 포함한다. 화소회로(PC)는 제1박막트랜지스터(T1), 제2박막트랜지스터(T2), 및 스토리지 커패시터(Cst)를 포함할 수 있다. 각 화소(P)는 유기발광다이오드(OLED)를 통해 예컨대, 적색, 녹색, 청색 또는 백색의 빛을 방출할 수 있다.

[0060] 제2박막트랜지스터(T2)는 스위칭 박막트랜지스터로서, 스캔라인(SL) 및 데이터라인(DL)에 연결되며, 스캔라인(SL)으로부터 입력되는 스위칭 전압에 따라 데이터라인(DL)으로부터 입력된 데이터 전압을 제1박막트랜지스터(T1)로 전달할 수 있다. 스토리지 커패시터(Cst)는 제2박막트랜지스터(T2)와 구동전압선(PL)에 연결되며, 제2박막트랜지스터(T2)로부터 전달받은 전압과 구동전압선(PL)에 공급되는 제1전원전압(ELVDD)의 차이에 해당하는 전압을 저장할 수 있다.

[0061] 제1박막트랜지스터(T1)는 구동 박막트랜지스터로서, 구동전압선(PL)과 스토리지 커패시터(Cst)에 연결되며, 스토리지 커패시터(Cst)에 저장된 전압 값에 대응하여 구동전압선(PL)으로부터 유기발광다이오드(OLED)를 흐르는 구동 전류를 제어할 수 있다. 유기발광다이오드(OLED)는 구동 전류에 의해 소정의 휘도를 갖는 빛을 방출할 수 있다. 유기발광다이오드(OLED)의 대향전극(예, 캐소드)은 제2전원전압(ELVSS)을 공급받을 수 있다.

[0062] 도 4는 화소회로(PC)가 2개의 박막트랜지스터와 1개의 스토리지 커패시터를 포함하는 것을 설명하고 있으나, 본 발명은 이에 한정되지 않는다. 박막트랜지스터의 개수 및 스토리지 커패시터의 개수는 화소회로(PC)의 설계에 따라 다양하게 변경될 수 있음을 물론이다.

[0063] 다시 도 3을 참조하면, 제1비표시영역(NDA1)은 개구영역(OA)을 둘러쌀 수 있다. 제1비표시영역(NDA1)은 빛을 방출하는 유기발광다이오드와 같은 표시요소가 배치되지 않은 영역으로, 제1비표시영역(NDA1)에는 개구영역(OA) 주변에 구비된 화소(P)들에 신호를 제공하는 신호라인들이 지나가거나 후술할 그루브(들)이 배치될 수 있다. 제2비표시영역(NDA2)에는 각 화소(P)에 스캔신호를 제공하는 스캔 드라이버(1100), 각 화소(P)에 데이터신호를 제공하는 데이터 드라이버(1200), 및 제1 및 제2전원전압을 제공하기 위한 메인 전원배선(미도시) 등이 배치될 수 있다. 도 4에는 데이터 드라이버(1200)가 기판(100)의 일 측면에 인접하게 배치된 것을 도시하나, 다른 실시예

에 따르면, 데이터 드라이버(1200)는 표시 패널(10)의 일 측에 배치된 패드와 전기적으로 접속된 FPCB(flexible Printed circuit board) 상에 배치될 수 있다.

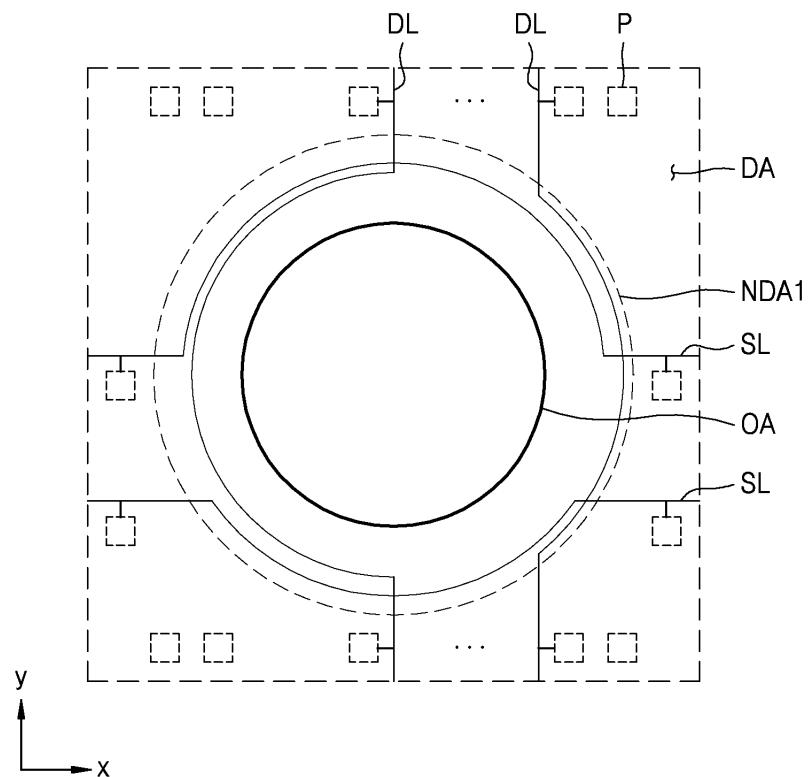

[0064] 도 5는 본 발명의 일 실시예에 따른 표시 패널의 일부를 나타낸 평면도로서, 제1비표시영역에 위치하는 신호라인들을 나타낸다.

[0065] 도 5를 참조하면, 개구영역(OA)을 중심으로 화소(P)들이 표시영역(DA)에 배치되며, 개구영역(OA)과 표시영역(DA) 사이에는 제1비표시영역(NDA1)이 위치할 수 있다.

[0066] 화소(P)들은 개구영역(OA)을 중심으로 상호 이격될 수 있다. 화소(P)들은 개구영역(OA)을 중심으로 위와 아래에 이격되거나, 및/또는 개구영역(OA)을 중심으로 좌우로 이격되어 배치될 수 있다.

[0067] 화소(P)들에 신호를 공급하는 신호라인들 중 개구영역(OA)과 인접한 신호라인들은 개구영역(OA)을 우회할 수 있다. 표시영역(DA)을 지나는 데이터라인들 중 일부 데이터라인(DL)은, 개구영역(OA)을 사이에 두고 위와 아래에 배치된 화소(P)들에 데이터신호를 제공하도록 y방향으로 연장되어, 제1비표시영역(NDA1)에서 개구영역(OA)의 가장자리를 따라 우회할 수 있다. 표시영역(DA)을 지나는 스캔라인들 중 일부 스캔라인(SL)은, 개구영역(OA)을 사이에 두고 좌우에 배치된 화소(P)들에 스캔신호를 제공하도록 x방향으로 연장되어, 제1비표시영역(NDA1)에서 개구영역(OA)의 가장자리를 따라 우회할 수 있다.

[0068] 도 6은 본 발명의 일 실시예에 따른 표시 패널의 일부를 나타낸 평면도로서, 제1비표시영역에 위치하는 그루브를 나타낸다.

[0069] 개구영역(OA)과 표시영역(DA) 사이에는 하나 또는 그 이상의 그루브들이 위치한다. 이와 관련하여, 도 6에서는 개구영역(OA)과 표시영역(DA) 사이에 3 개의 그루브(G)들이 위치한 것을 도시하나, 본 발명은 이에 한정되지 않는다. 다른 실시예로서, 제1비표시영역(NDA1)에는 1개, 2개, 또는 4개 이상의 그루브들이 배치될 수 있다.

[0070] 그루브(G)들은 제1비표시영역(NDA1)에서 개구영역(OA)을 전체적으로 둘러싸는 고리 형상일 수 있다. 그루브(G)들 각각의 직경은 개구영역(OA)의 직경보다는 크게 형성될 수 있다. 평면상에서 개구영역(OA)을 둘러싸는 그루브(G)들은 소정의 간격 이격될 수 있다.

[0071] 도 5와 도 6를 함께 고려하면, 그루브(G)들은 개구영역(OA)의 가장자리를 우회하는 데이터라인 또는/및 스캔라인의 우회 부분들 보다 개구영역(OA)에 더 인접하게 위치할 수 있다.

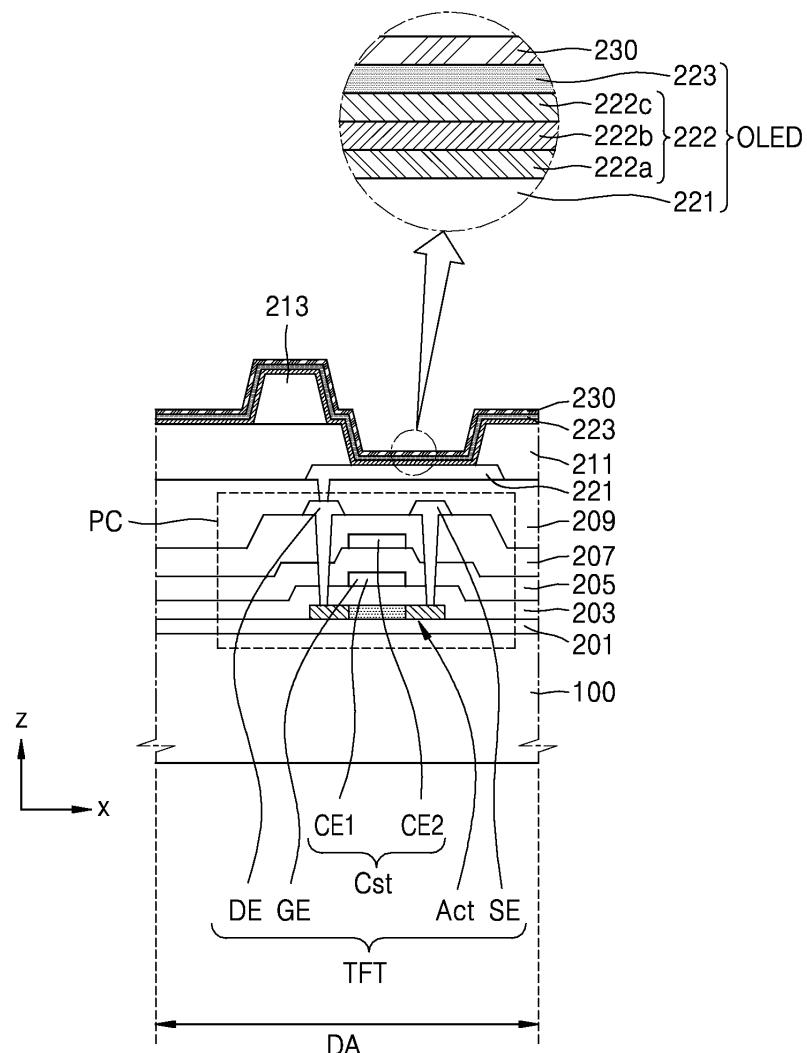

[0072] 도 7은 본 발명의 일 실시예에 따른 표시 패널에 구비된 화소의 단면도로서, 도 6의 VII- VII'선에 따른 단면에 대응할 수 있다.

[0073] 도 7을 참조하면, 표시영역(DA)에는 화소회로(PC) 및 화소회로(PC)에 전기적으로 연결된 유기발광 다이오드(OLED)가 배치될 수 있다.

[0074] 기판(100) 상에 위치하는 박막트랜지스터(TFT) 및 스토리지 커패시터(Cst) 및 이들에 전기적으로 연결된 화소전극(221)을 형성한다. 화소회로(PC)는 기판(100) 상에 배치되며, 화소회로(PC) 상에는 유기발광 다이오드(OLED)가 위치할 수 있다.

[0075] 기판(100)은 고분자 수지 또는 글래스를 포함할 수 있다. 일 실시예로, 기판(100)은 폴리에테르술폰(PES, polyethersulphone), 폴리아릴레이트(PAR, polyarylate), 폴리에테르 이미드(PEI, polyether imide), 폴리에틸렌 나프탈레이트(PEN, polyethylenene napthalate), 폴리에틸렌 테레프탈레이트(PET, polyethyleneterephthalate), 폴리페닐렌 살파이드(polyphenylene sulfide: PPS), 폴리아릴레이트(polyallylate), 폴리이미드(polyimide: PI), 폴리카보네이트(PC), 셀룰로오스 트리 아세테이트(TAC), 또는/및 셀룰로오스 아세테이트 프로피오네이트(cellulose acetate propionate: CAP) 등과 같은 고분자 수지를 포함할 수 있으며, 플렉서블한 성질을 가질 수 있다. 기판(100)은 SiO<sub>2</sub>를 주성분으로 하는 글래스재를 포함하거나, 강화 플라스틱과 같은 수지를 포함할 수 있으며, 리지드(rigid)한 성질을 가질 수 있다.

[0076] 기판(100) 상에는 불순물이 박막트랜지스터(TFT)의 반도체층(Act)으로 침투하는 것을 방지하기 위해 형성된 벼퍼층(201)이 형성될 수 있다. 벼퍼층(201)은 실리콘나이트라이드 또는 실리콘옥사이드와 같은 무기 절연물을 포함할 수 있으며, 전술한 무기 절연물을 포함하는 단층 또는 다층일 수 있다.

[0077] 벼퍼층(201) 상에는 화소회로(PC)가 배치될 수 있다. 화소회로(PC)는 박막트랜지스터(TFT) 및 스토리지 커패시터(Cst)를 포함한다. 박막트랜지스터(TFT)는 반도체층(Act), 게이트전극(GE), 소스전극(SE), 드레인전극(DE)을 포함할 수 있다. 도 7에 도시된 박막트랜지스터(TFT)는 도 4를 참조하여 설명한 구동 박막트랜지스터에 대응할

수 있다. 본 실시예에서는 게이트전극(GE)이 게이트절연층(203)을 가운데 두고 반도체층(Act) 상에 배치된 텁 게이트 타입을 도시하였으나, 또 다른 실시예에 따르면 박막트랜지스터(TFT)는 바텀 게이트 타입일 수 있다.

[0078] 반도체층(Act)은 폴리 실리콘을 포함할 수 있다. 또는, 반도체층(Act)은 아모퍼스 실리콘을 포함하거나, 산화물 반도체를 포함하거나, 유기 반도체 등을 포함할 수 있다. 게이트전극(GE)은 저저항 금속 물질을 포함할 수 있다. 게이트전극(GE)은 몰리브덴(Mo), 알루미늄(Al), 구리(Cu), 티타늄(Ti) 등을 포함하는 도전 물질을 포함할 수 있고, 상기의 재료를 포함하는 다층 또는 단층으로 형성될 수 있다.

[0079] 반도체층(Act)과 게이트전극(GE) 사이의 게이트절연층(203)은 실리콘옥사이드, 실리콘나이트라이드, 실리콘옥시나이트라이드, 알루미늄옥사이드, 티타늄옥사이드, 탄탈륨옥사이드, 하프늄옥사이드 등과 같은 무기 절연물을 포함할 수 있다. 게이트절연층(203)은 전술한 물질을 포함하는 단층 또는 다층일 수 있다.

[0080] 소스전극(SE) 및 드레인전극(DE)은 전도성이 좋은 재료를 포함할 수 있다. 소스전극(SE) 및 드레인전극(DE)은 몰리브덴(Mo), 알루미늄(Al), 구리(Cu), 티타늄(Ti) 등을 포함하는 도전 물질을 포함할 수 있고, 상기의 재료를 포함하는 다층 또는 단층으로 형성될 수 있다. 일 실시예로, 소스전극(SE) 및 드레인전극(DE)은 Ti/Al/Ti의 다층으로 형성될 수 있다.

[0081] 스토리지 커패시터(Cst)는 제1층간절연층(205)을 사이에 두고 중첩하는 하부 전극(CE1)과 상부 전극(CE2)을 포함한다. 스토리지 커패시터(Cst)는 박막트랜지스터(TFT)와 중첩될 수 있다. 이와 관련하여, 도 7은 박막트랜지스터(TFT)의 게이트전극(GE)이 스토리지 커패시터(Cst)의 하부 전극(CE1)인 것을 도시하고 있다. 다른 실시예로서, 스토리지 커패시터(Cst)는 박막트랜지스터(TFT)와 중첩하지 않을 수 있다. 스토리지 커패시터(Cst)는 제2층간절연층(207)으로 커버될 수 있다.

[0082] 제1 및 제2층간절연층(205, 207)은 실리콘옥사이드, 실리콘나이트라이드, 실리콘옥시나이트라이드, 알루미늄옥사이드, 티타늄옥사이드, 탄탈륨옥사이드, 하프늄옥사이드 등과 같은 무기 절연물을 포함할 수 있다. 제1 및 제2층간절연층(205, 207)은 전술한 물질을 포함하는 단층 또는 다층일 수 있다.

[0083] 박막트랜지스터(TFT) 및 스토리지 커패시터(Cst)를 포함하는 화소회로(PC)는 제1절연층(209)으로 커버될 수 있다. 제1절연층(209)은 평탄화 절연층으로서, 상면이 대략 편평한 면을 포함할 수 있다. 제1절연층(209)은 Polymethylmethacrylate(PMMA)나 Polystyrene(PS)과 같은 일반 범용고분자, 폐놀계 그룹을 갖는 고분자 유도체, 아크릴계 고분자, 이미드계 고분자, 아릴에테르계 고분자, 아마이드계 고분자, 불소계고분자, p-자일렌계 고분자, 비닐알콜계 고분자 및 이들의 블렌드 등과 같은 유기 절연물을 포함할 수 있다. 일 실시예로, 제1절연층(209)은 폴리이미드를 포함할 수 있다. 또는, 제1절연층(209)은 무기 절연물을 포함하거나, 무기 및 유기 절연물을 포함할 수 있다.

[0084] 화소전극(221)은 제1절연층(209) 상에 형성될 수 있다. 화소전극(221)은 인듐틴옥사이드(ITO; indium tin oxide), 인듐징크옥사이드(IZO; indium zinc oxide), 징크옥사이드(ZnO; zinc oxide), 인듐옥사이드( $In_2O_3$ ; indium oxide), 인듐갈륨옥사이드(IGO; indium gallium oxide) 또는 알루미늄징크옥사이드(AZO; aluminum zinc oxide)와 같은 도전성 산화물을 포함할 수 있다. 다른 실시예로, 화소전극(221)은 은(Ag), 마그네슘(Mg), 알루미늄(Al), 백금(Pt), 팔라듐(Pd), 금(Au), 니켈(Ni), 네오디뮴(Nd), 이리듐(Ir), 크로뮴(Cr) 또는 이들의 화합물을 포함하는 반사막을 포함할 수 있다. 또 다른 실시예로, 화소전극(221)은 전술한 반사막의 위/아래에 ITO, IZO, ZnO 또는  $In_2O_3$ 로 형성된 막을 더 포함할 수 있다.

[0085] 화소전극(221) 상에는 제2절연층(211)이 형성될 수 있다. 제2절연층(211)은 화소정의막일 수 있다. 제2절연층(211)은 화소전극(221)의 상면을 노출하는 개구를 포함하되, 화소전극(221)의 가장자리를 커버할 수 있다. 제2절연층(211)은 유기 절연물을 포함할 수 있다. 또는, 제2절연층(211)은 실리콘나이트라이드(SiNx)나 실리콘옥시나이트라이드(SiON), 또는 실리콘옥사이드( $SiO_x$ )와 같은 무기 절연물을 포함할 수 있다. 또는, 제2절연층(211)은 유기절연물 및 무기절연물을 포함할 수 있다.

[0086] 중간층(222)은 발광층(222b)을 포함한다. 중간층(222)은 발광층(222b)의 아래에 배치된 제1기능층(222a) 및/또는 발광층(222b)의 위에 배치된 제2기능층(222c)을 포함할 수 있다. 발광층(222b)은 소정의 색상의 빛을 방출하는 고분자 또는 저분자 유기물을 포함할 수 있다.

[0087] 제1기능층(222a)은 단층 또는 다층일 수 있다. 예컨대 제1기능층(222a)이 고분자 물질로 형성되는 경우, 제1기능층(222a)은 단층구조인 홀 수송층(HTL: Hole Transport Layer)으로서, 폴리에틸렌 디히드록시피오펜(PEDOT: poly-(3,4)-ethylene-dihydroxy thiophene)이나 폴리아닐린(PANI: polyaniline)으로 형성할 수 있다. 제1기능

층(222a)이 저분자 물질로 형성되는 경우, 제1기능층(222a)은 홀 주입층(HIL: Hole Injection Layer)과 홀 수송층(HTL)을 포함할 수 있다.

[0088] 제2기능층(222c)은 언제나 구비되는 것은 아니다. 예컨대, 제1기능층(222a)과 발광층(222b)을 고분자 물질로 형성하는 경우, 제2기능층(222c)을 형성하는 것이 바람직하다. 제2기능층(222c)은 단층 또는 다층일 수 있다. 제2기능층(222c)은 전자 수송층(ETL: Electron Transport Layer) 및/또는 전자 주입층(EIL: Electron Injection Layer)을 포함할 수 있다.

[0089] 중간층(222) 중 발광층(222b)은 표시영역(DA)에서 각 화소마다 배치될 수 있다. 발광층(222b)은 제2절연층(211)의 개구를 통해 노출된 화소전극(221)의 상면과 접촉할 수 있다. 중간층(222) 중 제1 및 제2기능층(222a, 222c)는 도 7의 표시영역(DA)뿐만 아니라 도 8a 및 도 8b를 참조하여 후술할 제1비표시영역(NDA1) 상에도 형성될 수 있다.

[0090] 대향전극(223)은 일함수가 낮은 도전성 물질로 이루어질 수 있다. 예컨대, 대향전극(223)은 은(Ag), 마그네슘(Mg), 알루미늄(Al), 백금(Pt), 팔라듐(Pd), 금(Au), 니켈(Ni), 네오디뮴(Nd), 이리듐(Ir), 크로뮴(Cr), 리튬(Li), 칼슘(Ca) 또는 이들의 합금 등을 포함하는 (반)투명층을 포함할 수 있다. 또는, 대향전극(223)은 전술한 물질을 포함하는 (반)투명층 상에 ITO, IZO, ZnO 또는  $In_2O_3$ 과 같은 층을 더 포함할 수 있다. 대향전극(223)은 표시영역(DA)뿐만 아니라 제1비표시영역(NDA1) 상에도 형성될 수 있다. 중간층(222) 및 대향전극(223)은 열 증착법에 의해 형성될 수 있다.

[0091] 제2절연층(211) 상에는 스페이서(213)가 형성될 수 있다. 스페이서(213)는 폴리이미드와 같은 유기 절연물을 포함할 수 있다. 또는, 스페이서(213)는 실리콘나이트라이드나 실리콘옥사이드와 같은 무기 절연물을 포함하거나, 유기 절연물 및 무기 절연물을 포함할 수 있다.

[0092] 스페이서(213)는 제2절연층(211)과 다른 물질을 포함할 수 있다. 또는, 스페이서(213)는 제2절연층(211)과 동일한 물질을 포함할 수 있으며, 이 경우 제2절연층(211)과 스페이서(213)는 하프톤 마스크 등을 이용한 마스크 공정에서 함께 형성될 수 있다. 일 실시예로서, 제2절연층(211) 및 스페이서(213)는 폴리이미드를 포함할 수 있다.

[0093] 캡핑층(230)은 대향전극(223) 상에 배치될 수 있다. 캡핑층(230)은 LiF, 무기물, 또는/및 유기물을 포함할 수 있다. 일 실시예에서, 캡핑층(230)은 생략될 수 있다.

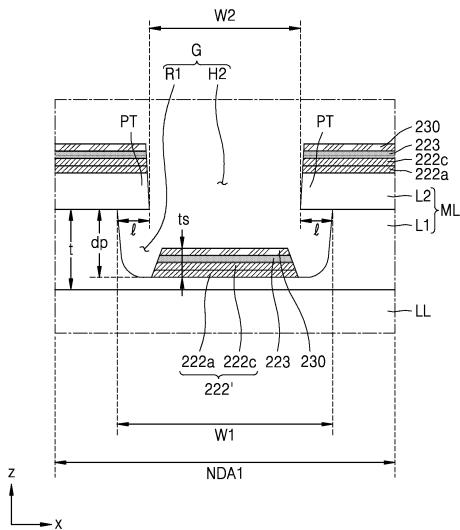

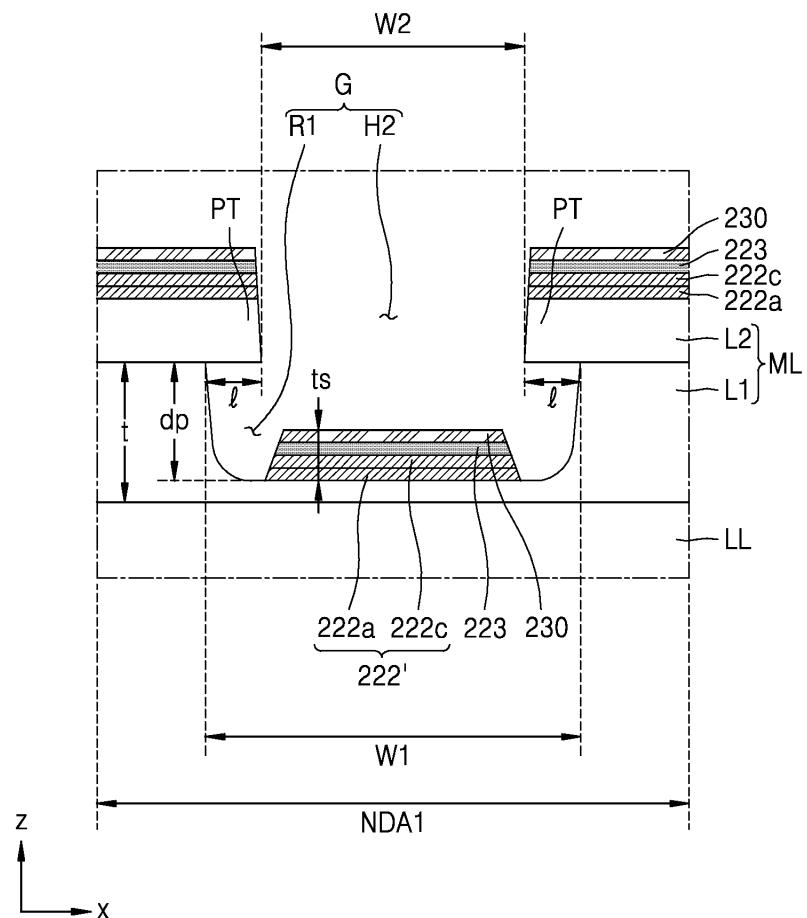

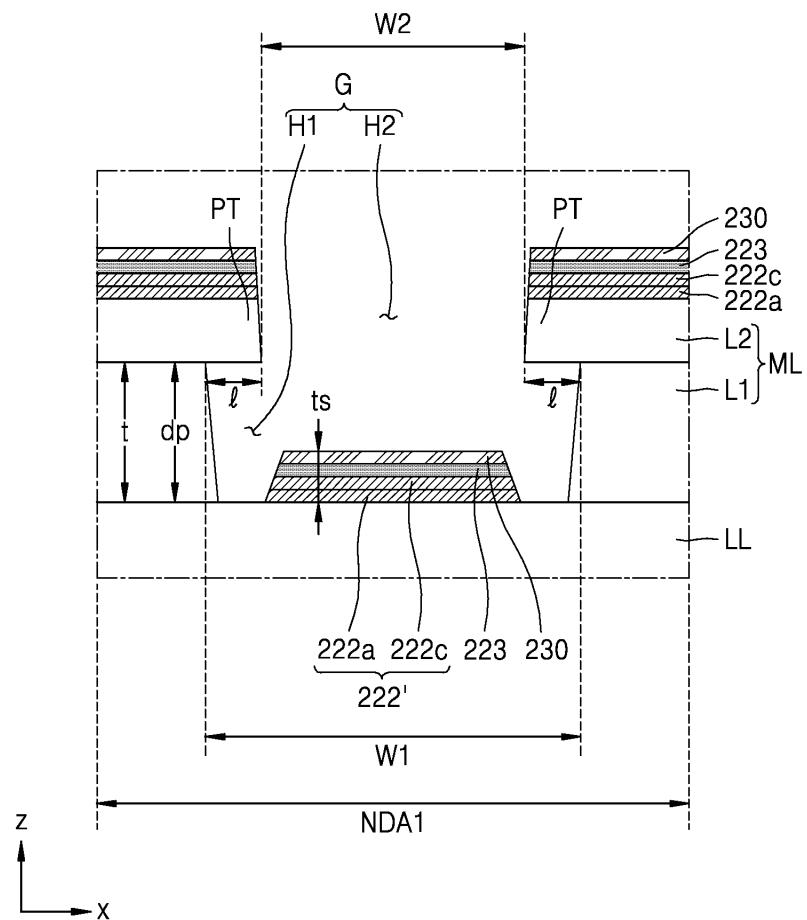

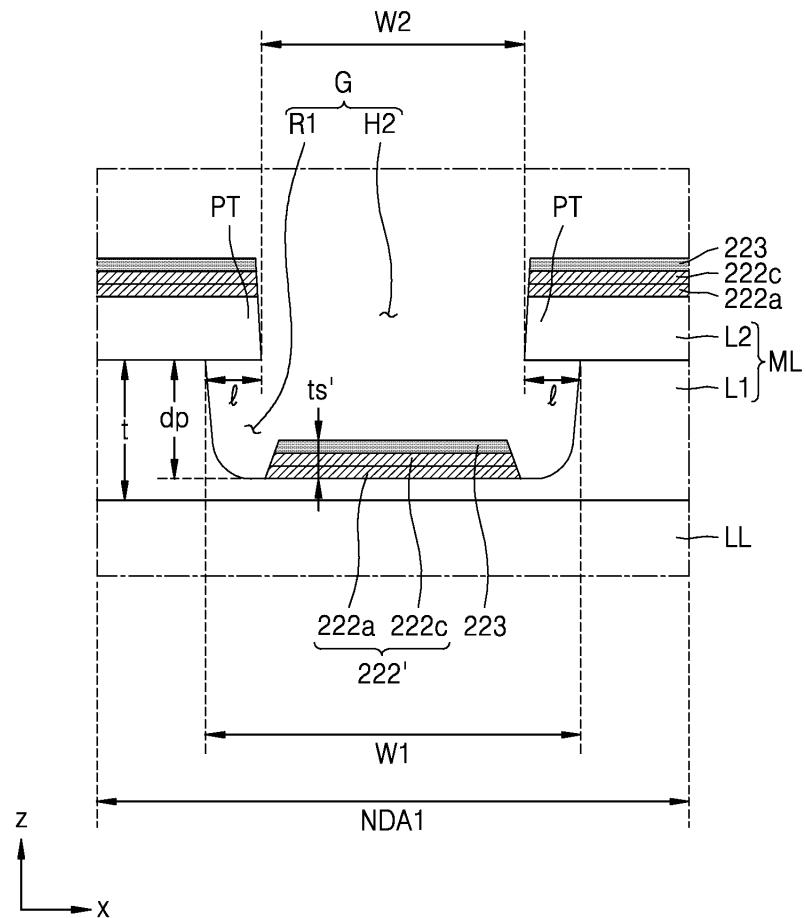

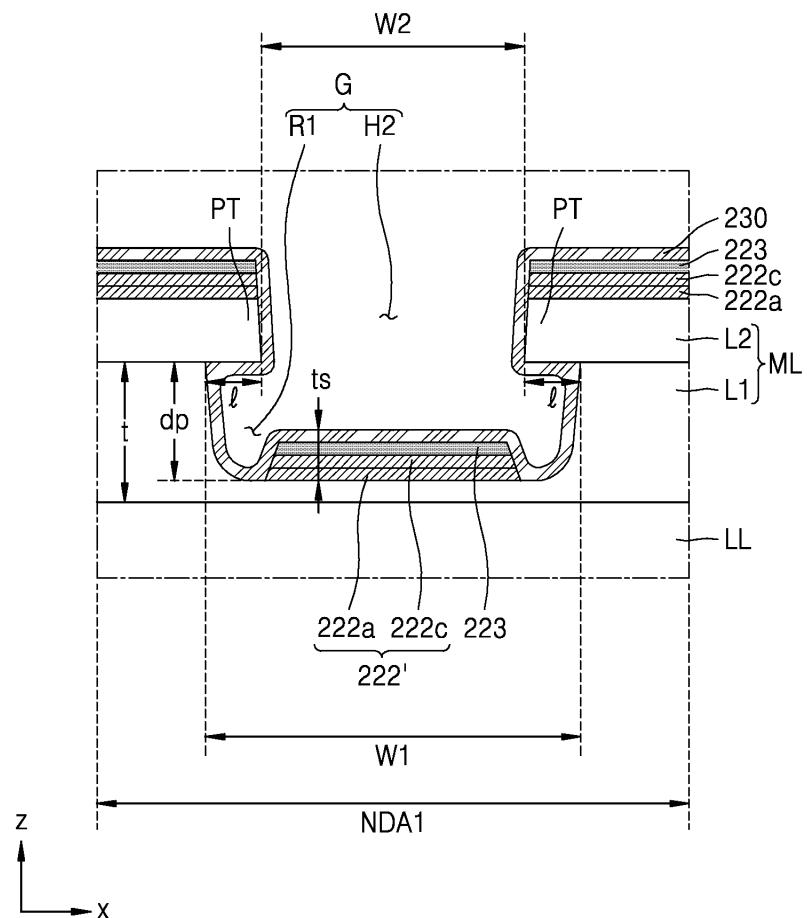

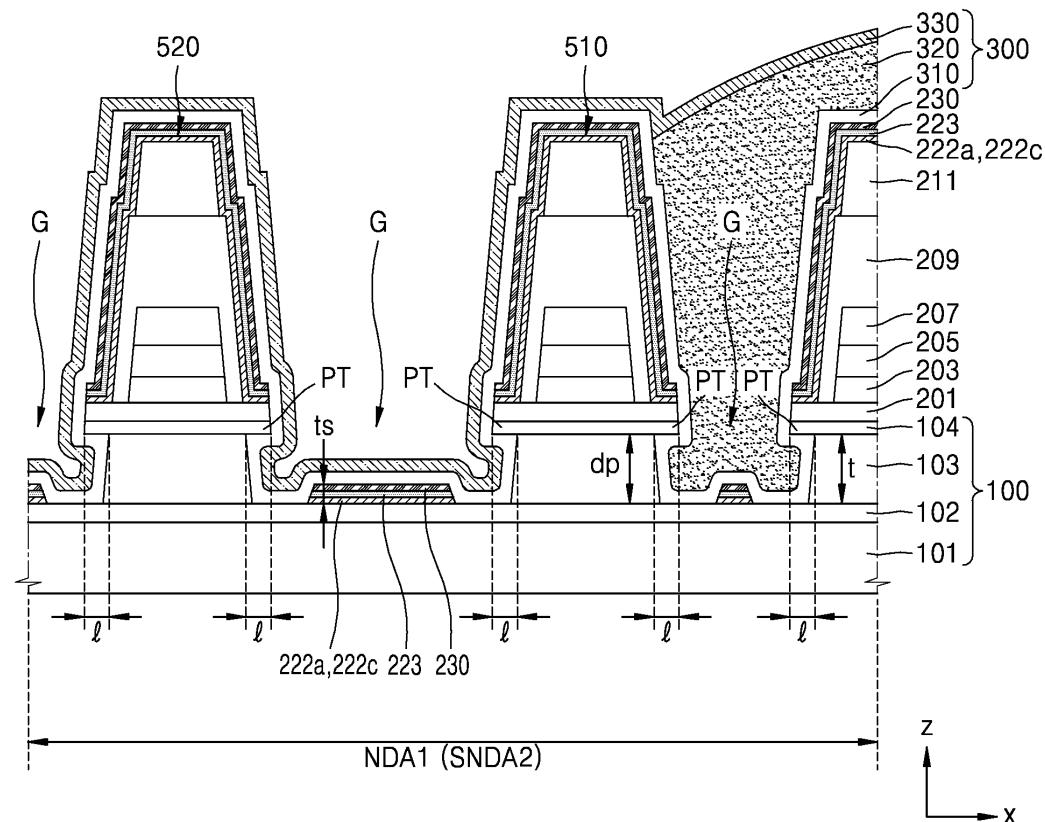

[0094] 도 8a 내지 도 8d는 본 발명의 일 실시예에 따른 표시 패널에 구비된 그루브의 단면도로서, 도 8a 내지 도 8d는 각각 도 6의 VIII- VIII'선에 따른 단면에 대응할 수 있다.

[0095] 도 8a 및 도 8b를 참조하면, 그루브(G)는 다층 막(ML)에 형성된다. 다층 막(ML)은 서로 다른 물질을 갖는 적어도 2개의 층을 포함한다. 이와 관련하여, 도 8a 및 도 8b는 유기물을 포함하는 제1층(L1)과 무기물을 포함하는 제2층(L2)을 포함하는 다층 막(ML)을 도시한다. 제1층(L1)은 유기 절연물을 포함할 수 있다. 예컨대, 제1층(L1)은 폴리이미드와 같은 고분자 수지를 포함할 수 있다. 제2층(L2)은 실리콘나이트라이드, 실리콘옥시나이트라이드나 실리콘옥사이드와 같은 무기 절연물을 포함할 수 있다. 또는, 제2층(L2)은 금속을 포함할 수 있다.

[0096] 도 8a 및 도 8b의 다층 막(ML)은 도 7을 참조하여 설명한 표시 패널의 구성요소들의 일부에 해당할 수 있다. 예컨대, 다층 막(ML)은 도 7을 참조하여 설명한 기판(100)의 서브 층일 수 있다. 또는, 다층 막(ML)은 표시 패널을 구성하는 층들, 예컨대 기판(100)위의 층들의 일부에 해당할 수 있다.

[0097] 그루브(G)는 다층 막(ML)의 깊이 방향을 따라 형성될 수 있다. 도 8a에 도시된 바와 같이 제2층(L2)을 에칭하여 제2층(L2)을 관통하는 제2홀(H2)을 형성하고, 제1층(L1)을 에칭하여 제1층(L1)의 두께 방향으로 오목한 제1리세스(R1)를 형성할 수 있다. 제1리세스(R1)와 제2홀(H2)은 공간적으로 연결되어 그루브(G)를 이룰 수 있다. 또는, 도 8b에 도시된 바와 같이 제2층(L2)을 에칭하여 제2층(L2)을 관통하는 제2홀(H2)을 형성하고, 제1층(L1)을 에칭하여 제1층(L1)을 관통하는 제1홀(H1)을 형성할 수 있다. 제1홀(H1)과 제2홀(H2)은 공간적으로 연결되어 그루브(G)를 이룰 수 있다. 전술한 에칭은 등방성 에칭 및/또는 이방성 에칭일 수 있다.

[0098] 그루브(G) 중 제2층(L2)을 지나는 부분의 폭은 제1층(L1)을 지나는 부분의 폭 보다 작게 형성될 수 있다. 예컨대, 제2홀(H2)의 폭(W2, 또는 직경)은 제1리세스(R1) 또는 제1홀(H1)의 폭(W1, 또는 직경) 보다 작게 형성될 수 있다.

[0099] 그루브(G)는 언더컷 단면을 가질 수 있다. 제2홀(H2)을 정의하는 제2층(L2)의 측면은 기판(100)의 상면(또는 하

면)에 평행한 방향(예, x방향)을 따라 제1리세스(R1) 또는 제1홀(H1)을 정의하는 제1층(L1)의 측면보다 더 돌출될 수 있다. 그루브(G)의 중심을 향해 돌출된 제2층(L2)의 부분들은 한 쌍의 처마(또는 한 쌍의 돌출 텁, PT)을 형성할 수 있다.

[0100] 그루브(G)는 앞서 도 7을 참조하여 설명한 중간층(222)을 형성하는 공정 이전에 형성될 수 있는데, 캡핑층(230)은 LiF를 포함하며, LiF는 서브층(222') 및 대향전극(223)과 마찬가지로 열증착법(thermal evaporation)으로 형성될 수 있다. 중간층의 서브층(222'), 대향전극(223), 및 캡핑층(230)은 그루브(G)에 의해 단절될 수 있다. 이와 관련하여, 도 8a 및 도 8b는 제1 및 제2기능층(222a, 222c), 대향전극(223), 및 캡핑층(230)이 그루브(G)의 텁(PT)을 중심으로 단절된 것을 도시하고 있다. 도 8a 및 도 8b에는, 제1 및 제2기능층(222a, 222c), 대향전극(223), 및 캡핑층(230)이 그루브(G) 또는 텁(PT)을 중심으로 단절된 것을 도시하나, 본 발명은 이에 한정되지 않는다. 다른 실시예로서, 제1 및 제2기능층(222a, 222c) 중 어느 하나 및/또는 캡핑층(230)은 생략될 수 있다.

[0101] 한 쌍의 텁(PT) 각각의 길이( $\ell$ )는  $2.0\mu\text{m}$  보다 작을 수 있다. 여기서, 텁(PT)의 길이( $\ell$ )는, 단면 상에서 텁(PT)을 구비하는 제2층(L2)의 바로 아래에 위치한 제1층(L1)의 측면과 상면이 만나는 지점으로부터 그루브(G)의 중심을 향해 수평 방향(또는, 기판의 상면이나 하면에 수직한 방향, x방향)을 따라 측정할 수 있다. 텁(PT)의 길이( $\ell$ )가  $2\mu\text{m}$  보다 작다는 것이  $0\mu\text{m}$ 인 경우를 포함하는 것은 아니다. 텁(PT)의 길이( $\ell$ )는  $0\mu\text{m}$  보다는 크고  $2\mu\text{m}$ 보다는 작은 범위에서 선택될 수 있다. 예컨대, 텁(PT)의 길이( $\ell$ )는  $0.3\mu\text{m} \leq \ell < 2.0\mu\text{m}$  이거나,  $0.5\mu\text{m} \leq \ell < 2.0\mu\text{m}$  이거나,  $0.8\mu\text{m} \leq \ell < 2.0\mu\text{m}$  이거나,  $1.0\mu\text{m} \leq \ell < 2.0\mu\text{m}$  일 수 있다. 텁(PT)의 길이( $\ell$ )가  $0.3\mu\text{m}$  보다 작은 경우, 서브층(222') 및 대향전극(223)이 텁(PT)을 중심으로 단절되지 않으며, 단절되지 않은 서브층(222') 등을 통해서 수분이 표시영역의 유기발광다이오드를 향해 침투하는 문제가 발생할 수 있다.

[0102] 텁(PT)의 길이( $\ell$ )가 전술한 상한을 벗어나는 경우, 표시 패널의 제조 공정이나 제조 이후에 텁(PT)에 크랙이 발생하거나 텁(PT)이 깨질 수 있다. 본원의 실험예로서, 서로 다른 길이의 텁을 갖는 표시 패널의 샘플들을 제작하였다. 샘플들은 각각  $0.8\mu\text{m}$  내지  $2.0\mu\text{m}$ 의 길이의 텁을 갖도록 제작되었으며, 제작된 샘플들을 습도가 85%이고 온도가 85°C인 챔버의 내부에 소정의 시간(예컨대, 240hr 이상) 방치한 후, 텁이 손상되었는지 여부를 측정하였다. 측정한 결과, 텁(PT)의 길이( $\ell$ )가  $2.0\mu\text{m}$  보다 작은 경우에는 손상된 텁이 없는데 반해, 텁(PT)의 길이( $\ell$ )가  $2.0\mu\text{m}$  이상인 경우에 손상된 텁이 발견되기 시작하였으며, 텁(PT)의 길이( $\ell$ )가  $2.0\mu\text{m}$  이상인 경우 텁의 손상률(손상된 텁의 개수/전체 텁의 개수)은 약 46.7% 정도임을 확인하였다.

[0103] 그루브(G)는 소정의 깊이(dp)를 가질 수 있다. 여기서, 그루브(G)의 깊이(dp)는 그루브(G) 중 제1층(L1)을 지나는 부분의 깊이를 나타낸다. 예컨대, 그루브(G)의 깊이(dp)는 텁(PT)의 바로 아래에 있는 제1층의 상면으로부터 그루브(G)의 바닥면까지의 수직 거리에 해당한다.

[0104] 그루브(G)의 깊이(dp)는 전술한 텁(PT)의 길이( $\ell$ ) 보다 클 수 있다. 일 실시예로, 그루브(G)의 깊이(dp)와 전술한 텁(PT)의 길이( $\ell$ )는,  $0.05 < (\ell / dp) < 0.50$ 이거나,  $0.1 < (\ell / dp) < 0.50$ 이거나,  $0.15 < (\ell / dp) < 0.50$ 이거나,  $0.2 < (\ell / dp) < 0.50$ 이거나,  $0.25 < (\ell / dp) < 0.50$ 이거나,  $0.25 < (\ell / dp) < 0.45$ 이거나,  $0.25 < (\ell / dp) < 0.40$ 이거나,  $0.25 < (\ell / dp) < 0.35$ 일 수 있다.

[0105] 그루브(G)의 깊이(dp)는, 그루브(G)를 중심으로 단절되는 제1 및 제2기능층(222a, 222c), 대향전극(223), 및 캡핑층(230)의 두께들의 합(ts) 보다 클 수 있다. 일 실시예로, 그루브(G)의 깊이(dp)는  $2.0\mu\text{m}$ 이거나 그 보다 클 수 있다. 또는, 그루브(G)의 깊이(dp)는  $3.0\mu\text{m}$ 이거나 그 보다 클 수 있다.

[0106] 도 8a를 참조하면, 그루브(G)의 깊이(dp)는 제1층(L1)의 두께(t) 보다 작을 수 있으며, 그루브(G)의 바닥면은 제1층(L1)의 상면과 하면 사이에 놓일 수 있다. 또는, 도 8b에 도시된 바와 같이 그루브(G)의 깊이(dp)는 제1층(L1)의 두께(t)와 동일할 수 있다. 따라서, 그루브(G)의 바닥면은 제1층(L1)의, 하면 또는 제1층(L1)의 아래에 있는 하부 층(LL)의 상면 상에 놓일 수 있다. 하부 층(LL)은 절연물, 예컨대 유기 또는 무기절연물을 포함할 수 있다. 일 실시예로, 깊이(dp)는  $6.0\mu\text{m}$ 이거나 그보다 작을 수 있다. 그루브(G)의 깊이(dp)는,  $2.0\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 이거나,  $2.5\mu\text{m} \leq dp \leq 6.0\mu\text{m}$  이거나,  $3.0\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 이거나,  $3.5\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 이거나,  $4.0\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 이거나,  $4.5\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 이거나,  $5.0\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 이거나,  $5.5\mu\text{m} \leq dp \leq 6.0\mu\text{m}$ 일 수 있다.

[0107] 한 쌍의 텁(PT) 사이의 거리, 즉 제2폭(W2)은 텁(PT)의 길이( $\ell$ ) 보다 크며, 일 실시예로 제2폭(W2)은 텁(PT)의 길이( $\ell$ )의 3배 내지 100배의 범위이거나, 5배 내지 70배의 범위이거나, 5배 내지 50배의 범위이거나, 5배 내지 30배의 범위이거나, 5배 내지 20배의 범위이거나, 7배 내지 20배의 범위일 수 있다. 제2폭(W2)은 그루브(G)의 깊이(dp)보다 클 수 있다. 예컨대, 제2폭(W2)은 그루브(G)의 깊이(dp)의 1.5배 이상이거나, 2배 이상이거나,

2,5배 이상일 수 있다.

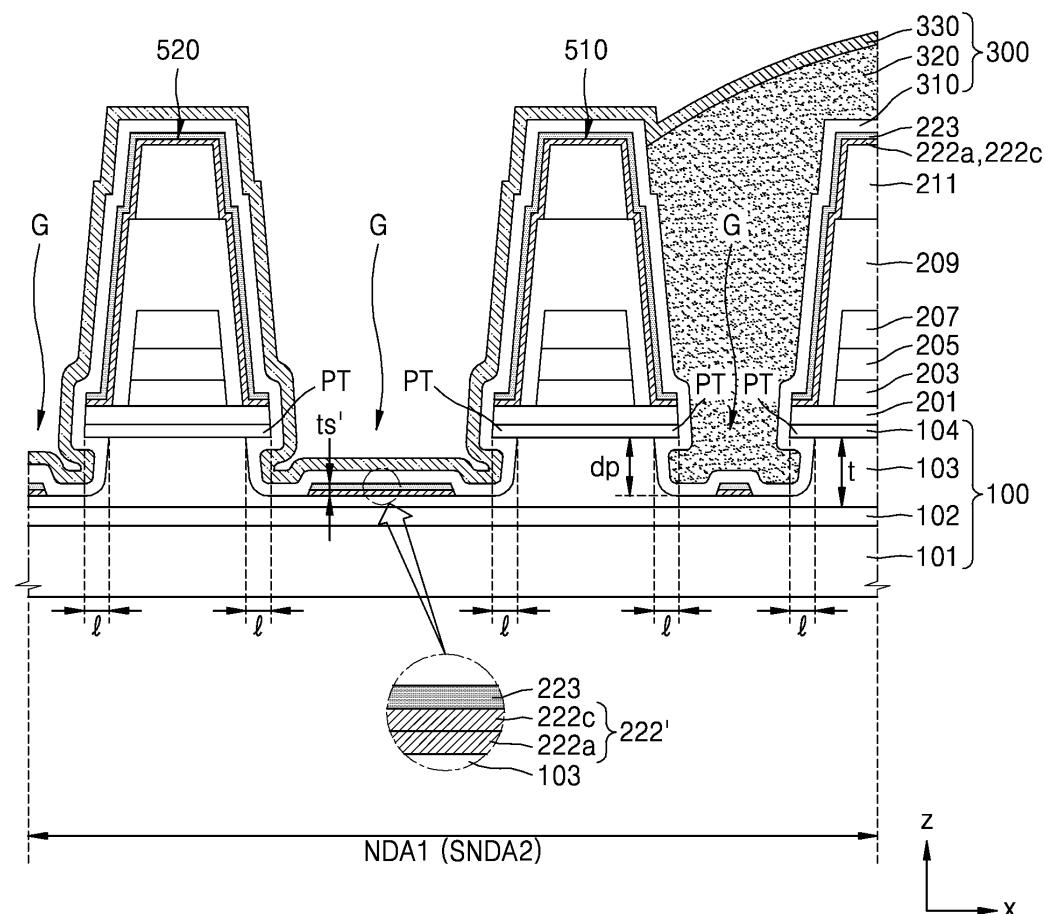

[0108] 도 8a 및 도 8b는 그루브(G) 또는 팁(PT)을 중심으로 단절된 제1 및 제2기능층(222a, 222c), 대향전극(223), 및 캡핑층(230)을 도시하였으나, 본 발명은 이에 한정되지 않는다. 다른 실시예로서, 도 8c에 도시된 바와 같이 캡핑층은 생략될 수 있다. 이 경우, 그루브(G)에 의해 단절된 층은 제1 및 제2기능층(222a, 222c) 및 대향전극(223)일 수 있다. 다른 실시예로, 제1 및 제2기능층(222a, 222c) 중 하나는 생략될 수 있다. 그루브(G)의 깊이(dp)는 제1 및 제2기능층(222a, 222c) 및 대향전극(223)의 적층체의 두께(ts') 보다 크다는 점은 앞서 설명한 바와 같다. 또한, 팁(PT)의 길이( $\ell$ ), 그루브(G)의 깊이(dp)에 대한 특징들은 앞서 도8a 및 도 8b를 참조하여 설명한 바와 같다. 도 8c에서 설명한 캡핑층이 생략된 구조는 도 8b를 참조하여 설명한 실시예에도 적용될 수 있음을 물론이다.

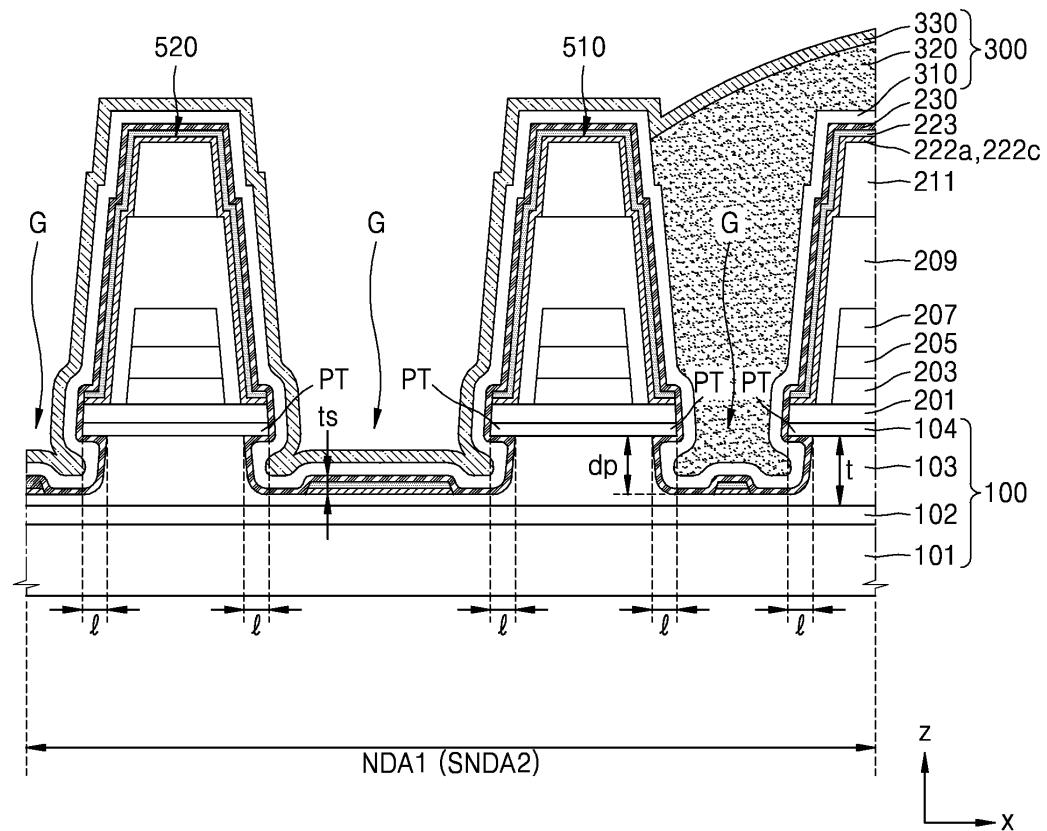

[0109] 다른 실시예로서, 캡핑층(230)은 도 8d에 도시된 바와 같이 그루브(G)를 중심으로 단절되지 않을 수 있다. 캡핑층(230)이 실리콘옥사이드, 실리콘 나이트라이드나 실리콘옥시나이트라이드와 같은 무기 절연물을 포함할 수 있으며, 전술한 무기 절연물은 화학기상증착법(CVD)로 형성될 수 있다. 무기 절연물(230)인 캡핑층(230)은 열증착법으로 형성되는 제1 및 제2기능층(222a, 222c) 및 대향전극(223) 보다 상대적으로 스텝 커버리지가 우수하므로, 도 8d에 도시된 바와 같이 그루브(G)의 내부 표면(inner surface)을 전체적으로 그리고 연속적으로 커버할 수 있다. 캡핑층(230)이 그루브(G)의 내부 표면을 연속적으로 커버하는 점을 제외한 다른 특징들은 앞서 도 8a 및 도 8b를 참조하여 설명한 바와 같다.

[0110] 다른 실시예로서, 캡핑층(230)이 유기물을 포함하는 경우, 도 8a 및 도 8b를 참조하여 설명한 바와 같이 그루브(G) 주변에서 단절될 수 있다.

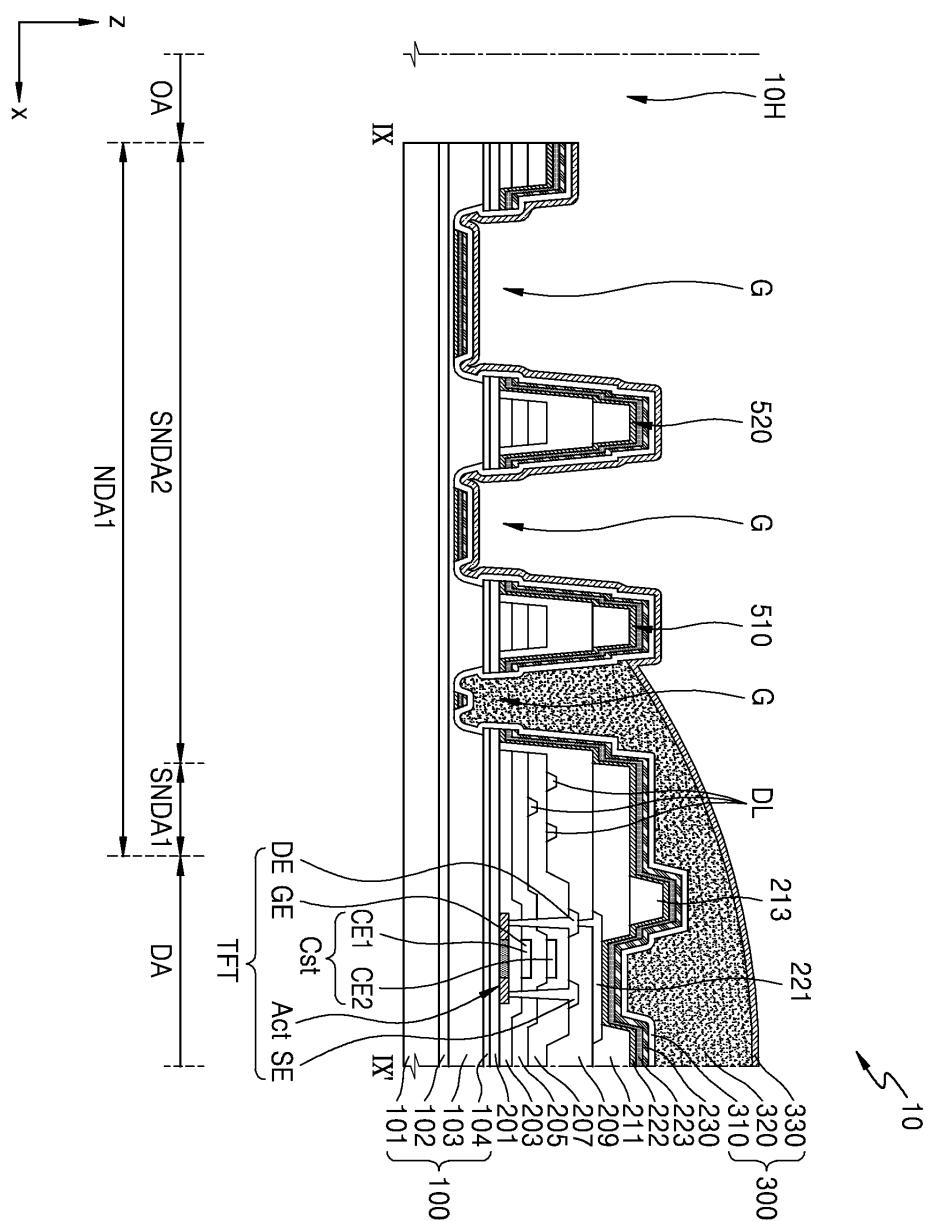

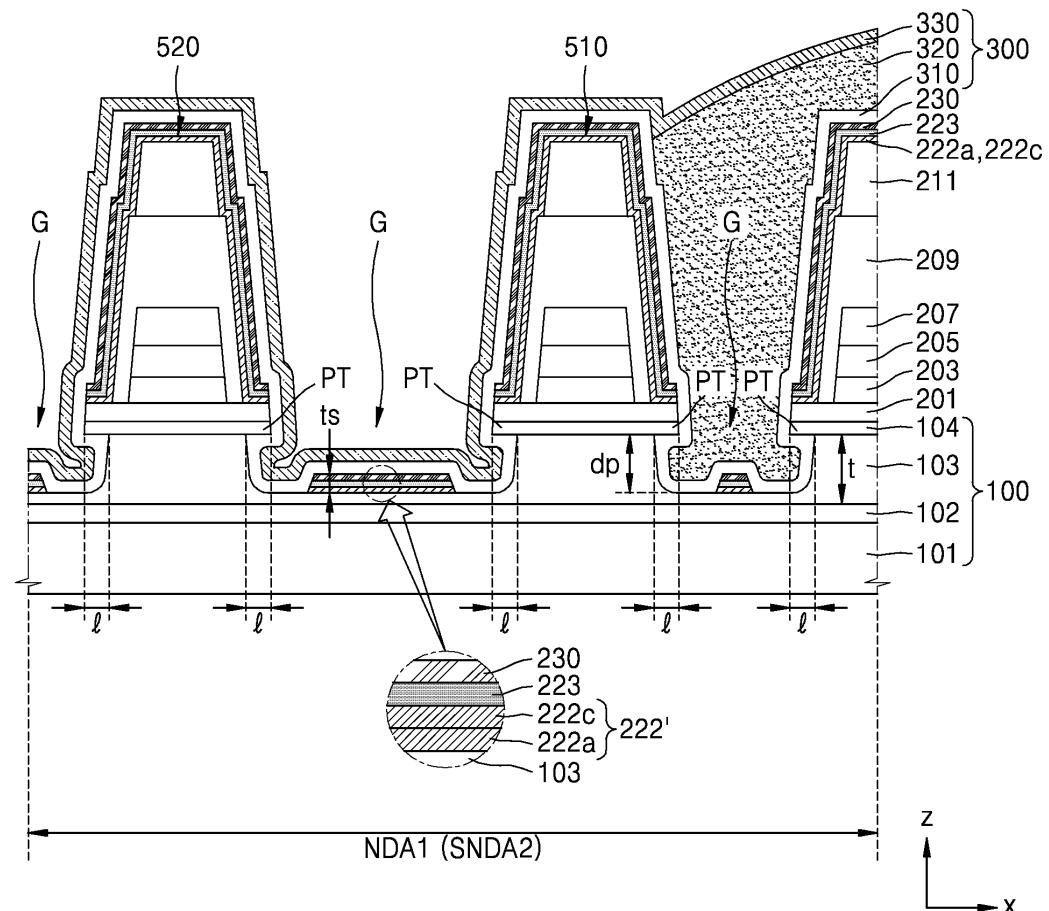

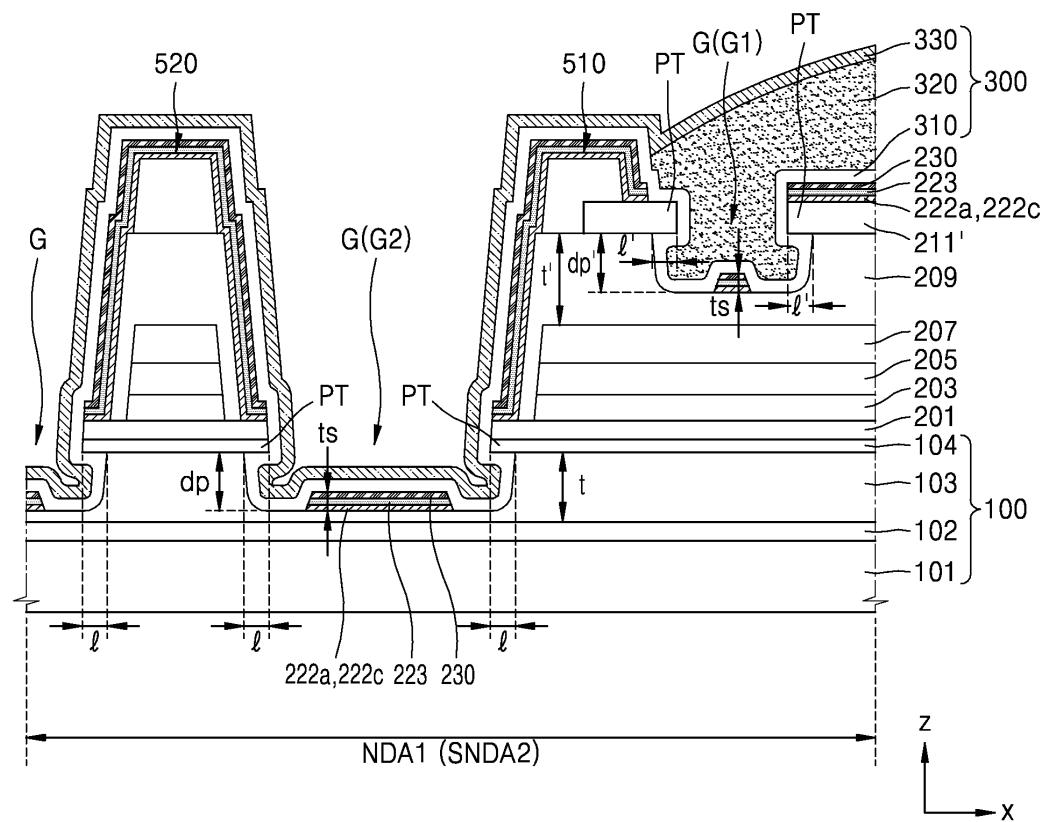

[0111] 도 9는 본 발명의 일 실시예에 따른 표시 패널의 단면도이고, 도 10은 본 발명의 일 실시예에 따른 표시 패널 중 그루브를 발췌하여 나타낸 단면도이고, 도 11은 본 발명의 다른 실시예에 따른 표시 패널 중 그루브를 발췌하여 나타낸 단면도이다. 도 9는 도 6의 IX-IX'선에 따른 단면에 대응할 수 있으며, 도 10은 도 9의 그루브를 발췌하여 확대한 단면도에 해당할 수 있다.

[0112] 도 9를 참조하면, 표시 패널(10)은 개구영역(OA), 표시영역(DA), 및 이들 사이의 제1비표시영역(NDA1)을 포함한다. 표시 패널(10)은 개구영역(OA)에 해당하는 제1개구(10H)를 포함할 수 있다.

[0113] 도 9의 표시영역(DA)을 참조하면, 표시영역(DA)에는 기판(100) 상의 박막트랜지스터(TFT) 및 스토리지 커퍼시터(Cst)가 배치된다.

[0114] 기판(100)은 다층일 수 있다. 예컨대, 기판(100)은 순차적으로 적층된, 제1베이스층(101), 제1배리어층(102), 제2베이스층(103), 및 제2배리어층(104)을 포함할 수 있다.

[0115] 제1 및 제2베이스층(101, 103)은 각각 고분자 수지를 포함할 수 있다. 예컨대, 제1 및 제2베이스층(101, 103)은 폴리에테르술폰(PES, polyethersulphone), 폴리아릴레이트(PAR, polyarylate), 폴리에테르 이미드(PEI, polyether imide), 폴리에틸렌 나프탈레이트(PEN, polyethylenene napthalate), 폴리에틸렌 테레프탈레이드(PET, polyethyleneterephthalate), 폴리페닐렌 설파이드(polyphenylene sulfide: PPS), 폴리아릴레이트(polyallylate), 폴리이미드(polyimide: PI), 폴리카보네이트(PC), 셀룰로오스 트리 아세테이트(TAC), 셀룰로오스 아세테이트 프로피오네이트(cellulose acetate propionate: CAP) 등과 같은 고분자 수지를 포함할 수 있다. 전술한 고분자 수지는 투명할 수 있다.

[0116] 제1 및 제2배리어층(102, 104)은 각각, 외부 이물질의 침투를 방지하는 배리어층으로서, 실리콘나이트라이드(SiNx) 및/또는 실리콘옥사이드(SiOx)와 같은 무기물을 포함하는 단층 또는 다층일 수 있다.

[0117] 박막트랜지스터(TFT)의 반도체층과 전극들 사이 및 스토리지 커퍼시터(Cst)의 전극들 사이에는 절연층들(201 내지 209)이 개재될 수 있다. 표시영역(DA)에는 박막트랜지스터(TFT)와 전기적으로 연결된 화소전극(221), 중간층(222), 대향전극(223), 및 캡핑층(230)이 배치될 수 있으며, 전술한 구조들은 앞서 도 7을 참조하여 설명한 바와 같다.

[0118] 화소전극(221), 중간층(222), 및 대향전극(223)을 포함하는 표시요소는 박막봉지층(300)으로 커버된다. 박막봉지층(300)은 적어도 하나의 유기봉지층 및 적어도 하나의 무기봉지층을 포함할 수 있다. 도 9는 박막봉지층(300)이 제1 및 제2무기봉지층(310, 330) 및 이들 사이에 개재된 유기봉지층(320)을 포함하는 것을 도시한다. 다른 실시예에서 유기봉지층의 개수와 무기봉지층의 개수 및 적층 순서는 변경될 수 있다.

[0119] 제1무기봉지층(310)은 알루미늄옥사이드, 티타늄옥사이드, 탄탈륨옥사이드, 하프늄옥사이드, 징크옥사이드, 실

리콘옥사이드, 실리콘나이트라이드, 또는 실리콘옥시나이트라이드와 같은 하나 이상의 무기 절연물을 포함할 수 있으며, 화학기상증착법(CVD) 등에 의해 형성될 수 있다. 유기봉지층(320)은 폴리머(polymer)계열의 소재를 포함할 수 있다. 폴리머 계열의 소재로는 아크릴계 수지, 에폭시계 수지, 폴리이미드 및 폴리에틸렌 등을 포함할 수 있다.

[0120] 도 9의 제1비표시영역(NDA1)을 참조하면, 제1비표시영역(NDA1)은 상대적으로 표시영역(DA)에 인접한 제1서브-비표시영역(SNDA1) 및 상대적으로 개구영역(OA) 또는 제1개구(10H)에 인접한 제2서브-비표시영역(SNDA2)을 포함할 수 있다.

[0121] 제1서브-비표시영역(SNDA1)은 신호라인들, 예컨대 도 5를 참조하여 설명한 데이터라인(DL)들이 지나는 영역일 수 있다. 도 9에 도시된 데이터라인(DL)들은 개구영역(OA)을 우회하는 데이터라인들에 해당할 수 있다. 제1서브-비표시영역(SNDA1)은 데이터라인(DL)들이 지나는 배선영역 또는 우회영역일 수 있다.

[0122] 데이터라인(DL)들은 도 9에 도시된 바와 같이 절연층을 사이에 두고 교변적으로 배치될 수 있다. 또는, 도시되지는 않았으나, 데이터라인(DL)들은 동일한 절연층 상에 배치될 수 있다. 이웃한 데이터라인(DL)들이 절연층(예컨대, 제2층간절연층: 207)을 사이에 두고 아래와 위에 각각 배치되는 경우, 이웃한 데이터라인(DL)들 사이의 캡(피치)을 줄일 수 있으며, 제1비표시영역(NDA1)의 폭을 줄일 수 있다. 도 9는 제1서브-비표시영역(SNDA1)에 데이터라인(DL)들이 위치하는 것을 나타내고 있으나, 앞서 도 5를 참조하여 설명한 개구영역(OA)을 우회하는 스캔라인들도 제1서브-비표시영역(SNDA1)에 위치할 수 있다.

[0123] 제2서브-비표시영역(SNDA2)은 그루브들이 배치되는 일종의 그루브영역으로서, 도 9는 제2서브-비표시영역(SNDA2)에 위치하는 3개의 그루브를 도시한다. 그루브(G)는 앞서 도 8a 및 도 8b를 참조하여 설명한 바와 같이 서로 다른 물질을 포함하는 제1 및 제2층을 구비하는 다층 막에 형성될 수 있는데, 일 실시예로서 도 9는 그루브(G)가 기판(100)에 구비된 서브층에 형성된 것을 도시한다.

[0124] 도 9의 제2서브-비표시영역(SNDA2) 및 도 10을 참조하면, 그루브(G)는 제2배리어층(104)의 일부 및 제2베이스층(103)의 일부를 제거하여 형성될 수 있다. 예컨대, 제2배리어층(104)과 베퍼층(201)을 관통하는 훌 및 제2베이스층(103)에 형성된 리세스는, 공간적으로 연결되어 그루브(G)를 형성할 수 있다. 제2베이스층(103)은 앞서 도 8a 및 도 8b를 참조하여 설명한 다층 막(ML)의 제1층(L1)에 대응하고, 제2배리어층(104)은 다층 막(ML)의 제2층(L2)에 대응할 수 있다.

[0125] 전술한 바와 같이, 그루브(G)를 형성하는 공정에서 제2배리어층(104) 상의 베퍼층(201)은 제2배리어층(104)과 함께 제거되어 그루브(G)를 형성할 수 있다. 본 명세서에서는, 베퍼층(201)과 제2배리어층(104)을 별도의 구성 요소로 설명하고 있으나, 기판(100)의 베퍼층(201)은 다층 구조를 갖는 제2배리어층(104)의 서브 층일 수 있다.

[0126] 그루브(G)의 텁(PT)은 소정의 길이( $\ell$ )를 가지며, 텁(PT)의 길이( $\ell$ )에 관한 특징은 앞서 도 8a 및 도 8b를 참조하여 설명한 바와 같다. 예컨대, 텁(PT)의 길이( $\ell$ )는  $2.0\mu\text{m}$  보다 작을 수 있다.

[0127] 그루브(G)의 깊이(dp)는 도 10에 도시된 바와 같이 제2배리어층(104)의 두께(t) 보다 작을 수 있다. 또는, 그루브(G)의 깊이(dp)는 도 11에 도시된 바와 같이 제2배리어층(104)의 두께(t)와 동일할 수 있으며, 깊이(dp)에 대한 특징은 앞서 도 8a 및 도 8b를 참조하여 설명한 바와 동일하다.

[0128] 제2서브-비표시영역(SNDA2)의 그루브(G)들에 의해 중간층의 서브층(222')에 해당하는 제1 및 제2기능층(222a, 222c), 대향전극(223), 및/또는 캡핑층(230)이 단절될 수 있음은 앞서 설명한 바와 같다.

[0129] 박막봉지층(300)의 제1무기봉지층(310)은 중간층의 서브층(222')에 해당하는 제1 및 제2기능층(222a, 222c), 대향전극(223), 및/또는 캡핑층(230) 보다 스텝 커버리지가 상대적으로 우수하다. 따라서, 제1무기봉지층(310)은 그루브(G)의 주변에서 단절되지 않은 채 연속적으로 형성될 수 있다.

[0130] 제1무기봉지층(310)은 도 9에 도시된 바와 같이 표시영역(DA) 및 제1비표시영역(NDA1)을 전체적으로 커버할 수 있다. 제1비표시영역(NDA1)에서, 제1무기봉지층(310)은 그루브(G)들의 내부 표면을 전체적으로 그리고 연속적으로 커버할 수 있다. 그루브(G)의 바닥면 상에는 텁(PT)을 중심으로 단절된 제1 및 제2기능층(222a, 222c), 대향전극(223) 및 캡핑층(230)의 스택이 배치되며, 제1무기봉지층(310)은 전술한 스택을 커버하면서 제2베이스층(103) 아래의 층, 예컨대 제1배리어층(102)과 접촉할 수 있다.

[0131] 유기봉지층(320)은 모노머를 도포한 후 이를 경화하여 형성할 수 있다. 모노머의 흐름은 격벽, 예컨대 제1 및 제2격벽(510, 520)에 의해 제어될 수 있다. 이와 관련하여, 도 9 내지 도 11에는 유기봉지층(320)의 단부가 제1 격벽(510)의 일측에 위치하는 것을 도시한다. 유기봉지층(320)은 어느 하나의 그루브(G)를 채울 수 있다. 예컨

대, 표시영역(NDA)과 제1격벽(510) 사이에 위치하는 그루브(G)의 제1무기봉지층(310) 위의 공간은 유기봉지층(320)으로 채워질 수 있다.

[0132] 제2무기봉지층(330)은 제1무기봉지층(310)과 마찬가지로 그루브(G)의 내부 표면을 전체적으로 그리고 연속적으로 커버할 수 있다. 제2무기봉지층(330)의 일부는 제2서브-비표시영역(SNDA2)에서 제1무기봉지층(310)과 직접 접촉할 수 있다. 복수의 그루브(G) 중 적어도 하나의 그루브(G) 상에서 제2무기봉지층(330)은 제1무기봉지층(310)과 직접 접촉할 수 있다. 제1 및 제2무기봉지층(310, 330)은 제1 및 제2격벽(510, 520)의 상면 위에서도 서로 접촉할 수 있다.

[0133] 도 12는 본 발명의 다른 실시예에 따른 표시 패널 중 그루브를 발췌하여 나타낸 단면도이다.

[0134] 도 12를 참조하면, 앞서 도 10을 참조하여 설명한 표시 패널과 달리 캡핑층이 생략될 수 있다. 캡핑층이 생략된 특징을 제외한 특징은 앞서 도 10을 참조하여 설명한 바와 같다. 예컨대, 그루브(G)의 텁(PT)의 길이( $\ell$ )에 관한 특징은 앞서 도 8a 내지 도 8c를 참조하여 설명한 바와 같다. 예컨대, 텁(PT)의 길이( $\ell$ )는  $2.0\mu\text{m}$  보다 작을 수 있다. 아울러, 그루브(G)의 깊이(dp)는 도 10에 도시된 바와 같이 제2배리어층(104)의 두께(t) 보다 작을 수 있다. 또는, 그루브(G)의 깊이(dp)는 도 11에 도시된 바와 같이 제2배리어층(104)의 두께(t)와 동일할 수 있으며, 깊이(dp)에 대한 특징은 앞서 도 8a 내지 도 8c를 참조하여 설명한 바와 동일하다. 도 12를 참조하여 설명한 캡핑층이 생략된 구조는 도 14 내지 도 17을 참조하여 설명할 실시예들 및 이들로부터 파생되는 실시예들에도 적용될 수 있음을 물론이다.

[0135] 도 9 내지 도 11을 참조하여 설명한 캡핑층(230)은 LiF와 같이 스텝 커버리지가 상대적으로 낮은 물질을 포함할 수 있으며, 따라서 도 9 내지 도 11은 그루브(G)를 중심으로 단절된 구조를 도시하나, 본 발명은 이에 한정되지 않는다.

[0136] 도 13은 본 발명의 다른 실시예에 따른 표시 패널 중 그루브를 발췌하여 나타낸 단면도이다.

[0137] 도 13을 참조하면, 캡핑층(230)은 무기절연물을 포함할 수 있다. 화학기상증착법과 같은 공정을 통해 형성되는 무기절연물의 캡핑층(230)은 스텝 커버리지가 상대적으로 우수하여 그루브(G)를 중심으로 단절되지 않고, 그루브(G)의 내부 표면을 연속적으로 커버할 수 있다.

[0138] 캡핑층(230)은 실리콘나이트라이드, 실리콘옥사이드 또는 실리콘옥시나이트라이드와 같은 무기물을 포함할 수 있으며, 캡핑층(230) 상에는 제1무기봉지층(310)이 배치될 수 있다. 제1무기봉지층(310)도 전술한 무기절연물을 포함할 수 있다. 일부 실시예에서, 무기절연물을 포함하는 캡핑층(230)은 다층인 제1무기봉지층(310)의 서브층일 수 있다. 일 실시예로, 막질이 서로 다른 적어도 2개의 실리콘옥시나이트라이드를 포함하는 제1무기봉지층(310) 중 어느 하나의 층이 캡핑층(230)일 수 있다.

[0139] 도 13을 참조하여 설명한 캡핑층(230)의 구조는 도 14 내지 도 17을 참조하여 설명한 실시예, 및 이들로부터 파생되는 실시예에도 적용될 수 있음을 물론이다.

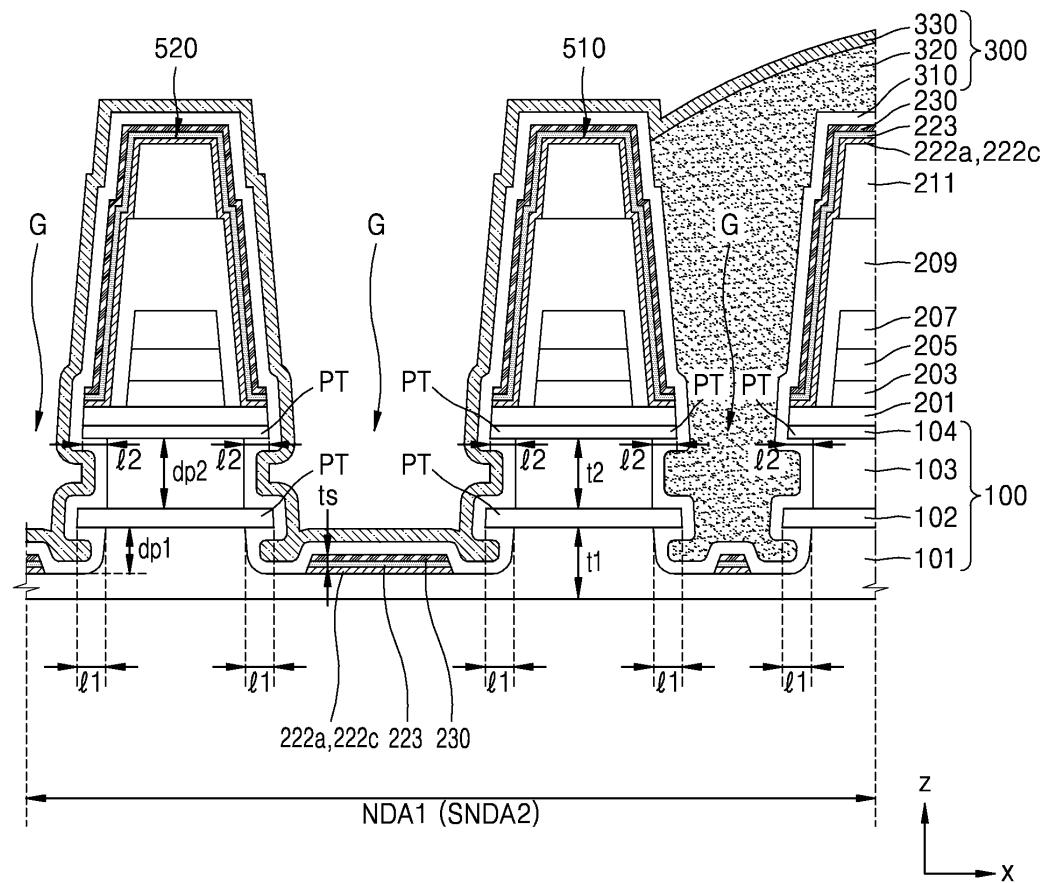

[0140] 도 14는 본 발명의 다른 실시예에 따른 표시 패널 중 그루브를 발췌하여 나타낸 단면도이다.

[0141] 도 14를 참조하면, 그루브(G)는 깊이 방향(또는 기판의 두께 방향)을 따라 중첩된 복수의 언더컷 단면을 가질 수 있다. 예컨대, 제1베이스층(101)과 제1배리어층(102)이 언더컷 단면(이하, 제1언더컷 단면이라 함)을 가지고, 제2베이스층(103)과 제2배리어층(104)이 언더컷 단면(이하, 제2언더컷 단면이라 함)을 가질 수 있다. 그루브(G)는 전술한 제1 및 제2언더컷 단면들이 중첩된 구조일 수 있다.

[0142] 제1배리어층(102) 및 제2배리어층(104) 각각의 텁(PT)은, 제1길이( $\ell$  1) 및 제2길이( $\ell$  2)를 갖는다. 제1 및 제2길이( $\ell$  1,  $\ell$  2)에 대한 특징은 앞서 도 8a 및 도 8b를 참조하여 설명한 길이( $\ell$ )에 대한 특징과 동일하다. 예컨대, 제1 및 제2길이( $\ell$  1,  $\ell$  2) 각각은  $2.0\mu\text{m}$  보다 작을 수 있다.

[0143] 제1베이스층(101) 및 제2베이스층(103) 각각은, 제1깊이(dp1) 및 제2깊이(dp2)를 갖는다. 제2베이스층(103)의 제2깊이(dp2)는 제2베이스층(103)의 두께(t2)와 동일할 수 있고, 제1베이스층(101)의 제1깊이(dp1)는 제1베이스층(101)의 두께(t1) 보다 작을 수 있다. 전술한 특징을 만족한다면, 앞서 도 8a 및 도 8b를 참조하여 설명한 깊이(dp)에 대한 특징은 도 14에 도시된 제1 및 제2깊이(dp1, dp2)에 대해서도 동일하게 적용될 수 있다. 제1 및 제2깊이(dp1, dp2)는 텁(PT)의 길이( $\ell$ )보다 클 수 있다. 또한, 제1 및 제2깊이(dp1, dp2)는 각각 대응하는 텁(PT)의 제1 및 제2길이( $\ell$  1,  $\ell$  2) 보다 클 수 있다. 한편, 제1깊이(dp1)는 그루브(G)를 중심으로 단절되는 제1 및 제2기능층(222a, 222c), 대향전극(223), 및 캡핑층(230)의 두께들의 합(ts) 보다 클 수 있다. 일 실시예로,

제1깊이(dp1)는  $2.0\mu\text{m}$ 이상이거나,  $3.0\mu\text{m}$ 이상일 수 있다.

[0144] 도 9 내지 도 14는, 그루브(G)가 형성되는 다층 막이 기판(100)의 서브층들에 형성된 것을 도시하나, 본 발명은 이에 한정되지 않는다. 도 15 및 도 16을 참조하여 후술하는 바와 같이 그루브(G)는 기판(100) 위에 위치할 수 있다.

[0145] 도 15는 본 발명의 다른 실시예에 따른 표시 패널 중 제1비표시영역에 배치된 그루브들을 나타낸 단면도이다.

[0146] 도 15를 참조하면, 복수의 그루브(G)들 중 하나의 그루브(G, 이하 제1그루브 G1라 함)는 기판(100) 위에 위치할 수 있으며, 다른 하나의 그루브(G, 이하, 제2그루브 G2라 함)는 기판(100)의 서브층들의 일부를 제거하여 형성할 수 있다. 제2그루브(G2)에 대한 특징은 앞서 도 8a 내지 도 11을 참조하여 설명한 바와 동일하므로, 이하에 서는 제1그루브(G1)를 중심으로 설명한다.

[0147] 제1그루브(G1)는 제1절연층(209) 및 제1절연층(209) 상의 제2절연층(211')을 제거하여 형성할 수 있다. 제1절연층(209)은 앞서 도 8a 및 도 8b를 참조하여 설명한 다층 막(ML)의 제1층(L1)에 대응하고, 제2절연층(211')은 다층 막(ML)의 제2층(L2)에 대응할 수 있다. 제1절연층(209)은 폴리아미드와 같은 유기물을 포함할 수 있고, 제2절연층(211')은 실리콘나이트라이드나 실리콘옥사이드와 같은 무기물을 포함할 수 있다.

[0148] 제1그루브(G1)는 언더컷 단면을 가질 수 있다. 예컨대, 도 15에 도시된 바와 같이, 제2절연층(211')의 훌과 제1절연층(209)의 리세스가 제1그루브(G1)를 이룰 수 있다. 다른 실시예로서, 도시되지는 않았으나, 제2절연층(211')의 훌과 제1절연층(209)의 훌이 제1그루브(G1)를 이룰 수 있음을 물론이다.

[0149] 제2절연층(211')에 구비된 텁(PT)의 길이( $\ell'$ )에 대한 특징은 앞서 도 8a 및 도 8b를 참조하여 설명한 길이( $\ell$ )에 대한 특징과 동일하다. 예컨대, 텁(PT)의 길이( $\ell'$ )는  $2.0\mu\text{m}$  보다 작을 수 있다.

[0150] 제1그루브(G1)의 깊이(dp'), 즉 제1절연층(209)의 리세스 또는 훌의 깊이에 대한 특징은 앞서 도 8a 및 도 8b를 참조하여 설명한 깊이(dp)에 대한 특징과 동일하다. 예컨대, 제1그루브(G1)의 깊이(dp')는 텁(PT)의 길이( $\ell'$ ) 보다 클 수 있다. 제1그루브(G1)의 깊이(dp')는 제1절연층(209)의 두께( $t'$ )와 같거나 그 보다 작을 수 있으며, 예컨대  $2.0\mu\text{m}$  이상이거나,  $3.0\mu\text{m}$  이상일 수 있다.

[0151] 여기서 제1절연층(209)의 두께라 함은, 제1그루브(G1)가 배치된 영역에서 제1절연층(209)의 상면과 하면 사이의 수직 거리로서, 도 15는 제2층간절연층(207)의 상면이 제1절연층(209)의 하면일 수 있다.

[0152] 제1 및 제2그루브(G1, G2)를 중심으로, 제1 및 제2기능층(222a, 222c), 대향전극(223), 및 캡핑층(230)이 단결될 수 있으며, 제1 및 제2그루브(G1, G2) 각각의 깊이(dp', dp)는 전술한 제1 및 제2기능층(222a, 222c), 대향전극(223), 및 캡핑층(230)의 스택의 두께(ts) 보다 클 수 있음을 도 8a 및 도 8b를 참조하여 설명한 바와 같다.

[0153] 제1 및 제2그루브(G1, G2)는 각각의 내부 표면은 제1무기봉지층(310)에 의해 연속적으로 커버될 수 있다. 제1그루브(G1) 중 제1무기봉지층(310) 위의 공간은 유기봉지층(320)으로 채워질 수 있다. 제1 및 제2그루브(G1, G2) 사이에는 격벽(530)이 위치할 수 있으며, 유기봉지층(320)의 단부는 격벽(530)의 일 측에 위치할 수 있다.

[0154] 도 15에서는 제2그루브(G2)가 도 10에 도시된 그루브와 동일한 구조인 것을 설명하였으나, 본 발명에서는 이에 한정되지 않는다. 다른 실시예로, 제2그루브(G2)는 도 11 내지 도 14를 참조하여 설명한 그루브와 동일한 구조를 가질 수 있다.

[0155] 도 15를 참조하여 설명한 특징, 예컨대 제1비표시영역(NDA1)의 그루브들, 예컨대 제1 및 제2그루브(G1, G2)가 서로 다른 다층 막에 형성된 특징은 다른 실시예에도 적용될 수 있다. 예컨대, 전술한 특징은 앞서 도 10 내지 도 14를 참조하여 설명한 실시예들, 도 16을 참조하여 후술할 실시예, 또는/및 이들로부터 파생되는 실시예들에도 적용될 수 있음을 물론이다.

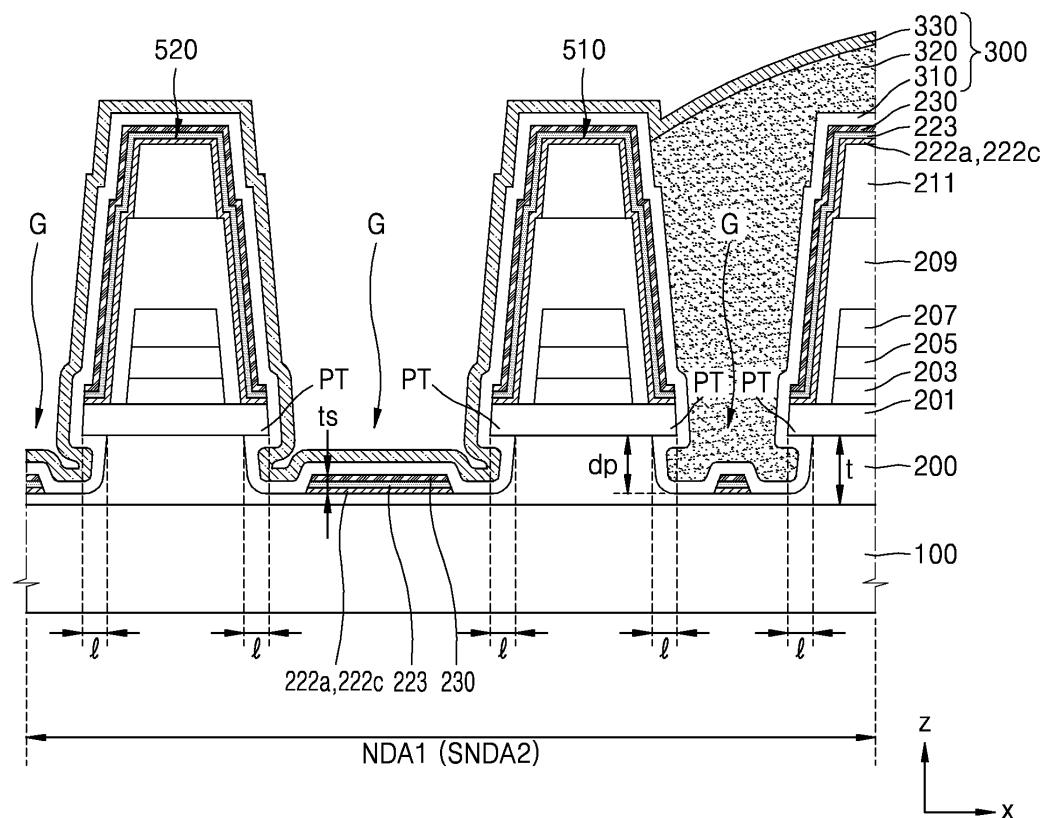

[0156] 도 16은 본 발명의 다른 실시예에 따른 표시 패널 중 제1비표시영역에 배치된 그루브들을 나타낸 단면도이다.

[0157] 도 16을 참조하면, 하나 또는 그 이상의 그루브(G)는 기판(100) 상에 위치하는 다층 막, 예컨대 절연층(200)과 베퍼층(201)의 다층 막에 형성될 수 있다. 절연층(200)은 베퍼층(201)과 다른 물질, 예컨대 폴리아미드와 같은 유기물을 포함할 수 있다. 베퍼층(201)은 도 7을 참조하여 설명한 바와 같이 무기물을 포함할 수 있다. 도시되지는 않았으나, 절연층(200)은 도 16에 도시된 바와 같이 제1비표시영역(NDA1) 뿐만 아니라 표시영역에도 존재할 수 있으며, 표시영역에서도 절연층(200)은 기판(100)과 베퍼층(201) 사이에 위치할 수 있다.

- [0158] 그루브(G)는 언더컷 단면을 가질 수 있다. 그루브(G)는 베피층(201)의 홀과 절연층(200)의 리세스 또는 홀이 공간적으로 연결되어 형성될 수 있다. 그루브(G)의 중심을 향해 연장된 베피층(201)의 팁(PT)의 길이( $\ell$ )는 앞서 도 8a 및 도 8b를 참조하여 설명한 내용과 같다. 예컨대, 팁(PT)의 길이( $\ell$ )는 2. 0 $\mu\text{m}$  보다 작을 수 있다. 그루브(G)의 깊이(dp)는 절연층(200)의 두께(t)와 같거나 그보다 작을 수 있다. 깊이(dp)에 대한 다른 특징은 도 8a 및 도 8b를 참조하여 설명한 내용과 동일하므로, 앞서 설명한 내용으로 간음한다.

- [0159] 기판(100) 위에 배치된 절연층(200)과 베피층(201)의 다층 막에 그루브(G)가 형성되므로, 기판(100)은 다양한 종류의 소재를 포함할 수 있다. 예컨대, 기판(100)은 무기물을 포함하거나, 유기물을 포함하거나 이 둘을 모두 포함할 수 있다. 예컨대, 기판(100)은 글래스, 금속, 수지 등과 같이 다양한 종류의 물질을 포함할 수 있다.

- [0160] 도 17은 본 발명의 다른 실시예에 따른 표시 패널의 단면도이다.

- [0161] 도 17에 도시된 표시 패널(10')은 앞서 도 9를 참조하여 설명한 표시 패널(10)과 달리 평탄화층(410)을 더 포함하는 점에 차이가 있다. 이하에서는 설명의 편의를 위하여 차이점을 중심으로 설명한다.

- [0162] 평탄화층(410)은 유기절연물을 포함할 수 있다. 일 실시예로서, 평탄화층(410)은 박막봉지층(300) 상에 포토레지스트(네거티브 또는 포지티브)이거나 폴리머(polymer) 계열의 유기물을 도포하고 이를 패터닝하여 형성할 수 있다. 평탄화층(410)의 끝단(410E)은 도 17에 도시된 바와 같이 어느 하나의 그루브(G)를 지나는 수직 선 상에 놓일 수 있다. 다른 실시예로서, 평탄화층(410)의 끝단(410E)은 기판(100)의 끝단(100E)과 동일한 수직 선 상에 놓일 수 있다.

- [0163] 평탄화층(410)은 제2서브-비표시영역(SNDA2) 중 유기봉지층(320)이 존재하지 않는 영역을 커버함으로써, 표시 패널(10)의 편평도를 향상시킬 수 있다. 따라서, 표시 패널(10) 상에 직접 형성되거나 점착층에 의해 결합되는 입력 감지 부재나 광학적 기능 부재 등이 표시 패널(10)로부터 분리 또는 이탈 것을 방지할 수 있다.

- [0164] 이와 같이 본 발명은 도면에 도시된 일 실시예를 참고로 하여 설명하였으나 이는 예시적인 것에 불과하며 당해 분야에서 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 실시예의 변형이 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호 범위는 첨부된 특허청구범위의 기술적 사상에 의하여 정해져야 할 것이다.

- ### 부호의 설명

- [0165] 10, 10': 표시 패널

100: 기판

101: 제1베이스층

102: 제1배리어층

103: 제2베이스층

104: 제2배리어층

G: 그루브

200: 절연층

201: 베피층

300: 박막봉지층

209: 제1절연층

211, 211': 제2절연층

L1: 제1층

L2: 제2층

ML: 다층 막

## 도면

## 도면1

## 도면2

도면3

도면4

도면5

도면6

도면7

도면8a

도면8b

도면8c

도면8d

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17