(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5426921号

(P5426921)

(45) 発行日 平成26年2月26日(2014.2.26)

(24) 登録日 平成25年12月6日(2013.12.6)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 2 6 Z

請求項の数 1 (全 46 頁)

(21) 出願番号 特願2009-109648 (P2009-109648)

(22) 出願日 平成21年4月28日 (2009.4.28)

(65) 公開番号 特開2010-253186 (P2010-253186A)

(43) 公開日 平成22年11月11日 (2010.11.11)

審査請求日 平成24年2月21日 (2012.2.21)

(73) 特許権者 000132747

株式会社ソフィア

群馬県桐生市境野町7丁目201番地

(74) 代理人 100075513

弁理士 後藤 政喜

(74) 代理人 100114236

弁理士 藤井 正弘

(74) 代理人 100120260

弁理士 飯田 雅昭

(74) 代理人 100137604

弁理士 須藤 淳

(72) 発明者 田中 雅也

群馬県太田市吉沢町990番地 株式会社

ソフィア内

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

遊技に係わる演出を行う複数の演出装置を備える遊技機において、

前記複数の演出装置を複数グループに分割し、該分割されたグループに属する演出装置

を制御するためのグループ単位制御手段を各グループ毎に設けるとともに、

複数の前記グループ単位制御手段を統括的に制御するグループ統括制御手段を設け、

該各グループ単位制御手段と該グループ統括制御手段とを、複数の接続線を一体化して

構成したハーネスによりコネクタを介して接続し、

該ハーネスは、

前記グループ統括制御手段から前記グループ単位制御手段へタイミング信号を伝達する

タイミング信号線と、

前記グループ統括制御手段から前記グループ単位制御手段へ演出制御データを伝達する

データ線と、

前記グループ単位制御手段に電源電圧を供給するための電源線と、

を含んでおり、

前記グループ統括制御手段は、

前記グループ単位制御手段へのデータ送信を開始する際に、前記タイミング信号線の信

号レベルをハイレベルに維持させた状態で前記データ線の信号レベルをハイレベルからロ

ウレベルに変化させることで送信開始を指令する送信開始指令手段と、

前記送信開始の指令後に、前記データ線の信号レベルを送信データに対応する信号レベ

10

ルに設定しながら、前記タイミング信号線の信号レベルを繰り返し変化させることによって、前記グループ単位制御手段にデータを順次送信するとともに、該データ線の信号レベルの変更を、前記タイミング信号線の信号レベルがロウレベルとなっている状態で行う送信手段と、

前記グループ単位制御手段へのデータ送信を終了する際に、前記タイミング信号線の信号レベルをハイレベルに維持させた状態で前記データ線の信号レベルをロウレベルからハイレベルに変化させることで送信終了を指令する送信終了指令手段と、

を備え、

前記グループ単位制御手段は、

前記ハーネスを構成するデータ線から、当該グループ単位制御手段宛の演出制御データを取り込む取込手段と、

10

前記ハーネスを構成する電源線からの電源供給が開始された場合に、当該グループ単位制御手段自身の初期化を行う初期化手段と、

を備えるとともに、該演出制御データに基づいて対応するグループに属する演出装置を制御することを特徴とする遊技機。

【発明の詳細な説明】

【技術分野】

【0001】

グループに分割された演出装置を制御する複数のグループ単位制御手段と、複数のグループ単位制御手段を制御するグループ統括制御手段とを備える遊技機に関し、特に、グループ統括制御手段からグループ単位制御手段へのデータ送信方法に関する。

20

【背景技術】

【0002】

主制御部と周辺制御部との間、特に主制御部から周辺制御部への信号の伝達方式を改良することにより、信号線系統の煩雑化を解消し、電気的構成の簡略化を図ることができる遊技機が知られている。この遊技機では、主制御部から周辺制御部への指令信号の伝送を、作動指令対象となる周辺制御部を特定可能な状態にて行う。これにより、複数の周辺制御部への信号伝送経路を共通化することが可能となる。その結果、指令信号の伝達経路を個々の周辺制御部毎に形成する態様と比較して信号線の数を大幅に減らすことができ、また、主制御部側の指令信号の出力ポートを統合できるので信号線系統の煩雑化を解消し、電気的構成の簡略化を図ることができる（例えば、特許文献1参照）。

30

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001-038021号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に開示された遊技機では、これ以上に基板間の配線を少なくすることはできなかった。

40

【0008】

本発明は、グループ統括制御手段とグループ単位制御手段とを接続する接続線の数を削減できる遊技機を提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明は、遊技に係わる演出を行う複数の演出装置を備える遊技機において、前記複数の演出装置を複数グループに分割し、該分割されたグループに属する演出装置を制御するためのグループ単位制御手段を各グループ毎に設けるとともに、複数の前記グループ単位制御手段を統括的に制御するグループ統括制御手段を設け、該各グループ単位制御手段と該グループ統括制御手段とを、複数の接続線を一体化して構成したハーネスによりコネク

50

タを介して接続し、該ハーネスは、前記グループ統括制御手段から前記グループ単位制御手段へタイミング信号を伝達するタイミング信号線と、前記グループ統括制御手段から前記グループ単位制御手段へ演出制御データを伝達するデータ線と、前記グループ単位制御手段に電源電圧を供給するための電源線と、を含んでおり、前記グループ統括制御手段は、前記グループ単位制御手段へのデータ送信を開始する際に、前記タイミング信号線の信号レベルをハイレベルに維持させた状態で前記データ線の信号レベルをハイレベルからロウレベルに変化させることで送信開始を指令する送信開始指令手段と、前記送信開始の指令後に、前記データ線の信号レベルを送信データに対応する信号レベルに設定しながら、前記タイミング信号線の信号レベルを繰り返し変化させることによって、前記グループ単位制御手段にデータを順次送信するとともに、該データ線の信号レベルの変更を、前記タイミング信号線の信号レベルがロウレベルとなっている状態で行う送信手段と、前記グループ単位制御手段へのデータ送信を終了する際に、前記タイミング信号線の信号レベルをハイレベルに維持させた状態で前記データ線の信号レベルをロウレベルからハイレベルに変化させることで送信終了を指令する送信終了指令手段と、を備え、前記グループ単位制御手段は、前記ハーネスを構成するデータ線から、当該グループ単位制御手段宛の演出制御データを取り込む取込手段と、前記ハーネスを構成する電源線からの電源供給が開始された場合に、当該グループ単位制御手段自身の初期化を行う初期化手段と、を備えるとともに、該演出制御データに基づいて対応するグループに属する演出装置を制御する。

【発明の効果】

【0015】

本発明によると、タイミング信号線及びデータ線だけを用いて、データの送信開始と送信終了をグループ単位制御手段に通知できるので、基板間の配線をさらに少なくすることができます。

【図面の簡単な説明】

【0021】

【図1】本発明の実施形態の遊技機の説明図である。

【図2】本発明の実施形態の遊技盤の正面図である。

【図3】本発明の実施形態の遊技機の構成を示すブロック図である。

【図4】本発明の実施形態の演出制御装置の構成を示すブロック図である。

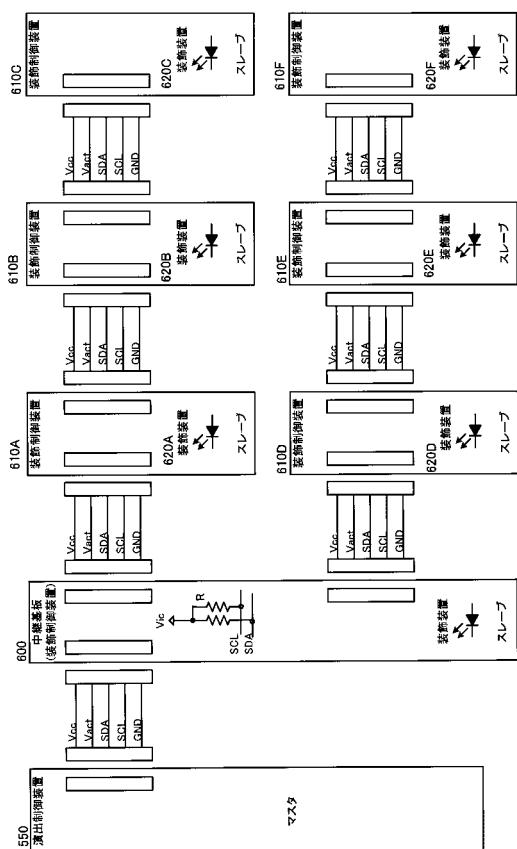

【図5】本発明の実施形態の装飾制御装置の接続の説明図である。

【図6】本発明の実施形態の装飾制御装置のブロック図である。

【図7】本発明の実施形態のI<sup>2</sup>C I/Oエクスパンダのブロック図である。

【図8A】本発明の実施形態の装飾装置を制御する装飾制御装置のI<sup>2</sup>C I/Oエクスパンダ周辺の回路図である。

【図8B】本発明の実施形態の役物駆動MOT及び役物駆動SOLを制御する装飾制御装置のI<sup>2</sup>C I/Oエクスパンダ周辺の回路図である。

【図9】本発明の実施形態の中継基板の入出力に関する接続線の回路図である。

【図10】本発明の実施形態の装飾制御装置の入出力に関する接続線の回路図である。

【図11】本発明の実施形態の装飾制御装置の配線基板におけるSDA接続パターン及びSCL接続パターンの説明図である。

【図12】本発明の実施形態のI<sup>2</sup>C I/OエクスパンダのVcc端子への電源の供給方法の説明図である。

【図13】本発明の実施形態の演出制御装置から装飾制御装置に出力されるデータに含まれるアドレスの説明図である。

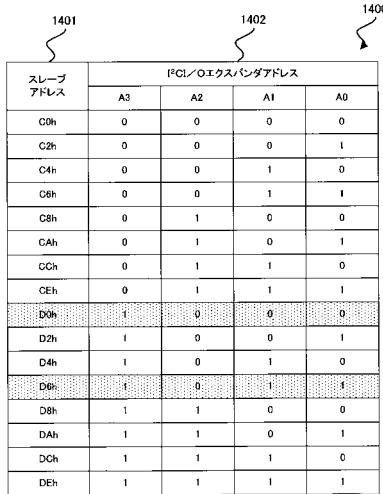

【図14】本発明の実施形態のI<sup>2</sup>C I/Oエクスパンダアドレステーブルの説明図である。

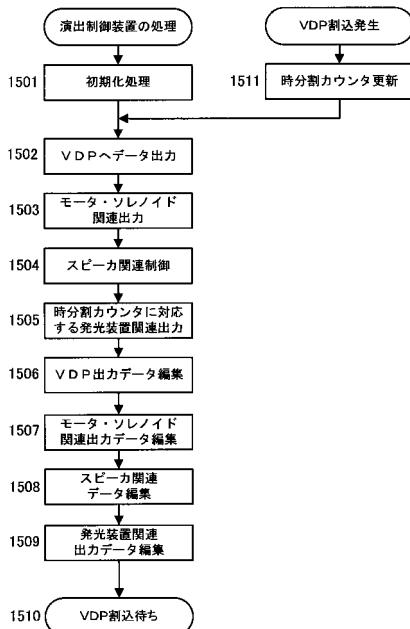

【図15】本発明の実施形態の演出制御装置による処理のフローチャートである。

【図16】本発明の実施形態のスレーブ選択順序テーブルの説明図である。

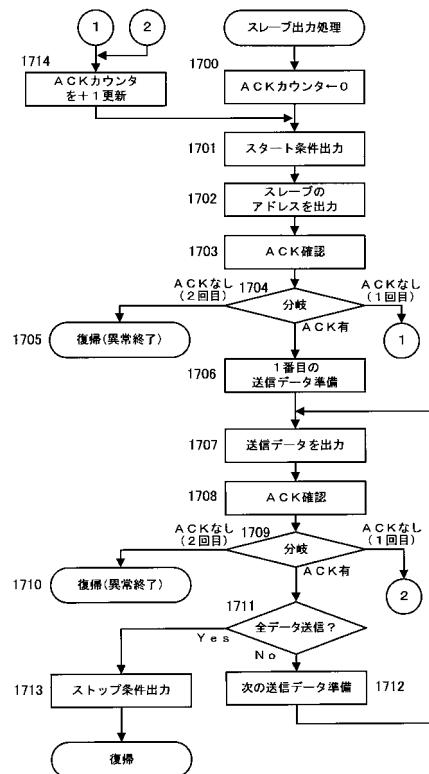

【図17】本発明の実施形態のマスタI<sup>C</sup>によるスレーブ出力処理のフローチャートである。

10

20

30

40

50

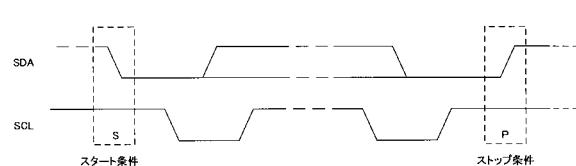

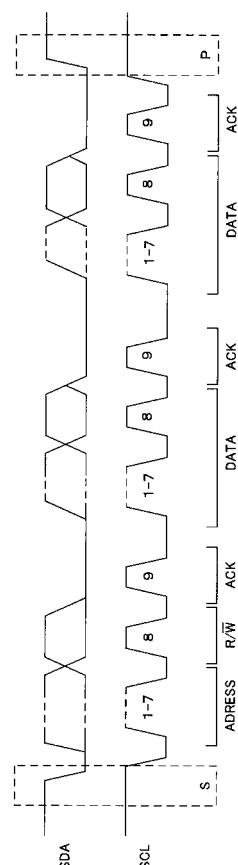

【図18】本発明の実施形態のマスタICが接続線SDA及び接続線SCLを介して出力するデータのスタート条件及びストップ条件の説明図である。

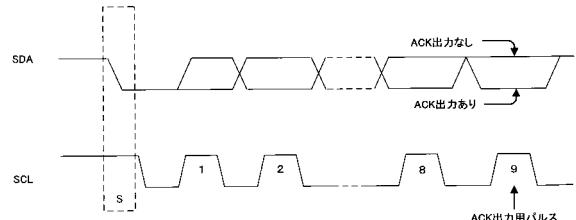

【図19】本発明の実施形態のマスタICから出力されたデータが入力された装飾制御装置610が返答信号を出力するタイミングチャートである。

【図20】本発明の実施形態のマスタICが演出制御データを出力する場合の接続線SDA及び接続線SCLの信号レベルのタイミングチャートである。

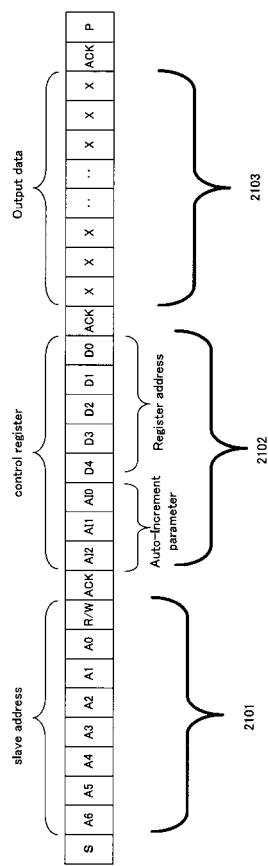

【図21】本発明の実施形態のマスタICが装飾制御装置にオールコールアドレスを設定する場合に、マスタICから出力されるデータの説明図である。

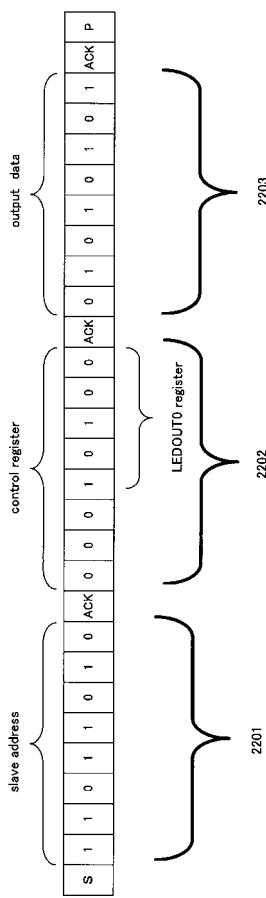

【図22】本発明の実施形態のオールコールアドレスが設定されている装飾制御装置を装飾制御する場合に、演出制御装置から出力されるデータの説明図である。 10

【図23】本発明の実施形態の演出制御装置に複数のマスタICが備わる場合のマスタICと装飾制御装置との接続の説明図である。

【発明を実施するための形態】

【0022】

(第1実施形態)

以下、本発明の実施形態について、図1～図23を参照して説明する。

【0023】

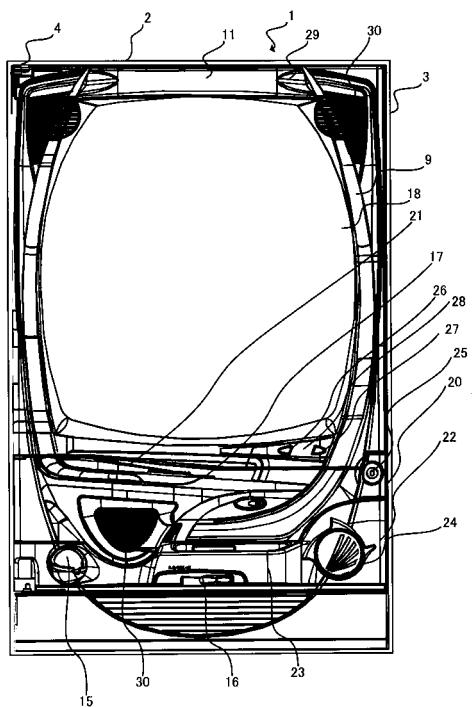

図1は、本発明の実施形態の遊技機1の説明図である。

【0024】

遊技機1の前面枠(遊技枠)3は本体枠(外枠)2にヒンジ4を介して、遊技機1の前面に開閉回動可能に組み付けられる。前面枠3の表側には、遊技盤10(図2参照)が収装される。また、前面枠3には、遊技盤10の前面を覆うカバーガラス(透明部材)を備えたガラス枠18が取り付けられている。 20

【0025】

ガラス枠18のカバーガラスの周囲には、装飾光が発光される装飾部材9が備えられている。この装飾部材9の内部にはランプやLED等からなる装飾装置620(図3参照)が備えられている。この装飾装置620を所定の発光態様によって発光することによって、装飾部材9が所定の発光態様によって発光する。

【0026】

ガラス枠18の左右には、音響(例えば、効果音)を発するスピーカ30が備えられている。また、ガラス枠18の上方には照明ユニット11が備えられている。照明ユニット11の内部には、前述した装飾装置620が備えられている。 30

【0027】

照明ユニット11の右側には、遊技機1において異常が発生したことを報知するための異常報知LED29が備えられている。

【0028】

前面枠3の下部の開閉パネル20には図示しない打球発射装置に遊技球を供給する上皿21が、固定パネル22には灰皿15、下皿23及び打球発射装置の操作部24等が備えられる。下皿23には、下皿23に貯まった遊技球を排出するための下皿球抜き機構16が備えられる。前面枠3下部右側には、ガラス枠18を施錠するための鍵25が備えられている。 40

【0029】

また、遊技者が操作部24を回動操作することによって、打球発射装置は、上皿21から供給される遊技球を発射する。

【0030】

また、上皿21の上縁部には、遊技者からの操作入力を受け付けるための演出ボタン17が備えられている。

【0031】

遊技者が演出ボタン17を操作することによって、遊技盤10に設けられた表示装置53(図2参照)における特図変動表示ゲームの演出内容を選択して、表示装置53におけ 50

る特図変動表示ゲームに、遊技者の操作を介入させた演出を行うことができる。

【0032】

なお、特図変動表示ゲームは、発射された遊技球が遊技盤10に備わる第1始動入賞口45(図2参照)又は普通変動入賞装置36(図2参照)の第2始動入賞口に入賞した場合に開始される。特図変動表示ゲームでは、表示装置53において複数の識別情報が変動表示する。そして、変動表示していた識別情報が停止し、停止した識別情報の結果態様が特定の結果態様である場合に、遊技機1の状態が遊技者に有利な状態(特典が付与される状態)である特別遊技状態に遷移する。

【0033】

上皿21の右上部には、遊技者が遊技球を借りる場合に操作する球貸ボタン26、及び、図示しないカードユニットからプリペイドカードを排出させるために操作される排出ボタン27が設けられている。これらのボタン26、27の間には、プリペイドカードの残高を表示する残高表示部28が設けられる。

【0034】

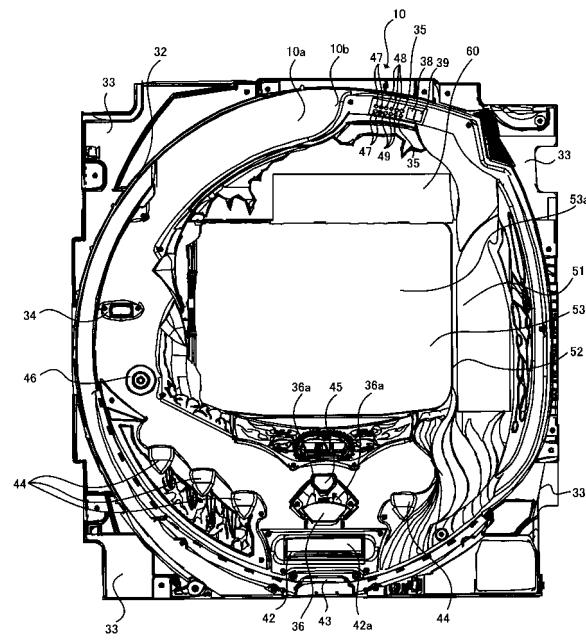

図2は、本発明の実施形態の遊技盤10の正面図である。

【0035】

図1に示す遊技機1は、内部の遊技領域10a内に遊技球を発射して(弾球して)遊技を行うもので、ガラス枠18のカバーガラスの奥側には、遊技領域10aを構成する遊技盤10が設置されている。

【0036】

遊技盤10は、各種部材の取付ベースとなる平板状の遊技盤本体10b(木製又は合成樹脂製)を備え、該遊技盤本体10bの前面にガイドレール32で囲まれた遊技領域10aを有している。また、遊技盤本体10bの前面であってガイドレール32の外側には、前面構成部材33、33、...が取り付けられている。そして、このガイドレール32で囲まれた遊技領域10a内に発射装置から遊技球(打球；遊技媒体)を発射して遊技を行うようになっている。

【0037】

遊技領域10aの略中央には、特図変動表示ゲームの表示領域となる窓部52を形成するセンタークース51が取り付けられている。このセンタークース51に形成された窓部52の後方には、複数の識別情報を変動表示する特図変動表示ゲームの演出を実行可能な演出表示装置としての表示装置53が配されるようになっている。この表示装置53は、例えば、液晶ディスプレイを備え、表示内容が変化可能な表示部53aがセンタークース51の窓部52を介して遊技盤10の前面側から視認可能となるように配されている。なお、表示装置53は、液晶ディスプレイを備えるものに限らず、E L、C R T等のディスプレイを備えるものであってもよい。

【0038】

センタークース51の窓部52の上端付近には、遊技状態に基づいて動作可能な可動役物60が取り付けられる。

【0039】

また、遊技盤10には、普図始動ゲート34と、普図変動表示ゲームの未処理回数を表示する普図記憶表示器47、普図変動表示ゲームを表示する普図表示器35が設けられている。また、遊技領域10a内には、第1の始動入賞領域をなす第1始動入賞口45と、第2の始動入賞領域をなす第2始動入賞口を有する普通変動入賞装置36と、が設けられている。そして、遊技球が第1始動入賞口45に入賞した場合は、補助遊技として第1特図変動表示ゲームが実行され、遊技球が普通変動入賞装置36に入賞した場合は、補助遊技として第2特図変動表示ゲームが実行されるようになっている。

【0040】

また、遊技盤10には、第1特図変動表示ゲームを表示する第1特図表示器38と、第2特図変動表示ゲームを表示する第2特図表示器39と、が設けられている。また、第1特図変動表示ゲームの未処理回数(第1特図始動記憶)を表示する第1特図記憶表示器4

10

20

30

40

50

8と、第2特図変動表示ゲームの未処理回数（第2特図始動記憶）を表示する第2特図記憶表示器49が設けられている。なお、普図記憶表示器47、普図表示器35、第1特図表示器38、第2特図表示器39、第1特図記憶表示器48、第2特図記憶表示器49は、遊技状態を表す遊技状態表示LED（図示略）と併せて、セグメントLEDとして一体に設けられている。

【0041】

さらに遊技領域10aには、上端側が手前側に倒れる方向に回動して開放可能になっているアタッカ形式の開閉扉42aを有し、第1特図変動表示ゲーム、第2特図変動表示ゲームの結果如何によって大入賞口を閉じた状態（遊技者にとって不利な状態）から開放状態（遊技者にとって有利な状態）に変換する特別変動入賞装置42、入賞口などに入賞しなかった遊技球を回収するアウト穴43が設けられている。この他、遊技領域10aには、一般入賞口44、44、…、打球方向変換部材としての風車46、多数の障害釘（図示略）などが配設されている。

10

【0042】

普図始動ゲート34内には、該普図始動ゲート34を通過した遊技球を検出するためのゲートSW34a（図3参照）が設けられている。そして、遊技領域10a内に打ち込まれた遊技球が普図始動ゲート34内を通過すると、普図変動表示ゲームが行われる。

【0043】

また、普図変動表示ゲームを開始できない状態中に、普図始動ゲート34を遊技球が通過すると、普図始動記憶数が上限数未満であるならば、普図始動記憶数が1加算されて、当該普図変動表示ゲームが当りとなるか否かを示す乱数が普図始動記憶として一つ記憶される。

20

【0044】

普図変動表示ゲームが開始できない状態とは、例えば、普図変動表示ゲームが既に行われ、その普図変動表示ゲームが終了していない状態や、普図変動表示ゲームが当って普通変動入賞装置36が開状態に変換されている状態のことをいう。

【0045】

なお、普図変動表示ゲームの始動記憶数は、LEDを備える普図記憶表示器47にて表示される。

【0046】

30

普図変動表示ゲームは、遊技盤10に設けられた普図表示器35で実行されるようになっている。なお、表示装置53の表示領域の一部で普図変動表示ゲームを表示するようにもよく、この場合は識別図柄として、例えば、数字、記号、キャラクタ図柄などを用い、この識別図柄を所定時間変動表示させた後、停止表示させることにより行うようとする。

【0047】

この普図変動表示ゲームの停止表示が特別の結果態様となれば、普図変動表示ゲームが当りとなって、普通変動入賞装置36の開閉部材36a、36aが所定時間（例えば、0.5秒間）開放される。これにより、普通変動入賞装置36に遊技球が入賞しやすくなり、第2特図変動表示ゲームの始動が容易となる。

40

【0048】

普通変動入賞装置36は左右一対の開閉部材36a、36aを具備し、第1始動入賞口45の下部に配設される。この開閉部材36a、36aは、常時は遊技球の直径程度の間隔をおいて閉じた状態（遊技者にとって不利な状態）を保持しているが、普図変動表示ゲームの結果が所定の停止表示態様となった場合（普図変動表示ゲームが当りとなった場合）には、駆動装置としてのソレノイド（普電SOL36b、図3参照）によって、逆「八」の字状に開いて普通変動入賞装置36に遊技球が流入し易い状態（遊技者にとって有利な状態）に変化させられるようになっている。

【0049】

また、本実施形態の遊技機1は、特図変動表示ゲームの結果態様に基づき、遊技状態と

50

して、表示装置 5 3 における特図変動表示ゲームの変動表示時間を短縮する時短動作状態（第2動作状態）を発生可能となっている。この時短動作状態（第2動作状態）は、普通変動入賞装置 3 6 の動作状態が、通常動作状態（第1動作状態）に比べて開放状態となりやすい状態である。

#### 【0050】

この時短動作状態においては、上述の普図変動表示ゲームの実行時間が、通常動作状態における長い実行時間よりも短くなるように制御され（例えば、10秒が1秒）、これにより、単位時間当たりの普通変動入賞装置 3 6 の開放回数が実質的に多くなるように制御される。また、時短動作状態においては、普図変動表示ゲームが当り結果となって普通変動入賞装置 3 6 が開放される場合に、開放時間が通常動作状態の短い開放時間より長くされるように制御される（例えば、0.3秒が1.8秒）。また、時短動作状態においては、普図変動表示ゲームの1回の当り結果に対して、普通変動入賞装置 3 6 が1回ではなく、複数回（例えば、2回）開放される。さらに、時短動作状態においては普図変動表示ゲームの当り結果となる確率が通常動作状態より高くなるように制御される。すなわち、通常動作状態よりも普通変動入賞装置 3 6 の開放回数が増加され、普通変動入賞装置 3 6 に遊技球が入賞しやすくなり、第2特図変動表示ゲームの始動が容易となる。

10

#### 【0051】

第1始動入賞口 4 5 の内部には第1始動口 SW 4 5 a（図3参照）が備えられ、この第1始動口 SW 4 5 a によって遊技球を検出することに基づき、補助遊技としての第1特図変動表示ゲームを開始する始動権利が発生するようになっている。また、普通変動入賞装置 3 6 の内部には第2始動口 SW 3 6 d（図3参照）が備えられ、この第2始動口 SW 3 6 d によって遊技球を検出することに基づき、補助遊技としての第2特図変動表示ゲームを開始する始動権利が発生するようになっている。

20

#### 【0052】

この第1特図変動表示ゲームを開始する始動権利は、所定の上限数（例えば4）の範囲内で第1始動記憶（特図1始動記憶）として記憶される。そして、この第1始動記憶数は、第1特図記憶表示器 4 8 に表示される。また、第2特図変動表示ゲームを開始する始動権利は、所定の上限数（例えば4）の範囲内で第2始動記憶（特図2始動記憶）として記憶される。そして、この第2始動記憶数は、第2特図記憶表示器 4 9 にて表示される。

30

#### 【0053】

そして、第1特図変動表示ゲームが開始可能な状態（第1始動記憶数及び第2始動記憶数が0の状態）で、第1始動入賞口 4 5 に遊技球が入賞すると、始動権利の発生に伴って抽出された乱数が第1始動記憶として記憶されて、第1始動記憶数が1加算されるとともに、直ちに第1始動記憶に基づいて、第1特図変動表示ゲームが開始され、この際に第1始動記憶数が1減算される。

#### 【0054】

また、第2特図変動表示ゲームは第1特図変動表示ゲームよりも優先して実行されるため、第1始動記憶数が0でなくとも、第2始動記憶数が0であれば、第2始動入賞口をなす普通変動入賞装置 3 6 に遊技球が入賞すると、始動権利の発生に伴って抽出された乱数が第2始動記憶として記憶されて、第2始動記憶数が1加算されるとともに、実行中の第1特図変動表示ゲームが終了後直ちに第2始動記憶に基づいて、第2特図変動表示ゲームが開始され、この際に第2始動記憶数が1減算される。

40

#### 【0055】

一方、第1特図変動表示ゲーム又は第2特図変動表示ゲームが直ちに開始できない状態、例えば、既に第1特図変動表示ゲーム又は第2特図変動表示ゲームが行われ、その特図変動表示ゲームが終了していない状態や、特別遊技状態となっている場合に、第1始動入賞口 4 5 に遊技球が入賞すると、第1始動記憶数が上限数未満（例えば、4個未満）ならば、第1始動記憶数が1加算されて、第1始動入賞口 4 5 に遊技球が入賞したタイミングで抽出された乱数が第1始動記憶として一つ記憶される。

#### 【0056】

50

同様に、この場合に第2始動入賞口をなす普通変動入賞装置36に遊技球が入賞すると、第2始動記憶数が上限数未満（例えば、4個未満）ならば、第2始動記憶数が1加算されて、第2始動入賞口に遊技球が入賞したタイミングで抽出された乱数が第2始動記憶として一つ記憶される。

【0057】

そして、第1特図変動表示ゲーム又は第2特図変動表示ゲームが開始可能な状態となると、第1始動記憶又は第2始動記憶に基づき第1特図変動表示ゲーム又は第2特図変動表示ゲームが開始される。このとき、第1特図変動表示ゲームと第2特図変動表示ゲームは同時に実行されることはなく、第2特図変動表示ゲームが第1特図変動表示ゲームよりも優先して実行されるようになっている。

10

【0058】

すなわち、第1始動記憶と第2始動記憶がある場合には、第2特図変動表示ゲームが実行される。

【0059】

補助遊技としての第1特図変動表示ゲーム、第2特図変動表示ゲームは、遊技盤10に設けられた第1特図表示器38、第2特図表示器39で実行されるようになっており、複数の識別情報を変動表示したのち、所定の結果態様を停止表示することで行われる。また、表示装置53にて各特図変動表示ゲームに対応して複数種類の識別情報（例えば、数字、記号、キャラクタ図柄など）を変動表示させる特図変動表示ゲームが実行される。そして、この特図変動表示ゲームの結果として、第1特図表示器38又は第2特図表示器39の表示態様が特別結果態様となった場合には、大当たりとなつて特別遊技状態（いわゆる、大当たり状態）となる。また、これに対応して表示装置53の表示態様も特別結果態様（例えば、「7, 7, 7」等のゾロ目数字の何れか）となる。なお、遊技機に第1特図表示器38、第2特図表示器39を備えずに、表示装置53のみで特図変動表示ゲームを実行するようにしてもよい。

20

【0060】

また、本実施形態の遊技機1は、特図変動表示ゲームの結果態様に基づき、遊技状態として確変状態（第2確率状態）を発生可能となっている。この確変状態（第2確率状態）は、特図変動表示ゲームでの当り結果となる確率が、通常確率状態（第1確率状態）に比べて高い状態である。なお、第1特図変動表示ゲームと第2特図変動表示ゲームのどちらの特図変動表示ゲームの結果態様に基づき確変状態となつても、第1特図変動表示ゲーム及び第2特図変動表示ゲームの両方が確変状態となる。また、確変状態と上述した時短動作状態はそれぞれ独立して発生可能であり、両方を同時に発生することも可能であるし、一方のみを発生させることも可能である。

30

【0061】

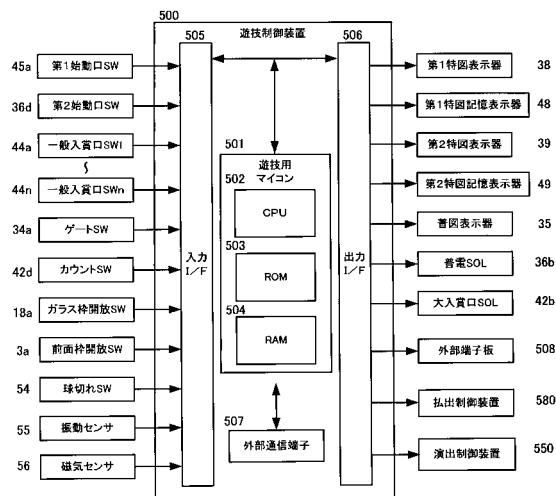

図3は、本発明の実施形態の遊技機1の構成を示すブロック図である。

【0062】

遊技機1は、遊技を統括的に制御する遊技制御装置500、各種演出を行うために表示装置53及びスピーカ30等を制御する演出制御装置550、遊技球を払い出すために図示しない払出モータを制御する払出制御装置580を備える。

40

【0063】

まず、遊技制御装置500について説明する。図4では、演出制御装置550について説明する。

【0064】

遊技制御装置500は、遊技用マイコン501、入力I/F（Interface）505、出力I/F（Interface）506、及び外部通信端子507を備える。

【0065】

遊技用マイコン501は、CPU502、ROM（Read Only Memory）503及びRAM（Random Access Memory）504を備える。

【0066】

50

C P U 5 0 2 は、遊技を統括的に制御する主制御装置であって、遊技制御を司る。R O M 5 0 3 は、遊技制御のための不变の情報（プログラム、データ等）を記憶している。R A M 5 0 4 は、遊技制御時にワークエリアとして利用される。

【0067】

外部通信端子 5 0 7 は、遊技制御装置 5 0 0 の設定情報等を検査する検査装置等の外部機器に遊技制御装置 5 0 0 を接続する。

【0068】

C P U 5 0 2 は、入力 I / F 5 0 5 を介して各種入力装置（第 1 始動口 S W 4 5 a、第 2 始動口 S W 3 6 d、一般入賞口 S W 4 4 a、ゲート S W 3 4 a、カウント S W 4 2 d、ガラス枠開放 S W 1 8 a、前面枠開放 S W 3 a、球切れ S W 5 4、振動センサ 5 5、及び磁気センサ 5 6）からの検出信号を受けて、大当たり抽選等、種々の処理を行う。

10

【0069】

第 1 始動口 S W 4 5 a は、第 1 始動入賞口 4 5 に遊技球が入賞したことを検出するスイッチである。第 2 始動口 S W 3 6 d は、普通変動入賞装置 3 6 の第 2 始動入賞口に遊技球が入賞したことを検出するスイッチである。

【0070】

一般入賞口 S W a 4 4 a ~ 4 4 n は、一般入賞口 4 4 に遊技球が入賞したことを検出するスイッチである。ゲート S W 3 4 a は、普図始動ゲート 3 4 を遊技球が通過したことを検出するスイッチである。

20

【0071】

カウント S W 4 2 d は、特別変動入賞装置 4 2 の大入賞口に遊技球が入賞したことを検出するスイッチである。

【0072】

ガラス枠開放 S W 1 8 a は、ガラス枠 1 8 が開放されたことを検出するスイッチである。前面枠開放 S W 3 a は、前面枠 3 が開放されたことを検出するスイッチである。

【0073】

球切れ S W 5 4 は、遊技機 1 の内部に貯留され、払い出しに用いられる遊技球の数が所定数以下になったことを検出するスイッチである。

【0074】

振動センサ 5 5 は、遊技機 1 に与えられた振動を検出するセンサであり、遊技機 1 に振動を与えて、不当に遊技球を獲得する不正を検出する。磁気センサ 5 6 は、第 1 始動入賞口 4 5、普通変動入賞装置 3 6 の第 2 始動入賞口、一般入賞口 4 4、特別変動入賞装置 4 2 の大入賞口、及び普図始動ゲート 3 4 付近に設けられ、磁力を検出するセンサである。磁気センサ 9 3 は、各入賞口付近に磁石を近づけて、遊技領域 1 0 a に発射された遊技球を各入賞口に導く不正を検出する。

30

【0075】

また、C P U 5 0 2 は、出力 I / F 5 0 6 を介して、第 1 特図表示器 3 8、第 1 特図記憶表示器 4 8、第 2 特図表示器 3 9、第 2 特図記憶表示器 4 9、普図表示器 3 5、普電 S O L 3 6 b、大入賞口 S O L 4 2 b、払出制御装置 5 8 0、及び演出制御装置 5 5 0 に指令信号を送信して、遊技を統括的に制御する。

40

【0076】

第 1 特図表示器 3 8 には、第 1 始動入賞口 4 5 に遊技球が入賞した場合に補助遊技として実行される第 1 特図変動表示ゲームが表示される。第 1 特図記憶表示器 4 8 には、所定の上限数の範囲内で記憶される第 1 特図変動表示ゲームを開始する始動権利である第 1 始動記憶数が表示される。

【0077】

第 2 特図表示器 3 9 には、普通変動入賞装置 3 6 の大入賞口に遊技球が入賞した場合に補助遊技として実行される第 2 特図変動表示ゲームが表示される。第 2 特図記憶表示器 4 9 には、所定の上限数の範囲内で記憶される第 2 特図変動表示ゲームを開始する始動権利である第 2 始動記憶数が表示される。

50

## 【0078】

普図表示器35には、遊技球が普図始動ゲート34を通過した場合に行われる普図変動表示ゲームが表示される。

## 【0079】

普電SOL36bは、普図表示器35で実行される普図変動表示ゲームの停止表示が特別の結果態様となった場合に、開閉部材36a、36aを開放し、普通変動入賞装置36の第2始動入賞口を遊技球が入賞しやすい状態にする。

## 【0080】

大入賞口SOL42bは、第1特図変動表示ゲーム又は第2特図変動表示ゲームの結果が特別の結果態様となり、特別遊技状態となった場合に、特別変動入賞装置42の開閉扉42aを開放して、大入賞口を遊技球が入賞しやすい状態に変換する。

10

## 【0081】

また、遊技制御装置500は、遊技機データを、外部情報端子508を介して、図示しない情報収集端末装置を介して、図示しない遊技場管理装置に出力する。遊技場管理装置は、遊技場に設置された遊技機1の遊技データを収集管理する計算機である。

## 【0082】

また、払出制御装置580は、遊技球が一般入賞口44又は大入賞口に入賞した場合に、入賞した入賞口に対応する数の遊技球の払い出し、又は球貸ボタン26が操作された場合に、所定数の遊技球の払い出しを行う払出指令を遊技制御装置500から受信した場合に、受信した払出指令に基づいて、図示しない払出モータを制御する。なお、払出指令には、払い出す遊技球の数が含まれる。

20

## 【0083】

遊技制御装置500は、変動開始コマンド、客待ちデモコマンド、ファンファーレコマンド、確率情報コマンド、及びエラー指定コマンド等を、遊技の状況を示す遊技データとして、出力I/F506を介して、演出制御装置550へ送信する。

## 【0084】

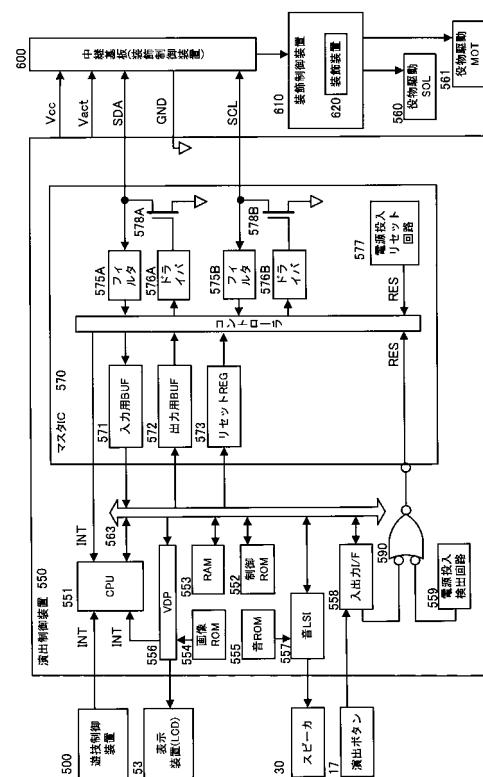

図4は、本発明の実施形態の演出制御装置550の構成を示すブロック図である。

## 【0085】

演出制御装置550は、遊技制御装置500から入力される遊技データに基づいて、演出内容を決定して、表示装置53、及びスピーカ30を制御するとともに、装飾制御装置610を介して装飾装置620、役物駆動SOL560(ソレノイド)、及び役物駆動MOT(モータ)561を制御する。詳細は後述するが、これら装飾装置620、役物駆動SOL560、及び役物駆動MOT561(総称して演出装置という)によって、遊技の演出が行われる。また、演出制御装置550は、演出ボタン17から当該演出ボタン17が操作されたことを示す信号が入力される。

30

## 【0086】

演出制御装置550は、CPU551、制御ROM552、RAM553、画像ROM554、音ROM555、VDP556、音LSI557、入出力I/F558、電源投入検出回路559、マスタIC570、及び加算器590を備える。

40

## 【0087】

CPU551は、遊技制御装置500に接続され、遊技制御装置500から指令信号が割込信号(INT)として入力され、入力された指令信号に基づいて、各種演出を制御する主制御装置である。また、CPU551には、マスタIC570の後述するコントローラ574から割込信号が入力されるとともに、VDP556から割込信号が入力される。

## 【0088】

なお、CPU551に割込信号が入力されると、CPU551は、現在実行中の処理を中断して、入力された割込信号に対応する処理を実行する。

## 【0089】

制御ROM552には、演出制御のための不变の情報(プログラム、データ等)が格納されている。RAM553は、演出制御時にワークエリアとして利用される。

50

## 【0090】

画像ROM554には、表示装置53に表示される画像データが格納され、画像ROM554はVDP556に接続されている。音ROM555には、スピーカ30から出力される音データが格納され、音ROM555は音LSI557に接続されている。

## 【0091】

VDP556は、表示装置53への画像出力を制御するプロセッサである。音LSI557は、スピーカ30からの音声出力を制御する回路である。

## 【0092】

なお、VDP556は、表示装置53に表示される画像を更新する周期（1/60秒周期）と同期する同期信号を発生させる同期信号発生手段を備える。同期信号発生手段は、同期信号を発生させるごとに、発生させた同期信号をCPU551に割込信号として入力する。

10

## 【0093】

入出力I/F558は、演出ボタン17に接続されるインターフェースである。

## 【0094】

なお、演出ボタン17は、上皿21の上縁部に設けられ、表示装置53で実行される第1特図変動表示ゲーム又は第2特図変動表示ゲームにおける演出で、遊技者によって操作される。

## 【0095】

CPU551、VDP556、RAM553、制御ROM552、音LSI557、及び入出力I/F558はバス563を介してそれぞれ接続されている。

20

## 【0096】

電源投入検出回路559は、演出制御装置550に電源が投入された場合に、マスタIC570の図示しないレジスタをデフォルト状態（すべて0）に初期化するリセット信号を加算器590を介して出力する。

## 【0097】

また、CPU551は、所定の条件が成立した場合に、リセット信号をバス563を介して入出力I/F558に出力し、入出力I/F558は入力されたリセット信号を加算器590へ出力する。

## 【0098】

30

いずれの場合にもリセット信号は加算器590を介してマスタIC570に入力されるので、電源投入検出回路559及びCPU551の少なくとも一方からリセット信号が出力されていれば、リセット信号がマスタIC570に入力される。

## 【0099】

次に、マスタIC570について説明する。

## 【0100】

マスタIC570は、制御対象となる演出装置の装飾制御装置610のアドレスを指定して、指定したアドレスの装飾制御装置610に演出装置の制御内容を出力する。

## 【0101】

マスタIC570は、接続線Vcc、接続線Vact、接続線SDA、接続線SCL、及び接続線GND（図5参照）の5本の接続線を介して、中継基板（装飾制御装置）600に接続される。

40

## 【0102】

接続線Vccは、中継基板600及び装飾制御装置610に電源を供給するための接続線である。接続線Vactは、演出装置に電源を供給するための接続線である。接続線SDAは、演出制御装置550と装飾制御装置610との間でデータを通信するための接続線であり、本実施形態におけるデータ線として機能する。接続線SCLは、接続線SDAでのデータ通信に用いられるクロック信号を入出力するための接続線であり、本実施形態におけるタイミング信号線として機能する。図5に示す接続線GNDは、接続線Vcc及び接続線Vactで供給される電源のグランドである。

50

## 【0103】

中継基板600と装飾制御装置610との間は、マスタIC570と中継基板600との間と同じく、接続線Vcc、接続線Vact、接続線SDA、接続線SCL、及び接続線GNDを介して接続される。

## 【0104】

マスタIC570と装飾制御装置610とは、接続線SDA及び接続SCLによって2ライン双方向通信を行う。

## 【0105】

マスタIC570は、中継基板600及び装飾制御装置610にデータを送信する場合には、まず、接続線SCLの信号レベルをHIGHに維持したまま、接続線SDAの信号レベルをHIGHからLOWに変化させることにより、装飾制御装置610へのデータ出力を開始するためのスタート条件を成立させる（装飾制御装置610に対してスタートコンディションを発行する）。

10

## 【0106】

この後、マスタIC570は、接続線SCLの信号レベルをLOWに変更し、接続線SCLの信号レベルがLOWである間に接続線SDAの信号レベルを送信データの最初のビットのレベルに設定し、所定時間後に接続線SCLの信号レベルをLOWからHIGHに変化させる。接続線SCLの信号レベルがHIGHに変化すると、装飾制御装置610は接続線SDAの信号レベルを取り込んで、送信データの最初のビットとして認識する。次いで、マスタIC570は、接続線SCLの信号レベルをHIGHからLOWに戻す。

20

## 【0107】

この手順を1回実行すると、マスタIC570から装飾制御装置610へ1ビットのデータが送信され、最終的にはこの手順が8回繰り返されることで、送信データの8ビット全てがマスタIC570から装飾制御装置610へ送信される（1バイト分のデータが送信される）。

## 【0108】

そして、マスタIC570は、最後の8ビット目のデータを送信し終えて、接続線SCLの信号レベルをHIGHからLOWに戻した際に、接続線SDAを解放して装飾制御装置610からの返答信号を受信することを待機する受信待機状態にする。

30

## 【0109】

受信待機状態になると、装飾制御装置610は、接続線SDAを介して1ビットの返答信号（後述するACK又はNACK）をマスタIC570に返す。次いで、マスタIC570は、接続線SCLの信号レベルをLOWからHIGHに変化させて返答信号のレベルを取り込み、所定時間後に接続線SCLの信号レベルをHIGHからLOWに変化させると、装飾制御装置610は接続線SDAを解放する。

## 【0110】

マスタIC570は、このような1バイト分のデータ送信と1ビット分の返答信号の受信とを交互に繰り返し、装飾制御装置610へ出力すべきデータがすべて出力されるまで継続する。マスタIC570は、出力すべきデータの出力が終了した場合には、接続線SCLの信号レベルをHIGHに維持したまま、接続線SDAの信号レベルをLOWからHIGHに変更されることにより、装飾制御装置610へのデータ出力を終了するためのストップ条件を成立させる（装飾制御装置610に対してストップコンディションを発行する）。

40

## 【0111】

入力用BUF571は、装飾制御装置610から接続線SDAを介して入力されたデータが一時的に記憶される記憶装置である。

## 【0112】

具体的には、マスタIC570が入力モードに設定された場合において、装飾制御装置610からマスタIC570に送信されたデータが、フィルタ575Aによりノイズが除去されて入力用BUF571に一時的に記憶される。

50

## 【0113】

出力用 B U F 5 7 2 は、装飾制御装置 6 1 0 に接続線 S D A を介して出力するデータが一時的に記憶される。

## 【0114】

リセット R E G 5 7 3 は、バス 5 6 3 に接続され、C P U 5 5 1 からの指令を受けてリセット信号をコントローラ 5 7 4 に出力する。コントローラ 5 7 4 は、マスター I C 5 7 0 を統括的に制御し、各種処理を実行する。

## 【0115】

フィルタ 5 7 5 A は、接続線 S D A から入力されたデータのノイズを除去する。ドライバ 5 7 6 A は、接続線 S D A からデータを出力する場合に、トランジスタ 5 7 8 A が動作可能な電圧をトランジスタ 5 7 8 A に印加する。

10

## 【0116】

図 9 に示すように接続線 S D A には、プルアップ抵抗 R によって所定の電圧が印加されて、接続線 S D A はフィルタ 5 7 5 A 及びトランジスタ 5 7 8 A に接続されている。

## 【0117】

トランジスタ 5 7 8 A は、電力消費を抑えるために電界効果トランジスタ (F E T) が用いられており、トランジスタ 5 7 8 A のゲートはドライバ 5 7 6 A に接続され、ドレインはプルアップ抵抗 R により所定の電圧が印加された接続線 S D A に接続され、ソースは接地されている。

20

## 【0118】

トランジスタ 5 7 8 A のゲートに印加される電圧がトランジスタ 5 7 8 A を動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れないので、接続線 S D A に印加された電圧は降下せず、その結果、接続線 S D A は H I G H レベルとなる。一方、トランジスタ 5 7 8 A のゲートに印加される電圧がトランジスタ 5 7 8 A を動作させる所定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流が流れることによって、接続線 S D A の電圧が低下し、その結果、接続線 S D A は L O W レベルとなる。

## 【0119】

なお、トランジスタ 5 7 8 A は、10 ミリアンペア程度の電流をドレインからソースへ流しても破損しない仕様のものを用いている。このため、接続線 S D A には、通常の  $I^2$  C バス使用で用いられる電流値よりもはるかに大きい 10 ミリアンペア程度の電流を流すことが可能であり、演出制御装置 5 5 0 と装飾制御装置 6 1 0 との間のデータ送信が、ノイズによる障害に耐えうる構成となっている。

30

## 【0120】

ドライバ 5 7 6 A は、データを接続線 S D A から出力する場合に、トランジスタ 5 7 8 A にドレインとソースとの間に電流を流すためにトランジスタ 5 7 8 A のゲートにトランジスタ 5 7 8 A が動作可能な値の電圧を印加する。そして、ドライバ 5 7 6 A は、接続線 S D A の電圧を、H I G H レベル又は L O W レベルに設定することによって、データを接続線 S D A から出力する。

## 【0121】

40

また、フィルタ 5 7 5 B は、接続線 S C L から入力されたデータのノイズを除去する。ドライバ 5 7 6 B は、接続線 S C L からデータを出力する場合に、トランジスタ 5 7 8 B が動作可能な電圧をトランジスタ 5 7 8 B に印加する。

## 【0122】

図 9 に示すように接続線 S C L は、プルアップ抵抗 R によって所定の電圧が印加されて、接続線 S D A はフィルタ 5 7 5 B 及びトランジスタ 5 7 8 B に接続されている。

## 【0123】

トランジスタ 5 7 8 B は、電力消費を抑えるために電界効果トランジスタ (F E T) が用いられており、トランジスタ 5 7 8 B のゲートはドライバ 5 7 6 B に接続され、ドレインはプルアップ抵抗 R により所定の電圧が印加された接続線 S C L に接続され、ソースは

50

接地されている。

【0124】

トランジスタ578Bのゲートに印加される電圧がトランジスタ578Bを動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れないので、接続線SCLに印加された電圧は降下せず、その結果、接続線SCLはHIGHレベルとなる。一方、トランジスタ578Bのゲートに印加される電圧がトランジスタ578Bを動作させる所定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流が流れることによって、接続線SCLの電圧が低下し、その結果、接続線SCLはLOWレベルとなる。

【0125】

なお、トランジスタ578Bは、10ミリアンペア程度の電流をドレインからソースへ流しても破損しない仕様のものを用いている。そのため、接続線SCLには、通常のI<sup>2</sup>Cバス使用で用いられる電流値よりもはるかに大きい10ミリアンペア程度の電流を流すことが可能であり、演出制御装置550と装飾制御装置610との間のデータ送信が、ノイズによる障害に耐えうる構成となっている。

【0126】

ドライバ576Bは、クロック信号を接続線SCLから出力する場合に、トランジスタ578Bにドレインとソースとの間に電流を流すためにトランジスタ578Bのゲートにトランジスタ578Bが動作可能な値の電圧を印加する。そして、ドライバ578Bは、接続線SCLの電圧を、HIGHレベルとLOWレベルとに繰り返し変化させることによって、クロック信号を接続線SCLから出力する。

【0127】

電源投入リセット回路577は、マスタIIC570に電源が投入されて、電源投入リセット回路577内の電圧が所定値に達した場合に、入力用BUF571及び出力用BUF572などの記憶領域をデフォルト状態にするためのリセット信号をコントローラ574に出力する。

【0128】

次に、中継基板600及び装飾制御装置610について説明する。

【0129】

なお、中継基板600は、装飾制御装置610のうちマスタIIC570に直接接続される、つまり最も上流側に位置するものである。

【0130】

装飾装置620は、装飾制御装置610に設けたI<sup>2</sup>C/I/Oエクスパンダ615（図6で後述）によって制御され、電流を流すことによって光が点滅して演出を行う発光装置であり、例えばLEDなどで構成される。役物駆動ソレノイド（SOL）560は、電流が流れると往復動作する装置であり、遊技盤10に配置される図示しない装飾のための役物を可動させて演出を行う。役物駆動モータ（MOT）561は、電流が流れると回転動作する装置であり、可動役物60を可動させて演出を行う。役物駆動ソレノイド（SOL）560及び役物駆動モータ（MOT）561も、装飾制御装置610に設けたI<sup>2</sup>C/I/Oエクスパンダ615によって制御される。

【0131】

なお、役物駆動SOL560が可動役物60を可動させててもよいし、役物駆動MOT561が図示しない役物を可動させててもよい。

【0132】

演出制御装置550と中継基板600との接続方法、及び中継基板600と中継基板600以外の装飾制御装置610との接続方法は、図5で詳細を説明する。装飾制御装置610は、図6～図10で詳細を説明する。

【0133】

図5は、本発明の実施形態の装飾制御装置610A～610Fの接続の説明図である。なお、説明の都合上、装飾制御装置610として、1個の中継基板600と、6個の装飾

10

20

30

40

50

制御装置 610A～610F を図示しているが、実際には、遊技機の仕様に対応して必要な数の装飾制御装置 610 が接続されている。

【0134】

演出制御装置 550 は、接続線 Vcc、接続線 Vact、接続線 SDA、接続線 SCL、及び接続線 GND（以下、この 5 本の接続線を一つのハーネスという）を介して演出制御装置 550 と接続される。

【0135】

中継基板 600 には、二つの装飾制御装置 610A 及び 610D がそれぞれハーネスによって並列に接続される。

【0136】

装飾制御装置 610A にはハーネスを介して装飾制御装置 610B が接続され、装飾制御装置 610B にはハーネスを介して装飾制御装置 610C が接続される。

【0137】

一方、装飾制御装置 610D にはハーネスを介して装飾制御装置 610E が接続され、装飾制御装置 610E にはハーネスを介して装飾制御装置 610F が接続される。

【0138】

各装飾制御装置 610 は、ハーネスを自身に接続するための取付口となるコネクタを備える。このコネクタは各装飾制御装置 610 で共通であるので、接続線を接続順の誤配線を防止できる。

【0139】

ここで、装飾制御装置 610 に設けた I<sup>2</sup>C I/O エクスパンダ 615（図 6 で後述）が装飾装置 620 を制御する方法について説明する。

【0140】

演出制御装置 550 は、遊技制御装置 500 から入力された遊技データに基づいて、演出内容を決定する。そして、演出制御装置 550 は、決定された演出内容で装飾制御装置 610 を制御するために、制御対象となる装飾制御装置 610 のアドレス（I<sup>2</sup>C I/O エクスパンダ 615 のアドレス）と演出内容を示す演出データとを含む演出制御データを中継基板 600 に出力する。このとき、演出制御データは、中継基板 600 を介して演出制御装置 550 に接続されるすべての装飾制御装置 610 に対して接続線 SDA から出力される。このため、マスタ I<sup>2</sup>C 570 は、マスタ I<sup>2</sup>C 570 に接続されるすべての装飾制御装置 610 を制御可能である。

【0141】

各装飾制御装置 610 には、一意なアドレスが予め設定されているので、演出制御データが入力されると、入力された演出制御データに含まれるアドレスと設定されているアドレスとが一致するか否かを判定する。そして、入力された演出制御データに含まれるアドレスと設定されているアドレスとが一致すると判定された場合には、装飾制御装置 610 の I<sup>2</sup>C I/O エクスパンダ 615 は、演出制御データに含まれる演出データに基づいて、装飾装置 620 を制御するとともに、8 ビット目のデータが入力された直後に返答信号をマスタ I<sup>2</sup>C 570 に出力する。

【0142】

このように、装飾制御装置 610 は、演出制御装置 550 からの指令に基づく制御を行うので、演出制御装置 550 と装飾制御装置 610 との関係は、演出制御装置 550 のマスタ I<sup>2</sup>C 570 がマスタであり、装飾制御装置 610 の I<sup>2</sup>C I/O エクスパンダ 615 がスレーブである。

【0143】

図 5 では、装飾制御装置 610 の制御対象が装飾装置 620 である場合について説明したが、装飾制御装置 610 の制御対象が役物駆動 SOL560 や役物駆動 MOT561 であってもよい。

【0144】

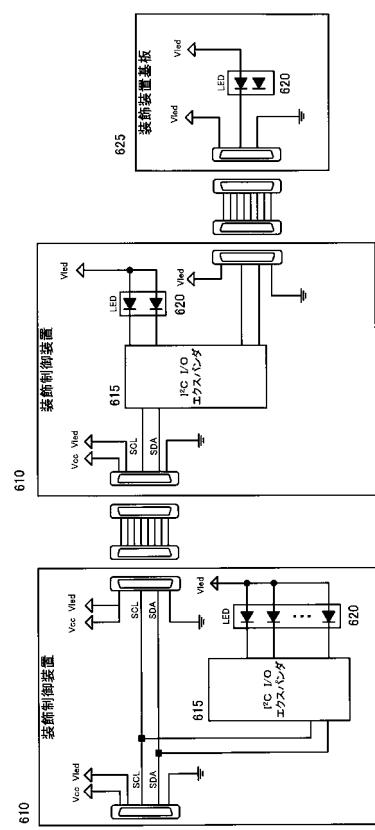

図 6 は、本発明の実施形態の装飾制御装置 610 のブロック図である。

10

20

30

40

50

## 【0145】

図6では、装飾制御装置610の内部に装飾装置620であるLEDを備える装飾制御装置610(図6の下側の装飾制御装置610)と、外部の装飾装置620に接続される装飾制御装置610(図6の中央の装飾制御装置610)と、について説明する。

## 【0146】

まず、装飾制御装置610の内部にLEDを備える装飾制御装置610について説明する。

## 【0147】

図6の下側の装飾制御装置610は、I<sup>2</sup>C I/Oエクスパンダ615及びLED(装飾装置20)を備える。接続線SDA及び接続線SCLは、装飾制御装置610内で二つに分岐し、一方は、そのまま次の装飾制御装置610に出力される。他方は、I<sup>2</sup>C I/Oエクスパンダ615に接続される。10

## 【0148】

また、I<sup>2</sup>C I/Oエクスパンダ615の出力側には、制御対象となる装飾装置620が接続される。I<sup>2</sup>C I/Oエクスパンダ615の出力側は、図7で説明するポート0～15によって構成される。さらに、装飾制御装置610のすべてのポートが、図8Aで後述する電流制限抵抗R0～R15を介して、内部のLEDに接続されている。なお、この電流制限抵抗R0～R15も、装飾制御装置610に備えられている。

## 【0149】

前述したように、I<sup>2</sup>C I/Oエクスパンダ615は、演出制御装置550から入力された演出制御データに含まれるアドレスと、当該I<sup>2</sup>C I/Oエクスパンダ615に設定されているアドレスとが一致する場合にのみ、演出制御データに含まれる装飾データに基づいて、I<sup>2</sup>C I/Oエクスパンダ615に接続されている装飾装置620を制御する。20

## 【0150】

次に、外部の装飾装置620に接続される装飾制御装置610について説明する。

## 【0151】

図6の中央の装飾制御装置610は、I<sup>2</sup>C I/Oエクスパンダ615及びLED(装飾装置20)を備え、装飾制御装置610の外部に接続される装飾装置基板625に備わるLEDに電流を流すための接続線、装飾装置基板625のLEDに電源電圧を供給する接続線、及び、グランドに接地する接続線を介して、装飾制御装置610と装飾装置基板625とが接続される。30

## 【0152】

装飾装置基板625は、I<sup>2</sup>C I/Oエクスパンダ615を備えておらず、LEDのみを備えた基板である。この場合、装飾装置基板625に備えたLEDに接続される電流制限抵抗(図8A)を、装飾装置基板625に設けることになるが、I<sup>2</sup>C I/Oエクスパンダ615が備えられた装飾制御装置610に設けてもよい。

## 【0153】

なお、装飾装置基板625に設けたLEDの数に対応して、装飾制御装置610から装飾装置基板625へ渡されることになる、これらのLEDに電流を流すための接続線の数が決定される。例えば、装飾装置基板625に二つのLEDを備えた場合には、I<sup>2</sup>C I/Oエクスパンダ615のポートとLEDVを接続する2本の制御線と、VLEDを供給する電源線が1本とが、少なくとも必要となる。40

## 【0154】

そして、中央の装飾制御装置610に設けられたI<sup>2</sup>C I/Oエクスパンダ615も、演出制御装置550から入力された演出制御データに含まれるアドレスと、当該I<sup>2</sup>C I/Oエクスパンダ615に設定されているアドレスとが一致する場合にのみ、演出制御データに含まれる装飾データに基づいて、I<sup>2</sup>C I/Oエクスパンダ615に接続されている装飾装置620を制御する。この場合、中央の装飾制御装置610に設けられた装飾装置620と、装飾装置基板625に設けられた装飾装置620の両方が、I<sup>2</sup>C I/Oエクスパンダ615によって制御される。50

## 【0155】

このように、装飾装置基板625を設けて、装飾制御装置610から一部の装飾装置(LED)を分離させることで、離れた箇所に配置されたLEDであっても、共通のI<sup>2</sup>C I/Oエクスパンダ615により制御することができる。

## 【0156】

なお、装飾制御装置610は、装飾装置620の代わりに、役物駆動SOL560や役物駆動MOT561を接続し、これらを制御してもよいが、詳細は、図8Bで後述する。

## 【0157】

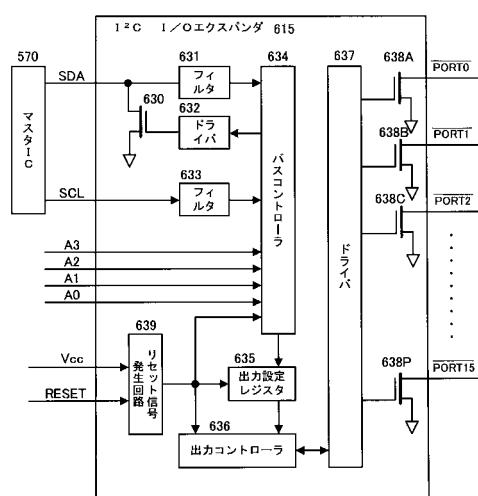

図7は、本発明の実施形態のI<sup>2</sup>C I/Oエクスパンダ615のブロック図である。

## 【0158】

I<sup>2</sup>C I/Oエクスパンダ615は、接続線SDAに接続されるトランジスタ630、接続線SDAに接続されるフィルタ631、接続線SDAに接続されるドライバ632、接続線SCLに接続されるフィルタ633、バスコントローラ634、出力設定レジスタ635、出力コントローラ636、I<sup>2</sup>C I/Oエクスパンダ615の出力側の各ポート0～15に接続されるドライバ637、各ポート0～15に接続されるトランジスタ638A～638P、及びリセット信号発生回路639を備える。

## 【0159】

フィルタ631は、接続線SDAに接続され、接続線SDAから入力されたデータのノイズを除去し、ノイズが除去されたデータをバスコントローラ634に出力する。ドライバ632は、返答信号を接続線SDAから出力する場合に、トランジスタ630が動作可能な電圧をトランジスタ630に印加する。

## 【0160】

ドライバ632は、接続線SDAからデータ(返答信号)を出力する場合に、トランジスタ630が動作可能な電圧をトランジスタ630に印加する。

## 【0161】

トランジスタ630は、電力消費を抑えるために電界効果トランジスタ(FET)が用いられており、トランジスタ630のゲートはドライバ631に接続され、ドレインはブルアップ抵抗R(図4参照)により所定の電圧が印加された接続線SDAに接続され、ソースは接地されている。

## 【0162】

トランジスタ630のゲートに印加される電圧がトランジスタ630を動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れない。一方、トランジスタ630のゲートに印加される電圧がトランジスタ630を動作させる所定値以上であれば、所定値の電圧が印加されたドレインから接地されているソースへ電流が流れることによって、接続線SDAの電圧が低下する。なお、トランジスタ630は、10ミリアンペア程度の電流をドレインからソースへ流しても破損しない仕様のものを用いている。

## 【0163】

ドライバ632は、データ(返答信号)を接続線SDAから出力する場合に、トランジスタ630にドレインとソースとの間に電流を流すためにトランジスタ630のゲートにトランジスタ630が動作可能な値の電圧を印加する。そして、ドライバ632は、接続線SDAの電圧をHIGHからLOWへ繰り返し変化させることによって、データを接続線SDAから出力する。

## 【0164】

フィルタ633は、接続線SCLに接続され、接続線SCLから入力されたデータのノイズを除去し、ノイズが除去されたデータをバスコントローラ634に出力する。

## 【0165】

また、I<sup>2</sup>C I/Oエクスパンダ615には、当該I<sup>2</sup>C I/Oエクスパンダ615に備わるアドレス設定用端子A0～A3によって固有のアドレスが設定されており、バスコントローラ634に入力されている。

## 【0166】

10

20

30

40

50

バスコントローラ 634 は、接続線 SDA から入力されたデータのアドレスが I<sup>2</sup>C I / O エクスパンダ 615 に設定されたアドレスと一致するか否かを判定し、一致している場合に当該データを取り込み、取り込んだデータにより出力設定レジスタ 635 を更新する。

【0167】

また、バスコントローラ 634 は、SCL 接続線の信号レベルの LOW から HIGH への変化回数が 8 回に達し 8 ビット目のデータを取り込んだ後、SCL 接続線の信号レベルが HIGH から LOW へ変化すると、返答信号を接続線 SDA からマスター IC570 に出力する。さらに、SCL 接続線の信号レベルが LOW から HIGH へ変化することが確認され、再度 SCL 接続線の信号レベルが HIGH から LOW へ変化すると、接続線 SDA を開放する。つまり、SCL 接続線の信号レベルの LOW から HIGH への変化回数が 9 回になるタイミングで返答信号を出力する。

10

【0168】

出力設定レジスタ 635 には、当該 I<sup>2</sup>C I / O エクスパンダ 615 の動作モードやポート 0 ~ 15 の出力状態が設定される。また、リセット信号が出力設定レジスタ 635 に入力されることによって、出力設定レジスタ 635 は、すべてのポート 0 ~ 15 に電流が流れないように初期状態に設定される。

【0169】

出力コントローラ 636 は、出力設定レジスタ 635 に設定されたデータに基づいて、ポートドライバ 637 を介して、各ポート 0 ~ 15 に接続された演出装置に電流を流すことによって、演出装置の出力状態を実際に制御する。

20

【0170】

ドライバ 637 は、ポートに電流を流す場合に、電流を流すポートに接続されるトランジスタ 638A ~ 638P が動作可能な電圧を当該トランジスタに印加する。

【0171】

トランジスタ 638A ~ 638P のゲートはドライバ 637 に接続され、ドレインは図 8A 及び図 8B に示すように演出装置を動作させるための電圧が印加された接続線に接続するポート端子に接続され、ソースは接地されている。

【0172】

トランジスタ 638A ~ 638P のゲートに印加される電圧がトランジスタ 638A ~ 638P を動作させる所定値よりも小さければ、ドレインとソースとの間に電流が流れない。一方、638A ~ 638P のゲートに印加される電圧がトランジスタ 638 を動作させる所定値以上であれば、図 8A に示す電源 V<sub>led</sub>、又は図 8B に示す電源 V<sub>mot</sub> や電源 V<sub>s01</sub> からゲートに印加されている所定の電圧が、トランジスタ 638 のドレインを介して接地されているソースへ電流が流れることによって、ポート端子に接続された演出装置の出力状態を制御できる。

30

【0173】

また、装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 は、I<sup>2</sup>C I / O エクスパンダ 615 のポート端子に接続された全ての演出装置を同時期に制御することができる、I<sup>2</sup>C I / O エクスパンダ 615 のポート端子に接続された一つの演出装置を一つのグループとして制御することができる。

40

【0174】

そして、各装飾制御装置 610 に備わる I<sup>2</sup>C I / O エクスパンダ 615 同士は、互いに異なるアドレスが割り当てられているので、演出装置が複数のグループに分割された形態となっている。即ち、各装飾制御装置 610 に備わる I<sup>2</sup>C I / O エクスパンダ 615 は、演出装置をグループ単位で制御可能なグループ単位制御手段として構成されているものである。

【0175】

従って、装飾制御装置 610 を統括する演出制御装置 550 は、グループ単位制御手段をグループを統括して制御するグループ統括制御手段として機能している。

50

## 【0176】

リセット信号発生回路 639 には、 $I^2C$  I / O エクスパンダ 615 に電源を供給する接続線 Vcc と接続される Vcc 端子、及び外部からのリセット信号を受け付ける RESET 端子が接続されている。

## 【0177】

リセット信号発生回路 639 は、 $I^2C$  I / O エクスパンダ 615 に電源が投入され、電圧が所定値まで立ち上がった場合、リセット信号を発生させ、発生させたリセット信号をバスコントローラ 634、出力設定レジスタ 635、及び出力コントローラ 636 に入力する。

## 【0178】

なお、外部から LOW レベルのリセット信号が入力された場合には、リセット信号発生回路 639 はリセット信号を出力するが、本実施形態では、図 8A 及び図 8B に示すように RESET 端子は HIGH にプルアップされているため、外部からリセット信号が入力されることはないので、リセット信号発生回路 639 は外部からの信号が入力されたことによって、リセット信号を発生させることはない。

## 【0179】

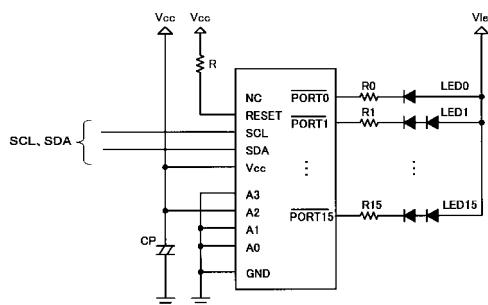

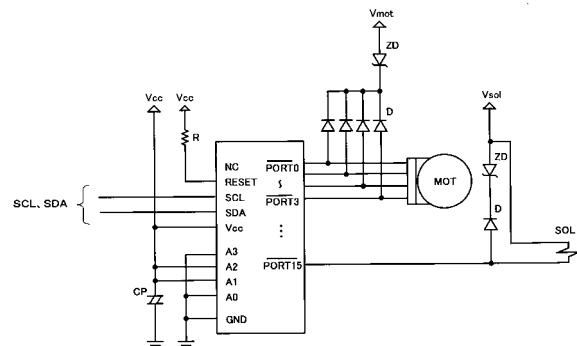

図 8A は、本発明の実施形態の装飾装置 620 を制御する装飾制御装置 610 の $I^2C$  I / O エクスパンダ 615 周辺の回路図である。

## 【0180】

$I^2C$  I / O エクスパンダ 615 は、入力端子として NC 端子、RESET 端子、SCL 端子、SDA 端子、Vcc 端子、A0 ~ A3 端子、及び GND 端子を備え、出力端子として、PORT0 ~ PORT15 を備える。

## 【0181】

RESET 端子には、プルアップ抵抗 R を介して $I^2C$  I / O エクスパンダ 615 に供給される電源が接続されている。このため、リセット端子に印加される電圧は常に HIGH に維持されている。

## 【0182】

SCL 端子は接続線 SCL に接続され、SDA 端子は接続線 SDA に接続される。

## 【0183】

Vcc 端子には、 $I^2C$  I / O エクスパンダ 615 に供給される電源が接続される。また、Vcc 端子には、電源ノイズを除去するコンデンサ C\_P が接続される。

## 【0184】

A0 端子 ~ A3 端子は、 $I^2C$  I / O エクスパンダ 615 にアドレスを設定するための端子である。なお、通常 $I^2C$  I / O エクスパンダ 615 のアドレスは、4 ビットで表現され、この端子に $I^2C$  I / O エクスパンダ 615 の電源が印加されている場合にはバスコントローラ 634 に「1」が設定され、この端子がグランドに接続されている場合にはバスコントローラ 634 に「0」が設定される。

## 【0185】

したがって、図 8A に示す $I^2C$  I / O エクスパンダ 615 のアドレスは「0100」であり、図 8B に示す $I^2C$  I / O エクスパンダ 615 のアドレスは「0110」である。GND 端子は、電圧をグランドするための端子である。

## 【0186】

各 PORT0 端子 ~ PORT15 端子は、電流制限抵抗 R0 ~ R15 を介して各 LED0 ~ LED15 からなる装飾装置 620 に接続される。なお、PORT0 によく、ポート 1 個に対して 1 個の LED を接続してもよいが、PORT1 ~ 15 のように、ポート 1 個に対して複数個の LED を接続してもよい。

## 【0187】

全てのポートに LED を 1 個ずつ設ける場合は、1 個の $I^2C$  I / O エクスパンダ 615 によって、最大で 16 個の LED を制御できることになる。また、各ポートに接続される LED の個数が異なる場合は、1 個のポートに直列に接続された全ての LED を 1 種類

10

20

30

40

50

のLEDということにすれば、1個のI<sup>2</sup>C I/Oエクスパンダ615によって、最大で16種類のLEDを制御できることになる。

【0188】

PORT0端子～PORT15端子に接続されるトランジスタ638A～638P(図7参照)のゲートに対してドライバ637から電圧が印加されると、電圧が印加されたトランジスタ638A～638Pのドレインからソースへ電流が流れることが可能になり、PORT0端子～PORT15端子に接続されるLED0～LED15に電流が流れ、各LED0～LED15は点灯する。

【0189】

一方、ドライバ637がトランジスタ638A～638Pのゲートに電圧を印加しなければ、各LED0～LED15に電流が流れない状態になり、各LED0～LED15は点灯しない。

【0190】

なお、I<sup>2</sup>C I/Oエクスパンダ615のPORT0端子～PORT15端子には、LEDの代わりに、モーターやソレノイドを接続することも可能であるので、I<sup>2</sup>C I/Oエクスパンダ615を用いて、モーターやソレノイドを駆動する場合について説明する。

【0191】

図8Bは、本発明の実施形態の役物駆動MOT561及び役物駆動SOL560を制御する装飾制御装置610のI<sup>2</sup>C I/Oエクスパンダ615周辺の回路図である。

【0192】

役物駆動MOT561はステッピングモータにより構成され、ステッピングモータを駆動する各相の信号端子に、所定の電圧を順次印加することで回動する。本実施形態では、役物駆動MOT561の各相の信号端子が、PORT0端子～PORT3端子に接続される。

【0193】

役物駆動MOT561に接続されているPORT0端子～PORT3端子に接続されるトランジスタ638A～638Dのいずれかのゲートに対してドライバ637から電圧が印加されると、電圧が印加されたトランジスタ638A～638Dのドレインからソースへ電流が流れることが可能になり、PORT0端子～PORT3端子に接続される役物駆動MOT561に電流が流れ、役物駆動MOT561が駆動する。

【0194】

なお、各PORT0端子～PORT3端子と役物駆動MOT561とを接続する接続線は分岐し、分岐した一方の接続線は、役物駆動MOT561に供給される電源にダイオードD及びツェナダイオードZDを介して接続される。

【0195】

また、PORT端子15は、役物駆動SOL560に接続される。役物駆動SOL560に接続されているPORT15端子に接続されるトランジスタ638Pのゲートに対してドライバ637から電圧が印加されると、電圧が印加されたトランジスタ638Pのドレインからソースへ電流が流れることが可能になり、PORT15端子に接続される役物駆動SOL560に電流が流れ、役物駆動AOL560が駆動する。

【0196】

なお、図8Bでは、I<sup>2</sup>C I/Oエクスパンダ615に役物駆動MOT561及び役物駆動SOL560の双方が接続されているが、一つのI<sup>2</sup>C I/Oエクスパンダ615に対して、役物駆動MOT561及び役物駆動SOL560の少なくとも一方だけを接続した構成でもよい。

【0197】

例えば、ステッピングモーターだけを制御するグループとしてのI<sup>2</sup>C I/Oエクスパンダ615を専用に設けたり、ソレノイドだけを制御するグループとしてのI<sup>2</sup>C I/Oエクスパンダ615を専用に設けるようにしてもよい。このような構成により、同一グループに属する演出装置を同じタイミングで制御することが可能となるので、高速処理が必

10

20

30

40

50

要な演出装置だけをグループ化して効率よく制御することも可能となる。

【0198】

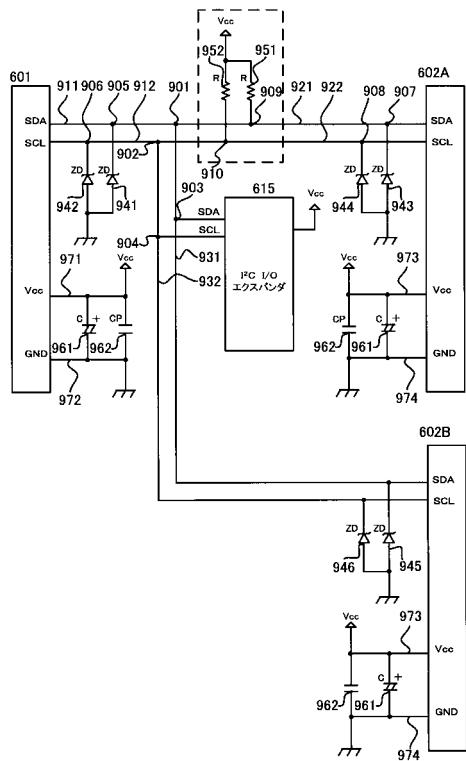

図9は、本発明の実施形態の中継基板600の入出力に関する接続線の回路図である。

【0199】

中継基板600は、上流コネクタ601、二つの下流コネクタ602A、602B、及びI<sup>2</sup>C I / Oエクスパンダ615を備える。

【0200】

上流コネクタ601は中継基板600よりも上流のマスタI C 570に接続されるコネクタであり、コネクタ602A、602Bは、中継基板600よりも下流の装飾制御装置610に接続される。

10

【0201】

二つの下流コネクタ602A、602Bに接続線SDAを接続するために、上流コネクタ601から延びる内部接続線SDA911は分岐901で第1接続線SDA921と第2接続線SDA931とに分岐する。第1接続線SDA921は下流コネクタ602Aに接続され、第2接続線SDA931は下流コネクタ602Bに接続される。

【0202】

同じく、上流コネクタ601から延びる内部接続線SCL912は分岐902で第1接続線SCL922と第2接続線SCL932とに分岐する。第1接続線SCL922は下流コネクタ602Aに接続され、第2接続線SCL932は下流コネクタ602Bに接続される。

20

【0203】

接続線SDAをI<sup>2</sup>C I / Oエクスパンダ615に接続するために、第2接続線SDA931は分岐903で分岐し、分岐した第2接続線SDA931はI<sup>2</sup>C I / Oエクスパンダ615の図8A及び図8に示すSDA端子に接続される。また、接続線SCLをI<sup>2</sup>C I / Oエクスパンダ615に接続するために、第2接続線SCL932は分岐904で分岐し、分岐した第2接続線SCL932はI<sup>2</sup>C I / Oエクスパンダ615の図8A及び図8Bに示すSCL端子に接続される。

【0204】

なお、I<sup>2</sup>C I / Oエクスパンダ615には、I<sup>2</sup>C I / Oエクスパンダ615の電源電圧となる電圧Vccが供給されている。また、図9では図示されていないが、I<sup>2</sup>C I / Oエクスパンダ615からは、中継基板600に設けたLED(装飾装置200)を駆動する各ポート0~15の信号線(図8A参照)が出力されている。

30

【0205】

また、I<sup>2</sup>C I / Oエクスパンダ615は、第2接続線SDA931及び第2接続線SCL932が接続されるとしたが、第1接続線SDA921及び第1接続線SCL922に接続されてもよい。

【0206】

I<sup>2</sup>C I / Oエクスパンダ615が上流のマスタI C 570に接続線SDAを介して出力する信号、及び上流のマスタI C 570から中継基板600のI<sup>2</sup>C I / Oエクスパンダ615へ接続線SDAを介して入力される信号のノイズを除去するために、内部接続線SDA911にはツェナダイオードZD941が接続されている。

40

【0207】

具体的には、内部接続線SDA911は分岐905で分岐し、分岐した内部接続線SDA911はツェナダイオードZD941のカソード側に接続され、ツェナダイオードZD941のアノード側は接地されている。

【0208】

このため、内部接続線SDA911に印加された所定以上の電圧(例えば、パルス性のノイズ信号)は、ツェナダイオードZD941によって逃がされる。

【0209】

また、上流のマスタI C 570から中継基板600のI<sup>2</sup>C I / Oエクスパンダ615

50

へ接続線 SCL を介して入力される信号のノイズを除去するために、内部接続線 SCL 912 にはツェナダイオード ZD942 が接続されている。

【0210】

具体的には、内部接続線 SCL 912 は分岐 906 で分岐し、分岐した内部接続線 SCL 912 はツェナダイオード ZD942 のカソード側に接続され、ツェナダイオード ZD942 のアノード側は接地されている。

【0211】

このため、内部接続線 SCL 912 に印加された所定以上の電圧（例えば、パルス性のノイズ信号）は、ツェナダイオード ZD942 によって逃がされる。

【0212】

中継基板 600 の I<sup>2</sup>C I / O エクスパンダ 615 が下流コネクタ 602A に接続された装飾制御装置 610 に接続線 SDA を介して出力する信号、及び下流コネクタ 602A に接続された装飾制御装置 610 から中継基板 600 の I<sup>2</sup>C I / O エクスパンダ 615 へ接続線 SDA を介して入力される信号のノイズを除去するために、第 1 接続線 SDA 921 にはツェナダイオード ZD943 が接続されている。

【0213】

具体的には、第 1 接続線 SDA 921 は分岐 907 で分岐し、分岐した第 1 接続線 SDA 921 はツェナダイオード ZD943 のカソード側に接続され、ツェナダイオード ZD943 のアノード側は接地されている。

【0214】

このため、内部接続線 SDA 921 に印加された所定以上の電圧（例えば、パルス性のノイズ信号）は、ツェナダイオード ZD943 によって逃がされる。

【0215】

また、第 1 接続線 SDA 921 に接続されるツェナダイオード ZD943 と同じく、第 2 接続線 SDA 931 にもツェナダイオード 945 が接続される。

【0216】

また、中継基板 600 の I<sup>2</sup>C I / O エクスパンダ 615 から下流コネクタ 602A に接続された装飾制御装置 610 へ接続線 SCL を介して入力される信号のノイズを除去するために、第 1 接続線 SCL 922 にはツェナダイオード ZD944 が接続されている。

【0217】

具体的には、第 1 接続線 SCL 922 は分岐 908 で分岐し、分岐した第 1 接続線 SCL 922 はツェナダイオード ZD944 のカソード側に接続され、ツェナダイオード ZD944 のアノード側は接地されている。

【0218】

このため、内部接続線 SCL 922 に印加された所定以上の電圧（例えば、パルス性のノイズ信号）は、ツェナダイオード ZD944 によって逃がされる。

【0219】

また、第 1 接続線 SCL 922 に接続されるツェナダイオード ZD944 と同じく、第 2 接続線 SCL 932 にもツェナダイオード ZD946 が接続される。

【0220】

また、マスタ I<sup>C</sup> 570 に接続される上流側の接続線 SDA、及び装飾制御装置 610 に接続される下流側の接続線 SDA の電圧をプルアップするためのプルアップ抵抗 R951 が、第 1 接続線 SDA 921 に接続される。同じく、マスタ I<sup>C</sup> 570 に接続される上流側の接続線 SCL、及び装飾制御装置 610 に接続される下流側の接続線 SCL の電圧をプルアップするためのプルアップ抵抗 R952 が、第 1 接続線 SDA 922 に接続される。

【0221】

具体的には、第 1 接続線 SDA 921 は分岐 909 で分岐し、分岐した第 1 接続線 SDA 921 はプルアップ抵抗 R951 に接続される。同じく第 1 接続線 SCL 922 は分岐 910 で分岐し、分岐した第 1 接続線 SCL 922 はプルアップ抵抗 R952 に接続され

10

20

30

40

50

る。

【0222】

なお、接続線 SDA 及び接続線 SCL の電圧をプルアップするプルアップ抵抗 951、952 は、中継基板 600 が備えなくてもよく、マスタ ICI 570 が備えてもよいし、中継基板 600 以外の装飾制御装置 610 が備えてもよい。要するに、接続線 SDA 及び接続線 SCL を駆動するトランジスタのドレインの端子に、電圧 Vcc を供給できる箇所であれば、どこでもよい。

【0223】

中継基板 600 の I<sup>2</sup>CI/O エクスパンダ 615 に電源電圧を供給する接続線 Vcc に接続される上流コネクタ 601 の Vcc 端子から延びる内部接続線 Vcc 971 と、上流コネクタ 601 の GND 端子から延び、接地されている内部接続線 GND 972 とは、平滑コンデンサ C961 及びバイパスコンデンサ 962 を介して接続されている。

10

【0224】

平滑コンデンサ C961 は、電源の電圧波形を滑らかにするためのコンデンサであり、バイパスコンデンサ C962 は、電源の電圧のノイズを除去するためのコンデンサである。

【0225】

このため、中継基板 600 の I<sup>2</sup>CI/O エクスパンダ 615 に供給される電源電圧は、平滑コンデンサ C961 により電圧が平滑化され、バイパスコンデンサ 962 によりノイズが除去されて、I<sup>2</sup>CI/O エクスパンダ 615 に供給される。

20

【0226】

同じく、下流コネクタ 602A、602B の Vcc 端子から延びる内部接続線 Vcc 973 と、GND 端子から延びる内部接続線 GND 974 とは、平滑コンデンサ C961 及びバイパスコンデンサ 962 を介して接続されている。これによって、平滑化され、ノイズが除去された電圧が下流の装飾制御装置 610 に接続される接続線 Vcc に印加される。

【0227】

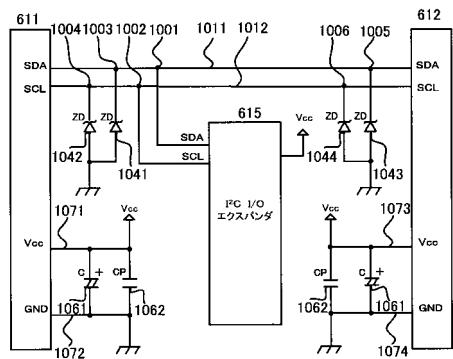

図 10 は、本発明の実施形態の装飾制御装置 610 の入出力に関する接続線の回路図である。

【0228】

30

装飾制御装置 610 は、上流コネクタ 611、I<sup>2</sup>CI/O エクスパンダ 615、及び下流コネクタ 612 を備える。

【0229】

上流コネクタ 611 には、中継基板 600 又は上流側の装飾制御装置 610 からバスが接続される。下流コネクタ 612 には、下流側の装飾制御装置 610 に接続するバスが接続される。

【0230】

上流コネクタ 611 の SDA 端子と下流コネクタ 612 の SDA 端子とは、内部接続線 SDA 1011 によって接続されている。また、上流コネクタ 611 の SCL 端子と下流コネクタ 612 の SCL 端子とは、内部接続線 SCL 1012 によって接続されている。

40

【0231】

接続線 SDA を I<sup>2</sup>CI/O エクスパンダ 615 に接続するために、内部接続線 SDA 1011 は分岐 1011 で分岐し、分岐した内部接続線 SDA 1011 は I<sup>2</sup>CI/O エクスパンダ 615 の図 8A 及び図 8 に示す SDA 端子に接続される。また、接続線 SCL を I<sup>2</sup>CI/O エクスパンダ 615 に接続するために、内部接続線 SCL 1012 は分岐 1002 で分岐し、分岐した内部接続線 SCL 1012 は I<sup>2</sup>CI/O エクスパンダ 615 の図 8A 及び図 8B に示す SCL 端子に接続される。

【0232】

なお、I<sup>2</sup>CI/O エクスパンダ 615 には、I<sup>2</sup>CI/O エクスパンダ 615 の電源電圧となる電圧 Vcc が供給されている。また、図 10 では図示されていないが、I<sup>2</sup>CI

50

/ O エクスパンダ 615 からは、当該装飾制御装置 610 に係わる LED (装飾装置 200) を駆動する各ポート 0 ~ 15 の信号線 (図 8A 参照) が出力されている。

【0233】

図 10 に示す装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 が上流コネクタ 611 に接続された上流の装飾制御装置 610 又は中継基板 600 に接続線 SDA を介して出力する信号、及び上流コネクタ 611 に接続された上流の装飾制御装置 610 又は中継基板 600 から図 10 に示す装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 へ接続線 SDA を介して入力される信号のノイズを除去するために、内部接続線 SDA 1011 にはツエナダイオード ZD 1041 が接続されている。

【0234】

具体的には、内部接続線 SDA 1011 は分岐 1003 で分岐し、分岐した内部接続線 SDA 1011 はツエナダイオード ZD 1041 のカソード側に接続され、ツエナダイオード ZD 1041 のアノード側は接地されている。

【0235】

このため、内部接続線 SDA 1011 に印加された所定以上の電圧 (例えば、パルス性のノイズ信号) は、ツエナダイオード ZD 1041 によって逃がされる。

【0236】

また、上流コネクタ 611 に接続される上流の装飾制御装置 610 又は中継基板 600 から図 10 に示す装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 へ接続線 SCL を介して入力される信号のノイズを除去するために、内部接続線 SCL 1012 にはツエナダイオード ZD 942 が接続されている。

【0237】

具体的には、内部接続線 SCL 1012 は分岐 1004 で分岐し、分岐した内部接続線 SCL 1012 はツエナダイオード ZD 1042 のカソード側に接続され、ツエナダイオード ZD 1042 のアノード側は接地されている。

【0238】

このため、内部接続線 SCL 1012 に印加された所定以上の電圧 (例えば、パルス性のノイズ信号) は、ツエナダイオード ZD 1042 によって逃がされる。

【0239】

図 10 に示す装飾制御装置 620 の I<sup>2</sup>C I / O エクスパンダ 615 が下流コネクタ 612 に接続された下流の装飾制御装置 610 に接続線 SDA を介して出力する信号、及び下流コネクタ 612 に接続された下流の装飾制御装置 610 から図 10 に示す装飾制御装置の I<sup>2</sup>C I / O エクスパンダ 615 へ接続線 SDA を介して入力される信号のノイズを除去するために、内部接続線 SDA 1011 にはツエナダイオード ZD 1043 が接続されている。

【0240】

具体的には、内部接続線 SDA 1011 は分岐 1005 で分岐し、分岐した内部接続線 SDA 1011 はツエナダイオード ZD 1043 のカソード側に接続され、ツエナダイオード ZD 1043 のアノード側は接地されている。

【0241】

このため、内部接続線 SDA 1011 に印加された所定以上の電圧 (例えば、パルス性のノイズ信号) は、ツエナダイオード ZD 1043 によって逃がされる。

【0242】

また、図 10 に示す装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 から下流コネクタ 612 に接続された下流の装飾制御装置 610 へ接続線 SCL を介して入力される信号のノイズを除去するために、内部接続線 SCL 1012 にはツエナダイオード ZD 1044 が接続されている。

【0243】

具体的には、内部接続線 SCL 1012 は分岐 1006 で分岐し、分岐した内部接続線 SCL 1012 はツエナダイオード ZD 1044 のカソード側に接続され、ツエナダイオ

10

20

30

40

50

ード Z D 1 0 4 4 のアノード側は接地されている。

【 0 2 4 4 】

このため、内部接続線 S C L 1 0 1 2 に印加された所定以上の電圧（例えば、パルス性のノイズ信号）は、ツェナダイオード Z D 1 0 4 4 によって逃がされる。

【 0 2 4 5 】

装飾制御装置 6 1 0 の I<sup>2</sup>C I / O エクスパンダ 6 1 5 に電源電圧を供給する接続線 V<sub>c c</sub> に接続される上流コネクタ 6 1 1 の V<sub>c c</sub> 端子から延びる内部接続線 V<sub>c c</sub> 1 0 7 1 と、上流コネクタ 6 1 1 の G N D 端子から延び、接地されている内部接続線 G N D 1 0 7 2 とは、平滑コンデンサ C 1 0 6 1 及びバイパスコンデンサ 1 0 6 2 を介して接続されている。

10

【 0 2 4 6 】

平滑コンデンサ C 1 0 6 1 は図 9 に示す平滑コンデンサ C 9 6 1 と同じコンデンサであり、バイパスコンデンサ C P 1 0 6 2 は図 9 に示すバイパスコンデンサ 9 6 2 と同じコンデンサである。

【 0 2 4 7 】

また、下流コネクタ 6 1 2 の V<sub>c c</sub> 端子から延びる内部接続線 V<sub>c c</sub> 1 0 7 3 と、 G N D 端子から延びる内部接続線 G N D 1 0 7 4 とは、平滑コンデンサ C 1 0 6 1 及びバイパスコンデンサ 1 0 6 2 を介して接続されている。

【 0 2 4 8 】

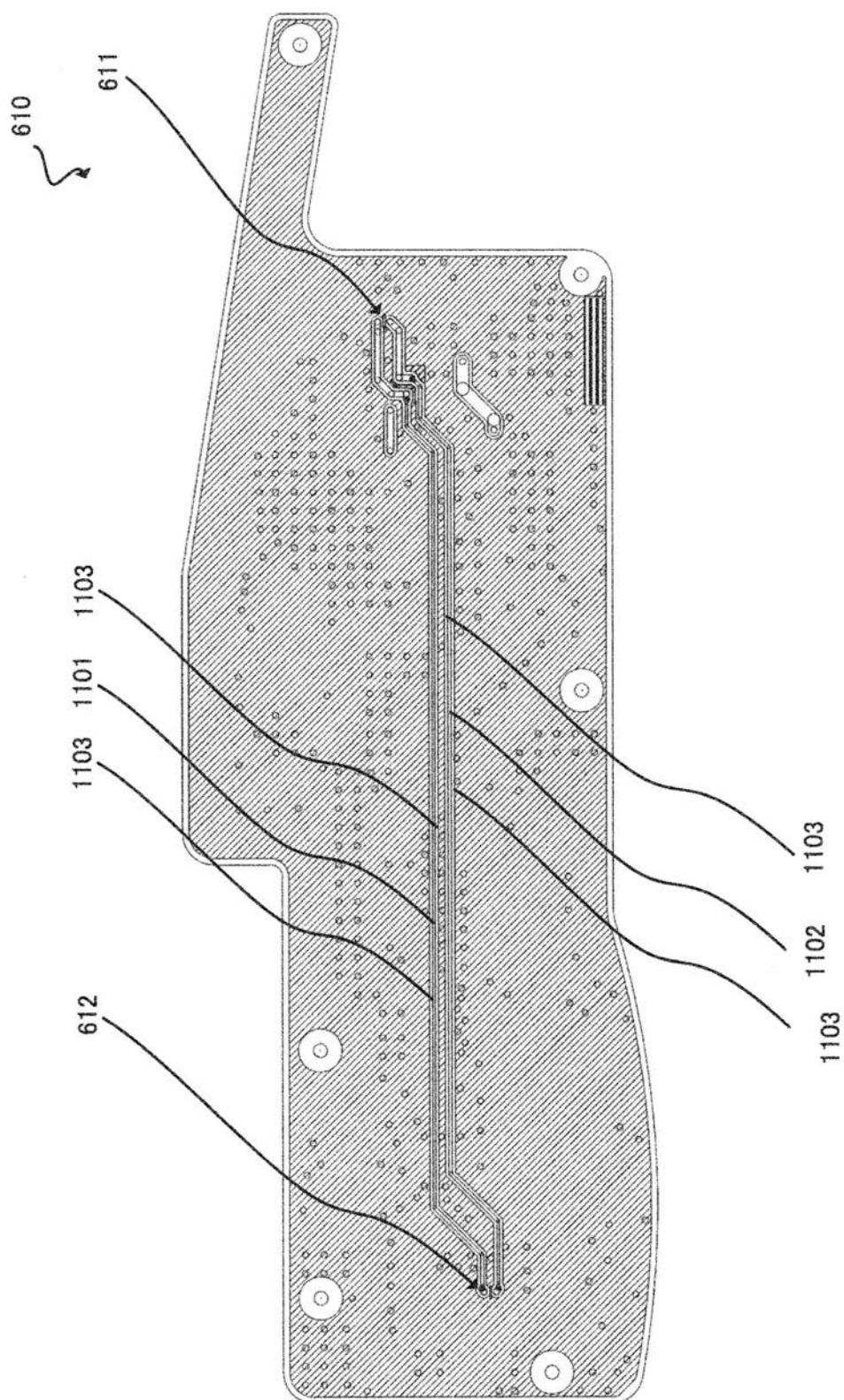

図 1 1 は、本発明の実施形態の装飾制御装置 6 1 0 の配線基板における S D A 接続パターン及び S C L 接続パターンの説明図である。

20

【 0 2 4 9 】

入力コネクタ 6 1 1 の S D A 端子と出力コネクタ 6 1 2 と S D A 端子は、内部 S D A 接続線である S D A 接続パターン 1 1 0 1 によって接続され、入力コネクタ 6 1 1 の S C L 端子と出力コネクタ 6 1 2 と S C L 端子は、内部 S C L 接続線である S C L 接続パターン 1 1 0 2 によって接続される。

【 0 2 5 0 】

S D A 接続パターン 1 1 0 1 と S C L 接続パターン 1 1 0 2 とは、略平行であって、ほぼ同じ長さとなるように配設される。

【 0 2 5 1 】

30

また、 S D A 接続パターン 1 1 0 1 及び S C L 接続パターン 1 1 0 2 の両側部は、絶縁体によって形成される G N D ガード 1 1 0 3 で覆われる。これによって、 S D A 接続パターン 1 1 0 1 に印加される電圧と S C L 接続パターン 1 1 0 2 に印加される電圧とが、互いに干渉して、誤った演出制御データが出力されることを防止できる。

【 0 2 5 2 】

なお、中継基板 6 0 0 の配線基板も、装飾制御装置 6 1 0 と同じく、 S D A 接続パターン及び S C L 接続パターンが絶縁体で覆われている。

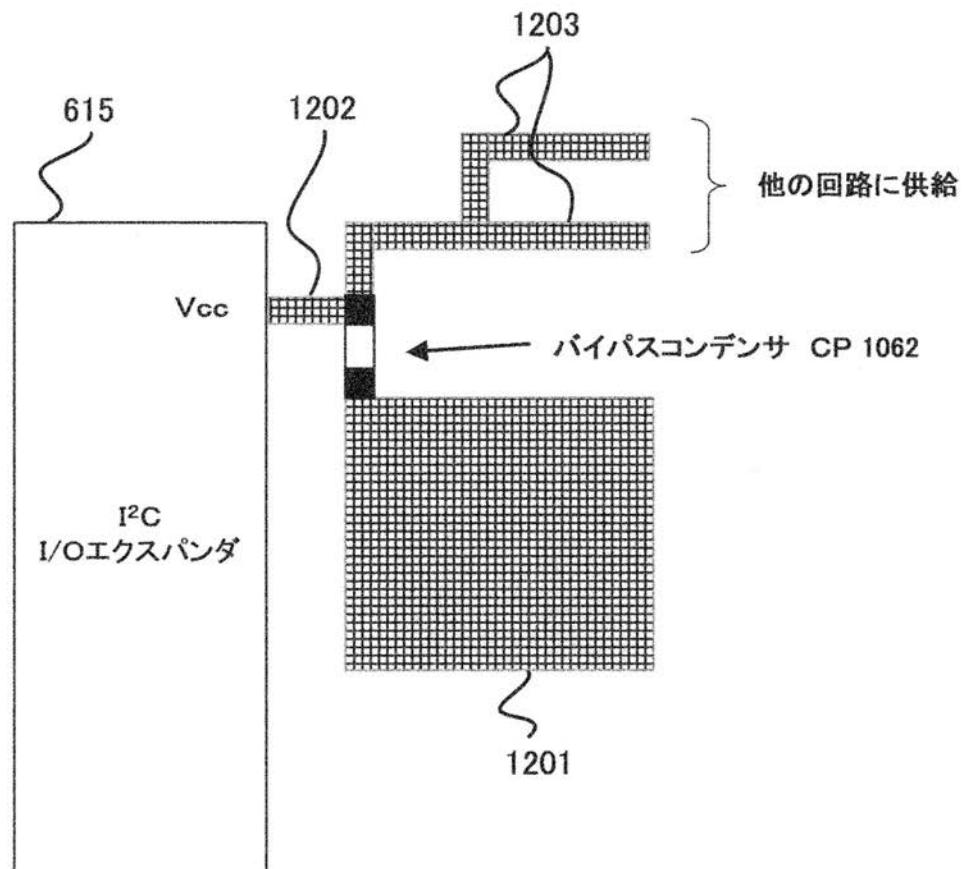

【 0 2 5 3 】

図 1 2 は、本発明の実施形態の I<sup>2</sup>C I / O エクスパンダ 6 1 5 の V<sub>c c</sub> 端子への電源の供給方法の説明図である。

40

【 0 2 5 4 】

上流の装飾制御装置 6 1 0 又は中継基板 6 0 0 から図 1 2 に示す I<sup>2</sup>C I / O エクスパンダ 6 1 5 を備える装飾制御装置 6 1 0 に接続される接続線 V<sub>c c</sub> から供給される I<sup>2</sup>C I / O エクスパンダ 6 1 5 の電源電圧は、 I<sup>2</sup>C I / O エクスパンダ 6 1 5 の V<sub>c c</sub> 端子から供給される。

【 0 2 5 5 】

また、図 1 0 で説明したように、 I<sup>2</sup>C I / O エクスパンダ 6 1 5 に供給される電源電圧は、接続線 V<sub>c c</sub> に印加される電圧が平滑コンデンサ 1 0 6 1 により平滑化されるとともに、バイパスコンデンサ 1 0 6 2 によりノイズが除去されたものである。

【 0 2 5 6 】

50

バイパスコンデンサ 1062 の一方は図 10 に示すようにグランドに接続される。このグランドは、装飾制御装置 610 の基板上では絶縁体である GND パターン 1201 により構成される。

【0257】

また、バイパスコンデンサ 1062 の他方は、I<sup>2</sup>C I / O エクスパンダ電源接続パターン 1202 によって I<sup>2</sup>C I / O エクスパンダ 615 の Vcc 端子に接続されるとともに、他回路電源接続パターン 1203 によって他の回路（例えば、下流コネクタ 612 の Vcc 端子など）に接続される。

【0258】

この場合、I<sup>2</sup>C I / O エクスパンダ電源接続パターン 1202 の長さが他回路電源接続パターン 1203 の長さよりも短くなるように、I<sup>2</sup>C I / O エクスパンダ 615 とバイパスコンデンサ 1062 とが配置されている。つまり、バイパスコンデンサ 1062 は、他の回路よりも I<sup>2</sup>C I / O エクスパンダ 615 に近くに配置される。

【0259】

また、I<sup>2</sup>C I / O エクスパンダ電源接続パターン 1202 上から他回路電源接続パターン 1203 が分岐しないようにする。

【0260】

これらは、I<sup>2</sup>C I / O エクスパンダ 615 にノイズが含まれた電源が供給されることを防止するためである。

【0261】

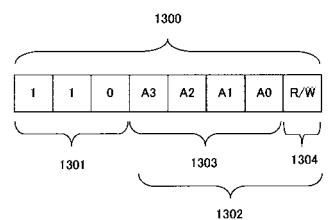

図 13 は、本発明の実施形態の演出制御装置 550 から装飾制御装置 610 に出力されるデータに含まれるスレーブアドレス 1300 の説明図である。

【0262】

スレーブアドレス 1300 は、上位 3 ビットからなる固定アドレス部 1301 及び下位 5 ビットからなる可変アドレス部 1302 を含む。

【0263】

固定アドレス部 1301 は、「110」が予め設定されていて、I<sup>2</sup>C I / O エクスパンダ 615 が変更できないアドレスである。

【0264】

可変アドレス部 1302 は、I<sup>2</sup>C I / O エクスパンダ 615 に設定可能なアドレスであり、制御対象となる I<sup>2</sup>C I / O エクスパンダ 615 の A0 ~ A3 の端子に設定されているパターンに対応した 4 ビットの I<sup>2</sup>C I / O エクスパンダアドレス 1303 と、当該データが読み出し要求であるのか書き込み要求であるのかを示す 1 ビットの R / W 識別データ 1304 と、が含まれる。

【0265】

演出制御装置 550 から装飾制御装置 610 に出力される演出制御データは、書き込み要求であるので、R / W 識別データ 1304 には、通常「0」が登録される。

【0266】

図 14 は、本発明の実施形態の I<sup>2</sup>C I / O エクスパンダアドレステーブル 1400 の説明図である。

【0267】

I<sup>2</sup>C I / O エクスパンダアドレステーブル 1400 は、マスター IC570 によって管理されるテーブルである。I<sup>2</sup>C I / O エクスパンダアドレステーブル 1400 は、スレーブアドレス 1401 と I<sup>2</sup>C I / O エクスパンダアドレス 1402 との対応関係を示している。

【0268】

スレーブアドレス 1401 には、演出制御装置 550 により送受信の対象として指定される装飾制御装置 610 のスレーブアドレスが格納されている。スレーブアドレスは、図 13 で前述したように、上位 3 ビットからなる固定アドレス部と、4 ビットの I<sup>2</sup>C I / O エクスパンダアドレスと、1 ビットの R / W 識別データとを組み合わせて構成される。

10

20

30

40

50

## 【0269】

I<sup>2</sup>C I / Oエクスパンダアドレス1402には、図8Aや図8Bで前述したように、各スレーブアドレスに対応する4ビットのI<sup>2</sup>C I / Oエクスパンダアドレスが登録される。

## 【0270】

ただし、I<sup>2</sup>C I / Oエクスパンダアドレスのうち、アドレス「1000」及びアドレス「1011」は、各I<sup>2</sup>C I / Oエクスパンダ615を相互に識別するための固有のアドレスとしては使用できない。

## 【0271】

「1000」は、すべての装飾制御装置610に対する指令を出力する場合に指定されるアドレス（オールコールアドレス）の電源投入時のデフォルト値として用いられる。「1011」はソフトウェアによってデバイスをリセットする場合に用いられるアドレスである。

## 【0272】

このように、装飾制御装置610のI<sup>2</sup>C I / Oエクスパンダ615に設定可能なアドレスは14個であるために、演出制御装置550は、14個のI<sup>2</sup>C I / Oエクスパンダ615を制御できる。また、一つの装飾制御装置610は、PORT0～PORT15を備えるので、16個（言い換えれば16種類）のLEDを制御できる。よって、演出制御装置550は、224個（言い換えれば224種類）のLEDを制御できる。

## 【0273】

図15は、本発明の実施形態の演出制御装置550による処理のフローチャートである。

## 【0274】

図15に示す処理では、例えば、装飾装置620のグループ、役物駆動SOL560のグループ、及び役物駆動MOT561のグループのように、演出装置の種類ごとのグループに分割し、装飾制御装置610は、分割されたグループに属する演出装置を制御する。例として、装飾装置620のグループが8グループ存在するものとして、それぞれ発光型演出装置のグループA～Hということにする。また、役物駆動SOL560と役物駆動MOT561は、同一のグループになっているものとして、これを可動型演出装置のグループということにする。

## 【0275】

図15に示す演出制御装置550の処理は、演出制御装置550のCPU551によって実行される。

## 【0276】

演出制御装置550は、演出制御装置550に電源が投入されると、まずステップ1501～1509の処理を実行し、ステップ1510の処理でVDP556から画像更新周期と同期する同期信号（例えば、1/30秒周期の同期信号）が割込信号としてCPU551に入力されるまで待機する。そして、VDP556から画像更新周期と同期する同期信号が割込信号としてCPU551に入力されると、ステップ1502～1509の処理を繰り返し実行する。

## 【0277】

まず、演出制御装置550は、演出制御装置550を初期化する（1501）。このとき、入出力I/F558を介してマスタIIC570が初期化され、さらに、マスタIIC570に指示して、全てのI<sup>2</sup>C I / Oエクスパンダ615をリセットして初期状態にする。

## 【0278】

次に、演出制御装置550は、表示装置53に画像を表示するために、VDP556に画像を表示させる指令となるデータを出力する（1502）。

## 【0279】

そして、演出制御装置550は、役物駆動SOL560及び役物駆動MOT561を遊

10

20

30

40

50

技状態に応じて制御するための演出制御データを、役物駆動SOL560及び役物駆動MOT561を制御する装飾制御装置610に出力する(1503)。

【0280】

そして、演出制御装置550は、スピーカ30から音を遊技状態に応じて出力させるために、音制御データを音LSI557に出力し、音LSI557に音制御データに基づいてスピーカ30から音を出力させる(1504)。

【0281】

そして、演出制御装置550は、図16に示すスレーブ選択順序テーブル1600を参照し、VDP556からCPU551に同期信号が入力されるごとに更新する時分割カウンタのスレーブ選択順序を選択し、選択したスレーブ選択順序に基づいて、装飾装置620を制御する各グループの装飾制御装置610に演出制御データをマスタIC570から出力する(1505)。

10

【0282】

なお、時分割カウンタは「0」～「3」までの値をとり、CPU551にVDP556から同期信号が入力されると、CPU551は、時分割カウンタをインクリメントする。なお、時分割カウンタが「3」である場合に、VDP556からCPU551に同期信号が入力されると、CPU551は、時分割カウンタを「0」に更新する。

【0283】

次に、演出制御装置550は、VDP556に次に出力されるデータを編集し(1506)、役物駆動SOL560及び役物駆動MOT561を制御する装飾制御装置610に次に出力される演出制御データを編集する(1507)。

20

【0284】

そして、演出制御装置550は、音LSI557に出力される音制御データを編集し(1508)、装飾装置620を制御する各グループの装飾制御装置610に次に出力される演出制御データを編集し(1509)、VDP556から同期信号がCPU551に入力されるまで待機する。

【0285】

なお、CPU551にVDP556から同期信号が入力されると、演出制御装置550は、時分割カウンタを更新し(1510)、ステップ1502の処理に進む。

30

【0286】

このように、図15による処理では、表示装置53の画像を更新する周期と同期して、演出制御装置550のマスタIC570から装飾制御装置610のI<sup>2</sup>CI/Oエクスパンダ615へ演出制御データを送信し、I<sup>2</sup>CI/Oエクスパンダ615は受信した演出制御データに基づいて演出装置620を制御するので、表示装置53における演出と演出装置620における演出とが調和し、遊技者に違和感を与えないで、興奮を高めることができる。

【0287】

また、図15による処理では、マスタIC570は、先に役物駆動SOL560及び役物駆動MOT561を制御する装飾制御装置610に演出制御データを出力し、後から装飾装置620を制御する装飾制御装置610に演出制御データを出力する。このため、同期信号の発生タイミングからの経過時間のばらつきが、役物駆動MOT561及び役物駆動MOT561に関しては小さく、装飾装置620に関しては大きくなる。そのため、役物駆動MOT561及び役物駆動MOT561が制御されるタイミングがより正確になり、遊技者の注目を集め可動役物60などを遊技状態に対して正確に制御できるので、遊技者に違和感を与えない。

40

【0288】

図16は、本発明の実施形態のスレーブ選択順序テーブル1600の説明図である。

【0289】

スレーブ選択順序テーブル1600は制御ROM552に記憶され、スレーブ選択順序テーブル1600には、時分割カウンタの値ごとに制御対象となる装飾制御装置610の

50

グループの制御順序が登録されている。

【0290】

なお、以下の説明では、前述したように、可動型演出装置グループは、役物駆動SOL560及び役物駆動MOT561を制御する装飾制御装置610のグループであり、発光型演出装置グループA～Hは、装飾装置620を制御する装飾制御装置610のグループである。

【0291】

スレーブ選択順序テーブル1600は、時分割カウンタ1601及びスレーブ選択順序1602を含む。

【0292】

時分割カウンタ1601には「0」～「3」の値が登録されている。スレーブ選択順序1602は、マスタIC570が演出制御データを出力する装飾制御装置620の順序が登録されている。ここでは、図15のステップ1503における「モータ・ソレノイド関連出力」の処理にて、可動型演出装置グループが制御され、その後、図15のステップ1505における「時分割カウンタに対応する発光装置関連出力」の処理にて、発光型演出装置グループA～Hのうち、時分割カウンタに対応するグループのみが表の上から下へ向かう順序で制御されることを示している。

【0293】

時分割カウンタ1601が「0」である場合のスレーブ選択順序1602には、可動型演出装置グループ、発光型演出装置グループA、発光型演出装置グループB、発光型演出装置グループD、及び発光型演出装置グループHが登録されている。CPU551は、可動型演出装置グループ、発光型演出装置グループA、発光型演出装置グループB、発光型演出装置グループD、及び発光型演出装置グループHの順で制御する。

【0294】

時分割カウンタ1601が「1」である場合のスレーブ選択順序1602には、可動型演出装置グループ、発光型演出装置グループA、発光型演出装置グループC、及び発光型演出装置グループEが登録されている。

【0295】

時分割カウンタ1601が「2」である場合のスレーブ選択順序1602には、可動型演出装置グループ、発光型演出装置グループA、発光型演出装置グループB、及び発光型演出装置グループFが登録されている。

【0296】

時分割カウンタ1601が「3」である場合のスレーブ選択順序1602には、可動型演出装置グループ、発光型演出装置グループA、発光型演出装置グループC、及び発光型演出装置グループGが登録されている。

【0297】

つまり、可動型演出装置グループの装飾制御装置610には、最初にマスタIC570から演出制御データが出力され、可動型演出装置グループの装飾制御装置610に演出制御データが出力された後に、発光型演出装置グループの装飾制御装置610に演出制御データが出力される。

【0298】

図17にて詳細に説明するが、マスタIC570は、制御対象の装飾制御装置610に演出制御データを初めに出力し、制御対象の装飾制御装置610からACKの返答信号が入力された場合には、次の制御対象となる装飾制御装置610を選択して演出制御データを出力する。

【0299】

したがって、ACKの返答信号が無条件に装飾制御装置610からマスタIC570に入力されるのであれば、同期信号に同期してマスタIC570から装飾制御装置610に演出制御データを送信できる。しかしながら、データ通信がノイズ等により正しく送信できない場合には、制御対象の装飾制御装置610からACKの返答信号が入力されない(

10

20

30

40

50

NACKの返答信号が入力される)ことになり、この場合には、再度同じデータを制御対象の装飾制御装置610に出力する処理を行っている。

#### 【0300】

このため、スレーブ選択順序が後になる装飾制御装置610ほど、マスターIC570から送信される演出制御データが入力されるタイミングが周期的にならない傾向がある。言い換えれば、同期信号の発生タイミングと演出制御データの送信タイミングとに時間差があり、この時間差のばらつきがスレーブ選択順序が後になる装飾制御装置610ほど大きくなるということになる。

#### 【0301】

また、可動型演出装置グループの装飾制御装置610が制御する演出装置は、遊技状態にあわせて可動するため、遊技状態にあわせて発光する装飾装置620よりも遊技者の注目を集めるものである。

#### 【0302】

したがって、可動型演出装置グループの装飾制御装置610が制御する演出装置の制御タイミングに遅れが生じないように、マスターIC570は、可動型演出装置グループの装飾制御装置610に最初に演出制御データを出力するようにしている。

#### 【0303】

次に、スレーブ選択順序テーブル1600による各グループの装飾制御装置610の制御頻度について説明する。

#### 【0304】

可動型演出装置グループ、及び発光型演出装置グループAは、時分割カウンタのすべてに登録されているので、VDP556からの同期信号がCPU551に入力されるごとに制御される。また、発光型演出装置グループB及び発光型演出装置グループCは、時分割カウンタが「1」である場合と「2」である場合とに登録されているので、VDP556から同期信号がCPU551に2回入力されると、1回制御される。また、発光型演出装置グループD～Hは、時分割カウンタが「0」～「3」のいずれか一つである場合に登録されているので、VDP556から同期信号がCPU551に4回入力されると、1回制御される。

#### 【0305】

なお、発光型演出装置グループA～Hは、グループに属するLEDの制御頻度に応じて、適宜割り当てられている。例えば、高速な輝度変化を必要とするLEDのグループをグループAとして割り当て、低速な輝度変化で充分なLEDのグループはグループD～Hを割り当てている。

#### 【0306】

これにより、可動型演出装置グループの装飾制御装置610の制御頻度が、発光型演出装置グループB～Hの装飾制御装置610の制御頻度以上になる。このため、遊技者の注目度の高い可動型演出装置グループの装飾制御装置610が制御する演出装置の制御間隔を細分化できるため、遊技者に違和感の少ない演出を行うことができる。

#### 【0307】

また、同期信号が発生するたびに、マスターIC570から、発光型演出装置グループA～Hの全てに演出制御データを送信するのではなく、時分割カウンタに対応する一部の発光型演出装置グループを選択して演出制御データを送信している。このため、同期信号の周期内に占める演出制御データの送信時間の割合が少なくなり、処理時間を効率化することができる。

#### 【0308】

また、本実施形態では、可動型演出装置グループの装飾制御装置610の制御頻度が、VDP556から出力される画像更新周期と同期する同期信号のタイミングで制御を行っているが、発光型演出装置グループA～Hの制御頻度だけを同期信号に同期させ、可動型演出装置グループの装飾制御装置610の制御頻度は、より高速(例えば2ミリ秒周期)にしてもよい。

10

20

30

40

50

## 【0309】

図17は、本発明の実施形態のマスタIC570によるスレーブ出力処理のフローチャートである。

## 【0310】

図15に示すステップ1503の処理が実行されると、可動型演出装置グループとなるスレーブが選択されて、マスタIC570のコントローラ574により、このスレーブ出力処理が実行される。また、図15に示すステップ1505の処理が実行された場合には、図16で前述した時分割カウンタに対応する発光型演出装置グループのスレーブが順に選択され、その都度、マスタIC570のコントローラ574により、このスレーブ出力処理が実行される。

10

## 【0311】

まず、マスタIC570は、装飾制御装置610からのACKの返答信号が受信できなかった回数を計数するためのACKカウンタを0に初期化する(1700)。次に、マスタIC570は、接続線SDA及び接続線SCLの信号レベルを、スタート条件を示す信号レベルに変化させる(1701)。

## 【0312】

具体的には、マスタIC570は、接続線SCLの信号レベルをHIGHに維持したまま、接続線SDAの信号レベルをHIGHからLOWに変化させることによってスタート条件を示す信号を出力する。

20

## 【0313】

装飾制御装置610にスタート条件が入力されると、装飾制御装置610は、接続線SCLの信号レベルをカウントするための図示しない信号変化カウンタを0回に初期化する。

## 【0314】

なお、マスタIC570は、スタート条件を示す信号を出力後、制御対象となる装飾制御装置610へデータを送るために、接続線SCLのレベルをLOWに変更する。

## 【0315】

次に、マスタIC570は、制御対象となる装飾制御装置610のスレーブアドレスのデータを、接続線SCLの信号レベルを変化させながら、接続線SDAを介して出力する(1702)。

30

## 【0316】

ステップ1702の処理で出力されるアドレスデータは図13に示すように8ビットのデータ列であるため、1回の出力処理(接続線SCLが8回HIGHに変化する間の出力)でアドレスデータが出力される。

## 【0317】

ステップ1702の処理で出力されたアドレスデータが装飾制御装置610に入力された場合、装飾制御装置610のI<sup>2</sup>CI/Oエクスパンダ615は、入力されたアドレスデータと自身に設定されているアドレスとが一致するか否かを判定する。

## 【0318】

入力されたアドレスデータと一致するアドレスが設定されているI<sup>2</sup>CI/Oエクスパンダ615は、接続線SCLのLOWからHIGHへの変更回数が8回目になった直後であって、そのHIGHレベルとなっている接続線SCLがLOWレベルへと変化することを契機として、返答信号を接続線SDAからマスタIC570に出力する。

40

## 【0319】

次に、マスタIC570は、ステップ1702の処理でアドレスデータが出力されてから所定時間以内にACKの返答信号がマスタIC570に入力されたか否かを確認する(1703)。

## 【0320】

ACKの返答信号が入力されたか否かによって、処理が以下の三つに分岐する(1704)。

50

## 【0321】

第1に、ステップ1702の処理でアドレスデータが初めて出力されてから所定時間以内にACKの返答信号が入力されない場合(ACKカウンタが0の状態でNACKの返答信号が入力された場合)には、マスターIC570は、再度アドレスデータを出力するために、ステップ1714の処理に移行する。ステップ1714の処理では、ACKの返答信号の受信に失敗したことを計数するためにACKカウンタを+1更新し、ステップ1701の処理に戻る。

## 【0322】

第2に、初めてステップ1702の処理で出力されたアドレスデータに対応するACKの返答信号が所定時間以内入力されず、再度ステップ1702の処理でアドレスデータが出力されてから所定時間以内にACKの返答信号が入力されない場合(ACKカウンタが1の状態でNACKの返答信号が入力された場合)には、マスターIC570は、スレーブ出力処理を異常終了する(1705)。この場合、今回選択している装飾制御装置610へのデータ送信を中止し、次の装飾制御装置610が選択されて、再度、スレーブ出力処理が先頭から実行されることになる。

10

## 【0323】

第3に、ステップ1702の処理でアドレスデータが初めて出力されてから所定時間以内にACKの返答信号が入力された場合、又は再度ステップ1702の処理でアドレスデータが初めて出力されてから所定時間以内にACKの返答信号が入力された場合には、マスターIC570は、出力用BUF572に記憶されているデータから8ビット分のデータを1番目に出力するデータとして取得し、取得したデータの出力を準備する(1706)。

20

## 【0324】

そして、マスターIC570は、取得したデータを接続線SDAから出力する(1707)。

## 【0325】

そして、ステップ1702の処理で出力されたアドレスデータが自身に設定されたアドレスと一致する装飾制御装置610のI<sup>2</sup>CI/Oエクスパンダ615は、ステップ1707の処理で出力されたデータを、接続線SCLがLOWからHIGHになったタイミングで取り込む。そして、当該装飾制御装置610のI<sup>2</sup>CI/Oエクスパンダ615は、接続線SCLの8回目のLOWからHIGHに変化したことでデータを取り込み、次いで接続線SCLがHIGHからLOWへ変化することを契機に、返答信号を接続線SDAからマスターIC570に出力する。

30

## 【0326】

次に、マスターIC570は、ステップ1707の処理でデータが出力されてから所定時間以内にACKの返答信号がマスターIC570に入力されたか否かを確認する(1708)。

## 【0327】

ACKの返答信号が入力されたか否かによって、処理が以下の三つに分岐する(1709)。

40

## 【0328】

第1に、ステップ1702の処理でアドレスデータが初めて出力されてから所定時間以内にACKの返答信号が入力されていない場合(ACKカウンタが0の状態でNACKの返答信号が入力された場合)には、マスターIC570は、再度アドレスデータを出力するために、ステップ1714の処理に移行する。ステップ1714の処理では、返答信号の受信に失敗したことを計数するためにACKカウンタを+1更新し、ステップ1701の処理に戻る。

## 【0329】

第2に、初めてステップ1707の処理で出力されたデータの返答信号が所定時間以内に入力されず、再度ステップ1707の処理でデータが出力されてから所定時間以内にA

50

C K の返答信号が入力されていない場合 (ACK カウンタが 1 の状態で NACK の返答信号が入力された場合) には、マスター I C 570 はスレーブ出力処理を異常終了する (1710)。この場合、今回選択している装飾制御装置 610 へのデータ送信を中止し、次の装飾制御装置 610 が選択されて、再度、スレーブ出力処理が先頭から実行されることになる。

【0330】

第3に、ステップ 1707 の処理でデータが初めて出力されてから所定時間以内に ACK の返答信号が入力された場合、又は再度ステップ 1707 の処理でデータが出力されてから所定時間以内に ACK の返答信号が入力された場合には、マスター I C 570 は、出力用 B U F 572 に記憶されているすべてのデータを出力したか否かを判定する (1711)。

10

【0331】

ステップ 1711 の処理で、出力用 B U F 572 に記憶されているデータが出力されていないと判定された場合、マスター I C 570 は、出力用 B U F 572 に記憶されている次の 8 ビット分のデータを次に出力するデータとして取得し、取得したデータの出力を準備し (1712)、ステップ 1706 の処理に戻る。

【0332】

一方、ステップ 1711 の処理で、出力用 B U F 572 に記憶されているすべてのデータを出力したと判定された場合、マスター I C 570 は、接続線 S D A 及び接続線 S C L の信号レベルを、ストップ条件を示す信号レベルに変化させ (1713)、スレーブ出力処理を終了する。

20

【0333】

ステップ 1713 の処理では、具体的には、マスター I C 570 は、接続線 S C L の信号レベルを H I G H に維持したまま、接続線 S D A の信号レベルを L O W から H I G H に変更させることによりストップ条件を示す信号を出力する。

【0334】

図 17 による処理では、マスター I C 570 は、8 ビットのデータを出力後に、装飾制御装置 610 からの返答信号を取り込むことにより、データ転送の成否を判定し、データ転送が失敗している場合 (つまり、NACK の返答信号がマスター I C 570 に入力された場合)、出力したデータを 1 回だけ再度出力するので、装飾制御装置 610 にデータを可能な限り確実に出力することができ、演出装置の誤動作を防止できる。また、出力したデータを 1 回だけ再度出力することにより、データ送信時間が必要以上に長くなることを防止できる。

30

【0335】

なお、図 17 による処理で、ステップ 1701 の処理でマスター I C 570 がスタート条件を送信する際には、接続線 S D A が H I G H になっている必要があるが、ノイズ等の影響によって、接続線 S D A が L O W となつたまま変化しない状態が発生する場合がある。

【0336】

本実施形態では、マスター I C 570 が装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 に送信するスレーブアドレスには、R / W 識別データが「0」 (書き込みを意味する) となっているものだけを用いている (図 13 参照) が、ノイズ等の影響によって、R / W 識別データが「1」 (読み出しを意味する) となった状態で、I<sup>2</sup>C I / O エクスパンダ 615 へ伝わることがある。

40

【0337】

この場合、I<sup>2</sup>C I / O エクスパンダ 615 は読み出しモードとなり、マスター I C 570 によって接続線 S C L の信号レベルが変化することに対応して、I<sup>2</sup>C I / O エクスパンダ 615 からマスター I C 570 へ、接続線 S D A を介してデータを 1 ビットごと伝送する処理を行う。

【0338】

このとき、I<sup>2</sup>C I / O エクスパンダ 615 は、8 ビットのデータを伝送するごとに、

50

マスタ I C 5 7 0 から接続線 S D A を介してアクノリッジ信号を受信する処理を行い、アクノリッジ信号を受信するとさらに 8 ビットのデータ伝送を行い、以後、この 8 ビットのデータ伝送とアクノリッジ信号の確認を繰り返すが、この間は、接続線 S D A が I<sup>2</sup> C I / O エクスパンダ 6 1 5 によって占有されている状態となる。

【 0 3 3 9 】

一方で、I<sup>2</sup> C I / O エクスパンダ 6 1 5 は、8 ビットのデータ伝送後に、マスタ I C 5 7 0 から接続線 S D A を介してアクノリッジ信号を受信できないときは、接続線 S D A を解放してデータ伝送を中止する。なお、I<sup>2</sup> C I / O エクスパンダ 6 1 5 は、マスタ I C 5 7 0 から接続線 S D A を介してアクノリッジ信号を受信する際には、接続線 S D A が L O W レベルであればアクノリッジ信号を受信したと解釈し、接続線 S D A が H I G H レベルであればアクノリッジ信号を受信しないと解釈する。

【 0 3 4 0 】

よって、マスタ I C 5 7 0 からのデータがノイズ等の影響により変化し、この変化したデータを勝手に受信して読み出しモードとなった I<sup>2</sup> C I / O エクスパンダ 6 1 5 が発生してしまうと、接続線 S D A がいつまでも解放されないことになる。

【 0 3 4 1 】

このような場合に、接続線 S D A の信号レベルは L O W に維持されたままになり、マスタ I C 5 7 0 と、本来送信を行うことを意図していた装飾制御装置 6 1 0 の I<sup>2</sup> C I / O エクスパンダ 6 1 5 との間で接続線 S D A を介した通信が行えなくなる。

【 0 3 4 2 】

そこで、マスタ I C 5 7 0 は、ステップ 1 7 0 1 の処理でスタート条件を示す信号を出力する前に、接続線 S D A からデータが出力できる状態であるか否かを判定するために、接続線 S D A の信号レベルが H I G H であるか否かを判定する。

【 0 3 4 3 】

接続線 S D A の信号レベルが H I G H でないと判定された場合、接続線 S D A からデータが出力できないので、ドライバ 5 7 6 A によりトランジスタ 5 7 8 A に動作可能な電圧を印加しないことによってトランジスタ 5 7 8 A をオンさせずに（接続線 S D A を解放した状態で）、接続 S C L の信号レベルを少なくとも 9 回変化させる。

【 0 3 4 4 】

このような処理を行うことで、読み出しモードとなった I<sup>2</sup> C I / O エクスパンダ 6 1 5 は、接続 S C L の信号レベルの変化に合わせて接続線 S D A にデータを出力するが、接続 S C L の信号レベルの変化が少なくとも 9 回行われる途中において、マスタ I C 5 7 0 からのアクノリッジ信号を確認するタイミングが発生する。このとき、接続線 S D A は解放されているので H I G H レベルとなり、読み出しモードとなった I<sup>2</sup> C I / O エクスパンダ 6 1 5 は、アクノリッジ信号を受信しなかったと判断するので、データ伝送をやめて接続線 S D A を解放することになる。

【 0 3 4 5 】

なお、この処理は、スタート条件を示す信号を出力する前だけでなく、マスタ I C 5 7 0 が飾制御装置 6 1 0 へデータを出力する前に行われるようにしてよい。具体的には、ステップ 1 7 0 2、1 7 0 7、及び 1 7 1 3 の処理の前に実行されてもよい。

【 0 3 4 6 】

このようにして、読み出しモードとなった装飾制御装置 6 1 0 の I<sup>2</sup> C I / O エクスパンダ 6 1 5 から強制的に接続線 S D A を解放させるので、接続線 S D A の信号レベルは H I G H に維持されるようになる。

【 0 3 4 7 】

図 1 8 は、本発明の実施形態のマスタ I C 5 7 0 が接続線 S D A 及び接続線 S C L を介して出力するデータのスタート条件及びストップ条件の説明図である。

【 0 3 4 8 】

接続線 S C L は通常時に信号レベルが H I G H になっており、マスタ I C 5 7 0 は、装飾制御装置 6 1 0 にデータを出力する際に、接続線 S C L の信号レベルを L O W から H I

10

20

30

40

50

G H に変化させ、装飾制御装置 610 が接続線 SDA のデータを取り込むためのストローブ信号として作用させる。

【0349】

接続線 SDA は通常時に信号レベルがHIGH になっており、接続線 SCL のクロック信号に合わせて接続線 SDA からデータが出力される。

【0350】

マスター I C 570 は、接続線 SCL の信号レベルをHIGH に維持したまま、接続線 SDA の信号レベルをHIGH からLOW に変化させることで、データの出力が開始することを示すスタート条件となる信号を出力する。

【0351】

装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 は、接続線 SDA 及び接続線 SCL からスタート条件となる信号が入力されると、データの出力が開始することを把握する。

10

【0352】

マスター I C 570 は、接続線 SCL の信号レベルをHIGH に維持したまま、接続線 SDA の信号レベルをLOW からHIGH に変化させることで、データの出力が終了することを示すストップ条件を示す信号を出力する。

【0353】

装飾制御装置 610 の I<sup>2</sup>C I / O エクスパンダ 615 は、ストップ条件が入力されると、データの出力が終了することを把握する。

20

【0354】

図19は、本発明の実施形態のマスター I C 570 から出力されたデータが入力された装飾制御装置 610 が返答信号を出力するタイミングチャートである。

【0355】

装飾制御装置 610 は、スタート条件が成立してから接続線 SCL の信号レベルの変化回数を計数し、接続線 SCL のクロック信号に合わせて接続線 SDA から入力されるデータを取り込む。

【0356】

そして、装飾制御装置 610 は、スタート条件が成立してから接続線 SCL の信号レベルの変化回数が9回に達する直前に、返答信号をマスター I C 570 に接続線 SDA を介して出力する。換言すると、装飾制御装置 610 は、接続線 SDA から8ビット目のデータを取り込んだ後に、接続線 SCL の信号レベルがHIGH からLOW に変化することを契機に、返答信号を当該接続線 SDA を介して出力する。

30

【0357】

なお、図に示すように、データの受信に成功したことを示す返答信号(ACKの返答信号)はLOWレベルによって示され、データの受信に失敗したことを示す返答信号(NACKの返答信号、図ではACK出力なしに相当)はHIGHレベルによって示される。

【0358】

また、マスター I C 570 は、スタート条件が成立してから接続線 SCL の信号レベルが8回変化すると、接続線 SDA を解放することによって、装飾制御装置 610 から返答信号の入力を待機する。そして、マスター I C 570 は、接続線 SDA を解放したまま、接続線 SCL の信号レベルを変化させて、装飾制御装置 610 からの返答信号を取り込む。

40

【0359】

図20は、本発明の実施形態のマスター I C 570 が演出制御データを出力する場合の接続線 SDA 及び接続線 SCL の信号レベルのタイミングチャートである。

【0360】

まず、マスター I C 570 は、演出制御データの出力を開始する場合には、接続線 SCL の信号レベルをHIGH に維持したまま、接続線 SDA の信号レベルをHIGH からLOW に変化させることによって、スタート条件を示す信号を出力し、これからデータを出力することを装飾制御装置 610 に通知する。

50

## 【0361】

次に、マスタ I C 570 は、合計 7 ビットからなる制御対象となる装飾制御装置 610 のアドレスを出力する。次に、マスタ I C 570 は、読み出し要求である書き込み要求であるかを示すデータを 8 ビット目に出力する。

## 【0362】

そして、マスタ I C 570 は、接続線 S C L の信号レベルが 9 回目に H I G H になるときに、装飾制御装置 610 から返答信号が入力されるので、A C K の返答信号であれば接続線 S D A の信号レベルが L O W に変化し、N A C K の返答信号であれば接続線 S D A の信号レベルが H I G H に変化する。

## 【0363】

次に、マスタ I C 570 は、アドレスデータの出力後、演出制御データを、8 の倍数となるビット数で出力する。マスタ I C 570 は、演出制御データの 8 ビット目を出力した後、A C K の返答信号が入力されるのを待って演出制御データの 9 ビット目を出力する。以降、8 の倍数番目に相当するビットのデータを出力すると、A C K の返答信号が入力されるのを確認してから、(8 の倍数 + 1) 番目のビットを出力し、全データが出力されるまで繰り返す。

## 【0364】

なお、マスタ I C 570 は、演出制御データの 8 の倍数番目となるビットを出力した後、所定時間経過しても A C K の返答信号が入力されない場合には、接続線 S D A を介して、再度アドレスデータを出力し、A C K の返答信号を確認しながら、もう一度、演出制御データを 1 ビット目から出力する。

## 【0365】

また、マスタ I C 570 は、演出制御データの最後のビットのデータを出力した後、A C K の返答信号が入力されるのを待って、ストップ条件を示す信号を出力する。

## 【0366】

なお、図 20 では、スタート条件を示す信号を出力してからストップ条件を示す信号を出力するまでの間に、合計 24 ビット(スレーブアドレス 8 ビット、演出制御データ 16 ビット)のデータを出力しているが、24 ビット以上であってもよいし、24 ビット以下であってもよい。

## 【0367】

図 21 は、本発明の実施形態のマスタ I C 570 が、スレーブアドレスを指定して装飾制御装置 610 にデータを設定する場合において、マスタ I C 570 と I<sup>2</sup> C I / O エクスパンダ 615 との間で授受されるデータのフォーマットを説明する図である。

## 【0368】

はじめに出力される 8 ビットのデータ 2101 には、データ送信の対象となる装飾制御装置 610 のアドレス「A0 ~ A6」と、当該データが読み出し要求であるか書き込み要求であるかを示す 1 ビットの R / W 識別データとが含まれる。このアドレス「A0 ~ A6」のうち、「A4 ~ A6」は値「110」となる固定アドレス部であり、「A0 ~ A3」は I<sup>2</sup> C I / O エクスパンダ 615 の A0 ~ A3 の端子に設定されているアドレスに相当する(図 13 参照)。

## 【0369】

次に、出力される 8 ビットのデータ 2102 には、出力設定レジスタ 635 には、I<sup>2</sup> C I / O エクスパンダ 615 の出力設定レジスタ 635(図 7 参照)に割り当てられている領域を指定するコントロールレジスタデータが含まれる。具体的には、5 ビットの「D0 ~ D4」からなるレジスタアドレスと、3 ビットの「A10 ~ A12」からなる自動書込パラメータとからなる。レジスタアドレスは出力設定レジスタ 635 の領域を指定する情報であり、マスタ I C 570 により書き込み又は読み出しを行う領域のアドレスを指定する。自動書込パラメータは、マスタ I C 570 によって、レジスタアドレスが指定する領域のみをアクセスするのか、指定する領域に隣接する領域も含んでアクセスするのかを指定するパラメータである。

10

20

30

40

50

## 【0370】

次に、出力される8の倍数となるビットのデータ2103には、コントロールレジスタデータによって指定される出力設定レジスタ635の領域に対して、実際に書き込まれるデータが割り当てられる。

## 【0371】

図22は、本発明の実施形態の装飾制御装置610を装飾制御する場合において、マスタI<sup>2</sup>C570とI<sup>2</sup>C I / Oエクスパンダ615との間で授受されるデータの具体的な数值例を示す説明図である。データは、図21のデータフォーマットによって、マスタI<sup>2</sup>C570とI<sup>2</sup>C I / Oエクスパンダ615との間で送受信される。

## 【0372】

はじめに出力される8ビットのデータ2201には、装飾制御装置610のI<sup>2</sup>C I / Oエクスパンダ615のスレーブアドレスを示す「1101100」が割り当てられている。

## 【0373】

次に出力される8ビットのデータ2202には、LEDの出力データを設定するために割り当てられている装飾制御装置610のI<sup>2</sup>C I / Oエクスパンダ615の出力設定レジスタ635のアドレスが含まれる。ここでは、I<sup>2</sup>C I / Oエクスパンダ615のPORT0端子～PORT3端子に接続されるLEDの発光状態を設定するための領域である、LEDOUT0レジスタ(アドレス=10100)を指定することにする。

## 【0374】

次に、出力される8ビットのデータ2203には、装飾制御装置610が装飾装置620に行う装飾制御の内容を示すデータが含まれる。具体的には、LEDOUT0レジスタに設定されるデータが割り当てられている。これにより、I<sup>2</sup>C I / Oエクスパンダ615のPORT0端子～PORT3端子に接続されるLEDの発光状態(点灯、消灯、点滅など)が指定され、指定された状態でLEDが発光する。

## 【0375】

このようにして、I<sup>2</sup>C I / Oエクスパンダ615のPORT0端子～PORT3端子のLEDの発光状態が制御されるが、I<sup>2</sup>C I / Oエクスパンダ615の他のPORT端子(PORT4～PORT15)も、コントロールレジスタデータ2202の値を指定して、出力データ2203を設定することで制御可能である。PORT端子に、モーター ソレノイドが接続されても、同様に制御される。

## 【0376】

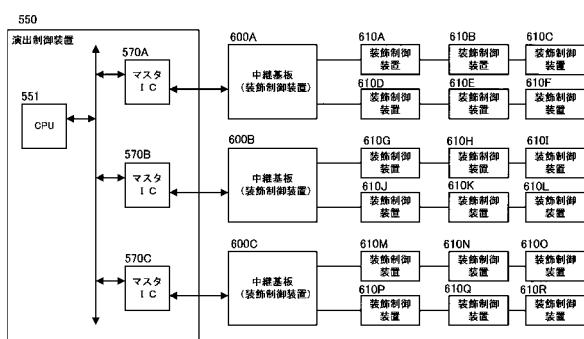

図23は、本発明の実施形態の演出制御装置550に複数のマスタI<sup>2</sup>C570が備わる場合のマスタI<sup>2</sup>C570と装飾制御装置610との接続の説明図である。

## 【0377】

図23では、演出制御装置550は、三つのマスタI<sup>2</sup>C570A～570Cを備える。

## 【0378】

マスタI<sup>2</sup>C570Aは、中継基板600Aと接続され、中継基板600Aは、装飾制御装置610A～610Cと直列に接続されるとともに、装飾制御装置610D～610Fと直列に接続される。

## 【0379】

マスタI<sup>2</sup>C570Bは、中継基板600Bと接続され、中継基板600Bは、装飾制御装置610G～610Iと直列に接続されるとともに、装飾制御装置610J～610Lと直列に接続される。

## 【0380】

マスタI<sup>2</sup>C570Cは、中継基板600Cと接続され、中継基板600Cは、装飾制御装置610M～610Oと直列に接続されるとともに、装飾制御装置610P～610Rと直列に接続される。

## 【0381】

ここで、一つのマスタI<sup>2</sup>C570に接続されている装飾制御装置610群を系統という

10

20

30

40

50

。系統とは、具体的には、マスタ I C 5 7 0 A であれば、中継基板 6 0 0 A、装飾制御装置 6 1 0 A ~ 6 1 0 F である。

【0382】

マスタ I C 5 7 0 は、接続されている装飾制御装置 6 1 0 にデータを出力可能であるため、マスタ I C 5 7 0 は、接続されている装飾制御装置 6 1 0 を制御可能である。

【0383】

このような構成により、1個のマスタ I C 5 7 0 で制御できる I<sup>2</sup> C I / O エクスパンダ 6 1 5 の数の制限（図 14 に示すように 14 個を上限とする）がなくなり、多彩な演出制御を可能とすることが期待できる。

【0384】

10

なお、今回開示した実施の形態は、全ての点で例示であって制限的なものではない。また、本発明の範囲は前述した発明の説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味及び内容の範囲での全ての変更が含まれることが意図される。

【産業上の利用可能性】

【0385】

以上のように、本発明は、演出制御装置が装飾制御装置を制御する遊技機に適用可能である。

【符号の説明】

【0386】

20

1 遊技機

2 本体枠（外枠）

3 前面枠

4 ヒンジ

1 0 遊技盤

1 1 照明ユニット

1 7 演出ボタン

1 8 ガラス枠

3 4 普通変動入賞装置

3 6 普通変動入賞装置

4 2 特別変動入賞装置

30

4 4 一般入賞口

4 5 第 1 始動入賞口

5 1 センターケース

5 2 窓部

5 3 表示装置

5 5 振動センサ

6 0 可動役物

5 0 0 遊技制御装置

5 5 0 演出制御装置

5 6 0 役物駆動 S O L

40

5 6 1 役物駆動 M O T

5 7 0 マスタ I C

5 8 0 払出制御装置

6 0 0 中継基板（装飾制御装置）

6 1 0 装飾制御装置

6 2 0 装飾装置

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8 A】

【図8 B】

【図9】

【図10】

【図13】

### 【図14】

【図15】

【図16】

【図17】

【图 18】

〔 図 20 〕

### 【図 19】

【図21】

【図22】

【図23】

【図 11】

【図12】

---

フロントページの続き

(72)発明者 松橋 光一

群馬県太田市吉沢町990番地 株式会社ソフィア内

審査官 阿南 進一

(56)参考文献 特開2001-038021(JP, A)

特開平02-170638(JP, A)

(58)調査した分野(Int.Cl., DB名)

A 63 F 7 / 02