(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2011년08월29일

(11) 등록번호 10-1060037

(24) 등록일자 2011년08월22일

(51) Int. Cl.

G11C 7/06 (2006.01) G11C 11/00 (2006.01)

(21) 출원번호 10-2005-7019216

(22) 출원일자(국제출원일자) 2004년04월08일

심사청구일자 2009년04월07일

(85) 번역문제출일자 2005년10월10일

(65) 공개번호 10-2006-0002967

(43) 공개일자 2006년01월09일

(86) 국제출원번호 PCT/US2004/010812

(87) 국제공개번호 WO 2004/093139

국제공개일자 2004년10월28일

(30) 우선권주장

10/412,490 2003년04월11일 미국(US)

(56) 선행기술조사문현

US6445632 B2

US5701268 A

전체 청구항 수 : 총 4 항

심사관 : 윤난영

(54) 감지 증폭기 및 자체 타이밍된 래치를 가지는 메모리 장치

### (57) 요 약

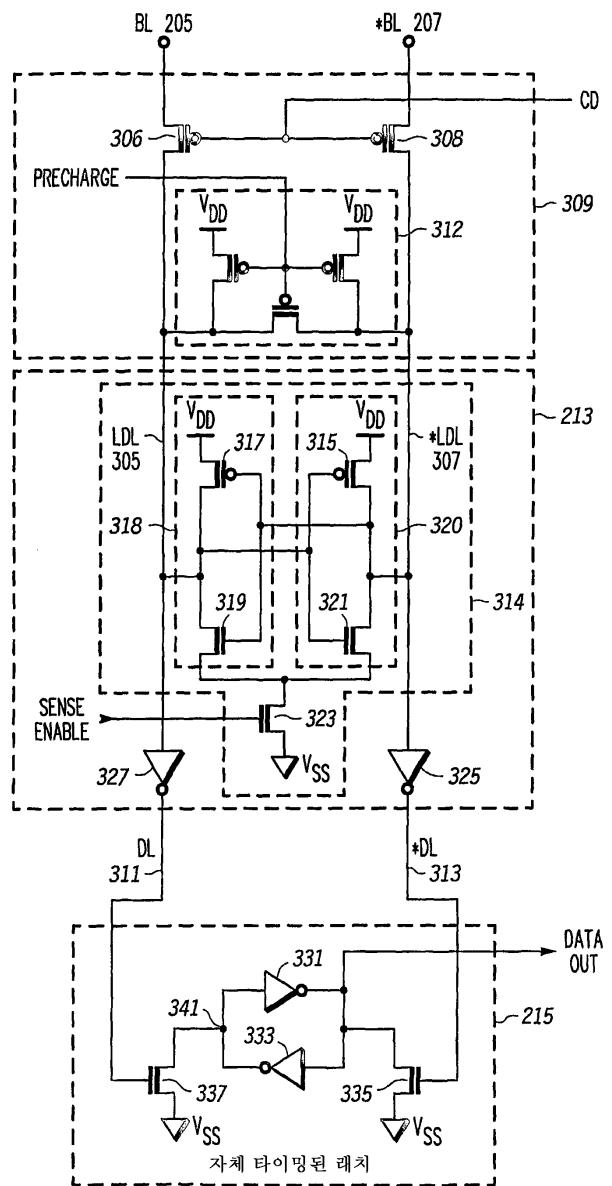

메모리 장치(201)는 다수의 메모리 셀들(203), 비트 라인들, 워드 라인들, 감지 증폭기(314) 및 자체 타이밍된 래치(215)를 포함한다. 감지 증폭기(314)는 감지 인에이블 신호에 응답하여 다수의 메모리 셀들 중 선택된 하나에 저장된 로직 상태에 대응하는 비트 라인들 상의 전압을 감지하고 증폭한다. 격리 회로(306, 308)는 비트 라인들(205, 207)과 감지 증폭기(314) 사이에 결합된다. 격리 회로(306, 308)는 감지 인에이블 신호의 어써트와 거의 동일한 시간 근방에서 다수의 메모리 셀들 중 선택된 하나를 감지 증폭기(314)로부터 분리한다. 자체 타이밍된 래치(215)는 감지 증폭기(314)에 결합된다. 자체 타이밍된 래치(215)는 클럭 신호를 수신하지 않으며, 단지 증폭된 전압에 반응한다.

### 대 표 도 - 도3

## 특허청구의 범위

### 청구항 1

각각이 비트 라인에 결합되는 복수의 메모리 셀들과,

감지 인에이블(enable) 신호의 어써트(assert)에 응답하여 상기 비트 라인을 통해 상기 복수의 메모리 셀들 중의 선택된 하나로부터의 데이터 신호를 증폭하여 증폭된 데이터 신호를 제공하는 감지 증폭기와,

상기 비트 라인과 상기 감지 증폭기 사이에 결합되며, 상기 감지 인에이블 신호의 어써트와 동시에 상기 복수의 메모리 셀들 중의 선택된 하나를 상기 감지 증폭기로부터 분리하는(decoupling) 격리 회로(isolation circuit) 와,

상기 감지 증폭기에 결합되며, 상기 증폭된 상기 데이터 신호에 응답하여서만 상기 증폭된 데이터 신호에 대응하는 데이터를 저장하는 자체 타이밍된(self-timed) 저장 장치

를 포함하는 메모리 장치.

### 청구항 2

각각이 제1 비트 라인에 및 제2 비트 라인에 결합되는 복수의 메모리 셀들과,

판독 싸이클의 적어도 일부 동안 상기 제1 비트 라인에 결합되는 제1 데이터 라인과,

상기 판독 싸이클의 적어도 일부 동안 상기 제2 비트 라인에 결합되는 제2 데이터 라인과,

상기 제1 데이터 라인에 및 상기 제2 데이터 라인에 결합되는 한 쌍의 교차결합된(cross-coupled) 인버터들을 구비하고, 감지 인에이블 신호의 어써트에 응답하여 상기 복수의 메모리 셀들 중의 선택된 하나로부터의 데이터 신호를 증폭하는 감지 증폭기와,

상기 제1 데이터 라인에 결합되는 입력, 및 출력을 구비하는 제1 버퍼 회로와,

상기 제2 데이터 라인에 결합되는 입력, 및 출력을 구비하는 제2 버퍼 회로와,

상기 제1 버퍼 회로의 출력에 결합되는 제1 입력과, 상기 제2 버퍼 회로의 출력에 결합되는 제2 입력을 구비하고, 상기 제1 버퍼 회로의 출력과 상기 제2 버퍼 회로의 출력 사이의 차분 전압에만 응답하는 자체 타이밍된 저장 장치

를 포함하는 메모리 장치.

### 청구항 3

각각이 비트 라인에 및 워드 라인에 결합되는 복수의 메모리 셀들을 포함하는 메모리 장치의 메모리 셀을 판독하는 방법으로서,

상기 복수의 메모리 셀들 중의 적어도 하나를 선택하는 단계와,

감지 인에이블 신호의 어써트에 응답하여 감지 증폭기를 이용하여 상기 비트 라인 상의 전압을 감지하고 증폭하여 증폭된 데이터 신호를 생성하는 단계 - 상기 증폭된 데이터 신호는 상기 선택에 의해서 선택된 상기 복수의 메모리 셀들 중의 적어도 하나에 저장된 로직 상태를 나타냄 - 와,

상기 감지 인에이블 신호가 어써트되는 것과 동시에 상기 비트 라인을 상기 감지 증폭기로부터 분리하는 단계와,

자체 타이밍된 래치에서 상기 증폭된 데이터 신호에 대응하는 데이터를 래치하는 단계 - 상기 자체 타이밍된 래치는 상기 증폭된 데이터 신호에만 응답하여 상기 데이터를 래치함 -

를 포함하는 메모리 셀 판독 방법.

### 청구항 4

복수의 메모리 셀들을 포함하는 메모리 장치의 메모리 셀을 판독하는 방법으로서,

상기 복수의 메모리 셀들 중의 적어도 하나를 선택하는 단계와,

감지 인에이블 신호의 어써트에 응답하여 감지 증폭기를 이용하여 전압을 감지하고 증폭하여 라인 상에 증폭된 데이터 신호를 생성하는 단계 - 상기 증폭된 데이터 신호는 상기 선택에 의해서 선택된 상기 복수의 메모리 셀들 중의 적어도 하나에 저장된 로직 상태를 나타냄 - 와,

자체 타이밍된 래치에서 상기 증폭된 데이터 신호에 대응하는 데이터를 래치하는 단계 - 상기 자체 타이밍된 래치는 상기 증폭된 데이터 신호에만 응답하여 상기 데이터를 래치함 - 와,

상기 감지 및 증폭 이후에 상기 라인을 사전충전하는(preecharging) 단계 - 상기 데이터는 적어도 상기 사전충전의 초기 부분 동안에는 래치된 상태로 남음 -

를 포함하는 메모리 셀 관독 방법.

청구항 5

삭제

청구항 6

삭제

청구항 7

삭제

청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

청구항 25

삭제

청구항 26

삭제

청구항 27

삭제

청구항 28

삭제

청구항 29

삭제

청구항 30

삭제

청구항 31

삭제

청구항 32

삭제

명세서

## 기술 분야

[0001]

본 발명은 전반적으로 집적 회로에 관한 것으로, 구체적으로는 메모리 장치에 관한 것이다.

## 배경 기술

[0002]

예컨대, RAM과 같은 메모리 장치들은 감지 증폭기에 결합되는 어레이의 메모리 셀에 저장되는 값을 나타내는 신호를 제공하는 감지 증폭기들을 포함한다.

[0003]

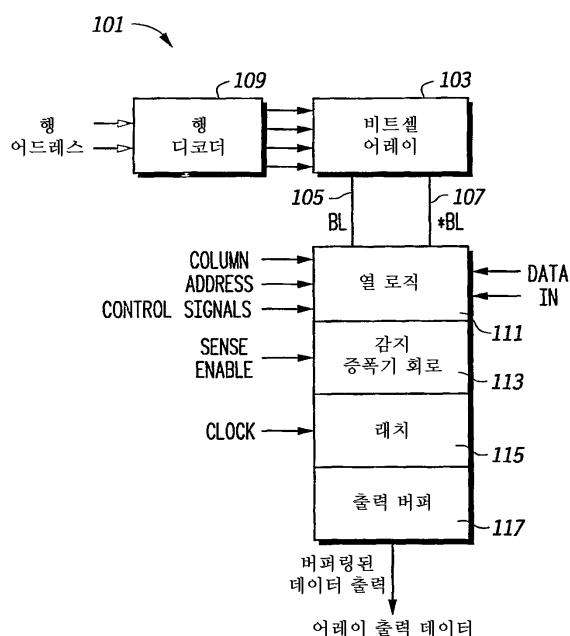

도 1은 종래 기술의 메모리 장치를 나타낸다. 메모리 장치(101)는 각각 데이터 비트를 저장하는 다수의 메모리 셀들을 가지는 비트셀 어레이(103)를 포함한다. 비트셀 어레이(103)의 메모리 셀들은 각각 한 쌍의 차분 비트 라인들 BL(105) 및 \*BL(107)에 결합된다. 어레이(103) 내의 각각의 셀은 행 디코더(109)에 결합되는 워드라인에 결합된다. 메모리 장치(101)는 열 로직(111), 감지 증폭기 회로(113), 래치(115) 및 출력 버퍼(117) 또한 포함한다. 열 로직(111)은 사전충전 및 등화 회로(precharge and equalization circuitry), 기록 회로, 열 디코드 회로 및 격리 트랜지스터들을 포함한다. 래치(115)는 래치(115)가 감지 증폭기 회로(113)의 출력으로부터 데이터를 샘플링할 수 있도록 하기 위한 용량 CLOCK 타이밍 신호를 수신한다. 제2 증폭기 회로(113)는 SENSE ENABLE 신호에 의해서 인에이블(enable)된다.

[0004]

다수의 감지 증폭기 회로들 및 래치들을 가지는 메모리 장치들에 대하여, 클럭 신호를 각각의 래치에 제공하는 것은 클럭 생성 회로에 많은 부하를 가하는 것이어서, 전력을 소비하며, 클럭 신호의 성능을 저하시킨다. 더욱이, 클럭 신호를 가지고서 래치(115)를 인에이블하는 것은 특정한 셋업 및 홀드 시간 요건이 클럭 신호와 감지 인에이블 신호 사이에 유지될 것을 요구한다. 메모리 장치의 성능 변화는 감지 증폭기 회로(113)의 출력을 래치할 수 없도록 할 수 있을 것이다. 부가적으로, 래치는 클럭 신호를 처리하기 위하여 추가적인 회로를 요구한다. 더욱이, 클럭 입력을 가지는 래치 회로를 가지는 것은 메모리 장치의 동작에 있어서 불필요한 지연을 유발 시킬 수 있을 것이다. 따라서, 향상된 메모리 장치가 요구된다.

## 발명의 상세한 설명

[0012]

아래에는 본 발명을 실시하는 모드(mode)의 상세한 설명이 기술된다. 이러한 상세한 설명은 본 발명에 대하여 예시적으로 기술된 것이며, 본 발명을 제한하는 것으로 간주되어서는 안된다.

[0013]

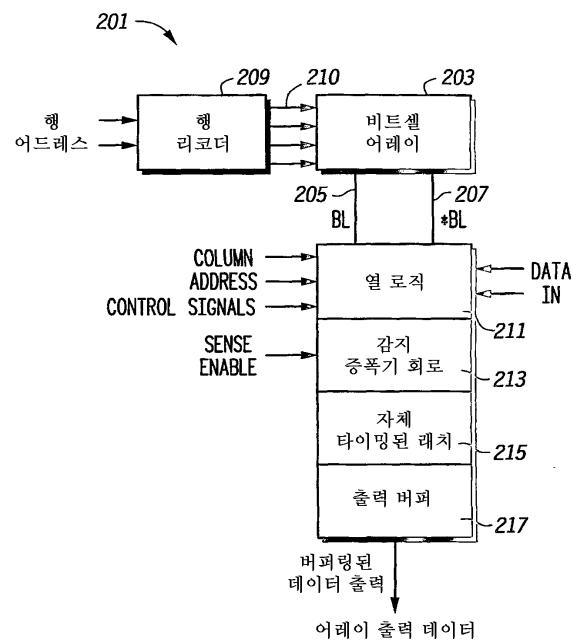

도 2는 본 발명에 따른 메모리 장치의 블럭도이다. 메모리 장치(201)는 데이터 비트를 각각 저장하는 다수의 메모리 셀들을 가지는 비트셀 어레이(203)를 포함한다. 일 실시예에서, 메모리 장치(201)는 SRAM 메모리이며, 비트셀 어레이(203)의 메모리 셀들은 6 트랜지스터 SRAM 셀들이다. 그러나, 다른 실시예들에서는 다른 타입들의 메모리 셀들이, 예컨대 다른 타입의 SRAM, DRAM, MRAM, 플래쉬 메모리, ROM, EPROM, EEPROM, 강자성 또는 다른 타입의 메모리 셀들과 같은 메모리 장치에서 이용될 수 있을 것이다. 몇몇 실시예에서, 비트셀 어레이(203) 내의 각각의 셀은 다수의 비트들을 저장한다. 비트셀 어레이(203)의 메모리 셀들은 각각 한 쌍의 차분 비트 라인들 BL(205) 및 \*BL(207)에 결합된다. 어레이(203) 내의 각각의 셀은 행 디코더(209)에 의해서 제어되는 워드 라인(예컨대, 210)에 결합된다. 행 디코더(209)는 입력부에서 행 어드레스를 수신하고, 디코드하여 행 어드레스에 의해서 지정되는 워드라인을 어셔트(assert)한다. 메모리 장치(201)는 열 로직(211) 또한 포함한다. 일 실시예에서, 열 로직은 사전충전 및 등화 회로, 기록 회로, 열 디코드 회로 및 격리 트랜지스터들(예컨대, 도 3에서 306 및 308)를 포함한다. 열 로직은 열 어드레스 라인들에 결합되고, 메모리 셀들에의 데이터 기록을 위하여 라인 단위로 데이터에 결합되는 입력들을 가진다. 몇몇 실시예에서, 열 로직(211)은 다수의 쌍의 비트 라인들에 결합될 수도 있으며, 열 로직(211)은 선택된 열을 감지 증폭기 회로(213)에 결합함에 있어 열 디코드 기능을 수행한다.

[0014]

감지 증폭기 회로(213)는 비트셀 어레이(203)의 메모리 셀의 메모리 소자에 저장되는 비트 값의 결정을 위한 판독 싸이클 동안에 로컬 데이터 라인들(예컨대, 도 3의 LDL(305) 및 \*LDL(307))에서의 차(difference)를 증폭한다. 메모리 소자에 저장된 비트 값은 메모리 소자의 로직 상태에 대응한다. 감지 증폭기 회로(213)는 로컬 데이터 라인들에서의 차를 증폭하도록 SENSE ENABLE 신호에 의해 인에이블된다.

[0015]

메모리 장치(201)는 자체 타이밍된 래치(215)를 포함한다. 자체 타이밍된 래치(215)는 감지 증폭기 회로(213)로부터 제공되는 데이터를 저장하는 데이터 저장 장치이다. 일 실시예에서, 자체 타이밍된 래치(215)는 단지 감지 증폭기 회로(213)로부터의 증폭된 차분 데이터 신호의 수신에 응답하여 데이터를 저장한다. 자체 타이밍된 래치(215)는 클럭 신호에 대한 입력을 가지지 않는다. 자체 타이밍된 래치(215)의 출력은 선택된 메모리 셀에

저장된 비트 값을 나타내는 버퍼링된 데이터 출력 신호를 제공하는 출력 버퍼에 제공된다.

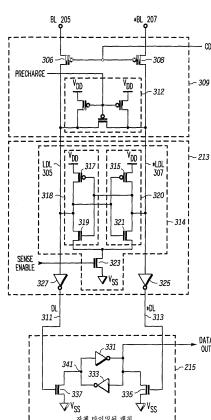

[0016] 도 3은 감지 증폭기 회로(213), 자체 타이밍된 래치(215) 및 열 로직(211)의 일부(309)(이하, "회로부(309)")의 일 실시예를 나타내는 개략도이다. 회로부(309)는 감지 증폭기 회로(213)로부터 비트 라인들 BL(205) 및 \*BL(207)을 격리하기 위한 2개의 격리 트랜지스터들(306, 308)을 포함한다. 신호 라인 앞의 "\*"는 신호 라인이 동일한 명칭을 가지지만 "\*" 표시가 없는 신호 라인의 논리적 상보(complement)임을 나타낸다. 격리 트랜지스터들(306, 308)은 격리 제어 신호(CD)에 의해서 제어된다. 일 실시예에서, 격리 제어 신호(CD)는 열 로직(211)의 열 디코더(도시되지 않음)에 의해서 제공되며, 열 로직(211)에 제공되는 열 어드레스로부터의 디코드된 신호이다. 회로부(309)는 로컬 데이터 라인들 LDL(305) 및 \*LDL(307)을 사전충전하기 위한 사전충전 및 등화 회로(312) 또한 포함한다. 비트 라인들로부터 격리 트랜지스터들(306, 308)의 반대측 상에 사전충전 및 등화 회로(312)를 가짐으로써, 기록 싸이클 동안 비트셀 어레이(203)가 기록되는 동안에 감지 증폭기 회로(213)의 감지 증폭기(314)가 사전충전될 수 있도록 한다.

[0017] 감지 증폭기(314)는 한 쌍의 교차결합된 인버터들(318, 320)을 포함한다. 인버터(318)는 트랜지스터들(317, 319)로부터 형성되며, 인버터(320)는 트랜지스터들(315, 321)로부터 형성된다. 트랜지스터들(319, 321)은 트랜지스터(323)의 전류 전극에 접속되는 전류 전극을 각각 포함한다. 트랜지스터(323)는 제어 전극에서 SENSE ENABLE 신호를 수신한다. 감지 증폭기(314)는 SENSE ENABLE 신호의 어써트에 응답하여 로컬 데이터 라인들 LDL(305) 및 \*LDL(307) 사이의 전압차를 증폭한다. 일 실시예에서, SENSE ENABLE 신호가 어써트되는 때에, 감지 증폭기(314)는 비트셀들로부터 비트 라인들 및 트랜지스터들(306, 308)을 통해 선택된 어레이(203)의 차분 데이터 신호에 기인하여 로컬 데이터 라인들(LDL(305) 및 \*LDL(307)) 중 어느 것이 보다 낮은 전압을 가지는지를 감지한다. 그 후에, 감지 증폭기(314)는 그러한 로컬 데이터 라인을 전력 공급 단자 VSS의 전압으로 구동하며, 다른 로컬 데이터 라인을 전력 공급 단자 VDD의 전압으로 구동하여 증폭된 차분 데이터 신호를 제공한다.

[0018] 도시된 실시예에서, 감지 증폭기 회로(213)는 자체 타이밍된 래치(215)로부터 감지 증폭기(314)를 격리하기 위한 버퍼들(예컨대, 인버터(327, 325)) 또한 포함한다. 다른 실시예들에서, 감지 증폭기 회로(213)는 버퍼들을 포함하지 않는다. 또 다른 실시예들에서, 비반전 버퍼들(non-inverting buffers)이 인버퍼들(327, 325) 대신에 이용될 수 있을 것이다.

[0019] 자체 타이밍된 래치(215)는 제어 전극들이 데이터 라인들 DL(311) 및 \*DL(313)에 각각 접속되는 트랜지스터들(337, 335)을 포함한다. 트랜지스터들(337, 335)은 교차결합된 인버터들(331, 333)에 결합되는 전류 단자를 각각 포함한다. 자체 타이밍된 래치(215)는 인버터(331)의 출력 단자 및 인버터(333)의 입력 단자에 접속되는 출력부에서 데이터를 출력한다. 자체 타이밍된 래치(215)는 출력(DATA OUT)에서 증폭된 차분 데이터 신호의 수신에 응답하여 차분 데이터 라인들 DL(311) 및 \*DL(313) 상에 수신된 증폭된 차분 데이터 신호의 값에 대응하는 값을 출력한다.

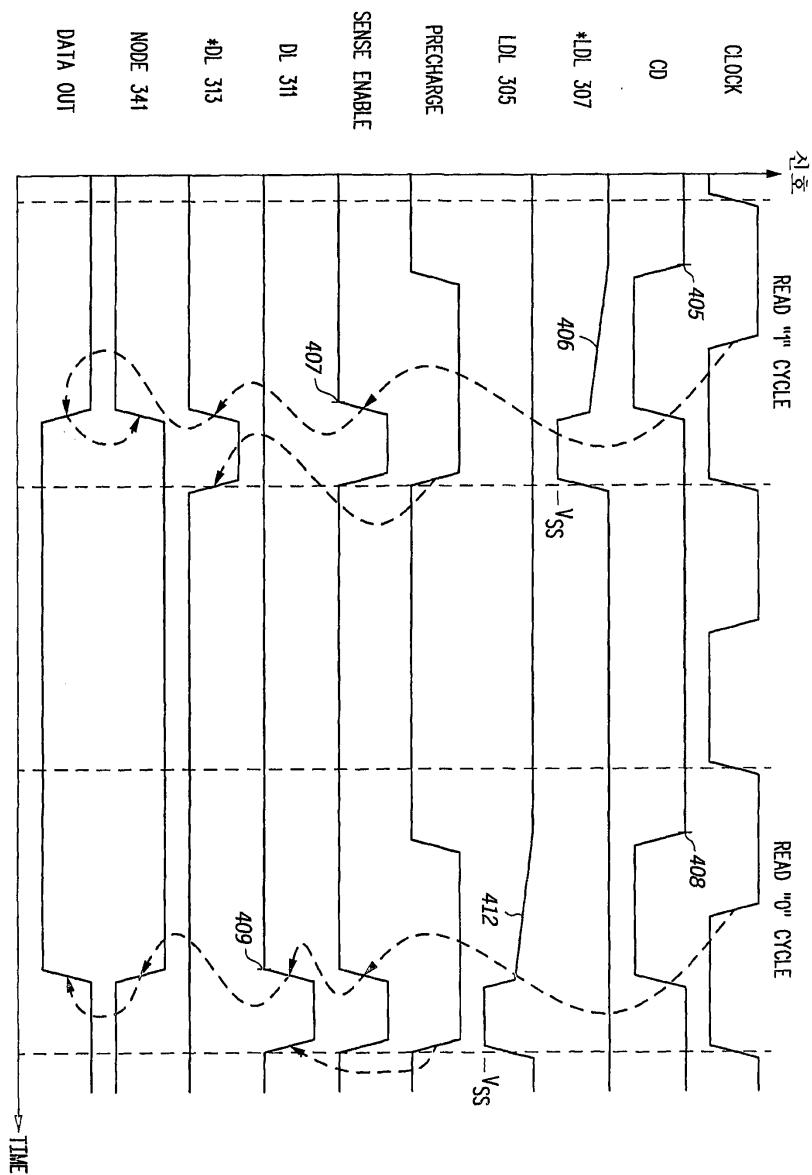

[0020] 도 4는 두 판독 싸이클 동안의 도 3의 회로에 대한 타이밍도의 일 실시예를 나타낸다. 타이밍도에서 READ "1" CYCLE로 레이블링된 부분은 값 "1"을 나타내는 저장된 로직 상태를 가지는 비트 어레이(203)의 선택된 메모리셀의 판독 싸이클 동안의 다양한 노드들, 신호들 및 데이터 라인들의 전압값들을 나타낸다. 타이밍도에서 READ "0" CYCLE로 레이블링된 부분은 값 "0"을 나타내는 저장된 로직 상태를 가지는 비트 어레이(203)의 선택된 메모리셀의 판독 싸이클 동안의 다양한 노드들, 신호들 및 데이터 라인들의 전압값들을 나타낸다. 저장된 로직 상태의 소정의 값으로의 지정은 몇몇 실시예에서 "1"을 지정하는 메모리셀의 로직 상태가 다른 실시예들에서 "0"을 지정할 수 있다는 점에서 임의적이다. CLOCK 신호는 메모리 장치 외부의 클럭 회로(예컨대, 도 5의 511)에 의해서 제공된다.

[0021] 판독 싸이클 동안, CD 신호는 (예컨대, 405에서)로우(low) 상태로 구동되어, 로컬 데이터 라인들 LDL(305) 및 \*LDL(307)을 비트 라인들 BL(205) 및 \*BL(207)에 각각 결합한다. 이러한 시간 동안, 비트셀 어레이(203) 내의 메모리셀은 비트셀과 관련된 워드 라인(예컨대, 210)을 활성화함으로써 판독을 위하여 선택된다. 또한, CD 신호가 로우 상태로 구동되는 때에, PRECHARGE 신호는 하이(high) 상태로 구동되어 사전충전 및 등화 회로(312)에 의해 로컬 데이터 라인들 LDL(305) 및 \*LDL(307)의 사전충전을 비활성화한다. 로컬 데이터 라인들 LDL(305) 및 \*LDL(307)을 비트 라인들 BL(205) 및 \*BL(207)에 각각 결합하고, 사전충전 및 등화 회로(312)를 비활성화하면, 선택된 메모리셀에 저장된 로직 상태에 따라 변하는 전압 차분을 LDL(305) 및 \*LDL(307) 양단에 발생시키도록 로컬 데이터 라인들 LDL(305) 및 \*LDL(307)이 선택된 비트셀에 결합될 수 있도록 한다. 도시된 실시예에서는 "1"을 지정하는 로직 상태가 선택된 메모리셀에 저장되기 때문에, \*LDL(307)의 전압이 CD 신호의 어써트에 의한 LDL(305)의 전압 레벨의 전압보다 낮은 전압 레벨로 풀(pull)된다(경사 라인(406) 참조).

- [0022] 405에서 CD 신호가 로우 상태로 구동된 때로부터 소정의 기간 이후에, 407에서 SENSE ENABLE 신호가 어쩌트된다(SENSE ENABLE 신호는 활성 하이 신호임). CD 신호와 PRECHARGE 신호뿐만 아니라 SENSE ENABLE 신호 또한 CLOCK 신호로부터 논리적으로 유도된다. SENSE ENABLE 신호를 어쩌트하면 감지 증폭기(314)를 트리거(trigger)하여 \*LDL(307)을 전력 공급 전압 단자 VSS의 전압 레벨로 구동한다. SENSE ENABLE 신호가 어쩌트되는 시간 근방에서, CD 신호가 하이 상태로 구동되어 로컬 데이터 라인들 LDL(305) 및 \*LDL(307)을 비트 라인들 BL(205) 및 \*BL(207)로부터 각각 격리시킨다. 비트 라인들(BL(205), \*BL(207))로부터 로컬 데이터 라인들(예컨대, LDL(305), \*LDL(307))을 격리시키면, 로컬 데이터 라인들이 비트 라인들에 결합되지 않는 경우에는 로컬 데이터 라인들 상의 용량이 감소된다는 점에서 로컬 데이터 라인들이 비트 라인들에 결합된 경우보다 빠른 속도로 감지 증폭기(314)가 로컬 데이터 라인들 상의 차분 데이터 신호를 증폭하는 것을 가능하게 한다.

- [0023] \*LDL(307)은 인버터(325)의 입력 단자에 접속되고, 데이터 라인 \*DL(313)은 인버터(325)의 출력 단자에 접속되며, \*LDL(307)은 VSS로 풀(pull)하면 \*DL(313)은 하이 상태로 구동한다. DL(311)은 인버터(327)를 통해서 LDL(305)에 결합되므로, DL(311)은 로우 전압 레벨로 남게된다. \*DL(313)이 하이 레벨로 되어 선택된 메모리 셀에 "1"이 저장된 것을 나타내는 것에 응답하여, DATA OUT 신호는 로우 상태로 천이한다. \*DL(313)이 하이 레벨로 되면, 트랜지스터(335)는 도전 상태가 되고, 인버터(331)에 과전력을 공급하고(over powering), 인버터(333)의 입력 단자를 로우 상태로 풀한다. 인버터(333)의 입력 단자가 로우 상태로 풀되는 것에 응답하여, 인버터(331)의 입력 단자(노드(341))는 하이 상태로 풀되고, DATA OUT 신호는 로우 상태로 풀된다.

- [0024] SENSE ENABLE 신호가 디어쩌트(deassert)되고, PRECHARGE 신호가 로우 상태로 됨으로써 사전충전 및 등화 회로(312)가 인에이블되는 때에, 로컬 데이터 라인 \*LDL(307)은 VDD로 다시 풀되고, \*DL(313)은 로우 상태로 풀하여 트랜지스터(335)를 턴 오프한다. 그러나, 자체 타이밍된 래치(215)의 래치 기능에 기인하여, DATA OUT 신호의 전압 레벨은 로우 전압 레벨에 래치된다. 따라서, 자체 타이밍된 래치(215)는 로컬 데이터 라인들 및 감지 증폭기(314)가 사전충전된 이후에 선택된 메모리 셀의 컨텐츠를 나타내는 값을 제공한다.

- [0025] DATA OUT 신호의 값은 후속하는 메모리 판독 싸이클 동안에 감지 증폭기에 의해서 반대 값이 감지될 때까지 소정의 값을 나타내는 동일한 레벨로 남는다. 예컨대, DATA OUT 신호의 전압은 후속하는 메모리 판독 싸이클 동안에 감지 증폭기(314)에 의해서 "0" 값이 감지될 때까지 로우 레벨로 남는다.

- [0026] READ "0" CYCLE 동안에, CD 신호는 (예컨대, 408에서) 로우 상태로 구동되어 로컬 데이터 라인들 LDL(305) 및 \*LDL(307)은 비트 라인들 BL(205) 및 \*BL(207)에 각각 결합된다. 이러한 시간 동안에, 비트셀 어레이(203) 내의 메모리 셀은 비트셀과 관련된 워드 라인(예컨대, 210)을 활성화함으로써 판독을 위하여 선택된다. CD 신호가 로우 상태로 구동된 때에도 PRECHARGE 신호는 하이 상태로 구동되어 사전충전 및 등화 회로(312)에 의한 로컬 데이터 라인들 LDL(305) 및 \*LDL(307)의 사전충전을 비활성화한다. "0"이 선택된 메모리 셀에 저장되며, LDL(305)의 전압은 \*LDL(307)의 전압 레벨의 전압보다 낮은 전압 레벨로 풀된다(도 4의 경사 라인(412) 참조).

- [0027] 408에서 CD 신호가 로우 상태로 구동된 때로부터 소정의 기간 이후에, SENSE ENABLE 신호가 409에서 어쩌트된다. SENSE ENABLE 신호를 어쩌트하면 감지 증폭기(314)를 트리거하여 LDL(305)을 전력 공급 전압 단자 VSS의 전압 레벨로 구동한다. SENSE ENABLE 신호가 어쩌트되는 시간 근방에서, CD 신호는 하이 상태로 구동되어 로컬 데이터 라인들 LDL(305) 및 \*LDL(307)은 비트 라인들 BL(205) 및 \*BL(207)로부터 각각 격리시킨다.

- [0028] LDL(305)은 인버터(327)의 입력 단자에 접속되고, 데이터 라인 DL(311)은 인버터(327)의 출력 단자에 접속되며, LDL(305)은 VSS로 풀하면, DL(311)은 하이 상태로 구동된다. \*DL(313)은 인버터(325)를 통해서 \*LDL(307)로 결합되며, \*DL(313)은 낮은 전압 레벨로 남는다. DL(311)이 하이 레벨로 되어 선택된 메모리 셀 내에 "0"이 저장되었음을 나타내는 것에 응답하여, DATA OUT 신호는 하이 전압 레벨로 천이한다. DL(311)이 하이 전압 레벨로 되면 트랜지스터(337)는 도전 상태가 되고, 인버터(333)에 과전력을 공급하고, 인버터(331)의 입력 단자(노드(341))를 로우 상태로 풀한다. 인버터(331)의 입력 단자가 로우 상태로 풀되는 것에 응답하여, 인버터(333)의 입력 단자 및 DATA OUT 신호는 하이 전압 레벨로 풀된다.

- [0029] SENSE ENABLE 신호가 디어쩌트되고, PRECHARGE 신호가 로우 상태로 됨으로써 사전충전 및 등화 회로(312)가 인에이블되는 때에, 로컬 데이터 라인 LDL(305)은 VDD로 다시 풀되고, DL(311)은 로우 상태로 풀되며, 트랜지스터(337)를 턴 오프한다. 그러나, 자체 타이밍된 래치(215)의 래치 기능에 기인하여, DATA OUT 신호의 전압 레벨은 하이 전압 레벨에서 래치된 상태로 남는다.

- [0030] 단지 감지 증폭기 회로의 출력에 응답하는 자체 타이밍된 래치를 제공하면, 증폭된 데이터 신호의 데이터를 캡

쳐하고 유지하기 위하여 감지 증폭기가 유지되어야 할 특정한 셋업 및 홀드 시간 요건을 가지는 클럭된 래치에 반대되는 증폭된 데이터 신호를 제공한 이후에 즉시 래치가 소정의 값을 래치할 수 있도록 한다. 또한, 클럭 입력을 가지지 않는 자체 타이밍된 래치를 제공하면 집적 회로의 클럭 발생 회로의 부하를 감소시킬 수 있을 것이다. 이는 메모리 장치 내에 래치 및 감지 증폭기 회로를 구현하기 위한 회로의 감소 또한 가능하게 할 수 있을 것이다.

[0031] 다른 실시예에서, 감지 증폭기 회로 및 래치는 다른 구성을 가질 수 있을 것이다. 예컨대, (반전 버퍼 기능을 수행하는)인버터들(325, 327)은 비반전 버퍼들로 대체될 수 있을 것이다. 이러한 실시예에서, 트랜지스터들(337, 335)은 P 채널 트랜지스터들로 대체될 수 있을 것이며, 그들의 전류 단자들은 전력 공급 단자 VSS 대신에 VDD에 접속될 수 있을 것이다. 또한, 다른 실시예에서 격리 트랜지스터들(306, 308)이 제외될 수 있을 것이다. 다른 실시예에서는, 예컨대 증폭된 차분 출력을 제공하는 다른 감지 증폭기들을 포함하는 다른 타입의 감지 증폭기 회로가 이용될 수 있을 것이다.

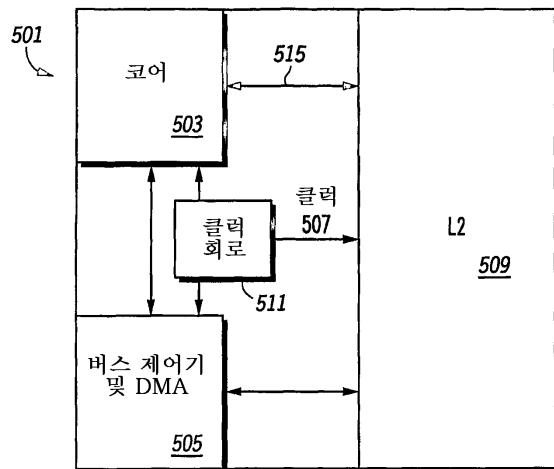

[0032] 도 5는 본 발명에 따른 집적 회로의 일 실시예의 블럭도이다. 집적 회로(501)는 코어 프로세서(core processor, 503), 클럭 회로(511), 버스 제어기 및 직접 메모리 액세스 회로(505) 및 L2 캐시(509)를 포함한다. 일 실시예에서, 버스 제어기 및 직접 메모리 액세스 회로(505)는 하나 이상의 버스 제어기들을 포함하며, 각각의 버스 제어기는 (예컨대, PCI 버스와 같은)상이한 시스템 버스에 결합된다. L2 캐시(509)는 다수의 열들을 포함하며 각각의 열들은 도 3의 감지 증폭기 회로(213), 자체 타이밍 래치(215) 및 회로부(309)와 유사한 감지 증폭기 회로, 자체 타이밍 래치 및 회로부를 포함한다. 클럭 회로(511)는 클럭 신호를 제공한다. 코어 프로세서(503)는 버스(515)를 통해서 행 및 열 어드레스를 L2 캐시(509)에 제공하며, 버스(515)를 통해서 L2 캐시(509)로부터 데이터를 수신한다. 집적 회로(501)는 다른 버스 제어기들 및 (예컨대, RAM 또는 플래시)메모리들과 같은 다른 장치들 또한 포함할 수 있을 것이다. 일 실시예에서, 집적 회로(501)는 상이한 프로토콜들의 버스들에 동작상 결합하는 통신 처리 회로이다.

[0033] 다른 실시예들에서, 본 명세서에서 기술된 감지 증폭기 회로, 자체 타이밍된 래치 및 열 로직은 다른 타입의 메모리 장치들에서 이용될 수 있을 것이다. 예컨대, 이들 회로들은 (예컨대, 내장형 RAM 또는 ROM과 같은)내장형 메모리 회로들 또는 독립형 메모리 장치들에서 이용될 수 있을 것이다.

[0034] 본 발명의 일 측면에서, 메모리 장치는 다수의 메모리 셀들을 포함한다. 다수의 메모리 셀들은 각각 비트 라인에 결합된다. 메모리 장치는 감지 인에이블 신호의 어썩트에 응답하여 증폭된 데이터 신호를 제공하기 위하여 다수의 메모리 셀들 중에서 비트 라인을 통해서 선택된 하나로부터 데이터 신호를 증폭하는 감지 증폭기 또한 포함한다. 메모리 장치는 비트 라인과 감지 증폭기 사이에 결합되는 격리 회로를 더 포함한다. 격리 회로는 감지 인에이블 신호의 어썩트와 거의 동일한 시간 근방에서 다수의 메모리 셀들 중에서 선택된 하나를 감지 증폭기로부터 분리한다. 메모리 장치는 단지 증폭된 데이터 신호에 응답하여 증폭된 데이터 신호에 대응하는 데이터를 저장하기 위하여 감지 증폭기에 결합되는 자체 타이밍된 저장 장치 또한 포함한다.

[0035] 본 발명의 다른 측면에서, 메모리 장치는 다수의 메모리 셀들을 포함한다. 다수의 메모리 셀들은 제1 비트 라인 및 제2 비트 라인에 각각 결합된다. 메모리 장치는 판독 싸이클의 적어도 일부 동안에 제1 비트 라인에 결합되는 제1 데이터 라인과, 판독 싸이클의 적어도 일부 동안에 제2 비트 라인에 결합되는 제2 데이터 라인을 포함한다. 메모리 장치는 한 쌍의 교차결합된 인버터를 가지는 감지 증폭기를 더 포함한다. 한 쌍의 교차결합된 인버터들은 감지 인에이블 신호의 어썩트에 응답하여 다수의 메모리 셀들 중에서 선택된 하나로부터의 데이터 신호를 증폭하기 위하여 제1 데이터 라인과 제2 데이터 라인에 결합된다. 메모리 장치는 제1 데이터 라인 및 출력에 결합되는 입력을 가지는 제1 버퍼 회로와, 제2 데이터 라인 및 출력에 결합되는 입력을 가지는 제2 버퍼 회로와, 제1 버퍼 회로의 출력에 결합되는 제1 입력 및 제2 버퍼 회로의 출력에 결합되는 제2 입력을 가지는 자체 타이밍된 저장 장치 또한 포함한다. 자체 타이밍된 저장 장치는 단지 제1 버퍼 회로의 출력과 제2 버퍼 회로의 출력 사이의 차분 전압에 응답한다.

[0036] 다른 측면에서, 본 발명은 메모리 장치의 메모리 셀을 판독하는 방법을 포함한다. 메모리 장치는 다수의 메모리 셀들을 포함한다. 다수의 메모리 셀들은 비트 라인 및 워드 라인에 각각 결합된다. 이러한 방법은 다수의 메모리 셀들 중 적어도 하나를 선택하는 단계와, 증폭된 데이터 신호를 생성하기 위하여 감지 인에이블 신호의 어썩트에 응답하여 감지 증폭기를 이용하여 비트 라인 상의 전압을 감지하고 증폭하는 단계를 포함한다. 증폭된 데이터 신호는 선택 단계에 의해서 선택된 다수의 메모리 셀들 중 적어도 하나에 저장된 로직 상태를 나타낸다. 상기 방법은 감지 인에이블 신호가 어썩트되는 것과 거의 동일한 시간 근방에서 감지 증폭기로부터 비트 라인을 분리하는 단계와, 자체 타이밍된 래치에서 증폭된 데이터 신호에 대응하는 데이터를 래치하는 단계 또한

포함한다. 자체 타이밍된 래치는 단지 증폭된 데이터 신호에 응답하여 데이터를 래치한다.

- [0037] 본 발명의 특정 실시예들이 도시되고 기술되었지만, 본 기술 분야의 당업자는 본 명세서에 기술된 바에 근거하여 본 발명 및 본 발명의 보다 넓은 측면들로부터 벗어나지 않고서 추가적인 변경 및 변화가 가능함을 이해할 수 있을 것이며, 첨부된 청구의 범위는 본 발명의 기술적 사상과 범주에 속하는 이러한 모든 변경들과 변화를 포함하는 것이다.

### 도면의 간단한 설명

- [0005] 첨부된 도면을 참조함으로써 본 발명이 보다 잘 이해될 것이며, 본 발명의 많은 목적들, 특징들 및 장점들이 본 기술 분야의 당업자에게 명백하게 될 것이다.

- [0006] 도 1은 종래 기술의 메모리 장치의 블럭도.

- [0007] 도 2는 본 발명에 따른 메모리 장치의 일 실시예의 블럭도.

- [0008] 도 3은 본 발명에 따른 감지 증폭기 회로 및 자체 타이밍된(self-timed) 래치를 포함하는, 도 2의 메모리 장치의 일부의 일 실시예의 회로도.

- [0009] 도 4는 본 발명에 따른 메모리 장치의 일 실시예의 타이밍도.

- [0010] 도 5는 본 발명에 따른 접속 회로의 일 실시예의 블럭도.

- [0011] 상이한 도면에서의 동일한 참조 부호의 사용은 달리 표시되지 않는 한 동일한 특징부를 나타낸다.

### 도면

#### 도면1

(종래 기술)

## 도면2

## 도면3

도면4

도면5