(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6622108号

(P6622108)

(45) 発行日 令和1年12月18日(2019.12.18)

(24) 登録日 令和1年11月29日(2019.11.29)

|                |           |

|----------------|-----------|

| (51) Int.Cl.   | F 1       |

| G 11 C 11/405  | (2006.01) |

| G 11 C 11/56   | (2006.01) |

| H 01 L 21/8242 | (2006.01) |

| H 01 L 27/108  | (2006.01) |

| H 01 L 29/786  | (2006.01) |

| G 11 C 11/405  | 11/405    |

| G 11 C 11/56   | 11/56     |

| H 01 L 27/108  | 27/108    |

| H 01 L 29/78   | 29/78     |

| H 01 L 29/786  | 29/78     |

|                | 250       |

|                | 321       |

|                | 613B      |

|                | 618B      |

請求項の数 3 (全 62 頁)

(21) 出願番号 特願2016-26288 (P2016-26288)

(22) 出願日 平成28年2月15日 (2016.2.15)

(65) 公開番号 特開2016-157506 (P2016-157506A)

(43) 公開日 平成28年9月1日 (2016.9.1)

審査請求日 平成31年2月5日 (2019.2.5)

(31) 優先権主張番号 特願2015-31747 (P2015-31747)

(32) 優先日 平成27年2月20日 (2015.2.20)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 加藤 清

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 松崎 隆徳

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 堀田 和義

最終頁に続く

(54) 【発明の名称】 記憶装置

(57) 【特許請求の範囲】

## 【請求項 1】

第1乃至第 $(n+1)$  ( $n$ は2以上の整数)のトランジスタと、

第1乃至第 $n$ の容量素子と、

第1乃至第 $n$ のノードと、

第1及び第2の配線と、を有し、

前記第 $i$ のノード ( $i$ は整数且つ $1 \leq i \leq n$ )は、前記第 $i$ の容量素子の第1の端子及び前記第 $i$ のトランジスタのゲートに電気的に接続され、

前記第1のトランジスタは、前記第1の配線と前記第2の配線との間の、導通又は非導通を制御する機能を有し、

前記第 $(i+1)$ のトランジスタは、前記第 $i$ のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有し、

前記第1乃至前記第 $n$ のノードは、それぞれ、 $J$ ビット ( $J$ は1以上の整数)のデータを保持する機能を有し、

前記第2乃至第 $(n+1)$ のトランジスタは、チャネル形成領域に酸化物半導体を含むことを特徴とする記憶装置。

## 【請求項 2】

メモリセルと、

第1乃至第 $n$ の記憶回路と、

第1及び第2の配線と、を有し、

10

20

前記メモリセルは、第1乃至第 $(n+1)$ ( $n$ は2以上の整数)のトランジスタと、第1乃至第 $n$ の容量素子と、第1乃至第 $n$ のノードと、を有し、

前記第 $i$ のノード( $i$ は整数且つ $1 \leq i \leq n$ )は、前記第 $i$ の容量素子の第1の端子及び前記第 $i$ のトランジスタのゲートに電気的に接続され、

前記第1のトランジスタは、前記第1の配線と前記第2の配線との間の、導通又は非導通を制御する機能を有し、

前記第 $(i+1)$ のトランジスタは、前記第 $i$ のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有し、

前記第1乃至前記第 $n$ のノードは、それぞれ、 $J$ ビット( $J$ は1以上の整数)のデータを保持する機能を有し、

前記第2乃至第 $(n+1)$ のトランジスタは、チャネル形成領域に酸化物半導体を含み、

前記第1乃至第 $n$ の記憶回路は、それぞれ、前記第1の配線に電気的に接続され、

前記第1乃至第 $n$ の記憶回路は、それぞれ、前記第2の配線に電気的に接続され、

前記第 $i$ の記憶回路は、前記第 $i$ のノードに保持されたデータを記憶する機能を有することを特徴とする記憶装置。

### 【請求項3】

請求項1または請求項2において、

前記第1のトランジスタ上に、前記第2乃至前記第 $(n+1)$ のトランジスタが設けられ、

前記第2乃至前記第 $(n+1)$ のトランジスタ上に、前記第1乃至前記第 $n$ の容量素子が設けられ、

前記第1のトランジスタはチャネル形成領域にシリコンを含むことを特徴とする記憶装置。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は記憶装置に関する。

#### 【0002】

本発明は、物、方法、又は製造方法に関する。又は、本発明は、プロセス、マシン、マニュファクチャ、又は組成物(コンポジション・オブ・マター)に関する。また、本発明の一態様は、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法又はそれらの製造方法に関する。特に、本発明の一態様は、酸化物半導体を含む半導体装置、表示装置、又は発光装置に関する。

#### 【0003】

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。表示装置、電気光学装置、半導体回路及び電子機器は、半導体装置を有する場合がある。

#### 【背景技術】

#### 【0004】

シリコン(Si)を半導体層に用いたトランジスタと、酸化物半導体(Oxide Semiconductor:OS)を半導体層に用いたトランジスタ(以下、OSトランジスタ)と、を組み合わせてデータの保持を可能にした記憶装置が注目されている(特許文献1、特許文献2参照)。

#### 【0005】

近年、扱われるデータ量の増大に伴って、大きな記憶容量を有する記憶装置が求められている。そうした中で、前述した特許文献1及び特許文献2に記載の記憶装置では、多値のデータを記憶し、該データを読み出す構成について開示している。

#### 【0006】

なお、本明細書中において、多値のデータとは、2ビット( $2^2 = 4$ 値)以上のデータを

10

20

30

40

50

表す。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2012-256400号公報

【特許文献2】特開2014-199707号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

例えば、特許文献1及び特許文献2に記載の記憶装置では、1つの保持ノードに、1つの多値データの書き込みを行っているが、多値データのビット数が増えると、それぞれのデータに対応する電位と電位の差が小さくなり、データを読み出す際の電位の判定が難しくなり、誤った値を読み出す可能性がある。また、保持ノードが1つのため、複数の多値データを同時に書き込むことができない。 10

【0009】

本発明の一態様は、複数の多値データの書き込みと読み出しが可能な記憶装置を提供することを課題の一とする。また、本発明の一態様は、新規な記憶装置を提供することを課題の一とする。また、本発明の一態様は、新規な半導体装置を提供することを課題の一とする。

【0010】

20

なお、複数の課題の記載は、互いの課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全て解決する必要はない。また、列記した以外の課題が、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、これらの課題も、本発明の一形態の課題となり得る。

【課題を解決するための手段】

【0011】

本発明の一態様は、第1乃至第5のトランジスタと、第1乃至第4の容量素子と、第1乃至第4のノードと、第1及び第2の配線と、を有する記憶装置である。前記第1のノードは、前記第1の容量素子の第1の端子及び前記第1のトランジスタのゲートに電気的に接続される。前記第2のノードは、前記第2の容量素子の第1の端子及び前記第2のトランジスタのゲートに電気的に接続される。前記第3のノードは、前記第3の容量素子の第1の端子及び前記第3のトランジスタのゲートに電気的に接続される。前記第4のノードは、前記第4の容量素子の第1の端子及び前記第4のトランジスタのゲートに電気的に接続される。前記第1のトランジスタは、前記第1の配線と前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第2のトランジスタは、前記第1のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第3のトランジスタは、前記第2のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第4のトランジスタは、前記第3のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第5のトランジスタは、前記第4のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第1のノードは、Jビット (Jは1以上の整数) のデータを保持する機能を有する。前記第2のノードは、Kビット (Kは1以上の整数) のデータを保持する機能を有する。前記第3のノードは、Lビット (Lは1以上の整数) のデータを保持する機能を有する。前記第4のノードは、Mビット (Mは1以上の整数) のデータを保持する機能を有する。前記第2乃至第5のトランジスタは、チャネル形成領域に酸化物半導体を含むことが好ましい。 30

【0012】

本発明の一態様は、メモリセルと、第1乃至第4の記憶回路と、第1及び第2の配線と、を有する記憶装置である。前記メモリセルは、第1乃至第5のトランジスタと、第1乃至第4の容量素子と、第1乃至第4のノードと、を有する。前記第1のノードは、前記第1の容量素子の第1の端子及び前記第1のトランジスタのゲートに電気的に接続される。前 40

50

記第2のノードは、前記第2の容量素子の第1の端子及び前記第2のトランジスタのゲートに電気的に接続される。前記第3のノードは、前記第3の容量素子の第1の端子及び前記第3のトランジスタのゲートに電気的に接続される。前記第4のノードは、前記第4の容量素子の第1の端子及び前記第4のトランジスタのゲートに電気的に接続される。前記第1のトランジスタは、前記第1の配線と前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第2のトランジスタは、前記第1のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第3のトランジスタは、前記第2のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第4のトランジスタは、前記第3のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第5のトランジスタは、前記第4のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第1のノードは、Jビット (Jは1以上の整数) の第1のデータを保持する機能を有する。前記第2のノードは、Kビット (Kは1以上の整数) の第2のデータを保持する機能を有する。前記第3のノードは、Lビット (Lは1以上の整数) の第3のデータを保持する機能を有する。前記第4のノードは、Mビット (Mは1以上の整数) の第4のデータを保持する機能を有する。前記第2乃至第5のトランジスタは、チャネル形成領域に酸化物半導体を含むことが好ましい。前記第1乃至第4の記憶回路は、前記第1の配線に電気的に接続される。前記第1乃至第4の記憶回路は、前記第2の配線に電気的に接続される。前記第1の記憶回路は、前記第1のデータを記憶する機能を有する。前記第2の記憶回路は、前記第2のデータを記憶する機能を有する。前記第3の記憶回路は、前記第3のデータを記憶する機能を有する。前記第4の記憶回路は、前記第4のデータを記憶する機能を有する。

10

#### 【0013】

上記態様において、前記第1乃至第4の記憶回路の何れか一は、第6及び第7のトランジスタと、第5の容量素子と、第5のノードと、を有することが好ましい。前記第5のノードは、前記第5の容量素子の第1の端子及び前記第6のトランジスタのゲートに電気的に接続される。前記第6のトランジスタは、前記第1の配線と前記第2の配線との導通又は非導通を制御する機能を有する。前記第7のトランジスタは、前記第5のノードと前記第2の配線との導通又は非導通を制御する機能を有する。前記第5のノードは、前記第1乃至第4のデータの何れか一を保持する機能を有する。前記第7のトランジスタはチャネル形成領域に酸化物半導体を有することが好ましい。

20

#### 【0014】

上記態様は、第1の層と、前記第1の層の上に設けられた第2の層と、前記第2の層の上に設けられた第3の層と、前記第3の層の上に設けられた第4の層と、を有することが好ましい。前記第1のトランジスタは、前記第1の層に設けられる。前記第2乃至第5のトランジスタは、前記第2又は第3の層に設けられる。前記第1乃至第4の容量素子は、前記第4の層に設けられる。前記第1のトランジスタはチャネル形成領域にシリコンを含むことが好ましい。

30

#### 【0015】

本発明の一態様は、第1乃至第4のトランジスタと、第1乃至第3の容量素子と、第1乃至第3のノードと、第1及び第2の配線と、を有する記憶装置である。前記第1のノードは、前記第1の容量素子の第1の端子及び前記第1のトランジスタのゲートに電気的に接続される。前記第2のノードは、前記第2の容量素子の第1の端子及び前記第2のトランジスタのゲートに電気的に接続される。前記第3のノードは、前記第3の容量素子の第1の端子及び前記第3のトランジスタのゲートに電気的に接続される。前記第1のトランジスタは、前記第1の配線と前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第2のトランジスタは、前記第1のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第3のトランジスタは、前記第2のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第4のトランジスタは、前記第3のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第1のノードは、Jビット (Jは1以上の整数) のデータを保持する機能を有す

40

50

る。前記第2のノードは、Kビット（Kは1以上の整数）のデータを保持する機能を有する。前記第3のノードは、Lビット（Lは1以上の整数）のデータを保持する機能を有する。前記第2乃至第4のトランジスタは、チャネル形成領域に酸化物半導体を含むことが好ましい。

#### 【0016】

本発明の一態様は、メモリセルと、第1乃至第3の記憶回路と、第1及び第2の配線と、を有する記憶装置である。前記メモリセルは、第1乃至第4のトランジスタと、第1乃至第3の容量素子と、第1乃至第3のノードと、を有する。前記第1のノードは、前記第1の容量素子の第1の端子及び前記第1のトランジスタのゲートに電気的に接続される。前記第2のノードは、前記第2の容量素子の第1の端子及び前記第2のトランジスタのゲートに電気的に接続される。前記第3のノードは、前記第3の容量素子の第1の端子及び前記第3のトランジスタのゲートに電気的に接続される。前記第1のトランジスタは、前記第1の配線と前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第2のトランジスタは、前記第1のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第3のトランジスタは、前記第2のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第4のトランジスタは、前記第3のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第1のノードは、Jビット（Jは1以上の整数）の第1のデータを保持する機能を有する。前記第2のノードは、Kビット（Kは1以上の整数）の第2のデータを保持する機能を有する。前記第3のノードは、Lビット（Lは1以上の整数）の第3のデータを保持する機能を有する。前記第2乃至第4のトランジスタは、チャネル形成領域に酸化物半導体を含むことが好ましい。前記第1乃至第3の記憶回路は、前記第1の配線に電気的に接続される。前記第1乃至第3の記憶回路は、前記第2の配線に電気的に接続される。前記第1の記憶回路は、前記第1のデータを記憶する機能を有する。前記第2の記憶回路は、前記第2のデータを記憶する機能を有する。前記第3の記憶回路は、前記第3のデータを記憶する機能を有する。

#### 【0017】

上記態様において、前記第1乃至第3の記憶回路の何れか一は、第5及び第6のトランジスタと、第4の容量素子と、第4のノードと、を有することが好ましい。前記第4のノードは、前記第4の容量素子の第1の端子及び前記第5のトランジスタのゲートに電気的に接続される。前記第5のトランジスタは、前記第1の配線と前記第2の配線との導通又は非導通を制御する機能を有する。前記第6のトランジスタは、前記第4のノードと前記第2の配線との導通又は非導通を制御する機能を有する。前記第4のノードは、前記第1乃至第3のデータの何れか一を保持する機能を有する。前記第5のトランジスタはチャネル形成領域に酸化物半導体を有することが好ましい。

#### 【0018】

上記態様は、第1の層と、前記第1の層の上に設けられた第2の層と、前記第2の層の上に設けられた第3の層と、前記第3の層の上に設けられた第4の層と、を有することが好ましい。前記第1のトランジスタは、前記第1の層に設けられる。前記第2乃至第4のトランジスタは、前記第2又は第3の層に設けられる。前記第1乃至第3の容量素子は、前記第4の層に設けられる。前記第1のトランジスタはチャネル形成領域にシリコンを含むことが好ましい。

#### 【0019】

本発明の一態様は、第1乃至第3のトランジスタと、第1及び第2の容量素子と、第1及び第2のノードと、第1及び第2の配線と、を有する記憶装置である。前記第1のノードは、前記第1の容量素子の第1の端子及び前記第1のトランジスタのゲートに電気的に接続される。前記第2のノードは、前記第2の容量素子の第1の端子及び前記第2のトランジスタのゲートに電気的に接続される。前記第1のトランジスタは、前記第1の配線と前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第2のトランジスタは、前記第1のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有

10

20

30

40

50

する。前記第3のトランジスタは、前記第2のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第1のノードは、Jビット（Jは1以上の整数）のデータを保持する機能を有する。前記第2のノードは、Kビット（Kは1以上の整数）のデータを保持する機能を有する。前記第2及び第3のトランジスタは、チャネル形成領域に酸化物半導体を含むことが好ましい。

#### 【0020】

本発明の一態様は、メモリセルと、第1及び第2の記憶回路と、第1及び第2の配線と、を有する記憶装置である。前記メモリセルは、第1乃至第3のトランジスタと、第1及び第2の容量素子と、第1及び第2のノードと、を有する。前記第1のノードは、前記第1の容量素子の第1の端子及び前記第1のトランジスタのゲートに電気的に接続される。前記第2のノードは、前記第2の容量素子の第1の端子及び前記第2のトランジスタのゲートに電気的に接続される。前記第1のトランジスタは、前記第1の配線と前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第2のトランジスタは、前記第1のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第3のトランジスタは、前記第2のノードと前記第2の配線との間の、導通又は非導通を制御する機能を有する。前記第1のノードは、Jビット（Jは1以上の整数）の第1のデータを保持する機能を有する。前記第2のノードは、Kビット（Kは1以上の整数）の第2のデータを保持する機能を有する。前記第2及び第3のトランジスタは、チャネル形成領域に酸化物半導体を含むことが好ましい。前記第1及び第2の記憶回路は、前記第1の配線に電気的に接続される。前記第1及び第2の記憶回路は、前記第2の配線に電気的に接続される。前記第1の記憶回路は、前記第1のデータを記憶する機能を有する。前記第2の記憶回路は、前記第2のデータを記憶する機能を有する。

10

20

30

#### 【0021】

上記態様において、前記第1及び第2の記憶回路の何れか一は、第4及び第5のトランジスタと、第3の容量素子と、第3のノードと、を有することが好ましい。前記第3のノードは、前記第3の容量素子の第1の端子及び前記第4のトランジスタのゲートに電気的に接続される。前記第4のトランジスタは、前記第1の配線と前記第2の配線との導通又は非導通を制御する機能を有する。前記第5のトランジスタは、前記第3のノードと前記第2の配線との導通又は非導通を制御する機能を有する。前記第3のノードは、前記第1及び第2のデータの何れか一を保持する機能を有する。前記第5のトランジスタはチャネル形成領域に酸化物半導体を有することが好ましい。

30

#### 【0022】

上記態様は、第1の層と、前記第1の層の上に設けられた第2の層と、前記第2の層の上に設けられた第3の層と、前記第3の層の上に設けられた第4の層と、を有することが好ましい。前記第1のトランジスタは、前記第1の層に設けられる。前記第2及び第3のトランジスタの一方は、前記第2の層に設けられる。前記第2及び第3のトランジスタの他方は、前記第3の層に設けられる。前記第1及び第2の容量素子は、前記第4の層に設けられる。前記第1のトランジスタはチャネル形成領域にシリコンを含むことが好ましい。

#### 【0023】

本発明の一態様は、上記態様に記載の記憶装置と、マイクロフォン、スピーカ、表示部、および操作キーのうちの少なくとも1つを有する電子機器である。

40

#### 【発明の効果】

#### 【0024】

本発明の一態様により、複数の多値データの書き込みと読み出しが可能な記憶装置を提供することが可能になる。また、本発明の一態様により、新規な記憶装置を提供することが可能になる。また、本発明の一態様により、新規な半導体装置を提供することが可能になる。

#### 【0025】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、

50

図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

【図面の簡単な説明】

【0026】

- 【図1】メモリセルの構成例を示す回路図。

- 【図2】メモリセルの構成例を示す回路図。

- 【図3】メモリセルの構成例を示す回路図。

- 【図4】メモリセルの動作例を示すタイミングチャート。

- 【図5】メモリセルの動作例を示すタイミングチャート。

- 【図6】メモリセルの構成例を示す回路図。

10

- 【図7】メモリセルの構成例を示す回路図。

- 【図8】メモリセルの構成例を示す回路図。

- 【図9】メモリセルの構成例を示す回路図。

- 【図10】メモリセルの構成例を示す回路図。

- 【図11】メモリセルの構成例を示す回路図。

- 【図12】記憶装置の構成例を示す回路図。

- 【図13】記憶装置の構成例を示す回路図。

- 【図14】記憶装置の構成例を示す回路図。

- 【図15】記憶装置の構成例を示す回路図。

- 【図16】メモリセルの構成例を示す回路図。

20

- 【図17】メモリセルアレイの構成例を示す回路図。

- 【図18】メモリセルアレイの動作例を示すタイミングチャート。

- 【図19】記憶装置の構成例を示す回路ブロック図。

- 【図20】トランジスタの構成例を示す上面図及び断面図。

- 【図21】トランジスタの構成例を示す断面図及びエネルギーバンド図。

- 【図22】酸素が拡散する経路を示す断面図。

- 【図23】トランジスタの構成例を示す上面図及び断面図。

- 【図24】トランジスタの構成例を示す上面図及び断面図。

- 【図25】トランジスタの構成例を示す上面図及び断面図。

- 【図26】トランジスタの構成例を示す上面図及び断面図。

- 【図27】トランジスタの構成例を示す上面図及び断面図。

- 【図28】メモリセルの構成例を示す断面図。

- 【図29】メモリセルの構成例を示す断面図。

30

- 【図30】トランジスタの構成例を示す断面図。

- 【図31】トランジスタの構成例を示す断面図。

- 【図32】CPUの構成例を示すブロック図。

- 【図33】電子器機器の一例を示す斜視図。

- 【図34】RFタグの使用例を示す斜視図。

- 【図35】C A A C - O S の断面におけるCs補正高分解能TEM像、およびC A A C - O S の断面模式図。

40

- 【図36】C A A C - O S の平面におけるCs補正高分解能TEM像。

- 【図37】C A A C - O S および単結晶酸化物半導体のXRDによる構造解析を説明する図。

- 【図38】C A A C - O S の電子回折パターンを示す図。

- 【図39】In - Ga - Zn酸化物の電子照射による結晶部の変化を示す図。

【発明を実施するための形態】

【0027】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、

50

以下の実施の形態の記載内容に限定して解釈されるものではない。

【0028】

また、本明細書は、以下の実施の形態を適宜組み合わせることが可能である。また、1つの実施の形態の中に、複数の構成例が示される場合は、互いに構成例を適宜組み合わせることが可能である。

【0029】

また、図面において、大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状または値などに限定されない。

【0030】

本明細書において、特に断りがない場合、オン電流とは、トランジスタがオン状態にあるときのドレイン電流をいう。オン状態とは、特に断りがない場合、nチャネル型トランジスタでは、ゲートとソースの間の電圧差( $V_{g s}$ )がしきい値電圧( $V_{t h}$ )以上の状態、pチャネル型トランジスタでは、 $V_{g s}$ が $V_{t h}$ 以下の状態をいう。例えば、nチャネル型のトランジスタのオン電流とは、 $V_{g s}$ が $V_{t h}$ 以上のときのドレイン電流を言う場合がある。また、トランジスタのオン電流は、ドレインとソースの間の電圧( $V_{d s}$ )に依存する場合がある。

10

【0031】

本明細書において、特に断りがない場合、オフ電流とは、トランジスタがオフ状態にあるときのドレイン電流をいう。オフ状態とは、特に断りがない場合、nチャネル型トランジスタでは、 $V_{g s}$ が $V_{t h}$ よりも低い状態、pチャネル型トランジスタでは、 $V_{g s}$ が $V_{t h}$ よりも高い状態をいう。例えば、nチャネル型のトランジスタのオフ電流とは、 $V_{g s}$ が $V_{t h}$ よりも低いときのドレイン電流を言う場合がある。トランジスタのオフ電流は、 $V_{g s}$ に依存する場合がある。従って、トランジスタのオフ電流が $10^{-21} A$ 未満である、とは、トランジスタのオフ電流が $10^{-21} A$ 未満となる $V_{g s}$ の値が存在することを言う場合がある。

20

【0032】

また、トランジスタのオフ電流は、 $V_{d s}$ に依存する場合がある。本明細書において、オフ電流は、特に記載がない場合、 $V_{d s}$ の絶対値が $0.1 V$ 、 $0.8 V$ 、 $1 V$ 、 $1.2 V$ 、 $1.8 V$ 、 $2.5 V$ 、 $3 V$ 、 $3.3 V$ 、 $10 V$ 、 $12 V$ 、 $16 V$ 、または $20 V$ におけるオフ電流を表す場合がある。または、当該トランジスタが含まれる半導体装置等において使用される $V_{d s}$ におけるオフ電流、を表す場合がある。

30

【0033】

なお、本明細書中において、高電源電圧をHレベル(又は $V_{D D}$ )、低電源電圧をLレベル(又は $GND$ )と呼ぶ場合がある。

【0034】

(実施の形態1)

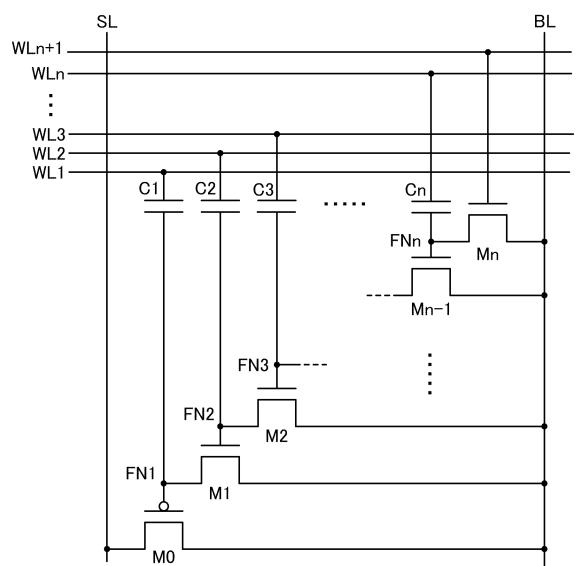

本実施の形態では、本発明の一態様であるメモリセルの構成例について、図1乃至図11を用いて説明を行う。

【0035】

40

メモリセルの構成例1

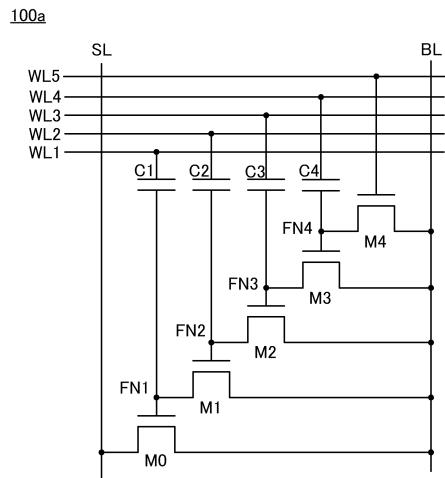

図1は、複数の2値又は多値データの書き込みと読み出しが可能なメモリセル100aの構成例を示す回路図である。

【0036】

メモリセル100aは、トランジスタM0、トランジスタM1、トランジスタM2、トランジスタM3と、トランジスタM4と、容量素子C1と、容量素子C2と、容量素子C3と、容量素子C4と、配線WL1と、配線WL2と、配線WL3と、配線WL4と、配線WL5と、ノードFN1と、ノードFN2と、ノードFN3と、ノードFN4と、配線SLと、配線BLと、を有する。

【0037】

50

ノードF N 1は、容量素子C 1の第1の端子及びトランジスタM 0のゲートに電気的に接続される。ノードF N 2は、容量素子C 2の第1の端子及びトランジスタM 1のゲートに電気的に接続される。ノードF N 3は、容量素子C 3の第1の端子及びトランジスタM 2のゲートに電気的に接続される。ノードF N 4は、容量素子C 4の第1の端子及びトランジスタM 3のゲートに電気的に接続される。

【0038】

容量素子C 1の第2の端子は、配線W L 1に電気的に接続される。容量素子C 2の第2の端子は、配線W L 2に電気的に接続される。容量素子C 3の第2の端子は、配線W L 3に電気的に接続される。容量素子C 4の第2の端子は、配線W L 4に電気的に接続される。トランジスタM 4のゲートは、配線W L 5に電気的に接続される。

10

【0039】

トランジスタM 0は、配線S Lと配線B Lとの間の導通又は非導通を制御する機能を有する。トランジスタM 1は、ノードF N 1と配線B Lとの間の導通又は非導通を制御する機能を有する。トランジスタM 2は、ノードF N 2と配線B Lとの間の導通又は非導通を制御する機能を有する。トランジスタM 3は、ノードF N 3と配線B Lとの間の導通又は非導通を制御する機能を有する。トランジスタM 4は、ノードF N 4と配線B Lとの間の導通又は非導通を制御する機能を有する。

【0040】

ノードF N 1は、Jビット( $2^J$ 値、Jは1以上の整数)の第1のデータを保持する機能を有する。第1のデータは2値あるいは多値のデータを含む。第1のデータは、配線B LからトランジスタM 1を介してノードF N 1に書き込まれる。

20

【0041】

ノードF N 2は、Kビット( $2^K$ 値、Kは1以上の整数)の第2のデータを保持する機能を有する。第2のデータは2値あるいは多値のデータを含む。第2のデータは、配線B LからトランジスタM 2を介してノードF N 2に書き込まれる。

【0042】

ノードF N 3は、Lビット( $2^L$ 値、Lは1以上の整数)の第3のデータを保持する機能を有する。第3のデータは2値あるいは多値のデータを含む。第3のデータは、配線B LからトランジスタM 3を介してノードF N 3に書き込まれる。

【0043】

ノードF N 4は、Mビット( $2^M$ 値、Mは1以上の整数)の第4のデータを保持する機能を有する。第4のデータは2値あるいは多値のデータを含む。第4のデータは、配線B LからトランジスタM 4を介してノードF N 4に書き込まれる。

30

【0044】

メモリセル100aは、ノードF N 1乃至F N 4が保持するデータを合計すると( $J + K + L + M$ )ビット( $2^{J+K+L+M}$ 値)のデータ保持が可能である。例えば、ノードF N 1乃至F N 4がそれぞれ4ビットのデータを保持すると仮定すると、メモリセル100aは、合計で16ビットのデータ保持が可能である。

【0045】

メモリセル100aは、ノードF N 1乃至F N 4を有することで、複数の2値又は多値データの保持が可能になる。

40

【0046】

トランジスタM 1乃至M 4は、導通状態と非導通状態とを切り換えることで、データの書き込みを制御するスイッチとしての機能を有する。また、非導通状態を保持することで、それぞれのノードに書き込んだ電荷を保持する機能を有する。

【0047】

トランジスタM 1乃至M 4には、非導通状態においてソースとドレインとの間を流れる電流(オフ電流)が低いトランジスタを用いることが好適である。ここでは、オフ電流が低いとは、室温において、ソースとドレインとの間の電圧を3Vとし、チャネル幅1μmあたりの規格化されたオフ電流が $10 \times 10^{-21} A$ 以下であることをいう。このようにオ

50

フ電流が低いトランジスタとしては、チャネル形成領域に酸化物半導体を有するOSトランジスタや、チャネル形成領域にワイドバンドギャップ半導体（バンドギャップが2.2eV以上の半導体）を用いたトランジスタが挙げられる。特に、OSトランジスタを用いることが好適である。

【0048】

配線SLは、高電源電位又は低電源電位が与えられる。

【0049】

トランジスタM0は、ノードFN1（トランジスタM0のゲート）に与えられた電位に応じてチャネル抵抗が変化する。配線SLと配線BLとの間に電位差を与えることによって、ノードFN1に与えられた電位を間接的に読み出すことが可能になる。

10

【0050】

トランジスタM0は、チャネル形成領域にシリコンを有するトランジスタ（以下、Siトランジスタ）を用いてもよい。Siトランジスタは、移動度が高くオン電流が大きい。トランジスタM0に、Siトランジスタを用いることで、メモリセル100aは、データの読み出し速度を向上させることが可能になる。

【0051】

トランジスタM0は、トランジスタM1乃至M4と同様に、チャネル形成領域に酸化物半導体を有するOSトランジスタを用いてもよい。OSトランジスタは、オフ電流が低いので、メモリセル100aの消費電力を低減することが可能になる。また、OSトランジスタは、短チャネル効果の影響を受けにくいため、トランジスタを微細化したときでも、ゲート絶縁膜を厚く形成することが可能である。そのため、トランジスタM0のゲート絶縁膜を厚く形成することが可能になり、トランジスタM0のゲートリーコを低く抑え、ノードFN1に書き込まれた電荷を長期間保持することが可能になる。

20

【0052】

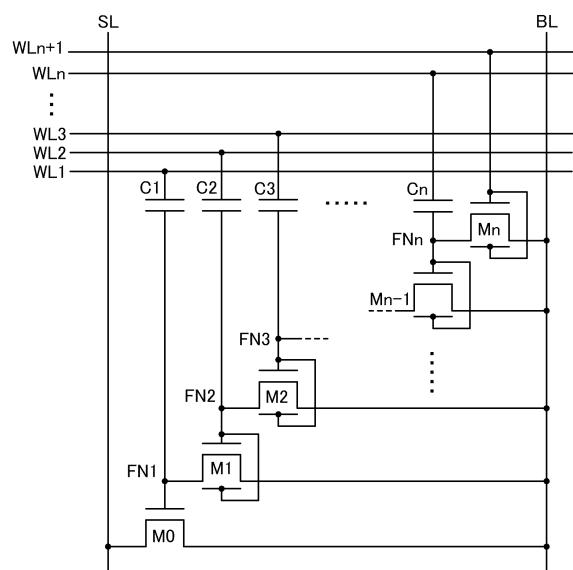

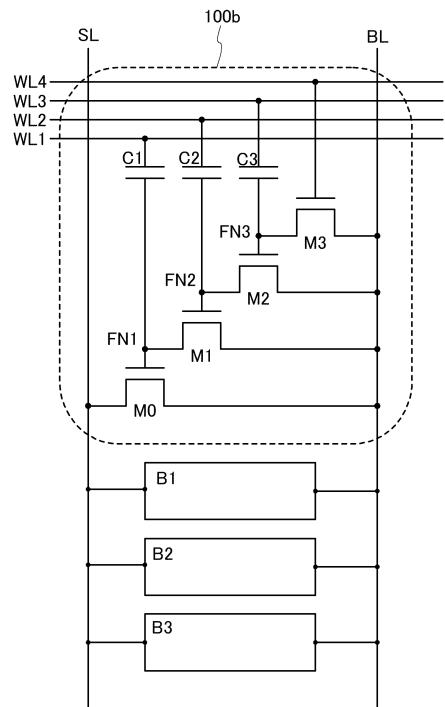

メモリセルの構成例2

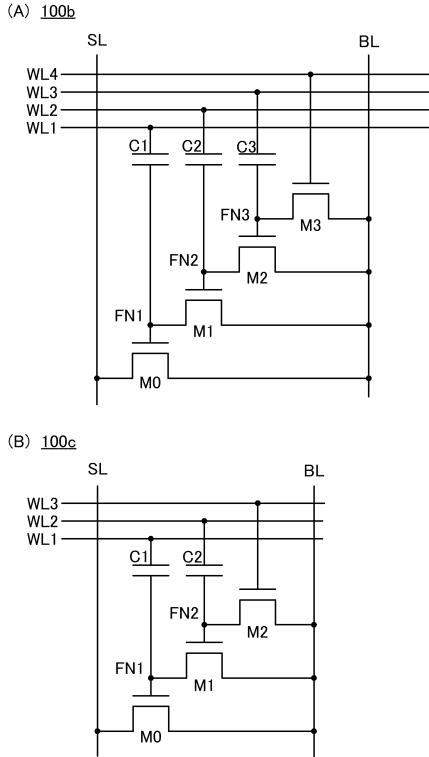

図2(A)に示すメモリセル100bは、図1のメモリセル100aにおいて、ノードFN4、トランジスタM4、容量素子C4及び配線WL5を省き、トランジスタM3のゲートを配線WL4に電気的に接続した場合の構成例である。

【0053】

30

それぞれの構成要素の詳細に関しては、メモリセル100aの記載を参照すればよい。

【0054】

メモリセル100bは、ノードFN1乃至FN3の3つのノードを有する。すなわち、メモリセル100aにおける第1乃至第3のデータを保持する機能を有する。

【0055】

メモリセル100bにおいて、トランジスタM1乃至M3には、オフ電流が低いトランジスタを用いることが好適である。オフ電流が低いトランジスタとしては、チャネル形成領域に酸化物半導体を有するOSトランジスタや、チャネル形成領域にワイドバンドギャップ半導体を用いたトランジスタが挙げられる。特に、OSトランジスタを用いることが好適である。

40

【0056】

また、トランジスタM0は、Siトランジスタを用いてもよい。トランジスタM0にSiトランジスタを用いることで、メモリセル100bは、データの読み出し速度を向上させることが可能になる。また、トランジスタM0はOSトランジスタを用いてもよい。トランジスタM0にOSトランジスタを用いることで、メモリセル100bは消費電力を低減することが可能になる。また、トランジスタM0のゲート絶縁膜を厚く形成することが可能になり、ノードFN1に書き込まれた電荷を長期間保持することが可能になる。

【0057】

メモリセルの構成例3

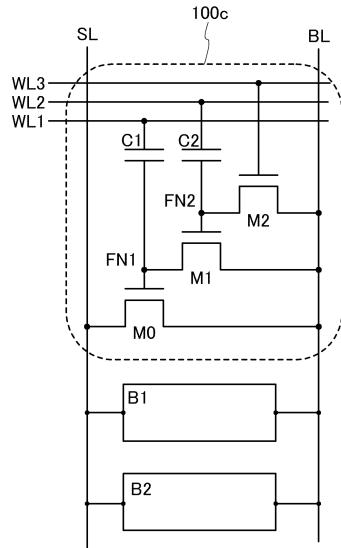

図2(B)に示すメモリセル100cは、図2(A)のメモリセル100bにおいて、ノードFN1に書き込まれた電荷を長期間保持することが可能になる。

50

ード F N 3、トランジスタ M 3、容量素子 C 3 及び配線 W L 4 を省き、トランジスタ M 2 のゲートを配線 W L 3 に電気的に接続した場合の構成例である。

【 0 0 5 8 】

それぞれの構成要素の詳細に関しては、メモリセル 1 0 0 a の記載を参照すればよい。

【 0 0 5 9 】

メモリセル 1 0 0 c は、ノード F N 1、F N 2 の 2 つのノードを有する。すなわち、メモリセル 1 0 0 a における第 1 及び第 2 のデータを保持する機能を有する。

【 0 0 6 0 】

メモリセル 1 0 0 c において、トランジスタ M 1、M 2 には、オフ電流が低いトランジスタを用いることが好適である。オフ電流が低いトランジスタとしては、チャネル形成領域に酸化物半導体を有する O S トランジスタや、チャネル形成領域にワイドバンドギャップ半導体を用いたトランジスタが挙げられる。特に、O S トランジスタを用いることが好適である。

10

【 0 0 6 1 】

また、トランジスタ M 0 は、S i トランジスタを用いてもよい。トランジスタ M 0 に S i トランジスタを用いることで、メモリセル 1 0 0 c は、データの読み出し速度を向上させることが可能になる。また、トランジスタ M 0 は O S トランジスタを用いてもよい。トランジスタ M 0 に O S トランジスタを用いることで、メモリセル 1 0 0 c は消費電力を低減することが可能になる。また、トランジスタ M 0 のゲート絶縁膜を厚く形成することが可能になり、ノード F N 1 に書き込まれた電荷を長期間保持することが可能になる。

20

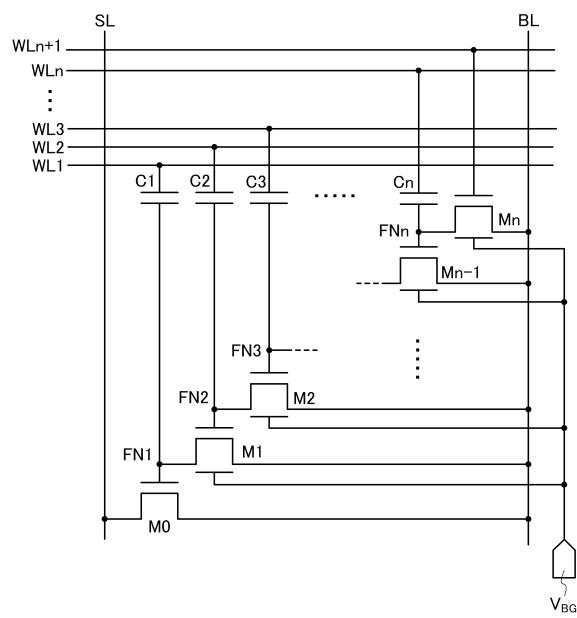

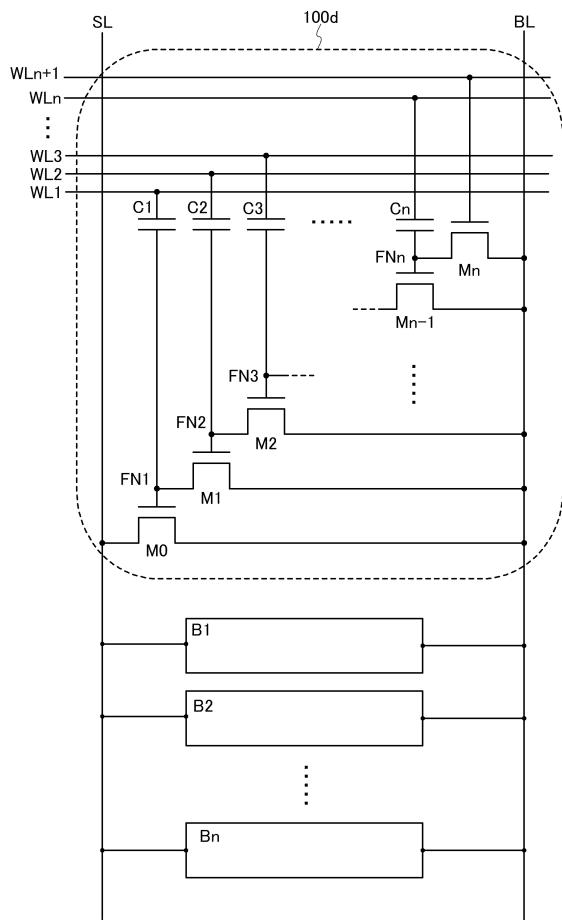

【 0 0 6 2 】

メモリセルの構成例 4

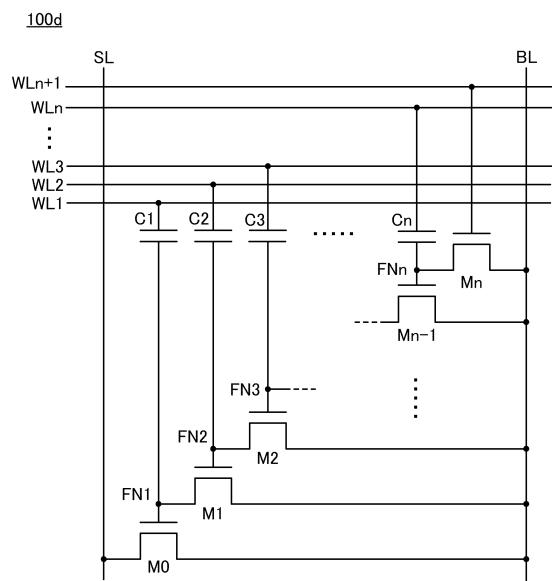

図 3 に示すメモリセル 1 0 0 d は、上述のメモリセル 1 0 0 a 乃至 1 0 0 c において、n (n は 2 以上の整数) の数の保持ノードを有する場合に一般化した場合の構成例である。メモリセル 1 0 0 d は、図 1 のメモリセル 1 0 0 a、図 2 (A) のメモリセル 1 0 0 b 及び図 2 (B) のメモリセル 1 0 0 c を含む。図 3 において、n = 4 の場合は、メモリセル 1 0 0 a に該当し、n = 3 の場合はメモリセル 1 0 0 b に該当し、n = 2 の場合は、メモリセル 1 0 0 c に該当する。

【 0 0 6 3 】

それぞれの構成要素の詳細に関しては、メモリセル 1 0 0 a の記載を参照すればよい。

30

【 0 0 6 4 】

メモリセル 1 0 0 d は、n の数のノード (ノード F N 1 乃至 F N n) を有する。すなわち、2 値又は多値のデータで構成される第 1 乃至第 n のデータを保持する機能を有する。

【 0 0 6 5 】

メモリセル 1 0 0 d において、トランジスタ M 1 乃至 M n には、オフ電流が低いトランジスタを用いることが好適である。オフ電流が低いトランジスタとしては、チャネル形成領域に酸化物半導体を有する O S トランジスタや、チャネル形成領域にワイドバンドギャップ半導体を用いたトランジスタが挙げられる。特に、O S トランジスタを用いることが好適である。

40

【 0 0 6 6 】

また、トランジスタ M 0 は、S i トランジスタを用いてもよい。トランジスタ M 0 に S i トランジスタを用いることで、メモリセル 1 0 0 d は、データの読み出し速度を向上させることが可能になる。また、トランジスタ M 0 は O S トランジスタを用いてもよい。トランジスタ M 0 に O S トランジスタを用いることで、メモリセル 1 0 0 d は消費電力を低減することが可能になる。また、トランジスタ M 0 のゲート絶縁膜を厚く形成することが可能になり、ノード F N 1 に書き込まれた電荷を長期間保持することが可能になる。

【 0 0 6 7 】

メモリセルの動作例

次に、図 2 (A) のメモリセル 1 0 0 b の動作の一例について、図 4 及び図 5 を用いて説明を行う。なお、メモリセル 1 0 0 a、1 0 0 c、1 0 0 d の動作についても、以下の説

50

明を適用することで、理解が可能である。

【0068】

なお、以下の説明ではトランジスタM0乃至M3は、nチャネル型トランジスタとして説明を行う。

【0069】

書き込み動作

まず、メモリセル100bの書き込み動作の一例について、図4を用いて説明を行う。

【0070】

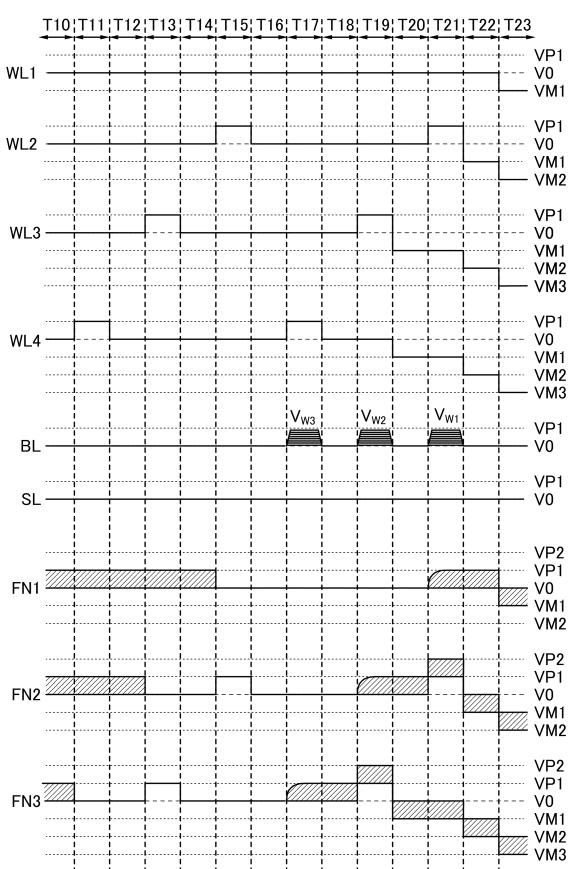

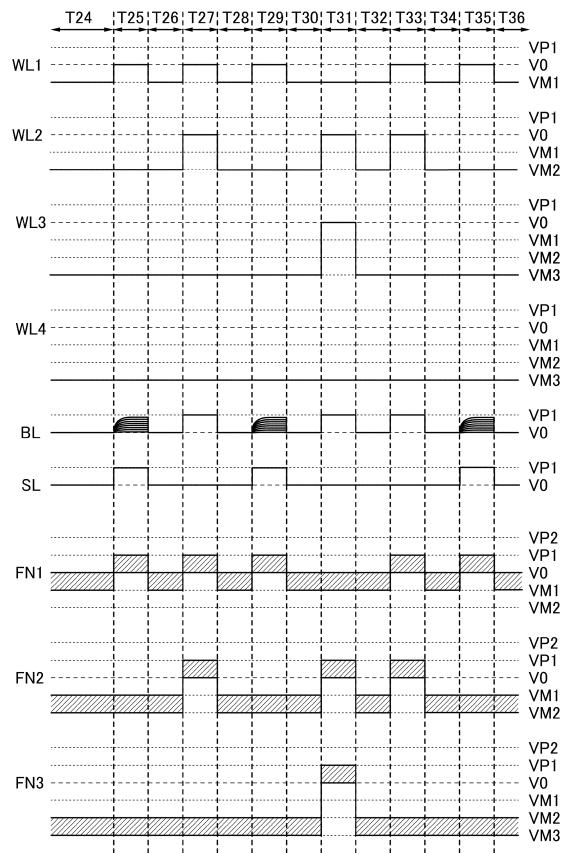

図4は、メモリセル100bの書き込み動作のタイミングチャートを示している。上から順に、配線WL1、配線WL2、配線WL3、配線WL4、配線BL、配線SL、ノードFN1、ノードFN2、ノードFN3の電位をそれぞれ表している。また、図中には、動作のタイミングを示すために、タイミングチャートを、期間T10乃至T23に分割している。

【0071】

図中のVP1、VP2、V0、VM1、VM2、VM3は、各配線及びノードの電位を表す。電位V0はGNDとする。トランジスタM0乃至M3のしきい値電圧を全てVthとした場合、電位VP1はVthと入力データの最大値(Vmax)の和より大きい値とする。電位VP1、VP2は、正電位であり、電位VP2はVP1の2倍とする。電位VM1、VM2、VM3は、負電位であり、電位VM1の絶対値は、電位VP1と等しい。電位VM2は電位VM1の2倍、電位VM3は電位VM1の3倍とする。

【0072】

なお、図4及び図5において、ノードFN1乃至FN3は、2値又は多値のデータが与えられ、ハッチングで示された範囲の電位をとり得る。

【0073】

まず、期間T10は準備期間であり、配線WL1乃至WL4、BL、SLは全てV0になっている。ノードFN1乃至FN3は、何かしらの電位を保持している。

【0074】

次に、期間T11乃至T16は、ノードFN1乃至FN3へのリセットを行う期間である。ノードFN3、ノードFN2、ノードFN1の順番でリセットを行う。

【0075】

期間T11において、配線WL4は電位VP1を与えられ、トランジスタM3はオン状態になる。このとき、ノードFN3は配線BLの電位V0を与えられる。ノードFN3は、リセットされる。

【0076】

期間T12において、配線WL4は電位V0を与えられ、トランジスタM3はオフ状態になる。このとき、ノードFN3は電位V0を維持する。

【0077】

期間T13において、配線WL3は電位VP1を与えられる。ノードFN3は、容量素子C3を介して、電位V0から電位VP1に持ち上げられる。このとき、トランジスタM2はオン状態になり、ノードFN2は電位V0を与えられる。ノードFN2はリセットされる。

【0078】

期間T14において、配線WL3は電位V0を与えられ、トランジスタM2は、オフ状態となる。ノードFN2は電位V0を維持する。

【0079】

期間T15において、配線WL2は電位VP1を与えられる。ノードFN2は、容量素子C2を介して、電位V0から電位VP1に持ち上げられる。このとき、トランジスタM1はオン状態になり、ノードFN1は電位V0が与えられる。ノードFN1はリセットされる。

【0080】

10

20

30

40

50

期間 T 1 6 において、配線 W L 2 は電位 V 0 を与えられ、トランジスタ M 1 は、オフ状態となる。ノード F N 1 は電位 V 0 を維持する。

【 0 0 8 1 】

以上、期間 T 1 1 乃至 T 1 6 の動作によりノード F N 1 、 F N 2 、 F N 3 のリセットが行われる。

【 0 0 8 2 】

次に、期間 T 1 7 乃至 T 2 3 において、ノード F N 1 乃至 F N 3 にデータの書き込みを行う。ノード F N 3 、ノード F N 2 、ノード F N 1 の順番で書き込みを行う。

【 0 0 8 3 】

期間 T 1 7 において、配線 W L 4 は電位 V P 1 を与えられる。トランジスタ M 3 はオン状態になる。このとき、ノード F N 3 は電位 V W 3 を書き込まれる。例えば、電位 V W 3 は、データの値に応じて、電位 V F 0 乃至 V F 1 5 ( 16 値 ) をとり得る。 10

【 0 0 8 4 】

期間 T 1 8 において、配線 W L 4 は電位 V 0 を与えられ、トランジスタ M 3 はオフ状態となり、ノード F N 3 は電位 V W 3 を保持する。

【 0 0 8 5 】

期間 T 1 9 において、配線 W L 3 は電位 V P 1 を与えられる。これによりノード F N 3 は、容量素子 C 3 を介して電位 V P 1 だけ持ち上げられ、電位 V W 3 に電位 V P 1 を加算した値になる。このとき、トランジスタ M 2 はオン状態になり、ノード F N 2 は電位 V W 2 を書き込まれる。電位 V W 2 は、データの値に応じて、例えば、電位 V F 0 乃至 V F 1 5 ( 16 値 ) をとり得る。 20

【 0 0 8 6 】

期間 T 2 0 において、配線 W L 3 は電位 V M 1 を与えられる。ノード F N 3 は容量素子 C 3 を介して負の電位をとり、トランジスタ M 2 はオフ状態となる。ノード F N 2 は電位 V W 2 を保持する。

【 0 0 8 7 】

期間 T 2 1 において、配線 W L 2 は電位 V P 1 を与えられる。これによりノード F N 2 は、容量素子 C 2 を介して、電位 V P 1 だけ持ち上げられる。このとき、トランジスタ M 1 はオン状態になり、ノード F N 1 に電位 V W 1 が書き込まれる。ノード F N 1 の電位 V W 1 は、データ値に応じて、例えば、電位 V F 0 乃至 V F 1 5 ( 16 値 ) をとり得る。 30

【 0 0 8 8 】

期間 T 2 2 において、配線 W L 2 は電位 V M 1 を与えられる。トランジスタ M 1 はオフ状態になり、ノード F N 1 は電位 V W 1 を保持する。このとき、トランジスタ M 2 、 M 3 をオフ状態にするため、配線 W L 3 、 W L 4 は電位 V M 2 を与えられる。その結果、ノード F N 3 は電位 V W 3 を保持する。

【 0 0 8 9 】

期間 T 2 3 において、配線 W L 1 は電位 V M 1 を与えられ、配線 W L 2 は電位 V M 2 を与えられ、配線 W L 3 、 W L 4 は電位 V M 3 を与えられる。このとき、トランジスタ M 0 はオフ状態になり、配線 S L と配線 B L 間は非導通状態となる。

【 0 0 9 0 】

以上の動作によって、メモリセル 1 0 0 b に、複数の 2 値又は多値のデータを書き込むことが可能になる。

【 0 0 9 1 】

読み出し動作

次に、図 4 で書き込まれたデータを、読み出す動作の一例について、図 5 を用いて説明を行う。

【 0 0 9 2 】

図 5 は、メモリセル 1 0 0 b の読み出し動作のタイミングチャートを示している。図 4 と同様に、上から順に、配線 W L 1 、配線 W L 2 、配線 W L 3 、配線 W L 4 、配線 B L 、配線 S L 、ノード F N 1 、ノード F N 2 、ノード F N 3 の電位をそれぞれ表している。また 50

、図中には、動作のタイミングを示すために、タイミングチャートを、期間T24乃至T36に分割している。

【0093】

データの読み出しは、ノードFN1の電位 $V_{W1}$ 、ノードFN2の電位 $V_{W2}$ 、ノードFN3の電位 $V_{W3}$ の順番で行う。ノードFN2の電位 $V_{W2}$ の読み出しは、ノードFN1の電位 $V_{W1}$ を読み出した後、ノードFN2の電位 $V_{W2}$ をノードFN1に移し、トランジスタM0で読み出しを行う。ノードFN3の電位 $V_{W3}$ の読み出しは、ノードFN1に移した電位 $V_{W2}$ を読み出した後、ノードFN3の電位 $V_{W3}$ をノードFN2に移し、その後、ノードFN1に移し、トランジスタM0で読み出しを行う。

【0094】

図5の期間T24は、書き込み動作を行なった後のホールド期間である。それぞれの配線及びノードは、図4の期間T23の状態を維持している。

【0095】

期間T25において、配線SLは電位VP1を与えられ、配線WL1は電位V0を与えられる。また、配線BLは電気的に浮遊状態にされる。このとき、トランジスタM0は、ゲート電位（ノードFN1の電位）に応じた電流を流し、配線BLに電荷が充電される。最終的には、ノードFN1と配線BLの電位差が、トランジスタM0のVthを下まわった段階で、配線BLの充電が終了する。

【0096】

配線BLに充電された電圧を配線BLに電気的に接続されたセンサ回路で読み出すことにより、ノードFN1の電位を読み出すことが可能になる。すなわち、ノードFN1に書き込まれた2値又は多値のデータを読み出すことが可能になる。

【0097】

期間T26において、配線SLは電位V0を与えられ、配線WL1は電位VM1を与えられる。このとき、トランジスタM0はオフ状態になる。

【0098】

期間T27において、ノードFN2のデータをノードFN1に移動する。配線WL2は電位V0を与えられ、配線BLは電位VP1を与えられる。トランジスタM1は、ノードFN2に書き込まれた電荷に応じて、ノードFN1を充電する。その結果、ノードFN2の電位 $V_{W2}$ がノードFN1に電位 $V_{W2}'$ として移動する。

【0099】

期間T28において、配線BLは電位V0を与えられ、配線WL1は電位VM1を与えられ、配線WL2は電位VM2を与えられる。このとき、トランジスタM0及びトランジスタM1はオフ状態になる。

【0100】

期間T29において、配線SLは電位VP1を与えられ、配線WL1は電位V0を与えられる。また、配線BLは電気的に浮遊状態にされる。トランジスタM0は、ノードFN1の電位に応じた電流を流し、配線BLは充電される。

【0101】

配線BLに充電された電圧を、配線BLに電気的に接続されたセンサ回路で読み出すことにより、ノードFN2に書き込まれた2値又は多値のデータを読み出すことが可能になる。

【0102】

期間T30において、配線SL及び配線BLは電位V0を与えられ、配線WL1は電位VM1を与えられる。このとき、トランジスタM0がオフ状態となる。

【0103】

期間T31において、ノードFN3のデータをノードFN2に移動する。配線WL2及び配線WL3は電位V0を与えられ、配線BLは電位VP1を与えられる。トランジスタM2はノードFN3の電位に応じてオン状態になり、ノードFN2を充電する。その結果、ノードFN3の電位 $V_{W3}$ がノードFN2に電位 $V_{W3}'$ として移動する。

10

20

30

40

50

## 【0104】

期間T32において、配線BLは電位V0を与えられ、配線WL2は電位VM2を与えられ、配線WL3は電位VM3を与えられる。このとき、トランジスタM2がオフ状態になる。

## 【0105】

期間T33において、期間T31でノードFN2に移動したノードFN3のデータを、さらにノードFN1に移動する。配線WL1、WL2は電位V0を与えられ、配線BLは電位VP1を与えられる。トランジスタM0は、ノードFN2の電位に応じてオン状態になり、ノードFN1を充電する。その結果、ノードFN2の電位V<sub>W3</sub>がノードFN1に電位V<sub>W3</sub>として移動する。

10

## 【0106】

期間T34において、配線BLは電位V0を与えられ、配線WL1は電位VM1を与えられ、配線WL2は電位VM2を与えられる。このとき、トランジスタM0、M1はオフ状態になる。

## 【0107】

期間T35において、配線SLは電位VP1を与えられ、配線WL1は電位V0を与えられる。また、配線BLは電気的に浮遊状態にされる。トランジスタM0は、ノードFN1の電位に応じて電流を流し、配線BLは充電される。

## 【0108】

配線BLに充電された電圧を配線BLに電気的に接続されたセンサ回路で読み出すことにより、ノードFN3に保存された2値又は多値のデータを読み出すことが可能になる。

20

## 【0109】

以上の動作によって、メモリセル100bは、書き込まれた複数の2値又は多値のデータを読み出すことが可能になる。

## 【0110】

## メモリセルの構成例5

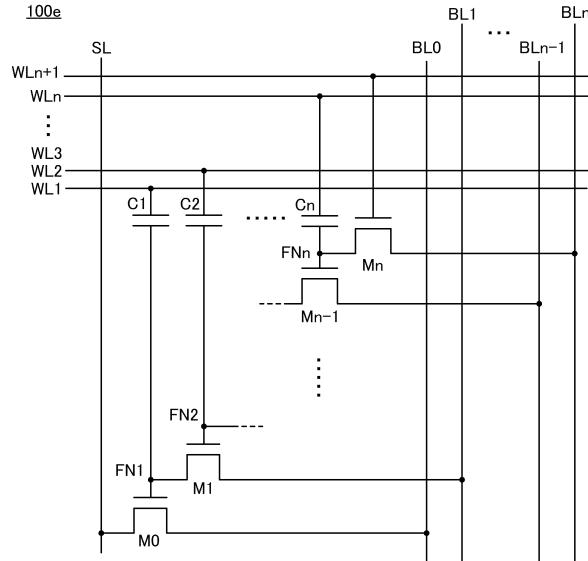

図3に示すメモリセル100dは、配線BLを配線BL0乃至BLnに分割し、トランジスタM0のソース及びドレインの一方を配線BL0に接続し、トランジスタM1のソース及びドレインの一方を配線BL1に接続し、トランジスタMnのソース及びドレインの一方を配線BLnに接続してもよい(図6、メモリセル100e)。

30

## 【0111】

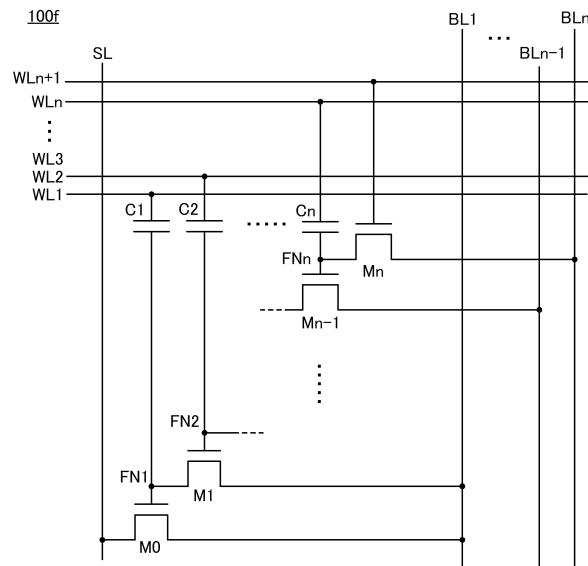

## メモリセルの構成例6

図3に示すメモリセル100dは、配線BLを配線BL1乃至BLnに分割し、トランジスタM0のソース及びドレインの一方と、トランジスタM1のソース及びドレインの一方を配線BL1に接続し、トランジスタMnのソース及びドレインの一方を配線BLnに接続してもよい(図7、メモリセル100f)。

## 【0112】

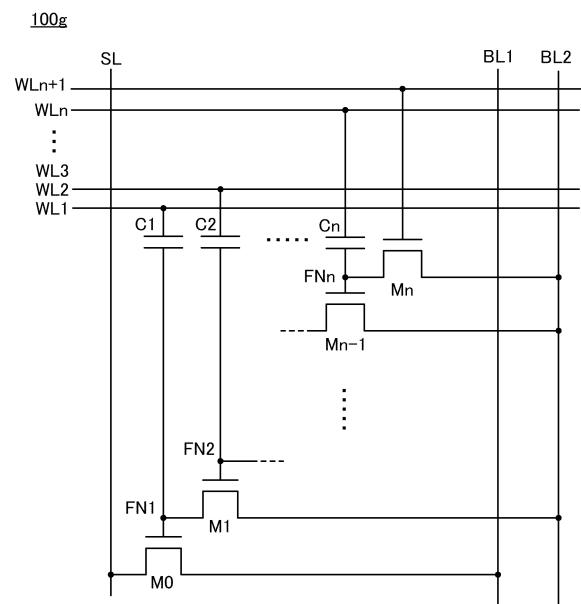

## メモリセルの構成例7

図3に示すメモリセル100dは、配線BLを配線BL1及び配線BL2に分割し、トランジスタM0のソース及びドレインの一方を配線BL1に接続し、トランジスタM1乃至Mnのソース及びドレインの一方を配線BL2に接続してもよい(図8、メモリセル100g)。

40

## 【0113】

## メモリセルの構成例8

図3に示すメモリセル100dは、トランジスタM1乃至Mnに第2のゲート電極を設けてよい。第2のゲート電極は、半導体層(チャネル形成領域)を間に介して、第1のゲート電極と重なる領域を有することが好ましい。なお、トランジスタM1乃至Mnの第2のゲート電極には共通の電位V<sub>BG</sub>を与えてもよい(図9、メモリセル100h)。こうすることで、トランジスタM1乃至Mnのしきい値を制御することが可能になる。

## 【0114】

50

### メモリセルの構成例 9

また、図9に示すトランジスタM1乃至Mnの第2のゲート電極は、それぞれのトランジスタの第1のゲート電極に電気的に接続されてもよい(図10、メモリセル100i)。こうすることで、トランジスタM1乃至Mnのオン電流を増大させることが可能になる。

### 【0115】

#### メモリセルの構成例 10

図3に示すメモリセル100dは、トランジスタM0にpチャネル型トランジスタを用いてよい(図11、メモリセル100k)。

### 【0116】

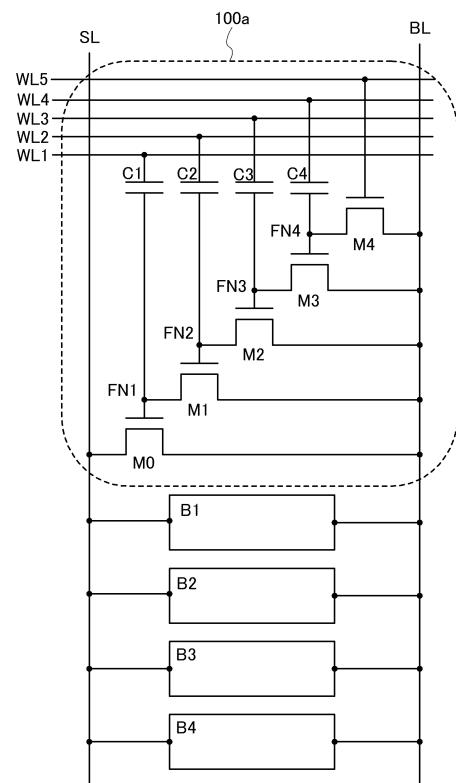

#### (実施の形態2)

10

本実施の形態では、本発明の一態様である記憶装置の構成例について、図12乃至図18を用いて説明を行う。

### 【0117】

実施の形態1に示したメモリセル100a乃至100kは、書き込まれたデータの読み出しを行うと、書き込まれたデータが消失してしまう。例えば、図5のタイミングチャートにおいて、メモリセル100bはノードFN2に書き込まれたデータを読み出す場合、ノードFN1に書き込まれたデータを失ってしまう。本実施の形態に示すメモリセルは、各ノードに書き込まれたデータを一時的に保持するための記憶回路を有し、データが消失することを防ぐ。

### 【0118】

20

#### 記憶装置の構成例 1

図12は、メモリセル100aに、記憶回路B1、記憶回路B2、記憶回路B3及び記憶回路B4が接続された例を示している。記憶回路B1乃至B4は、配線SL及び配線BLを介して、メモリセル100aに接続されている。

### 【0119】

記憶回路B1は、ノードFN1のデータを読み出す際に、当該データを一時的に保持する機能を有する。記憶回路B2は、ノードFN2のデータを読み出す際に、当該データを一時的に保持する機能を有する。記憶回路B3は、ノードFN3のデータを読み出す際に、当該データを一時的に保持する機能を有する。記憶回路B4は、ノードFN4のデータを読み出す際に、当該データを一時的に保持する機能を有する。全てのノードの読み出しが完了した後に、記憶回路B1乃至B4は、それぞれのノードにデータを書き戻す機能を有する。

30

### 【0120】

#### 記憶装置の構成例 2

図13は、メモリセル100bに、記憶回路B1乃至B3が接続された例を示している。記憶回路B1乃至B3は、配線SL及び配線BLを介して、メモリセル100bに接続されている。

### 【0121】

記憶回路B1は、ノードFN1のデータを読み出す際に、当該データを一時的に保持する機能を有する。記憶回路B2は、ノードFN2のデータを読み出す際に、当該データを一時的に保持する機能を有する。記憶回路B3は、ノードFN3のデータを読み出す際に、当該データを一時的に保持する機能を有する。全てのノードの読み出しが完了した後に、記憶回路B1乃至B3は、それぞれのノードにデータを書き戻す機能を有する。

40

### 【0122】

#### 記憶装置の構成例 3

図14は、メモリセル100cに、記憶回路B1、B2が接続された例を示している。記憶回路B1、B2は、配線SL及び配線BLを介して、メモリセル100cに接続されている。

### 【0123】

記憶回路B1は、ノードFN1のデータを読み出す際に、当該データを一時的に保持する

50

機能を有する。記憶回路B2は、ノードFN2のデータを読み出す際に、当該データを一時的に保持する機能を有する。全てのノードの読み出しが完了した後に、記憶回路B1、B2は、それぞれのノードにデータを書き戻す機能を有する。

【0124】

記憶装置の構成例4

図15は、メモリセル100dに、記憶回路B1乃至Bnが接続された例を示している。記憶回路B1乃至Bnは、配線SL及び配線BLを介して、メモリセル100dに接続されている。

【0125】

記憶回路B1は、ノードFN1のデータを読み出す際に、当該データを一時的に保持する機能を有する。記憶回路Bnは、ノードFNnのデータを読み出す際に、当該データを一時的に保持する機能を有する。全てのノードの読み出しが完了した後に、記憶回路B1乃至Bnは、それぞれのノードにデータを書き戻す機能を有する。 10

【0126】

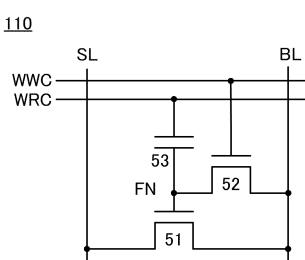

記憶回路の構成例

図16は、記憶回路B1乃至Bnに適用可能な、メモリセル110の構成例を示す回路図である。メモリセル110は、トランジスタ51と、トランジスタ52と、容量素子53と、ノードFNとを有している。

【0127】

ノードFNは、トランジスタ51のゲート及び容量素子53の第1の端子に電気的に接続されている。容量素子53の第2の端子は、配線WRCに電気的に接続されている。トランジスタ52は、ノードFNと配線BLとの間の導通又は非導通を制御する機能を有する。トランジスタ52のゲートは配線WWCに電気的に接続されている。トランジスタ51は、配線SLと配線BLとの間の導通又は非導通を制御する機能を有する。 20

【0128】

ノードFNは、ノードFN1乃至FNnの何れか一に書き込まれたデータを保持する機能を有する。当該データは、配線BL及びトランジスタ52を経由して、ノードFNに書き込まれる。

【0129】

トランジスタ52には、オフ電流が低いトランジスタを用いることが好適である。このようにオフ電流が低いトランジスタとしては、チャネル形成領域に酸化物半導体を有するOSトランジスタや、チャネル形成領域にワイドバンドギャップ半導体を用いたトランジスタが挙げられる。特に、OSトランジスタを用いることが好適である。 30

【0130】

トランジスタ51は、ノードFN(トランジスタ51のゲート)に与えられた電位に応じてチャネル抵抗が変化する。配線SLと配線BLとの間に電位差を与え、配線SLと配線BLとの間を流れる電流、又は、配線BLの電位を検出することで、ノードFNに与えられた電位を間接的に読み出すことが可能になる。

【0131】

トランジスタ51は、Siトランジスタを用いてもよい。トランジスタ51に、Siトランジスタを用いることで、メモリセル110は、データの読み出し速度を向上させることが可能になる。 40

【0132】

トランジスタ51はOSトランジスタを用いてもよい。トランジスタ51にOSトランジスタを適用することで、メモリセル110は消費電力を低減することが可能になる。また、トランジスタ51のゲート絶縁膜を厚く形成することが可能になり、ノードFNに書き込まれた電荷を長期間保持することが可能になる。

【0133】

メモリアレイの構成例

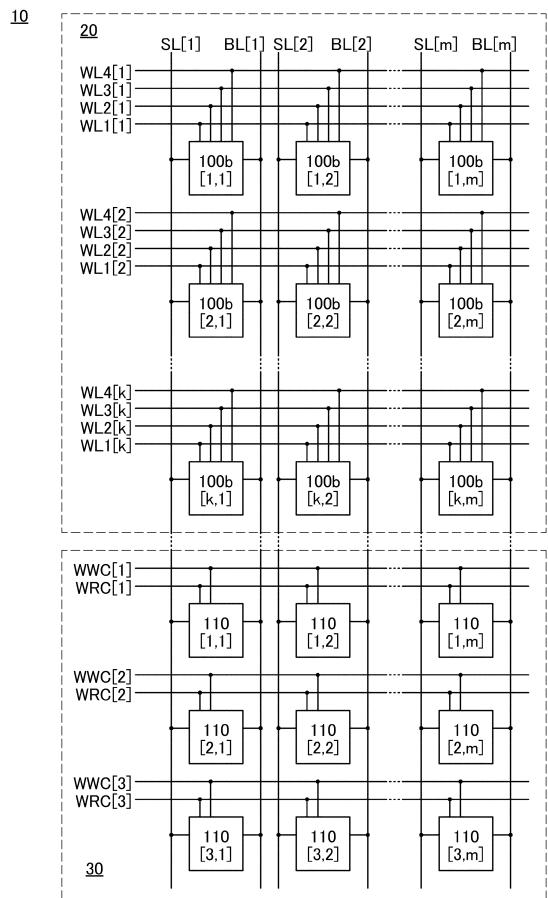

図17にメモリセルアレイ10の構成例を示す。メモリセルアレイ10は、メインメモリ 50

セルアレイ20と、一時保管用のサブメモリセルアレイ30を有する。メインメモリセルアレイ20は、実施の形態1に示すメモリセルがマトリクス状に設けられている。図17は、一例として、図2(A)のメモリセル100bがk行m列(k、mは2以上の整数)マトリックス状に配置されている例を示す。サブメモリセルアレイ30は、図16に示すメモリセル110が3行m列のマトリックス状に設けられている例を示す。

#### 【0134】

サブメモリセルアレイ30の縦方向の段数(行の数)は、メモリセル100bが有する保持ノードの数に対応する(メモリセル100bの場合は、ノードFN1、FN2、FN3の3つ)。サブメモリセルアレイ30の横方向の段数(列の数)は、メインメモリセルアレイ20のそれと同じとする。

10

#### 【0135】

##### サブメモリセルアレイの動作例

次に、サブメモリセルアレイ30の動作の一例について、図18を用いて説明を行う。図18は、一例として、メインメモリセルアレイ20に配置されたメモリセル100b[1、1]と、サブメモリセルアレイ30に配置されたメモリセル110[1、1]、110[2、1]、110[3、1]の動作について考える。

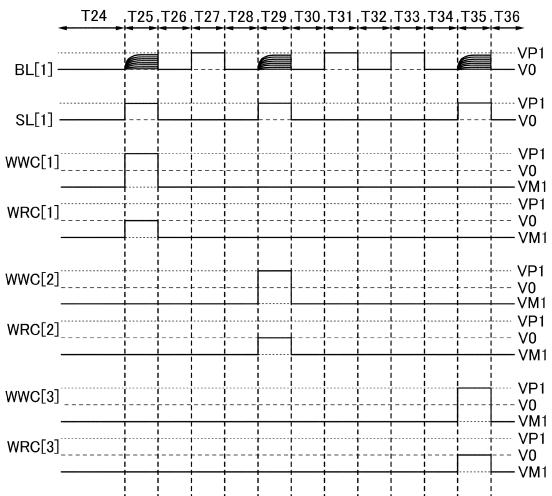

#### 【0136】

メモリセル100b[1、1]の読み出し動作については、図5のタイミングチャートを参考すればよい。図18のタイミングチャートは、配線BL1[1]、配線SL[1]、配線WWC[1]、配線WRC[1]、配線WWC[2]、配線WRC[2]、配線WWC[3]、配線WRC[3]についてのみ記載する。なお、図18に示す期間T24乃至T36は、図5に示す期間T24乃至T36と同じタイミングを表す。

20

#### 【0137】

期間T24の準備期間において、配線BL[1]、SL[1]に電位V0を与え、配線WWC[1]、WRC[1]、WWC[2]、WRC[2]、WWC[3]、WRC[3]に、電位VM1を与える。

#### 【0138】

期間T25において、メモリセル100b[1、1]のノードFN1のデータを読み出す際に、配線WWC[1]に電位VP1を与え、配線WRC[1]に電位V0を与える。このとき、該当するメモリセル110[1、1]のトランジスタ52がオン状態となる。配線BLには、ノードFN1のデータにあたる電位Vw1が出力されているので、メモリセル110[1、1]のノードFNに、電位Vw1が書き込まれる。

30

#### 【0139】

期間T26において、配線WWC[1]、WRC[1]に電位VM1を与える。このとき、メモリセル110[1、1]のトランジスタ52がオフ状態となる。メモリセル100b[1、1]のノードFN1のデータを一時的に保存する。

#### 【0140】

期間T29において、メモリセル100b[1、1]のノードFN2のデータを読み出す際に、配線WWC[2]に電位VP1を与え、配線WRC[2]に電位V0を与える。このとき、メモリセル110[2、1]のトランジスタ52がオン状態となる。配線BLには、ノードFN2のデータにあたる電位Vw2'が出力されているので、メモリセル110[2、1]のノードFNに電位Vw2'が書き込まれる。

40

#### 【0141】

次の期間T30において、配線WWC[2]、WRC[2]に電位VM1を与える。このとき、メモリセル110[2、1]のトランジスタ52がオフ状態となり、メモリセル100b[1、1]のノードFN2のデータを一時的に保存する。

#### 【0142】

期間T35において、メモリセル100b[1、1]のノードFN3のデータを読み出す際に、配線WWC[3]に電位VP1を与え、配線WRC[3]に電位V0を与える。このとき、メモリセル110[3、1]のトランジスタ52がオン状態となる。配線BLに

50

は、ノード FN 2 のデータにあたる電位  $V_{W_3}$  が出力され、メモリセル 110 [3, 1] のノード FN に、電位  $V_{W_3}$  が書き込まれる。

【0143】

次の期間 T36 において、配線 WWC [3]、WRC [3] に電位 VM1 を与える。このとき、メモリセル 110 [3, 1] のトランジスタ 52 がオフ状態となり、メモリセル 100b [1, 1] のノード FN3 のデータを一時的に保存する。

【0144】

メモリセル 100b [1, 1] のデータ読み出しが完了したら、サブメモリセルアレイ 30 に保存されたデータを、メモリセル 100b [1, 1] に書き戻す。データの書き戻しは、メモリセル 110 [3, 1]、110 [2, 1]、110 [1, 1] の順に行えばよい。例えば、メモリセル 110 [3, 1] のデータの書き戻しは、配線 BL を電気的に浮遊状態にし、配線 SL、WRC [3]、WL4 [1] に電位 VP1 を与えることで行えばよい。配線 BL は、メモリセル 110 [3, 1] のノード FN に対応した電位になり、メモリセル 100b [1, 1] のノード FN3 にデータが書き戻される。メモリセル 110 [2, 1]、110 [1, 1] についても同様である。

【0145】

以上の動作により、メモリセルアレイ 10 は、保持されたデータを失うことなく、データの読み出しを行うことが可能になる。

【0146】

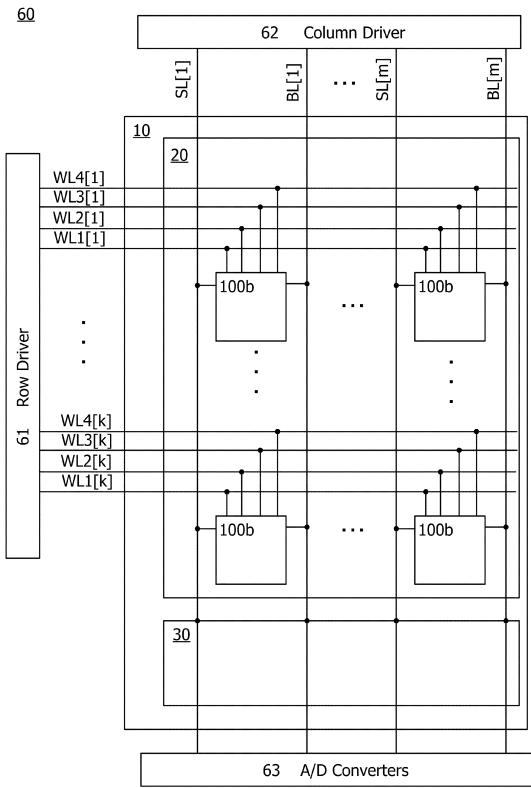

記憶装置の構成例

図 19 は、記憶装置の構成例を示すブロック図である。図 19 に示す記憶装置 60 は、図 17 で説明したメモリセルアレイ 10、行選択ドライバ 61、列選択ドライバ 62、および A/D コンバータ 63 を有する。

【0147】

行選択ドライバ 61 は、メモリセル 100b の各行におけるトランジスタ M3 を選択的に導通状態とする機能、およびメモリセル 100b の各行におけるノード FN1 乃至 FN3 の電位を選択的に変化させる機能、を備えた回路である。行選択ドライバ 61 を備えることで、記憶装置 60 は、メモリセル 100b へのデータの書き込みおよび読み出しを行毎に選択して行うことが可能になる。

【0148】

列選択ドライバ 62 は、メモリセル 100b の各列におけるノード FN1 乃至 FN3 に選択的にデータを書き込む機能、配線 BL、SL の電位を初期化する機能、配線 BL を電気的に浮遊状態とする機能、などを備えた回路である。列選択ドライバ 62 を備えることで、記憶装置 60 は、メモリセル 100b へのデータの書き込みおよび読み出しを列毎に選択して行うことが可能になる。

【0149】

A/D コンバータ 63 は、アナログ値である配線 BL の電位を、デジタル値に変換して外部に出力する機能を備えた回路である。具体的には、フラッシュ型の A/D コンバータを有する回路である。A/D コンバータ 63 を備えることで、記憶装置 60 は、メモリセル 100b より読み出されたデータに対応する配線 BL の電位を外部に出力することが可能になる。

【0150】

なお A/D コンバータ 63 は、フラッシュ型の A/D コンバータとして説明を行うが、逐次比較型、マルチスロープ型、デルタシグマ型の A/D コンバータを用いてもよい。

【0151】

(実施の形態 3)

本実施の形態では、上記実施の形態に示すトランジスタ M0 乃至 Mn に適用可能な OS トランジスタの構造について説明する。

【0152】

トランジスタの構成例 1

10

20

30

40

50

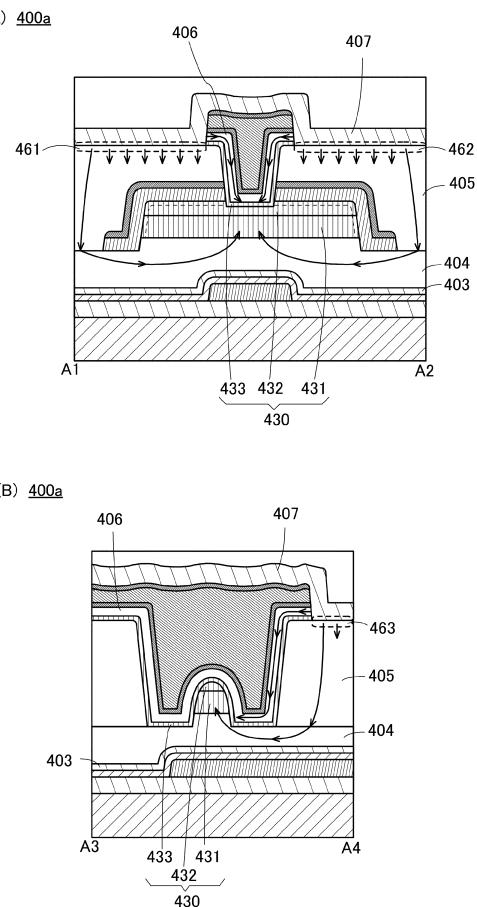

図20(A)乃至(C)は、トランジスタ400aの上面図および断面図である。図20(A)は上面図である。図20(B)は、図20(A)に示す一点鎖線A1-A2に対応する断面図であり、図20(C)は、図20(A)に示す一点鎖線A3-A4に対応する断面図である。なお、図20(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。なお、一点鎖線A1-A2をトランジスタ400aのチャネル長方向、一点鎖線A3-A4をトランジスタ400aのチャネル幅方向と呼ぶ場合がある。

【0153】

トランジスタ400aは、基板450と、基板450上の絶縁膜401と、絶縁膜401上の導電膜414と、導電膜414を覆うように形成された絶縁膜402と、絶縁膜402上の絶縁膜403と、絶縁膜403上の絶縁膜404と、絶縁膜404上に、金属酸化物431、金属酸化物432の順で形成された積層と、金属酸化物432の上面及び側面と接する導電膜421と、同じく金属酸化物432の上面及び側面と接する導電膜423と、導電膜421上の導電膜422と、導電膜423上の導電膜424と、導電膜422、424上の絶縁膜405と、金属酸化物431、432、導電膜421乃至424及び絶縁膜405と接する金属酸化物433と、金属酸化物433上の絶縁膜406と、絶縁膜406上の導電膜411と、導電膜411上の導電膜412と、導電膜412上の導電膜413と、導電膜413を覆うように形成された絶縁膜407と、絶縁膜407上の絶縁膜408を有する。なお、金属酸化物431、金属酸化物432および金属酸化物433をまとめて、金属酸化物430と呼称する。

【0154】

金属酸化物432は半導体であり、トランジスタ400aのチャネルとしての機能を有する。

【0155】

また、金属酸化物431及び金属酸化物432は、領域441及び領域442を有する。領域441は、導電膜421と、金属酸化物431、432が接する領域の近傍に形成され、領域442は、導電膜423と、金属酸化物431、432が接する領域の近傍に形成される。

【0156】

領域441、442は低抵抗領域としての機能を有する。金属酸化物431、432は、領域441を有することで、導電膜421との間のコンタクト抵抗を低減させることができになる。同様に、金属酸化物431、432は、領域442を有することで、導電膜423との間のコンタクト抵抗を低減させることができになる。

【0157】

導電膜421、422は、トランジスタ400aのソース電極又はドレイン電極の一方としての機能を有する。導電膜423、424は、トランジスタ400aのソース電極又はドレイン電極の他方としての機能を有する。

【0158】

導電膜422は導電膜421よりも酸素を透過しにくい機能を有する。これにより、酸化による導電膜421の導電率の低下を防ぐことが可能になる。

【0159】

同様に、導電膜424は導電膜423よりも酸素を透過しにくい機能を有する。これにより、酸化による導電膜423の導電率の低下を防ぐことが可能になる。

【0160】

導電膜411乃至413は、トランジスタ400aの第1のゲート電極としての機能を有する。

【0161】

導電膜411、413は、導電膜412よりも酸素を透過しにくい機能を有する。これにより、酸化による導電膜412の導電率の低下を防ぐことが可能になる。

【0162】

絶縁膜406は、トランジスタ400aの第1のゲート絶縁膜としての機能を有する。

10

20

30

40

50

## 【0163】

導電膜414は、トランジスタ400aの第2のゲート電極としての機能を有する。

## 【0164】

導電膜411乃至413と導電膜414は同じ電位が与えられてもよいし、異なる電位が与えられてもよい。また導電膜414は、場合によっては省略してもよい。

## 【0165】

絶縁膜401乃至404は、トランジスタ400aの下地絶縁膜としての機能を有する。また、絶縁膜402乃至404は、トランジスタ400aの第2のゲート絶縁膜としての機能も有する。

## 【0166】

絶縁膜405、407、408は、トランジスタ400aの保護絶縁膜又は層間絶縁膜としての機能を有する。

## 【0167】

図20(C)に示すように、金属酸化物432の側面は、導電膜411に囲まれている。上記構成をとることで、導電膜411の電界によって、金属酸化物432を電気的に取り囲むことができる。ゲート電極の電界によって、半導体を電気的に取り囲むトランジスタの構造を、surrounded channel(s-channel)構造とよぶ。金属酸化物432の全体(バルク)にチャネルが形成されるため、s-channel構造は、トランジスタのソース-ドレイン間に大電流を流すことができ、トランジスタのオン電流を高くすることができる。

10

20

## 【0168】

s-channel構造は、高いオン電流が得られるため、LSI(Large Scale Integration)など微細化されたトランジスタが要求される半導体装置に適した構造といえる。トランジスタを微細化できるため、該トランジスタを有する半導体装置は、集積度の高い、高密度化された半導体装置とすることが可能となる。

## 【0169】

トランジスタ400aにおいて、ゲート電極として機能する領域は、絶縁膜405などに形成された開口部を埋めるように自己整合(self-align)的に形成される。

## 【0170】

図20(B)に示すように、導電膜411と導電膜422は、絶縁膜を間に介して、互いに重なる領域を有する。同様に、導電膜411と導電膜423は、絶縁膜を間に介して、互いに重なる領域を有する。これらの領域は、ゲート電極と、ソース電極又はドレイン電極との間に生じた寄生容量として機能し、トランジスタ400aの動作速度を低下させる原因になり得る。トランジスタ400aは、絶縁膜405を設けることで、上述の寄生容量を低下させることができになる。絶縁膜405は、比誘電率の低い材料からなることが好ましい。

30

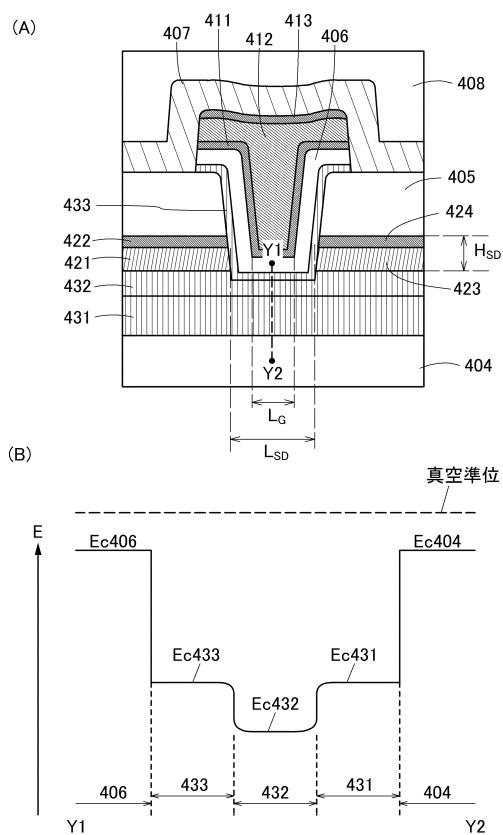

## 【0171】

図21(A)は、トランジスタ400aの中央部を拡大したものである。図21(A)において、導電膜411の底面が、絶縁膜406及び金属酸化物433を介して、金属酸化物432の上面と平行に面する領域の長さを、幅 $L_G$ として示す。幅 $L_G$ は、ゲート電極の線幅を表す。また、図21(A)において、導電膜421と導電膜423の間の長さを、幅 $L_{SD}$ として示す。幅 $L_{SD}$ は、ソース電極とドレイン電極との間の長さを表す。

40

## 【0172】

幅 $L_{SD}$ は最小加工寸法で決定されることが多い。図21(A)に示すように、幅 $L_G$ は、幅 $L_{SD}$ よりも小さい。すなわち、トランジスタ400aは、ゲート電極の線幅を、最小加工寸法より小さくすることが可能になる。具体的には、幅 $L_G$ は、5nm以上60nm以下、好ましくは5nm以上30nm以下とすることが可能になる。

## 【0173】

図21(A)において、導電膜421及び導電膜422の厚さの合計、又は、導電膜423及び導電膜424の厚さの合計を高さ $H_{SD}$ と表す。

50

## 【0174】

絶縁膜406の厚さを、高さH<sub>SD</sub>以下とすることで、ゲート電極からの電界がチャネル形成領域全体に印加することが可能になり好ましい。絶縁膜406の厚さは、30nm以下、好ましくは10nm以下とする。

## 【0175】

また、導電膜422と導電膜411の間に形成される寄生容量、及び、導電膜424と導電膜411の間に形成される寄生容量の値は、絶縁膜405の厚さに反比例する。例えば、絶縁膜405の厚さを、絶縁膜406の厚さの3倍以上、好ましくは5倍以上することで、寄生容量は無視できるほど小さくなり、好ましい。その結果、トランジスタ400aを高周波数で動作させることが可能になる。

10

## 【0176】

以下、トランジスタ400aの各構成要素について説明を行う。

## 【0177】

## 金属酸化物層

まず、金属酸化物431乃至433に適用可能な金属酸化物について説明を行う。

## 【0178】

トランジスタ400aは、非導通状態においてソースとドレインとの間を流れる電流（オフ電流）が低いことが好適である。オフ電流が低いトランジスタとしては、チャネル形成領域に酸化物半導体を有するトランジスタが挙げられる。

20

## 【0179】

金属酸化物432は、例えば、インジウム（In）を含む酸化物半導体である。金属酸化物432は、例えば、インジウムを含むと、キャリア移動度（電子移動度）が高くなる。また、金属酸化物432は、元素Mを含むと好ましい。元素Mは、好ましくは、アルミニウム（Al）、ガリウム（Ga）、イットリウム（Y）またはスズ（Sn）などとする。そのほかの元素Mに適用可能な元素としては、ホウ素（B）、シリコン（Si）、チタン（Ti）、鉄（Fe）、ニッケル（Ni）、ゲルマニウム（Ge）、ジルコニウム（Zr）、モリブデン（Mo）、ランタン（La）、セリウム（Ce）、ネオジム（Nd）、ハフニウム（Hf）、タンタル（Ta）、タンゲステン（W）などがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。元素Mは、例えば、酸素との結合エネルギーが高い元素である。例えば、酸素との結合エネルギーがインジウムよりも高い元素である。または、元素Mは、例えば、金属酸化物のエネルギーギャップを大きくする機能を有する元素である。また、金属酸化物432は、亜鉛（Zn）を含むと好ましい。金属酸化物は、亜鉛を含むと結晶化しやすくなる場合がある。

30

## 【0180】

ただし、金属酸化物432は、インジウムを含む酸化物半導体に限定されない。金属酸化物432は、例えば、亜鉛スズ酸化物、ガリウムスズ酸化物などの、インジウムを含まず、亜鉛を含む酸化物半導体、ガリウムを含む酸化物半導体、スズを含む酸化物半導体などであっても構わない。

## 【0181】

金属酸化物432は、例えば、エネルギーギャップが大きい酸化物半導体を用いる。金属酸化物432のエネルギーギャップは、例えば、2.5eV以上4.2eV以下、好ましくは2.8eV以上3.8eV以下、さらに好ましくは3eV以上3.5eV以下とする。

40

## 【0182】

金属酸化物432は、後述するCAC-O<sub>5</sub>膜であることが好ましい。

## 【0183】

例えば、金属酸化物431および金属酸化物433は、金属酸化物432を構成する酸素以外の元素一種以上、または二種以上から構成される金属酸化物である。金属酸化物432を構成する酸素以外の元素一種以上、または二種以上から金属酸化物431および金属酸化物433が構成されるため、金属酸化物431と金属酸化物432との界面、および

50

金属酸化物432と金属酸化物433との界面において、界面準位が形成されにくい。

【0184】

なお、金属酸化物431がIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%より高く、さらに好ましくはInが25atomic%未満、Mが75atomic%より高いとする。金属酸化物431をスパッタリング法で成膜する場合、上記の組成を満たすスパッタリングターゲットを用いることが好ましい。例えば、In:M:Zn=1:3:2、In:M:Zn=1:3:4などが好ましい。

【0185】

また、金属酸化物432がIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが25atomic%より高く、Mが75atomic%未満、さらに好ましくはInが34atomic%より高く、Mが66atomic%未満とする。金属酸化物432をスパッタリング法で成膜する場合、上記の組成を満たすスパッタリングターゲットを用いることが好ましい。例えば、In:M:Zn=1:1:1、In:M:Zn=1:1:1.2、In:M:Zn=2:1:3、In:M:Zn=3:1:2、In:M:Zn=4:2:4.1が好ましい。特に、スパッタリングターゲットとして、原子数比がIn:Ga:Zn=4:2:4.1を用いる場合、成膜される金属酸化物432の原子数比は、In:Ga:Zn=4:2:3近傍となる場合がある。

【0186】

また、金属酸化物433がIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%より高く、さらに好ましくはInが25atomic%未満、Mが75atomic%より高くする。例えば、In:M:Zn=1:3:2、In:M:Zn=1:3:4などが好ましい。また、金属酸化物433は、金属酸化物431と同種の金属酸化物を用いても構わない。

【0187】

また、金属酸化物431または金属酸化物433がインジウムを含まなくても構わない場合がある。例えば、金属酸化物431または金属酸化物433が酸化ガリウムであっても構わない。

【0188】

次に、金属酸化物431乃至433の積層により構成される金属酸化物430の機能およびその効果について、図21(B)に示すエネルギー・バンド構造図を用いて説明する。図21(B)は、図21(A)にY1-Y2の鎖線で示した部位のエネルギー・バンド構造を示している。また、図21(B)は、トランジスタ400aのチャネル形成領域とその近傍のエネルギー・バンド構造を示している。

【0189】

図21(B)中、Ec404、Ec431、Ec432、Ec433、Ec406は、それぞれ、絶縁膜404、金属酸化物431、金属酸化物432、金属酸化物433、絶縁膜406の伝導帯下端のエネルギーを示している。

【0190】

ここで、真空準位と伝導帯下端のエネルギーとの差(「電子親和力」ともいう。)は、真空準位と価電子帯上端のエネルギーとの差(イオン化ポテンシャルともいう。)からエネルギー・ギャップを引いた値となる。なお、エネルギー・ギャップは、分光エリプソメータを用いて測定できる。また、真空準位と価電子帯上端のエネルギー差は、紫外線光電子分光分析(UPS: ultraviolet Photoelectron Spectroscopy)装置を用いて測定できる。

【0191】

絶縁膜404と絶縁膜406は絶縁体であるため、Ec406とEc404は、Ec431、Ec432、およびEc433よりも真空準位に近い(電子親和力が小さい)。

10

20

30

40

50

## 【0192】

金属酸化物432は、金属酸化物431および金属酸化物433よりも電子親和力の大きい金属酸化物を用いる。例えば、金属酸化物432として、金属酸化物431および金属酸化物433よりも電子親和力の0.07eV以上1.3eV以下、好ましくは0.1eV以上0.7eV以下、さらに好ましくは0.15eV以上0.4eV以下大きい金属酸化物を用いる。なお、電子親和力は、真空準位と伝導帯下端のエネルギーとの差である。

## 【0193】

なお、インジウムガリウム酸化物は、小さい電子親和力と、高い酸素ブロック性を有する。そのため、金属酸化物433がインジウムガリウム酸化物を含むと好ましい。ガリウム原子割合[Ga / (In + Ga)]は、例えば、70%以上、好ましくは80%以上、さらに好ましくは90%以上とする。

10

## 【0194】

このとき、ゲート電圧を印加すると、金属酸化物431、金属酸化物432、金属酸化物433のうち、電子親和力の大きい金属酸化物432にチャネルが形成される。

## 【0195】

このとき、電子は、金属酸化物431、433の中ではなく、金属酸化物432の中を主として移動する。そのため、金属酸化物431と絶縁膜404との界面、あるいは、金属酸化物433と絶縁膜406との界面に、電子の流れを阻害する界面準位が多く存在したとしても、トランジスタのオン電流にはほとんど影響を与えない。金属酸化物431、433は、絶縁膜のように機能する。

20

## 【0196】

金属酸化物431と金属酸化物432との間には、金属酸化物431と金属酸化物432との混合領域を有する場合がある。また、金属酸化物432と金属酸化物433との間には、金属酸化物432と金属酸化物433との混合領域を有する場合がある。混合領域は、界面準位密度が低くなる。そのため、金属酸化物431、金属酸化物432および金属酸化物433の積層体は、それぞれの界面近傍において、エネルギーが連続的に変化する（連続接合ともいう。）バンド構造となる。

## 【0197】

金属酸化物431と金属酸化物432の界面、あるいは、金属酸化物432と金属酸化物433との界面は、上述したように界面準位密度が小さいため、金属酸化物432中で電子の移動が阻害されることが少なく、トランジスタのオン電流を高くすることが可能になる。

30

## 【0198】

例えば、トランジスタ中の電子の移動は、チャネル形成領域の物理的な凹凸が大きい場合に阻害される。トランジスタのオン電流を高くするためには、例えば、金属酸化物432の上面または下面（被形成面、ここでは金属酸化物431の上面）の、 $1\text{ }\mu\text{m} \times 1\text{ }\mu\text{m}$ の範囲における二乗平均平方根（RMS：Root Mean Square）粗さが1nm未満、好ましくは0.6nm未満、さらに好ましくは0.5nm未満、より好ましくは0.4nm未満とすればよい。また、 $1\text{ }\mu\text{m} \times 1\text{ }\mu\text{m}$ の範囲における平均面粗さ（Raともいう。）が1nm未満、好ましくは0.6nm未満、さらに好ましくは0.5nm未満、より好ましくは0.4nm未満とすればよい。また、 $1\text{ }\mu\text{m} \times 1\text{ }\mu\text{m}$ の範囲における最大高低差（P-Vともいう。）が10nm未満、好ましくは9nm未満、さらに好ましくは8nm未満、より好ましくは7nm未満とすればよい。RMS粗さ、RaおよびP-Vは、エスアイアイ・ナノテクノロジー株式会社製走査型プローブ顕微鏡システムSPA-500などを用いて測定することができる。

40

## 【0199】

チャネルの形成される領域中の欠陥準位密度が高い場合にも、電子の移動は阻害される。例えば、金属酸化物432が酸素欠損（V<sub>o</sub>とも表記。）を有する場合、酸素欠損のサイトに水素が入り込むことでドナー準位を形成することがある。以下では酸素欠損のサイトに水素が入り込んだ状態をV<sub>o</sub>Hと表記する場合がある。V<sub>o</sub>Hは電子を散乱するため、

50

トランジスタのオン電流を低下させる要因となる。なお、酸素欠損のサイトは、水素が入るよりも酸素が入る方が安定する。したがって、金属酸化物432中の酸素欠損を低減することで、トランジスタのオン電流を高くすることができる場合がある。

#### 【0200】

例えば、金属酸化物432のある深さにおいて、または、金属酸化物432のある領域において、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)で測定される水素濃度は、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、 $2 \times 10^{20}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、 $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下とする。

10

#### 【0201】

金属酸化物432の酸素欠損を低減するために、例えば、絶縁膜404に含まれる過剰酸素を、金属酸化物431を介して金属酸化物432まで移動させる方法などがある。この場合、金属酸化物431は、酸素透過性を有する層(酸素を通過または透過させる層)であることが好ましい。

#### 【0202】

なお、トランジスタがs-channel構造を有する場合、金属酸化物432の全体にチャネルが形成される。したがって、金属酸化物432が厚いほどチャネル領域は大きくなる。即ち、金属酸化物432が厚いほど、トランジスタのオン電流を高くすることができる。

20

#### 【0203】

また、トランジスタのオン電流を高くするためには、金属酸化物433は薄いほど好ましい。金属酸化物433は、例えば、10 nm未満、好ましくは5 nm以下、さらに好ましくは3 nm以下の領域を有していればよい。一方、金属酸化物433は、チャネルの形成される金属酸化物432へ、隣接する絶縁体を構成する酸素以外の元素(水素、シリコンなど)が入り込まないようブロックする機能を有する。そのため、金属酸化物433は、ある程度の厚さを有することが好ましい。金属酸化物433は、例えば、0.3 nm以上、好ましくは1 nm以上、さらに好ましくは2 nm以上の厚さの領域を有していればよい。また、金属酸化物433は、絶縁膜404などから放出される酸素の外方拡散を抑制するために、酸素をブロックする性質を有すると好ましい。

30

#### 【0204】

また、信頼性を高くするためには、金属酸化物431は厚く、金属酸化物433は薄いことが好ましい。金属酸化物431は、例えば、10 nm以上、好ましくは20 nm以上、さらに好ましくは40 nm以上、より好ましくは60 nm以上の厚さの領域を有していればよい。金属酸化物431の厚さを、厚くすることで、隣接する絶縁体と金属酸化物431との界面からチャネルの形成される金属酸化物432までの距離を離すことができる。ただし、半導体装置の生産性が低下する場合があるため、金属酸化物431は、例えば、200 nm以下、好ましくは120 nm以下、さらに好ましくは80 nm以下の厚さの領域を有していればよい。

40

#### 【0205】

例えば、金属酸化物432と金属酸化物431との間に、例えば、SIMS分析において、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、 $2 \times 10^{18}$  atoms/cm<sup>3</sup>未満のシリコン濃度となる領域を有する。また、金属酸化物432と金属酸化物433との間に、SIMSにおいて、 $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、 $1 \times 10^{19}$  atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以上、 $2 \times 10^{18}$  atoms/cm<sup>3</sup>未満のシリコン濃度となる領域を有する。

50

## 【0206】

また、金属酸化物432の水素濃度を低減するために、金属酸化物431および金属酸化物433の水素濃度を低減すると好ましい。金属酸化物431および金属酸化物433は、S I M Sにおいて、 $1 \times 10^{16}$  atoms / cm<sup>3</sup>以上、 $2 \times 10^{20}$  atoms / cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$  atoms / cm<sup>3</sup>以上、 $5 \times 10^{19}$  atoms / cm<sup>3</sup>以下、より好ましくは $1 \times 10^{16}$  atoms / cm<sup>3</sup>以上、 $1 \times 10^{19}$  atoms / cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms / cm<sup>3</sup>以上、 $5 \times 10^{18}$  atoms / cm<sup>3</sup>以下の水素濃度となる領域を有する。また、金属酸化物432の窒素濃度を低減するために、金属酸化物431および金属酸化物433の窒素濃度を低減すると好ましい。金属酸化物431および金属酸化物433は、S I M Sにおいて、 $1 \times 10^{16}$  atoms / cm<sup>3</sup>以上、 $5 \times 10^{19}$  atoms / cm<sup>3</sup>未満、好ましくは $1 \times 10^{16}$  atoms / cm<sup>3</sup>以上、 $5 \times 10^{18}$  atoms / cm<sup>3</sup>以下、より好ましくは $1 \times 10^{16}$  atoms / cm<sup>3</sup>以上、 $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms / cm<sup>3</sup>以上、 $5 \times 10^{17}$  atoms / cm<sup>3</sup>以下の窒素濃度となる領域を有する。10

## 【0207】

金属酸化物431乃至433の成膜は、スパッタリング法、C V D ( C h e m i c a l V a p o r D e p o s i t i o n ) 法、M B E ( M o l e c u l a r B e a m E p i t a x y ) 法またはP L D ( P u l s e d L a s e r D e p o s i t i o n ) 法、A L D ( A t o m i c L a y e r D e p o s i t i o n ) 法などを用いて行えばよい20。

## 【0208】

金属酸化物431、432を形成した後に、第1の加熱処理を行うと好ましい。第1の加熱処理は、250以上650以下、好ましくは450以上600以下、さらに好ましくは520以上570以下で行えばよい。第1の加熱処理は、不活性ガス雰囲気、または酸化性ガスを10ppm以上、1%以上もしくは10%以上含む雰囲気で行う。第1の加熱処理は減圧状態で行ってもよい。または、第1の加熱処理は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上、1%以上または10%以上含む雰囲気で加熱処理を行ってもよい。第1の加熱処理によって、金属酸化物431、432の結晶性を高めることや、水素や水などの不純物を除去することが可能になる。30

## 【0209】

上述の3層構造は一例である。例えば、金属酸化物431または金属酸化物433のない2層構造としても構わない。または、金属酸化物431の上もしくは下、または金属酸化物433上もしくは下に、金属酸化物431、金属酸化物432または金属酸化物433のいずれか一を有する4層構造としても構わない。または、金属酸化物431の上、金属酸化物431の下、金属酸化物433の上、金属酸化物433の下のいずれか二箇所以上に、金属酸化物431、金属酸化物432または金属酸化物433のいずれか一をそれぞれ有するn層構造(nは5以上の整数)としても構わない。

## 【0210】

## 基板

基板450としては、例えば、絶縁体基板、半導体基板または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板(イットリア安定化ジルコニア基板など)、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムなどの単体半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムからなる化合物半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えばS O I ( S i l i c o n O n I n s u l a t o r ) 基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。40

らには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてもよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。

#### 【0211】

また、基板450として、可とう性基板を用いてもよい。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板450に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。なお、基板450として、纖維を編みこんだシート、フィルムまたは箔などを用いてもよい。また、基板450が伸縮性を有してもよい。また、基板450は、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有してもよい。または、元の形状に戻らない性質を有してもよい。基板450の厚さは、例えば、5 μm以上700 μm以下、好ましくは10 μm以上500 μm以下、さらに好ましくは15 μm以上300 μm以下とする。基板450を薄くすると、半導体装置を軽量化することができる。また、基板450を薄くすることで、ガラスなどを用いた場合にも伸縮性を有する場合や、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有する場合がある。そのため、落下などによって基板450上の半導体装置に加わる衝撃などを緩和することができる。即ち、丈夫な半導体装置を提供することができる。

#### 【0212】

可とう性基板である基板450としては、例えば、金属、合金、樹脂もしくはガラス、またはそれらの纖維などを用いることができる。可とう性基板である基板450は、線膨張率が低いほど環境による変形が抑制されて好ましい。可とう性基板である基板450としては、例えば、線膨張率が $1 \times 10^{-3} / K$ 以下、 $5 \times 10^{-5} / K$ 以下、または $1 \times 10^{-5} / K$ 以下である材質を用いればよい。樹脂としては、例えば、ポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミドなど）、ポリイミド、ポリカーボネート、アクリル、ポリテトラフルオロエチレン（PTFE）などがある。特に、アラミドは、線膨張率が低いため、可とう性基板である基板450として好適である。

#### 【0213】

##### 下地絶縁膜

絶縁膜401は、基板450と導電膜414を電気的に分離させる機能を有する。

#### 【0214】

絶縁膜401又は絶縁膜402は、単層構造または積層構造の絶縁膜で形成される。絶縁膜を構成する材料には、例えば、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどがある。

#### 【0215】

また、絶縁膜402として、TEOS（Tetra-Ethyl-Ortho-Silicate）若しくはシラン等と、酸素若しくは亜酸化窒素等とを反応させて形成した段差被覆性の良い酸化シリコンを用いてもよい。

#### 【0216】

また、絶縁膜402を成膜した後、その上面の平坦性を高めるためにCMP法等を用いた平坦化処理を行ってもよい。

#### 【0217】

絶縁膜404は、酸化物を含むことが好ましい。特に加熱により一部の酸素が脱離する酸化物材料を含むことが好ましい。好適には、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物を用いることが好ましい。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物膜は、加熱により一部の酸素が脱離する。絶縁膜404から脱離した酸素は金属酸化物430に供給され、金属酸化物430の酸素欠損を低減することが可能となる

10

20

30

40

50

。その結果、トランジスタの電気特性の変動を抑制し、信頼性を高めることができる。

【0218】

化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物膜は、例えば、TDS ( Thermal Desorption Spectroscopy ) 分析にて、酸素原子に換算しての酸素の脱離量が  $1.0 \times 10^{18}$  atoms / cm<sup>3</sup> 以上、好ましくは  $3.0 \times 10^{20}$  atoms / cm<sup>3</sup> 以上である酸化物膜である。なお、上記 TDS 分析時における膜の表面温度としては 100 以上 700 以下、または 100 以上 500 以下の範囲が好ましい。

【0219】

絶縁膜 404 は、金属酸化物 430 に酸素を供給することができる酸化物を含むことが好ましい。例えば、酸化シリコンまたは酸化窒化シリコンを含む材料を用いることが好ましい。

【0220】

または、絶縁膜 404 として、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等の金属酸化物を用いてよい。

【0221】

絶縁膜 404 に酸素を過剰に含有させるためには、例えば酸素雰囲気下にて絶縁膜 404 の成膜を行えばよい。または、成膜後の絶縁膜 404 に酸素を導入して酸素を過剰に含有する領域を形成してもよく、双方の手段を組み合わせてもよい。

10

【0222】

例えば、成膜後の絶縁膜 404 に、酸素（少なくとも酸素ラジカル、酸素原子、酸素イオンのいずれかを含む）を導入して酸素を過剰に含有する領域を形成する。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理などを用いることができる。

【0223】

酸素導入処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、例えば酸素、亜酸化窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。また、酸素導入処理において、酸素を含むガスに希ガスを含ませてもよい。または、水素等を含ませてもよい。例えば、二酸化炭素、水素及びアルゴンの混合ガスを用いるとよい。

20

【0224】

また、絶縁膜 404 を成膜した後、その上面の平坦性を高めるために CMP 法等を用いた平坦化処理を行ってよい。

30

【0225】

絶縁膜 403 は、絶縁膜 404 に含まれる酸素が、導電膜 414 に含まれる金属と結びつき、絶縁膜 404 に含まれる酸素が減少することを防ぐバッシベーション機能を有する。

【0226】

絶縁膜 403 は、酸素、水素、水、アルカリ金属、アルカリ土類金属等のブロッキングできる機能を有する。絶縁膜 403 を設けることで、金属酸化物 430 からの酸素の外部への拡散と、外部から金属酸化物 430 への水素、水等の入り込みを防ぐことができる。

40

【0227】

絶縁膜 403 としては、例えば、窒化物絶縁膜を用いることができる。該窒化物絶縁膜としては、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。なお、窒化物絶縁膜の代わりに、酸素、水素、水等のブロッキング効果を有する酸化物絶縁膜を設けてよい。酸化物絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。

【0228】

トランジスタ 400a は、電荷捕獲層に電子を注入することで、しきい値電圧を制御する

50

ことが可能になる。電荷捕獲層は、絶縁膜402又は絶縁膜403に設けることが好ましい。例えば、絶縁膜403を酸化ハフニウム、酸化アルミニウム、酸化タンタル、アルミニウムシリケート等で形成することで、電荷捕獲層として機能させることができる。

#### 【0229】

##### ゲート電極

導電膜411乃至414として、銅(Cu)、タングステン(W)、モリブデン(Mo)、金(Au)、アルミニウム(Al)、マンガン(Mn)、チタン(Ti)、タンタル(Ta)、ニッケル(Ni)、クロム(Cr)、鉛(Pb)、錫(Sn)、鉄(Fe)、コバルト(Co)、ルテニウム(Ru)、白金( Pt)、イリジウム(Ir)、ストロンチウム(Sr)の低抵抗材料からなる単体、合金、またはこれらを主成分とする化合物を含む導電膜の単層または積層とすることが好ましい。特に、耐熱性と導電性を両立するタングステンやモリブデンなどの高融点材料を用いることが好ましい。また、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。さらに、Cu-Mn合金を用いると、酸素を含む絶縁体との界面に酸化マンガンを形成し、酸化マンガンがCuの拡散を抑制する機能を持つので好ましい。

10

#### 【0230】

##### ソース電極、ドレイン電極

導電膜421乃至424として、銅(Cu)、タングステン(W)、モリブデン(Mo)、金(Au)、アルミニウム(Al)、マンガン(Mn)、チタン(Ti)、タンタル(Ta)、ニッケル(Ni)、クロム(Cr)、鉛(Pb)、錫(Sn)、鉄(Fe)、コバルト(Co)、ルテニウム(Ru)、白金( Pt)、イリジウム(Ir)、ストロンチウム(Sr)の低抵抗材料からなる単体、合金、またはこれらを主成分とする化合物を含む導電膜の単層または積層とすることが好ましい。特に、耐熱性と導電性を両立するタングステンやモリブデンなどの高融点材料を用いることが好ましい。また、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。さらに、Cu-Mn合金を用いると、酸素を含む絶縁体との界面に酸化マンガンを形成し、酸化マンガンがCuの拡散を抑制する機能を持つので好ましい。

20

#### 【0231】

また、導電膜421乃至424には、酸化イリジウム、酸化ルテニウム、ストロンチウムルテナイトなど、貴金属を含む導電性酸化物を用いることが好ましい。これらの導電性酸化物は、酸化物半導体と接しても酸化物半導体から酸素を奪うことが少なく、酸化物半導体の酸素欠損を作りにくい。

30

#### 【0232】

##### 低抵抗領域

領域441、442は、例えば、導電膜421、423が、金属酸化物431、432の酸素を引き抜くことで形成される。酸素の引き抜きは、高い温度で加熱するほど起こりやすい。トランジスタの作製工程には、いくつかの加熱工程があることから、領域441、442には酸素欠損が形成される。また、加熱により該酸素欠損のサイトに水素が入り込み、領域441、442に含まれるキャリア濃度が増加する。その結果、領域441、442が低抵抗化する。

40

#### 【0233】

##### ゲート絶縁膜

絶縁膜406は、比誘電率の高い絶縁体を有することが好ましい。例えば、絶縁膜406は、酸化ガリウム、酸化ハフニウム、アルミニウムおよびハフニウムを有する酸化物、アルミニウムおよびハフニウムを有する酸化窒化物、シリコンおよびハフニウムを有する酸化物、またはシリコンおよびハフニウムを有する酸化窒化物などを有することが好ましい。

#### 【0234】

また、絶縁膜406は、酸化シリコンまたは酸化窒化シリコンと、比誘電率の高い絶縁体との積層構造を有することが好ましい。酸化シリコンおよび酸化窒化シリコンは、熱的

50

に安定であるため、比誘電率の高い絶縁体と組み合わせることで、熱的に安定かつ比誘電率の高い積層構造とすることができます。例えば、酸化アルミニウム、酸化ガリウムまたは酸化ハフニウムを金属酸化物 433 側に有することで、酸化シリコンまたは酸化窒化シリコンに含まれるシリコンが、金属酸化物 432 に混入することを抑制することができる。

【0235】

また、例えば、酸化シリコンまたは酸化窒化シリコンを金属酸化物 433 側に有することで、酸化アルミニウム、酸化ガリウムまたは酸化ハフニウムと、酸化シリコンまたは酸化窒化シリコンと、の界面にトラップセンターが形成される場合がある。該トラップセンターは、電子を捕獲することでトランジスタのしきい値電圧をプラス方向に変動させることができる場合がある。

10

【0236】

層間絶縁膜、保護絶縁膜

絶縁膜 405 は、比誘電率の低い絶縁体を有することが好ましい。例えば、絶縁膜 405 は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコンまたは樹脂などを有することが好ましい。または、絶縁膜 405 は、酸化シリコンまたは酸化窒化シリコンと、樹脂と、の積層構造を有することが好ましい。酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため、樹脂と組み合わせることで、熱的に安定かつ比誘電率の低い積層構造とすることができます。樹脂としては、例えば、ポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミドなど）、ポリイミド、ポリカーボネートまたはアクリルなどがある。

20

【0237】

絶縁膜 407 は、酸素、水素、水、アルカリ金属、アルカリ土類金属等のプロッキングできる機能を有する。絶縁膜 407 を設けることで、金属酸化物 430 からの酸素の外部への拡散と、外部から金属酸化物 430 への水素、水等の入り込みを防ぐことができる。

【0238】

絶縁膜 407 としては、例えば、窒化物絶縁膜を用いることができる。該窒化物絶縁膜としては、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。なお、窒化物絶縁膜の代わりに、酸素、水素、水等のプロッキング効果を有する酸化物絶縁膜を設けてもよい。酸化物絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。

30

【0239】

酸化アルミニウム膜は、水素、水分などの不純物、および酸素の両方に対して膜を透過させない遮断効果が高いので絶縁膜 407 に適用するのに好ましい。

【0240】

絶縁膜 407 は、スパッタリング法、CVD 法など酸素を含むプラズマを用いて成膜することで、絶縁膜 405、406 の側面及び表面に、酸素を添加することが可能になる。また、絶縁膜 407 を成膜した後、何れかのタイミングにおいて、第 2 の加熱処理を行うことが好ましい。第 2 の加熱処理によって、絶縁膜 405、406 に添加された酸素が、絶縁膜中を拡散し、金属酸化物 430 に到達し、金属酸化物 430 の酸素欠損を低減することが可能になる。

40

【0241】

図 22 (A)、(B) は、絶縁膜 407 を成膜する際に絶縁膜 405、406 に添加された酸素が、第 2 の加熱処理によって絶縁膜中を拡散し、金属酸化物 430 に到達する様子を描いた模式図である。図 22 (A) は、図 20 (B) の断面図において、酸素が拡散する様子を矢印で示している。同様に、図 22 (B) は、図 20 (C) の断面図において、酸素が拡散する様子を矢印で示している。

【0242】

図 22 (A)、(B) に示すように、絶縁膜 406 の側面に添加された酸素が、絶縁膜 406 の内部を拡散し、金属酸化物 430 に到達する。また、絶縁膜 407 と絶縁膜 405

50

の界面近傍に、酸素を過剰に含む領域 4 6 1、領域 4 6 2 及び領域 4 6 3 が形成される場合がある。領域 4 6 1 乃至 4 6 3 に含まれる酸素は、絶縁膜 4 0 5、絶縁膜 4 0 4 を経由し、金属酸化物 4 3 0 に到達する。絶縁膜 4 0 5 が酸化シリコンを含み、絶縁膜 4 0 7 が酸化アルミニウムを含む場合、領域 4 6 1 乃至 4 6 3 は、シリコンとアルミニウムと酸素の混合層が形成される場合がある。

【 0 2 4 3 】

絶縁膜 4 0 7 は、酸素をブロックする機能を有し、酸素が絶縁膜 4 0 7 より上方に拡散することを防ぐ。同様に、絶縁膜 4 0 3 は、酸素をブロックする機能を有し、酸素が絶縁膜 4 0 3 より下方に拡散することを防ぐ。

【 0 2 4 4 】

なお、第 2 の加熱処理は、絶縁膜 4 0 5、4 0 6 に添加された酸素が金属酸化物 4 3 0 まで拡散する温度で行えばよい。例えば、第 1 の加熱処理についての記載を参照しても構わない。または、第 2 の加熱処理は、第 1 の加熱処理よりも低い温度が好ましい。第 1 の加熱処理と第 2 の加熱処理の温度差は、20 以上 150 以下、好ましくは 40 以上 100 以下とする。これにより、絶縁膜 4 0 4 から余分に酸素が放出することを抑えることができる。なお、第 2 の加熱処理は、同等の加熱処理を各層の成膜時の加熱によって兼ねることができる場合、行わなくてもよい場合がある。

【 0 2 4 5 】

このように、金属酸化物 4 3 0 は、絶縁膜 4 0 7 の成膜及び第 2 の加熱処理によって、上下方向から酸素が供給されることが可能になる。

【 0 2 4 6 】

また、In - M - Zn 酸化物など、酸化インジウムを含む膜を絶縁膜 4 0 7 として成膜することで、絶縁膜 4 0 5、4 0 6 に酸素を添加してもよい。

【 0 2 4 7 】

絶縁膜 4 0 8 には、酸化アルミニウム、窒化酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどから選ばれた一種以上含む絶縁体を用いることができる。また、絶縁膜 4 0 8 には、ポリイミド樹脂、ポリアミド樹脂、アクリル樹脂、シロキサン樹脂、エポキシ樹脂、フェノール樹脂等の樹脂を用いることもできる。また、絶縁膜 4 0 8 は上記材料の積層であってもよい。

【 0 2 4 8 】

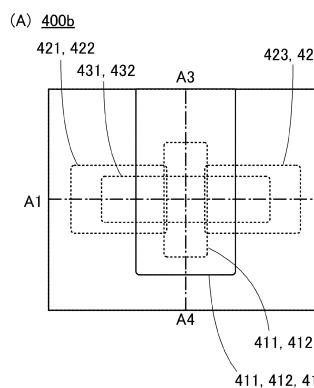

トランジスタの構成例 2

図 2 0 に示すトランジスタ 4 0 0 a は、導電膜 4 1 4 及び絶縁膜 4 0 2、4 0 3 を省略してもよい。その場合の例を図 2 3 に示す。

【 0 2 4 9 】

図 2 3 ( A ) 乃至 ( C ) は、トランジスタ 4 0 0 b の上面図および断面図である。図 2 3 ( A ) は上面図である。図 2 3 ( B ) は、図 2 3 ( A ) に示す一点鎖線 A 1 - A 2 に対応する断面図であり、図 2 3 ( C ) は、図 2 3 ( A ) に示す一点鎖線 A 3 - A 4 に対応する断面図である。なお、図 2 3 ( A ) の上面図では、図の明瞭化のために一部の要素を省いて図示している。なお、一点鎖線 A 1 - A 2 をトランジスタ 4 0 0 b のチャネル長方向、一点鎖線 A 3 - A 4 をトランジスタ 4 0 0 b のチャネル幅方向と呼ぶ場合がある。

【 0 2 5 0 】

トランジスタの構成例 3

図 2 0 に示すトランジスタ 4 0 0 a において、導電膜 4 2 1、4 2 3 は、ゲート電極 (導電膜 4 1 1 乃至 4 1 3 ) と重なる部分の膜厚を薄くしてもよい。その場合の例を図 2 4 に示す。

【 0 2 5 1 】

図 2 4 ( A ) 乃至 ( C ) は、トランジスタ 4 0 0 c の上面図および断面図である。図 2 4 ( A ) は上面図である。図 2 4 ( B ) は、図 2 4 ( A ) に示す一点鎖線 A 1 - A 2 に対応

10

20

30

40

50

する断面図であり、図24(C)は、図24(A)に示す一点鎖線A3-A4に対応する断面図である。なお、図24(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。なお、一点鎖線A1-A2をトランジスタ400cのチャネル長方向、一点鎖線A3-A4をトランジスタ400cのチャネル幅方向と呼ぶ場合がある。

【0252】

図24(B)のトランジスタ400cにおいて、ゲート電極と重なる部分の導電膜421が薄膜化され、その上を導電膜422が覆っている。同様に、ゲート電極と重なる部分の導電膜423が薄膜化され、その上を導電膜424が覆っている。

【0253】

トランジスタ400cは、図24(B)に示すような構成にすることで、ゲート電極とソース電極との間の距離、又は、ゲート電極とドレイン電極との間の距離を長くすることが可能になり、ゲート電極とソース電極及びドレイン電極との間に形成される寄生容量を低減することが可能になる。その結果、高速動作が可能なトランジスタを得ることが可能になる。

【0254】

トランジスタの構成例4

図24に示すトランジスタ400cにおいて、A3-A4方向に、金属酸化物431、432の幅を広げてもよい。その場合の例を図25に示す。

【0255】

図25(A)乃至(C)は、トランジスタ400dの上面図および断面図である。図25(A)は上面図である。図25(B)は、図25(A)に示す一点鎖線A1-A2に対応する断面図であり、図25(C)は、図25(A)に示す一点鎖線A3-A4に対応する断面図である。なお、図25(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。なお、一点鎖線A1-A2をトランジスタ400dのチャネル長方向、一点鎖線A3-A4をトランジスタ400dのチャネル幅方向と呼ぶ場合がある。

【0256】

トランジスタ400dは、図25に示す構成にすることで、オン電流を増大させることが可能になる。

【0257】

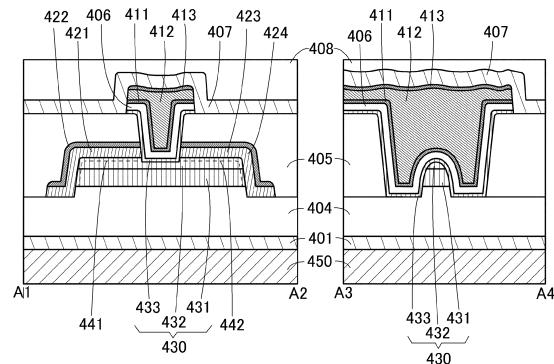

トランジスタの構成例5

図24に示すトランジスタ400cにおいて、A3-A4方向に、金属酸化物431、432から成る領域(以下、フィンと呼ぶ)を複数設けてよい。その場合の例を図26に示す。

【0258】

図26(A)乃至(C)は、トランジスタ400eの上面図および断面図である。図26(A)は上面図である。図26(B)は、図26(A)に示す一点鎖線A1-A2に対応する断面図であり、図26(C)は、図26(A)に示す一点鎖線A3-A4に対応する断面図である。なお、図26(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。なお、一点鎖線A1-A2をトランジスタ400eのチャネル長方向、一点鎖線A3-A4をトランジスタ400eのチャネル幅方向と呼ぶ場合がある。

【0259】

トランジスタ400eは、金属酸化物431a、432aから成る第1のフィンと、金属酸化物431b、432bから成る第2のフィンと、金属酸化物431c、432cから成る第3のフィンと、を有している。

【0260】

トランジスタ400eは、チャネルが形成される金属酸化物432a乃至432cを、ゲート電極が取り囲むことで、チャネル全体にゲート電界を印加することが可能になり、オン電流が高いトランジスタを得ることが可能になる。

【0261】

トランジスタの構成例6

10

20

30

40

50

図27(A)及び図27(B)は、トランジスタ680の上面図および断面図である。図27(A)は上面図であり、図27(A)に示す一点鎖線A-B方向の断面が図27(B)に相当する。なお、図27(A)及び図27(B)では、図の明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線A-B方向をチャネル長方向と呼称する場合がある。

【0262】

図27(B)に示すトランジスタ680は、第1のゲートとして機能する導電膜689と、第2のゲートとして機能する導電膜688と、半導体682と、ソース及びドレインとして機能する導電膜683及び導電膜684と、絶縁膜681と、絶縁膜685と、絶縁膜686と、絶縁膜687と、を有する。

10

【0263】

導電膜689は、絶縁表面上に設けられる。導電膜689と、半導体682とは、絶縁膜681を間に挟んで、互いに重なる。また、導電膜688と、半導体682とは、絶縁膜685、絶縁膜686及び絶縁膜687を間に挟んで、互いに重なる。また、導電膜683及び導電膜684は、半導体682に、接続されている。

【0264】

導電膜689及び導電膜688の詳細は、図20に示す導電膜411乃至414の記載を参照すればよい。

【0265】

導電膜689と導電膜688は、異なる電位が与えられてもよいし、同時に同じ電位が与えられてもよい。トランジスタ680は、第2のゲート電極として機能する導電膜688を設けることで、しきい値を安定化させることが可能になる。なお、導電膜688は、場合によっては省略してもよい。

20

【0266】

半導体682の詳細は、図20に示す金属酸化物432の記載を参照すればよい。また、半導体682は、一層でも良いし、複数の半導体層の積層でも良い。

【0267】

導電膜683及び導電膜684の詳細は、図20に示す導電膜421乃至424の記載を参照すればよい。

【0268】

30

絶縁膜681の詳細は、図20に示す絶縁膜406の記載を参照すればよい。

【0269】

なお、図27(B)では、半導体682、導電膜683及び導電膜684上に、順に積層された絶縁膜685乃至絶縁膜687が設けられている場合を例示しているが、半導体682、導電膜683及び導電膜684上に設けられる絶縁膜は、一層でも良いし、複数の絶縁膜の積層でも良い。

【0270】

半導体682に酸化物半導体を用いた場合、絶縁膜686は、化学量論的組成以上の酸素が含まれており、加熱により上記酸素の一部を半導体682に供給する機能を有する絶縁膜であることが望ましい。ただし、絶縁膜686を半導体682上に直接設けると、絶縁膜686の形成時に半導体682にダメージが与えられる場合、図27(B)に示すように、絶縁膜685を半導体682と絶縁膜686の間に設けると良い。絶縁膜685は、その形成時に半導体682に与えるダメージが絶縁膜686の場合よりも小さく、なおかつ、酸素を透過する機能を有する絶縁膜であることが望ましい。ただし、半導体682に与えられるダメージを小さく抑えつつ、半導体682上に絶縁膜686を直接形成することができるのであれば、絶縁膜685は必ずしも設けなくとも良い。

40

【0271】

例えば、絶縁膜686及び絶縁膜685として、酸化シリコンまたは酸化窒化シリコンを含む材料を用いることが好ましい。または、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフ

50

ニウム、酸化窒化ハフニウム等の金属酸化物を用いることもできる。

【0272】

絶縁膜687は、酸素、水素、水の拡散を防ぐブロッキング効果を有することが、望ましい。或いは、絶縁膜687は、水素、水の拡散を防ぐブロッキング効果を有することが、望ましい。

【0273】

絶縁膜は、密度が高くて緻密である程、また未結合手が少なく化学的に安定である程、より高いブロッキング効果を示す。酸素、水素、水の拡散を防ぐブロッキング効果を示す絶縁膜は、例えば、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等を用いて、形成することができる。水素、水の拡散を防ぐブロッキング効果を示す絶縁膜は、例えば、窒化シリコン、窒化酸化シリコン等を用いることができる。

10

【0274】

絶縁膜687が水、水素などの拡散を防ぐブロッキング効果を有する場合、パネル内の樹脂や、パネルの外部に存在する水、水素などの不純物が、半導体682に侵入するのを防ぐことができる。半導体682に酸化物半導体を用いる場合、酸化物半導体に侵入した水または水素の一部は電子供与体（ドナー）となるため、上記ブロッキング効果を有する絶縁膜687を用いることで、トランジスタ680の閾値電圧がドナーの生成によりシフトするのを防ぐことができる。

20

【0275】

また、半導体682に酸化物半導体を用いる場合、絶縁膜687が酸素の拡散を防ぐブロッキング効果を有することで、酸化物半導体からの酸素が外部に拡散するのを防ぐことができる。よって、酸化物半導体中において、ドナーとなる酸素欠損が低減されるので、トランジスタ680の閾値電圧がドナーの生成によりシフトするのを防ぐことができる。

【0276】

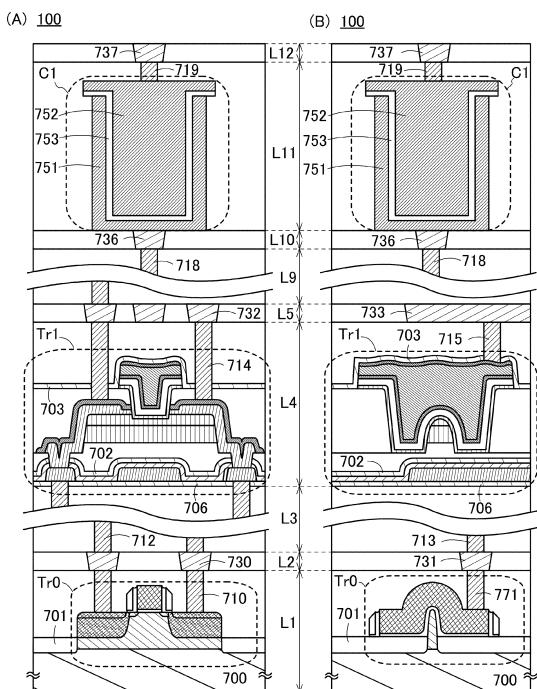

（実施の形態4）

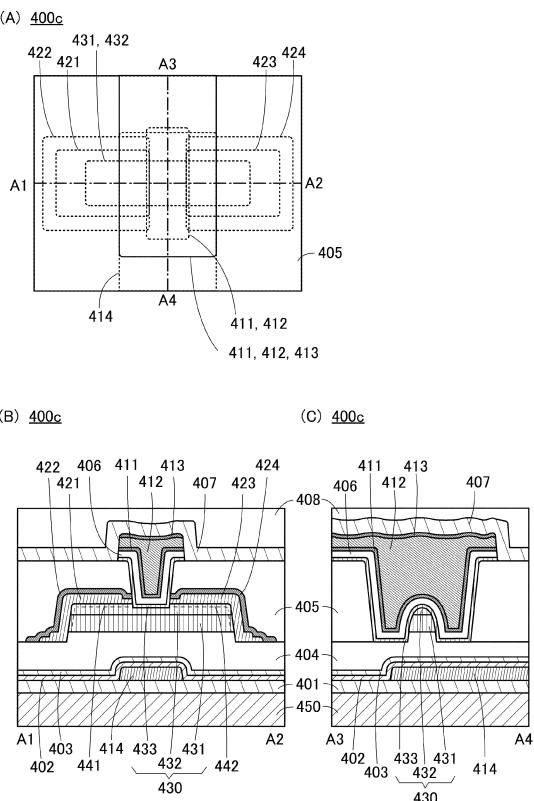

本実施の形態では、上記実施の形態に示すメモリセル100a乃至100k（以下、まとめてメモリセル100と呼称する）に適用可能なデバイスの構成例について、図28乃至図31を用いて説明を行う。

【0277】

30

チップ構成例1

図28（A）、（B）に示す断面図はメモリセル100が1つのチップに形成された例を示している。図28（A）は、メモリセル100を構成するトランジスタのチャネル長方向の断面図を表している。また、図28（B）は、メモリセル100を構成するトランジスタのチャネル幅方向の断面図を表している。

【0278】

図28（A）、（B）に示すメモリセル100は、下から順に、層L1、L2、L3、L4、L5、L6、L7、L8、L9、L10、L11、L12を有している。

【0279】

層L1は、基板700と、基板700に形成されたトランジスタTr0と、素子分離層701と、プラグ710、711などの複数のプラグを有する。

40

【0280】

層L2は、配線730、731などの複数の配線を有する。

【0281】

層L3は、プラグ712、713などの複数のプラグと、複数の配線（図示せず）を有する。

【0282】

層L4は、絶縁膜706と、トランジスタTr1と、絶縁膜702と、絶縁膜703と、プラグ714、715などの複数のプラグを有する。

【0283】

50

層 L 5 は、配線 732、733 などの複数の配線を有する。

【0284】

層 L 6 は、プラグ 716 などの複数のプラグを有する。

【0285】

層 L 7 は、トランジスタ Tr 2 と、絶縁膜 704、705 と、プラグ 717 などの複数のプラグを有する。

【0286】

層 L 8 は、配線 734、735 などの複数の配線を有する。

【0287】

層 L 9 は、プラグ 718 などの複数のプラグと、複数の配線（図示せず）を有する。

10

【0288】

層 L 10 は、配線 736 などの複数の配線を有する。

【0289】

層 L 11 は、容量素子 C1 と、容量素子 C2 乃至 Cn（図示せず）と、プラグ 719 などの複数のプラグとを有している。また、容量素子 C1 は、第1の電極 751 と、第2の電極 752 と、絶縁膜 753 と、を有している。

【0290】

層 L 12 は、配線 737 などの複数の配線を有している。

【0291】

トランジスタ Tr 1、Tr 2 は、実施の形態 3 に示した OS トランジスタを適用することが好ましい。図 28 (A)、(B) は、トランジスタ Tr 1、Tr 2 に、図 24 (A) 乃至 (B) に示すトランジスタ 400c を適用した例を示している。

20

【0292】

トランジスタ Tr 0 は、トランジスタ Tr 1、Tr 2 とは異なる半導体材料で形成されることが好ましい。図 28 (A)、(B) では、トランジスタ Tr 0 に Si トランジスタを適用した例を示している。

【0293】

基板 700 としては、シリコンや炭化シリコンからなる単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムからなる化合物半導体基板や、SOI 基板などを用いることができる。

30

【0294】

また、基板 700 として、例えば、ガラス基板、石英基板、プラスチック基板、金属基板、可撓性基板、貼り合わせフィルム、纖維状の材料を含む紙、又は基材フィルム、などを用いてもよい。また、ある基板を用いて半導体素子を形成し、その後、別の基板に半導体素子を転置してもよい。図 28 (A)、(B) では、一例として、基板 700 に単結晶シリコンウェハを用いた例を示している。

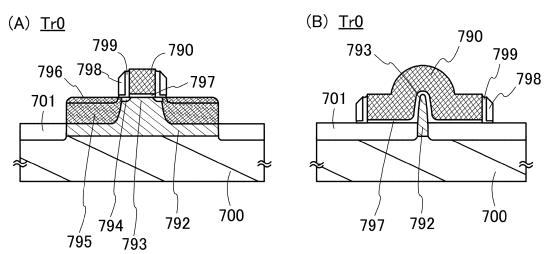

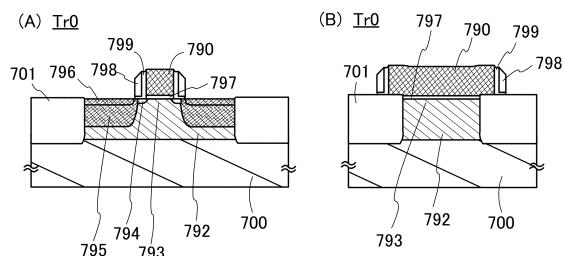

【0295】

図 30 (A)、(B) を用いて、トランジスタ Tr 0 の詳細について説明を行う。図 30 (A) はトランジスタ Tr 0 のチャネル長方向の断面図を示し、図 30 (B) はトランジスタ Tr 0 のチャネル幅方向の断面図を示している。トランジスタ Tr 0 は、ウェル 792 に設けられたチャネル形成領域 793 と、低濃度不純物領域 794 及び高濃度不純物領域 795（これらを合わせて単に不純物領域とも呼ぶ）と、該不純物領域に接して設けられた導電性領域 796 と、チャネル形成領域 793 上に設けられたゲート絶縁膜 797 と、ゲート絶縁膜 797 上に設けられたゲート電極 790 と、ゲート電極 790 の側面に設けられた側壁絶縁層 798、799 とを有する。なお、導電性領域 796 には、金属シリサイド等を用いてもよい。

40

【0296】

図 30 (B) において、トランジスタ Tr 0 はチャネル形成領域 793 が凸形状を有し、その側面及び上面に沿ってゲート絶縁膜 797 及びゲート電極 790 が設けられている。このような形状を有するトランジスタを FIN 型トランジスタと呼ぶ。本実施の形態では

50

、半導体基板の一部を加工して凸部を形成する場合を示したが、S O I 基板を加工して凸形状を有する半導体層を形成してもよい。

【0297】

なお、トランジスタTr0は、FIN型トランジスタに限定されず、図31(A)、(B)に示すプレーナー型トランジスタを用いてもよい。図31(A)は、トランジスタTr0のチャネル長方向の断面図を示し、図31(B)はトランジスタTr0のチャネル幅方向の断面図を示している。図31に示す符号は、図30に示す符号と同一である。

【0298】

図28(A)、(B)において、絶縁膜702乃至706は、水素、水等に対するプロッキング効果を有することが好ましい。水、水素等は酸化物半導体中にキャリアを生成する要因の一つであるので、水素、水等に対するプロッキング層を設けることにより、トランジスタM1乃至Mnの信頼性を向上させることが可能になる。水素、水等に対するプロッキング効果を有する絶縁物には、例えば、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム、イットリア安定化ジルコニア(YSZ)等がある。

10

【0299】

配線730乃至737、及び、プラグ710乃至719には、銅(Cu)、タングステン(W)、モリブデン(Mo)、金(Au)、アルミニウム(Al)、マンガン(Mn)、チタン(Ti)、タンタル(Ta)、ニッケル(Ni)、クロム(Cr)、鉛(Pb)、錫(Sn)、鉄(Fe)、コバルト(Co)の低抵抗材料からなる単体、もしくは合金、またはこれらを主成分とする化合物を含む導電膜の単層または積層とすることが好ましい。特に、耐熱性と導電性を両立するタングステンやモリブデンなどの高融点材料を用いることが好ましい。また、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。さらに、Cu-Mn合金を用いると、酸素を含む絶縁体との界面に酸化マンガンを形成し、酸化マンガンがCuの拡散を抑制する機能を持つので好ましい。

20

【0300】

図28において、符号及びハッチングパターンが与えられていない領域は、絶縁体で構成されている。上記絶縁体には、酸化アルミニウム、窒化酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどから選ばれた一種以上の材料を含む絶縁体を用いることができる。また、当該領域には、ポリイミド樹脂、ポリアミド樹脂、アクリル樹脂、シロキサン樹脂、エポキシ樹脂、フェノール樹脂等の有機樹脂を用いることもできる。なお、本明細書において、酸化窒化物とは、窒素よりも酸素の含有量が多い化合物をいい、窒化酸化物とは、酸素よりも窒素の含有量が多い化合物をいう。

30

【0301】

実施の形態1又は実施の形態2に示すトランジスタM1乃至MnにOSトランジスタを適用した場合、トランジスタM1乃至Mnは、層L4又は層L7に形成されることが好ましい。

40

【0302】

実施の形態1又は実施の形態2に示すトランジスタM0にSiトランジスタを適用した場合、トランジスタM0は層L1に形成されることが好ましい。

【0303】

実施の形態1又は実施の形態2に示すトランジスタM0にOSトランジスタを適用した場合、トランジスタM0は層L4又は層L7に形成されることが好ましい。

【0304】

メモリセル100の周辺に形成される駆動回路をOSトランジスタで形成する場合、該OSトランジスタは層L4又は層L7に形成してもよい。

【0305】

メモリセル100の周辺に形成される駆動回路をSiトランジスタで形成する場合、該Si

50

iトランジスタは層L1に形成してもよい。

【0306】

メモリセル100は、図28に示す構成にすることで、占有面積を小さくし、メモリセルを高集積化することが可能になる。

【0307】

チップ構成例2

メモリセル100は、メモリセル100が有する全てのOSトランジスタを、同一の層に形成してもよい。その場合の例を、図29(A)、(B)に示す。図28と同様に、図29(A)はメモリセル100を構成するトランジスタのチャネル長方向の断面図を表し、図29(B)はメモリセル100を構成するトランジスタのチャネル幅方向の断面図を表している。

10

【0308】

図29(A)、(B)は、層L6乃至L8が省かれ、層L5の上に層L9が形成されている点で、図28(A)、(B)に示す断面図と相違する。図29(A)、(B)のその他の詳細は、図28(A)、(B)の記載を参照する。

【0309】

実施の形態1又は実施の形態2に示すトランジスタM1乃至MnにOSトランジスタを適用した場合、トランジスタM1乃至Mnは、層L4に形成されることが好ましい。

20

【0310】

実施の形態1又は実施の形態2に示すトランジスタM0にSiトランジスタを適用した場合、トランジスタM0は層L1に形成されることが好ましい。

【0311】

実施の形態1又は実施の形態2に示すトランジスタM0にOSトランジスタを適用した場合、トランジスタM0は層L4に形成されることが好ましい。

【0312】

メモリセル100の周辺に形成される駆動回路をOSトランジスタで形成する場合、該OSトランジスタは層L4に形成してもよい。

30

【0313】

メモリセル100の周辺に形成される駆動回路をSiトランジスタで形成する場合、該Siトランジスタは層L1に形成してもよい。

【0314】

メモリセル100は、図29(A)、(B)に示す構成にすることで、製造工程を単純化することが可能になる。

【0315】

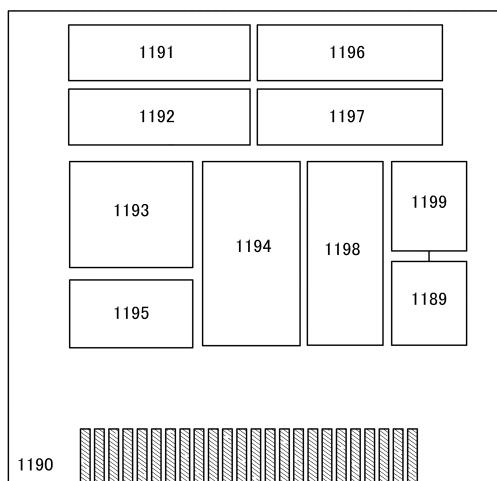

(実施の形態5)

本実施の形態では、上記実施の形態に示したメモリセル及び記憶装置を用いることが可能なCPUについて説明する。

【0316】

図32は、CPUの一例の構成を示すブロック図である。

40

【0317】

図32に示すCPUは、基板1190上に、ALU1191(ALU: Arithmetic logic unit、演算回路)、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース1198(Bus I/F)、書き換え可能なROM1199、およびROMインターフェース1189(ROM I/F)を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてよい。もちろん、図32に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。例えば、図32に示すCPUまたは演算回路を含む構成を一つのコアとし、当該コアを複数含

50

み、それぞれのコアが並列で動作するような構成としてもよい。また、CPUが内部演算回路やデータバスで扱えるビット数は、例えば8ビット、16ビット、32ビット、64ビットなどとすることができます。

【0318】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

【0319】

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

10

【0320】

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号を元に、内部クロック信号を生成する内部クロック生成部を備えており、内部クロック信号を上記各種回路に供給する。

20

【0321】

図32に示すCPUでは、レジスタ1196に、上記実施の形態に示すメモリセルを用いることが可能である。

【0322】

(実施の形態6)

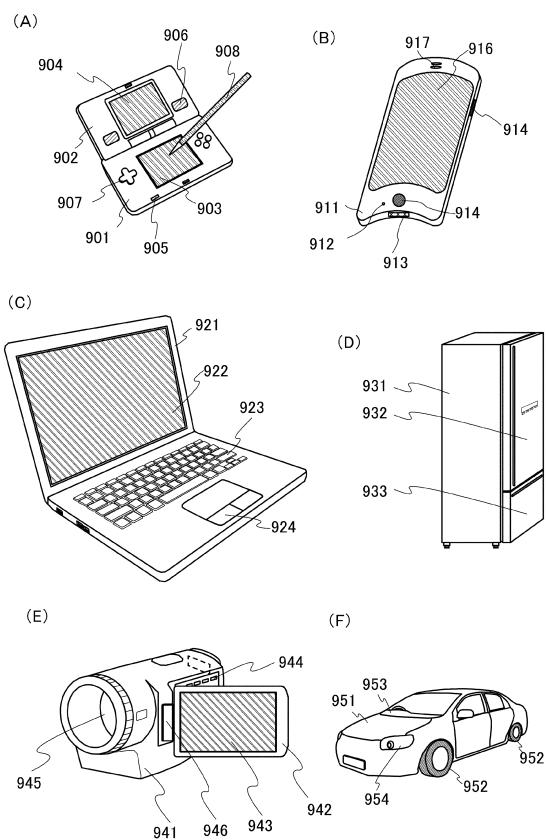

本発明の一態様に係る記憶装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る記憶装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯データ端末、電子書籍端末、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図33に示す。

30

【0323】

図33（A）は携帯型ゲーム機であり、筐体901、筐体902、表示部903、表示部904、マイクロフォン905、スピーカ906、操作キー907、スタイルス908等を有する。なお、図33（A）に示した携帯型ゲーム機は、2つの表示部903と表示部904とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

40

【0324】

図33（B）は、携帯電話機であり、筐体911、表示部916、操作ボタン914、外部接続ポート913、スピーカ917、マイク912などを備えている。図33（B）に示す携帯電話機は、指などで表示部916に触れることで、情報を入力することができる。また、電話を掛ける、或いは文字を入力するなどのあらゆる操作は、指などで表示部916に触れることにより行うことができる。また、操作ボタン914の操作により、電源のON、OFF動作や、表示部916に表示される画像の種類を切り替えることができる。例えば、メール作成画面から、メインメニュー画面に切り替えることができる。

【0325】

50

図33( C )はノート型パーソナルコンピュータであり、筐体921、表示部922、キーボード923、ポインティングデバイス924等を有する。

【0326】

図33( D )は電気冷凍冷蔵庫であり、筐体931、冷蔵室用扉932、冷凍室用扉933等を有する。

【0327】

図33( E )はビデオカメラであり、第1筐体941、第2筐体942、表示部943、操作キー944、レンズ945、接続部946等を有する。操作キー944およびレンズ945は第1筐体941に設けられており、表示部943は第2筐体942に設けられている。そして、第1筐体941と第2筐体942とは、接続部946により接続されており、第1筐体941と第2筐体942の間の角度は、接続部946により変更が可能である。表示部943における映像を、接続部946における第1筐体941と第2筐体942との間の角度に従って切り替える構成としても良い。

10

【0328】

図33( F )は自動車であり、車体951、車輪952、ダッシュボード953、ライト954等を有する。

【0329】

次に、本発明の一態様の半導体装置又は記憶装置を備えることができる表示装置の使用例について説明する。一例としては、表示装置は、画素を有する。画素は、例えば、トランジスタや表示素子を有する。または、表示装置は、画素を駆動する駆動回路を有する。駆動回路は、例えば、トランジスタを有する。例えば、これらのトランジスタとして、他の実施の形態で述べたトランジスタを採用することができる。

20

【0330】

例えば、本明細書等において、表示素子、表示素子を有する装置である表示装置、発光素子、及び発光素子を有する装置である発光装置は、様々な形態を用いること、又は様々な素子を有することが出来る。表示素子、表示装置、発光素子又は発光装置は、例えば、EL(エレクトロルミネッセンス)素子(有機物及び無機物を含むEL素子、有機EL素子、無機EL素子)、LEDチップ(白色LEDチップ、赤色LEDチップ、緑色LEDチップ、青色LEDチップなど)、トランジスタ(電流に応じて発光するトランジスタ)、プラズマディスプレイ(PDP)、電子放出素子、カーボンナノチューブを用いた表示素子、液晶素子、電子インク、エレクトロウェッティング素子、電気泳動素子、MEMS(マイクロ・エレクトロ・メカニカル・システム)を用いた表示素子(例えば、グレーティングライトバルブ(GLV)、デジタルマイクロミラーデバイス(DMD)、DMS(デジタル・マイクロ・シャッター)、MIRASOL(登録商標)、IMOD(インターフェアレンス・モジュレーション)素子、シャッター方式のMEMS表示素子、光干渉方式のMEMS表示素子、圧電セラミックディスプレイなど)、または、量子ドットなどの少なくとも一つを有している。これらの他にも、表示素子、表示装置、発光素子又は発光装置は、電気的または磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有していてもよい。EL素子を用いた表示装置の一例としては、ELディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッショニングディスプレイ(FED)又はSED方式平面型ディスプレイ(SED:Surface-conduction Electron-emitter Display)などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ(透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ)などがある。電子インク、電子粉流体(登録商標)、又は電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。量子ドットを各画素に用いた表示装置の一例としては、量子ドットディスプレイなどがある。なお、量子ドットは、表示素子としてではなく、バックライトの一部に設けてよい。量子ドットを用いることにより、色純度の高い表示を行うことができる。なお、半透過型液晶ディスプレイや反射型液晶ディスプレイを実現する場合には、画素電極の一部、または、全部

30

40

50

が、反射電極としての機能を有するようにすればよい。例えば、画素電極の一部、または全部が、アルミニウム、銀、などを有するようにすればよい。さらに、その場合、反射電極の下に、S R A Mなどの記憶回路を設けることも可能である。これにより、さらに、消費電力を低減することができる。なお、L E Dチップを用いる場合、L E Dチップの電極や窒化物半導体の下に、グラフェンやグラファイトを配置してもよい。グラフェンやグラファイトは、複数の層を重ねて、多層膜としてもよい。このように、グラフェンやグラファイトを設けることにより、その上に、窒化物半導体、例えば、結晶を有するn型G a N半導体層などを容易に成膜することができる。さらに、その上に、結晶を有するp型G a N半導体層などを設けて、L E Dチップを構成することができる。なお、グラフェンやグラファイトと、結晶を有するn型G a N半導体層との間に、A l N層を設けてもよい。なお、L E Dチップが有するG a N半導体層は、M O C V Dで成膜してもよい。ただし、グラフェンを設けることにより、L E Dチップが有するG a N半導体層は、スパッタ法で成膜することも可能である。また、M E M S（マイクロ・エレクトロ・メカニカル・システム）を用いた表示素子においては、表示素子が封止されている空間（例えば、表示素子が配置されている素子基板と、素子基板に対向して配置されている対向基板との間）に、乾燥剤を配置してもよい。乾燥剤を配置することにより、M E M Sなどが水分によって動きにくくなることや、劣化しやすくなることを防止することができる。

### 【0331】

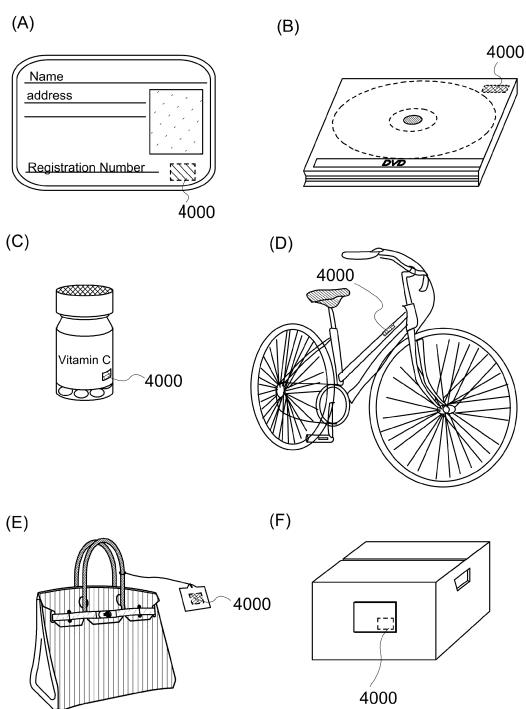

#### （実施の形態7）

本実施の形態では、本発明の一態様の記憶装置を備えることができるR Fタグの使用例について図34を用いながら説明する。R Fタグの用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類（運転免許証や住民票等、図34（A）参照）、記録媒体（D V Dやビデオテープ等、図34（B）参照）、包装用容器類（包装紙やボトル等、図34（C）参照）、乗り物類（自転車等、図34（D）参照）、身の回り品（鞄や眼鏡等）、食品類、植物類、動物類、人体、衣類、生活用品類、薬品や薬剤を含む医療品、または電子機器（液晶表示装置、E L表示装置、テレビジョン装置、または携帯電話）等の物品、若しくは各物品に取り付ける荷札（図34（E）、図34（F）参照）等に設けて使用することができる。

### 【0332】

本発明の一態様に係るR Fタグ4000は、表面に貼る、または埋め込むことにより、物品に固定される。例えば、本であれば紙に埋め込み、有機樹脂からなるパッケージであれば当該有機樹脂の内部に埋め込み、各物品に固定される。本発明の一態様に係るR Fタグ4000は、小型、薄型、軽量を実現するため、物品に固定した後もその物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、または証書類等に本発明の一態様に係るR Fタグ4000を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、または電子機器等に本発明の一態様に係るR Fタグを取り付けることにより、検品システム等のシステムの効率化を図ることができる。また、乗り物類であっても、本発明の一態様に係るR Fタグを取り付けることにより、盗難などに対するセキュリティ性を高めることができる。

### 【0333】

以上のように、本発明の一態様に係わるR Fタグを本実施の形態に挙げた各用途に用いることにより、情報の書き込みや読み出しを含む動作電力を低減できるため、最大通信距離を長くとることが可能となる。また、電力が遮断された状態であっても情報を極めて長い期間保持可能であるため、書き込みや読み出しの頻度が低い用途にも好適に用いることができる。

### 【0334】

#### （実施の形態8）

本実施の形態では、上記実施の形態で説明したO Sトランジスタに適用可能な酸化物半導体膜の構造について説明する。

10

20

30

40

50

## 【0335】

本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「略平行」とは、二つの直線が-30°以上30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。

## 【0336】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

10

## 【0337】

## 酸化物半導体の構造

以下では、酸化物半導体の構造について説明する。

## 【0338】

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体とに分けられる。非単結晶酸化物半導体としては、C AAC - OS (C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、nc - OS (nanocrystalline Oxide Semiconductor)、擬似非晶質酸化物半導体 (a - like OS: amorphous like Oxide Semiconductor)、非晶質酸化物半導体などがある。

20

## 【0339】

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体とに分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、C AAC - OS、多結晶酸化物半導体、nc - OSなどがある。

## 【0340】

非晶質構造の定義としては、一般に、準安定状態で固定化していないこと、等方的であって不均質構造を持たないことなどが知られている。また、結合角度が柔軟であり、短距離秩序性は有するが、長距離秩序性を有さない構造と言い換えることもできる。

## 【0341】

逆の見方をすると、本質的に安定な酸化物半導体の場合、完全な非晶質 (complete amorphous) 酸化物半導体と呼ぶことはできない。また、等方的でない (例えば、微小な領域において周期構造を有する) 酸化物半導体を、完全な非晶質酸化物半導体と呼ぶことはできない。ただし、a - like OSは、微小な領域において周期構造を有するものの、鬆 (ボイドともいう。) を有し、不安定な構造である。そのため、物性的には非晶質酸化物半導体に近いといえる。

30

## 【0342】

## C AAC - OS

まずは、C AAC - OSについて説明する。

## 【0343】

C AAC - OSは、c軸配向した複数の結晶部 (ペレットともいう。) を有する酸化物半導体の一つである。

40

## 【0344】

透過型電子顕微鏡 (TEM: Transmission Electron Microscope) によって、C AAC - OSの明視野像と回折パターンとの複合解析像 (高分解能TEM像ともいう。) を観察すると、複数のペレットを確認することができる。一方、高分解能TEM像ではペレット同士の境界、即ち結晶粒界 (グレインバウンダリーともいう。) を明確に確認することができない。そのため、C AAC - OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

## 【0345】

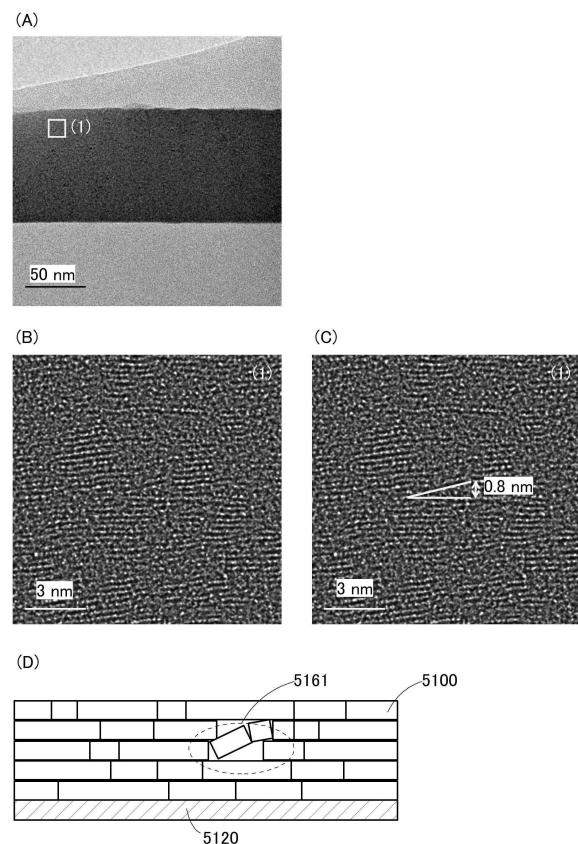

以下では、TEMによって観察したC AAC - OSについて説明する。図35(A)に、

50

試料面と略平行な方向から観察した C AAC - OS の断面の高分解能 TEM 像を示す。高分解能 TEM 像の観察には、球面収差補正 (Spherical Aberration Corrector) 機能を用いた。球面収差補正機能を用いた高分解能 TEM 像を、特に Cs 補正高分解能 TEM 像と呼ぶ。Cs 補正高分解能 TEM 像の取得は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡 JEM - ARM 200 F などによって行うことができる。

#### 【0346】

図 35 (A) の領域 (1) を拡大した Cs 補正高分解能 TEM 像を図 35 (B) に示す。図 35 (B) より、ペレットにおいて、金属原子が層状に配列していることを確認できる。金属原子の各層の配列は、C AAC - OS の膜を形成する面 (被形成面ともいう。) または上面の凹凸を反映しており、C AAC - OS の被形成面または上面と平行となる。

#### 【0347】

図 35 (B) に示すように、C AAC - OS は特徴的な原子配列を有する。図 35 (C) は、特徴的な原子配列を、補助線で示したものである。図 35 (B) および図 35 (C) より、ペレット一つの大きさは 1 nm 以上のものや、3 nm 以上のものがあり、ペレットとペレットとの傾きにより生じる隙間の大きさは 0.8 nm 程度であることがわかる。したがって、ペレットを、ナノ結晶 (nc : nanocrystal) と呼ぶこともできる。また、C AAC - OS を、C ANC (C - Axis Aligned nanocrystals) を有する酸化物半導体と呼ぶこともできる。

#### 【0348】

ここで、Cs 補正高分解能 TEM 像をもとに、基板 5120 上の C AAC - OS のペレット 5100 の配置を模式的に示すと、レンガまたはブロックが積み重なったような構造となる (図 35 (D) 参照。)。図 35 (C) で観察されたペレットとペレットとの間で傾きが生じている箇所は、図 35 (D) に示す領域 5161 に相当する。

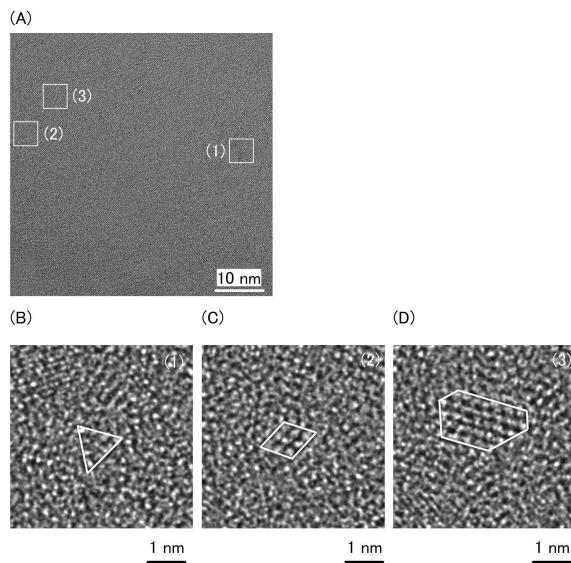

#### 【0349】

また、図 36 (A) に、試料面と略垂直な方向から観察した C AAC - OS の平面の Cs 補正高分解能 TEM 像を示す。図 36 (A) の領域 (1)、領域 (2) および領域 (3) を拡大した Cs 補正高分解能 TEM 像を、それぞれ図 36 (B)、図 36 (C) および図 36 (D) に示す。図 36 (B)、図 36 (C) および図 36 (D) より、ペレットは、金属原子が三角形状、四角形状または六角形状に配列していることを確認できる。しかしながら、異なるペレット間で、金属原子の配列に規則性は見られない。

#### 【0350】

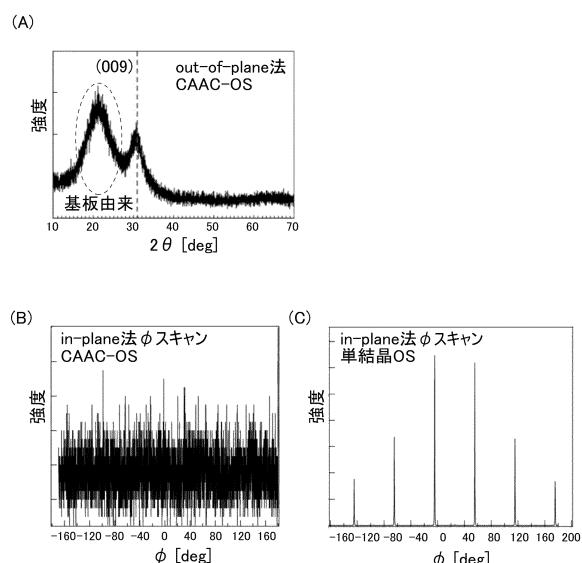

次に、X 線回折 (XRD : X - Ray Diffraction) によって解析した C AAC - OS について説明する。例えば、InGaZnO<sub>4</sub> の結晶を有する C AAC - OS に対し、out - off - plane 法による構造解析を行うと、図 37 (A) に示すように回折角 (2θ) が 31° 近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub> の結晶の (009) 面に帰属されることから、C AAC - OS の結晶が c 軸配向性を有し、c 軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

#### 【0351】

なお、C AAC - OS の out - off - plane 法による構造解析では、2θ が 31° 近傍のピークの他に、2θ が 36° 近傍にもピークが現れる場合がある。2θ が 36° 近傍のピークは、C AAC - OS 中の一部に、c 軸配向性を有さない結晶が含まれることを示している。より好ましい C AAC - OS は、out - off - plane 法による構造解析では、2θ が 31° 近傍にピークを示し、2θ が 36° 近傍にピークを示さない。

#### 【0352】

一方、C AAC - OS に対し、c 軸に略垂直な方向から X 線を入射させる in - plane 法による構造解析を行うと、2θ が 56° 近傍にピークが現れる。このピークは、InGaZnO<sub>4</sub> の結晶の (110) 面に帰属される。C AAC - OS の場合は、2θ を 56° 近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析 (スキャン) を行っても、図 37 (B) に示すように明瞭なピークは現れない。これに対

10

20

30

40

50

し、 $InGaZnO_4$  の単結晶酸化物半導体であれば、2 を 56° 近傍に固定してスキャンした場合、図 37 (C) に示すように (110) 面と等価な結晶面に帰属されるピークが 6 本観察される。したがって、XRD を用いた構造解析から、CAAC-OS は、a 軸および b 軸の配向が不規則であることが確認できる。

#### 【0353】

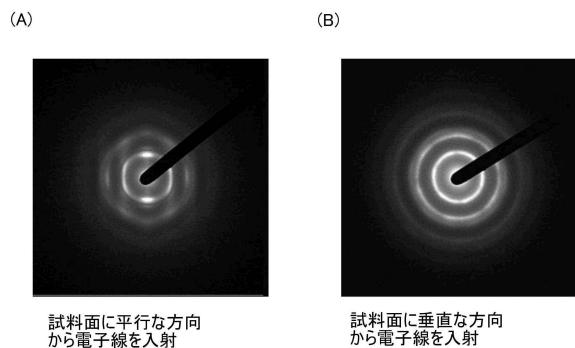

次に、電子回折によって解析した CAAC-OS について説明する。例えば、 $InGaZnO_4$  の結晶を有する CAAC-OS に対し、試料面に平行にプローブ径が 300 nm の電子線を入射させると、図 38 (A) に示すような回折パターン（制限視野透過電子回折パターンともいう。）が現れる場合がある。この回折パターンには、 $InGaZnO_4$  の結晶の (009) 面に起因するスポットが含まれる。したがって、電子回折によっても、CAAC-OS に含まれるペレットが c 軸配向性を有し、c 軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が 300 nm の電子線を入射させたときの回折パターンを図 38 (B) に示す。図 38 (B) より、リング状の回折パターンが確認される。したがって、電子回折によっても、CAAC-OS に含まれるペレットの a 軸および b 軸は配向性を有さないことがわかる。なお、図 38 (B) における第 1 リングは、 $InGaZnO_4$  の結晶の (010) 面および (100) 面などに起因すると考えられる。また、図 38 (B) における第 2 リングは (110) 面などに起因すると考えられる。

#### 【0354】

上述したように、CAAC-OS は結晶性の高い酸化物半導体である。酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、逆の見方をすると CAAC-OS は不純物や欠陥（酸素欠損など）の少ない酸化物半導体ともいえる。

#### 【0355】

なお、不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。

#### 【0356】

酸化物半導体が不純物や欠陥を有する場合、光や熱などによって特性が変動する場合がある。例えば、酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。また、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。

#### 【0357】

不純物および酸素欠損の少ない CAAC-OS は、キャリア密度の低い酸化物半導体である。具体的には、 $8 \times 10^{11}$  個 /  $\text{cm}^3$  未満、好ましくは  $1 \times 10^{11}$  /  $\text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{10}$  個 /  $\text{cm}^3$  未満であり、 $1 \times 10^{-9}$  個 /  $\text{cm}^3$  以上のキャリア密度の酸化物半導体とすることができます。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。CAAC-OS は、不純物濃度が低く、欠陥準位密度が低い。即ち、安定な特性を有する酸化物半導体であるといえる。

#### 【0358】

n c - OS

次に、n c - OS について説明する。

#### 【0359】

n c - OS は、高分解能 TEM 像において、結晶部を確認することができる領域と、明確な結晶部を確認することのできない領域と、を有する。n c - OS に含まれる結晶部は、1 nm 以上 10 nm 以下、または 1 nm 以上 3 nm 以下の大きさであることが多い。なお、結晶部の大きさが 10 nm より大きく 100 nm 以下である酸化物半導体を微結晶酸化物半導体と呼ぶことがある。n c - OS は、例えば、高分解能 TEM 像では、結晶粒界を

10

20

30

40

50

明確に確認できない場合がある。なお、ナノ結晶は、CAAC-OSにおけるペレットと起源を同じくする可能性がある。そのため、以下ではnc-OSの結晶部をペレットと呼ぶ場合がある。

【0360】

nc-OSは、微小な領域（例えば、1nm以上10nm以下の領域、特に1nm以上3nm以下の領域）において原子配列に周期性を有する。また、nc-OSは、異なるペレット間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、nc-OSは、分析方法によっては、a-like OSや非晶質酸化物半導体と区別が付かない場合がある。例えば、nc-OSに対し、ペレットよりも大きい径のX線を用いた場合、out-of-plane法による解析では、結晶面を示すピークは検出されない。また、nc-OSに対し、ペレットよりも大きいプローブ径（例えば50nm以上）の電子線を用いる電子回折を行うと、ハローパターンのような回折パターンが観測される。一方、nc-OSに対し、ペレットの大きさと近いかペレットより小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、nc-OSに対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。さらに、リング状の領域内に複数のスポットが観測される場合がある。

【0361】

このように、ペレット（ナノ結晶）間では結晶方位が規則性を有さないことから、nc-OSを、RANC（Random Aligned nanocrystals）を有する酸化物半導体、またはNANC（Non-Aligned nanocrystals）を有する酸化物半導体と呼ぶこともできる。

【0362】

nc-OSは、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、nc-OSは、a-like OSや非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、nc-OSは、異なるペレット間で結晶方位に規則性が見られない。そのため、nc-OSは、CAAC-OSと比べて欠陥準位密度が高くなる。

【0363】

a-like OS

a-like OSは、nc-OSと非晶質酸化物半導体との間の構造を有する酸化物半導体である。

【0364】

a-like OSは、高分解能TEM像において鬆が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。

【0365】

鬆を有するため、a-like OSは、不安定な構造である。以下では、a-like OSが、CAAC-OSおよびnc-OSと比べて不安定な構造であることを示すため、電子照射による構造の変化を示す。

【0366】

電子照射を行う試料として、a-like OS（試料Aと表記する。）、nc-OS（試料Bと表記する。）およびCAAC-OS（試料Cと表記する。）を準備する。いずれの試料もIn-Ga-Zn酸化物である。

【0367】

まず、各試料の高分解能断面TEM像を取得する。高分解能断面TEM像により、各試料は、いずれも結晶部を有することがわかる。

【0368】

なお、どの部分を一つの結晶部と見なすかの判定は、以下のように行えばよい。例えば、 $InGaZnO_4$ の結晶の単位格子は、In-O層を3層有し、またGa-Zn-O層を6層有する、計9層がc軸方向に層状に重なった構造を有することが知られている。これ

10

20

30

40

50

らの近接する層同士の間隔は、(009)面の格子面間隔(  $d$  値ともいう。)と同程度であり、結晶構造解析からその値は0.29nmと求められている。したがって、格子縞の間隔が0.28nm以上0.30nm以下である箇所を、InGaZnO<sub>4</sub>の結晶部と見なすことができる。なお、格子縞は、InGaZnO<sub>4</sub>の結晶のa-b面に対応する。

#### 【0369】

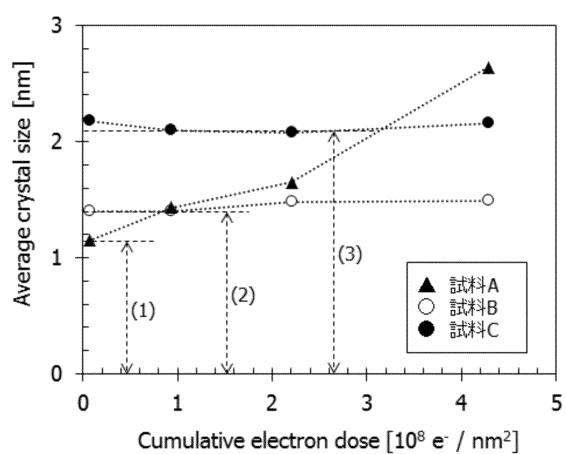

図39は、各試料の結晶部(22箇所から45箇所)の平均の大きさを調査した例である。ただし、上述した格子縞の長さを結晶部の大きさとしている。図39より、a-like OSは、電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。具体的には、図39中に(1)で示すように、TEMによる観察初期においては1.2nm程度の大きさだった結晶部(初期核ともいう。)が、累積照射量が $4.2 \times 10^8 e^-/nm^2$ においては2.6nm程度の大きさまで成長していることがわかる。一方、nc-OSおよびCAAC-OSは、電子照射開始時から電子の累積照射量が $4.2 \times 10^8 e^-/nm^2$ までの範囲で、結晶部の大きさに変化が見られないことがわかる。具体的には、図39中の(2)および(3)で示すように、電子の累積照射量によらず、nc-OSおよびCAAC-OSの結晶部の大きさは、それぞれ1.4nm程度および2.1nm程度であることがわかる。

#### 【0370】

このように、a-like OSは、電子照射によって結晶部の成長が見られる場合がある。一方、nc-OSおよびCAAC-OSは、電子照射による結晶部の成長がほとんど見られないことがわかる。即ち、a-like OSは、nc-OSおよびCAAC-OSと比べて、不安定な構造であることがわかる。

#### 【0371】