#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2014/004770 A2

- (43) International Publication Date 3 January 2014 (03.01.2014)

- (51) International Patent Classification: *H01L 27/112* (2006.01)

- (21) International Application Number:

PCT/US2013/048088

(22) International Filing Date:

27 June 2013 (27.06.2013)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/666,649 29 June 2012 (29.06.2012) US 13/684,107 21 November 2012 (21.11.2012) US

- (71) Applicant: QUALCOMM INCORPORATED [US/US]; Attn: International IP Administration, 5775 Morehouse Drive, San Diego, California 92121 (US).

- (72) Inventors: WANG, Zhongze; 5775 Morehouse Drive, San Diego, California 92121 (US). ZHU, John Jianhong; 5775 Morehose Drive, San Diego, California 92121 (US). LI, Xia; 5775 Morehouse Drive, San Diego, California 92121 (US).

- (74) Agent: GALLARDO, Michelle, S.; 5775 Morehouse Drive, San Diego, California 92121 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

[Continued on next page]

#### (54) Title: INTEGRATED CIRCUIT DEVICE FEATURING AN ANTIFUSE AND METHOD OF MAKING SAME

FIG. 1

## Published:

without international search report and to be republished upon receipt of that report (Rule 48.2(g))

# INTEGRATED CIRCUIT DEVICE FEATURING AN ANTIFUSE AND METHOD OF MAKING SAME

## **CLAIM OF PRIORITY**

[0001] The present application for patent claims priority to U.S. Provisional Patent Application No. 61/666,649 entitled "Integrated Circuit Device Featuring an Anti-fuse" filed June 29, 2012, the entire disclosure of which is hereby expressly incorporated by reference herein.

## **BACKGROUND**

### **Field**

[0002] Various features relate to integrated circuits, and more particularly to methods and apparatuses for improved programmable memory cells featuring antifuses.

## **Background**

[0003] Integrated circuits are interconnected networks of electrical components fabricated on a common foundation called a substrate. The substrate is typically a wafer of semiconductor material, such as silicon. Various fabrication techniques, such as layering, doping, masking, and etching, are used to build millions of resistors, transistors, and other electrical components on the wafer. The components are then wired together, or interconnected, to define a specific electrical circuit, such as a processor or a memory device.

[0004] Fusible elements are employed in integrated circuits to permit changes in the configuration of the integrated circuits after fabrication. For example, fusible elements may be used to replace defective circuits with redundant circuits. As another example, fusible elements may be used to create one time programmable (OTP) or multi-time programmable (MTP) memory circuits. Individual memory cells of an OTP memory cell may be written to once in order to create read only memory modules that cannot be easily altered and/or are secure.

[0005] One type of fusible element is a metal fuse. The metal fuse is composed of a metal alloy or metal, such as copper, that may change its state from a conductive, closed circuit state to a substantially non-conductive, open circuit state if a sufficient amount of current flows through the metal fuse. Metal fuses have several disadvantages. For example, the current needed to program the fuse (i.e., blow the fuse to change it from a

closed circuit state to an open circuit state) is relatively high. Generating this current consumes a substantial amount of power, particularly for mobile devices where power consumption is a concern. Moreover, relatively large transistors (i.e., transistors having a large chip area) are required to generate the current drive needed to blow the metal fuses. Furthermore, the integrated circuit package having the metal fuses may require a dedicated power pin to handle the high current used for programming the metal fuses. Additionally, metal fuses provide poor security because the blown fuses may, in some cases, be seen optically. Also, metal fuses offer poor reliability and in some cases may require serial programming.

[0006] Another type of fusible element is a gate dielectric antifuse. An antifuse comprises two conductive terminals separated by an insulator or a dielectric, and is fabricated as an open circuit. The antifuse is programmed by applying a high voltage across its terminals to rupture the insulator and form an electrical path between the terminals. Typical prior art gate dielectric antifuses used for programmable memory cells require a high voltage to change the state of the antifuse from an open circuit state to a closed circuit state. The voltage needed to cause the state change is generated using a charge pump. However, charge pumps consume a substantial amount of the integrated circuit's active chip area that may otherwise be used for other active components, such as memory cells.

[0007] Therefore, there exists a need for integrated circuits, such as OTP and MTP memory cells, that feature fusible elements that do not suffer from the disadvantages described above in connection with metal fuses and gate dielectric fuses.

#### **SUMMARY**

[0008] One feature provides an integrated circuit that comprises an access transistor including at least one source/drain region, and an antifuse having a conductor-insulator-conductor structure. The antifuse includes a first conductor that is a first electrode, an antifuse dielectric, and a second conductor, where a first surface of the first electrode is coupled to a first surface of the antifuse dielectric, a second surface of the antifuse dielectric is coupled to a first surface of the second conductor, and the second conductor is electrically coupled to the access transistor's source/drain region. According to one aspect, the antifuse is adapted to transition from an open circuit state to a closed circuit state if a programming voltage  $V_{pp}$  greater than or equal to an antifuse dielectric breakdown voltage is applied between the first electrode and the second conductor.

According to another aspect, the programming voltage  $V_{pp}$  is approximately equal to an input/output (I/O) voltage  $V_{IO}$  of the integrated circuit. According to yet another aspect, the antifuse dielectric has a thickness t, and increasing t increases the antifuse dielectric breakdown voltage. According to yet another aspect, the access transistor further includes a gate terminal, a gate dielectric having a gate dielectric breakdown voltage, and a body, the gate dielectric interposed between the gate and the body, and the antifuse dielectric breakdown voltage is less than the gate dielectric breakdown voltage. [0009] According to one aspect, the gate dielectric and the antifuse dielectric are made of at least one different dielectric material. According to another aspect, the antifuse is

of at least one different dielectric material. According to another aspect, the antifuse is positioned, at least in part, above the source/drain region. According to yet another aspect, the antifuse is positioned, at least in part, in a same vertical plane as the source/drain region. According to yet another aspect, the second conductor is a metal source/drain contact coupled to the source/drain region.

[0010] According to one aspect, the second conductor is a second electrode having a second surface that is electrically coupled to the source/drain region. According to another aspect, the first surface of the antifuse dielectric faces an opposite direction of the second surface of the antifuse dielectric. According to yet another aspect, at least one of the first electrode, the antifuse dielectric, and/or the second conductor has at least one of a substantially planar and/or rectangular cuboid shape. According to yet another aspect, the first electrode lies, at least in part, in a same horizontal plane as a resistor of the integrated circuit.

[0011] According to one aspect, the first electrode and the resistor are made of a same material. According to another aspect, the antifuse dielectric lies, at least in part, in a same horizontal plane as a dielectric support positioned underneath the resistor, where the antifuse dielectric and the dielectric support are made of a same dielectric material. According to yet another aspect, the integrated circuit is a one-time programmable (OTP) memory cell. According to yet another aspect, the integrated circuit is a multitime programmable (MTP) memory cell. According to yet another aspect, the integrated circuit is incorporated into at least one of a music player, a video player, an entertainment unit, a navigation device, a communications device, a mobile phone, a smartphone, a personal digital assistant, a fixed location terminal, a tablet computer, and/or a laptop computer.

[0012] Another feature provides a method of manufacturing an integrated circuit, where the method comprises providing a substrate, forming an access transistor including at least one source/drain region in the substrate, providing a first conductor to form a first electrode, providing an antifuse dielectric, providing a second conductor, forming an antifuse by coupling a first surface of the first electrode to a first surface of the antifuse dielectric, and coupling a second surface of the antifuse dielectric to a first surface of the second conductor, and electrically coupling the second conductor to the access transistor's source/drain region. According to one aspect, the method further comprises sharing a mask to provide the first electrode and a resistor, wherein the resistor and the first electrode are made of a same material. According to another aspect, the access transistor further includes a gate terminal, a gate dielectric having a gate dielectric breakdown voltage, and a body, and the method further comprises interposing the gate dielectric between the gate and the body, where the antifuse dielectric breakdown voltage is less than the gate dielectric breakdown voltage. According to yet another aspect, the method further comprises positioning the antifuse, at least in part, above the source/drain region.

[0013] According to one aspect, the method further comprises positioning the antifuse, at least in part, in a same vertical plane as the source/drain region. According to another aspect, the second conductor is a metal source/drain contact, and the method further comprises coupling the metal source/drain contact to the source/drain region. According to yet another aspect, the second conductor forms a second electrode having a second surface, and the method further comprises electrically coupling the second surface of the second electrode to the source/drain region. According to yet another aspect, the method further comprises forming a resistor, and positioning the first electrode, at least in part, in a same horizontal plane as the resistor of the integrated circuit.

[0014] According to one aspect, the method further comprises forming the first electrode and the resistor using a same material. According to another aspect, the method further comprises forming a dielectric support underneath the resistor, and positioning the antifuse dielectric, at least in part, in a same horizontal plane as the dielectric support, the antifuse dielectric and the dielectric support made of a same dielectric material.

[0015] Another feature provides an integrated circuit that comprising an access transistor including at least one source/drain region, and an antifuse having a conductor-

insulator-conductor structure, the antifuse including a first means for conducting, a means for insulating, and a second means for conducting, wherein a first surface of the first means for conducting is coupled to a first surface of the means for insulating, a second surface of the means for insulating is coupled to a first surface of the second means for conducting, and the second means for conducting is electrically coupled to the access transistor's source/drain region. According to one aspect, the antifuse is adapted to transition from an open circuit state to a closed circuit state if a programming voltage  $V_{pp}$  greater than or equal to a breakdown voltage of the means for insulating is applied between the first means for conducting and the second means for conducting. According to another aspect, the access transistor further includes a gate terminal, a gate dielectric having a gate dielectric breakdown voltage, and a body, the gate dielectric interposed between the gate and the body, and the breakdown voltage of the means for insulating is less than the gate dielectric breakdown voltage. According to yet another aspect, the gate dielectric and the means for insulating are made of at least one different dielectric material.

[0016] According to one aspect, the second means for conducting is a metal source/drain contact coupled to the source/drain region. According to another aspect, the first means for conducting is a first electrode, and the second means for conducting is a second electrode having a first surface coupled to the second surface of the means for insulating and a second surface that is electrically coupled to the source/drain region. According to yet another aspect, at least one of the first means for conducting, the means for insulating, and/or the second means for conducting has at least one of a substantially planar and/or rectangular cuboid shape. According to yet another aspect, the first means for conducting lies, at least in part, in a same horizontal plane as a resistor of the integrated circuit, the first means for conducting and the resistor being made of a same material.

# **BRIEF DESCRIPTION OF THE DRAWINGS**

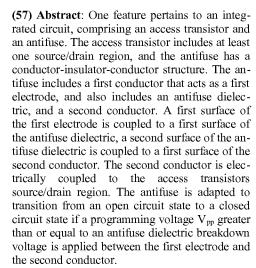

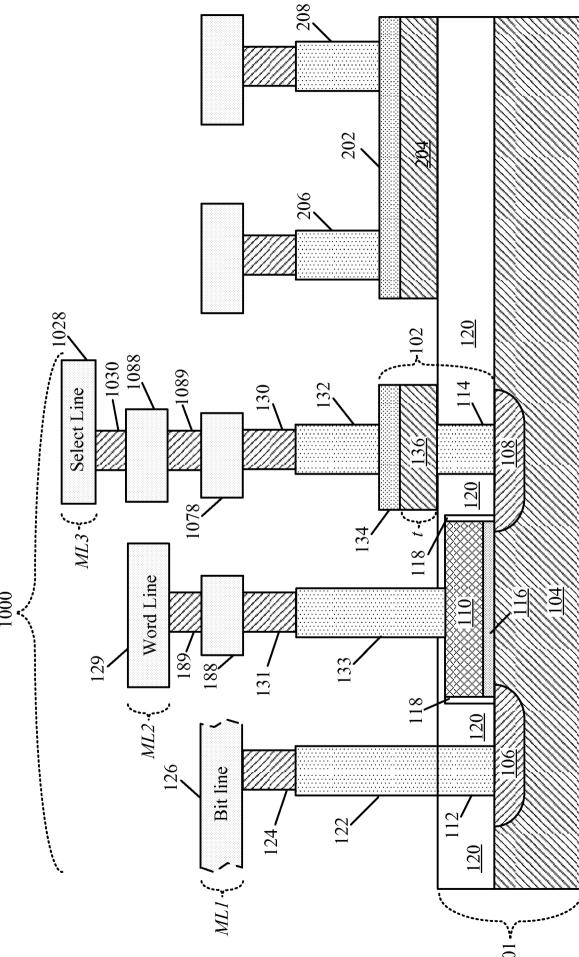

[0017] FIG. 1 illustrates a cross-sectional, schematic view of an integrated circuit programmable memory cell featuring an antifuse.

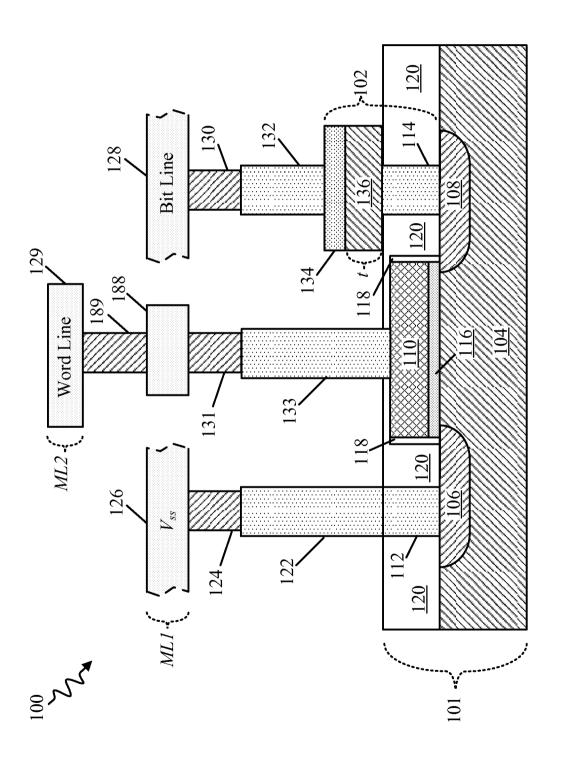

[0018] FIG. 2 illustrates a cross-sectional, schematic view of an integrated circuit resistor that is located adjacent to a programmable memory cell.

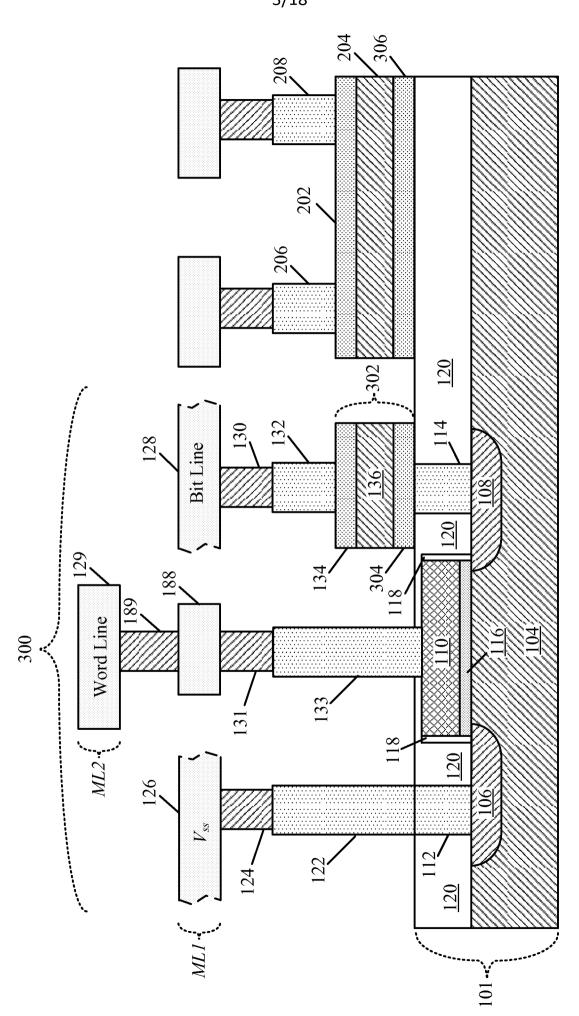

[0019] FIG. 3 illustrates a cross-sectional, schematic view of an integrated circuit programmable memory cell featuring an antifuse.

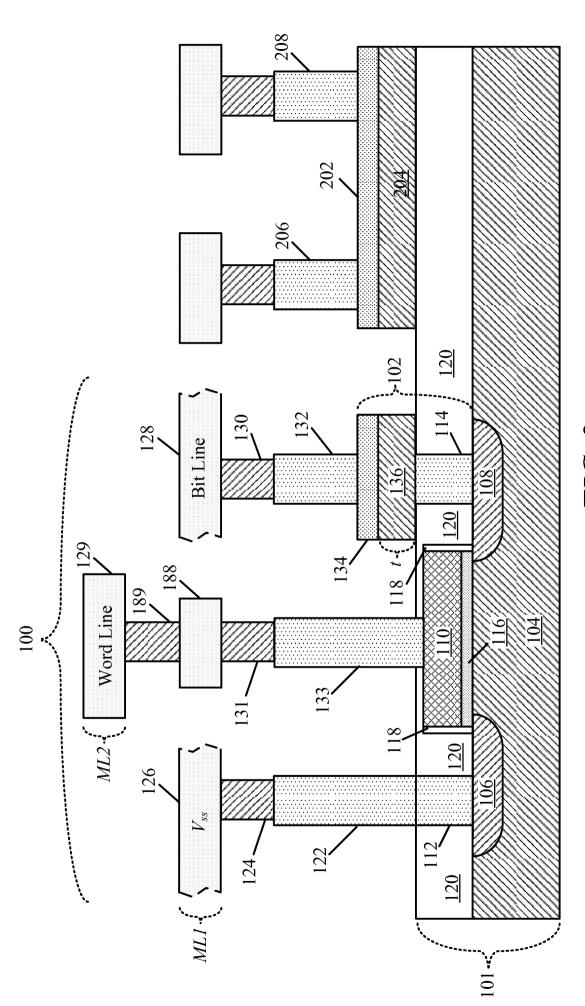

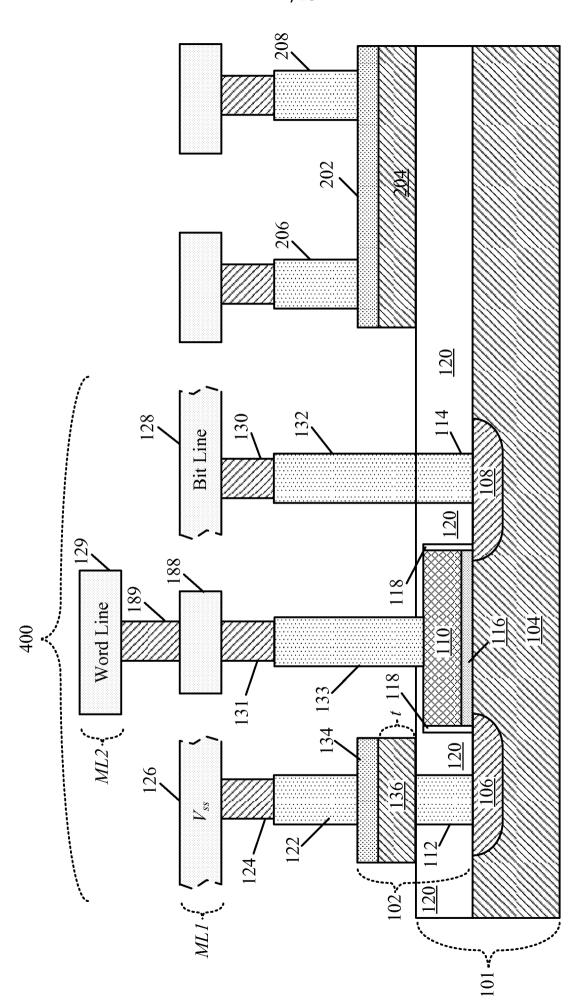

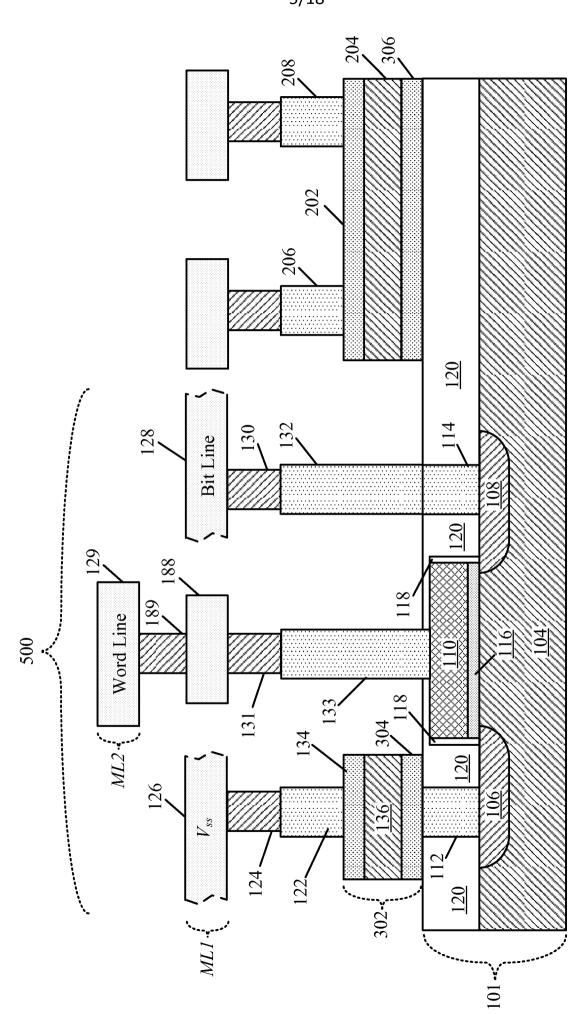

[0020] FIGS. 4 and 5 illustrate cross-sectional, schematic views of integrated circuit programmable memory cells featuring antifuses positioned over a source contact.

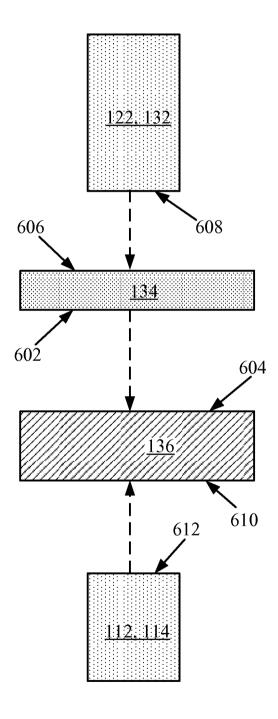

[0021] FIG. 6 illustrates a source/drain interconnect, a top electrode, an antifuse dielectric, and a source/drain contact separated from one another to better illustrate various surfaces of these components.

**[0022]** FIG. 7 illustrates a source/drain interconnect, a top electrode, an antifuse dielectric, a bottom electrode, and a source/drain contact separated from one another to better illustrate various surfaces of these components.

[0023] FIGS. 8 and 9 illustrate schematic diagrams of a programmable memory cell array.

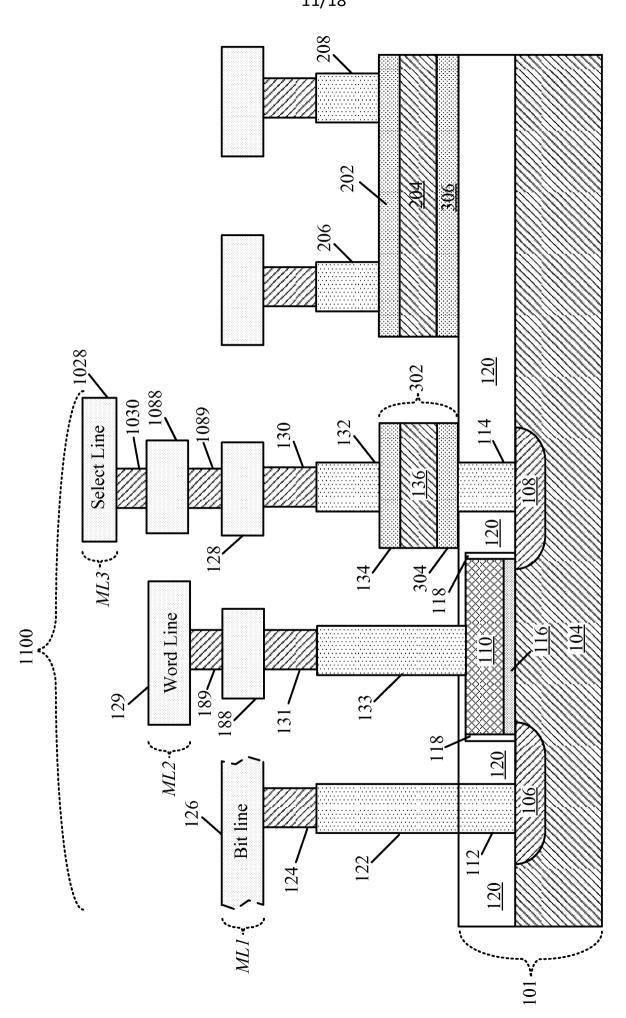

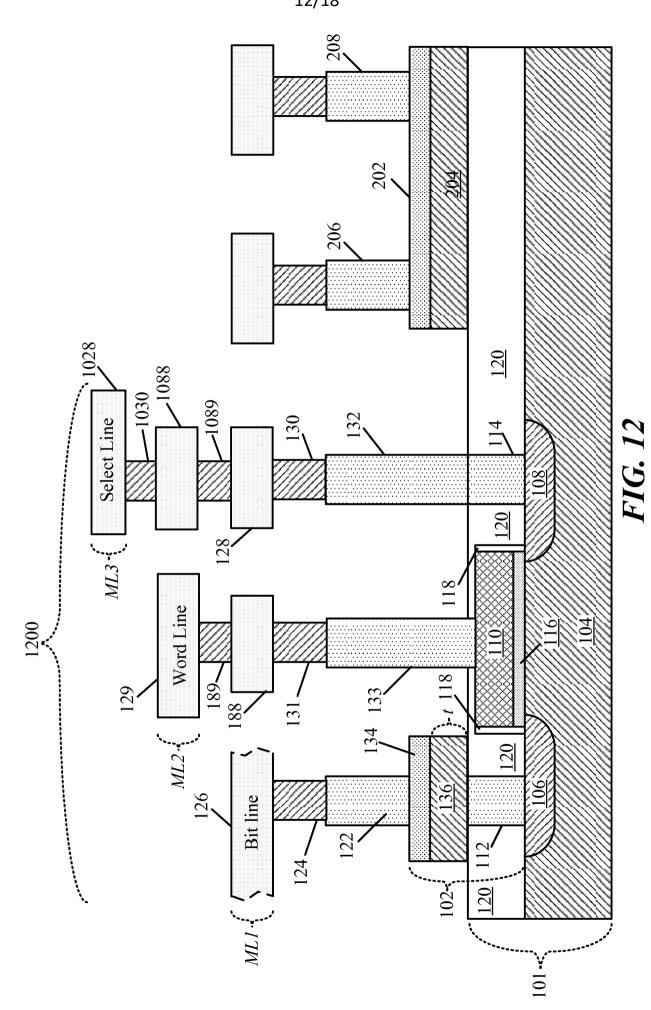

[0024] FIGS. 10, 11, 12, and 13 illustrate cross-sectional, schematic views of IC programmable memory cells featuring the antifuses.

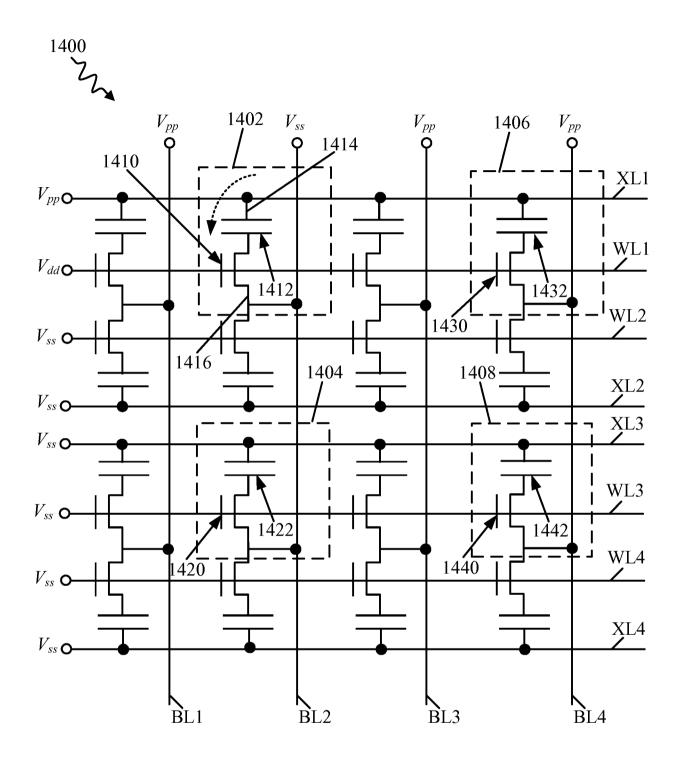

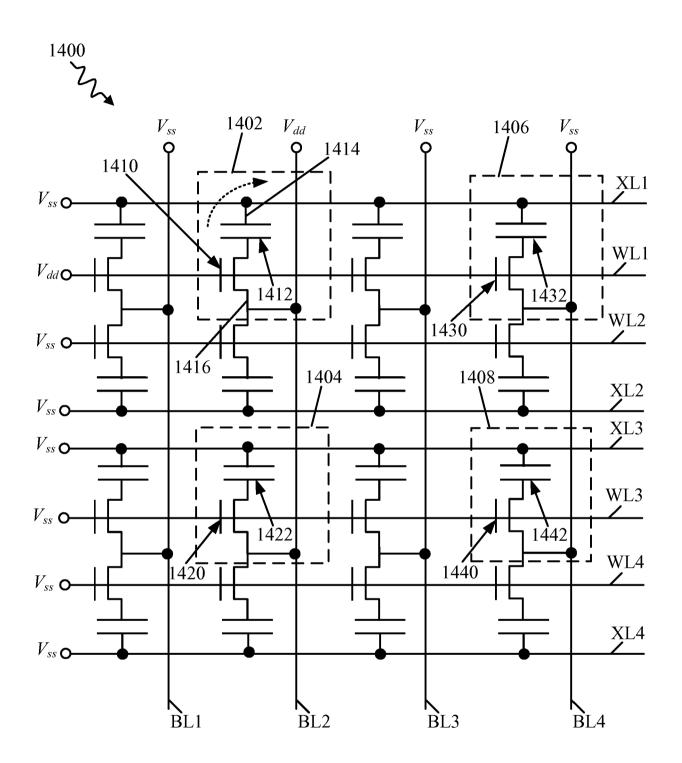

[0025] FIGS. 14 and 15 illustrate a schematic diagram of a programmable memory cell array.

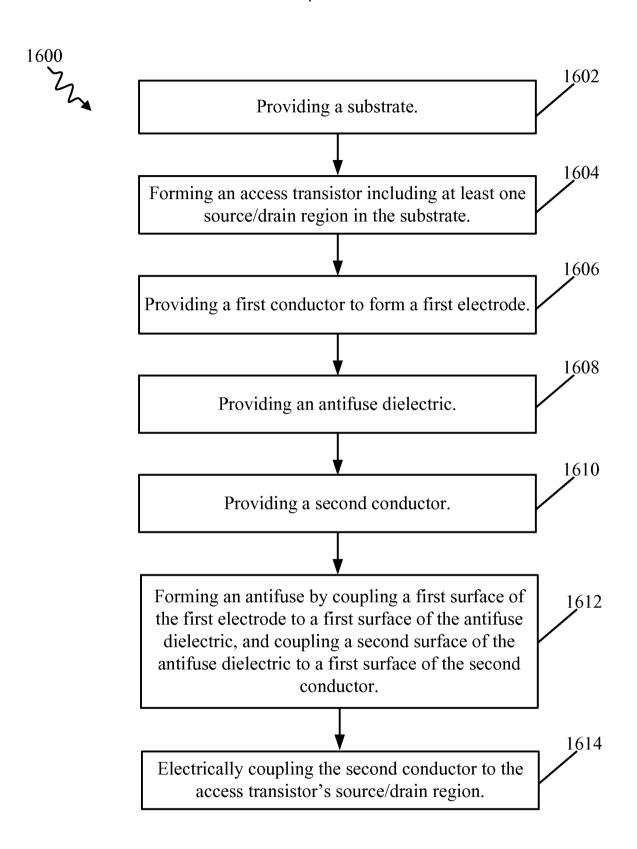

[0026] FIG. 16 illustrates a method of manufacturing an integrated circuit.

[0027] FIG. 17 illustrates various electronic devices that may include an integrated circuit.

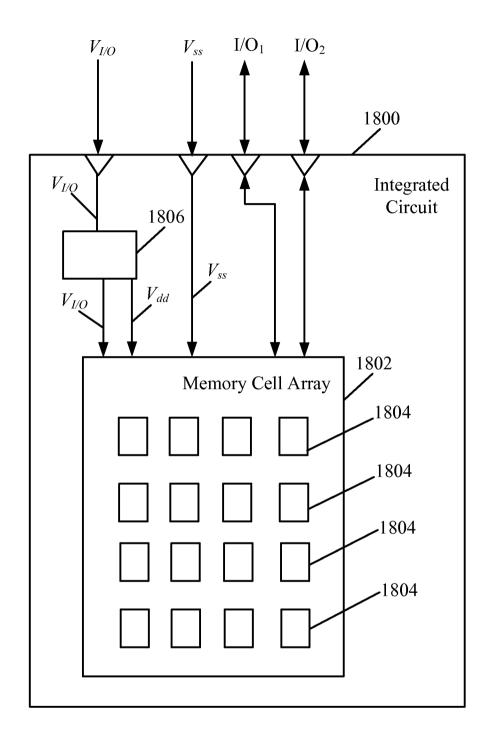

[0028] FIG. 18 illustrates a schematic view of an integrated circuit.

### DETAILED DESCRIPTION

[0029] In the following description, specific details are given to provide a thorough understanding of the various aspects of the disclosure. However, it will be understood by one of ordinary skill in the art that the aspects may be practiced without these specific details. For example, circuits may be shown in block diagrams in order to avoid obscuring the aspects in unnecessary detail. In other instances, well-known circuits, structures and techniques may not be shown in detail in order not to obscure the aspects of the disclosure.

[0030] The word "exemplary" is used herein to mean "serving as an example, instance, or illustration." Any implementation or aspect described herein as "exemplary" is not necessarily to be construed as preferred or advantageous over other aspects of the disclosure. Likewise, the term "aspects" does not require that all aspects of the disclosure include the discussed feature, advantage or mode of operation. The term "electrically coupled" is used herein to refer to the direct or indirect coupling

between two objects that allows for the flow of electrical current to take place between the two objects. For example, if object A physically touches object B, and object B physically touches object C, then objects A and C may still be considered electrically coupled to one another—even if they do not directly physically touch each other—if object B is a conductor that allows for the flow of electrical current from object A to object C and/or from object C to object A.

[0031] The terms wafer and substrate may be used herein to include any structure having an exposed surface with which to form an integrated circuit (IC) according to aspects of the present disclosure. The term substrate is understood to include semiconductor wafers. The term substrate is also used to refer to semiconductor structures during fabrication, and may include other layers that have been fabricated thereupon. The term substrate includes doped and undoped semiconductors, epitaxial semiconductor layers supported by a base semiconductor, or semiconductor layers supported by an insulator, as well as other semiconductor structures well known to one skilled in the art. The term insulator is defined to include any material that is less electrically conductive than materials generally referred to as conductors by those skilled in the art. The term "horizontal" is defined as a plane substantially parallel to the conventional plane or surface of a wafer or substrate, regardless of the orientation of the wafer or substrate. The term "vertical" refers to a direction substantially perpendicular to the horizontal as defined above. Prepositions, such as "above," "below," "on," "upper," "side," "higher," "lower," "over," and "under" when used with respect to the integrated circuits described herein are defined with respect to the conventional plane or surface being on the top surface of the wafer or substrate, regardless of the orientation of the wafer or substrate. The prepositions "above," "below," "on," "upper," "side," "higher," "lower," "over," and "under" are thereby defined with respect to "horizontal" and "vertical."

[0032] The terms "source" and "drain" refer generally to the terminals or diffusion regions of a field effect transistor. A terminal or a diffusion region may be more specifically described as a "source" or a "drain" on the basis of a voltage applied to it when the field effect transistor is in operation. P-type conductivity is conductivity associated with holes in a semiconductor material, and n-type conductivity is conductivity associated with electrons in a semiconductor material.

[0033] FIG. 1 illustrates a cross-sectional, schematic view of an integrated circuit programmable memory cell 100 featuring an antifuse 102 according to one aspect. The programmable memory cell 100 may be, for example, a one-time programmable (OTP) memory cell. In other aspects of the disclosure, the memory cell 100 may be a multi-time programmable (MTP) memory cell, such as resistive random access memory (RRAM or ReRAM).

[0034] The memory cell 100 includes a field effect transistor 101 formed on a semiconductor substrate 104. The transistor 101 includes a source 106 terminal, a drain 108 terminal, and a gate 110 terminal. The substrate 104 acts as the body of the transistor 101 and maybe, for example, a p-type semiconductor. In one aspect, the substrate 104 may actually be a p-type well within another semiconductor substrate. The source 106 and the drain 108 may be n-type semiconductor regions within the p-type substrate body 104, and the gate 110 may be composed of a conductor, such as metal. By controlling the voltages applied to the source 106, the drain 108, the gate 110, and the body 104 relative to one another, the current flow through the transistor 101 (i.e., the current flow between the source 106 and the drain 108) is also controlled. For example, a gate-source voltage  $(V_{GS})$  that exceeds the threshold voltage  $(V_{TH})$  of the transistor 101 causes an inversion layer (not shown) to form at the interface between the body 104 and a gate dielectric 116 below the gate 110 that allows current to flow between the source 106 and the drain 108. Although the illustrated example shows an n-type channel transistor (e.g., NMOS), the same concepts presented herein equally apply to p-type channel transistors (e.g., PMOS) with the polarity of the voltages and currents modified where appropriate.

[0035] As illustrated in FIG. 1, a conductive ohmic source contact 112 electrically couples to the source 106, and another conductive ohmic drain contact 114 electrically couples to the drain 108. The contacts 112, 114 may be composed of a metal, such as tungsten or a tungsten alloy. A gate dielectric 116 lies between the conductive metal gate 110 and the substrate body 104. The gate dielectric 116 may be, but is not limited to, silicon dioxide or a high-K dielectric material such as hafnium silicate, zirconium silicate, and/or hafnium dioxide. The gate 110 may have one or more spacers 118 on its sides. An insulating layer 120, such as silicon nitride, may cover the source 106, the drain 108, and the gate 110.

[0036] The source contact 112 may be electrically coupled to a source interconnect 122, which in turn may be electrically coupled to a first metal trace 126 through a vertical interconnect access (via) 124. According to one aspect, the first metal trace 126 may be associated with a first metal layer MLI and may be electrically coupled to ground  $(V_{ss})$ .

[0037] By contrast to the transistor's source 106 that has an electrically conductive path between the source contact 112 and the first metal trace 126, the transistor's drain 108 does not necessarily have a low resistance electrically conductive path between the drain contact 114 and a second metal trace 128. Instead, an antifuse 102 is interposed in the path between the second metal trace 128 and the drain contact 114, which may be in either an "open" non-conductive state or in a "closed" conductive state. According to one aspect, the second metal trace 128 is associated with the first metal layer *ML1*, and is electrically coupled to the memory bit line (BL). According to the example shown, the second metal trace 128 is electrically coupled to a via 130, which in turn is electrically coupled to the drain interconnect 132.

[0038] In the illustrated example, the antifuse 102 lies between drain contact 114 and a drain interconnect 132. However, in other examples the antifuse 102 may lie between the drain interconnect 132 and the via 130, or between the via 130 and the second metal 128. According to one aspect, regardless of whether the antifuse 102 is positioned between the drain contact 114 and the drain interconnect 132, the drain interconnect 132 and the via 130, or the via 130 and the second metal trace 128, the antifuse 102 may be positioned such that it is generally above the drain 108 of the transistor 101 (or above the source 106 of the transistor, see FIGS. 4 and 5). That is, at least a portion of the antifuse 102 may be positioned in a region or space that is above the drain 108, an example of which is shown in FIG. 1. According to one aspect, the antifuse 102 is positioned, at least in part, in a same vertical plane as the drain region 108 as shown in FIG. 1.

[0039] The gate 110 may be electrically coupled to a third metal trace 129 associated with a second metal layer *ML2* that is in turn electrically coupled to the word line (WL). There may be a via 131 and/or an interconnect 133 that electrically couples the gate 110 to a trace 188 associated with the first metal layer *ML1*. The trace 188 may be in turn electrically coupled to the third trace 188 through a via 189. The metals traces 126, 128,

129, 188, the interconnects 122, 132, 133, the vias 124, 130, 131, 189 and the antifuse 102 may all be encased in an insulating material (not shown).

[0040] The antifuse 102 includes an antifuse dielectric 136. The antifuse 102 may also include a conductive top electrode 134 (e.g., "first electrode") that is electrically coupled to the top side of the antifuse dielectric 136. According to one aspect, the antifuse 102 also includes a conductive bottom element that is electrically coupled to the bottom side of the dielectric 136. According to one example, the conductive bottom element may include the source contact 112 or the drain contact 114. According to other examples, the conductive bottom element may include the source interconnect 122, the via 124, the drain interconnect 132, and the via 130. In this fashion, the antifuse 102 has a conductor-insulator-conductor (e.g., metal-insulator-metal) structure where the first electrode 134 is the first conductor, the antifuse dielectric 136 is the insulator, and the bottom conductor, such as the source or the drain contact 112, 114 is the second conductor.

[0041] The antifuse 102 and may either be in an "open circuit state" or a "closed circuit state." While the antifuse 102 is in an open state, the antifuse dielectric 136 acts as an open circuit insulator and prevents current flow between the drain interconnect 132 and the drain contact 114, and thus prevents current from flowing through the transistor's 101 source/drain terminals 106, 108. While the antifuse 102 is in a closed circuit state, the antifuse dielectric 136 acts substantially like a conductor allowing current to flow through the drain interconnect 132 and the drain contact 114, thereby allowing current to flow through the transistor's 101 source/drain terminals 106, 108.

[0042] In order to change the antifuse's 102 state from an open circuit state to a closed circuit state, a sufficiently high voltage is applied across the antifuse dielectric 136 (e.g., between the top electrode 134 and the drain contact 114) causing the antifuse dielectric 136 to rupture and create a conductive path. Depending on the type of dielectric material 136 selected, the conductive path created may be substantially permanent or temporary. For example, if the memory cell 100 is desired to be an OTP memory cell, then the dielectric 136 selected may be of a type that when ruptured the conductive path created is permanent. Examples of such dielectrics that can be used for OTP purposes include, but are not limited to, silicon nitride (SiN), silicon dioxide (SiO<sub>2</sub>), hafnium oxide (HfO), etc. Thus, the OTP memory cell may be "programmed" by applying a sufficiently high voltage across the antifuse 102 to create the permanent conductive path.

[0043] By contrast, if the memory cell 100 is desired to be an MTP memory cell, then the particular dielectric used for the antifuse dielectric136 may be of a type that can be reset to a non-conductive, insulating state after having been ruptured to create a conductive path. Examples of such dielectrics include, but are not limited to, titanium oxide (TiO), hafnium oxide (HfO), etc. Thus, the MTP memory cell may be reset or "reprogrammed" by applying different voltage across the antifuse 102.

[0044] The type and thickness t of the antifuse dielectric 136 chosen directly affects the voltage (hereinafter referred to as  $V_{BD}$ ) necessary to break down the dielectric 136, and thus change the antifuse 102 from an open circuit state to a closed circuit state. For example, as the thickness t is reduced, less voltage across the dielectric 136 is needed to change its state from open to closed, i.e.,  $V_{BD}$  is reduced. As the thickness t is increased, more voltage across the antifuse dielectric 136 is needed to change its state from open to closed, i.e.,  $V_{BD}$  is increased. Notably, the thickness and type of the antifuse dielectric 136 may be selected such that the  $V_{BD}$  is substantially equal to the input/output (I/O) voltage  $V_{I/O}$  that supplies the integrated circuit in which the memory cell 100 resides. Thus, the antifuse 102 may be programmed using the IC's I/O voltage rather than requiring a dedicated charge pump that requires substantial resources, such as chip area and power.

[0045] The dielectric 136 used in the antifuse 102 may be different than the insulating material used for the gate dielectric 116 that separates the metal gate 110 from the substrate body 104. The gate dielectric 116 may have a  $V_{BD}$  that is significantly higher than the  $V_{BD}$  of the antifuse dielectric 136. Thus, during fabrication of the IC that contains the memory cell, one type of dielectric material having a relatively large  $V_{BD}$  (e.g., greater than 1.5 times the IC's I/O voltage  $V_{I/O}$ ) may be used to create the gate dielectric 116 and another type of dielectric material having a lower  $V_{BD}$  (e.g., slightly less than the IC's I/O voltage but greater than  $V_{DD}$ ) may be used to create the dielectric 136 for the antifuse 102. According to one example, the  $V_{BD}$  of the antifuse dielectric 136 and the IC's I/O voltage  $V_{I/O}$  is about 1.8 volts, and the nominal supply voltage  $V_{DD}$  for the IC is about 1.2 volts. In such a case, the  $V_{BD}$  of the gate dielectric 116 may be, for example, greater than 2 volts.

**[0046]** Of course the value ranges for  $V_{BD}$  of the antifuse 102,  $V_{BD}$  of the gate dielectric 116,  $V_{UO}$ , and  $V_{DD}$  may vary considerably depending on the application and scaling of the IC. For example, the IC's I/O voltage  $V_{UO}$  may range from 0.4 volts to

10.0 volts, and the nominal supply voltage  $V_{DD}$  may have a correspondingly lower range, for example, 0.25 volts to 8.0 volts. Accordingly,  $V_{BD}$  of the antifuse 102 may be less than  $V_{I\!O}$  but greater than  $V_{DD}$  (e.g., it may range from 0.26 volts to 9.99 volts), and  $V_{BD}$  of the gate dielectric 116 may then be greater than  $V_{I\!O}$  (e.g., greater than 0.40 volts).

[0047] FIG. 2 illustrates a cross-sectional, schematic view of an integrated circuit resistor 202 that is located adjacent to the programmable memory cell 100 described above according to one aspect. One end of the resistor 202 may be electrically coupled to an interconnect 206, while the other end of the resistor 202 may be electrically coupled to another interconnect 208. The resistor 202 may be deposited on top of a dielectric support 204.

[0048] In the illustrated example, the resistor 202 is composed of the same material used for the top electrode 134 of the antifuse 102. In this fashion, a separate deposition step using a different material just for the top electrode 134 is unnecessary. Similarly, the dielectric support 204 is composed of the same material used for the antifuse dielectric 136 of the antifuse 102. Thus, during fabrication of the IC, the masks responsible for creating the antifuse dielectric 136 and top electrode 134 of the antifuse 102 may be simultaneously used to create the dielectric support 204 and the resistor 202. In this fashion, manufacturing costs may be minimized by reducing the number of masks necessary to create both the antifuse 102 and resistor 202. According to one aspect, the resistor 202 and the top electrode 134 may be made of titanium nitride (TiN). According to other aspects, the top electrode 134 and the resistor 202 may be made of any other conductive material.

[0049] FIG. 3 illustrates a cross-sectional, schematic view of an integrated circuit programmable memory cell 300 featuring an antifuse 302 according to one aspect. The memory cell 300 is identical to the memory cell 100 shown in FIGS. 1 and 2, except that the memory cell 300 of FIG. 3 features an antifuse 302 having a bottom electrode 304 (e.g., "second electrode") as well. In this fashion, the bottom surface of antifuse dielectric 136 is electrically coupled to a conductive bottom electrode 304, and the top surface of the antifuse dielectric 136 is electrically coupled to the conductive top electrode 134. Interposing the antifuse dielectric 136 in between two electrodes 134, 304 may allow for improved electrical contact at the bottom and top surfaces of the antifuse dielectric 136, thereby allowing for more reliable and predictable breakdown of

the antifuse dielectric 136 if the proper  $V_{BD}$  is applied across the antifuse dielectric 136. Thus, the antifuse 302 has a conductor-insulator-conductor (e.g., metal-insulator-metal) structure where the first electrode 134 is the first conductor, the antifuse dielectric 136 is the insulator, and the second electrode 304 is the second conductor.

[0050] In the illustrated example, the antifuse 302 lies between the drain contact 114 and a drain interconnect 132. However, in other examples the antifuse 302 may lie between the drain interconnect 132 and the via 130, or between the via 130 and the second metal trace 128. According to one aspect, regardless of whether the antifuse 302 is positioned between the drain contact 114 and the drain interconnect 132, the drain interconnect 132 and the via 130, or the via 130 and the second metal trace 128, the antifuse 302 may be positioned such that it is generally above the drain 108 of the transistor 101. That is, at least a portion of the antifuse 302 may be positioned in a region or space that is above the drain 108, an example of which is shown in FIG. 3. According to one aspect, the antifuse 302 is positioned, at least in part, in a same vertical plane as the source/drain region as shown in FIG. 3.

[0051] Also illustrated in FIG. 3 is the resistor 202 that is located adjacent to the memory cell 300. In this example, the dielectric support 204 is deposited on top of a conductive layer 306. The conductive layer 306 and the bottom electrode 304 may be both made of the same material. During fabrication of the IC, the masks responsible for creating the bottom electrode 304, the dielectric 136, and the top electrode 134 of the antifuse 302 may be simultaneously used to create the conductive layer 306, the dielectric support 204, and the resistor 202. In this fashion, manufacturing costs may be minimized by reducing the number of masks necessary to create both the antifuse 302 and resistor 202. According to one aspect, the bottom electrode 304 and the conductive layer 306 may be both made of titanium nitride (TiN). According to other aspects, other conductive materials may be used.

[0052] In the aspects of the disclosure described above with respect to FIGS. 1-3, the antifuses 102, 302 are not limited to being positioned above/over the drain contact 114. Instead, the antifuses 102, 302 may similarly be positioned above/over the source contact 112 with no significant difference in operation.

[0053] FIGS. 4 and 5 illustrate cross-sectional, schematic views of integrated circuit programmable memory cells 400, 500 featuring the antifuses 102, 302, respectively, positioned over the source contact 112 according to one aspect. In the illustrated

examples, the antifuses 102, 302 lie between the source contact 112 and the source interconnect 122. However, in other examples the antifuses 102, 302 may lie between the source interconnect 122 and the via 124, or between the via 124 and the first metal trace 126. According to one aspect, regardless of whether the antifuses 102, 302 are positioned between the source contact 112 and the source interconnect 122, the source interconnect 122 and the via 124, or the via 124 and the first metal trace 126, the antifuses 102, 302 may be positioned such that they are generally above the source 106 of the transistor 101. That is, at least a portion of the antifuses 102, 302 may be positioned in a region or space that is above the source 106, examples of which are shown in FIGS. 4 and 5. According to one aspect, the antifuses 102, 302 may be positioned, at least in part, in a same vertical plane as the source region 106 as shown in FIGS. 4 and 5.

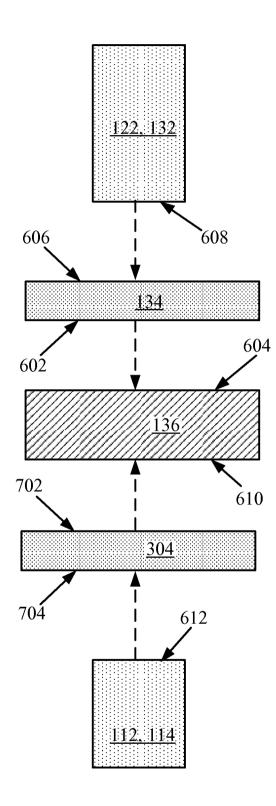

[0054] FIG. 6 illustrates the source/drain interconnect 122, 132 (e.g., either the source interconnect 122 from FIG. 4 or the drain interconnect 132 from FIGS. 1 and 2), the top electrode 134, the antifuse dielectric 136, and the source/drain contact 112, 114 (e.g., either the source contact 112 from FIG. 4 or the drain contact 114 from FIGS. 1 and 2) separated from one another to better illustrate various surfaces of these components. The top electrode 134 (e.g., "first electrode", or "first conductor") has a bottom surface 602 (e.g., "first surface") that may couple to a top surface 604 (e.g., "first surface") of the antifuse dielectric 136. The top electrode 134 may also feature a top surface 606 (e.g., "second surface") that is coupled to a bottom surface 608 (e.g., "first surface") of a conducting element, such as the source/drain interconnect 122, 132. The antifuse dielectric 136 may also have a bottom surface 610 (e.g., "second surface") that is coupled to a top surface 612 (e.g., "first surface") of a second conductor, such as the source/drain contact 112, 114. According to one aspect, the top electrode 134 serves as a first means for conducting, the antifuse dielectric refers to a first means for insulating, and the source/drain contact 112, 114 serves as a second means for conducting.

[0055] FIG. 7 illustrates the source/drain interconnect 122, 132 (e.g., either the source interconnect 122 from FIG. 5 or the drain interconnect 132 from FIG. 3), the top electrode 134, the antifuse dielectric 136, the bottom electrode 304, and the source/drain contact 112, 114 (e.g., either the source contact 112 from FIG. 5 or the drain contact 114 from FIG. 3) separated from one another to better illustrate various surfaces of these components. In this example, the antifuse dielectric's 136 bottom surface 610 is coupled

to a top surface 702 (e.g., "first surface") of the bottom electrode 304 (e.g., "second conductor"). A bottom surface 704 (e.g., "second surface") of the bottom electrode 304 may in turn be coupled to the top surface 612 of a conductor, such as the source/drain contact 112, 114. According to one aspect, the second electrode 304 serves as a second means for conducting.

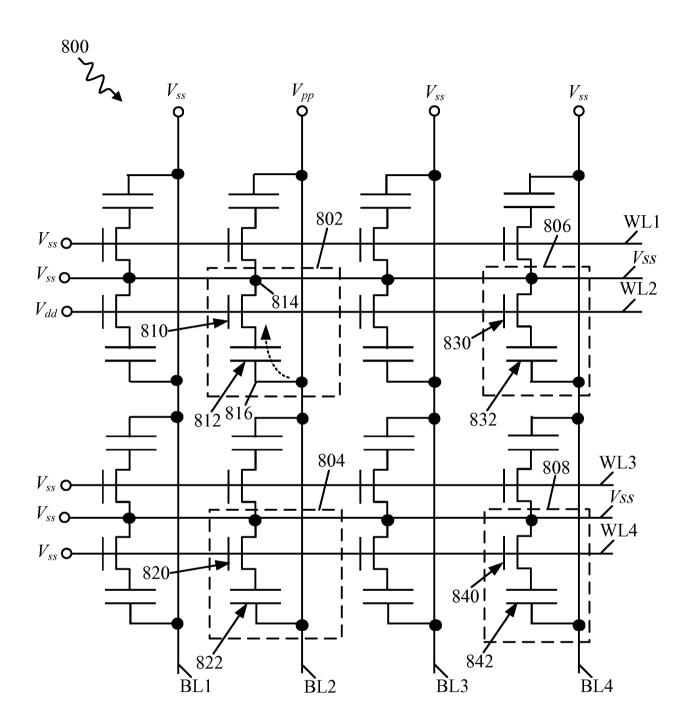

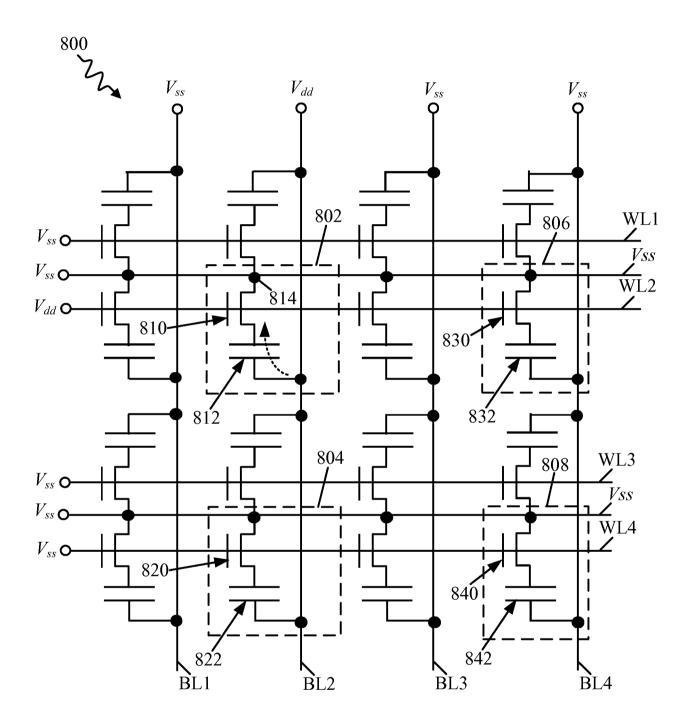

[0056] FIGS. 8 and 9 illustrate schematic diagrams of a programmable memory cell array 800 according to one aspect of the present disclosure. The array 800 is comprised of a plurality of programmable memory cells 802, 804, 806, 808 having antifuses as described herein. The "read" and "write" operations of the memory cells 802, 804, 806, 808 are controlled by the voltages applied to their respective bit lines (BL) and word lines (WL). The memory cells 802, 804, 806, 808 may each be any one of the memory cells 100, 300, 400, 500 described with respect to FIGS. 1-5. The memory cells 802, 804, 806, 808 each comprise an access transistor 810, 820, 830, 840 and an antifuse 812, 822, 832, 842. The access transistors 810, 820, 830, 840 may be, for example, an n-channel field effect transistor. The access transistors 810, 820, 830, 840 may be identical to the transistor 101 shown in FIGS. 1-5 and thus include the source 106, the drain 108, the gate 110, and the body 104. The antifuses 812, 822, 832, 842 may be any one of the antifuses 102, 302 shown in FIGS. 1 – 5. According to one aspect, the memory cells 802, 804, 806, 808 may be OTP memory cells where the antifuses 812, 822, 832, 842 may only change their state from an open circuit state to a closed circuit state once.

[0057] Referring to FIG. 8, a memory cell 802 is undergoing a write operation (i.e., it is being programmed). In order to write a value (e.g., change the logical state from "0" to "1" to "0") of the memory cell 802, various voltages at the terminals of the access transistor 810 and the antifuse 812 must be appropriately set. The voltage at the gate of the transistor 810 is controlled by a word line WL2, and the voltage at one side 816 (e.g., the top electrode 134 in FIGS. 1-5) of the antifuse 812 is controlled by a bit line BL2. For example, as shown in FIG. 8, a value may be written by electrically coupling the access transistor's source 814 to the ground reference voltage  $V_{ss}$ , setting WL2 and the transistor's 810 gate to the nominal supply voltage  $V_{dd}$ , and setting BL2 and an antifuse's terminal 816 (e.g., top electrode 134 in FIGS. 1-5) to the programming voltage  $V_{pp}$ . Note that the nominal supply voltage  $V_{dd}$  is greater than the threshold voltage  $V_{TH}$  of the transistor 810. According to one aspect of the disclosure

$V_{pp} > V_{dd}$ , and  $V_{pp}$  may be equal to the I/O voltage of the IC in which the memory cell array 800 resides. Moreover,  $V_{pp}$  is greater than the breakdown voltage  $V_{BD}$  of the antifuse 812. As just one example,  $V_{pp}$  may be approximately 1.8 volts and  $V_{dd}$  may be approximately 1.2 volts.

[0058] Applying the voltage  $V_{dd}$  to the access transistor's 810 gate causes the access transistor 810 to activate and become conductive (i.e., an inversion layer is formed below the gate making substantial current flow between the source and the drain possible), assuming the body terminal of the transistor is grounded. Increasing the bit line BL2 voltage to  $V_{pp}$  causes the antifuse 812 to transition from an open circuit state to a closed circuit state (i.e., the antifuse dielectric 136 material within the antifuse 812 ruptures) because the voltage across the antifuse 812 exceeds the breakdown voltage  $V_{BD}$  of the antifuse's 812 dielectric. The resulting conductive path across the antifuse 812 makes current flow through the bit line BL2 and the access transistor 810 (as indicated by the curved, dashed arrow) possible if a positive voltage is subsequently applied to the bit line BL2 and the gate voltage of the access transistor 810 exceeds  $V_{TH}$ . [0059] While the memory cell 802 is undergoing a write operation (i.e. programming operation), the memory cell 804 comprised of the access transistor 820 and the antifuse 822 is essentially inactive and no significant current flows through the access transistor 820. Since the gate of the transistor 820 is coupled to  $V_{ss}$  the transistor 820 is inactive and no significant current (i.e., besides negligible leakage current) may flow through the transistor 820. Similarly, the memory cell 806 comprised of the transistor 830 and the antifuse 832 is also inactive and no significant current flows through the transistor 830. Although the voltage of the gate of the transistor 830 is  $V_{dd}$ , no current flows through the access transistor 830 because both the source and the drain of the access transistor 830 are grounded. Similarly, the memory cell 808 comprised of the transistor 840 and the antifuse 842 is also inactive because the gate, the drain, and the source of the transistor 840 are grounded, and hence now current flows through the transistor 840.

**[0060]** Referring to FIG. 9, the memory cell 802 is undergoing a "read" operation. In order to read a value (e.g., read the logical state "0" or "1") from the memory cell 802, various voltages at the terminals of the transistor 810 and the antifuse 812 must be appropriately set. For example, as shown in FIG. 9, this may include setting the transistor's source 814 to  $V_{ss}$ , and setting the transistor's 810 gate and the antifuse's terminal 816 to  $V_{dd}$ . Applying the voltage  $V_{dd}$  to the gate of the transistor 810 causes the

transistor 810 to activate and become conductive (i.e., an inversion layer is formed below the gate making current flow between the source and the drain possible). Increasing the bit line BL2 voltage to  $V_{dd}$  may cause current to flow through the antifuse 812 and the transistor 810 depending on the state of the antifuse 812. For example, if the antifuse 812 is in an open circuit state (e.g., it has not been programmed), then no significant current will flow through the bit line BL2, which may represent a first logical state, such as "0." If the antifuse 812 is in a conductive, closed circuit state (e.g., it has been programmed/written), then a significant amount of current will flow (as indicated by the dashed, curved arrow) through the bit line BL2, which may represent a second logical state, such as "1."

[0061] While the memory cell 802 is undergoing a read operation, memory cells 804, 806, and 808 may be inactive because the gate voltages of their associated access transistors 820, 830, 840 may not exceed  $V_{TH}$  and/or the voltage differential between their sources and drains is negligible.

[0062] In this fashion, setting the voltages of the bit lines to  $V_{pp}$  may allow for programming of the memory cells 802, 804, 806, 808 while setting the voltages of the bit lines to  $V_{dd}$  may allow for reading of the memory cells 802, 804, 806, 808. Thus, the memory cells 802, 804, 806, 808 may be programmed using an I/O voltage of the IC and read using a nominal supply voltage that is less than the I/O voltage, such the nominal supply voltage.

[0063] According to another aspect, the memory cells 802, 804, 806, 808 may be MTP memory cells where the antifuses 812, 822, 832, 842 may change their states from an open circuit state to a closed circuit state and back again to an open circuit state multiple times if the antifuse dielectric used within the antifuse 812, 822, 832, 842 is designed to form and break conductive paths multiple times based on the voltage applied across the antifuse dielectric. In such a case, the memory cells 802, 804, 806, 808 may be reprogrammed (i.e. re-written) by applying appropriate voltages to the terminals of the transistors 810, 820, 830, 840 and the antifuses 812, 822, 832, 842. For example, the memory cell 802 may be reprogrammed to an open circuit state by applying a voltage  $V_{dd}$  to the transistor's 810 gate,  $V_{pp}$  to the access transistor's source 814, and  $V_{ss}$  to the BL2.

[0064] FIGS. 10 and 11 illustrate cross-sectional, schematic views of IC programmable memory cells 1000, 1100 featuring the antifuses 102, 302, respectively,

according to one aspect. The memory cell 1000 is identical to the memory cell 100 shown in FIGS. 1 and 2, except that the first metal trace 126 is electrically coupled to a bit line, and a second metal trace 1028 associated with a third metal layer *ML3* is electrically coupled to a select line (XL). The second metal 1028 of the third metal layer *ML3* may be electrically coupled to the via 130 through a series of traces 1088, 1078 and vias 1030, 1089. The memory cell 1100 is identical to the memory cell 300 shown in FIG. 3, except that the first metal trace 126 is electrically coupled to the bit line, and the second metal trace 1028 associated with the third metal layer *ML3* is electrically coupled to the select line (XL). The third metal trace 1028 of the third metal layer *ML3* may be electrically coupled to the via 130 through a series of traces 1088, 1078 and vias 1030, 1089.

[0065] In the examples of memory cells 100, 300 shown in FIGS. 10 and 11, the antifuses 102, 302 are positioned above the first source/drain region 108. However, similar to the memory cells 400, 500 shown in FIGS. 4 and 5, the antifuses 102, 302 of the memory cells 1000, 1100 of FIGS. 10 and 11 may be positioned so that they are above the second source/drain region 106. FIGS. 12 and 13 illustrate cross-sectional, schematic views of IC programmable memory cells 1200, 1300 that feature antifuses 102, 302, respectively, that are positioned above the second source/drain region 106 according to one aspect. Although, as described herein, the elements 106, 112, 122, and 124 may be associated with the "source" of the transistor 101, and elements 108, 114, 132, and 130 may be associated with the "drain" of the transistor 101, these elements may be associated with either the actual source or the drain depending on the polarity of the voltage applied to the source/drain terminals 106, 108 of the transistor 101.

[0066] FIGS. 14 and 15 illustrate a schematic diagram of a programmable memory cell array 1400 according to another aspect of the present disclosure. The array 1400 is comprised of a plurality of programmable memory cells 1402, 1404, 1406, 1408 having antifuses as described herein. The "read" and "write" operations of the memory cells 1402, 1404, 1406, 1408 are controlled by the voltages applied to their respective bit lines (BL), word lines (WL), and select lines (XL). The memory cells 1402, 1404, 1406, 1408 may each be any one of the memory cells 1000, 1100, 1200, 1300 described with respect to FIGS. 10 – 13. The memory cells 1402, 1404, 1406, 1408 each comprise an access transistor 1410, 1420, 1430, 1440 and an antifuse 1412, 1422, 1432, 1442. The access transistors 1410, 1420, 1430, 1440 may be, for example, n-channel field effect

transistors. The access transistors 1410, 1420, 1430, 1440 may be identical to the transistor 101 shown in FIGS. 10-13 and thus include the source 106, the drain 108, the gate 110, and the body 104. The antifuses 1412, 1422, 1432, 1442 may be any one of the antifuses 102, 302 shown in FIGS. 10-13. According to one aspect, the memory cells 1402, 1404, 1406, 1408 may be OTP memory cells where the antifuses 1412, 1422, 1432, 1442 may only change their state from an open circuit state to a closed circuit state once.

[0067] Referring to FIG. 14, a memory cell 1402 is undergoing a write operation (i.e., it is being programmed). In order to write a value (e.g., change the logical state from "0" to "1" or "1" to "0") of the memory cell 1402, various voltages at the terminals of the access transistor 1410 and the antifuse 1412 must be appropriately set. The voltage at the transistor's source 1416 is controlled by a bit line BL2, the voltage at the gate of the transistor 1410 is controlled by a word line WL1, and the voltage at one side 1414 (e.g., the top electrode 134 in FIGS. 10 - 13) of the antifuse 1412 is controlled by a select line XL1.

For example, as shown in FIG. 14, a value may be written by electrically coupling the transistor's source 1416 to the ground reference voltage  $V_{ss}$ , setting the transistor's 1410 gate to the nominal supply voltage  $V_{dd}$ , and setting an antifuse's terminal 1414 (e.g., top electrode 134 in FIGS. 10-13) to the programming voltage  $V_{pp}$ . Note that the nominal supply voltage  $V_{dd}$  is greater than the threshold voltage  $V_{TH}$  of the transistor 1410. According to one aspect of the disclosure  $V_{pp} > V_{dd}$ , and  $V_{pp}$  may be equal to the I/O voltage of the IC in which the memory cell array 1400 resides. Moreover,  $V_{pp}$  is greater than the breakdown voltage  $V_{BD}$  of the antifuse 1412. As just one example,  $V_{pp}$  may be approximately 1.8 volts and  $V_{dd}$  may be approximately 1.2 volts.

[0068] Applying the voltage  $V_{dd}$  to the gate of the transistor 1410 causes the transistor 1410 to activate and become conductive assuming the body terminal of the transistor is grounded (i.e., an inversion layer is formed below the gate making substantial current flow between the source and the drain possible). Increasing the select line XL1 voltage to  $V_{pp}$  causes the antifuse 1412 to transition from an open circuit state to a closed circuit state (i.e., the dielectric material within the antifuse 1412 ruptures) because the voltage across the antifuse 1412  $V_{pp}$  exceeds the breakdown voltage  $V_{BD}$  of the antifuse's 1412 antifuse dielectric. The resulting conductive path across the antifuse 1412 makes current flow through XL1, BL2, and the transistor 1410 (as indicated by the curved, dashed

arrow) possible if the BL2 voltage is less than the XL1 voltage, and the gate voltage of the transistor 1410 exceeds  $V_{TH}$ .

[0069] While the memory cell 1402 is undergoing a write operation (i.e. programming operation), the memory cell 1404 comprised of the transistor 1420 and antifuse 1422 is essentially inactive and no significant current flows through the transistor 1420 because the gate, the drain, and the source of the transistor 1420 are grounded. Similarly, the memory cell 1406 comprised of the transistor 1430 and the antifuse 1432 is also inactive and no significant current flows through the transistor 1430. Although the voltage of the gate of the transistor 1430 is at  $V_{dd}$ , no current flows through the transistor 1430 because both the source and the drain are grounded. Similarly, the memory cell 1408 comprised of the transistor 1440 and the antifuse 1442 is also inactive. Since the gate of the transistor 1440 is coupled to  $V_{ss}$  the transistor 1440 is inactive and no significant current (i.e., besides negligible leakage current) may flow through the transistor (i.e., from source to drain) 1440.

[0070] Referring to FIG. 15, the memory cell 1402 is undergoing a "read" operation. In order to read a value (e.g., read the logical state "0" or "1") from the memory cell 1402, various voltages at the terminals of the transistor 1410 and the antifuse 1412 must be appropriately set. For example, as shown in FIG. 15, this may include setting the antifuse's terminal 1414 (e.g., the top electrode 134 in FIGS. 10-13) to  $V_{ss}$ , and setting the transistor's 1410 gate and drain 1416 to  $V_{dd}$ . (Note, that since BL2 has a greater voltage than XL1 in this example, the node 1416 is now the drain and the other side of the transistor 1410 is the source.) Applying the voltage  $V_{dd}$  to the gate of the transistor 1410 causes the transistor 1410 to activate and become conductive. Increasing the BL2 voltage to  $V_{dd}$  may cause current to flow through the antifuse 1412 and the transistor 1410 depending on the state of the antifuse 1412. For example, if the antifuse 1412 is in an open circuit state (e.g., it has not been programmed), then no significant current will flow through BL2 and XL1, which may represent a first logical state, such as "0." If the antifuse 1412 is in a conductive, closed circuit state (e.g., it has been programmed/written), then a significant amount of current will flow (as indicated by the dashed, curved arrow) through BL2 and XL1, which may represent a second logical state, such as "1."

[0071] While the memory cell 1402 is undergoing a read operation, memory cells 1404, 1406, and 1408 may be inactive because the gates voltages of their associated

transistors 1420, 1430, 1440 may not exceed  $V_{TH}$  and/or the voltage differential between their sources and drains is negligible. In this fashion, setting the voltages of the select lines to  $V_{pp}$  and the bit lines to  $V_{ss}$  may allow for programming of the memory cells 1402, 1404, 1406, 1408 while setting the voltages of the select lines to  $V_{ss}$  and the bit lines to  $V_{dd}$  may allow for reading of the memory cells 1402, 1404, 1406, 1408.

[0072] According to another aspect, the memory cells 1402, 1404, 1406, 1408 may be MTP memory cells where the antifuses 1412, 1422, 1432, 1442 may change their states from an open circuit state to a closed circuit state and back again to an open circuit state multiple times if the dielectric used within the antifuse 1412, 1422, 1432, 1442 is designed to form and break conductive paths multiple times based on the voltage applied across the dielectric. In such a case, the memory cells 1402, 1404, 1406, 1408 may be reprogrammed (i.e. re-written) by applying appropriate voltages to the terminals of the transistors 1410, 1420, 1430, 1440 and the antifuses 1412, 1422, 1432, 1442. For example, the memory cell 1402 may be reprogrammed to an open circuit state by applying a voltage  $V_{dd}$  to the transistor's 1410 gate,  $V_{ss}$  to XL1, and  $V_{pp}$  to the BL2. Moreover, BL1, BL3, and BL4 will have to be set to  $V_{ss}$  to inactivate other memory cells within the array 1400 from unintentional programming.

[0073] According to one aspect, the first electrode 134, the antifuse dielectric 136, and/or the second electrode 304 may be planar as shown in FIGS. 1-7 and 10-13. According to another aspect, the first electrode 134, the antifuse dielectric 136, and/or the second electrode 304 may have a substantially rectangular cuboid shape.

[0074] FIG. 16 illustrates a method 1600 of manufacturing an integrated circuit according to one aspect. At step 1602, the method comprises providing a substrate. At step 1604, the method further comprises forming an access transistor including at least one source/drain region in the substrate. At step 1606, the method further comprises providing a first conductor to form a first electrode. At step 1608, the method further comprises providing an antifuse dielectric. At step 1610, the method further comprises providing a second conductor. At step 1612, the method further comprises forming an antifuse by coupling a first surface of the first electrode to a first surface of the antifuse dielectric, and coupling a second surface of the antifuse dielectric to a first surface of the second conductor. At step 1614, the method further comprises electrically coupling the second conductor to the access transistor's source/drain region.

[0075] FIG. 17 illustrates various electronic devices that may include an integrated circuit 1700 according to one aspect. The integrated circuit 1700 may be any one of the integrated circuit memory cells 100, 300, 400, 500, 1000, 1100, 1200, 1300 and/or memory cell arrays 800, 1400 described above with respect to FIGS. 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, and/or 16. For example, a mobile telephone 1702, a laptop computer 1704, and a fixed location terminal 1706 may include the integrated circuit 1700. The devices 1702, 1704, 1706 illustrated in FIG. 17 are merely exemplary. Other electronic devices may also feature the integrated circuit 1700 including, but not limited to, hand-held personal communication systems (PCS) units, portable data units such as personal data assistants, GPS enabled devices, navigation devices, set top boxes, music players, video players, entertainment units, fixed location data units such as meter reading equipment, or any other device that stores or retrieves data or computer instructions, or any combination thereof.

[0076] FIG. 18 illustrates a schematic view of an integrated circuit 1800 according to one aspect of the present disclosure. The IC 1800 may include a memory cell array 1802 comprising a plurality of memory cells 1804. The memory cell array 1802 may be any of the memory cell arrays 800, 1400 described herein. The memory cells 1804 may be any of the OTP or MTP memory cells 100, 300, 400, 500, 1000, 1100, 1200, 1300 described herein. The IC 1800 may be externally supplied an I/O voltage  $V_{I/O}$  that is used by the IC's voltage converter circuit1806 to generate a nominal supply voltage  $V_{dd}$  that is less than  $V_{I/O}$ . Both  $V_{I/O}$  and  $V_{dd}$  may be supplied to the memory cell array 1802 as shown. In other aspects, the IC 1800 may be externally supplied both  $V_{I/O}$  and  $V_{dd}$ , and thus the IC 1800 does not have to generate  $V_{dd}$  on-chip using a voltage converter circuit 1806. The IC 1800 may have one or more input/output (I/O) signal lines I/O<sub>1</sub>, I/O<sub>2</sub>.

[0077] One or more of the components, steps, features, and/or functions illustrated in FIGS. 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, and/or 18 may be rearranged and/or combined into a single component, step, feature or function or embodied in several components, steps, or functions. Additional elements, components, steps, and/or functions may also be added without departing from the invention.

[0078] Also, it is noted that the aspects of the present disclosure may be described as a process that is depicted as a flowchart, a flow diagram, a structure diagram, or a block diagram. Although a flowchart may describe the operations as a sequential process,

many of the operations can be performed in parallel or concurrently. In addition, the order of the operations may be re-arranged. A process is terminated when its operations are completed. A process may correspond to a method, a function, a procedure, a subroutine, a subprogram, etc. When a process corresponds to a function, its termination corresponds to a return of the function to the calling function or the main function.

[0079] The various features of the invention described herein can be implemented in different systems without departing from the invention. It should be noted that the foregoing aspects of the disclosure are merely examples and are not to be construed as limiting the invention. The description of the aspects of the present disclosure is intended to be illustrative, and not to limit the scope of the claims. As such, the present teachings can be readily applied to other types of apparatuses and many alternatives, modifications, and variations will be apparent to those skilled in the art.

### **CLAIMS**

### WHAT IS CLAIMED IS:

- 1. An integrated circuit, comprising:

- an access transistor including at least one source/drain region; and

- an antifuse having a conductor-insulator-conductor structure, the antifuse including a first conductor that is a first electrode, an antifuse dielectric, and a second conductor, wherein a first surface of the first electrode is coupled to a first surface of the antifuse dielectric, a second surface of the antifuse dielectric is coupled to a first surface of the second conductor, and the second conductor is electrically coupled to the access transistor's source/drain region.

- 2. The integrated circuit of claim 1, wherein the antifuse is adapted to transition from an open circuit state to a closed circuit state if a programming voltage  $V_{pp}$  greater than or equal to an antifuse dielectric breakdown voltage is applied between the first electrode and the second conductor.

- 3. The integrated circuit of claim 2, wherein the programming voltage  $V_{pp}$  is approximately equal to an input/output (I/O) voltage  $V_{I/O}$  of the integrated circuit.

- 4. The integrated circuit of claim 2, wherein the antifuse dielectric has a thickness *t*, and increasing *t* increases the antifuse dielectric breakdown voltage.

- 5. The integrated circuit of claim 2, wherein the access transistor further includes a gate terminal, a gate dielectric having a gate dielectric breakdown voltage, and a body, the gate dielectric interposed between the gate and the body, and the antifuse dielectric breakdown voltage is less than the gate dielectric breakdown voltage.

- 6. The integrated circuit of claim 5, wherein the gate dielectric and the antifuse dielectric are made of at least one different dielectric material.

- 7. The integrated circuit of claim 1, wherein the antifuse is positioned, at least in part, above the source/drain region.

8. The integrated circuit of claim 1, wherein the antifuse is positioned, at least in part, in a same vertical plane as the source/drain region.

- 9. The integrated circuit of claim 1, wherein the second conductor is a metal source/drain contact coupled to the source/drain region.

- 10. The integrated circuit of claim 1, wherein the second conductor is a second electrode having a second surface that is electrically coupled to the source/drain region.

- 11. The integrated circuit of claim 1, wherein the first surface of the antifuse dielectric faces an opposite direction of the second surface of the antifuse dielectric.

- 12. The integrated circuit of claim 1, wherein at least one of the first electrode, the antifuse dielectric, and/or the second conductor has at least one of a substantially planar and/or rectangular cuboid shape.

- 13. The integrated circuit of claim 1, wherein the first electrode lies, at least in part, in a same horizontal plane as a resistor of the integrated circuit.

- 14. The integrated circuit of claim 13, wherein the first electrode and the resistor are made of a same material.

- 15. The integrated circuit of claim 13, wherein the antifuse dielectric lies, at least in part, in a same horizontal plane as a dielectric support positioned underneath the resistor, the antifuse dielectric and the dielectric support made of a same dielectric material.

- 16. The integrated circuit of claim 1, wherein the integrated circuit is a one-time programmable (OTP) memory cell.

- 17. The integrated circuit of claim 1, wherein the integrated circuit is a multi-time programmable (MTP) memory cell.

18. The integrated circuit of claim 1, wherein the integrated circuit is incorporated into at least one of a music player, a video player, an entertainment unit, a navigation device, a communications device, a mobile phone, a smartphone, a personal digital assistant, a fixed location terminal, a tablet computer, and/or a laptop computer.

19. A method of manufacturing an integrated circuit, the method comprising: providing a substrate;

forming an access transistor including at least one source/drain region in the substrate;

providing a first conductor to form a first electrode;

providing an antifuse dielectric;

providing a second conductor;

forming an antifuse by

coupling a first surface of the first electrode to a first surface of the antifuse dielectric, and

coupling a second surface of the antifuse dielectric to a first surface of the second conductor; and

electrically coupling the second conductor to the access transistor's source/drain region.

20. The method of claim 19, further comprising:

sharing a mask to provide the first electrode and a resistor, wherein the resistor and the first electrode are made of a same material.

- 21. The method of claim 19, wherein the antifuse is adapted to transition from an open circuit state to a closed circuit state if a programming voltage  $V_{pp}$  greater than or equal to an antifuse dielectric breakdown voltage is applied between the first electrode and the second conductor.

- 22. The method of claim 21, wherein the programming voltage  $V_{pp}$  is approximately equal to an input/output (I/O) voltage  $V_{I/O}$  of the integrated circuit.

23. The method of claim 21, wherein the access transistor further includes a gate terminal, a gate dielectric having a gate dielectric breakdown voltage, and a body, the method further comprising:

interposing the gate dielectric between the gate and the body, the antifuse dielectric breakdown voltage being less than the gate dielectric breakdown voltage.

- 24. The method of claim 23, wherein the gate dielectric and the antifuse dielectric are made of at least one different dielectric material.

- 25. The method of claim 19, further comprising: positioning the antifuse, at least in part, above the source/drain region.

- 26. The method of claim 19, further comprising:

positioning the antifuse, at least in part, in a same vertical plane as the source/drain region.

- 27. The method of claim 19, wherein the second conductor is a metal source/drain contact, the method further comprising:

coupling the metal source/drain contact to the source/drain region.

28. The method of claim 19, wherein the second conductor forms a second electrode having a second surface, the method further comprising:

electrically coupling the second surface of the second electrode to the source/drain region.

- 29. The method of claim 19, wherein at least one of the first electrode, the antifuse dielectric, and/or the second conductor has at least one of a substantially planar and/or rectangular cuboid shape.

- 30. The method of claim 19, further comprising:

forming a resistor; and

positioning the first electrode, at least in part, in a same horizontal plane as the resistor of the integrated circuit.

31. The method of claim 30, further comprising: forming the first electrode and the resistor using a same material.

32. The method of claim 30, further comprising:

forming a dielectric support underneath the resistor; and

positioning the antifuse dielectric, at least in part, in a same horizontal plane as the dielectric support, the antifuse dielectric and the dielectric support made of a same dielectric material.

- 33. The method of claim 19, wherein the integrated circuit is a one-time programmable (OTP) memory cell.

- 34. An integrated circuit, comprising:

an access transistor including at least one source/drain region; and

an antifuse having a conductor-insulator-conductor structure, the antifuse including a first means for conducting, a means for insulating, and a second means for conducting, wherein a first surface of the first means for conducting is coupled to a first surface of the means for insulating, a second surface of the means for insulating is coupled to a first surface of the second means for conducting, and the second means for conducting is electrically coupled to the access transistor's source/drain region.

- 35. The integrated circuit of claim 34, wherein the antifuse is adapted to transition from an open circuit state to a closed circuit state if a programming voltage  $V_{pp}$  greater than or equal to a breakdown voltage of the means for insulating is applied between the first means for conducting and the second means for conducting.

- 36. The integrated circuit of claim 35, wherein the programming voltage  $V_{pp}$  is approximately equal to an input/output (I/O) voltage  $V_{I/O}$  of the integrated circuit.

- 37. The integrated circuit of claim 35, wherein the access transistor further includes a gate terminal, a gate dielectric having a gate dielectric breakdown voltage, and a body,

the gate dielectric interposed between the gate and the body, and the breakdown voltage of the means for insulating is less than the gate dielectric breakdown voltage.

- 38. The integrated circuit of claim 37, wherein the gate dielectric and the means for insulating are made of at least one different dielectric material.

- 39. The integrated circuit of claim 34, wherein the antifuse is positioned, at least in part, above the source/drain region.

- 40. The integrated circuit of claim 34, wherein the second means for conducting is a metal source/drain contact coupled to the source/drain region.

- 41. The integrated circuit of claim 34, wherein the first means for conducting is a first electrode, and the second means for conducting is a second electrode having a first surface coupled to the second surface of the means for insulating and a second surface that is electrically coupled to the source/drain region.

- 42. The integrated circuit of claim 34, wherein at least one of the first means for conducting, the means for insulating, and/or the second means for conducting has at least one of a substantially planar and/or rectangular cuboid shape.

- 43. The integrated circuit of claim 34, wherein the first means for conducting lies, at least in part, in a same horizontal plane as a resistor of the integrated circuit, the first means for conducting and the resistor being made of a same material.

FIG. 1

FIG. 2

FIG. 4

FIG. 5

*FIG.* 6

**FIG.** 7

**FIG.** 8

FIG. 9

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18