(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 102 46 738 B4 2004.05.06

(12)

## Patentschrift

(21) Aktenzeichen: 102 46 738.2

(51) Int Cl.<sup>7</sup>: G11C 7/06

(22) Anmelddatum: 07.10.2002

(43) Offenlegungstag: 05.06.2003

(45) Veröffentlichungstag

der Patenterteilung: 06.05.2004

Innerhalb von 3 Monaten nach Veröffentlichung der Erteilung kann Einspruch erhoben werden.

(30) Unionspriorität:

09/991571 16.11.2001 US

(72) Erfinder:

Rickes, Jurgen T., Los Altos Hills, Calif., US;

McAdams, Hugh P., Mc Kinney, Tex., US; Grace,

James W., Los Altos Hills, Calif., US

(71) Patentinhaber:

Agilent Technologies, Inc. (n.d.Ges.d.Staates

Delaware), Palo Alto, Calif., US

(56) Für die Beurteilung der Patentfähigkeit in Betracht

gezogene Druckschriften:

US 50 31 143

(74) Vertreter:

Schoppe, Zimmermann, Stöckeler & Zinkler, 82049

Pullach

(54) Bezeichnung: **Leseverstärker mit unabhängiger Rückschreibefähigkeit für ferroelektrische Direktzugriffsspeicher**

(57) Hauptanspruch: Erfassungsschaltung, die eine unabhängige Rückschreibefähigkeit aufweist, mit folgenden Merkmalen:

einem Leseverstärker (14), der ein Eingangssignal mit einem Referenzsignal vergleicht und ein Ausgangssignal erzeugt; wobei der Leseverstärker (14) folgende Merkmale umfaßt:

einen p-Kanal-Transistor, der eine Source, die mit Leistung verbunden ist, und einen ersten Drain aufweist;

einen ersten und einen zweiten Schenkel, wobei jeder Schenkel mit dem Drain des p-Kanal-Transistors und Masse verbunden ist, wobei jeder Schenkel ferner folgende Merkmale umfaßt:

einen ersten p-Kanal-Transistor, der eine Source aufweist, die mit dem ersten Drain verbunden ist,

einen zweiten p-Kanal-Transistor, der eine Source aufweist, die mit dem Drain des ersten p-Kanal-Transistors an einem ersten Knoten verbunden ist, zwei n-Kanal-Transistoren, die parallel geschaltet sind, und deren Drains mit dem Drain des zweiten p-Kanal-Transistors an einem zweiten Knoten verbunden sind, und deren Sources mit Masse verbunden sind,

einen dritten n-Kanal-Transistor, der in Serie mit dem Gate des ersten p-Kanal-Transistors...

**Beschreibung**

## Stand der Technik

[0001] Der digitale Differenzkomparator, der in **Fig. 1** gezeigt ist, wird in dynamischen Direktzugriffspeichern (DRAM) sowie in statischen Direktzugriffspeichern (SRAM) verwendet. Diese Schaltung findet jedoch üblicherweise in dem Datenpfad außerhalb des Speicherarrays selbst Anwendung und verstärkt das Datensignal, das von dem Speicherarray empfangen wird, und leitet dasselbe weiter zu dem Ausgangspuffer. Da diese Schaltung keine Fähigkeit aufweist, zurück auf die Eingangsknoten zu schreiben, und da sie um einiges komplexer als der herkömmliche Zwischenspeicher-Leseverstärker ist, der in **Fig. 2** gezeigt ist, findet sie normalerweise keine Anwendung in dem Speicherarray selbst.

[0002] Ferroelektrische Speicher sind gegenüber EEPROM und Flash-Speichern hinsichtlich einer Schreibzugriffszeit und eines Gesamtleistungsverbrauchs überlegen. Sie werden in Anwendungen verwendet, in denen ein nichtflüchtiger Speicher mit diesen Merkmalen erforderlich ist, z. B. Digitalkameras und berührungsfreien Smart-Cards. Berührungsreie Smart-Cards benötigen nichtflüchtige Speicher mit einem niedrigen Leistungsverbrauch, da sie nur eine elektromagnetische Kopplung verwenden, um die elektronischen Chips auf der Karte hochzufahren. Digitalkameras erfordern sowohl einen niedrigen Leistungsverbrauch als auch schnelle häufige Schreiberoperationen, um ein gesamtes Bild in weniger als 0,1 Sekunden in den Speicher zu speichern und zurückzuspeichern.

[0003] Ein typischer Lese-Zugriff auf einen ferroelektrischen Speicher besteht aus einem Schreiben-Zugriff, gefolgt durch ein Erfassen. Zur Darstellung wird eine „0“ in den ferroelektrischen Kondensator geschrieben, um den ursprünglichen Dateninhalt der Speicherzelle zu entdecken. Wenn der ursprüngliche Inhalt der Speicherzelle eine „1“ ist, kehrt das Schreiben einer „0“ die Richtung der Polarisierung in dem ferroelektrischen Kondensator um. Dies induziert eine große Stromspitze auf dem Erfassungsdraht. Andererseits gibt es keine Stromspitze auf dem Erfassungsdraht, wenn der ursprüngliche Inhalt des ferroelektrischen Kondensators ebenfalls eine „0“ war. Deshalb werden durch ein Erfassen des Vorliegens einer Stromspitze auf dem Erfassungsdraht die ursprünglichen Daten des ferroelektrischen Kondensators, auf den zugegriffen wird, bestimmt.

[0004] Die Lese-Operation ist, wie beschrieben wurde, destruktiv, da eine „0“ in jede Speicherzelle geschrieben wird, auf die für eine Lese-Operation zugegriffen wird. Die ursprünglichen Daten jedoch werden in dem Leseverstärker gespeichert und können auch wieder in der Speicherzelle, auf die zugegriffen wird, zurückgespeichert werden. Anders ausgedrückt ist ein Lesen-Zugriff erst nach dem zweiten Schreiben vollständig, das die ursprünglichen Daten zurück-

speichert.

[0005] Aus der US 5,031,143 ist eine Erfassungsschaltung für ferroelektrische Speichervorrichtungen bekannt, welche einen Leseverstärker und Rückschreibeblock hat. Der Leseverstärker vergleicht ein Eingangssignal mit einem Referenzsignal und erzeugt ein Ausgangssignal. Der Rückschreibeblock weist ein Aktivierungssignal und ein Rückschreibausgangssignal auf. Das Ausgangssignal des Leseverstärkers ist mit dem Rückschreibeblock gekoppelt.

**Aufgabenstellung**

[0006] Es ist die Aufgabe der vorliegenden Erfindung, eine Erfassungsschaltung und einen Leseverstärker zu schaffen, die ein schnelles, energiesparendes Erfassen bzw. Lesen von Daten ermöglichen.

[0007] Diese Aufgabe wird durch Erfassungsschaltungen nach den Patentansprüchen 1, 2 und 3 sowie durch einen Leseverstärker nach Anspruch 4 gelöst.

[0008] Eine Erfassungsschaltung mit einer unabhängigen Rückschreibefähigkeit umfaßt einen Leseverstärker, der ein Eingangssignal und ein Referenzsignal empfängt, und einen Tri-State-fähigen Rückschreibeblock, der ein Schreibaktivierungssignal und das Ausgangssignal des Leseverstärkers empfängt. Ein optionaler Datenpuffer empfängt außerdem das Ausgangssignal des Leseverstärkers.

**Ausführungsbeispiel**

[0009] Bevorzugte Ausführungsbeispiele der vorliegenden Erfindung werden nachfolgend Bezug nehmend auf die beigefügten Zeichnungen näher erläutert. Es zeigen:

[0010] **Fig. 1** einen digitalen Differenzkomparator des Stands der Technik;

[0011] **Fig. 2** einen Zwischenspeicher-Leseverstärker des Stands der Technik;

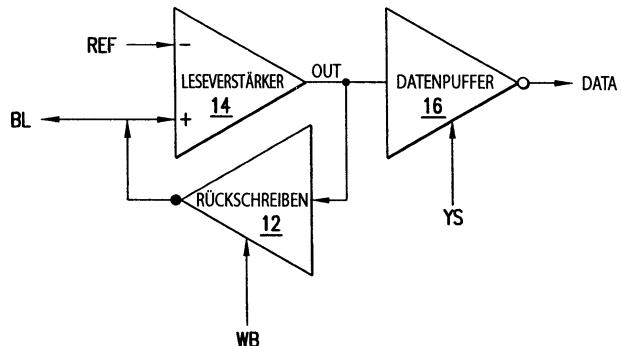

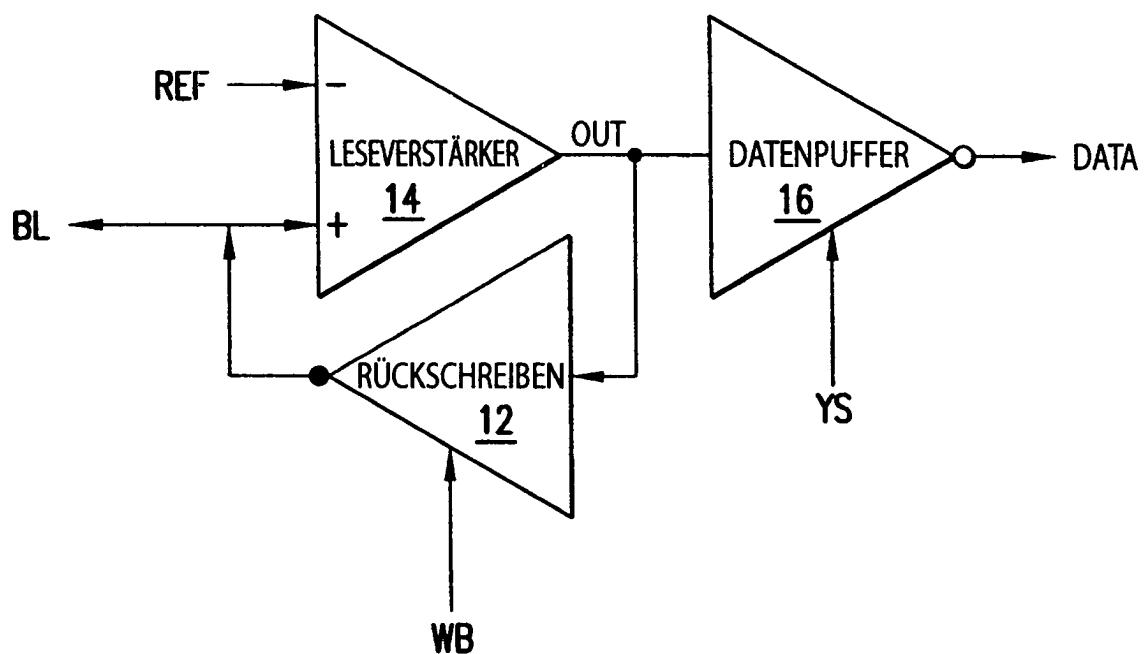

[0012] **Fig. 3** ein Funktionsblockdiagramm der vorliegenden Erfindung;

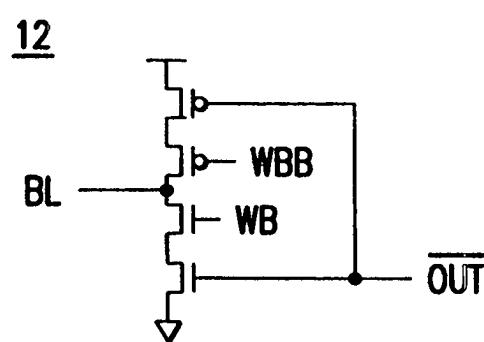

[0013] **Fig. 4** den Rückschreibefunktionsblock aus **Fig. 3**;

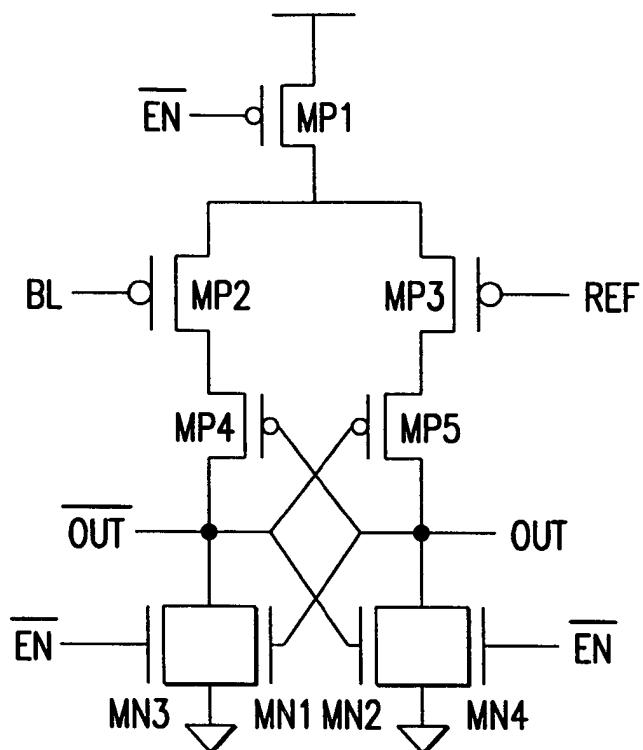

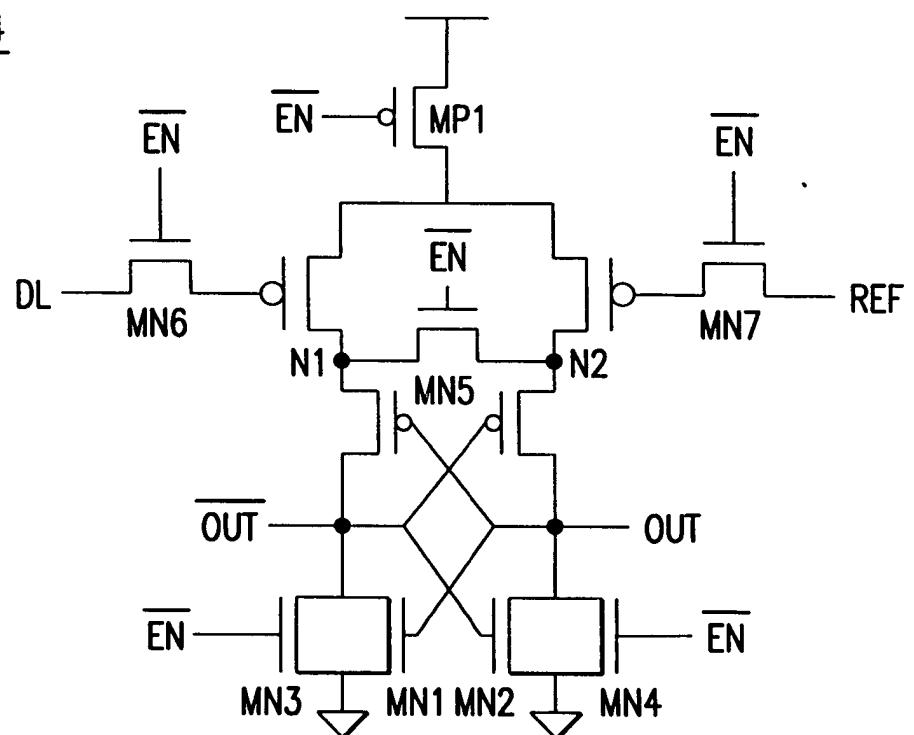

[0014] **Fig. 5** den Leseverstärker aus **Fig. 3**;

[0015] **Fig. 6** einen alternativen Laserverstärker aus **Fig. 3**; und

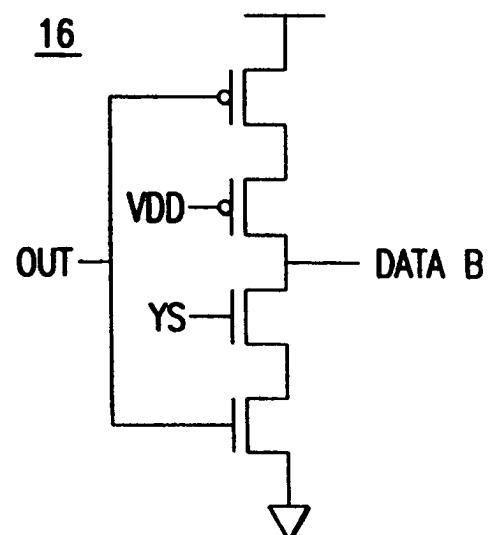

[0016] **Fig. 7** den optionalen Datenpuffer aus **Fig. 3**.

[0017] Die optimale Anzahl von Zellen pro Bitleitung eines ferroelektrischen Speichers neigt dazu, größer zu sein als die eines DRAM. Deshalb kann ein etwas komplexerer Leseverstärker leichter toleriert werden, da es weniger Partitionen des Speicherarrays gibt und die Zelleffizienz dazu neigt, höher zu sein. Die höhere Bitleitungskapazität des FeRAM bedeutet aufgrund der größeren Anzahl von Bits, daß die Verwendung eines älteren Zwischenspeicher-Leseverstärkers (in **Fig. 2** gezeigt) zu noch langsameren Zugriffszeiten führt. Da eine angemessene Spannungstrennung zwischen Bitleitung und Bitleitung auftreten

muß, bevor dieselben mit dem Ausgangsdatenpfad gekoppelt werden können, wird zusätzliche Zeit benötigt, um die stark belasteten Bitleitungen zu laden oder zu entladen.

[0018] Ein Funktionsblockdiagramm **10** der vorliegenden Erfindung ist in **Fig. 3** gezeigt. Der Rückschreibefunktionsblock **12** wird durch ein Eingangssignal WB aktiviert. Im Betrieb vergleicht der Leseverstärker die Spannung auf der Bitleitung (BL) mit der Spannung an dem Referenzeingang (REF). Das Ausgangssignal (OUT) des Leseverstärkers wird durch den Rückschreibefunktionsblock **12** empfangen. Ein optionaler Datenpuffer **16** empfängt außerdem das Ausgangssignal. So wird die stark belastete Bitleitung von den leichtbelasteten internen Erfassungsknoten getrennt.

[0019] **Fig. 4** zeigt den Rückschreibefunktionsblock **12** aus **Fig. 3**. In Serie geschaltet von Leistung zu Masse sind ein erster und ein zweiter p-Kanal-Transistor gefolgt durch einen ersten und einen zweiten n-Kanal-Transistor. Das BL-Signal ist mit den Knoten zwischen dem zweiten p-Kanal-Transistor und dem ersten n-Kanal-Transistor verbunden. Die Gates des ersten p-Kanal-Transistors und des zweiten n-Kanal-Transistors sind gemeinsam mit dem Knoten OUT verbunden, der das Komplement des Ausgangssignals OUT des Leseverstärkers ist. Das Gate des zweiten p-Kanal-Transistors empfängt ein Steuerungssignal Rückschreiben (WBB), während das Gate des ersten n-Kanal-Transistors ein Steuerungssignal Rückschreiben (WB) empfängt.

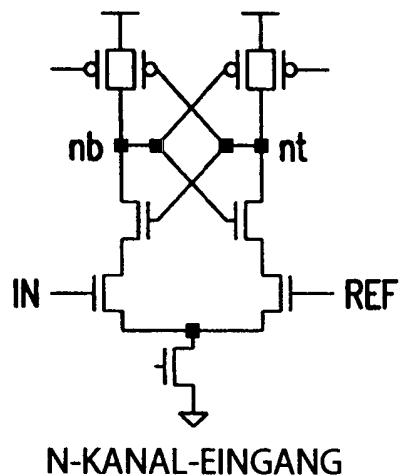

[0020] **Fig. 5** stellt den Leseverstärker **14** aus **Fig. 3** dar. Bei einem dritten p-Kanal-Transistor MP1 ist dessen Source mit Leistung verbunden, wobei sein Drain mit dem ersten und dem zweiten Schenkel verbunden ist. Jeder Schenkel umfaßt zwei in Serie geschaltete p-Kanal-Transistoren (MP2, MP4; MP3, MP5) gefolgt durch zwei parallel geschaltete n-Kanal-Transistoren (MN3, MN1; MN2, MN4).

[0021] Für den ersten Schenkel sind an dem OUT-Tor der Knoten zwischen dem Drain des zweiten p-Kanal-Transistors MP4 und den Drains der beiden parallel geschalteten n-Kanal-Transistoren MN3, MN1 mit dem Gate des zweiten p-Kanal-Transistors MP5 des zweiten Schenkels und dem Gate des n-Kanal-Transistors MN2 verbunden. Für den zweiten Schenkel sind an dem OUT-Tor der Knoten zwischen dem Drain des zweiten p-Kanal-Transistors MP5 und den Drains der beiden parallel geschalteten n-Kanal-Transistoren MN2, MN4 mit dem Gate des zweiten p-Kanal-Transistors MP4 des ersten Schenkels und dem Gate des zweiten n-Kanal-Transistors MN1 verbunden.

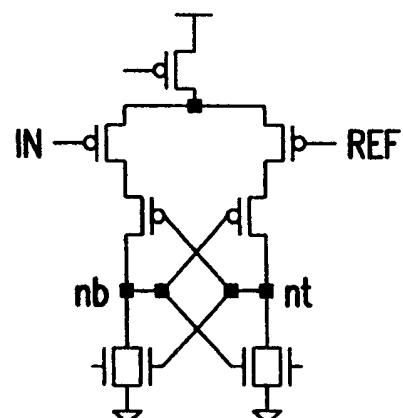

[0022] **Fig. 6** stellt ein alternatives Ausführungsbeispiel für den Leseverstärker aus **Fig. 3** dar. Zusätzlich zu der elektrischen Anschlußmöglichkeit, die in **Fig. 5** beschrieben wurde, verbindet ein fünfter n-Kanal-Transistor MN5 Knoten N1 und N2 und wird zum Ausgleich verwendet. Ein sechster n-Kanal-Transistor MN6 ist in Serie mit dem Gate des p-Kanal-Transistor

sistors MP2 geschaltet. Ein siebter n-Kanal-Transistor MN7 ist in Serie mit dem Gate des p-Kanal-Transistors MP3 geschaltet. Die Gates der n-Kanal-Transistoren MN5, MN6 und MN7 sind mit EN verbunden. N-Kanal-Transistoren MN6 und MN7 sind Trennungsvorrichtungen.

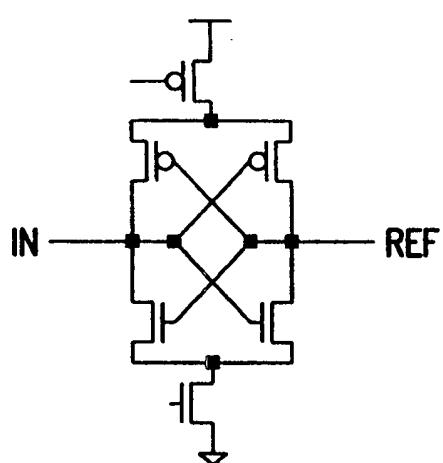

[0023] **Fig. 7** stellt den optionalen Datenpuffer **16** aus **Fig. 3** dar. Ein erster und ein zweiter p-Kanal-Transistor sind in Serie zwischen Leistung und ein Tor DATA geschaltet. Das Gate des ersten p-Kanal-Transistors empfängt ein Signal OUT, während das Gate des zweiten p-Kanal-Transistors ein Signal VDD empfängt. Zwei n-Kanal-Transistoren sind in Serie zwischen das Tor DATA und Masse geschaltet. Das Gate des ersten n-Kanal-Transistors ist mit OUT verbunden, während das Gate des zweiten n-Kanal-Transistors ein Signal YS empfängt.

[0024] Im Betrieb wird der Mangel einer Rückschreibfähigkeit, der dem alleinstehenden Leseverstärker inhärent ist, durch die Hinzufügung des Serien-p-Kanal- und des Serien-n-Kanal-Transistors, die mit BL verbunden sind, überwunden, was in einem Speicherarray die Bit- oder Datenleitung wäre. WB und WBB sind zusätzliche komplementäre Steuerungssignale, die erzeugt werden, nachdem der Leseverstärker durch ein Anlegen von VSS an EN und VDD an EN aktiviert wurde, nachdem OUT und OUT auf ihre vollen logischen Pegel getrieben wurden. Gleichzeitig mit der Rückschreibezurückspeicherung auf der Bitleitung kann auf Daten über das YS-Signal zugegriffen werden und dieselben können auf ihrem Pfad zu dem Datenausgangspuffer des Chips starten, und zwar unabhängig von der Zeit, die benötigt wird, um das Rückschreiben zu erzielen.

## Patentansprüche

1. Erfassungsschaltung, die eine unabhängige Rückschreibfähigkeit aufweist, mit folgenden Merkmalen:

einem Leseverstärker (**14**), der ein Eingangssignal mit einem Referenzsignal vergleicht und ein Ausgangssignal erzeugt; wobei der Leseverstärker (**14**) folgende Merkmale umfaßt:

einen p-Kanal-Transistor, der eine Source, die mit Leistung verbunden ist, und einen ersten Drain aufweist;

einen ersten und einen zweiten Schenkel, wobei jeder Schenkel mit dem Drain des p-Kanal-Transistors und Masse verbunden ist, wobei jeder Schenkel ferner folgende Merkmale umfaßt:

einen ersten p-Kanal-Transistor, der eine Source aufweist, die mit dem ersten Drain verbunden ist,

einen zweiten p-Kanal-Transistor, der eine Source aufweist, die mit dem Drain des ersten p-Kanal-Transistors an einem ersten Knoten verbunden ist, zwei n-Kanal-Transistoren, die parallel geschaltet sind, und deren Drains mit dem Drain des zweiten p-Kanal-Transistors an einem zweiten Knoten verbunden sind, und deren Sources mit Masse verbunden sind,

einen dritten n-Kanal-Transistor, der in Serie mit dem Gate des ersten p-Kanal-Transistors geschaltet ist, und

wobei für jeden Schenkel der zweite Knoten mit den Gates des zweiten p-Kanal-Transistors und einem der beiden n-Kanal-Transistoren des anderen Schenkels verbunden ist; und

einen ersten n-Kanal-Transistor, der über die ersten Knoten des ersten und des zweiten Schenkels verbunden ist;

einem Tri-State-fähigen Rückschreibeblock (12), der ein Aktivierungs- und ein Rückschreibeausgangssignal aufweist, wobei das Ausgangssignal des Leseverstärkers mit dem Rückschreibeblock gekoppelt ist.

2. Erfassungsschaltung, die eine unabhängige Rückschreibefähigkeit aufweist, mit folgenden Merkmalen:

einem Leseverstärker (14), der ein Eingangssignal mit einem Referenzsignal vergleicht und ein Ausgangssignal erzeugt;

einem Tri-State-fähigen Rückschreibeblock (12), der ein Aktivierungs- und ein Rückschreibeausgangssignal aufweist,

wobei das Ausgangssignal des Leseverstärkers mit dem Rückschreibeblock gekoppelt ist; und

einem Datenpuffer (16), der das Ausgangssignal des Leseverstärkers empfängt, wobei der Datenpuffer (16) folgende Merkmale umfaßt:

einen ersten n-Kanal-Transistor, der einen Drain aufweist, der ein Daten-Aus-Signal erzeugt, und der ein Gate aufweist, das ein Steuerungssignal empfängt; und

einen zweiten n-Kanal-Transistor, der einen Drain, der mit der Source des ersten n-Kanal-Transistors verbunden ist, eine Source, die mit Masse verbunden ist, und ein Gate aufweist, das das Ausgangssignal des Leseverstärkers empfängt.

3. Erfassungsschaltung, die eine unabhängige Rückschreibefähigkeit aufweist, mit folgenden Merkmalen:

einem Leseverstärker (14), der ein Eingangssignal mit einem Referenzsignal vergleicht und ein Ausgangssignal erzeugt; und

einem Tri-State-fähigen Rückschreibeblock (12), der ein Aktivierungs- und ein Rückschreibeausgangssignal aufweist,

wobei das Ausgangssignal des Leseverstärkers mit dem Rückschreibeblock gekoppelt ist, wobei der Rückschreibeblock (12) folgende Merkmale umfaßt: einen ersten p-Kanal-Transistor, der eine Source aufweist, die mit Leistung verbunden ist;

einen zweiten p-Kanal-Transistor, der eine Source aufweist, die mit dem Drain des ersten p-Kanal-Transistors verbunden ist;

einen ersten n-Kanal-Transistor, der einen Drain aufweist, der mit dem Drain des zweiten p-Kanal-Transistors verbunden ist, der das Rückschreibeaus-

gangssignal bildet, das mit dem Eingangssignal verbunden ist; und

einen zweiten n-Kanal-Transistor, der einen Drain aufweist, der mit der Source des ersten n-Kanal-Transistors verbunden ist, und der eine Source aufweist, die mit Masse verbunden ist, wobei die Gates des ersten p-Kanal- und des zweiten n-Kanal-Transistors das Komplement des Ausgangssignals empfangen.

4. Leseverstärker mit folgenden Merkmalen: einem p-Kanal-Transistor, der eine Source, die mit Leistung verbunden ist, und einen ersten Drain aufweist;

einem ersten und einem zweiten Schenkel, wobei jeder Schenkel mit dem Drain des p-Kanal-Transistors und Masse verbunden ist, wobei jeder Schenkel ferner folgende Merkmale umfaßt:

einen ersten p-Kanal-Transistor, der eine Source aufweist, die mit dem ersten Drain verbunden ist, einen zweiten p-Kanal-Transistor, der eine Source aufweist, die mit dem Drain des ersten p-Kanal-Transistors an einem ersten Knoten verbunden ist, zwei n-Kanal-Transistoren, die parallel geschaltet und mit dem Drain des zweiten p-Kanal-Transistors an einem zweiten Knoten und Masse verbunden sind,

einen dritten n-Kanal-Transistor, der in Serie mit dem Gate des ersten p-Kanal-Transistors geschaltet ist, und

wobei für jeden Schenkel der zweite Knoten mit dem zweiten p-Kanal-Transistor und einem der beiden n-Kanal-Transistoren des anderen Schenkels verbunden ist; und

einem ersten n-Kanal-Transistor, der über die ersten Knoten des ersten und des zweiten Schenkels verbunden ist.

5. Erfassungsschaltung gemäß Anspruch 2, bei der der Datenpuffer (16) ferner folgende Merkmale umfaßt:

einen ersten p-Kanal-Transistor, der eine Source, die mit Leistung verbunden ist, ein Gate, das das Ausgangssignal des Leseverstärkers empfängt und einen Drain aufweist; und

einen zweiten p-Kanal-Transistor, der mit dem Drain des ersten p-Kanal-Transistors und dem Drain des ersten n-Kanal-Transistors verbunden ist und ein Gate aufweist, das mit VDD verbunden ist.

6. Erfassungsschaltung gemäß Anspruch 2, bei der der Datenpuffer (16) ferner folgende Merkmale umfaßt:

einen ersten p-Kanal-Transistor, der eine Source, die mit Leistung verbunden ist, ein Gate, das das Ausgangssignal des Leseverstärkers empfängt und einen Drain aufweist; und

einen zweiten p-Kanal-Transistor, der mit dem Drain des ersten p-Kanal-Transistors und dem Drain des ersten n-Kanal-Transistors verbunden ist und ein

Gate aufweist, das mit dem Komplement des Gate-Steuerungssignals des ersten n-Kanal-Transistors verbunden ist.

Es folgen 3 Blatt Zeichnungen

Anhängende Zeichnungen

N-KANAL-EINGANG

P-KANAL-EINGANG

**FIG.1** STAND DER TECHNIK

**FIG.2** STAND DER TECHNIK

FIG.3

FIG.4

FIG.7

14

FIG.5

14

FIG.6