(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4551146号

(P4551146)

(45) 発行日 平成22年9月22日(2010.9.22)

(24) 登録日 平成22年7月16日(2010.7.16)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| GO2F 1/1345 (2006.01) | GO2F 1/1345     |

| GO2F 1/13 (2006.01)   | GO2F 1/13 101   |

| GO2F 1/133 (2006.01)  | GO2F 1/133 550  |

| GO2F 1/1333 (2006.01) | GO2F 1/1333 500 |

| GO2F 1/1368 (2006.01) | GO2F 1/1368     |

請求項の数 11 (全 14 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2004-206356 (P2004-206356) |

| (22) 出願日     | 平成16年7月13日 (2004.7.13)       |

| (65) 公開番号    | 特開2005-37942 (P2005-37942A)  |

| (43) 公開日     | 平成17年2月10日 (2005.2.10)       |

| 審査請求日        | 平成18年5月29日 (2006.5.29)       |

| (31) 優先権主張番号 | 2003-047723                  |

| (32) 優先日     | 平成15年7月14日 (2003.7.14)       |

| (33) 優先権主張国  | 韓国 (KR)                      |

(73) 特許権者 390019839

三星電子株式会社

SAMSUNG ELECTRONICS

CO., LTD.

大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si,

Gyeonggi-do 442-742

(KR)

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

最終頁に続く

(54) 【発明の名称】下部基板用母基板、表示パネル用基板及び表示パネルの製造方法。

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに從属的に接続された複数のステージからなるシフトレジストに接続された全ての入力ラインを電気的に接続して外部から受信された第1検査信号を前記複数の入力ラインに提供する検査ラインと、前記シフトレジストとを含み、前記検査ラインを通じて提供される前記第1検査信号に応答して第2検査信号を出力する駆動部と、前記第2検査信号に応答して駆動する画素部とを含む下部基板と、

前記下部基板と対向する上部基板と、を含み、

前記シフトレジストは前記下部基板上に形成されることを特徴とする表示パネル用基板。

10

## 【請求項 2】

前記検査ラインは、

互いに所定の間隔に離隔した多数の入力ラインと、

前記入力ラインを電気的に連結する連結ラインと、で構成されることを特徴とする請求項1記載の表示パネル用基板。

## 【請求項 3】

前記下部基板の端部には前記入力ラインの端部が配置され、前記入力ラインの端部の間に電気的に連結された連結ラインが前記下部基板のエッジに配置されることを特徴とする請求項2記載の表示パネル用基板。

## 【請求項 4】

20

前記下部基板は部分的にグラインドされ、前記下部基板がグラインドされる時、前記エッジ部に配置される前記入力ラインの端部と前記連結ラインの端部は除去されることを特徴とする請求項3記載の表示パネル用基板。

**【請求項5】**

前記複数の入力ラインは開始信号入力ラインと、クロック入力ラインと、駆動電圧入力ラインと、を含むことを特徴とする請求項2記載の表示パネル用基板。

**【請求項6】**

前記駆動電圧入力ラインは前記開始信号入力ラインとクロック入力ラインより大きい幅を有することを特徴とする請求項5記載の表示パネル用基板。

**【請求項7】**

前記駆動電圧入力ラインは外部から前記第1検査信号を受信し、受信された前記第1検査信号を前記検査ラインに提供することを特徴とする請求項6記載の表示パネル用基板。

**【請求項8】**

前記下部基板と上部基板との間に介在される液晶層をさらに含むことを特徴とする請求項1記載の表示パネル用基板。

**【請求項9】**

互いに従属性に接続された複数のステージからなるシフトレジストに接続された全ての入力ラインを電気的に接続して外部から受信された第1検査信号を前記複数の入力ラインに提供する検査ラインと、下部基板に形成され、前記複数のシフトレジストを含み、前記検査ラインから提供される前記第1検査信号に応答して第2検査信号を出力する駆動部と、前記第2検査信号に応答して駆動する画素部とを含む下部基板及び、前記下部基板と対向する上部基板で構成される表示パネル用基板を製造する段階と、

前記検査ラインに前記第1検査信号を提供して前記駆動部及び画素部を検査する段階と、

前記検査ラインと前記入力ラインとを絶縁させて表示パネルを完成する段階と、を含み、

前記シフトレジストは前記下部基板上に形成されることを特徴とする表示パネル製造方法。

**【請求項10】**

前記表示パネル用基板を製造する段階以前には、

前記検査ラインから延長された検査パッド部を具備する下部基板用母基板を製造する段階と、

前記検査パッド部に前記第1検査信号を提供して前記下部基板用母基板を検査する段階と、

上部基板用母基板を製造する段階と、

前記下部基板用母基板と前記上部基板用母基板とを結合する段階と、

結合された基板を表示パネル単位で切断して前記表示パネル用基板を完成する段階と、を含むことを特徴とする請求項9記載の表示パネル製造方法。

**【請求項11】**

前記表示パネル用基板の端部をグラインディング処理することで前記検査ラインをとり除くことを特徴とする請求項9記載の表示パネル製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は下部基板用母基板、表示パネル用基板及び表示パネルの製造方法に関する。

**【背景技術】**

**【0002】**

液晶表示装置は、一般に、映像を表示する液晶表示パネル、液晶表示パネルを駆動するためのゲート及びデータ駆動部を含む。

**【0003】**

液晶表示パネルは下部基板、下部基板と向い合う上部基板及び下部基板と上部基板との

10

20

30

40

50

間に介在された液晶層で構成される。下部基板には第1方向に延長されたデータライン、第1方向と直交する第2方向に延長されたゲートライン、ゲートラインとデータラインによって定義される画素領域でゲート及びデータラインに連結された画素を含む。画素は薄膜トランジスタ（以下、TFTと称する）及びTFTに連結された液晶キャパシターの第1電極として利用される画素電極で構成される。

【0004】

ゲート駆動部はゲートラインに連結されてゲート駆動信号を出力し、データ駆動部はデータラインに連結されてデータ信号を出力する。一般に、ゲート及びデータ駆動部はチップ形態で液晶表示パネル上に実装されるかテープキャリアパッケージ（以下、TCPと称する）に実装されて液晶表示パネルと電気的に連結される。

10

【0005】

ゲート駆動部をチップ形態で具現して液晶表示パネルに直接実装する場合、ゲート駆動部を前記液晶表示パネル上に実装する以前に液晶表示パネルが正常に動作するかを検査するための検査工程が先行される。即ち、検査工程を通じて正常に動作可能なことで判定された液晶表示パネルにのみ前記ゲート駆動部を実装する。

【0006】

しかし、最近には液晶表示パネルにTFTを形成する工程を通じてゲート駆動部が共に下部基板の一側に直接集積されている。従って、ゲート駆動部が下部基板に予め集積されている状態で液晶表示パネルが正常に動作するかを検査することができる方案が必要とされる

20

【発明の開示】

【発明が解決しようとする課題】

【0007】

従って、本発明はゲート駆動部が集積されている表示パネルの生産性及び収率を向上させるための下部基板用母基板を提供する。

【0008】

本発明は、ゲート駆動部が集積されている表示パネルの生産性及び収率を向上させるための表示パネル用基板を提供する。

【0009】

本発明はゲート駆動部が集積されている表示パネルの生産性及び収率を向上させるための表示パネルの製造方法を提供する。

30

【課題を解決するための手段】

【0010】

第1に、互いに従属的に接続された複数のステージからなるシフトレジストに接続された全ての入力ラインを電気的に接続して外部から受信された第1検査信号を前記複数の入力ラインに提供する検査ラインと、前記シフトレジストとを含み、前記検査ラインを通じて提供される前記第1検査信号に応答して第2検査信号を出力する駆動部と、前記第2検査信号に応答して駆動する画素部とを含む下部基板と、前記下部基板と対向する上部基板と、を含み、前記シフトレジストは前記下部基板上に形成されることを特徴とする表示パネル用基板を提供する。

40

【0011】

前記検査ラインは、互いに所定の間隔に離隔した多数の入力ラインと、前記入力ラインを電気的に連結する連結ラインと、で構成されることを特徴とする。

前記下部基板の端部には前記入力ラインの端部が配置され、前記入力ラインの端部の間に電気的に連結された連結ラインが前記下部基板のエッジに配置されることを特徴とする。

【0012】

前記下部基板は部分的にグラインドされ、前記下部基板がグラインドされる時、前記エッジ部に配置される前記入力ラインの端部と前記連結ラインの端部は除去されることを特徴とする。

50

前記複数の入力ラインは開始信号入力ラインと、クロック入力ラインと、駆動電圧入力ラインと、を含むことを特徴とする。

【0013】

前記駆動電圧入力ラインは前記開始信号入力ラインとクロック入力ラインより大きい幅を有することを特徴とする。

前記駆動電圧入力ラインは外部から前記第1検査信号を受信し、受信された前記第1検査信号を前記検査ラインに提供することを特徴とする。

前記下部基板と上部基板との間に介在される液晶層をさらに含むことを特徴とする。

【0014】

第2に、互いに従属的に接続された複数のステージからなるシフトレジストに接続された10

全ての入力ラインを電気的に接続して外部から受信された第1検査信号を前記複数の入

力ラインに提供する検査ラインと、下部基板に形成され、前記複数のシフトレジストを含

み、前記検査ラインから提供される前記第1検査信号に応答して第2検査信号を出力する

駆動部と、前記第2検査信号に応答して駆動する画素部とを含む下部基板及び、前記下部

基板と対向する上部基板で構成される表示パネル用基板を製造する段階と、前記検査ライ

ンに前記第1検査信号を提供して前記駆動部及び画素部を検査する段階と、前記検査ライ

ンと前記入力ラインとを絶縁させて表示パネルを完成する段階と、を含み、前記シフトレ

ジストは前記下部基板上に形成されることを特徴とする表示パネル製造方法を提供する。

【0015】

前記表示パネル用基板を製造する段階以前には、前記検査ラインから延長された検査パッド部を具備する下部基板用母基板を製造する段階と、前記検査パッド部に前記第1検査信号を提供して前記下部基板用母基板を検査する段階と、上部基板用母基板を製造する段階と、前記下部基板用母基板と前記上部基板用母基板とを結合する段階と、結合された基板を表示パネル単位で切断して前記表示パネル用基板を完成する段階と、を含むことを特徴とする。

前記表示パネル用基板の端部をグラインディング処理することで前記検査ラインをとり除くことを特徴とする。

【0016】

このような下部基板用母基板、表示パネル用基板及び表示パネルの製造方法によると、駆動部が集積されている表示パネルを製造する過程で下部基板用母基板及び表示パネル用基板が完成された段階で容易く検査工程を実施することができる。これによって、表示パネルの生産性及び収率を向上させることができる。

【発明を実施するための最良の形態】

【0017】

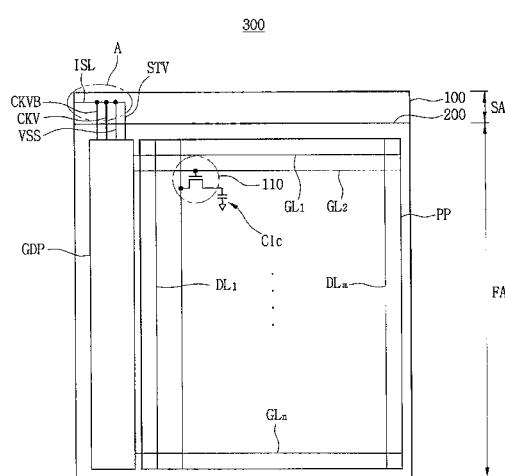

図1は本発明の一実施例による表示パネル用結合基板を示す平面図である。

【0018】

図1に示すように、本発明の一実施例による表示パネル用結合基板(300)は、下部基板(100)、前記下部基板(100)と向い合う上部基板(200)を含む。

【0019】

前記上部基板(200)は、前記下部基板(100)より小さなサイズを有する。従つて、前記下部基板(100)は、前記上部基板(200)と向い合う第1領域(FA)と、前記上部基板(200)と向い合わない第2領域(SA)と、で区分される。前記下部基板(100)は、映像を表示する画素部(PP)及び前記画素部(PP)を駆動するゲート駆動部(GDP)で構成される。

【0020】

前記画素部(PP)は、複数のゲートライン(GL1~GLn)、前記複数のゲートライン(GL1~GLn)と直交する複数のデータライン(DL1~DLm)を具備し、前記ゲートライン(GL1~GLn)とデータライン(DL1~DLm)によって定義される領域にはTFT(110)及び液晶キャパシター(C1c)の第1電極である画素電極がそれぞれ具備される。

10

20

30

40

50

## 【0021】

前記ゲート駆動部（GDP）は、前記複数のゲートライン（GL1～GLn）の一端部に電気的に連結され、前記複数のゲートライン（GL1～GLn）に駆動信号を出力する。前記ゲート駆動部（GDP）は、例えば外部から各種信号の提供を受ける開始信号入力ライン（STV）、第1クロック入力ライン（CKV）、第2クロック入力ライン（CKVB）及びアース電圧入力ライン（VSS）と電気的に連結されている。

## 【0022】

ここで、前記各入力ライン（STV、CKV、CKVB、VSS）は、互いに所定の間隔で離隔され、互いに実質的に一直線に配置される。前記各入力ライン（STV、CKV、CKVB、VSS）の一端部は、外部から前記各種信号の提供を受けるために前記ゲート駆動部（GDP）から前記第2領域（SA）にまで延長される。また、前記各入力ライン（STV、CKV、CKVB、VSS）は前記下部基板100上に形成される。

10

## 【0023】

前記下部基板（100）の前記第2領域（SA）には、前記入力ライン（STV、CKV、CKVB、VSS）に電気的に連結された検査ライン（ISL）が具備される。従って、前記入力ライン（STV、CKV、CKVB、VSS）は、前記検査ライン（ISL）を通じて互いに電気的に連結される。前記検査ライン（ISL）は外部から検査信号を受信して前記入力ライン（STV、CKV、CKVB、VSS）に提供する。

## 【0024】

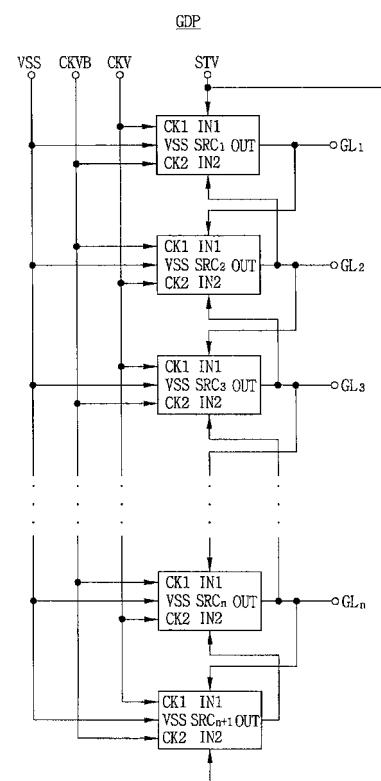

図2は図1に図示されたゲート駆動部と入力ラインを具体的に示す図面である。

20

## 【0025】

図2に示すように、ゲート駆動部（GDP）は互いに従属的に連結された複数のステージ（SRC1～SRCn+1）からなる一つのシフトレジスタを含む。

## 【0026】

前記複数のステージ（SRC1～SRCn+1）は、それぞれ第1クロック端子（CK1）、第2クロック端子（CK2）、第1入力端子（IN1）、第2入力端子（IN2）、出力端子（OUT）及びアース電圧端子（VSS）を具備する。

## 【0027】

前記複数のステージのうち、奇数番目のステージ（SRC1、SRC3、SRCn+1）の前記第1クロック端子（CK1）には第1クロック（CKV）が提供され、偶数番目のステージ（SRC2、SRCn）の前記第1クロック端子（CK2）には前記第1クロック（CKV）と異なる位相を有する第2クロック（CKVB）が提供される。

30

## 【0028】

一方、前記奇数番目のステージ（SRC1、SRC3、…、SRCn+1）の前記第2クロック端子（CK2）には前記第2クロック（CKVB）が提供され、前記偶数番目ステージ（SRC2、…、SRCn）の前記第2クロック端子（CK2）には前記第1クロック（CKV）が提供される。ここで、前記第1クロック（CKV）と前記第2クロック（CKVB）は互いに反転された位相を有する。

## 【0029】

前記奇数番目ステージ（SRC1、SRC3、…、SRCn+1）の前記出力端子（OUT）は、前記第1クロック（CKV）を出力し、前記偶数番目のステージ（SRC2、…、SRCn）の前記出力端子（OUT）は前記第2クロック（CKVB）を出力する。

40

## 【0030】

前記n個のステージ（SRC1～SRCn）の出力端子（OUT）は前記画素部（PP、図1に図示される）に具備されたn個のゲートライン（GL1～GLn）のうち、対応するゲートラインに電気的に連結される。従って、前記シフトレジスタは前記n個のゲートライン（GL1～GLn）を順次に駆動する。

## 【0031】

前記第1入力端子（IN1）には前段ステージの出力端子（OUT）から出力された信号が印加され、前記第2入力端子（IN2）には次段ステージの出力端子（OUT）から

50

出力された信号が印加される。ここで、前記一番目のステージ (S R C 1) の第1入力端子 (I N 1) には前段ステージの出力信号ではなく開始信号 (S T V) が提供される。また、n 番目ステージ (S R C n) の第2入力端子 (I N 2) に出力信号を提供するために用意された n+1 番目ステージ (S R C n+1) の第2入力端子 (I N 2) には、次段ステージの出力信号の代りに前記開始信号 (S T V) が提供される。

【0032】

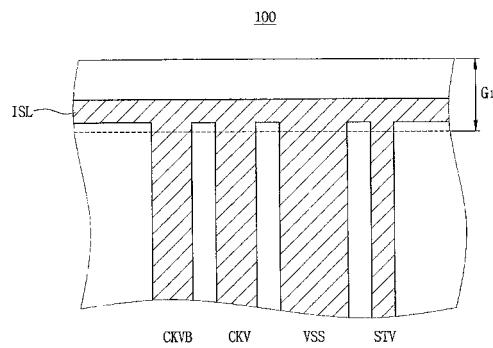

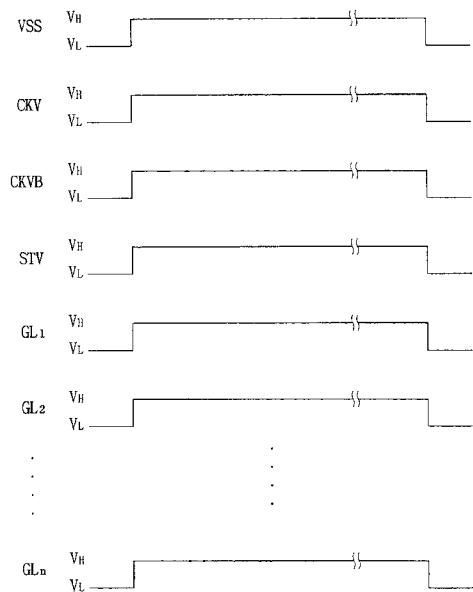

図3は図1に図示されたA部分の拡大図で、図4は図1に図示された表示パネル用結合基板を検査するために前記入力ライン及びゲートラインに印加される信号の波形図である。

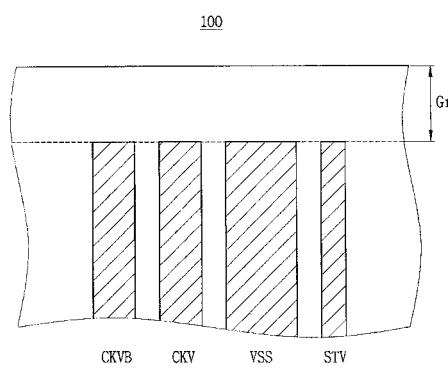

【0033】

図3に示すように、前記下部基板 (100) の第2領域 (S A) には検査ライン (I S L) が具備され、前記検査ライン (I S L) は、前記開始信号入力ライン (S T V)、アース電圧入力ライン (V S S)、第1クロック入力ライン (C K V) 及び第2クロック入力ライン (C K V B) に共通に連結される。

【0034】

特に、前記検査ライン (I S L) は、グラインディング (grinding) 領域 (G 1) に具備され、前記グラインディング領域 (G 1) 内で前記開始信号入力ライン (S T V)、アース電圧入力ライン (V S S)、第1クロック入力ライン (C K V) 及び第2クロック入力ライン (C K V B) と電気的に連結される。ここで、前記グラインディング領域 (G 1) は、前記表示パネル (図示せず) が完成される前に実施されるグラインディング工程のために用意された領域である。前記グラインディング領域 (G 1) は、例えば、下部基板 (100) の端部に設けられている。

【0035】

この実施例において、前記入力ライン (S T V、C K V、C K V B、V S S) のうち、前記アース電圧入力ライン (V S S) が最も広い幅を有する。従って、前記検査信号はまず、前記アース電圧入力ライン (V S S) に提供され、前記アース電圧入力ライン (V S S) に提供された前記検査信号は前記検査ライン (I S L) を通じて他の入力ライン (C K、C K V B、S T V) に提供されることができる。特に、肉眼検査 (以下、V/Iと称する) 工程で、前記アース電圧入力ライン (V S S) には検査信号が提供される。受信された前記検査信号は前記検査ライン (I S L) を通じて前記開始信号入力ライン (S T V)、第1クロック入力ライン (C K V) 及び第2クロック入力ライン (C K V B) にそれぞれ提供される。

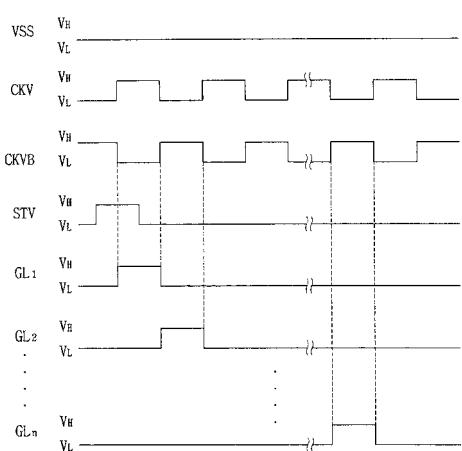

【0036】

図4に図示されたように、前記検査信号は所定の電圧レベルを有する信号として、前記開始信号入力ライン (S T V)、第1クロック入力ライン (C K V)、第2クロック入力ライン (C K V B) 及びアース電圧入力ライン (V S S) にそれぞれ提供される。ここで、後述のように、前記検査信号は複数のステージを同時に駆動させるくらいの電圧レベルを有している。前記検査信号は、前記入力ライン (S T V、C K V、C K V B、V S S) を通じて前記ゲート駆動部 (G D P) (図2に図示される) の各ステージに提供されて前記複数のステージを同時に駆動させる。従って、前記複数のステージ (S R C 1 ~ S R C n) に連結された n 個のゲートライン (G L 1 ~ G L n) には駆動信号が同時に output される。

【0037】

図面に図示していないが、前記画素部 (P P) (図1に図示される) に具備された複数のデータライン (D L 1 ~ D L m) も検査信号を受信する。前記データライン (D L 1 ~ D L m) は全体的に連結されるかグループ単位で連結されて前記検査信号を受信することができる。ここで、前記グループは偶数番目のデータラインからなる第1グループと奇数番目のデータラインからなる第2グループとで構成される。全体あるいはグループ単位で複数のデータライン (D L 1 ~ D L m) に前記検査信号が提供され、前記ゲートライン (G 1 ~ G L n) にも前記検査信号が提供されると、前記表示パネル用結合基板 (300)

10

20

30

40

50

は画面を表示する。従って、使用者（あるいは検査者）は肉眼で前記表示パネル用結合基板（300）の不良を検査することができる。

【0038】

図5はグラインディング（grinding）された表示パネルを示す図面で、図6は映像を表示する過程でゲートライン及び入力ラインに印加された信号の波形図である。図5に示すように、V/I工程が完了した表示パネル用結合基板（300）（図1に図示される）は、グラインディング工程を経た後、表示パネルとして完成される。前記グラインディング工程を通じて、図5に示す前記グラインディング領域（G1）内にいる前記下部基板の端部が、柔らかい表面構造を有するようになる。

【0039】

前記グラインディング工程を経た表示パネルには、互いに所定の間隔で離隔され絶縁状態を保持する入力ライン（STV、CKV、CKVB、VSS）が具備される。即ち、開始信号入力ライン（STV）、第1クロック入力ライン（CKV）、第2クロック入力ライン（CKVB）及びアース電圧入力ライン（VSS）を互いに電気的に連結させた検査ラインはグラインディング工程によって前記下部基板（100）から除去される。

【0040】

従って、前記開始信号入力ライン（STV）、第1クロック入力ライン（CKV）、第2クロック入力ライン（CKVB）及びアース電圧入力ライン（VSS）は、互いに絶縁された状態で保持されることができる。

【0041】

図6に図示されたように、表示パネルの画素部（PP）を駆動するために、前記開始信号入力ライン（STV）、第1クロック入力ライン（CKV）、第2クロック入力ライン（CKVB）及びアース電圧入力ライン（VSS）に開始信号、第1クロック、第2クロック及びアース電圧がそれぞれ提供される。

【0042】

前記ゲート駆動部（GDP）は開始信号（STV）、第1クロック（CKV）、第2クロック（CKVB）及びアース電圧（VSS）に応答して前記複数のステージ（SRC1～SRCn）から順次に、ゲートライン（GL1～GL2）に駆動信号を出力する。これによって、前記表示パネルの画素部（PP）を駆動することができる。

【0043】

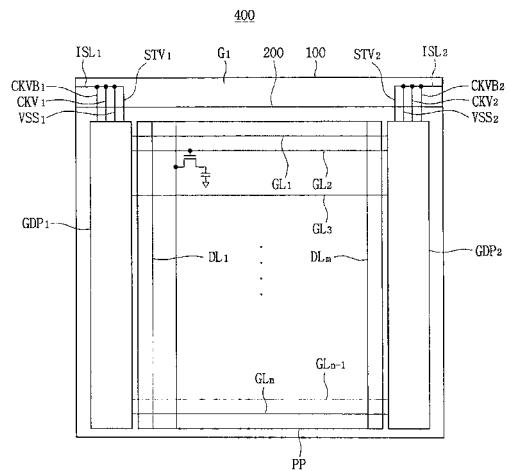

図7は本発明の他の実施例による表示パネル用結合基板を示す平面図である。たである。、図7では図1に図示された構成要素と等しい構成要素に対しては等しい参照符号を付与し、それに対する具体的な説明は省略する。

【0044】

図7に示すように、本発明の他の実施例による表示パネル用結合基板（400）は、下部基板（100）、前記下部基板（100）と向い合う上部基板（200）を含む。

【0045】

前記下部基板（100）は、映像を表示する画素部（PP）、前記画素部（PP）の左側周辺に具備された第1ゲート駆動部（GDP1）及び前記画素部（PP）の右側周辺に具備された第2ゲート駆動部（GDP2）で構成される。

【0046】

前記第1ゲート駆動部（GDP1）は前記複数のゲートライン（GL1～GL2）の一端部に結合され奇数番目のゲートライン（G1～GLn-1）に駆動信号を出力する。また、前記第2ゲート駆動部（GDP2）は前記複数のゲートライン（GL1～GL2）の一端部に結合され偶数番目のゲートライン（GL2～GLn）に駆動信号を出力する。

【0047】

前記第1ゲート駆動部（GDP1）は、外部から各種信号の提供を受ける第1開始信号入力ライン（STV1）、第1クロック入力ライン（CKV1）、第2クロック入力ライン（CKVB1）及び第1アース電圧入力ライン（VSS1）と電気的に連結される。

【0048】

10

20

30

40

50

前記下部基板(100)は、グラインディング領域(G1)(図3に図示される)に前記入力ライン(STV1、CKV1、CKVB1、VSS1)と電気的に連結された第1検査ライン(ISL1)を具備する。従って、前記入力ライン(STV1、CKV1、CKVB1、VSS1)は前記第1検査ライン(ISL1)を通じて互いに電気的に連結される。

【0049】

前記第2ゲート駆動部(GDP2)は、外部から各種信号の提供を受ける第2開始信号入力ライン(STV2)、第3クロック入力ライン(CKV2)、第4クロック入力ライン(CKVB2)及び第2アース電圧入力ライン(VSS2)と電気的に連結される。前記下部基板(100)は、グラインディング領域(G1)に前記入力ライン(STV2、CKV2、CKVB2、VSS2)と電気的に連結された第2検査ライン(ISL2)をさらに具備する。従って、前記入力ライン(STV2、CKV2、CKVB2、VSS2)は前記第2検査ライン(ISL2)を通じて互いに電気的に連結される。

10

【0050】

前記第1及び第2アース電圧入力ライン(VSS1、VSS2)は、他の入力ラインより広い幅を有する。従って、前記第1アース電圧入力ライン(VSS1)は、外部から検査信号を受信して前記第1検査ライン(ISL2)に提供して、前記第2アース電圧入力ライン(VSS2)は外部から検査信号を受信して前記第2検査ライン(ISL2)に提供する。

【0051】

20

肉眼検査(以下、V/Iと称する)工程で、前記第1アース電圧入力ライン(VSS1)に検査信号が提供されると、受信された前記検査信号は前記第1検査ライン(ISL1)を通じて前記第1開始信号入力ライン(STV1)、第1クロック入力ライン(CKV1)及び第2クロック入力ライン(CKVB1)に提供される。

【0052】

また、前記第2アース電圧入力ライン(VSS2)に検査信号が提供されると、受信された前記検査信号は前記第2検査ライン(ISL2)を通じて前記第2開始信号入力ライン(STV2)、第3クロック入力ライン(CKV2)及び第4クロック入力ライン(CKVB2)に提供される。

【0053】

30

前記検査信号は、前記第1ゲート駆動部(GDP1)の各ステージに提供されて複数のステージを同時に駆動させる。従って、前記複数のステージ(SRC1～SRCn)に連結された奇数番目のゲートライン(G1～GLn-1)に駆動信号を同時に出力する。

【0054】

また、前記検査信号は、前記第2ゲート駆動部(GDP2)の各ステージに提供されて複数のステージを同時に駆動させる。従って、前記複数のステージ(SRC1～SRCn)に連結された偶数番目のゲートライン(GL2～GLn)に駆動信号を同時に出力する。

【0055】

図1ないし図7に図示していないが、前記表示パネル用結合基板(300、400)は前記下部基板(100)と上部基板(200)との間に液晶層(図示せず)を介在する液晶表示パネル用結合基板であることができる。

40

【0056】

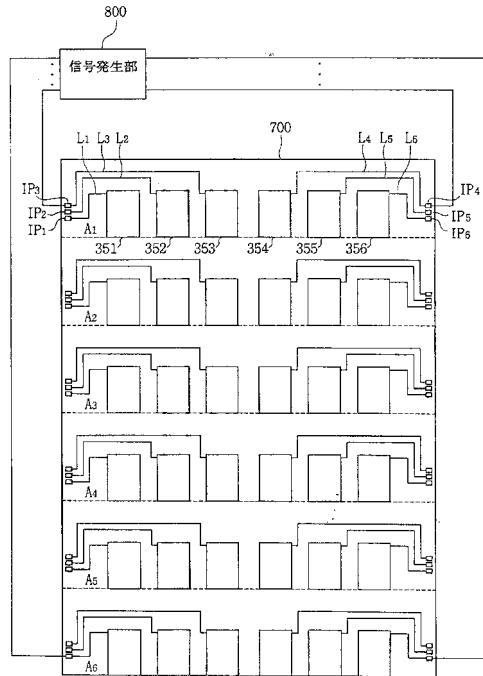

図8は本発明のまた他の実施例による下部基板用母基板を具体的に示す図面である。

【0057】

図8に示すように、本発明の他の実施例による下部基板用母基板(700)は、互いに等しい構造を有する第1ないし第6領域(A1、A2、A3、A5、A6)で構成される。以下、前記第1領域(A1)の構造に対して説明することで、前記第2ないし第6領域(A2～A6)に対する説明に代る。この実施例において、6個のTFT領域が前記第1ないし第6領域(A1、A2、A3、A5、A6)にそれぞれ形成されることを一例とし

50

て説明するが、前記 TFT 領域の数は可変されることがある。

【0058】

前記第1領域 (A1) には、第1ないし第6 TFT 領域 (351～356) が具備される。前記第1領域 (A1) の左側には信号発生部 (800) から検査信号の入力を受ける第1ないし第3検査パッド部 (IP1、IP2、IP3) が具備される。前記第1ないし第3 TFT 領域 (351～353) と前記第1ないし第3検査パッド部 (IP1～IP3) とは第1ないし第3外部検査ライン (L1、L2、L3) を通じてそれぞれ電気的に連結される。

【0059】

図8に図示していないが、前記第1ないし第3外部検査ライン (L1～L3) は前記第1ないし第3 TFT 領域 (351～353) の内部に具備された検査ラインとそれぞれ電気的に連結される。従って、前記第1ないし第3 TFT 領域 (351～353) は、前記検査信号によって駆動される。これによって、前記下部基板用母基板 (700) に形成された前記第1ないし第3 TFT 領域 (351～353) を検査することができる。各、第1ないし第6 TFT 領域 (351～356) に設けられた、内部の検査ラインは、図1や図7に示すように構成されていても良い。

10

【0060】

また、前記第1領域 (A1) の右側には前記信号発生部 (800) から前記検査信号の入力を受ける第4ないし第6検査パッド部 (IP4、IP5、IP6) が具備される。前記第4ないし第6 TFT 領域 (354～356) と前記第4ないし第6検査パッド部 (IP4～IP6) とは第4ないし第6外部検査ライン (L4、L5、L6) を通じて連結される。

20

【0061】

図8に図示していないが、前記第4ないし第6外部検査ライン (L4～L6) は、前記第4ないし第6 TFT 領域 (354～356) の内部に具備された検査ラインとそれぞれ電気的に連結される。従って、前記第4ないし第6 TFT 領域 (354～356) は、前記検査信号によって駆動される。これによって、前記下部基板用母基板 (700) に形成された前記第4ないし第6 TFT 領域 (354～356) を検査することができる。

【0062】

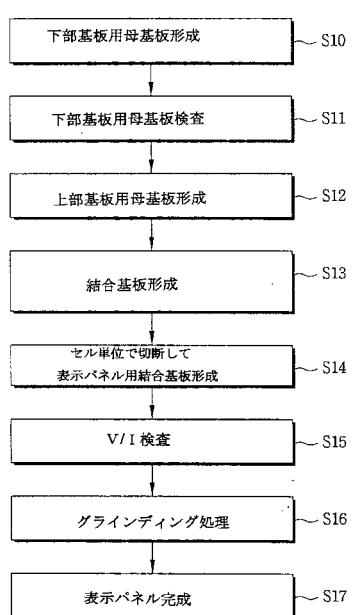

図9は本発明のまた他の実施例による表示パネルの製造方法を示す工程図である。

30

【0063】

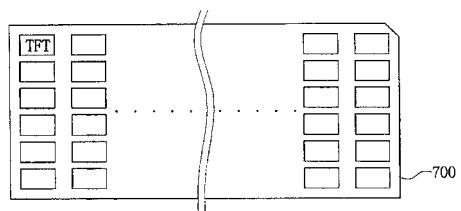

図10は図9に図示された製造方法によって製造された下部基板用母基板を示す図面で、図11は図9に図示された製造方法によって製造された上部基板用基板を示す図面である。図12は図9に図示された製造方法により製造された結合基板を示す断面図である。

【0064】

図9及び図10に示すように、複数のTFT領域 (TFT) が形成された下部基板用母基板 (700) が完成される (S10)。以後、完成された前記下部基板用母基板 (700) を検査する (S11)。

【0065】

具体的に、図8に図示されたように、前記下部基板用母基板 (700) に具備されている検査パッド部 (IP1～IP6) に検査信号を印加すると、前記検査信号は外部検査ライン (L1～L6) を通じて各TFT領域 (TFT) に印加される。各TFT領域 (TFT) に印加された前記検査信号はゲート駆動部 (GDP) を駆動させてn個のゲートライン (GL1～GL2) (図1に図示される) に駆動信号を同時に出力する。これによって、前記下部基板用母基板 (700) に形成されている前記各TFT領域 (TFT) を検査することができる。

40

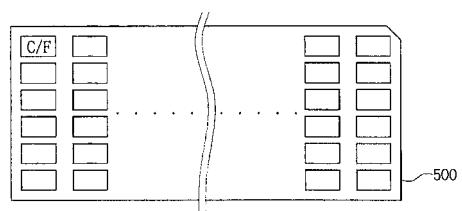

【0066】

次に、図9及び図11に示すように、複数のカラーフィルター領域 (C/F) が形成された上部基板用母基板 (500) が完成される (S12)。前記複数のカラーフィルター領域 (C/F) は、前記下部基板用母基板 (700) のTFT領域 (PP) と一対一で対

50

応する。

【0067】

前記カラーフィルター領域 (C/F) それぞれは、R、G、B 色画素からなるカラーフィルター (味到の時) 及び前記カラーフィルター上に形成され液晶キャパシター (C1c) (図1に図示される) の第2電極に利用される共通電極 (図示せず) を含む。

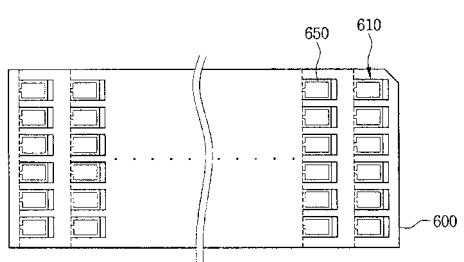

【0068】

以後、図9及び図12に示すように、完成された下部基板用母基板 (700) と上部基板用母基板 (500) とが互いに対向され、結合部材 (以下、シーラント) (650) は、前記下部基板用母基板 (700) と上部基板用母基板 (500)との間に介在されてこれらを結合させる。これによって、複数のセル (610) を有する結合基板 (600) が完成される (S13)。 10

【0069】

次に、前記結合基板 (600) を前記セル単位で切断して、表示パネル用結合基板 (300) を完成する (S14)。以後、前記表示パネル用結合基板 (300) が正常に駆動されるかを検査するためのV/I検査工程を実施する (S15)。

【0070】

前記V/I検査工程が完了すると、前記表示パネル用結合基板 (300) の端部をグラインディング処理する (S16)。従って、V/I工程のために前記表示パネル用結合基板 (300) に形成された検査ラインが除去される。これによって、前記表示パネル用結合基板 (300) が表示パネルとして完成される (S17)。 20

【0071】

このような下部基板用母基板、表示パネル用基板及び表示パネルの製造方法によると、下部基板は、第1検査信号を受信する検査ライン、前記検査ラインと電気的に連結され前記第1検査信号に応答して第2検査信号を出力するゲート駆動部及び前記第2検査信号に応答して駆動する画素部で構成される。

【0072】

従って、前記ゲート駆動部が集積されている表示パネルを製造する過程の下部基板用母基板及び表示パネル用基板が完成された段階で、前記ゲート駆動部を通じて前記画素部を容易に検査することができる。これによって、表示パネルの生産性及び収率を向上させることができる。 30

【0073】

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離れることなく、本発明を修正または変更できる。

【図面の簡単な説明】

【0074】

【図1】本発明の一実施例による表示パネル用結合基板を示す平面図である。

【図2】図1に図示されたゲート駆動部と入力ラインを具体的に示す図面である。

【図3】図1に示されたA部分の拡大図である。

【図4】検査工程で前記入力ライン及びゲートラインに印加される信号の波形図である。

【図5】グラインディングされた表示パネルを示す図面である。

【図6】映像を表示する過程でゲートライン及び入力ラインに印加された信号の波形図である。

【図7】本発明の他の実施例による表示パネル用結合基板を示す平面図である。

【図8】本発明のまた他の実施例による下部基板用母基板を具体的に示す図面である。

【図9】本発明のまた他の実施例による表示パネルの製造方法を示す工程図である。

【図10】図8の段階S10で製造された下部基板用母基板を示す図面である。

【図11】図8の段階S12で製造された上部基板用母基板を示す図面である。

【図12】図8の段階S13で製造された結合基板を示す図面である。

【符号の説明】

10

20

30

40

50

## 【0075】

PP画素部

100 下部基板

200 上部基板

300、400 表示パネル用結合基板

500 上部基板用母基板

600 結合基板

650 シーラント

700 下部基板用母基板

800 信号発生部

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

|                        |                    |

|------------------------|--------------------|

| (51)Int.Cl.            | F I                |

| G 0 9 F 9/00 (2006.01) | G 0 9 F 9/00 3 5 2 |

| G 0 9 F 9/30 (2006.01) | G 0 9 F 9/30 3 3 8 |

(72)発明者 李 栢 遠

大韓民国ソウル特別市瑞草区方背本洞779-7番地401号

審査官 福田 知喜

(56)参考文献 特開平02-267527 (JP, A)

特開2002-229056 (JP, A)

特開2002-009407 (JP, A)

特開平08-190087 (JP, A)

特開平05-005866 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |             |

|---------|-------------|

| G 0 2 F | 1 / 1 3 4 5 |

| G 0 2 F | 1 / 1 3     |

| G 0 2 F | 1 / 1 3 3   |

| G 0 2 F | 1 / 1 3 3 3 |

| G 0 2 F | 1 / 1 3 6 8 |

| G 0 9 F | 9 / 0 0     |

| G 0 9 F | 9 / 3 0     |