(12)发明专利

(10)授权公告号 CN 106997746 B

(45)授权公告日 2019.07.23

(21)申请号 201611097179.2

(22)申请日 2016.12.02

(65)同一申请的已公布的文献号

申请公布号 CN 106997746 A

(43)申请公布日 2017.08.01

(30)优先权数据

2016-012135 2016.01.26 JP

(73)专利权人 株式会社日本显示器

地址 日本东京都

(72)发明人 涩泽诚 木村裕之 森田哲生

(74)专利代理机构 北京尚诚知识产权代理有限公司 11322

代理人 邝万杰 徐飞跃

(51)Int.Cl.

G09G 3/3208(2016.01)

(54)发明名称

显示装置

(57)摘要

本发明提供一种可实现窄边框的显示装置。该显示装置包括：发光元件；与发光元件连接的驱动晶体管；与驱动晶体管和主电源线连接的第一开关元件；与驱动晶体管和复位电源线连接的第二开关元件；与驱动晶体管和信号线连接的第三开关元件；与第三开关元件和初始化电源线连接的第四开关元件；和与驱动晶体管和第三开关元件连接的电容元件，第二开关元件、第三开关元件和第四开关元件各自的栅极端子被供给2个水平期间的导通信号。

(56)对比文件

CN 100583212 C, 2010.01.20, 说明书第6-14页, 附图1-8.

US 2011193850 A1, 2011.08.11, 说明书20-70段, 附图1-5.

US 2015187323 A1, 2015.07.02, 说明书64-82段, 附图3-6b.

CN 101751846 A, 2010.06.23, 全文.

CN 101093641 A, 2007.12.26, 全文.

CN 203480807 U, 2014.03.12, 全文.

CN 1744182 A, 2006.03.08, 全文.

KR 20080109137 A, 2008.12.17, 全文.

CN 103680406 A, 2014.03.26, 全文.

CN 100587776 C, 2010.02.03, 全文.

CN 103117041 A, 2013.05.22, 全文.

审查员 张辉

权利要求书4页 说明书13页 附图9页

1. 一种显示装置,其特征在于:

具有在行方向和列方向上排列的多个像素,

所述多个像素各自具有:

发光元件;

源极和漏极中的一者与所述发光元件连接的驱动晶体管;

第一开关元件,其源极和漏极中的一者与所述驱动晶体管的源极和漏极中的另一者连接,源极和漏极中的另一者与主电源线连接;

第二开关元件,其源极和漏极中的一者与所述驱动晶体管的源极和漏极中的一者连接,源极和漏极中的另一者与复位电源线连接;

第三开关元件,其源极和漏极中的一者与所述驱动晶体管的栅极端子连接,源极和漏极中的另一者与信号线连接;

第四开关元件,其源极和漏极中的一者与所述第三开关元件的源极和漏极中的一者连接,源极和漏极中的另一者与初始化电源线连接;和

电容元件,其一个电极与所述驱动晶体管的源极和漏极中的一者连接,另一个电极与所述第三开关元件的源极和漏极中的一者连接,

所述第二开关元件、所述第三开关元件和所述第四开关元件各自的栅极端子被供给2个水平期间的导通信号,

所述显示装置具有第一复位期间、第二复位期间、阈值补偿期间和写入期间,

在所述第一复位期间,所述第一开关元件为截止状态,所述第二开关元件为导通状态,所述第三开关元件为截止状态,所述第四开关元件为截止状态,

在所述第二复位期间,所述第一开关元件为截止状态,所述第二开关元件为导通状态,所述第三开关元件为截止状态,所述第四开关元件为导通状态,

在所述阈值补偿期间,所述第一开关元件为导通状态,所述第二开关元件为截止状态,所述第三开关元件为截止状态,所述第四开关元件为导通状态,

在所述写入期间,所述第一开关元件为截止状态,所述第二开关元件为截止状态,所述第三开关元件为导通状态,所述第四开关元件为截止状态。

2. 一种显示装置,其特征在于:

具有在行方向和列方向上排列的多个像素,

所述多个像素各自具有:

发光元件;

源极和漏极中的一者与所述发光元件连接的驱动晶体管;

第一开关元件,其源极和漏极中的一者与所述驱动晶体管的源极和漏极中的另一者连接,源极和漏极中的另一者与主电源线连接;

第二开关元件,其源极和漏极中的一者与所述驱动晶体管的源极和漏极中的一者连接,源极和漏极中的另一者与复位电源线连接;

第三开关元件,其源极和漏极中的一者与所述驱动晶体管的栅极端子连接,源极和漏极中的另一者与信号线连接;

第四开关元件,其源极和漏极中的一者与所述第三开关元件的源极和漏极中的一者连接,源极和漏极中的另一者与初始化电源线连接;和

电容元件,其一个电极与所述驱动晶体管的源极和漏极中的一者连接,另一个电极与所述第三开关元件的源极和漏极中的一者连接,

所述第二开关元件、所述第三开关元件和所述第四开关元件各自的栅极端子被供给2个水平期间的导通信号,

所述显示装置具有:

将已被供给到所述复位电源线的复位电压供给到所述驱动晶体管的源极和漏极中的一者的第一复位期间;

将已被供给到所述初始化电源线的初始化电压供给到所述驱动晶体管的栅极端子的第二复位期间;

将已被供给到所述驱动晶体管的源极和漏极中的一者的所述复位电压断开,将已被供给到所述主电源线的主电压供给到所述驱动晶体管的源极和漏极中的另一者,使所述电容元件保持基于所述驱动晶体管的阈值电压的电荷的阈值补偿期间;和

将已被供给到所述驱动晶体管的源极和漏极中的另一者的所述主电压和已被供给到所述驱动晶体管的栅极端子的所述初始化电压断开,将已被供给到所述信号线的信号电压供给到所述驱动晶体管的栅极端子,使所述电容元件保持基于所述阈值电压和所述信号电压的电荷的写入期间。

3. 一种显示装置,其特征在于:

具有在行方向和列方向上排列的多个像素,

所述多个像素各自具有:

发光元件;

源极和漏极中的一者与所述发光元件连接的驱动晶体管;

第一开关元件,其源极和漏极中的一者与所述驱动晶体管的源极和漏极中的另一者连接;

第二开关元件,其源极和漏极中的一者与所述第一开关元件的源极和漏极中的另一者连接,源极和漏极中的另一者与主电源线连接;

第三开关元件,其源极和漏极中的一者与所述驱动晶体管的栅极端子连接,源极和漏极中的另一者与信号线连接;

第四开关元件,其源极和漏极中的一者与所述第三开关元件的源极和漏极中的一者连接,源极和漏极中的另一者与初始化电源线连接;

电容元件,其一个电极与所述驱动晶体管的源极和漏极中的一者连接,另一个电极与所述第三开关元件的源极和漏极中的一者连接,

所述第一开关元件的源极和漏极中的另一者和所述第二开关元件的源极和漏极中的一者经由第五开关元件与复位电源线连接,

所述第三开关元件、所述第四开关元件和所述第五开关元件各自的栅极端子被供给2个水平期间的导通信号。

4. 如权利要求3所述的显示装置,其特征在于:

还具有对各行设置的多个移位寄存器,

第n行的所述移位寄存器控制第n行的所述第三开关元件、第n+2行的所述第四开关元件和第n+3行的所述第五开关元件。

5. 如权利要求3所述的显示装置,其特征在于:

所述显示装置具有第一复位期间、第二复位期间、阈值补偿期间和写入期间,

在所述第一复位期间,所述第一开关元件为导通状态,所述第二开关元件为截止状态,所述第三开关元件为截止状态,所述第四开关元件为截止状态,所述第五开关元件为导通状态,

在所述第二复位期间,所述第一开关元件为导通状态,所述第二开关元件为截止状态,所述第三开关元件为截止状态,所述第四开关元件为导通状态,所述第五开关元件为导通状态,

在所述阈值补偿期间,所述第一开关元件为导通状态,所述第二开关元件为导通状态,所述第三开关元件为截止状态,所述第四开关元件为导通状态,所述第五开关元件为截止状态,

在所述写入期间,所述第一开关元件为截止状态,所述第二开关元件为截止状态,所述第三开关元件为导通状态,所述第四开关元件为截止状态,所述第五开关元件为截止状态。

6. 如权利要求3所述的显示装置,其特征在于,具有:

将已被供给到所述复位电源线的复位电压供给到所述驱动晶体管的源极和漏极中的另一者的第一复位期间;

将已被供给到所述初始化电源线的初始化电压供给到所述驱动晶体管的栅极端子的第二复位期间;

将已被供给到所述驱动晶体管的源极和漏极中的另一者的所述复位电压断开,将已被供给到所述主电源线的主电压供给到所述驱动晶体管的源极和漏极中的另一者,使所述电容元件保持基于所述驱动晶体管的阈值电压的电荷的阈值补偿期间;和

将已被供给到所述驱动晶体管的源极和漏极中的另一者的所述主电压和已被供给到所述驱动晶体管的栅极端子的所述初始化电压断开,将已被供给到所述信号线的信号电压供给到所述驱动晶体管的栅极端子,使所述电容元件保持基于所述阈值电压和所述信号电压的电荷的写入期间。

7. 一种显示装置,其特征在于:

具有在行方向和列方向上排列的多个像素,

所述多个像素各自具有:

发光元件;

具有与所述发光元件连接的第一端子、第二端子和第一栅极端子的驱动晶体管;

具有第二栅极端子、与所述第二端子连接的第三端子和与主电源线连接的第四端子的第一开关元件;

具有第三栅极端子、与所述第一端子连接的第五端子和与复位电源线连接的第六端子的第二开关元件;

具有第四栅极端子、与所述第一栅极端子连接的第七端子和与信号线连接的第八端子的第三开关元件;

具有第五栅极端子、与所述第七端子连接的第九端子和与初始化电源线连接的第十端子的第四开关元件;和

具有与所述第一端子连接的第一电容端子和与所述第七端子连接的第二电容端子的

电容元件，

所述第三栅极端子、所述第四栅极端子和所述第五栅极端子各自被供给2个水平期间的导通信号，

所述显示装置具有第一复位期间、第二复位期间、阈值补偿期间和写入期间，

在所述第一复位期间，所述第一开关元件为截止状态，所述第二开关元件为导通状态，所述第三开关元件为截止状态，所述第四开关元件为截止状态，

在所述第二复位期间，所述第一开关元件为截止状态，所述第二开关元件为导通状态，所述第三开关元件为截止状态，所述第四开关元件为导通状态，

在所述阈值补偿期间，所述第一开关元件为导通状态，所述第二开关元件为截止状态，所述第三开关元件为截止状态，所述第四开关元件为导通状态，

在所述写入期间，所述第一开关元件为截止状态，所述第二开关元件为截止状态，所述第三开关元件为导通状态，所述第四开关元件为截止状态。

8. 一种显示装置，其特征在于：

具有在行方向和列方向上排列的多个像素，

所述多个像素各自具有：

发光元件；

具有与所述发光元件连接的第一端子、第二端子和第一栅极端子的驱动晶体管；

具有第二栅极端子、与所述第二端子连接的第三端子和与主电源线连接的第四端子的第一开关元件；

具有第三栅极端子、与所述第一端子连接的第五端子和与复位电源线连接的第六端子的第二开关元件；

具有第四栅极端子、与所述第一栅极端子连接的第七端子和与信号线连接的第八端子的第三开关元件；

具有第五栅极端子、与所述第七端子连接的第九端子和与初始化电源线连接的第十端子的第四开关元件；和

具有与所述第一端子连接的第一电容端子和与所述第七端子连接的第二电容端子的电容元件，

所述第三栅极端子、所述第四栅极端子和所述第五栅极端子各自被供给2个水平期间的导通信号，

所述显示装置具有：

将已被供给到所述复位电源线的复位电压供给到所述第一端子的第一复位期间；

将已被供给到所述初始化电源线的初始化电压供给到所述第一栅极端子的第二复位期间；

将已被供给到所述第一端子的所述复位电压断开，将已被供给到所述主电源线的主电压供给到所述第二端子，使所述电容元件保持基于所述驱动晶体管的阈值电压的电荷的阈值补偿期间；和

将已被供给到所述第二端子的所述主电压和已被供给到所述第一栅极端子的所述初始化电压断开，将已被供给到所述信号线的信号电压供给到所述第一栅极端子，使所述电容元件保持基于所述阈值电压和所述信号电压的电荷的写入期间。

## 显示装置

### 技术领域

[0001] 本发明涉及显示装置。特别是，本发明涉及显示装置的电路结构。

### 背景技术

[0002] 近年来，在移动用途的发光显示装置中，高精细化、窄边框化的要求变强。作为移动用途的显示装置，采用有液晶显示装置 (Liquid Crystal Display Device;LCD)、在显示部使用有机EL元件 (Organic Light-Emitting Diode;OLED) 的显示装置、或者电子纸等的显示装置。

[0003] 使用上述的有机EL元件的显示装置中，不需要液晶显示装置所需要的背光光源、偏光板。并且，作为光源的发光元件的驱动电压低，因此，使用有机EL元件的显示装置作为低耗电且薄型的发光显示装置非常受到关注。另外，使用有机EL元件的显示装置仅由薄膜形成，因此，能够实现可弯折(柔性)的显示装置。该柔性的显示装置不使用玻璃基板。因此，能够实现轻且不容易损坏的显示装置，所以非常受到关注。

[0004] 有机EL元件的发光亮度因在元件中流动的电流而变化。在有机EL元件中流动的电流受到有源矩阵面板所使用的薄膜晶体管 (TFT) 元件的特性的影响。在有机EL显示装置中，电源线与有机EL元件之间串联连接有驱动晶体管。因此，有机EL元件中流动的电流受到驱动晶体管的阈值电压 (VTH) 偏差的影响。当有机EL元件中流动的电流在每个像素中不同时，成为显示不均而使显示品质降低的主要原因。

[0005] 于是，为了抑制驱动晶体管的特性偏差对显示品质产生的影响，开发了VTH补偿电路。VTH补偿电路是利用使有机EL元件中流动的电流恒定的恒流电路来抑制驱动晶体管的特性偏差的技术。

[0006] 例如，如日本特开2009-276744号公报所示，VTH补偿电路能够减小驱动晶体管的VTH偏差的影响。因此，通过输入的灰阶数据来正确地控制向有机EL元件供给的电流量。因此，驱动晶体管固有的VTH偏差被有效地补偿，所以有机EL显示装置的显示品质大幅提高。

[0007] 但是，VTH补偿电路需要控制多个晶体管。因此，需要对多个晶体管中的各晶体管设置控制电路。该控制电路配置在显示装置的周边区域。当对设置在VTH补偿电路的多个晶体管供给的信号复杂化时，驱动电路变大，因此周边区域的面积变大。其结果，产生边框变大的问题。

### 发明内容

[0008] 鉴于上述情况，本发明的目的在于提供可实现窄边框的显示装置。

[0009] 用于解决技术问题的技术方案

[0010] 本发明的一实施方式的显示装置，其是具有在行方向和列方向上排列的多个像素的显示装置，多个像素各自具有：发光元件；源极和漏极中的一者与发光元件连接的驱动晶体管；第一开关元件，其源极和漏极中的一者与驱动晶体管的源极和漏极中的另一者连接，源极和漏极中的另一者与主电源线连接；第二开关元件，其源极和漏极中的一者与驱动晶

体管的源极和漏极中的一者连接,源极和漏极中的另一者与复位电源线连接;第三开关元件,其源极和漏极中的一者与驱动晶体管的栅极端子连接,源极和漏极中的另一者与信号线连接;第四开关元件,其源极和漏极中的一者与第三开关元件的源极和漏极中的一者连接,源极和漏极中的另一者与初始化电源线连接;和电容元件,其一个电极与驱动晶体管的源极和漏极中的一者连接,另一个电极与第三开关元件的源极和漏极中的一者连接,第二开关元件、第三开关元件和第四开关元件各自的栅极端子被供给2个水平期间的导通信号。

[0011] 本发明的一实施方式的显示装置,其是具有在行方向和列方向上排列的多个像素的显示装置,上述多个像素各自具有:发光元件;源极和漏极中的一者与发光元件连接的驱动晶体管;第一开关元件,其源极和漏极中的一者与驱动晶体管的源极和漏极中的另一者连接;第二开关元件,其源极和漏极中的一者与第一开关元件的源极和漏极中的另一者连接,源极和漏极中的另一者与主电源线连接;第三开关元件,其源极和漏极中的一者与驱动晶体管的栅极端子连接,源极和漏极中的另一者与信号线连接;第四开关元件,其源极和漏极中的一者与第三开关元件的源极和漏极中的一者连接,源极和漏极中的另一者与初始化电源线连接;电容元件,其一个电极与驱动晶体管的源极和漏极中的一者连接,另一个电极与第三开关元件的源极和漏极中的一者连接,第一开关元件的源极和漏极中的另一者和第二开关元件的源极和漏极中的一者经由第五开关元件与复位电源线连接,第三开关元件、第四开关元件和第五开关元件各自的栅极端子被供给2个水平期间的导通信号。

[0012] 本发明的一实施方式的显示装置,其是具有在行方向和列方向上排列的多个像素的显示装置,上述多个像素各自具有:发光元件;具有与发光元件连接的第一端子、第二端子和第一栅极端子的驱动晶体管;具有与第二端子连接的第三端子、与主电源线连接的第四端子、第二栅极端子的第一开关元件;具有与第一端子连接的第五端子、与复位电源线连接的第六端子、第三栅极端子的第二开关元件;具有与第一栅极端子连接的第七端子、与信号线连接的第八端子、第四栅极端子的第三开关元件;具有与第七端子连接的第九端子、与初始化电源线连接的第十端子、第五栅极端子的第四开关元件;和具有与第一端子连接的第一电容端子和与第七端子连接的第二电容端子的电容元件,第三栅极端子、第四栅极端子和第五栅极端子各自被供给2个水平期间的导通信号。

## 附图说明

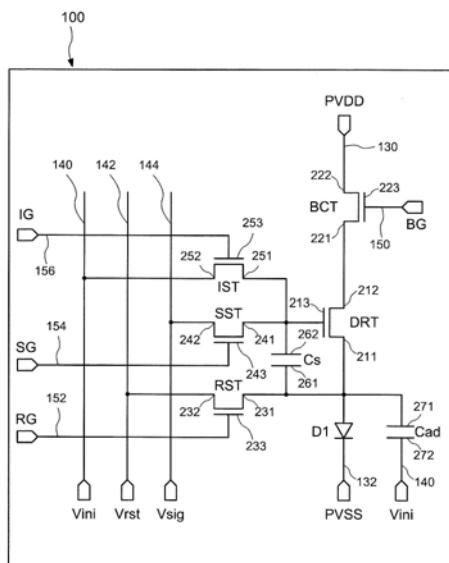

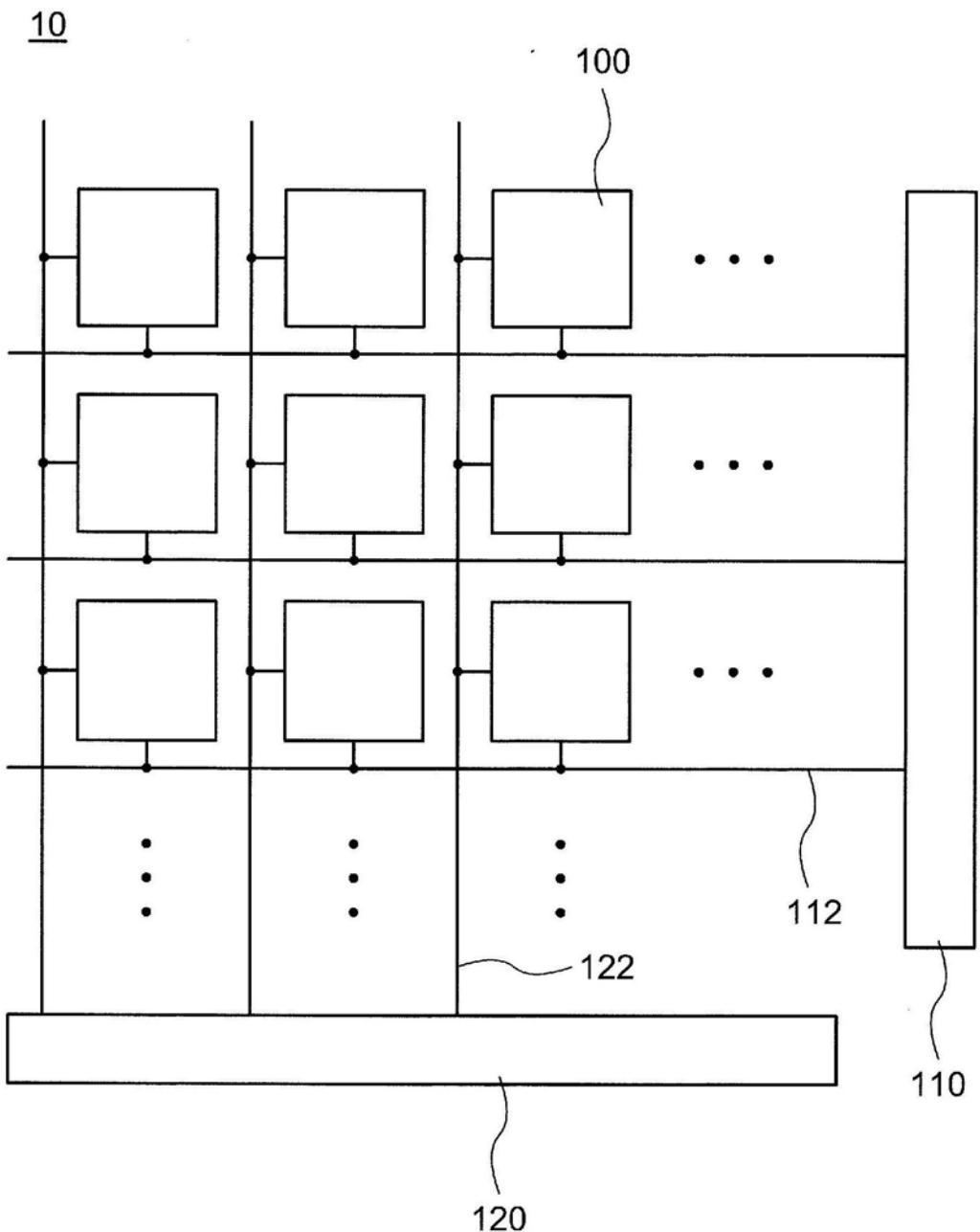

- [0013] 图1是表示本发明的一实施方式的显示装置的电路结构的一例的概略图。

- [0014] 图2是表示本发明的一实施方式的像素电路的电路结构的一例的电路图。

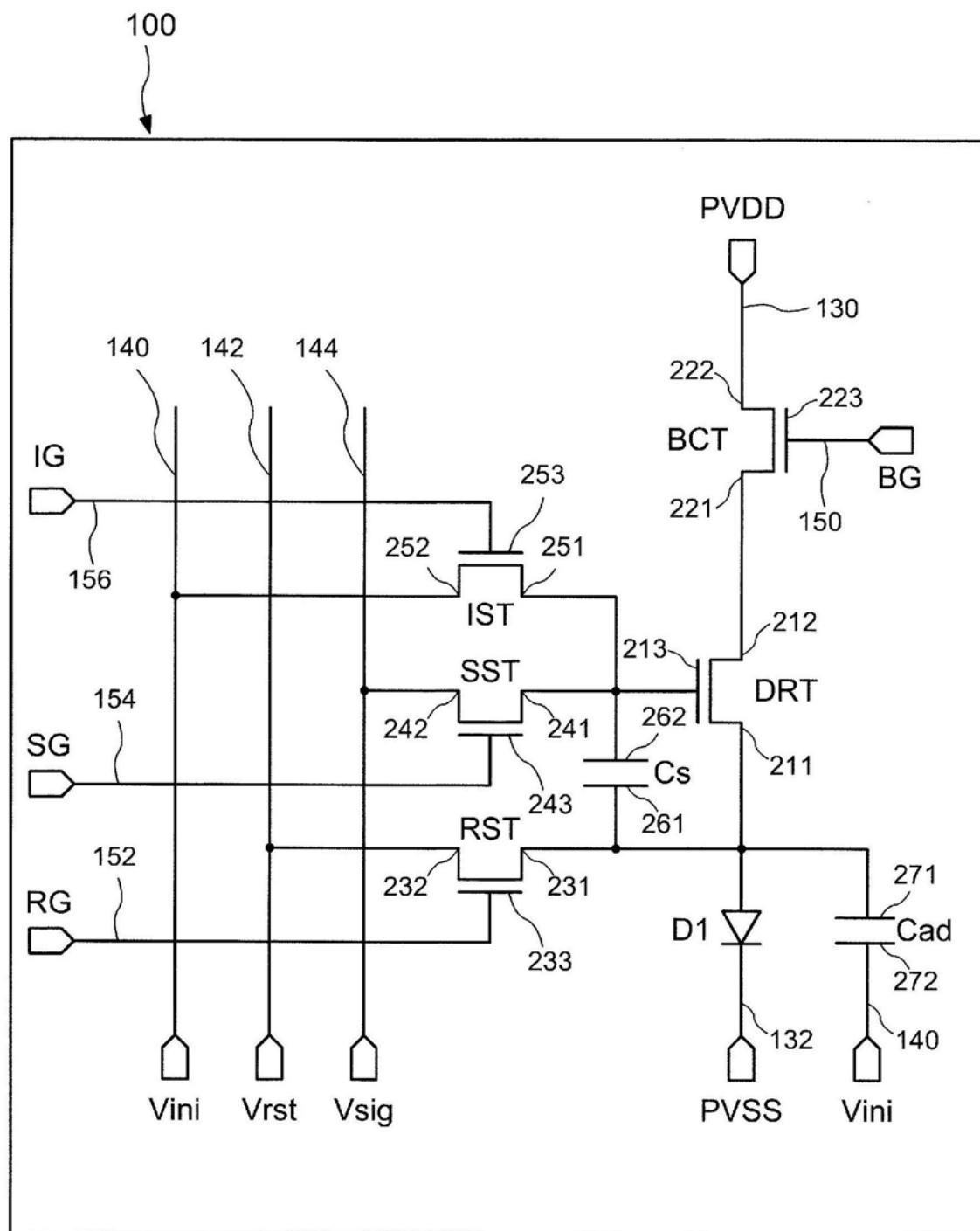

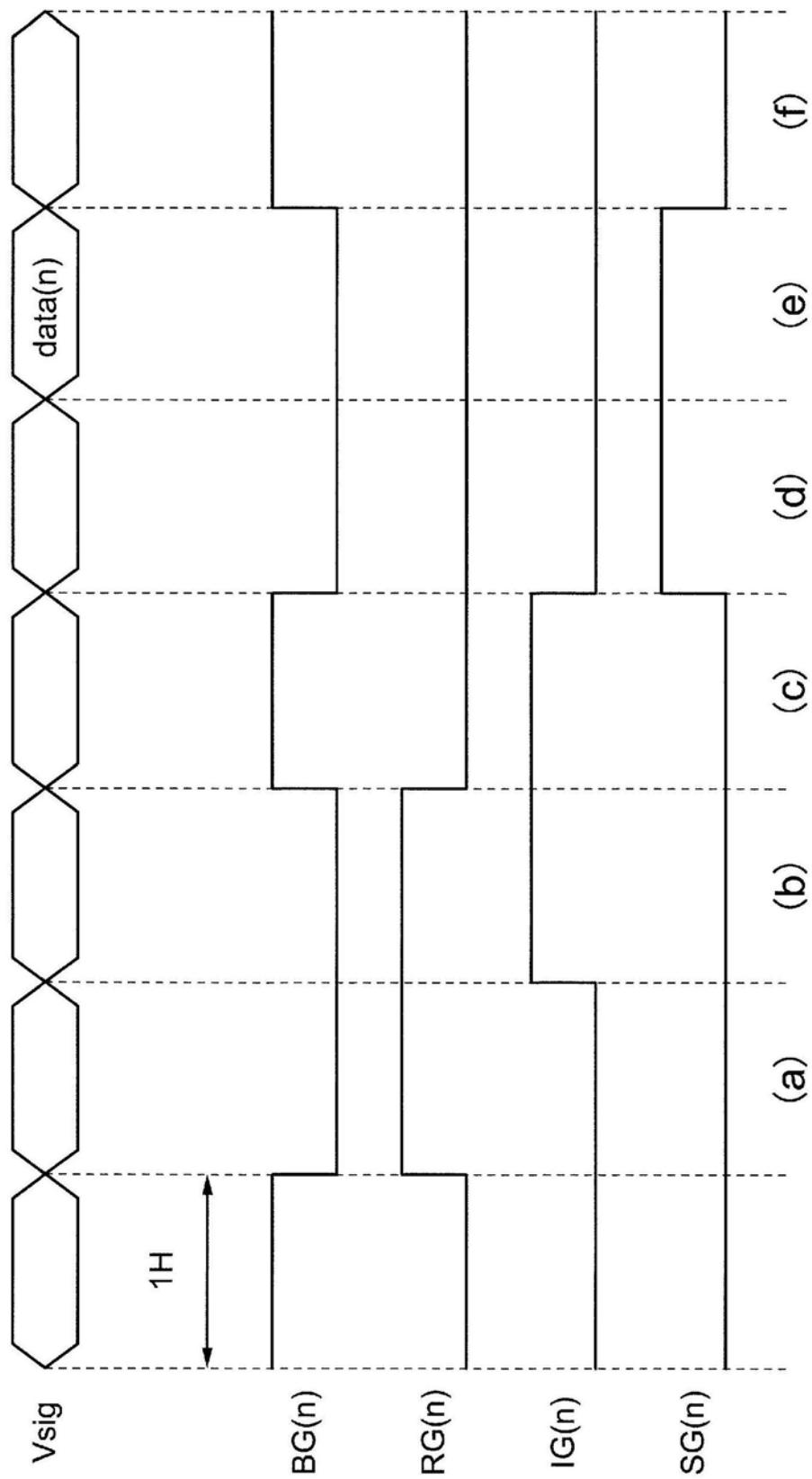

- [0015] 图3是表示本发明的一实施方式的像素电路的驱动方法的时序的图。

- [0016] 图4是表示本发明的一实施方式的周边电路的电路结构的一例的电路图。

- [0017] 图5是表示本发明的一实施方式的多行像素电路的驱动方法的时序图。

- [0018] 图6是表示本发明的一实施方式的像素电路的电路结构的一例的电路图。

- [0019] 图7是表示本发明的一实施方式的像素电路的驱动方法的时序图。

- [0020] 图8是表示本发明的一实施方式的周边电路的电路结构的一例的电路图。

- [0021] 图9是表示本发明的一实施方式的多行像素电路的驱动方法的时序图。

- [0022] 附图标记说明

- [0023] 10:显示装置;100:像素电路;110:行驱动器;112:控制信号线;120:列驱动器;

122:数据信号线;130:第一主电源线;132:第二主电源线;140:初始化电源线;142:复位电源线;144:图像数据信号线;150:输出控制信号线、152:复位控制信号线;154:像素控制信号线;156:初始化控制信号线;158:发光控制信号线;211、221、231、241、251、261、271、281:第一端子;212、222、232、242、252、262、272、282:第二端子;213、223、233、243、253、283:栅极端子;300、302、304、306:周边电路;310、312、314:移位寄存器;320、322、324、326:初始化控制信号线;330、332、334、336:复位控制信号线、340、342、344、346:OR电路;350、352、354、356、380、382、384、386:反相器、360、362、364、366:输出控制信号线;370、372、374、376:像素控制信号线;390、392、394、396:发光控制信号线;BCT:输出晶体管;CCT:发光控制晶体管;Cad:辅助电容;Cs:保持电容;D1:发光元件;DRT:驱动晶体管;IST:初始化晶体管;RST:复位晶体管;SST:像素晶体管。

## 具体实施方式

[0024] 以下,参照附图对本发明的各实施方式进行说明。此外,公开的不过是一个例子,对于本领域技术人员而言,在保持发明的主旨的情况下容易想到的适当的变更,当然也包含于本发明的范围内。另外,为了使附图更加明确,与实际的方式相比,有时示意性地表示各部分的宽度、厚度、形状等,这些仅是一个例子,不限定本发明的解释。另外,在本说明书和各附图中,对于与之前附图中叙述过的要素相同的要素标注相同的附图标记,适当省略详细的说明。

[0025] <实施方式1>

[0026] 使用图1~图5,对本发明的一实施方式的显示装置的概要进行说明。在实施方式1中,对设置有驱动晶体管的阈值补偿电路的有机EL显示装置进行说明。

[0027] [显示装置10的结构]

[0028] 图1是表示本发明的一实施方式的显示装置的电路结构的一例的概略图。如图1所示,在显示装置10中,像素电路100配置成n行m列的矩阵状。各像素电路100由行驱动器110、列驱动器120控制。在此,n=1、2、3、…,m=1、2、3、…。例如,n=3指配置在第三行的像素电路组。m=3指配置在第三列的像素电路组。在图1中例示了3行3列的像素电路组,但是不限于该方式,n和m的数量可以任意决定。

[0029] 行驱动器110选择进行数据的写入的行。如后述的方式,在像素电路100中配置有多个晶体管,行驱动器110控制该多个晶体管。换言之,行驱动器110与多个控制信号线112连接,该多个控制信号线112与配置在像素电路100中的多个晶体管各自的栅极电极(或者,栅极端子)连接。在实施方式1中,多个控制信号线112包括输出控制信号线、像素控制信号线、复位控制信号线、初始化控制信号线和复位电源线,详细内容后述。这些控制信号线112在各行中按规定顺序依次排他地被选择。

[0030] 列驱动器120基于被输入的图像数据决定灰阶,将与决定了的灰阶相应的数据电压供给到像素电路100。列驱动器120与多个数据信号线122连接。该多个数据信号线122与配置在像素电路100中的多个晶体管的一部分的源极和漏极电极中的一者连接。换言之,上述图像数据经由数据信号线122被供给到各列的像素电路100。在实施方式1中,多个数据信号线122包括像素数据信号线,详细内容后述。另外,主电源线和初始化电源线在与数据信号线122相同的方向上延伸。此外,这些电源线可以与数据信号线122同样地与列驱动器120

连接。这些数据信号线122对由上述的控制信号线112选择了的行的像素电路100供给图像数据或规定的电位。

[0031] 图2是表示本发明的一实施方式的像素电路的电路结构的一例的电路图。构成图2所示的像素电路100的晶体管都是n沟道型晶体管。如图2所示，像素电路100包括发光元件D1、驱动晶体管DRT、输出晶体管BCT、复位晶体管RST、像素晶体管SST、初始化晶体管IST、保持电容Cs和辅助电容Cad。在以下的说明中，将晶体管的源极和漏极中的一者称为第一端子，将源极和漏极中的另一者称为第二端子。另外，将电容元件的一个端子称为第一电容端子，将电容元件的另一个端子称为第二电容端子。

[0032] 驱动晶体管DRT的第一端子211与发光元件D1的阳极端子、保持电容Cs的第一电容端子261和辅助电容Cad的第一电容端子271连接。驱动晶体管DRT的第二端子212与输出晶体管BCT的第一端子221连接。输出晶体管BCT的第二端子222与第一主电源线130连接。复位晶体管RST的第一端子231与驱动晶体管DRT的第一端子211、保持电容Cs的第一电容端子261、发光元件D1的阳极端子和辅助电容Cad的第一电容端子271连接。复位晶体管RST的第二端子232与复位电源线142连接。

[0033] 像素晶体管SST的第一端子241与驱动晶体管DRT的栅极端子213、初始化晶体管IST的第一端子251和保持电容Cs的第二电容端子262连接。像素晶体管SST的第二端子242与图像数据信号线144连接。初始化晶体管IST的第二端子252与初始化电源线140连接。辅助电容Cad的第二电容端子272与初始化电源线140连接。另外，发光元件D1的阴极端子与第二主电源线132连接。在此，第一主电源线130与辅助电容Cad的第二电容端子272可以连接，第二主电源线132与辅助电容Cad的第二电容端子272也可以连接。

[0034] 在此，第一主电源线130被供给第一主电源电压PVDD。第二主电源线132被供给第二主电源电压PVSS。第一主电源电压PVDD被施加至阳极。第二主电源电压PVSS被施加至阴极。初始化电源线140被供给初始化电源电压Vini。复位电源线142被供给复位电源电压Vrst。图像数据信号线144被供给图像数据Vsig。

[0035] 此外，输出晶体管BCT的栅极端子223与输出控制信号线150连接。复位晶体管RST的栅极端子233与复位控制信号线152连接。像素晶体管SST的栅极端子243与像素控制信号线154连接。初始化晶体管IST的栅极端子253与初始化控制信号线156连接。输出控制信号线150被供给输出控制信号BG。复位控制信号线152被供给复位控制信号RG。像素控制信号线154被供给像素控制信号SG。初始化控制信号线156被供给初始化控制信号IG。

[0036] 换言之，在上述结构中，保持电容Cs的第一电容端子261与驱动晶体管DRT的第一端子211连接，保持电容Cs的第二电容端子262与像素晶体管SST的第一端子241连接。另外，在实施方式1中，例示了构成像素电路100的晶体管都是n沟道型晶体管的结构，但是不限于该结构。例如，构成像素电路100的驱动晶体管DRT以外的晶体管，可以都是p沟道型晶体管，也可以使用n沟道型晶体管和p沟道型晶体管两者。另外，上述的晶体管为能够切换导通状态和截止(断开)状态的开关元件即可，可以为晶体管以外的开关元件。

[0037] 输出控制信号线150、复位控制信号线152、像素控制信号线154、初始化控制信号线156和复位电源线142包含于图1的控制信号线112中。即，这些控制信号线和电源线在显示装置10的行方向上延伸。另一方面，第一主电源线130、初始化电源线140和图像数据信号线144包含于图1的数据信号线122中。即，这些控制信号线和电源线在显示装置10的列方向

上延伸。此外,第二主电源线132配置在基板整个面。

[0038] [显示装置10的驱动方法]

[0039] 图3是表示本发明的一实施方式的像素电路的驱动方法的时序图。此外,本实施方式中,构成像素电路的晶体管都是n沟道型。即,当晶体管的栅极端子被供给“低电平”的控制信号时,该晶体管成为截止状态(非导通状态)。另一方面,当晶体管的栅极端子被供给“高电平”的控制信号时,该晶体管成为导通状态。以下,使用图2的电路图和图3的时序图,对显示装置10的驱动方法进行说明。此外,在此说明对第n行的像素电路组写入图像数据的例子。

[0040] 如图3所示,显示装置10包括(a)第一复位期间、(b)第二复位期间、(c)阈值补偿期间、(d)第一写入期间、(e)第二写入期间和(f)发光期间。以下,参照图2和图3说明这些期间。此外,由图3的虚线划分的期间相当于1个水平期间(1H)。1个水平期间是指对某1行的全部像素电路写入图像数据信号的期间。

[0041] (a) 第一复位期间

[0042] 在第一复位期间,输出控制信号BG从高电平成为低电平,输出晶体管BCT成为截止状态。因此,驱动晶体管DRT的第二端子212被输出晶体管BCT从第一主电源线130断开。复位控制信号RG从低电平成为高电平,复位晶体管RST成为导通状态。因此,驱动晶体管DRT的第一端子211和保持电容Cs的第一电容端子261经由复位晶体管RST被供给复位电源电压Vrst。初始化控制信号IG和像素控制信号SG被维持低电平,初始化晶体管IST和像素晶体管SST被维持为截止状态。即,驱动晶体管DRT的栅极端子213和保持电容Cs的第二电容端子262成为浮动状态。

[0043] 在此,复位电源电压Vrst设定为比第二主电源电压PVSS低的电压。但是,复位电源电压Vrst并不需要一定比第二主电源电压PVSS低,在之后说明的第二复位期间中使电流不在发光元件D1中流动的电压即可。具体来说,复位电源电压Vrst为比第二主电源电压PVSS仅高出发光元件D1的阈值电压的量的电压以下即可。如果复位电源电压Vrst与第二主电源电压PVSS相同,则显示装置的驱动所需的电源电压的种类减少,因此使得窄边框化、能量消耗削减。另外,为了使驱动晶体管DRT不成为导通状态,复位电源电压Vrst可以设定为比驱动晶体管DRT的栅极端子213的浮动电压(即,有能够被供给到栅极端子213的电压)低的电压。例如,作为复位电源电压Vrst被供给-3V。通过上述的动作,停止向发光元件D1的电流供给,成为非发光状态。另外,在该期间中,进行辅助电容Cad的充放电,保持于辅助电容Cad的电荷量稳定。在实施方式1中,辅助电容Cad的第二电容端子272与初始化电源线140连接,因此,在第一复位期间,辅助电容Cad中保持基于初始化电源电压Vini与复位电源电压Vrst的电位差的电荷。另一方面,保持电容Cs的第二电容端子262是浮动的,因此,不进行保持电容Cs的充放电,与第一电容端子261的电位的变化相应地,第二电容端子262的电位发生变化。

[0044] (b) 第二复位期间

[0045] 在第二复位期间,初始化控制信号IG从低电平成为高电平,初始化晶体管IST成为导通状态。因此,驱动晶体管DRT的栅极端子213经由初始化晶体管IST被供给初始化电源电压Vini。复位控制信号RG被维持高电平,复位晶体管RST被维持导通状态。输出控制信号BG和像素控制信号SG被维持低电平,输出晶体管BCT和像素晶体管SST被维持截止状态。即,驱动晶体管DRT的第一端子211和保持电容Cs的第一电容端子261被供给复位电源电压Vrst,

驱动晶体管DRT的栅极端子213和保持电容Cs的第二电容端子262被供给初始化电源电压Vini。

[0046] 在此,作为初始化电源电压Vini,被供给比复位电源电压Vrst高的电压。例如,作为初始化电源电压Vini被供给+1V。因此,在驱动晶体管DRT中,栅极端子213的电位(Vini)相对于第一端子211的电位(Vrst)为高电平,因此,驱动晶体管DRT成为导通状态。这是因为,考虑驱动晶体管DRT的阈值电压的偏差,为了使驱动晶体管DRT导通,需要将充分高的电压施加到驱动晶体管DRT的栅极、源极间。另外,在该期间,保持电容Cs中保持基于复位电源电压Vrst与初始化电源电压Vini的电位差的电荷。

[0047] 如上所述,在第一复位期间对辅助电容Cad进行充放电,在第二复位期间对保持电容Cs进行充放电。即,在各自不同的复位期间对辅助电容Cad和保持电容Cs进行充放电。

[0048] (c) 阈值补偿期间

[0049] 在阈值补偿期间,输出控制信号BG从低电平成为高电平,输出晶体管BCT成为导通状态。因此,驱动晶体管DRT的第二端子212经由输出晶体管BCT被供给第一主电源电压PVDD。复位控制信号RG从高电平成为低电平,复位晶体管RST成为截止状态。因此,驱动晶体管DRT的第一端子211被复位晶体管RST从复位电源线142断开。初始化控制信号IG被维持高电平,初始化晶体管IST被维持导通状态。像素控制信号SG被维持低电平,像素晶体管SST被维持截止状态。

[0050] 在此,驱动晶体管DRT在上述的第二复位期间成为导通状态,因此,从第一主电源电压PVDD供给的电流从驱动晶体管DRT的第二端子212流向第一端子211。通过该电流,第一端子211的电位上升。而且,在第一端子211的电位与栅极端子213的电位之差达到驱动晶体管DRT的阈值电压(VTH)时,驱动晶体管DRT成为截止状态。

[0051] 在此,栅极端子213被供给Vini,因此,在第一端子211的电位达到(Vini-VTH)时,驱动晶体管DRT成为截止状态。此时,保持电容Cs的第二电容端子262被供给Vini,第一电容端子261被供给(Vini-VTH),因此,保持电容Cs中保持基于VTH的电荷。换言之,在阈值补偿期间中,保持电容Cs中保存基于驱动晶体管DRT的VTH的信息。此外,为了抑制阈值补偿期间中的发光元件D1的发光,优选以满足((Vini-VTH)-PVSS) < (发光元件的阈值电压)的条件的方式设定Vini。

[0052] (d) 第一写入期间

[0053] 在第一写入期间中,输出控制信号BG和初始化控制信号IG从高电平成为低电平,输出晶体管BCT和初始化晶体管IST成为截止状态。因此,驱动晶体管DRT的第二端子212被输出晶体管BCT从第一主电源线130断开,驱动晶体管DRT的栅极端子213被初始化晶体管IST从初始化电源线140断开。像素控制信号SG从低电平成为高电平,像素晶体管SST成为导通状态。复位控制信号RG被维持低电平,复位晶体管RST被维持截止状态。如上所述,在第一写入期间,像素电路为能够对驱动晶体管DRT的栅极端子213供给图像数据Vsigt的状态。在此,在实施方式1中,在第一写入期间,图像数据信号线144不被供给与本行的像素100对应的图像数据Vsigt,而被供给与前行的像素100对应的图像数据Vsigt。

[0054] (e) 第二写入期间

[0055] 在第二写入期间中,图像数据信号线144被供给灰阶数据data(n)作为图像数据Vsigt。此外,第二写入期间的输出控制信号BG、复位控制信号RG、初始化控制信号IG和像素

控制信号SG的电平(高电平或低电平)与第一写入期间相同。如上所述,驱动晶体管DRT的栅极端子213和保持电容Cs的第二电容端子262经由像素晶体管SST被供给灰阶数据data(n)。[0056] 在此,当保持电容Cs的第二电容端子262的电位从Vini变化为Vsigt时,第一电容端子261的电位基于(Vsig-Vini)而上升。具体来说,由于保持电容Cs和辅助电容Cad串联连接,因此位于这些电容的中间的第一电容端子261的电位(Vs)由以下的式(1)表示。

$$[0057] \quad Vs = (Vini - VTH) + (Vsigt - Vini) \frac{Cs}{Cs + Cad} \quad \dots (1)$$

[0058] 因此,第一端子211的电位与栅极端子213的电位的电位差(Vgs)由以下的式(2)表示。即,当对栅极端子213供给图像数据Vsigt时,保持电容Cs中保持基于驱动晶体管DRT的VTH和图像数据Vsigt的电荷。如上所述,驱动晶体管DRT成为基于对图像数据Vsigt加上驱动晶体管DRT的VTH而得的电位差的导通状态。

$$[0059] \quad Vgs = Vsigt - \left\{ (Vini - VTH) + (Vsigt - Vini) \frac{Cs}{Cs + Cad} \right\} \dots (2)$$

[0060] (f) 发光期间

[0061] 在发光期间,输出控制信号BG从低电平成为高电平,输出晶体管BCT成为导通状态。像素控制信号SG从高电平成为低电平,像素晶体管SST成为截止状态。复位控制信号RG和初始化控制信号IG被维持低电平,复位晶体管RST和初始化晶体管IST被维持截止状态。如上所述,驱动晶体管DRT将供给到第二端子212的第一主电源电压PVDD中的基于上述的式(2)的电流提供到发光元件D1。

[0062] 在此,驱动晶体管DRT中流动的电流(Id)由以下的式(3)表示。通过将式(2)代入到式(3),驱动晶体管DRT的VTH成分从式(3)被消去,Id如以下的式(4)所示,成为不依赖于VTH的电流。

$$[0063] \quad Id = \beta (Vgs - VTH)^2 \dots (3)$$

$$[0064] \quad Id = \beta \left\{ (Vsigt - Vini) \frac{Cad}{Cs + Cad} \right\}^2 \dots (4)$$

[0065] 如以上所示,在发光期间,排除了驱动晶体管DRT的VTH的影响的电流被供给到发光元件D1。即,补偿了驱动晶体管DRT的VTH后的电流被供给到发光元件D1。

[0066] 如图3所示,在显示装置10中,在第一复位期间和第二复位期间分别被供给1个水平期间的高电平的信号。由于第一复位期间和第二复位期间连续,因此复位控制信号RG被供给2个水平期间的高电平的信号。即,复位晶体管RST的栅极端子233被供给2个水平期间的导通信号。第一写入期间和第二写入期间分别被供给1个水平期间的高电平的信号。由于第一写入期间和第二写入期间连续,因此像素控制信号SG被供给2个水平期间的高电平的信号。即,像素晶体管SST的栅极端子243被供给2个水平期间的导通信号。

[0067] 在上述的第一写入期间,在本行(第n行)的驱动晶体管DRT中不进行图像数据的写入,前行(第n-1行)的驱动晶体管DRT被写入图像数据Vsigt,详细内容后述。在实施方式1中,例示了在第一写入期间,第n-1行的驱动晶体管DRT被写入图像数据的驱动方法,但是不限于该驱动方法。例如,第n-1行以外的驱动晶体管DRT也可以被写入图像数据。在实施方式1中,例示了在第一写入期间,图像数据信号线144被供给第n-1行的图像数据Vsigt,在第二写入期间作为第n行的图像数据Vsigt被供给灰阶数据data(n)的驱动方法,但是,不限于该驱动方法。

动方法。

[0068] [显示装置10的周边电路的电路结构]

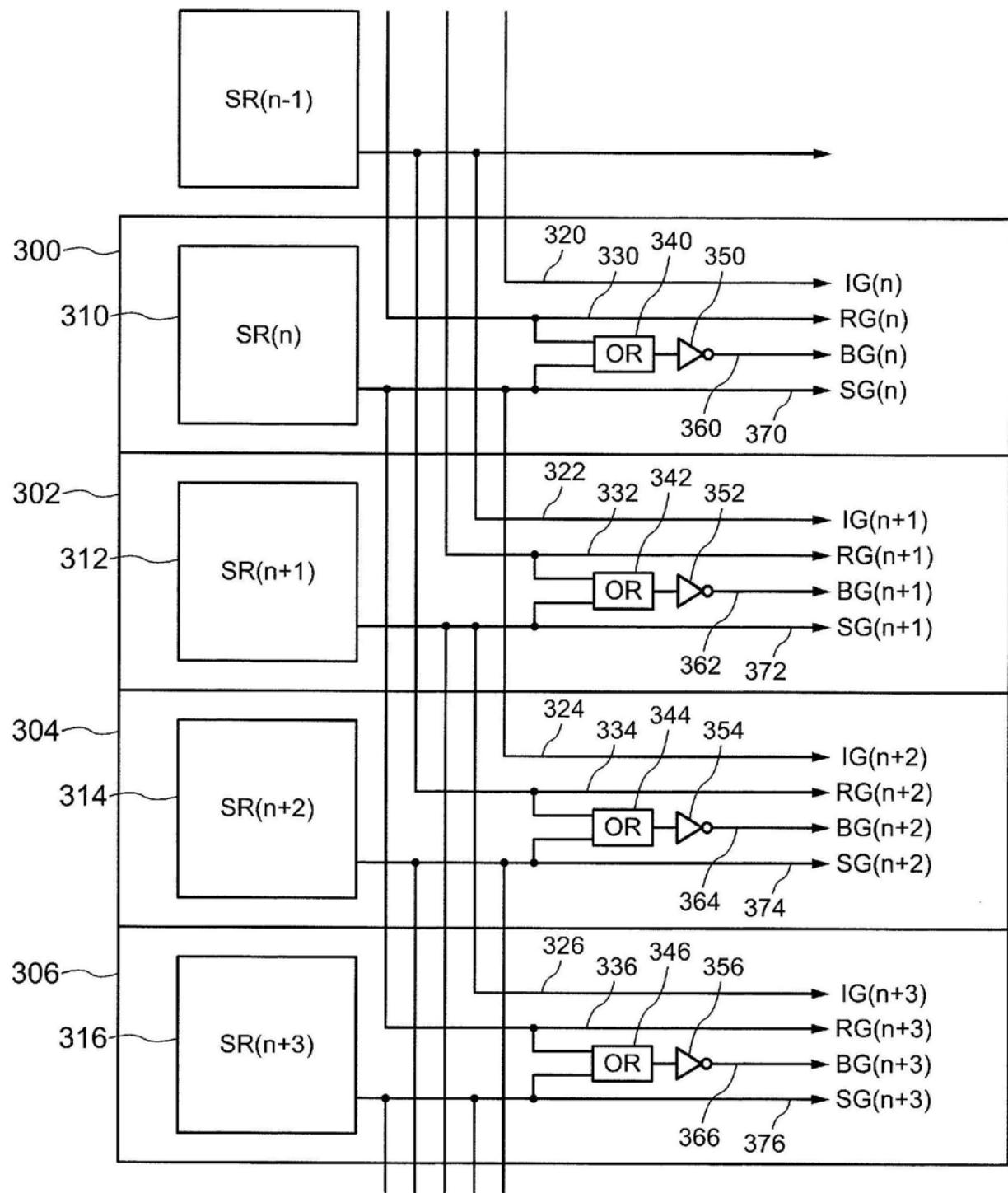

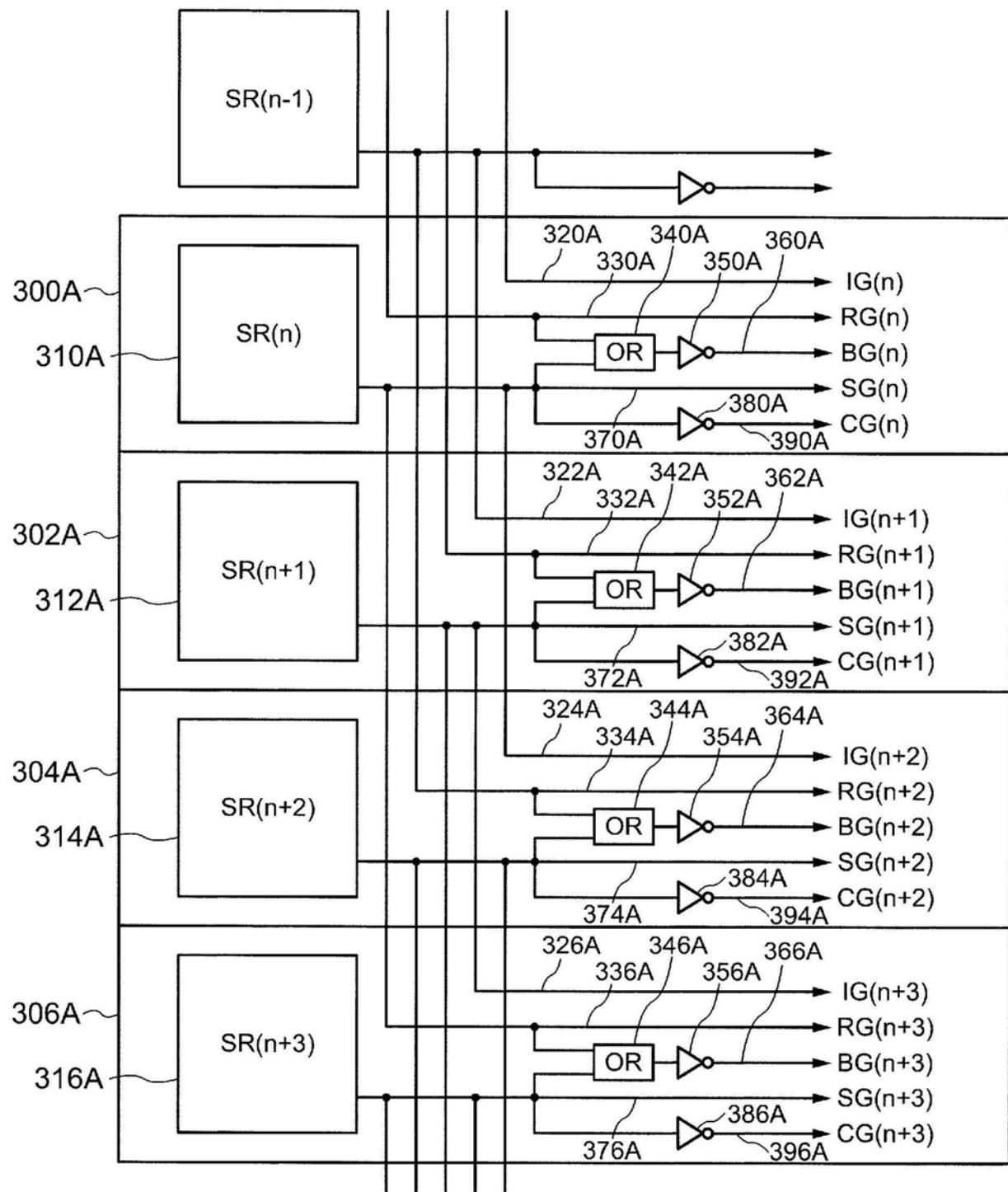

[0069] 图4是表示本发明的一实施方式的周边电路的电路结构的一例的电路图。图4表示从第n行至第n+3行的周边电路的一部分。如图4所示,第n~n+3行的周边电路300、302、304和306各自配置有移位寄存器310、312、314和316。第n行的周边电路300包括初始化控制信号线320、复位控制信号线330、OR电路340、反相器350、输出控制信号线360和像素控制信号线370。此外,输出控制信号线360经由OR电路340和反相器350与复位控制信号线330和像素控制信号线370连接。

[0070] 与第n行的周边电路300同样,第n+1行的周边电路302具有初始化控制信号线322、复位控制信号线332、OR电路342、反相器352、输出控制信号线362和像素控制信号线372。第n+2行的周边电路304具有初始化控制信号线324、复位控制信号线334、OR电路344、反相器354、输出控制信号线364和像素控制信号线374。第n+3行的周边电路306具有初始化控制信号线326、复位控制信号线336、OR电路346、反相器356、输出控制信号线366和像素控制信号线376。

[0071] 上述的第n行的周边电路300中的4个控制信号线中的、像素控制信号线370与移位寄存器310连接。另一方面,初始化控制信号线320和复位控制信号线330与第n行以外的移位寄存器连接。移位寄存器310与第n+2行的初始化控制信号线324和第n+3行的复位控制信号线336连接。即,像素控制信号线370的像素控制信号SG(n)、初始化控制信号线324的初始化控制信号IG(n+2)和复位控制信号线336的复位控制信号RG(n+3)被供给相同的时序信号SR(n)。

[0072] 并且,参照图2和图4进行说明时,第n行的移位寄存器310经由第n行的像素控制信号线370控制第n行的像素晶体管SST。第n行的移位寄存器310经由第n+2行的初始化控制信号线324控制第n+2行的初始化晶体管IST。第n行的移位寄存器310经由第n+3行的复位控制信号线336控制第n+3行的复位晶体管RST。

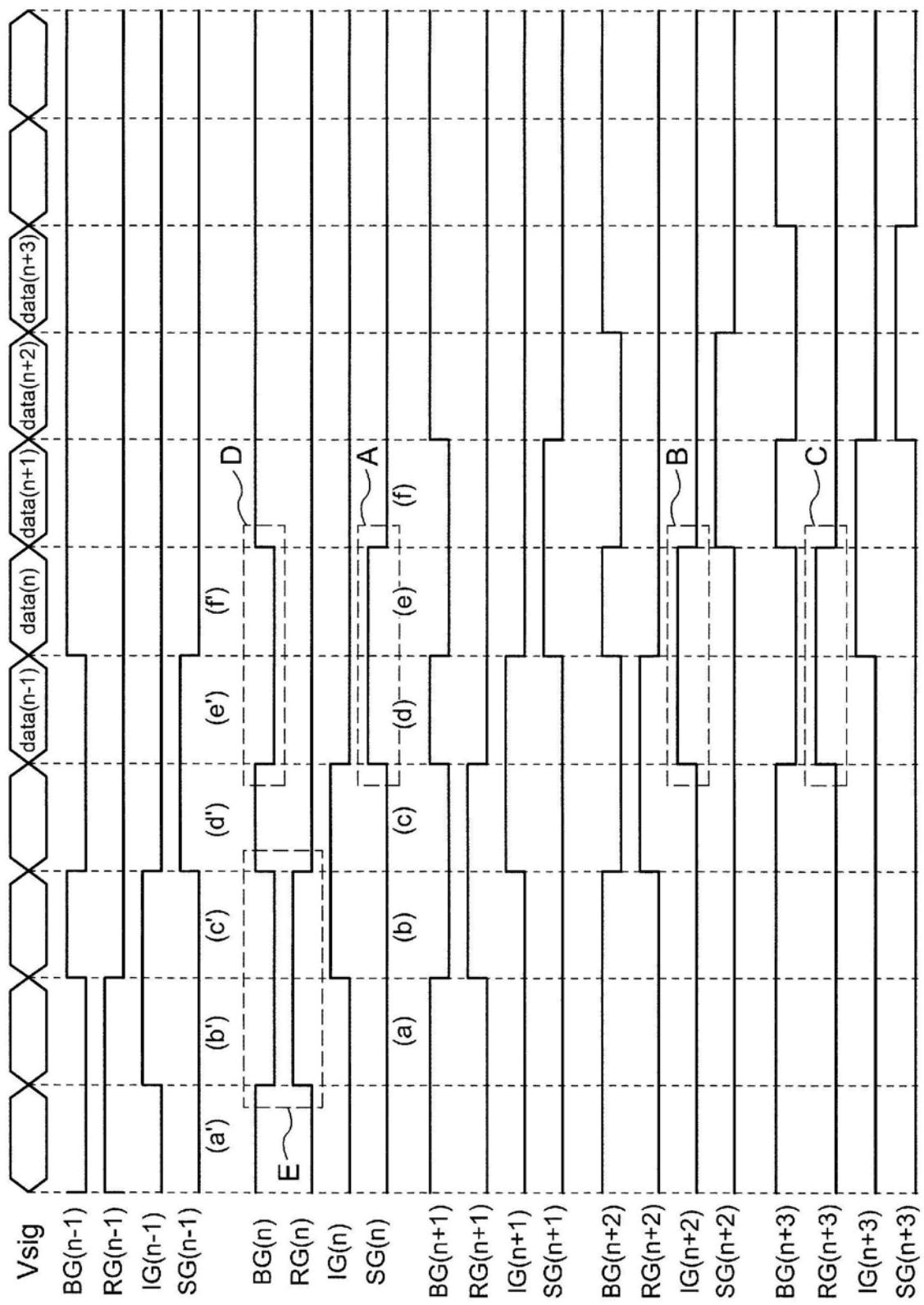

[0073] 在此,使用图5,对使用图4所示的多个移位寄存器的显示装置10的驱动方法进行说明。图5是表示本发明的一实施方式的多行像素电路的驱动方法的时序的图。图5表示向第n行至第n+3行的像素电路供给的时序信号。当参照图4时,从第n行的移位寄存器310供给的时序信号SR(n)作为SG(n)、IG(n+2)和RG(n+3)被供给。即,如图5所示,SG(n)、IG(n+2)和RG(n+3)被供给相同的时序信号(参照图5中的A、B和C)。

[0074] 当参照图4时,BG(n)经由OR电路340和反相器350被供给作为SG(n)和RG(n)供给了的时序信号。即,如图5所示,BG(n)被供给RG(n)和SG(n)反转了的时序信号(参照图5中的A、D和E)。

[0075] 如上所述,BG(n)、RG(n)、IG(n)和SG(n)均被供给2个水平期间的时序信号。因此,在周边电路配置供给2个水平期间的时序信号的移位寄存器即可。即,不需要对1行供给具有多种期间的时序信号,因此,通过对1行配置一种移位寄存器而使像素电路驱动。

[0076] 另外,如图5所示,例如,第n行(本行)的第一写入期间(d)与其前行的第n-1行的第二写入期间(e')重叠,作为Vsigt被供给第n-1行的灰阶数据data(n-1)。即,在第n行的第一写入期间(d)中,在第n-1行的像素电路中被写入灰阶数据data(n-1)。而且,在第n行的第二写入期间(e)中,第n行的像素电路被写入灰阶数据data(n)。如上所述,能够在第一写入期

间中对前行的像素电路进行写入,在第二写入期间对本行的像素电路进行写入。

[0077] 如以上的方式,根据实施方式1的显示装置10,作为像素电路进行驱动的时序信号,全都使用2个水平期间的时序信号。由此,在周边电路配置供给2个水平期间的时序信号的移位寄存器即可,因此,能够减小周边电路的专有面积。其结果,能够提供可实现窄边框的显示装置。

[0078] 另外,在各自不同的复位期间,对辅助电容Cad和保持电容Cs分别进行充放电,由此,对连接于辅助电容Cad与保持电容Cs之间的复位电源线142施加的负载被分散于各自的复位期间。由此,行方向上相邻的像素电路中的发光偏差降低。并且,显示装置10具有第一写入期间和第二写入期间,因此,能够确保用于写入的充足的时间。因此,能够更加正确地进行信号写入。另外,在第一写入期间,对像素电路施加前行的信号电压。在第二写入期间,当对像素电路施加本行的信号电压时,对像素电路施加的信号电压变动与前行的信号电压的差的量。因此,能够避免对像素电路施加的信号电压较大地变动。

[0079] <实施方式2>

[0080] 使用图6~图9,对本发明的一实施方式的显示装置的概要进行说明。在实施方式2中,对设置有驱动晶体管的阈值补偿电路的有机EL显示装置进行说明。

[0081] [显示装置10A的结构]

[0082] 显示装置10A整体的电路结构与图1所示的实施方式1的显示装置10相同,因此,在此省略说明,参照图1进行说明。

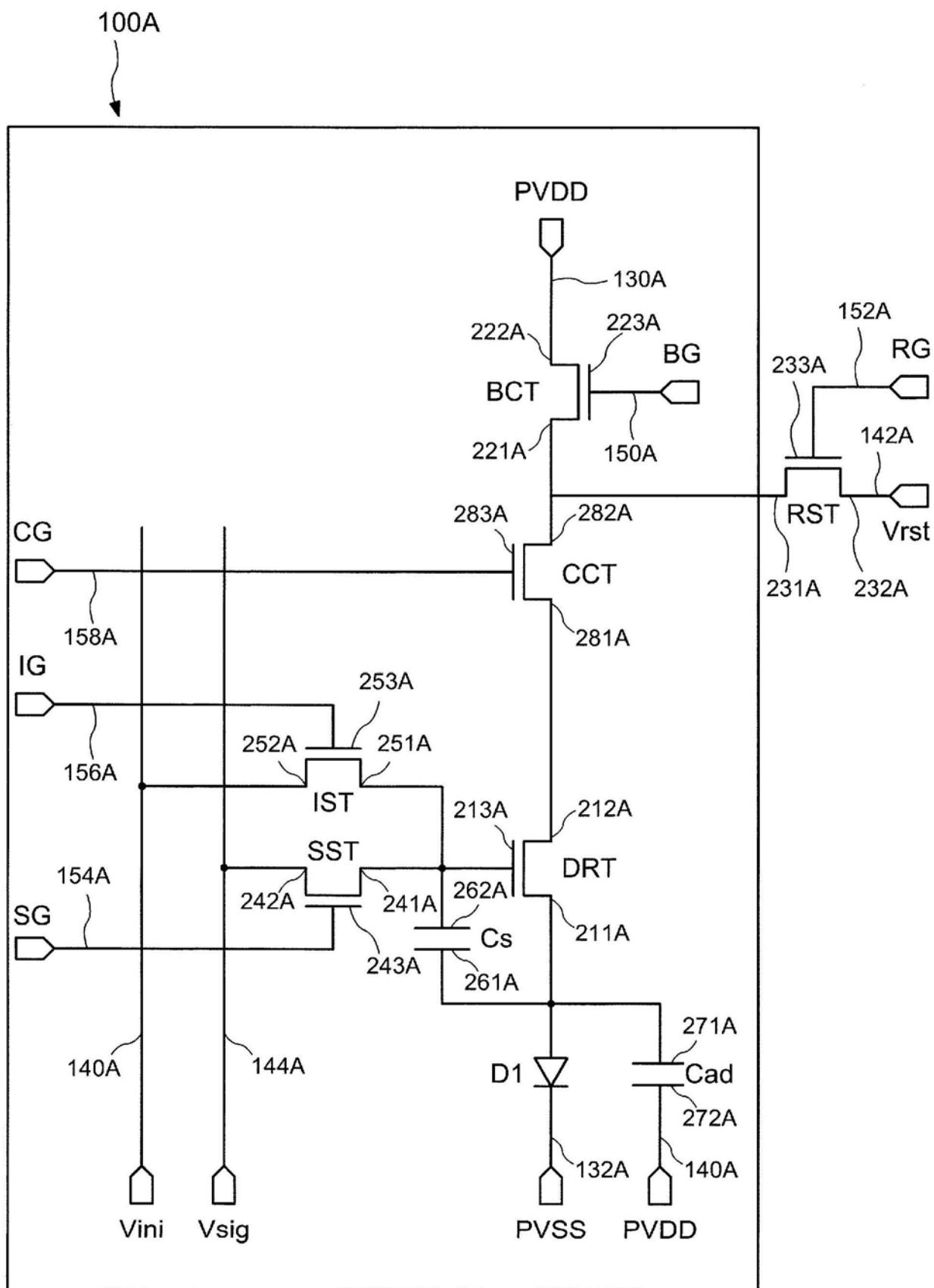

[0083] 图6是表示本发明的一实施方式的像素电路的电路结构的一例的电路图。构成图6所示的像素电路100A的晶体管全是n沟道型晶体管。如图6所示,像素电路100A包括发光元件D1、驱动晶体管DRT、发光控制晶体管CCT、输出晶体管BCT、像素晶体管SST、初始化晶体管IST、保持电容Cs和辅助电容Cad。在像素电路100A中,例如,周边电路等的配置在像素电路100A外的复位晶体管RST与像素电路100A连接。在以下的说明中,将晶体管的源极和漏极中的一者称为第一端子,将源极和漏极中的另一者称为第二端子。另外,将电容元件的一个端子称为第一电容端子,将电容元件的另一个端子称为第二电容端子。

[0084] 驱动晶体管DRT的第一端子211A与发光元件D1的阳极端子、保持电容Cs的第一电容端子261A和辅助电容Cad的第一电容端子271A连接。第二端子212A与发光控制晶体管CCT的第一端子281A连接。发光控制晶体管CCT的第二端子282A与输出晶体管BCT的第一端子221A和复位晶体管RST的第一端子231A连接。输出晶体管BCT的第二端子222A与第一主电源线130A连接。

[0085] 像素晶体管SST的第一端子241A与驱动晶体管DRT的栅极端子213A、初始化晶体管IST的第一端子251A和保持电容Cs的第二电容端子262A连接。像素晶体管SST的第二端子242A与图像数据信号线144A连接。初始化晶体管IST的第二端子252A与初始化电源线140A连接。辅助电容Cad的第二电容端子272A与初始化电源线140A连接。发光元件D1的阴极端子与第二主电源线132A连接。

[0086] 配置在像素电路100A外的复位晶体管RST的第一端子231A如上述的方式与发光控制晶体管CCT的第二端子282A和输出晶体管BCT的第一端子221A连接。第二端子232A与复位电源线142A连接。

[0087] 在此,第一主电源线130A被供给第一主电源电压PVDD。第二主电源线132A被供给

第二主电源电压PVSS。第一主电源电压PVDD被施加到阳极。第二主电源电压PVSS被施加到阴极。初始化电源线140A被供给初始化电源电压Vini。复位电源线142A被供给复位电源电压Vrst。图像数据信号线144A被供给图像数据Vsigt。

[0088] 此外,发光控制晶体管CCT的栅极端子283A与发光控制信号线158A连接。输出晶体管BCT的栅极端子223A与输出控制信号线150A连接。像素晶体管SST的栅极端子243A与像素控制信号线154A连接。初始化晶体管IST的栅极端子253A与初始化控制信号线156A连接。发光控制信号线158A被供给发光控制信号CG。输出控制信号线150A被供给输出控制信号BG。像素控制信号线154A被供给像素控制信号SG。初始化控制信号线156A被供给初始化控制信号IG。复位晶体管RST的栅极端子233A与复位控制信号线152A连接。复位控制信号线152A被供给复位控制信号RG。

[0089] 换言之,在上述的结构中,保持电容Cs的第一电容端子261A与驱动晶体管DRT的第一端子211A连接,保持电容Cs的第二电容端子262A与像素晶体管SST的第一端子241A连接。另外,在实施方式2中,例示了构成像素电路100A的晶体管都是n沟道型晶体管的结构,但是不限于该结构。例如,构成像素电路100A的驱动晶体管DRT以外的晶体管,可以都是p沟道型晶体管,也可以使用n沟道型晶体管和p沟道型晶体管两者。

[0090] [显示装置10A的驱动方法]

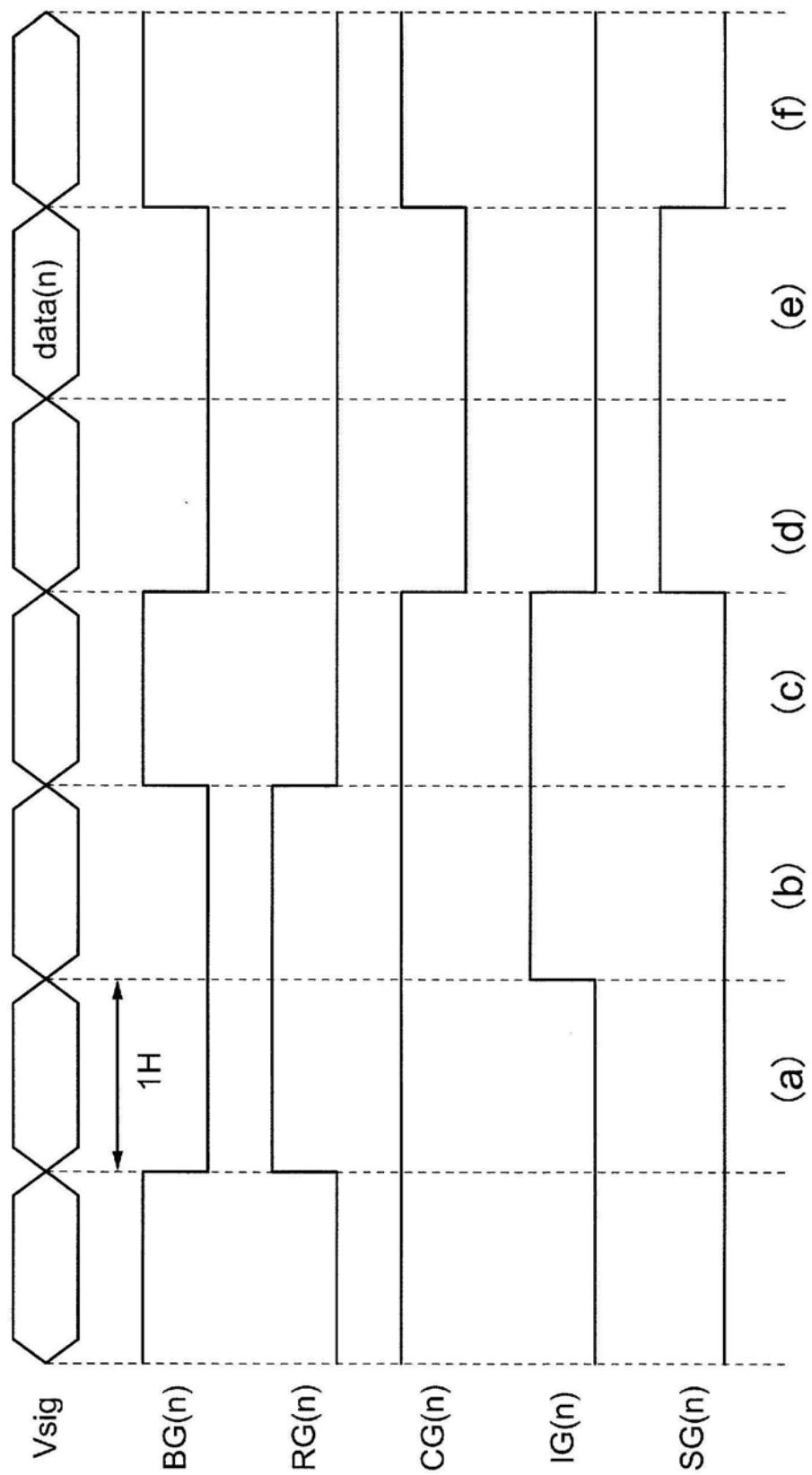

[0091] 图7是表示本发明的一实施方式的像素电路的驱动方法的时序图。此外,在本实施方式中,构成像素电路的晶体管都是n沟道型。即,晶体管的栅极端子被供给“低电平”的控制信号时,该晶体管成为截止状态(非导通状态)。另一方面,当晶体管的栅极端子被供给“高电平”的控制信号时,该晶体管成为导通状态。以下,使用图6的电路图和图7的时序图,对显示装置10A的驱动方法进行说明。此外,在此说明对第n行的像素电路组写入图像数据的例子。

[0092] 如图7所示,显示装置10A具有(a)第一复位期间、(b)第二复位期间、(c)阈值补偿期间、(d)第一写入期间、(e)第二写入期间和(f)发光期间。以下,参照图6和图7说明上述期间。此外,由图7的虚线划分的期间相当于1个水平期间(1H)。1个水平期间指对某1行的全部像素电路写入图像数据信号的期间。此外,上述的各期间的动作的概要与实施方式1相似,因此省略详细的说明。

[0093] (a) 第一复位期间

[0094] 在第一复位期间,输出控制信号BG从高电平成为低电平,复位控制信号RG从低电平成为高电平。发光控制信号CG被维持高电平,初始化控制信号IG和像素控制信号SG被维持低电平。即,发光控制晶体管CCT和复位晶体管RST成为导通状态,输出晶体管BCT、像素晶体管SST和初始化晶体管IST成为截止状态。由此,驱动晶体管DRT的第二端子212A被供给复位电源电压Vrst。此外,复位电源电压Vrst为在第一复位期间中为了驱动晶体管DRT导通而足够高的电压即可。换言之,复位电源电压Vrst为对第二主电源电压PVSS加上相对于驱动晶体管DRT的阈值电压VTH带有余量的电压的程度的电压即可。

[0095] (b) 第二复位期间

[0096] 在第二复位期间中,初始化控制信号IG从低电平成为高电平。输出控制信号BG和像素控制信号SG被维持低电平,复位控制信号RG和发光控制信号CG被维持高电平。即,复位晶体管RST、发光控制晶体管CCT和初始化晶体管IST成为导通状态,输出晶体管BCT和像素

晶体管SST成为截止状态。由此,驱动晶体管DRT的第二端子212A被供给复位电源电压Vrst,驱动晶体管DRT的栅极端子213A和保持电容Cs的第二电容端子262A被供给初始化电源电压Vini。

[0097] 在此,复位电源电压Vrst和初始化电源电压Vini被供给驱动晶体管DRT成为导通状态的电压。因此,经由驱动晶体管DRT对第一端子211A和保持电容Cs的第一电容端子261A供给复位电源电压Vrst。

[0098] (c) 阈值补偿期间

[0099] 在阈值补偿期间,输出控制信号BG从低电平成为高电平,复位控制信号RG从高电平成为低电平。发光控制信号CG和初始化控制信号IG被维持高电平,像素控制信号SG被维持低电平。即,输出晶体管BCT、发光控制晶体管CCT和初始化晶体管IST成为导通状态,复位晶体管RST和像素晶体管SST成为截止状态。

[0100] 在此,由于驱动晶体管DRT在上述的第二复位期间成为导通状态,因此,从第一主电源电压PVDD供给的电流从驱动晶体管DRT的第二端子212A流向第一端子211。因该电流而使第一端子211A的电位上升。于是,当第一端子211A的电位与栅极端子213A的电位的差达到驱动晶体管DRT的阈值电压(VTH)时,驱动晶体管DRT成为截止状态。

[0101] 在此,由于栅极端子213A被供给Vini,因此,当达到第一端子211A的电位(Vini-VTH)时,驱动晶体管DRT成为截止状态。此时,保持电容Cs的第二电容端子262A被供给Vini,第一电容端子261A被供给(Vini-VTH),因此保持电容Cs中保持基于VTH的电荷。换言之,在阈值补偿期间,保持电容Cs中保存基于驱动晶体管DRT的VTH的信息。

[0102] (d) 第一写入期间

[0103] 在第一写入期间,输出控制信号BG、发光控制信号CG和初始化控制信号IG从高电平成为低电平,像素控制信号SG从低电平成为高电平。复位控制信号RG被维持低电平。即,像素晶体管SST成为导通状态,输出晶体管BCT、复位晶体管RST、发光控制晶体管CCT和初始化晶体管IST成为截止状态。如上所述,在第一写入期间,像素电路成为能够对驱动晶体管DRT的栅极端子213A供给图像数据Vsigt的状态。在此,在实施方式2中,在第一写入期间,图像数据信号线144A不被供给与本行的像素100A对应的图像数据Vsigt,而被供给与前行的像素100A对应的图像数据Vsigt。

[0104] (e) 第二写入期间

[0105] 在第二写入期间,灰阶数据data(n)作为图像数据Vsigt被供给到图像数据信号线144A。此外,第二写入期间的输出控制信号BG、复位控制信号RG、发光控制信号CG、初始化控制信号IG和像素控制信号SG的电平(高电平或低电平)与第一写入期间相同。如上所述,驱动晶体管DRT的栅极端子213A和保持电容Cs的第二电容端子262A经由像素晶体管SST被供给灰阶数据data(n)。此时,驱动晶体管DRT的第一端子211A的电位与栅极端子213A的电位的电位差(Vgs)由上述的式(2)表示。

[0106] (f) 发光期间

[0107] 在发光期间,输出控制信号BG和发光控制信号CG从低电平成为高电平,像素控制信号SG从高电平成为低电平。复位晶体管RST和初始化晶体管IST被维持截止状态。即,输出晶体管BCT和发光控制晶体管CCT成为导通状态,复位晶体管RST、初始化晶体管IST和像素晶体管SST成为截止状态。如上所述,驱动晶体管DRT将供给到第二端子212A的第一主电源

电压PVDD中的、基于上述的式(2)的电流供给到发光元件D1。

[0108] 在此,在驱动晶体管DRT中流动的电流(Id)由上述的式(4)表示。即,Id为不依赖于VTH的电流。

[0109] 如以上的方式,在发光期间中,排除了驱动晶体管DRT的VTH的影响后的电流被供给到发光元件D1。即,补偿了驱动晶体管DRT的VTH后的电流被供给到发光元件D1。

[0110] 如图7所示,在显示装置10A中,在第一复位期间和第二复位期间各自被供给1个水平期间的高电平的信号。第一复位期间和第二复位期间连续,因此复位控制信号RG被供给2个水平期间的高电平的信号。即,复位晶体管RST的栅极端子233A被供给2个水平期间的导通信号。第一写入期间和第二写入期间各自被供给1个水平期间的高电平的信号。第一写入期间和第二写入期间连续,因此像素控制信号SG被供给2个水平期间的高电平的信号。即,像素晶体管SST的栅极端子243A被供给2个水平期间的导通信号。

[0111] 在上述的第一写入期间,在本行(第n行)的驱动晶体管DRT中不进行图像数据的写入,对前行(第n-1行)的驱动晶体管DRT写入图像数据Vsigt,详细内容后述。其中,在第一写入期间,可以对第n-1行以外的驱动晶体管DRT写入图像数据。

[0112] [显示装置10A的周边电路的电路结构]

[0113] 图8是表示本发明的一实施方式的周边电路的电路结构的一例的电路图。图8表示从第n行至第n+3行的周边电路的一部分。如图8所示,在第n~n+3行的周边电路300A、302A、304A和306A各自配置移位寄存器310A、312A、314A和316A。第n行的周边电路300A具有初始化控制信号线320A、复位控制信号线330A、OR电路340A、反相器350A、输出控制信号线360A、像素控制信号线370A、反相器380A和发光控制信号线390A。此外,输出控制信号线360A经由OR电路340A和反相器350A与复位控制信号线330A和像素控制信号线370A连接。另外,发光控制信号线390A经由反相器380A与像素控制信号线370A连接。

[0114] 与第n行的周边电路300A同样,第n+1行的周边电路302A具有初始化控制信号线322A、复位控制信号线332A、OR电路342A、反相器352A、输出控制信号线362A、像素控制信号线372A、反相器382A和发光控制信号线392A。第n+2行的周边电路304A具有初始化控制信号线324A、复位控制信号线334A、OR电路344A、反相器354A、输出控制信号线364A、像素控制信号线374A、反相器384A和发光控制信号线394A。第n+3行的周边电路306A具有初始化控制信号线326A、复位控制信号线336A、OR电路346A、反相器356A、输出控制信号线366A、像素控制信号线376A、反相器386A和发光控制信号线396A。

[0115] 上述的第n行的周边电路300A的5个控制信号线中的、像素控制信号线370A和发光控制信号线390A与移位寄存器310A连接。另一方面,初始化控制信号线320A和复位控制信号线330A与第n行以外的移位寄存器连接。移位寄存器310A与第n+2行的初始化控制信号线324A和第n+3行的复位控制信号线336A连接。即,像素控制信号线370A的像素控制信号SG(n)、初始化控制信号线324A的初始化控制信号IG(n+2)和复位控制信号线336A的复位控制信号RG(n+3)被供给相同的时序信号SR(n)。

[0116] 并且,参照图6和图8进行说明时,第n行的移位寄存器310A经由第n行的像素控制信号线370A控制第n行的像素晶体管SST。第n行的移位寄存器310A经由第n+2行的初始化控制信号线324A控制第n+2行的初始化晶体管IST。第n行的移位寄存器310A经由第n+3行的复位控制信号线336A控制第n+3行的复位晶体管RST。

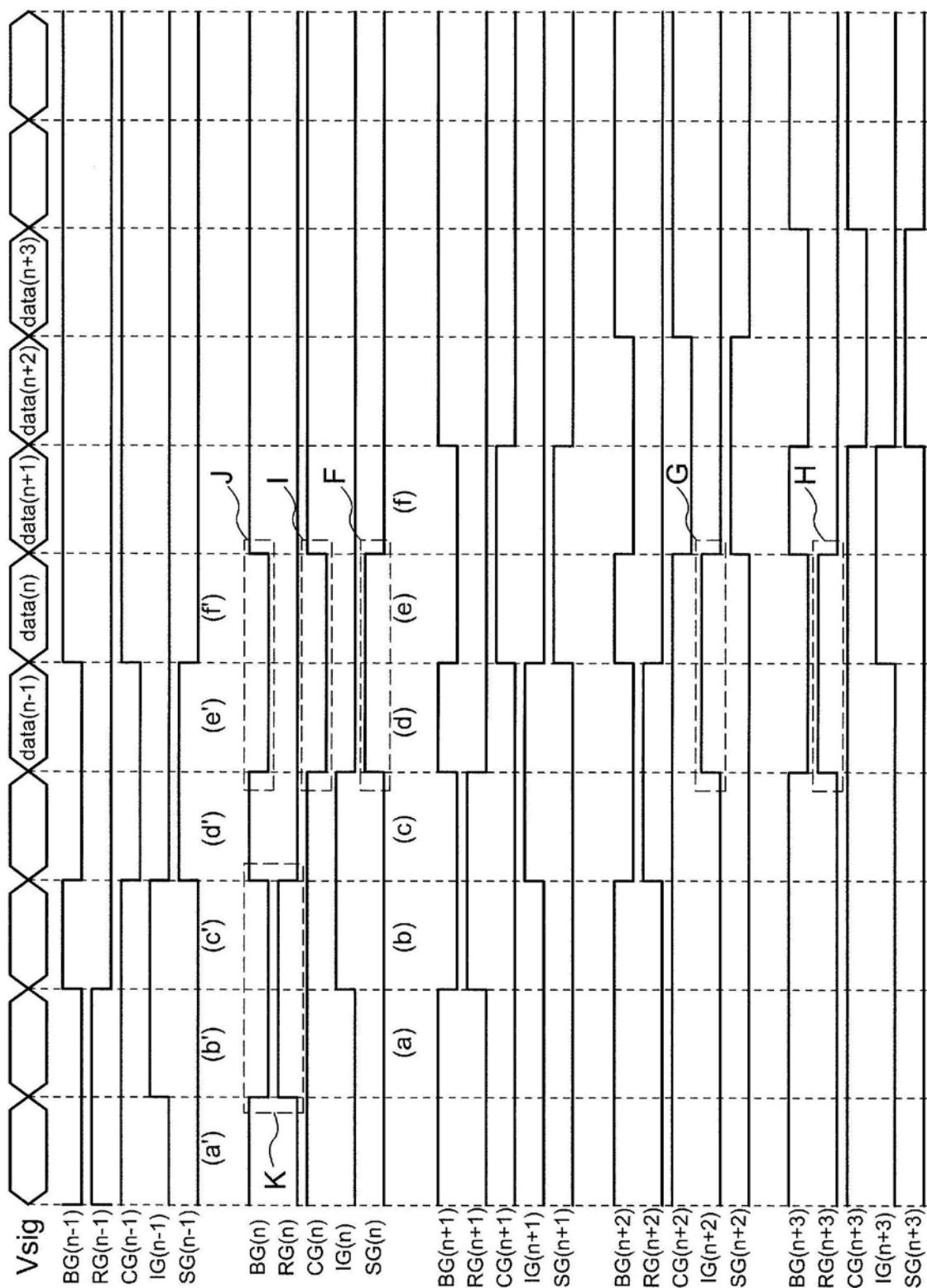

[0117] 在此,使用图9,对使用图8所示的多个移位寄存器的显示装置10A的驱动方法进行说明。图9是表示本发明的一实施方式的多行像素电路的驱动方法的时序的图。图9表示向从第n行至第n+3行的像素电路供给的时序信号。参照图8,从第n行的移位寄存器310A供给的时序信号SR (n) 作为SG (n) 、IG (n+2) 和RG (n+3) 被供给。即,如图9所示,SG (n) 、IG (n+2) 和RG (n+3) 被供给相同的时序信号(参照图9中的F、G和H)。

[0118] 参照图8,CG (n) 经由反相器380A被供给作为SG (n) 供给的时序信号。即,如图9所示,对CG (n) 供给SG (n) 反转了的时序信号(参照图9中的F和I)。BG (n) 经由OR电路340A和反相器350A被供给作为SG (n) 和RG (n) 供给的时序信号。即,如图9所示,BG (n) 被供给RG (n) 和SG (n) 反转了的时序信号(参照图5中的F、J和K)。

[0119] 如上述的方式,BG (n) 、RG (n) 、CG (n) 、IG (n) 和SG (n) 都被供给2个水平期间的时序信号。因此,在周边电路配置供给2个水平期间的时序信号的移位寄存器即可。即,不需要对一行供给具有多种期间的时序信号,因此,通过对一行配置一种移位寄存器而使像素电路驱动。

[0120] 另外,如图9所示,例如,第n行(本行)的第一写入期间(d)与该前行的第n-1行的第二写入期间(e')重叠,作为Vsig被供给第n-1行的灰阶数据data (n-1)。即,在第n行的第一写入期间(d),第n-1行的像素电路被写入灰阶数据data (n-1)。而且,在第n行的第二写入期间(e),第n行的像素电路被写入灰阶数据data (n)。如上所述,能够在第一写入期间对前行的像素电路进行写入,在第二写入期间对本行的像素电路进行写入。

[0121] 如以上的方式,根据实施方式2的显示装置10A,作为像素电路进行驱动的时序信号,都能够使用2个水平期间的时序信号。由此,在周边电路配置供给2个水平期间的时序信号的移位寄存器即可,因此,能够减小周边电路的专有面积。其结果,能够提供可实现窄边框的显示装置。

[0122] 另外,在相互不同的复位期间,对辅助电容Cad和保持电容Cs分别进行充放电,由此,对连接于辅助电容Cad与保持电容Cs之间的复位电源线142A施加的负载分散于各自的复位期间。由此,在行方向上相邻的像素电路中的发光偏差降低。并且,显示装置10A具有第一写入期间和第二写入期间,因此,能够确保用于写入的充分的时间。因此,能够进一步进行正确的信号写入。另外,在第一写入期间,对像素电路施加前行的信号电压。在第二写入期间,当对像素电路施加本行的信号电压时,向像素电路施加的信号电压仅变动与前行的信号电压的差的量。因此,能够避免向像素电路施加的信号电压较大地变动。

[0123] 此外,本发明不限于上述的实施方式,在不脱离主旨的范围内能够适当变更。

图1

图2

图3

图4

图5

图6

图7

图8

图9