(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6109159号

(P6109159)

(45) 発行日 平成29年4月5日(2017.4.5)

(24) 登録日 平成29年3月17日(2017.3.17)

(51) Int.Cl.

F 1

|              |           |      |        |      |

|--------------|-----------|------|--------|------|

| H01L 21/301  | (2006.01) | H01L | 21/78  | S    |

| H01L 21/3065 | (2006.01) | H01L | 21/302 | 105A |

| H01L 21/302  | (2006.01) | H01L | 21/302 | 201B |

| B23K 26/364  | (2014.01) | H01L | 21/302 | 104H |

| B23K 26/00   | (2014.01) | H01L | 21/78  | B    |

請求項の数 15 (全 19 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-515856 (P2014-515856)  |

| (86) (22) 出願日 | 平成24年5月31日 (2012.5.31)        |

| (65) 公表番号     | 特表2014-523117 (P2014-523117A) |

| (43) 公表日      | 平成26年9月8日 (2014.9.8)          |

| (86) 國際出願番号   | PCT/US2012/040307             |

| (87) 國際公開番号   | W02012/173793                 |

| (87) 國際公開日    | 平成24年12月20日 (2012.12.20)      |

| 審査請求日         | 平成27年5月8日 (2015.5.8)          |

| (31) 優先権主張番号  | 13/161,026                    |

| (32) 優先日      | 平成23年6月15日 (2011.6.15)        |

| (33) 優先権主張国   | 米国(US)                        |

|                                                |                                            |

|------------------------------------------------|--------------------------------------------|

| (73) 特許権者                                      | 390040660                                  |

| アプライド マテリアルズ インコーポレイテッド                        | APPPLIED MATERIALS, INCORPORATED           |

| アメリカ合衆国 カリフォルニア州 95054 サンタクララ バウアーズ アベニュー 3050 | アメリカ合衆国 カリフォルニア州 95130 サンノゼ デュバル ドライブ 1786 |

| (74) 代理人                                       | 100101502                                  |

| 弁理士 安齋 嘉章                                      | レイ ウェイ シエン                                 |

| (72) 発明者                                       | アメリカ合衆国 カリフォルニア州 95130 サンノゼ デュバル ドライブ 1786 |

最終頁に続く

(54) 【発明の名称】マルチパルスバーストのパルス列レーザ及びプラズマエッティングを用いたウェハダイシング

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の集積回路を含む半導体ウェハのダイシング方法であって、前記半導体ウェハの上方にマスクを形成するステップであって、前記マスクが前記集積回路を被覆し、保護する層を含むステップと、前記マスクを、マルチパルスバーストを用いるパルス列レーザスクライビング工程でパターニングし、ギャップを有するパターニングされたマスクを形成して、前記半導体ウェハの前記集積回路間の領域を露出させるステップであって、前記マルチパルスバーストを用いるパルス列レーザスクライビング工程は、前記ギャップのカーフ幅及び深さを正確に制御するために使用されるステップと、

前記半導体ウェハを前記パターニングされたマスク内の前記ギャップを通じてエッティングし、前記集積回路を個片化するステップとを含む方法。

## 【請求項 2】

請求項 1 に記載の方法において、

前記マスクを、前記マルチパルスバーストを用いるパルス列レーザスクライビング工程でパターニングするステップが、1バーストあたり2~5パルスのバーストを使用することを含む方法。

## 【請求項 3】

請求項 1 に記載の方法において、

前記マスクを、前記マルチパルスバーストを用いるパルス列レーザスクライビング工程

10

20

でパターニングするステップが、300 kHz ~ 10 MHz の範囲のバースト周波数と、前記バースト周波数の10 ~ 20倍のパルス周波数を使用することを含む方法。

**【請求項4】**

請求項3に記載の方法において、

前記パルス周波数により、50 ~ 500 フェムト秒の範囲のパルス時間間隔が提供される方法。

**【請求項5】**

請求項1に記載の方法において、

前記マスクを、前記マルチパルスバーストを用いるパルス列レーザスクライビング工程でパターニングするステップが、フェムト秒レーザを使用することを含む方法。 10

**【請求項6】**

請求項5に記載の方法において、

前記フェムト秒レーザを使用するステップが、540 ナノメートル以下の波長のレーザを使用することを含む方法。

**【請求項7】**

請求項1に記載の方法において、

前記マスクを、前記マルチパルスバーストを用いるパルス列レーザスクライビング工程でパターニングするステップが、前記半導体ウェハの前記集積回路間の前記領域に溝を形成することを含み、前記半導体ウェハをエッティングするステップが、前記マルチパルスバーストを用いるパルス列レーザスクライビング工程で形成された前記溝をエッティングすることを含む方法。 20

**【請求項8】**

複数の集積回路を含む半導体ウェハをダイシングするシステムであって、

ファクトリインタフェースと、

前記ファクトリインタフェースに連結され、マルチパルスバーストのパルス列を供給するように構成されたレーザを含むレーザスクライプ装置と、

前記ファクトリインタフェースに連結されたクラスタツールとを含み、前記クラスタツールは、プラズマエッティングチャンバを含み、前記ファクトリインタフェースは、前記レーザスクライプ装置を有する外部製造施設と前記クラスタツールとの間で前記半導体ウェハを搬送するためのものであり、前記レーザスクライプ装置は、前記半導体ウェハの上方に形成されたマスクをパターニングして、前記半導体ウェハの前記集積回路間の領域を露出させるギャップを形成するためのものであり、前記マルチパルスバーストのパルス列は、前記ギャップのカーブ幅及び深さを正確に制御するために使用され、前記プラズマエッティングチャンバは、前記ギャップを通じて前記半導体ウェハをエッティングするためのものであるシステム。 30

**【請求項9】**

請求項8に記載のシステムにおいて、

前記マルチパルスバーストのパルス列を供給するように構成されたレーザがモードロックレーザであるシステム。

**【請求項10】**

請求項9に記載のシステムにおいて、

前記モードロックレーザが、電気光学変調器と音響光学変調器からなる群から選択された変調器に基づくパルスピッカに連結されるシステム。 40

**【請求項11】**

請求項8に記載のシステムにおいて、

前記マルチパルスバーストのパルス列を供給するように構成されたレーザがフェムト秒レーザであるシステム。

**【請求項12】**

請求項11に記載のシステムにおいて、

前記フェムト秒レーザの波長が540 ナノメートル以下であるシステム。 50

**【請求項 1 3】**

請求項 8 に記載のシステムにおいて、

前記レーザスクライプ装置が、前記半導体ウェハの集積回路間のストリートのレーザアブレーションを実行するように構成され、前記プラズマエッチングチャンバが、前記レーザアブレーションの後に、前記半導体ウェハをエッチングして、前記集積回路を個片化するように構成されたシステム。

**【請求項 1 4】**

複数の集積回路を含む半導体ウェハのダイシング方法であって、

シリコン基板の上方にポリマ層を形成するステップであって、前記ポリマ層が、前記シリコン基板上に配置された集積回路を被覆し、保護し、前記集積回路が低誘電率材料層と銅層の上方に配置された二酸化ケイ素層を含むステップと、

前記ポリマ層、前記二酸化ケイ素層、前記低誘電率材料層及び前記銅層を、マルチパルスバーストを用いるパルス列レーザスクライビング工程でパターニングし、前記シリコン基板の前記集積回路間の領域を露出させるギャップを形成するステップであって、マルチパルスバーストを用いるパルス列レーザスクライビング工程は、前記ギャップのカーフ幅及び深さを正確に制御するために使用されるステップと、

前記シリコン基板を、前記ギャップを通じてエッチングして、前記集積回路を個片化するステップとを含む方法。

**【請求項 1 5】**

請求項 1 4 に記載の方法において、

前記二酸化ケイ素層、前記低誘電率材料層、前記銅層を、前記マルチパルスバーストを用いるパルス列レーザスクライビング工程でパターニングするステップが、前記二酸化ケイ素層のアブレーションを行ってから、前記低誘電率材料層と前記銅層のアブレーションを行うことを含む方法。

**【発明の詳細な説明】****【背景】****【0 0 0 1】****1 ) 分野**

本発明の実施形態は半導体加工分野に係り、特に各ウェハに複数の集積回路が搭載されている半導体ウェハのダイシング方法に関する。

**【0 0 0 2】****2 ) 関連技術の説明**

半導体ウェハの加工においては、集積回路がシリコン又はその他の半導体材料からなるウェハ（基板とも呼ばれる）の上に形成される。一般に、半導体、導体又は絶縁体のいずれかである各種材料の層を利用して集積回路が形成される。これらの材料は、集積回路形成のための周知の各種工程により、ドープ、堆積及びエッチングされる。各ウェハは、集積回路を搭載した、ダイスと呼ばれる個々の領域が多数形成されるように加工される。

**【0 0 0 3】**

集積回路形成工程に続き、ウェハは「ダイシング」されて、個々のダイが相互に分離され、その後パッケージングされるか、又はパッケージされない状態でより大きな回路に使用される。ウェハダイシングに使用される2つの主な技術が、スクライビングとソーイングである。スクライビングでは、先端がダイヤモンドのスクライプを、ウェハ表面を事前に形成されたスクライブラインに沿って横断するよう移動させる。これらのスクライブラインは、ダイス間の間隔に沿って延びる。このような間隔は一般に、「ストリート」と呼ばれる。ダイヤモンドスクライプにより、ウェハ表面にストリートに沿った浅い傷が形成される。例えばローラで圧力をかけると、ウェハはスクライブラインに沿って割断される。ウェハの割断はウェハ基板の結晶格子構造に従って起こる。スクライビングを用いることのできるウェハの厚さは、約 10 mil (1インチの 1 0 0 0 分の 1) 以下である。これより厚いウェハに関しては、現在のところ、ソーイングがダイシング方法として好ましい。

10

20

30

40

50

## 【0004】

ソーイングの場合、先端がダイヤモンドのソーが高い回転毎分で回転してウェハ表面と接触し、ウェハをストリートに沿って切断する。ウェハは、支持部材、例えばフィルムの枠にわたって引き伸ばされた接着フィルムの上に載せ、垂直及び水平ストリートの両方にソーを繰り返し当てる。スクライビング又はソーイングに伴う1つの問題は、ダイスのいくつかの縁辺に欠けやむしれが生じうことである。これに加えて、ダイスの縁辺にクラックが入り、そこから基板内へと伝播し、それによって集積回路が動作不能となる可能性がある。欠けやクラックはスクライビングの場合に特に問題であり、これは、正方形又は長方形のダイの片側しか、結晶構造の<110>方向にスクライブできないからである。したがって、ダイの反対側を割裂すると、分離線がぎざぎざになる。欠けやクラックが生じることから、ウェハ上のダイス間には、集積回路の損傷を防止するために、余分な間隔を設ける必要があり、例えば欠けやクラックが実際の集積回路から距離をおいて保持される。間隔要求によって、標準サイズのウェハ上にそれほど多くのダイスを形成できず、回路に使用できたはずのウェハ利用可能面積が無駄になる。ソーの使用により、半導体ウェハ上の利用可能面積の無駄がさらに増大する。ソーの刃の厚さは約15マイクロメートルである。そのため、ソーにより形成される切断部周辺のクラックやその他の損傷が確実に集積回路に損害を与えないようにするために、しばしば、各ダイスの回路間を300~500マイクロメートル離さなければならない。さらに、切断後に、各ダイを実質的に洗浄し、ソーイング工程で発生した粒子やその他の汚染物質を除去する必要がある。

10

## 【0005】

20

プラズマダイシングもしばしば使用されてきたが、同様に制約がありうる。例えば、プラズマダイシングの実行の障害となる1つの制約はコストであろう。レジストをパターニングするための標準的なリソグラフィ作業により、実行コストは法外なものとなりうる。プラズマダイシングの実行の障害となる可能性のある他の制約は、ストリートに沿ったダイシング中に一般的に遭遇する金属（銅等）のプラズマ加工が、製造上の問題やスループットの限界の原因となりうることである。

## 【概要】

## 【0006】

本発明の実施形態は、各ウェハに複数の集積回路が搭載されている半導体ウェハのダイシング方法を含む。

30

## 【0007】

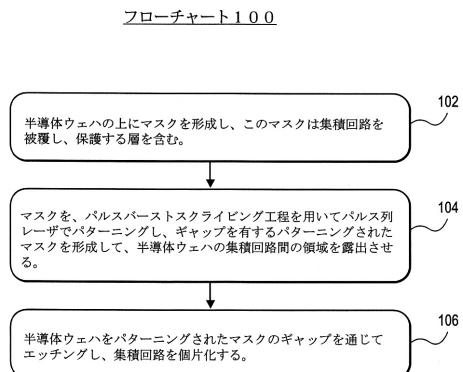

一実施形態において、複数の集積回路を有する半導体ウェハのダイシング方法は、半導体ウェハ上にマスクを形成するステップを含み、このマスクは集積回路を被覆し、保護する層を含む。マスクは次に、マルチパルスバーストを用いるパルス列レーザスクライビング工程でパターニングされ、ギャップを有するパターニングされたマスクが形成され、半導体ウェハの集積回路間の領域が露出する。次に、半導体ウェハは、パターニングされたマスクのギャップを通じてエッチングされて、集積回路が個片化される。

## 【0008】

他の実施形態において、半導体ウェハをダイシングするシステムは、ファクトリインタフェースを含む。レーザスクライブ装置は、ファクトリインタフェースに連結され、マルチパルスバーストのパルス列を供給するように構成されたレーザを含む。プラズマエッチングチャンバもまた、ファクトリインタフェースに連結される。

40

## 【0009】

他の実施形態において、複数の集積回路を有する半導体ウェハのダイシング方法は、シリコン基板上にポリマ層を形成するステップを含む。このポリマ層は、シリコン基板上に堆積された集積回路を被覆し、保護する。集積回路は、低誘電率材料層と銅層の上方に堆積された二酸化ケイ素層を含む。ポリマ層、二酸化ケイ素層、低誘電率材料層、銅層は、マルチパルスバーストを用いるパルス列レーザスクライビング工程により、シリコン基板の集積回路間の領域が露出するようにパターニングされる。その後、シリコン基板はギャップからエッチングされ、集積回路が個片化される。

50

**【図面の簡単な説明】****【0010】**

【図1】本発明の一実施形態に係る、複数の集積回路を含む半導体ウェハのダイシング方法の中の作業を示すフローチャートである。

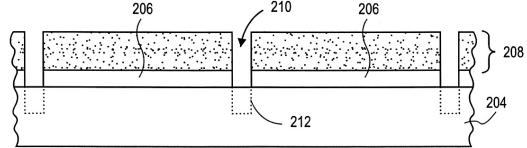

【図2A】本発明の一実施形態に係る、半導体ウェハダイシング方法の実行中の図1のフローチャートの作業102に対応する、複数の集積回路を含む半導体ウェハの断面図である。

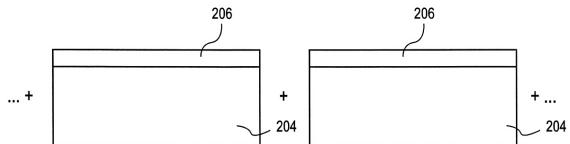

【図2B】本発明の一実施形態に係る、半導体ウェハダイシング方法の実行中の図1のフローチャートの作業104に対応する、複数の集積回路を含む半導体ウェハの断面図である。10

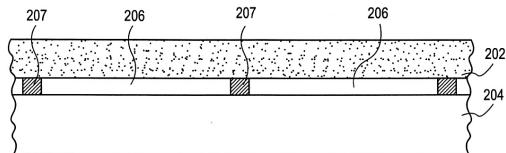

【図2C】本発明の一実施形態に係る、半導体ウェハダイシング方法の実行中の図1のフローチャートの作業106に対応する、複数の集積回路を含む半導体ウェハの断面図である。

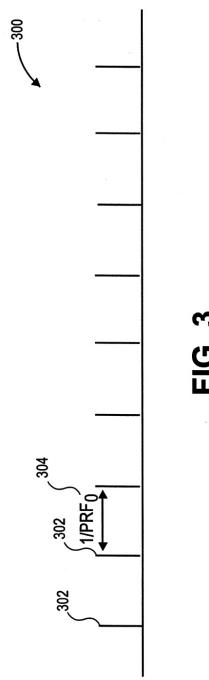

【図3】本発明の一実施形態に係る、単一パルスの時間プロットを示す。

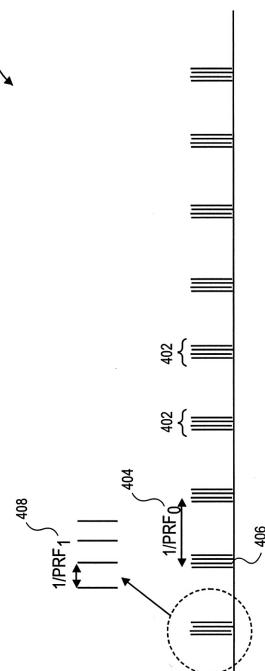

【図4】本発明の一実施形態に係る、マルチパルスバースト列の時間プロットを示す。

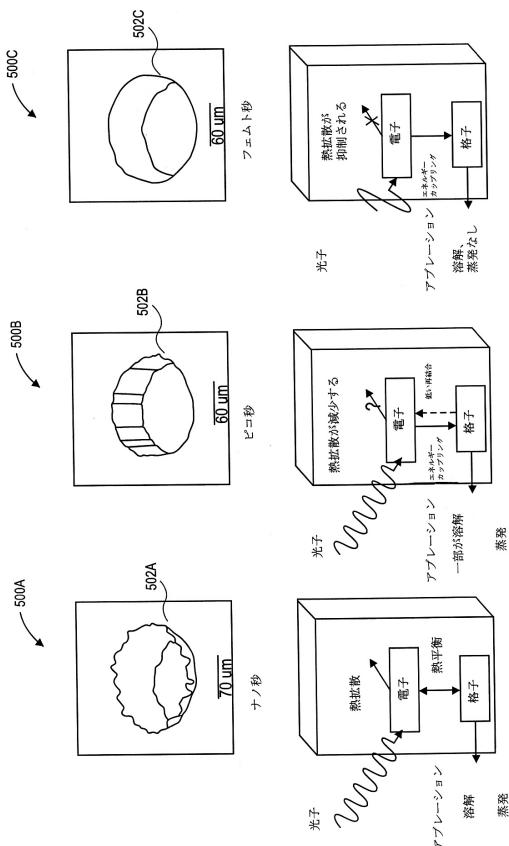

【図5】本発明の一実施形態に係る、フェムト秒範囲のレーザパルスを用いた場合の、それより長いパルス時間のものと比較した効果を示す図である。

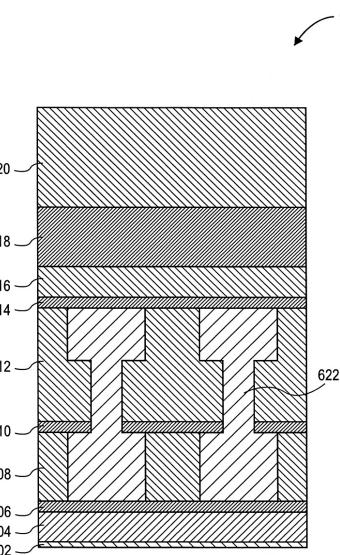

【図6】本発明の一実施形態に係る、半導体ウェハ又は基板のストリート領域に使用できる材料積層体の断面図である。20

【図7A】~

【図7D】本発明の一実施形態に係る、半導体ウェハのダイシング方法の中の各種作業を示す断面図である。

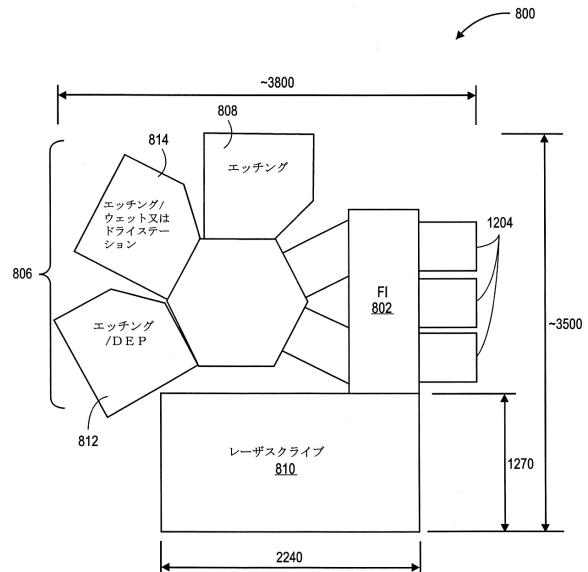

【図8】本発明の一実施形態に係る、ウェハ又は基板のレーザ及びプラズマダイシング用工具レイアウトのブロック図である。

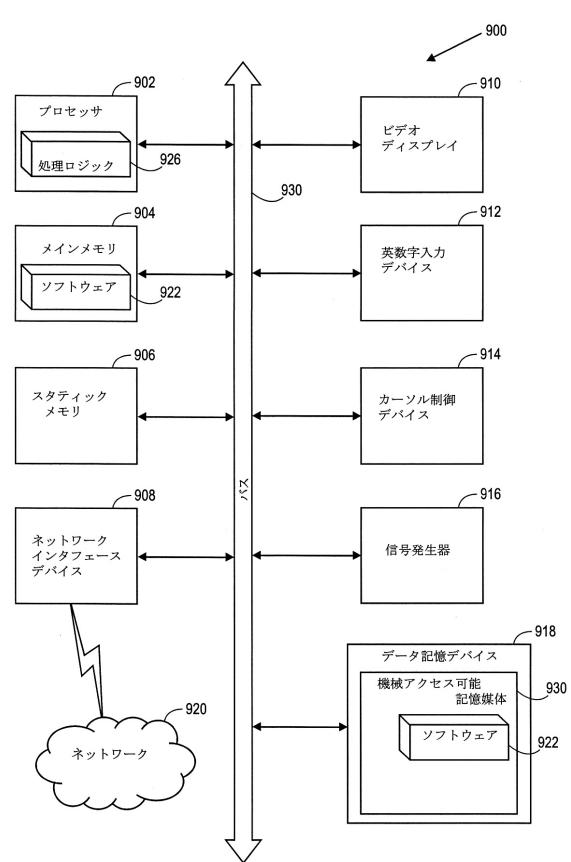

【図9】本発明の一実施形態に係る、例示的なコンピュータシステムのブロック図である。20

**【詳細な説明】****【0011】**

各ウェハに複数の集積回路が搭載されている半導体ウェハのダイシング方法が開示される。以下の説明において、多数の具体的な詳細、例えばパルス列マルチパルスバーストによるフェムト秒レーザスクライビングやプラズマエッチングの条件及び材料の詳細が、本発明の実施形態を十分に理解できるように明記されている。当業者にとっては当然のことながら、本発明の実施形態は、これらの具体的な詳細がなくても実施できる。また別の場合には、周知の態様、例えば集積回路の製造を、本発明の実施形態を必要に不明瞭としないように、詳細には説明していない。さらに、当然のことながら、図面に示された各種の実施形態は代表例であり、必ずしも一定の縮尺で描かれていません。30

**【0012】**

まず、レーザスクライブを行い、その後、プラズマエッチングを行う、ウェハ又は基板のハイブリッドダイシング工程を、ダイの個片化に利用してもよい。レーザスクライブ工程は、マスク層、有機及び無機誘電体層及びデバイス層をきれいに除去するために用いてもよい。その後、レーザエッチング工程は、ウェハ又は基板が露出するか、これらが部分的にエッチングされたところで終了してもよい。次に、ダイシング工程のプラズマエッチング部を用いて、ウェハ又は基板のバルクの全厚、例えばバルク単結晶シリコンの全厚をエッチングすることにより、ダイ又はチップの個片化、すなわちダイシングを行ってもよい。

**【0013】**

レーザスクライブとプラズマエッチングの複合的個片化工程のうちのレーザスクライブ部では、レーザによってマスク層、有機及び無機誘電体層、デバイス層を特定の順序で完全に除去することが望ましいこともある。次に、プラズマエッチング工程を、下地のシリコン層又は基板の残りのすべての部分の全厚に適用し、チップの個片化、すなわちダイシ40

50

ングを行う。フェムト秒レーザが工程の最初の部分で使用される場合であっても、主要な製造上の課題、例えば、これらに限定されないが、マイクロクラック、異なる層間の剥離、無機誘電体層の欠けの防止、厳格なカーフ幅制御の必要可能性、又は精密なアブレーション深さ制御の必要可能性が依然として存在しうる。

#### 【0014】

レーザアブレーションの場合、所定のパルス繰り返し率の単一パルス列を個片化対象のウェハ又は基板に印加してもよい。各パルスは一般に、時間的に等間隔である（例えば、パルス間の時間間隔は、パルス繰り返し周波数の逆数と等しい）。本発明の一実施形態によれば、単一パルス列の代わりに、時間波形整形フェムト秒マルチパルスバースト列がレーザスクライビング工程のために印加される。時間波形整形マルチパルスバースト列の印加は、イオン化工程をよりよく制御し、アブレーション閾値を下げるために使用してもよい。一実施形態において、マルチパルスバースト列は、アブレーション幅（カーフ幅等）と深さをより正確に制御するために使用される。10

#### 【0015】

それゆえ、本発明のある態様において、マルチパルスバーストを用いるパルス列レーザスクライビング工程とプラズマエッティング工程の組合せを使用して、半導体ウェハを個片化された集積回路にダイシングしてもよい。図1は、本発明の一実施形態による、複数の集積回路を有する半導体ウェハのダイシング方法の作業を示すフローチャート100である。図2A～2Cは、本発明の一実施形態による、半導体ウェハのダイシング方法の実行中のフローチャート100の作業に対応する、複数の集積回路を含む半導体ウェハの断面図である。20

#### 【0016】

フローチャート100の作業102と、これに対応する図2Aを参照すると、マスク202が半導体ウェハ又は基板204の上方に形成される。マスク202は、半導体ウェハ204の表面上に形成された集積回路206を被覆し、保護する層からなる。マスク202はまた、集積回路206の各々の間に形成される介在ストリート207も被覆する。

#### 【0017】

本発明の一実施形態によれば、マスク202を形成するステップは、層、例えば、これらに限定されないが、フォトレジスト層又はエラインパターニング層を形成することを含む。例えば、ポリマ層、例えばフォトレジスト層は、他の点でリソグラフィ工程用として適した材料で構成してもよい。一実施形態において、フォトレジスト層は、ポジティブフォトレジスト材料、例えば、これらに限定されないが、248ナノメートル(nm)対応レジスト、193nm対応レジスト、157nmの対応レジスト、極紫外線(EUV)対応レジスト又は、ジアゾナフトキノン増感剤を用いたフェノール樹脂マトリクス等からなる。他の実施形態において、フォトレジスト層は、ネガティブフォトレジスト材料、例えば、これらに限定されないが、ポリシスイソブレン及びポリビニルシンナメート等からなる。30

#### 【0018】

一実施形態において、半導体ウェハ又は基板204は、製造工程に耐えるのに適した材料からなり、その上に半導体加工層を適当に堆積させてもよい。例えば、一実施形態において、半導体ウェハ又は基板204はIV族材料、例えば、これらに限定されないが、結晶シリコン、ゲルマニウム又はシリコン/ゲルマニウムからなる。ある具体的な実施形態において、半導体ウェハ204を提供するステップは、単結晶シリコン基板を提供することを含む。ある特定の実施形態において、単結晶シリコン基板には不純物原子をドープする。他の実施形態において、半導体ウェハ又は基板204は、III-V族材料、例えば発光ダイオード(LED)の製作に使用されるIII-V族材料の基板からなる。40

#### 【0019】

一実施形態において、半導体ウェハ又は基板204の上又はその中に、集積回路206の一部として半導体デバイスのアレイが設置される。このような半導体デバイスの例としては、これらに限定されないが、シリコン基板内に製作され、誘電体層の中に包囲された

50

20

30

40

50

メモリデバイス又は相補型金属酸化物半導体( C M O S )トランジスタ等がある。複数の金属製相互接続配線をデバイス又はトランジスタの上及び、周囲の誘電体層の中に形成してもよく、これを使用して、デバイス又はトランジスタを電気的に連結して集積回路 206 を形成してもよい。ストリート 207 を構成する材料は、集積回路 206 を形成するために使用された材料と同様又は同じであってもよい。例えば、ストリート 207 は、誘電体材料、半導体材料及び金属配線の層からなっていてもよい。一実施形態において、ストリート 207 の 1 つ又はそれ以上には、集積回路 206 の実際のデバイスと同様の試験デバイスが含まれる。

#### 【 0 0 2 0 】

フローチャート 100 の作業 104 と、これに対応する図 2B を参照すると、マスク 202 がマルチパルスバーストを用いるパルス列レーザスクライビング工程によってパターンングされて、ギャップ 210 を有するパターンングされたマスク 208 が形成され、半導体ウェハ又は基板 204 の集積回路 206 間の領域が露出する。したがって、レーザスクライビング工程を使って、もともと集積回路 206 間に形成されていたストリート 207 の材料が除去される。本発明の一実施形態によれば、マスク 202 を、マルチパルスバーストを用いるパルス列レーザスクライビング工程によってパターンングするステップは、図 2B に示すように、一部分が半導体ウェハ 204 の集積回路 206 間の領域の中に入る溝 212 を形成することを含む。

#### 【 0 0 2 1 】

レーザパルス列は、フローチャート 100 の作業 104 に関連して使用してもよい。例えば、図 3 は、本発明の一実施形態による単一パルス列の時間プロット 300 を示す。図 3 を参照すると、単一パルス 302 の列は、水平軸に沿って時間的に示されるパルス繰り返し周波数( P R F<sub>0</sub> ) 304 に基づいている。単一パルス 302 間の間隔は、図 3 に示すように、 P R F<sub>0</sub> の逆数である。すなわち、各パルス 302 は一般に、時間的に均等に離間されている( 例えば、パルス間の時間的間隔がパルス繰り返し周波数の逆数と等しい )。単一パルス 302 の列は、個片化対象のウェハ又は基板に印加されてもよい。

#### 【 0 0 2 2 】

アブレーションが行われる層の複雑さに応じて、単一パルス列が提供するエネルギーは、アブレーション実行のために最適ではない場合がある。しかしながら、単一パルス幅でより高い強度を提供した場合、欠陥の発生につながりうる。その代わりに、マルチパルスバースト列をアブレーションに使用してもよい。例えば、図 4 は、本発明の一実施形態によるマルチパルスバースト列の時間プロット 400 を示す。

#### 【 0 0 2 3 】

図 4 を参照すると、マルチパルスバースト 402 の列は、水平軸に沿って時間的に示される第 1 のパルス繰り返し周波数( P R F<sub>0</sub> ) 404 に基づいている。マルチパルスバースト 402 間( 例えば、単一パルス 406 の集合の中心間 )の間隔は、図 4 に示すように、 P R F<sub>0</sub> の逆数である。すなわち、各マルチパルスバースト 402 は一般に、時間的に等間隔である( 例えば、マルチパルスバーストの集合とマルチパルスバーストの集合との時間的間隔が、第 1 のパルス繰り返し周波数の逆数に等しい )。マルチパルスバースト 402 の中の単一パルス 406 の各々は、同様に水平軸に沿って時間的に示される第 2 のパルス繰り返し周波数( P R F<sub>1</sub> ) 408 に基づく。単一パルス 406 間の間隔は、図 4 に示すように、 P R F<sub>1</sub> の逆数である。すなわち、各単一パルス 406 は一般に、時間的に均等に離間されている。マルチパルスバースト 402 の列は、個片化対象のウェハ又は基板に印加されてもよい。

#### 【 0 0 2 4 】

所定のマルチパルスバースト 402 に使用する単一パルス 406 は、任意の好適な数であってもよい。一実施形態において、所定のマルチパルスバースト 402 の中に使用される単一パルス 406 の数は、約 2 ~ 5 の範囲である。一実施形態において、第 1 のパルス繰り返し周波数( P R F<sub>0</sub> ) 404 は、約 2 0 0 k H z ~ 1 0 M H z の範囲であるが、好みしくは 5 0 0 k H z ~ 5 M H z の範囲である。1 つのこのような実施形態において、第

10

20

30

40

50

2 のパルス繰り返し周波数 ( P R F<sub>1</sub> ) 408 は、第1のパルス繰り返し周波数 ( P R F<sub>0</sub> ) 404 の約 10 ~ 20 倍である ( 例えば、単一パルス 406 間の間隔はマルチパルスバースト 402 の中心間の間隔の約 1 / 10 ~ 1 / 20 の緊密さである。他のこのような実施形態において、所定のマルチパルスバースト 402 の中の単一パルス 406 間の間隔は、約数 10 ~ 数 100 フェムト秒の範囲、例えば約 50 ~ 500 フェムト秒の範囲の時間間隔に基づく。ある具体的な実施形態において、マルチパルスバースト 402 は、一定のバースト繰り返し率で供給される。 )

#### 【 0025 】

図 3 と 4 を再び参照すると、プロット 300 のパルス列は、各バーストの中に 1 つのパルスだけがある、時間的に整形されたフェムト秒パルスバースト列と考えてもよい。これに対して、プロット 400 のパルス列は、各バースト内に 2 つ以上のパルスがある、時間的に整形されたフェムト秒マルチパルスバースト列である。このようなマルチパルスバーストと単一パルスバーストを使用することにより、一実施形態において、個片化のためにウェハ又は基板により消費される光子エネルギーが小さくなり、その結果、熱損傷が少なくなる。熱損傷が少ないことから、マイクロクラック、異なる層間の剥離、又は有機誘電体層の欠けが最小限となりうる。本発明の一実施形態によれば、時間的に整形されたフェムト秒マルチパルスバースト列は、単一パルス列の代わりに、レーザスクライビング工程に利用される。この方法は、スクライビングのためにウェハ又は基板、又はその上の膜に供給されるレーザ強度を量子化しうる。 )

#### 【 0026 】

一実施形態において、パルスバースト 402 の個々のパルス 406 は、第 1 と第 2 のパルス繰り返し率を持つパルス列という形態のモードロックレーザを使用することによって供給してもよい。そのようなパルス列から、例えば特定のパルスだけを伝送し、その他すべてをブロックするために、供給する特定のパルスを選択してもよい。選択的な供給は、パルスピッカで実行してもよく、これは基本的に、電気的に制御される光スイッチである。一実施形態において、パルスピッカは、電気光学変調器又は音響光学変調器に、適当な電子ドライバを組み合わせたものに基づく。 )

#### 【 0027 】

電気光学機器の場合、パルスピッカは、ポッケルスセル及び偏光光学系、例えば薄膜偏光板で構成されてもよい。ポッケルスセルは偏光状態を操作するために使用してもよく、すると、偏光板はパルスをその偏光に応じて伝送又はブロックすることができる。音響光学パルスピッカの場合、短い R F パルスを音響光学変調器に印加して、所望のパルスを若干変化させた方向に偏向させてもよい。その後、偏向されたパルスは開口部を通過してもよく、これに対してその他はブロックされる。いずれの場合も、必要な変調器速度は、パルス幅によってではなく、そのパルス列におけるパルスの時間的距離によって ( 例えば、パルス源のパルス繰り返し率によって ) 決定されてもよい。 )

#### 【 0028 】

パルスピッカの電子ドライバは、別の機能を果たしてもよい。例えば、一実施形態において、電子ドライバは高速フォトダイオードからの信号を使用し、当初のパルス列を感じし、切替を入力パルスと同期させる。すると、トリガ信号はいつ発生されてもよく、電子機器が適正なタイミングでスイッチに作用して、次に到達する入力パルスを伝送する。超短パルスの高いパルスエネルギーを得るために、パルス繰り返し率を低くしてもよい。率を下げるには、パルスピッカをシードレーザと増幅器との間に設置してもよい。増幅器は、所望のパルスにのみ作用するように構成される。ブロックされたパルスは必ずしも強いエネルギー損失となるわけではなく、これは、シードレーザの平均出力が、増幅器の平均出力と比較して小さいこともあり、残りの平均出力で十分に増幅器を飽和させることができるからである。 )

#### 【 0029 】

あるパルス列の中にマルチパルスバーストを使用したとしても、フェムト秒レーザを使用することにより ( ピコ秒レーザ又はナノ秒レーザ等と比較して ) 、個片化工程の対象の )

10

20

30

40

50

複雑な積層体のアブレーション性能をさらに最適化してもよい。それゆえ、一実施形態において、レーザスクライビング工程でマスク 206 をパターニングするステップは、パルス幅がフェムト秒範囲のレーザを使用することを含む。具体的には、波長が可視スペクトル領域及び紫外線（U V）と赤外線（I R）範囲（全体として、広帯域光スペクトラル）のレーザを使用して、フェムト秒レーザ、すなわち、パルス幅がフェムト秒（ $10^{-15}$  秒）のオーダーのレーザを提供してもよい。一実施形態において、アブレーションは全く、又は基本的に波長依存しないため、マスク 202、ストリート 207 及び、おそらくは半導体ウェハ又は基板 204 の一部の膜といった複雑な膜に適している。

## 【0030】

図 5 は、本発明の一実施形態による、フェムト秒範囲のレーザパルスを使用した場合の、より長いパルス幅の場合と比較した効果を示している。図 5 を参照すると、フェムト秒範囲のパルス幅のレーザを使用すると、熱損傷の問題は、より長いパルス幅の場合（例えば、ビア 500B のピコ秒での加工においては 502B のように損傷が見られ、ビア 500A のナノ秒での加工においては 502A のように大きな損傷が見られる）に対して、軽減又は排除される（例えば、ビア 500C のフェムト秒での加工においては 502C のように損傷はわずかか、まったくない）。ビア 500C の形成中に損傷が排除又は軽減されるのは、図 5 に示すように、低エネルギー再結合（ピコ秒レーザアブレーションの場合に見られる）又は熱平衡（ナノ秒レーザアブレーションの場合に見られる）がないからでありうる。

## 【0031】

パルス幅等のレーザパラメータの選択は、レーザスクライプによる鮮鋭な切断を実現するために、欠け、マイクロクラック及び層間剥離を最小限にする良好なレーザスクライビング及びダイシング工程を開発する上で重要であろう。レーザクライプの切断面が鮮鋭であるほど、最終的なダイ個片化のために実行されるエッチング工程が円滑になる。半導体デバイス用ウェハには、一般に、材料タイプ（導体、絶縁体、半導体等）と厚さの異なる多くの機能層が積層される。このような材料には例えば、これらに限定されないが、ポリマ等の有機材料、金属又は、二酸化ケイ素又は窒化ケイ素等の無機誘電材料がある。

## 【0032】

ウェハ又は基板上に堆積される個々の集積回路間のストリートは、集積回路そのものと同様又は同じ層を含んでいてもよい。例えば、図 6 は、本発明の一実施形態による、半導体ウェハ又は基板のストリート領域に使用可能な材料の積層体の断面図である。

## 【0033】

図 6 を参照すると、ストリート領域 600 は、シリコン基板 602 の上部、第 1 の二酸化ケイ素層 604、第 1 のエッチトップ層 606、第 1 の低誘電率層 608（例えば、二酸化ケイ素に関しては、誘電率が 4.0 未満の誘電率を有する）、第 2 のエッチトップ層 610、第 2 の低誘電率層 612、第 3 のエッチトップ層 614、ドープなし石英ガラス（USG）層 616、第 2 の二酸化ケイ素層 618、フォトレジスト層 620 を含み、図には相対的な厚さが示されている。銅配線層 622 は、第 1 と第 3 のエッチトップ層 606 と 614 の間に、第 2 のエッチトップ層 610 を貫通して堆積される。ある具体的な実施形態において、第 1、第 2、第 3 のエッチトップ層 606、610、614 は窒化ケイ素からなり、低誘電率層 608、612 は炭素ドープ酸化ケイ素材料からなる。

## 【0034】

従来のレーザ照射（例えば、ナノ秒又はピコ秒レーザ照射）を受けると、ストリート 600 の材料は、光吸収及びアブレーションメカニズムの点で、まったく異なる挙動を示す。例えば、二酸化ケイ素等の誘電体層は、通常の条件下で、事実上商用のレーザ波長すべてを透過させる。これに対して、金属、有機物（低誘電率材料等）及びケイ素は、特にナノ秒又はピコ秒レーザ照射に応答して、光子と容易に結合する。一実施形態において、マルチパルスバースト列レーザは、二酸化ケイ素層のアブレーションを行ってから、低誘電率材料層と銅層のアブレーションを行うことにより、フェムト秒レーザスクライビング工

10

20

30

40

50

程で二酸化ケイ素層、低誘電率材料層、銅層をパターニングするために使用される。

#### 【0035】

本発明の一実施形態において、適当なフェムト秒レーザ工程は、ピーク強度（放射照度）が高く、通常、これによって各種材料における相互作用が非線形となることを特徴とする。1つのこのような実施形態において、フェムト秒レーザ源のパルス幅は、約10フェムト秒～500フェムト秒の範囲であるが、好ましくは、100フェムト秒～400フェムト秒の範囲である。一実施形態において、フェムト秒レーザ源の波長は、約1570ナノメートル～200ナノメートルの範囲であるが、好ましくは540ナノメートル～250ナノメートルの範囲である。一実施形態において、レーザとこれに対応する光学システムにより、作業面でられる焦点は、約3マイクロメートル～15マイクロメートルの範囲であるが、好ましくは約5マイクロメートル～10マイクロメートルの範囲である。10

#### 【0036】

作業面の空間ビームプロファイルは、シングルモード（ガウシアン）であっても、整形トップハットプロファイルであってもよい。一実施形態において、レーザ源が供給する作業面でのパルスエネルギーは、約0.5μJ～100μJであるが、好ましくは約1μJ～5μJである。一実施形態において、レーザスクライピング工程が加工対象物の表面に沿って実行される速度は、約300mm/秒～5m/秒の範囲であるが、好ましくは約500mm/秒～2m/秒の範囲である。

#### 【0037】

スクライピング工程は、1行程のみであっても、あるいは複数行程でもよいが、一実施形態では、好ましくは1～2行程である。一実施形態において、加工対象物のスクライピング深さは、約5マイクロメートル～50マイクロメートルの深さの範囲、好ましくは10マイクロメートル～20マイクロメートルの深さの範囲である。一実施形態において、発生されるレーザビームのカーフ幅は、約2マイクロメートル～15マイクロメートルの範囲であるが、シリコンウェハのスクライピング／ダイシングにおいては、デバイス／シリコン界面で測定して、好ましくは約6マイクロメートル～10マイクロメートルの範囲である。20

#### 【0038】

レーザパラメータは、十分に高いレーザ強度を提供して、無機誘電体（二酸化ケイ素等）のイオン化を達成し、無機誘電体の直接アブレーションの前に下層の損傷により発生する剥離と欠けを最小限にすること等の恩恵と利点が得られるように選択してもよい。また、パラメータは、アブレーション幅（カーフ幅等）と深さを正確に制御して、工業用として有意義な工程スループットが得られるように選択してもよい。前述のように、フェムト秒レーザは、ピコ秒及びナノ秒レーザアブレーション工程と比較して、上記の利点を提供するのに格段に適している。30

#### 【0039】

しかしながら、フェムト秒レーザアブレーションのスペクトルの中でも、特定の波長においては、他の波長よりよい性能が提供されうる。例えば、一実施形態において、UV範囲に近い、又はその範囲内の波長のフェムト秒レーザ工程では、IR範囲に近い、又はその範囲内の波長のフェムト秒レーザ工程より鮮鋭なアブレーション工程が提供される。ある具体的なこののような実施形態において、半導体ウェハ又は基板のスクライピングに適したフェムト秒レーザ工程は、約540ナノメートル以下の波長のレーザに基づく。ある特定のこののような実施形態において、約540ナノメートル以下の波長のレーザの約400フェムト秒以下のパルスが使用される。しかしながら、代替の実施形態では、2波長レーザ（IRレーザとUVレーザの組合せ等）が使用される。40

#### 【0040】

フローチャート100の作業106と、これに対応する図2Cを参照すると、半導体ウェハ204は、パターニングされたマスク208のギャップ210からエッチングされ、集積回路206が個片化される。本発明の一実施形態によれば、半導体ウェハ204をエッチングするステップは、図2Cに示すように、マルチパルスバーストのパルス列を使用50

したレーザスクライビング工程で当初形成された溝 212 をエッティングすることにより、最終的に半導体ウェハ 204 の全厚を完全にエッティングすることを含む。

#### 【0041】

一実施形態において、半導体ウェハ 204 をエッティングするステップは、プラズマエッティング工程を使用することを含む。一実施形態においては、シリコン貫通ピア型エッティング工程が使用される。例えば、ある具体的な実施形態において、半導体ウェハ 204 の材料のエッティング速度は、毎分 25 マイクロメートルを超える。超高密度プラズマ源をダイ個片化工程のプラズマエッティング部に使用してもよい。このようなプラズマエッティング工程の実行に適したプロセスチャンバの 1 例は、米国カリフォルニア州 Sunnyvale の Applied Materials から入手可能な Applied Centura (登録商標) Silvia (商標) Etch システムである。Applied Centura (登録商標) Silvia (商標) Etch システムは、容量性及び誘導型 RF 結合を組み合わせたもので、それによって、たとえ磁力強化により改善されたとしても、容量性カップリングのみを用いた場合に可能な程度より、はるかに独立してイオン密度とイオンエネルギーを制御できる。このような組合せによって、イオン密度とイオンエネルギーを有効に切り離し、非常に低圧であっても、DC バイアスを損傷しうるほど高いレベルとすることなく、比較的高密度のプラズマを提供できる。その結果、プロセスウィンドウを例外的に広くすることができる。しかしながら、シリコンのエッティングが可能な、どのようなプラズマエッティングチャンバを使用してもよい。ある例示的な実施形態においては、深掘りシリコンエッティングを使用して、単結晶シリコン基板又はウェハ 404 を、従来のシリコンエッティング速度の約 40 % より速いエッティング速度でエッティングし、その際、常にプロファイル制御は基本的に正確に行われ、側壁は事実上、スカラップのない状態とされる。ある具体的な実施形態において、シリコン貫通ピア型エッティング工程が使用される。このエッティング工程は、反応性ガスから発生されるプラズマに基づいており、このガスは一般に、SF<sub>6</sub>、C<sub>4</sub>F<sub>8</sub>、CHF<sub>3</sub>、XeF<sub>2</sub> 等のフッ素系ガス又は、比較的高速のエッティング速度でシリコンをエッティングできる他の反応性ガスである。一実施形態において、図 4C に示すように、マスク層 408 は個片化工程の後に除去される。10 20

#### 【0042】

したがって、フローチャート 100 と図 2A ~ 2C を再び参照すると、ウェハダイシングは、マスク層全厚、ウェハストリート（金属配線層を含む）全厚と、シリコン基板の一部の、パルス列レーザスクライビング工程を用いた初期のアブレーションによって実行してもよい。その後、これに続くシリコン全厚の深掘りプラズマエッティングによってダイの個片化を完了させてもよい。本発明の一実施形態によるダイシングのための材料積層体の具体例を、図 7 ~ 7D に関連して、以下に説明する。30

#### 【0043】

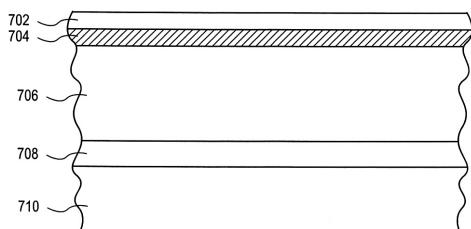

図 7A を参照すると、レーザアブレーションとプラズマエッティングのハイブリッドダイシングのための材料積層体は、マスク層 702、デバイス層 704、基板 706 を含む。マスク層、デバイス層、基板層は、裏打ちテープ 710 に接着されたダイアタッチフィルム 708 の上に堆積される。一実施形態において、マスク層 702 はフォトレジスト層、例えばマスク 202 に関して上述したフォトレジスト層である。デバイス層 704 は、1 つ又はそれ以上の金属層（例えば、銅層）及び 1 つ又はそれ以上の低誘電率誘電体層（例えば、炭素ドープ酸化物層）の上に堆積された無機誘電体層（例えば、二酸化ケイ素）を含む。デバイス層 704 はまた、集積回路間に配置されたストリートを含み、これらのストリートは集積回路と同じ又は同様の層を含む。基板 706 は、バルク単結晶シリコン基板である。40

#### 【0044】

一実施形態において、バルク単結晶シリコン基板 706 は、裏面から薄化されてから、ダイアタッチフィルム 708 に接着される。薄化は、裏面研削工程により行ってもよい。一実施形態において、バルク単結晶シリコン基板 706 は、厚さ約 50 ~ 100 マイクロメートルの範囲まで薄化される。留意すべき点として、一実施形態において、薄化は、レ50

ーザアプリケーションとプラズマエッティングによるダイシング工程の前に行われる。一実施形態において、フォトレジスト層702の厚さは、約5マイクロメートルであり、デバイス層704の厚さは、約2～3マイクロメートルの範囲である。一実施形態において、ダイアタッチフィルム708（又は、薄化された、又は薄いウェハ又は基板を裏打ちテープ710に接着できる、どのような適当な代替物であってもよい）の厚さは、約20マイクロメートルである。

#### 【0045】

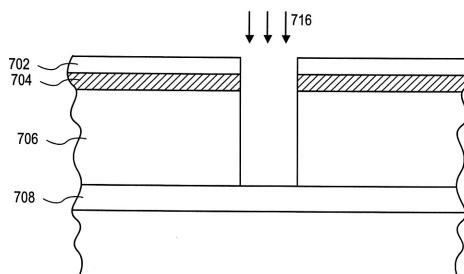

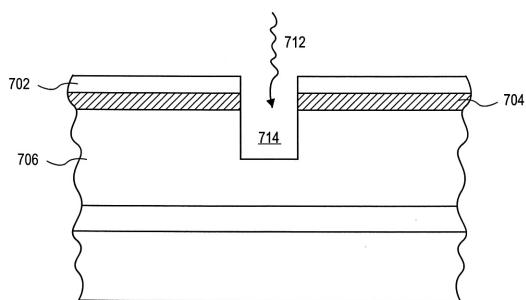

図7Bを参照すると、マスク702、デバイス層704、基板706の一部が、マルチパルスバーストを使用したパルス列レーザスクライビング工程712によってパターニングされ、基板706に溝714が形成される。図7Cを参照すると、シリコン貫通深掘りプラズマエッティング工程716を使って、溝714がダイアタッチフィルム708まで延ばされ、ダイアタッチフィルム708の上部が露出し、それによってシリコン基板706が個片化される。デバイス層704は、シリコン貫通深掘りプラズマエッティング工程716の実行中、フォトレジスト層702により保護される。

10

#### 【0046】

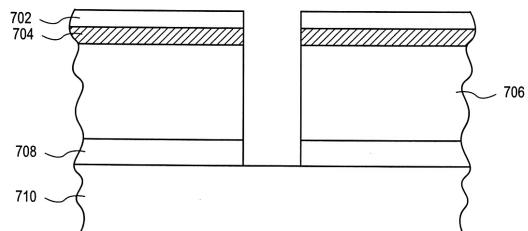

図7Dを参照すると、個片化工程はさらに、ダイアタッチフィルム708をパターニングするステップを含み、これによって裏打ちテープ710の上部が露出し、ダイアタッチフィルム708が個片化される。一実施形態において、ダイアタッチフィルムは、レーザ工程又はエッティングプロセスによって個片化される。さらなる実施形態は、その後、基板706の個片化された部分（個々の集積回路等）を裏打ちテープ710から剥がすステップを含んでいてもよい。一実施形態において、個片化されたダイアタッチフィルム708は、基板706の個片化された部分の裏面に保持される。他の実施形態は、マスキング用フォトレジスト層702をデバイス層704から除去するステップを含んでいてもよい。代替の実施形態において、基板706が約50マイクロメートルより薄い場合、レーザアプリケーション工程712を使って基板706を完全に個片化し、追加のプラズマ工程を利用しない。

20

#### 【0047】

ダイアタッチフィルム708を個片化した後に、一実施形態では、マスキング用フォトレジスト層702がデバイス層704から除去される。一実施形態において、個片化された集積回路は裏打ちテープ710から除去されて、パッケージングされる。このような一実施形態において、パターニングされたダイアタッチフィルム708は各集積回路の裏面に保持され、最終的なパッケージングに含められる。しかしながら、他の実施形態では、パターニングされたダイアタッチフィルム708は、個片化工程中又はその後に除去される。

30

#### 【0048】

マルチパルスバースト列レーザアプリケーションとプラズマエッティングのハイブリッド個片化工程の中の作業の多く又は全部を実行するように、1つの加工ツールを構成してもよい。例えば、図8は、本発明の一実施形態による、ウェハ又は基板のレーザ及びプラズマダイシングのためのツールレイアウトのブロック図である。

40

#### 【0049】

図8を参照すると、加工ツール800は、複数のロードロック804が連結されたファクトリインタフェース802（FI）を含む。クラスタツール806がファクトリインタフェース802に連結されている。クラスタツール806は、1つ又はそれ以上のプラズマエッティングチャンバ、例えばプラズマエッティングチャンバ808を含む。レーザスクライブ装置810もまた、ファクトリインタフェース802に連結されている。加工ツール800の全体的設置面積は、一実施形態において、図8に示すように、約3500ミリメートル（3.5メートル）×約3800ミリメートル（3.8メートル）である。

#### 【0050】

一実施形態において、レーザスクライブ装置810は、マルチパルスバーストのパルス列を供給するように構成されたレーザを格納する。このレーザは、ハイブリッド式のレー

50

ザ及びエッティング個片化工程のレーザアブレーション部、例えば前述のレーザアブレーション工程を実行するのに適している。一実施形態において、可動ステージもまたレーザスクライプ装置 810 に含まれており、この可動ステージは、ウェハ又は基板（又はそのキャリア）をレーザに関して移動させるように構成される。ある具体的な実施形態においては、レーザもまた可動式である。レーザスクライプ装置 810 の全体的な設置面積は、一実施形態において、図 8 に示すように、約 2240 ミリメートル × 約 1270 ミリメートルであってもよい。

#### 【0051】

一実施形態において、1つ又はそれ以上のプラズマエッティングチャンバ 808 は、パターニングされたマスクの中のギャップからウェハ又は基板をエッティングし、複数の集積回路を個片化するように構成されている。1つのこのような実施形態において、その1つ又はそれ以上のプラズマエッティングチャンバ 808 は、深掘りシリコンエッティング工程を実行するように構成されている。ある具体的な実施形態において、その1つ又は複数のプラズマエッティングチャンバ 808 は、米国カリフォルニア州 Sunnyvale の Applied Materials から入手可能な Applied Centura（登録商標）Silvia（商標）Etch システムである。エッティングチャンバは、単結晶シリコン基板又はウェハの上又は中に格納された個々の集積回路を製作するために使用可能な深掘りシリコンエッティング用として特に設計されていてもよい。一実施形態において、シリコンエッティングを高速化しやすくするために、高密度プラズマ源がプラズマエッティングチャンバ 808 内に含められている。一実施形態において、複数のエッティングチャンバが加工ツール 800 のクラスタツール 806 部に含められ、個片化又はダイシング工程の高い製造スループットを実現する。

#### 【0052】

ファクトリインタフェース 802 は、レーザスクライプ装置 810 を有する外部製造施設とクラスタツール 806 との間をつなぐ適當な大気開放ポートであってもよい。ファクトリインタフェース 802 は、貯蔵ユニット（例えば、前方開口式カセット一体型搬送保管箱）からクラスタツール 806 又はレーザスクライプ装置 810 のいずれか又は両方にウェハ（又はそのキャリア）を搬送するためのアーム又はブレードを備えるロボットを含んでいてもよい。

#### 【0053】

クラスタツール 806 は、個片化方法において機能を果たすのに適した他のチャンバを含んでいてもよい。例えば、一実施形態において、別のエッティングチャンバの代わりに、成膜チャンバ 812 が含まれる。成膜チャンバ 812 は、ウェハ又は基板のレーザスクライピングの前に、ウェハ又は基板のデバイス層の上又は上方にマスクを蒸着するように構成されていてもよい。一実施形態において、成膜チャンバ 812 は、フォトレジスト層の成膜に適している。他の実施形態において、別のエッティングチャンバの代わりに、ウェット／ドライステーション 814 を含める。ウェット／ドライステーションは、基板又はウェハのレーザスクライプ及びプラズマエッティング個片化工程の後の残渣や破片の洗浄又はマスクの除去に適していてもよい。一実施形態においては、計量ステーションもまた工程ツール 800 の構成要素として含められる。

#### 【0054】

本発明の実施形態は、命令が記憶された機械可読媒体を含むことができるコンピュータプログラム製品、すなわちソフトウェアとして提供してもよく、これらを用いて、本発明の実施形態による工程を実行するようにコンピュータシステム（又はその他の電子デバイス）をプログラムしてもよい。一実施形態において、コンピュータシステムは、図 8 に関する説明した加工ツール 800 と連結されていてもよい。機械可読媒体は、機械（コンピュータ等）によって読み取可能な形態の情報を記憶又は転送するためのどのような機構を含んでいてもよい。例えば、機械可読（コンピュータ可読等）の媒体としては、機械（コンピュータ等）可読記憶媒体（リードオンリーメモリ（ROM）、ランダムアクセスメモリ（RAM）、磁気ディスク記憶媒体、光記憶媒体、フラッシュメモリデバイス等）、機

10

20

30

40

50

械（コンピュータ等）可読伝送媒体（電気、光、音響又はその他の形態による伝播信号（赤外線信号、デジタル信号等））その他が含まれる。

#### 【0055】

図9は、機械に本明細書に記載した方法のいずれか1つ又はそれ以上を実行させるための1つの命令セットを実行することができる、コンピュータシステム900の例示的形態機械を表す概略図である。他の実施形態において、機械は、ローカルエリアネットワーク（LAN）、インターネット、エクストラネット又はインターネットにおいて他の機械に接続（ネットワーク接続等）されてもよい。機械は、クライアント・サーバネットワーク環境におけるサーバ又はクライアントマシンとして、又はピア・ツー・ピア（又は分散型）ネットワーク環境におけるピアマシンとして動作してもよい。機械は、パーソナルコンピュータ（PC）、タブレットPC、セットトップボックス（STB）、携帯型情報端末（PDA）、携帯電話、ウェブアプライアンス、サーバ、ネットワークルータ、スイッチ又はブリッジ、あるいはその機械により実行される動作を特定する1つの命令セット（逐次的又はその他）を実行できるどのような機械であってもよい。さらに、1台の機械だけが示されているが、「機械（マシン）」という用語はまた、個々に、又は共同で1つの（又は複数の）命令セットを実行して、本明細書に記載の方法のいずれか1つ又は複数を行う任意の機械（コンピュータ等）の集合を含むと理解するものとする。10

#### 【0056】

例示的なコンピュータシステム900は、プロセッサ902、メインメモリ904（リードオンリーメモリ（ROM）、フラッシュメモリ、同期DRAM（SDRAM）又はラムバスDRAM（RDRAM）等のダイナミックランダムアクセスメモリ（DRAM）その他等）、スタティックメモリ906（フラッシュメモリ、スタティックランダムアクセスメモリ（SRAM）その他等）と、補助メモリ918（データ記憶デバイス等）を含み、これらはバス930を介して相互に通信する。20

#### 【0057】

プロセッサ902は、1つ又は複数の汎用処理デバイス、例えばマイクロプロセッサ、中央処理ユニット等を表す。より具体的には、プロセッサ902は、複合命令セット演算（CISC）マイクロプロセッサ、縮小命令セット演算（RISC）マイクロプロセッサ、超長命令語（VLIW）マイクロプロセッサ、他の命令セットを実行するプロセッサ、又は複合的な命令セットを実行するプロセッサであってもよい。プロセッサ902はまた、1つ又は複数の特定用途処理デバイス、例えば、特定用途集積回路（ASIC）、フィールドプログラマブルゲートアレイ（FPGA）、デジタル信号プロセッサ（DSP）、ネットワークプロセッサ又はその他であってもよい。プロセッサ902は、本明細書に記載する作業を行うための処理ロジック926を実行するように構成される。30

#### 【0058】

コンピュータシステム900は、ネットワークインターフェースデバイス908をさらに含んでいてもよい。コンピュータシステム900はまた、ビデオディスプレイユニット910（液晶ディスプレイ（LCD）、発光ダイオードディスプレイ（LED）又は陰極線管（CRT）等）、英数字入力デバイス912（キーボード等）、カーソル制御デバイス914（マウス等）及び信号発生器916（スピーカ等）を含んでいてもよい。40

#### 【0059】

補助メモリ918は、機械アクセス可能記憶媒体（又は、より具体的には、コンピュータ可読記憶媒体）931を含んでいてもよく、そこには本明細書に記載した方法又は機能のいずれか1つ又はそれ以上を実行する1つ又は複数の命令セット（ソフトウェア922等）が記憶されている。ソフトウェア922はまた、コンピュータシステム900によるその実行中、完全に、又は少なくとも部分的にメインメモリ904及び/又はプロセッサ902の中にあってもよく、メインメモリ904とプロセッサ902が機械可読記憶媒体にもなる。ソフトウェア922はさらに、ネットワーク920上でネットワークインターフェースデバイス908を介して送受信されてもよい。

#### 【0060】

機械アクセス可能記憶媒体 931 は、例示的実施形態において、1つの媒体として示されているが、「機械可読記憶媒体」という用語は、1つ又は複数の命令セットを記憶させた1つの媒体又は複数の媒体（中央集中型又は分散型データベース、及び／又は関連するキャッシュとサーバ等）を含むと理解するものとする。「機械可読記憶媒体」という用語はまた、機械によって実行される命令セットを記憶又は符号化でき、機械に本発明の方法のいずれか1つ又はそれ以上を実行させる任意の媒体を含むと理解するものとする。「機械可読記憶媒体」という用語はしたがって、例えば、これらに限定されないが、ソリッドステートメモリ、光及び磁気媒体を含むと理解するものとする。

#### 【0061】

本発明の一実施形態によれば、機械アクセス可能記憶媒体には、データ処理システムに複数の集積回路を有する半導体ウェハのダイシング方法を実行させる命令が格納されている。この方法は、半導体ウェハ上にマスクを形成するステップを含み、このマスクは、集積回路を被覆し、保護する層からなる。マスクは次に、マルチパルスバーストを用いるパルス列レーザスクライビング工程によってパターニングされ、ギャップを有するパターニングされたマスクが形成される。半導体ウェハの領域は、集積回路間ににおいて露出する。半導体ウェハは次に、パターニングされたマスクのギャップからエッチングされ、集積回路が個片化される。

#### 【0062】

以上、各ウェハが複数の集積回路を有する半導体ウェハのダイシング方法を説明した。本発明の一実施形態によれば、複数の集積回路を有する半導体ウェハのダイシング方法は、半導体ウェハ上にマスクを形成するステップを含み、このマスクは、集積回路を被覆し、保護する層からなる。この方法はまた、マスクを、マルチパルスバーストを用いるパルス列レーザスクライビング工程によってパターニングするステップを含み、ギャップを有するパターニングされたマスクが形成され、半導体ウェハの集積回路間の領域が露出する。この方法はまた、半導体ウェハを、パターニングされたマスクのギャップからエッチングするステップも含み、これによって集積回路が個片化される。一実施形態において、マルチパルスバーストを用いるパルス列レーザスクライビング工程によってマスクをパターニングするステップは、1バーストあたり2～5パルスのバーストを用いることを含む。一実施形態において、マルチパルスバーストを用いるパルス列レーザスクライビング工程でマスクをパターニングするステップは、フェムト秒レーザを使用することを含む。

10

20

30

【図1】

FIG. 1

【図2B】

FIG. 2B

【図2C】

FIG. 2C

【図2A】

FIG. 2A

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7A】

FIG. 7A

【図7C】

FIG. 7C

【図7B】

FIG. 7B

【図7D】

FIG. 7D

【図8】

【図9】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/304 (2006.01) B 23 K 26/364

B 23 K 26/00 H

H 01 L 21/304 631

(72)発明者 シン サラブジート

アメリカ合衆国 カリフォルニア州 95051 サンタ クララ キーリー ブルバード

1000 ナンバー74

(72)発明者 ヤラマンチリ マダーバ ラオ

アメリカ合衆国 カリフォルニア州 95037 モーガン ヒル アベニーダ デ ロス パ

ドレス 1660

(72)発明者 イートン ブラッド

アメリカ合衆国 カリフォルニア州 94025 メンロ パーク エイス アベニュー 5

63

(72)発明者 クマール エージェイ

アメリカ合衆国 カリフォルニア州 95014 クパチーノ マンザニータ コート 1045

7

審査官 鈴木 和樹

(56)参考文献 特開2006-253402 (JP, A)

国際公開第2010/111089 (WO, A1)

特開2008-193034 (JP, A)

特開2008-226991 (JP, A)

特開2000-223425 (JP, A)

特表2009-544145 (JP, A)

特表2012-522374 (JP, A)

米国特許出願公開第2010/0129984 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 301

B 23 K 26 / 00

B 23 K 26 / 364

H 01 L 21 / 302

H 01 L 21 / 3065

H 01 L 21 / 304