(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-344929

(P2006-344929A)

(43) 公開日 平成18年12月21日(2006.12.21)

(51) Int.C1.

HO1L 27/105 (2006.01)

HO1L 21/8246 (2006.01)

F1

HO1L 27/10 444B

テーマコード(参考)

5FO83

審査請求 未請求 請求項の数 35 O L (全 36 頁)

(21) 出願番号 特願2006-92049 (P2006-92049)

(22) 出願日 平成18年3月29日 (2006.3.29)

(31) 優先権主張番号 10-2005-0048531

(32) 優先日 平成17年6月7日 (2005.6.7)

(33) 優先権主張国 韓国 (KR)

(特許庁注:以下のものは登録商標)

1. F R A M

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞 416

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】強誘電体キャパシタの製造方法及びこれを利用した半導体装置の製造方法

## (57) 【要約】

【課題】向上された特性を有する強誘電体キャパシタ及びこれを利用した半導体装置の製造方法が開示される。

【解決手段】基板上に少なくとも一つの下部電極膜を含む下部電極層を形成した後、下部電極層上に強誘電体層を形成する。強誘電体層上に上部電極層を形成した後、上部電極層上に第1ハードマスク及び第2ハードマスクを具備するハードマスク構造物を形成する。ハードマスク構造物を利用して、上部電極層、強誘電体層、及び下部電極層をエッチングして、基板上に下部電極、強誘電体層パターン、及び上部電極を形成する。強誘電体層パターンのエッチング損傷による強誘電体層パターンの劣化を防止する一方、強誘電体層パターンの有効面積を拡張させて強誘電体キャパシタの電気的及び強誘電的特性を改善することができる。

【選択図】図 11

**【特許請求の範囲】****【請求項 1】**

基板上に少なくとも一つの下部電極膜を含む下部電極層を形成する段階と、

前記下部電極層上に強誘電体層を形成する段階と、

前記強誘電体層上に上部電極層を形成する段階と、

前記上部電極層上に第1ハードマスク及び第2ハードマスクを具備するハードマスク構造物を形成する段階と、

前記ハードマスク構造物をエッティングマスクとして利用して、前記上部電極層、前記強誘電体層、及び前記下部電極層を部分的にエッティングして前記基板上に下部電極、強誘電体層パターン、及び上部電極を形成する段階と、を含む強誘電体キャパシタの製造方法。 10

**【請求項 2】**

前記ハードマスク構造物を形成する段階は、

前記強誘電体層上に第1ハードマスク層を形成する段階と、

前記第1ハードマスク層上に第2ハードマスク層を形成する段階と、

前記第2ハードマスク層及び前記第1ハードマスク層をエッティングして前記上部電極層上に前記第1ハードマスク及び前記第2ハードマスクを形成する段階と、を更に含むことを特徴とする請求項1記載の強誘電体キャパシタの製造方法。

**【請求項 3】**

前記第1ハードマスク層は、前記上部電極層に対してエッティング選択比を有する物質を使用して形成されることを特徴とする請求項2記載の強誘電体キャパシタの製造方法。 20

**【請求項 4】**

前記第2ハードマスク層は、前記第1ハードマスク層、前記上部電極層、及び前記強誘電体層に対してエッティング選択比を有する物質を使用して形成されることを特徴とする請求項2記載の強誘電体キャパシタの製造方法。

**【請求項 5】**

前記上部電極層、前記強誘電体層、及び前記下部電極層を部分的にエッティングする段階は、

前記第2ハードマスクをエッティングマスクとして利用して前記第1ハードマスク層及び前記上部電極層を部分的にエッティングする段階と、

前記第1ハードマスクをエッティングマスクとして利用して、前記強誘電体層及び前記下部電極層を部分的にエッティングする段階と、を更に含むことを特徴とする請求項4記載の強誘電体キャパシタの製造方法。 30

**【請求項 6】**

前記第1ハードマスク層は、ストロンチウムルテニウム酸化物(SRO)、ストロンチウムチタニウム酸化物(STO)、カルシウムルテニウム酸化物(CRO)、シリコン窒化物、及びシリコン酸窒化物からなる群から選択されたいずれか一つを使用して形成されることを特徴とする請求項2記載の強誘電体キャパシタの製造方法。

**【請求項 7】**

前記第1ハードマスク層は、スパッタリング工程、化学気相蒸着工程、原子層積層工程、又は、パルスレーザー蒸着工程を利用して形成されることを特徴とする請求項2記載の強誘電体キャパシタの製造方法。 40

**【請求項 8】**

前記第2ハードマスク層は、シリコン窒化物、シリコン酸化物、ドーピングされないポリシリコン、及びシリコン酸窒化物からなる群から選択されたいずれか一つを使用して形成されることを特徴とする請求項2記載の強誘電体キャパシタの製造方法。

**【請求項 9】**

前記第2ハードマスク層は、化学気相蒸着工程、原子層積層工程、パルスレーザー蒸着工程、又はプラズマ化学気相成長工程を利用して形成されることを特徴とする請求項2記載の強誘電体キャパシタの製造方法。

**【請求項 10】**

前記第1ハードマスクと前記第2ハードマスクの厚さの比は、1：1～1：10であることを特徴とする請求項1記載の強誘電体キャパシタの製造方法。

**【請求項11】**

前記上部電極を形成した後、前記強誘電体層パターンを形成する前に、前記第2ハードマスクを除去する段階を更に含むことを特徴とする請求項12記載の強誘電体キャパシタの製造方法。

**【請求項12】**

前記強誘電体キャパシタの側壁は、前記基板に水平な方向に対して80～90°の角度を有することを特徴とする請求項1記載の強誘電体キャパシタの製造方法。

**【請求項13】**

前記下部電極層を形成する段階は、

前記基板上に第1下部電極膜を形成する段階と、

前記第1下部電極膜上に第2下部電極膜を形成する段階と、を更に含むことを特徴とする請求項1記載の強誘電体キャパシタの製造方法。

**【請求項14】**

前記第1下部電極膜は、チタニウムアルミニウム窒化物、アルミニウム窒化物、チタニウム窒化物、チタニウムシリコン窒化物、タンタル窒化物、及びタンタルシリコン窒化物からなる群から選択されたいずれか一つを使用して形成され、前記第2下部電極膜はイリジウム、白金、ルテニウム、パラジウム、及び金からなる群から選択されたいずれか一つを使用して形成されることを特徴とする請求項13記載の強誘電体キャパシタの製造方法。

。

**【請求項15】**

前記下部電極層を形成する段階は、前記第2下部電極膜上に第3下部電極膜を形成する段階を更に含むことを特徴とする請求項13記載の強誘電体キャパシタの製造方法。

**【請求項16】**

前記第3下部電極膜は、ストロンチウムルテニウム酸化物(SRO)、ストロンチウムチタニウム酸化物(STO)、ランタンニッケル酸化物(LNO)、及びカルシウムルテニウム酸化物(CRO)からなる群から選択されたいずれか一つを使用して形成されることを特徴とする請求項15記載の強誘電体キャパシタの製造方法。

**【請求項17】**

前記下部電極層を形成する前に、

前記基板上に絶縁構造物を形成する段階と、

前記絶縁構造物を貫通するホールを形成する段階と、

前記ホールを部分的に埋め立てるパッドを形成する段階と、を更に含むことを特徴とする請求項1記載の強誘電体キャパシタの製造方法。

**【請求項18】**

前記下部電極層を形成する段階は、

前記パッド上に前記ホールを完全に埋め立てる第1下部電極膜を形成する段階と、

前記第1下部電極膜及び前記絶縁構造物上に第2下部電極膜を形成する段階と、を含むことを特徴とする請求項17記載の強誘電体キャパシタの製造方法。

**【請求項19】**

前記強誘電体層は、PZT[Pb(Zr,Ti)O<sub>3</sub>]、SBT(SrBi<sub>2</sub>Ti<sub>2</sub>O<sub>9</sub>)、BLT[Bi(La,Ti)O<sub>3</sub>]、PLZT[Pb(La,Zr)TiO<sub>3</sub>]、及びBST[Bi(Sr,Ti)O<sub>3</sub>]からなる群から選択されたいずれか一つ、又は、カルシウム(Ca)、ランタン(Ln)、マンガン(Mn)、又はビスマス(Bi)がドーピングされたPZT、SBT、BLT、PLZT、及びBSTからなる群から選択されたいずれか一つを使用して形成されることを特徴とする請求項1記載の強誘電体キャパシタの製造方法。

**【請求項20】**

前記上部電極層は、イリジウム、白金、ルテニウム、白金-マンガン合金、イリジウム

10

- ルテニウム合金、イリジウム酸化物、ストロンチウムルテニウム酸化物（SRO）、ストロンチウムチタニウム酸化物（STO）、ランタンニッケル酸化物（LNO）、及びカルシウムルテニウム酸化物（CRO）からなる群から選択されたいずれか一つを使用して形成されることを特徴とする請求項1記載の強誘電体キャパシタの製造方法。

#### 【請求項21】

前記上部電極層を形成する段階は、

前記強誘電体層上に第1上部電極膜を形成する段階と、

前記第2上部電極膜上に第2上部電極膜を形成する段階と、を更に含むことを特徴とする請求項1記載の強誘電体キャパシタの製造方法。

#### 【請求項22】

前記第1上部電極膜は、ストロンチウムルテニウム酸化物（SRO）、ストロンチウムチタニウム酸化物（STO）、ランタンニッケル酸化物（LNO）、及びカルシウムルテニウム酸化物（CRO）からなる群から選択されたいずれか一つを使用して形成され、前記第2上部電極膜は、イリジウム、白金、ルテニウム、パラジウム、及び金からなる群から選択されたいずれか一つを使用して形成されることを特徴とする請求項21記載の強誘電体キャパシタの製造方法。

#### 【請求項23】

基板上に下部構造物を形成する段階と、

前記下部構造物上に絶縁構造物を形成する段階と、

前記絶縁構造物を貫通して前記下部構造物に接触されるパッドを形成する段階と、

前記パッド及び絶縁構造物上に少なくとも一つの下部電極膜を含む下部電極層を形成する段階と、

前記下部電極層上に強誘電体層を形成する段階と、

前記強誘電体層上に上部電極層を形成する段階と、

前記上部電極層上に第1ハードマスク及び第2ハードマスクを具備するハードマスク構造物を形成する段階と、

前記ハードマスク構造物をエッティングマスクとして利用して、前記上部電極層、前記強誘電体層、及び前記下部電極層を部分的にエッティングして、前記絶縁構造物及びパッド上に下部電極、強誘電体層パターン、並びに上部電極を形成する段階と、を含む半導体装置の製造方法。

#### 【請求項24】

前記ハードマスク構造物を形成する段階は、

前記強誘電体層上に第1ハードマスク層を形成する段階と、

前記第1ハードマスク層上に第2ハードマスク層を形成する段階と、

前記第2ハードマスク層及び前記第1ハードマスク層を部分的にエッティングして前記上部電極層上に前記第1ハードマスク及び前記第2ハードマスクを形成する段階と、を更に含むことを特徴とする請求項23記載の半導体装置の製造方法。

#### 【請求項25】

前記第1ハードマスク層は、前記上部電極層に対してエッティング選択比を有する物質を使用し形成され、前記第2ハードマスク層は、前記第1ハードマスク層、前記上部電極層、及び前記強誘電体層に対してエッティング選択比を有する物質を使用して形成されることを特徴とする請求項24記載の半導体装置の製造方法。

#### 【請求項26】

前記上部電極層、前記強誘電体層、及び前記下部電極層を部分的にエッティングする段階は、

前記第2ハードマスクをエッティングマスクとして利用して前記第1ハードマスク層及び前記上部電極層を部分的にエッティングする段階と、

前記第1ハードマスクをエッティングマスクとして利用して前記強誘電体層及び前記下部電極層を部分的にエッティングする段階と、を更に含むことを特徴とする請求項25記載の半導体装置の製造方法。

10

20

30

40

50

**【請求項 27】**

前記第1ハードマスク層は、ストロンチウムルテニウム酸化物(SRO)、ストロンチウムチタニウム酸化物(STO)、カルシウムルテニウム酸化物(CRO)、シリコン窒化物、及びシリコン酸窒化物からなる群から選択されたいずれか一つを使用して形成され、前記第2ハードマスク層は、シリコン窒化物、シリコン酸化物、ドーピングされないポリシリコン、及びシリコン酸窒化物からなる群から選択されたいずれか一つを使用して形成されることを特徴とする請求項24記載の半導体装置の製造方法。

**【請求項 28】**

前記第1ハードマスク層は、スパッタリング工程、化学気相蒸着工程、原子層積層工程、又は、パルスレーザー蒸着工程を利用して形成され、前記第2ハードマスク層は、化学気相蒸着工程、原子層積層工程、パルスレーザー蒸着工程、又はプラズマ化学気相成長工程を利用して形成されることを特徴とする請求項24記載の半導体装置の製造方法。 10

**【請求項 29】**

前記上部電極を形成した後、前記強誘電体層パターンを形成する前に、前記第2ハードマスクを除去する段階を更に含むことを特徴とする請求項24記載の半導体装置の製造方法。

**【請求項 30】**

前記第1ハードマスクと前記第2ハードマスクの厚さの比は、1:1~1:10であることを特徴とする請求項23記載の半導体装置の製造方法。

**【請求項 31】**

前記下部電極層を形成する段階は、

前記絶縁構造物及び前記パッド上に第1下部電極膜を形成する段階と、

前記第1下部電極膜上に第2下部電極膜を形成する段階と、を更に含むことを特徴とする請求項23記載の半導体装置の製造方法。 20

**【請求項 32】**

前記下部電極層を形成する段階は、前記第2下部電極膜上に第3下部電極膜を形成する段階を更に含むことを特徴とする請求項31記載の半導体装置の製造方法。

**【請求項 33】**

前記パッドを形成する段階は、

前記絶縁構造物に前記下部構造物を露出させるホールを形成する段階と、

前記ホールを満たしながら前記絶縁構造物上に導電層を形成する段階と、

前記導電層を除去して前記ホールを部分的に埋め立てる前記パッドを形成する段階と、を更に含むことを特徴とする請求項23記載の半導体装置の製造方法。 30

**【請求項 34】**

前記下部電極層を形成する段階は、

前記パッド上に前記ホールを完全に埋め立てる第1下部電極膜を形成する段階と、

前記第1下部電極膜及び前記絶縁構造物上に第2下部電極膜を形成する段階と、を含むことを特徴とする請求項33記載の半導体装置の製造方法。

**【請求項 35】**

前記上部電極層を形成する段階は、

前記強誘電体層上に第1上部電極膜を形成する段階と、

前記第2上部電極膜上に第2上部電極膜を形成する段階と、を更に含むことを特徴とする請求項23記載の半導体装置の製造方法。 40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、強誘電体キャバシタの製造方法及びこれを利用した半導体装置の製造方法に係り、より詳細には、有効面積の拡張を通じて向上された強誘電的及び電気的特性を有する強誘電体キャバシタの製造方法及びこれを利用した半導体装置及びその製造方法に関する。 50

## 【背景技術】

## 【0002】

半導体メモリ装置は、電源供給が中断された場合に、保存されたデータを失う揮発性半導体メモリ装置と、電源供給が中断される場合にも保存されたデータを失わない不揮発性半導体メモリ装置とに区分される。前記揮発性半導体メモリ装置としては、DRAM装置やSRAM装置等が挙げられ、前記不揮発性半導体メモリ装置としては、EPROM装置、EEPROM装置、又はフラッシュメモリ装置等が開発されている。

## 【0003】

これに対し、FRAM装置は、読み書きが全部可能な揮発性であるRAM装置の特性と不揮発性であるROM装置の特性を全部有している。前記FRAM装置において、現在の製造技術水準がDRAM装置に達していないので、FRAM装置の動作速度がDRAM装置に対して相対的に劣化するが、FRAM装置は電源供給が中断されても、強誘電体が有している自発分極特性のために、保存された情報を失わないという優れた情報保存特性を有する。又、前記FRAM装置は、EPROM装置やEEPROM装置に対して低い電力で駆動させることができ、情報の入出力回数を顕著に増加させることができるという長所も有する。

## 【0004】

前記FRAM装置の製造のために、開発されている強誘電体は大きく2種類に区分される。その一つは、PZT[Pb(Zr,Ti)O<sub>3</sub>]系列の強誘電体であり、他の一つは、SBT(SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>)系列の強誘電体である。PZT系列の強誘電体の場合には、約650程度の相対的に低い温度で製造することができ、残留分極が大きいという長所が有するが、PZT系列の強誘電体は分極反転を反復する場合に、強誘電体薄膜の疲労現象が深刻になり、有害な鉛(Pb)を含有しているという短所を有する。SBT系列の強誘電体は白金(Platinum)電極を使用して、約1000回以上の分極反転を繰り返しても疲労現象が現れず、分極-電圧履歴曲線(P-V hysteresis)が特定方向に傾く現象がないという長所を有する。しかし、SBT系列の強誘電体は結晶化のために、約800以上の高温で熱処理をしなければならないという短所を有する。

## 【0005】

前記強誘電体を利用して強誘電体キャパシタを製造する方法は、特許文献1、特許文献2、及び特許文献3に開示されている。

【特許文献1】韓国特許出願公開第2001/113271号明細書

【特許文献2】韓国特許出願公開第2001/4306号明細書

【特許文献3】米国特許出願公開第2004/175954号明細書

## 【0006】

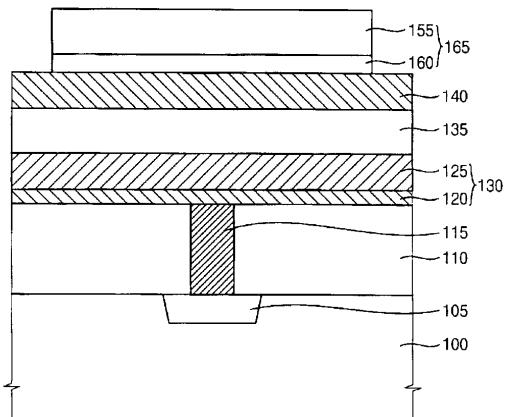

図1乃至図3は、従来の強誘電体キャパシタの製造方法を説明するための断面図である。

## 【0007】

図1を参照すると、半導体基板10上に酸化物を使用して絶縁膜15を形成した後、フォトリソグラフィ工程で絶縁膜15をエッチングして、絶縁膜15に半導体基板10に形成されたコンタクト領域(図示せず)を露出させるホールを形成する。

## 【0008】

前記ホールを埋め立てながら絶縁膜15上に導電層を形成した後、絶縁膜15が露出されるまで、前記導電層を除去して前記ホール内にパッド25を形成する。

## 【0009】

絶縁膜15及びパッド25上に第1下部電極層30及び第2下部電極層35を順次に形成する。ここで、第1下部電極層30は、金属窒化物を使用して形成され、第2下部電極層35は金属を使用して形成される。

## 【0010】

第2下部電極層35上にPZT又はSBTのような強誘電体を使用して強誘電体層40を形成した後、強誘電体層40上に上部電極層45を形成する。上部電極層45は、金属

10

20

30

40

50

酸化物又は金属を使用して形成される。

【0011】

上部電極層45上にハーダマスク層50を形成する。ハーダマスク層50は、窒化物を使用して形成される。従って、第1下部電極層30とハーダマスク層50は全て窒化物を含む。

【0012】

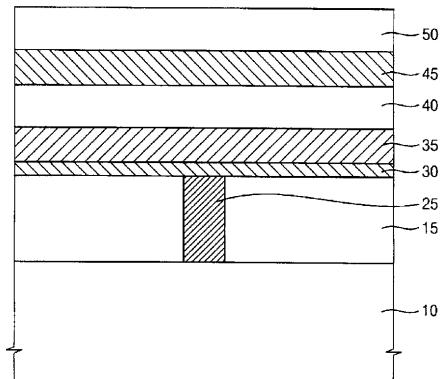

図2を参照すると、ハーダマスク層50上にフォトレジストパターン(図示せず)を形成した後、前記フォトレジストパターンをエッティングマスクとして利用してハーダマスク層50をパターニングすることにより、上部電極層45上にハーダマスク51を形成する。

10

【0013】

ハーダマスク51をエッティングマスクとして利用して、上部電極層45及び強誘電体層40を順次にエッティングすることによって、第2下部電極層35上に強誘電体層パターン60及び上部電極55を形成する。

【0014】

図3を参照すると、ハーダマスク51を継続的にエッティングマスクとして利用して、第2下部電極層35をパターニングすることにより、第1下部電極層30上に第2下部電極層パターン65を形成する。

【0015】

その後、第1下部電極層30をエッティングしながら、同時にハーダマスク51を除去して、絶縁膜15上に強誘電体キャパシタ80を形成する。強誘電体キャパシタ80は、下部電極、強誘電体層パターン60、及び上部電極55を含む。前記下部電極は、絶縁膜15及びパッド25上に順次に形成された第1下部電極層パターン70及び第2下部電極層パターン65を含む。

20

【0016】

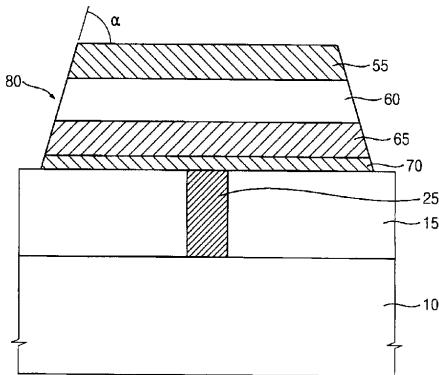

しかし、前述した従来の強誘電体キャパシタの製造方法において、窒化物からなるハーダマスク51を利用して、上部電極層45、強誘電体層40、及び第2下部電極層35をエッティングするので、強誘電体キャパシタ80の実質的に低い側壁傾斜角度( )を有するので、強誘電体キャパシタ80の有効面積が減少される問題点がある。これを添付図面を参照して説明すると、次の通りである。

30

【0017】

図4は、従来の強誘電体キャパシタの断面電子顕微鏡写真を示す図である。

【0018】

図3及び図4を参照すると、窒化物ハーダマスク51を利用して、上部電極55、強誘電体層パターン60、及び第2下部電極層パターン65をエッティングする工程が進行されるにつれて、初期には約80°の側壁傾斜角度を有する上部電極55と強誘電体層パターン60の側壁が漸次崩れながら約60°以下の低い側壁傾斜を有することになる。たとえ、第1下部電極層パターン70が形成されると、強誘電体キャパシタ80の側壁傾斜角度( )は少し増加されるが、上部電極55と強誘電体層パターン60の側壁傾斜角度が低いので、結局、強誘電体キャパシタ80は実質的に68°以上の側壁傾斜角度( )を有するのは難しくなる。特に、高温で強誘電体層40をエッティングする場合には、前記高温エッティング工程の間、窒化物ハーダマスク51が強誘電体層40を十分に保護しないので、強誘電体層パターン60の側壁傾斜角度が大幅に低くなるのみならず、強誘電体層パターン60にエッティング損傷が発生することになる。このように、強誘電体キャパシタ80が低い側壁傾斜角度( )を有する場合、強誘電体層パターン60を含む強誘電体キャパシタ80の有効面積が減少することになる。従って、強誘電体層パターン60に蓄積される電荷も減少されると同時に、強誘電体層パターン80の2Pr値のような分極特性も低下されることにより、結局、強誘電体キャパシタ80のデータセンシングマージンも大幅減少することになる。又、強誘電体層パターン60にエッティング損傷が発生する場合、強誘電体層パターン60から漏洩電流が増加し、強誘電体層パターン60のデータ保存特性

40

が低下される等のように、強誘電体キャパシタ80の強誘電的及び電気的特性も大きく劣化される問題が発生する。

【発明の開示】

【発明が解決しようとする課題】

【0019】

本発明の第1目的は、有効面積の拡張を通じて向上された強誘電的及び電気的特性を有する強誘電体キャパシタの製造方法を提供することにある。

【0020】

本発明の第2目的は、有効面積の拡張を通じて向上された強誘電的及び電気的特性を有する強誘電体キャパシタを具備する半導体装置の製造方法を提供することにある。 10

【課題を解決するための手段】

【0021】

前記した本発明の第1目的を達成するために、本発明の好ましい実施例による強誘電体キャパシタの製造方法において、基板上に少なくとも一つの下部電極膜を含む下部電極層を形成した後、前記下部電極層上に強誘電体層を形成する。前記強誘電体層上に上部電極層を形成した後、前記上部電極層上に第1ハードマスク及び第2ハードマスクを具備するハードマスク構造物を形成する。次いで、前記ハードマスク構造物を利用して、前記上部電極層、前記強誘電体層、及び前記下部電極層をエッチングして、前記基板上に下部電極、強誘電体層パターン、及び上部電極を形成する。前記ハードマスク構造物を形成する段階において、前記強誘電体層上に順次に第1ハードマスク層及び第2ハードマスク層を形成した後、前記第2ハードマスク層及び前記第1ハードマスク層をエッチングして前記上部電極層上に前記第1ハードマスク及び前記第2ハードマスクを形成する。 20

【0022】

前述した本発明の第2目的を達成するために、本発明の好ましい実施例による半導体装置の製造方法において、基板上に下部構造物を形成した後、前記下部構造物上に絶縁構造物を形成する。次いで、前記絶縁構造物を貫通して前記下部構造物に接触されるパッドを形成した後、前記パッド及び絶縁構造物上に少なくとも一つの下部電極膜を含む下部電極層を形成する。継続して、前記下部電極層上に強誘電体層を形成した後、前記強誘電体層上に上部電極層を形成する。次いで、前記上部電極層上に第1ハードマスク及び第2ハードマスクを具備するハードマスク構造物を形成した後、前記ハードマスク構造物を利用して、前記上部電極層、前記強誘電体層、及び前記下部電極層をエッチングして、前記絶縁構造物及びパッド上に下部電極、強誘電体層パターン、及び上部電極を形成する。 30

【0023】

本発明によると、第1及び第2ハードマスクを含むハードマスク構造物を利用して、上部電極、強誘電体層パターン、及び下部電極を形成することにより、高い側壁傾斜角度によって拡張された有効面積を有する強誘電体キャパシタを形成することができる。従って、このような強誘電体層パターンを含む強誘電体キャパシタのデータセンシングマージンをより大きく確保することができ、データ保存力又は分極保存力等のような強誘電的特性が改善された強誘電体キャパシタを形成することができる。又、前記ハードマスク構造物を利用して強誘電体層パターンのエッチング損傷による劣化を最小化することができるので、強誘電体層パターンから漏洩電流が発生することを防止することができるので、強誘電体キャパシタの電気的特性を向上させることができる。又、前記強誘電体キャパシタを具備するFRAM装置のような半導体装置の信頼性を充分に確保することができる。 40

【発明を実施するための最良の形態】

【0024】

以下、本発明による好ましい実施例による強誘電体キャパシタの製造方法及びこれを利用した半導体装置の製造方法を添付図面を参照して詳細に説明する。添付図面において、基板、層(膜)、領域、パッド、パターン、又は構造物の寸法は、本発明の明確性のために、実際より拡大して示した。又、添付図面において、実質的に同じであるか、類似な部材には、同じであるか、類似な参照符号を付与する。本発明において、各層(膜)、領域 50

、パッド、パターン、又は構造物が基板、各層（膜）、領域、パッド、又はパターンの「上に」、「上部に」、又は「下部」に形成されると言及される場合には、各層（膜）、領域、パッド、パターン、又は構造物が直接基板、各層（膜）、領域、パッド、又はパターン上に形成されるか、下に位置することを意味するか、他の層（膜）、他の領域、他のパッド、他のパターン、又は他の構造物が基板上に追加的に形成されることがある。又、各層（膜）、領域、パッド、パターン、構造物、又は電極が「第1」、「第2」、及び／又は「第3」として言及される場合、このような部材を限定するためのものではないが、但し、各層（膜）、領域、パッド、構造物、又は電極を区分するためのものである。従つて、「第1」、「第2」、及び／又は「第3」は、各層（膜）、領域、パッド、パターン、構造物、又は電極に対してそれぞれ選択的に又は交換的に使用されることがある。

10

### 強誘電体キャパシタの製造方法

#### 【0025】

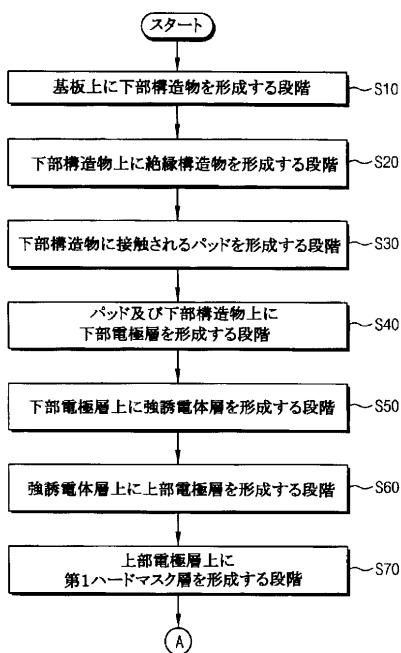

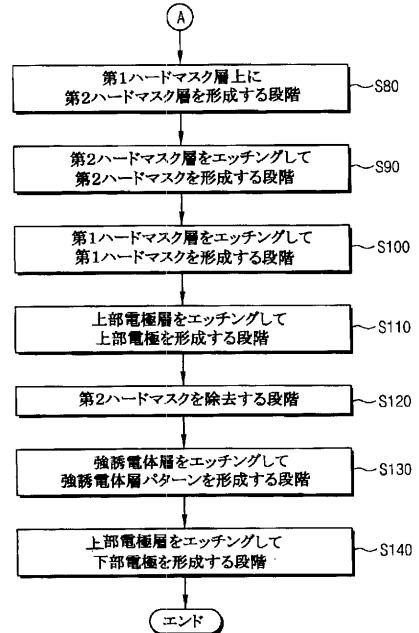

図5及び図6は、本発明の一実施例による強誘電体キャパシタの製造方法を説明するための工程順序図を示す図であり、図7乃至図13は、本発明の一実施例による強誘電体キャパシタの製造方法を説明するための断面図を示す図である。

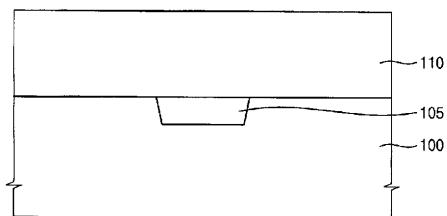

#### 【0026】

図5及び図7を参照すると、基板100上に下部構造物105を形成する（段階S10）。基板100は、シリコンウェーハ乃至SOI（Silicon On Insulator）基板のような半導体基板又は金属酸化物単結晶基板を含む。例えば、基板100は、アルミニウム酸化物（Al<sub>2</sub>O<sub>3</sub>）単結晶基板、ストロンチウムチタニウム酸化物（SrTiO<sub>3</sub>）単結晶基板又はマグネシウム酸化物（MgO）単結晶基板等を含む。下部構造物105は、基板100に形成されたコンタクト領域、パッド、プラグ、導電性配線、導電性パターン、ゲート構造物、又はトランジスタ等を具備する。

20

#### 【0027】

下部構造物105をカバーしながら、基板100上に絶縁構造物110を形成する（段階S20）。絶縁構造物110は、下部電極190（図13参照）と下部構造物105を電気的に絶縁させる。絶縁構造物110は、少なくとも一つの絶縁膜又は層間絶縁膜を具備する。絶縁構造物110は、酸化物、窒化物、及び／又は酸窒化物を使用して形成される。例えば、絶縁構造物110は、BPSG（Boro-Phosphor Silicate Glass）、PSG（Phosphor Silicate Glass）、USG（Undoped Silicate Glass）、SOG（Spin On Glass）、FOX（Flowable Oxide）、PE-TEOS（Plasma Enhanced-Tetra Ethyl Ortho Silicate）、HDP-CVD（High Density Plasma-Chemical Vapour Deposition）酸化物、シリコン窒化物、又はシリコン酸窒化物等を使用して形成される。ここで、絶縁構造物110は、化学気相蒸着（CVD）工程、プラズマ化学気相成長工程（PECVD）、原子層積層（ALD）工程、又は高密度プラズマ化学気相蒸着（HDP-CVD）工程を利用して形成される。

30

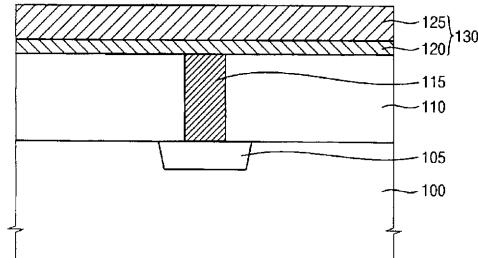

#### 【0028】

図5及び図8を参照すると、絶縁構造物110を部分的にエッティングして、下部構造物105を露出させるホール（図示せず）を形成した後、前記ホールを満たしながら、絶縁構造物110上に導電層を形成する。前記導電層は、不純物でドーピングされたポリシリコン、金属、又は導電性金属窒化物を使用して形成される。例えば、前記導電層は、タンゲステン（W）、アルミニウム（Al）、銅（Cu）、チタニウム（Ti）、タンゲステン窒化物（WN）、アルミニウム窒化物（AlN）、又はチタニウム窒化物（TiN）等を使用して形成される。前記導電層は、スパッタリング工程、化学気相蒸着（CVD）工程、原子層積層（ALD）工程、又はパルスレーザー蒸着（PLD）工程を利用して形成される。

40

#### 【0029】

絶縁構造物110が露出されるまで、前記導電層を部分的に除去して、前記ホールを埋

50

め立てるパッド 115 を形成する（段階 S30）。前記導電層は、エッチバック工程、化学機械的研磨（CMP）工程、又は化学機械的研磨（CMP）とエッチバックを組合せた工程を利用して部分的にエッチングされる。

#### 【0030】

パッド 115 及び絶縁構造物 110 上に下部電極層 130 を形成する（段階 S40）。下部電極層 130 は、パッド 115 及び絶縁構造物 110 上に順次に形成された第1下部電極膜 120 及び第2下部電極膜 125 を含む。第1下部電極膜 120 は、絶縁構造物 110 の上面から約 50 ~ 300 程度の厚さに形成される。又、第2下部電極膜 125 は、第1下部電極膜 120 の上面から約 300 ~ 1200 程度の厚さに形成される。

#### 【0031】

より具体的に、第1下部電極膜 120 は、パッド 115 及び絶縁構造物 110 上に導電性金属窒化物を化学気相蒸着（CVD）工程、原子層積層（ALD）工程、スパッタリング工程、又はパルスレーザー蒸着（PLD）工程で蒸着して形成される。例えば、第1下部電極膜 120 は、チタニウムアルミニウム窒化物（TiAlN）、アルミニウム窒化物、チタニウム窒化物、チタニウムシリコン窒化物（TiSiN）、タンタル窒化物（Ta<sub>N</sub>）、タンタルシリコン窒化物（TaSiN）、又はタンゲステン窒化物等を使用して形成される。好ましくは、第1下部電極膜 120 は、パッド 115 及び絶縁構造物 110 上にチタニウムアルミニウム窒化物を原子層積層工程で蒸着して形成される。

#### 【0032】

第2下部電極膜 125 は、金属をスパッタリング工程、パルスレーザー蒸着（PLD）工程、化学気相蒸着（CVD）工程、又は原子層積層（ALD）工程で第1下部電極膜 120 上に蒸着して形成される。例えば、第2下部電極膜 125 は、イリジウム（Ir）、白金（Pt）、ルテニウム（Ru）、パラジウム（Pd）、又は金（Au）等を使用して形成される。好ましくは、第2下部電極膜 125 は、第1下部電極膜 120 上にイリジウムをスパッタリング工程で蒸着して形成される。第2下部電極膜 125 を形成する段階において、基板 100 が収容された反応チャンバーは、約 20 ~ 350 程度の温度及び約 3 ~ 10 mTorr 程度の圧力で維持される。この際、第2下部電極膜 125 は、不活性ガス雰囲気下で約 300 ~ 1000 W 程度の電力を印加して形成される。例えば、前記不活性ガスは、アルゴンガス、窒素ガス、ヘリウムガス、又はこれらが混合されたガスを含む。

#### 【0033】

本発明の他の実施例によると、絶縁構造物 110 と第1下部電極膜 120 との間の接着力を向上させるために、絶縁構造物 110 と第1下部電極膜 120 との間に接着膜（図示せず）を更に形成することができる。前記接着膜は、絶縁構造物 110 及びパッド 215 上に金属又は導電性金属窒化物をスパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程で蒸着して形成される。例えば、前記接着膜は、チタニウム、タンタル、アルミニウム、タンゲステン、チタニウム窒化物、タンタル窒化物、アルミニウム窒化物、又はタンゲステン窒化物を使用して形成される。

#### 【0034】

図 5 及び図 9 を参照すると、第2下部電極膜 125 上に強誘電体層 135 を形成する（段階 S50）。強誘電体層 135 は、第2下部電極膜 125 の上面から約 200 ~ 1200 程度の厚さに形成される。強誘電体層 135 は、有機金属化学気相蒸着（MOCVD）工程、ゾル・ゲル工程、原子層積層工程、又は化学気相蒸着工程を利用して形成される。

#### 【0035】

本発明の一実施例によると、強誘電体層 135 は、PZT [ Pb(Zr, Ti)O<sub>3</sub> ]、SBT (SrBi<sub>2</sub>Ti<sub>2</sub>O<sub>9</sub>)、BLT [ Bi(La, Ti)O<sub>3</sub> ]、PLZT [ Pb(La, Zr)TiO<sub>3</sub> ]、及び BST [ Bi(Sr, Ti)O<sub>3</sub> ] 等の強誘電体を使用して形成される。本発明の他の実施例によると、強誘電体層 135 は、カルシウム、ランタン、マンガン、乃至ビスマス等の金属がドーピングされた PZT、SBT、BLT、

10

20

30

40

50

P L Z T、又はB S T等の強誘電体を使用して形成される。本発明の更に他の実施例によると、強誘電体層135は、チタニウム酸化物( $TiO_x$ )、タンタル酸化物( $TaO_x$ )、アルミニウム酸化物( $AlO_x$ )、亜鉛酸化物( $ZnO_x$ )、又はハフニウム酸化物( $HfO_x$ )等の金属酸化物を使用して形成される。好ましくは、強誘電体層135は、第2下部電極膜125上にP Z Tを有機金属化学気相蒸着工程で蒸着して形成される。前記有機金属化学気相蒸着工程で第2下部電極膜125上に強誘電体層135を形成する段階において、基板100が収容された反応チャンバーは、約350～650程度の温度及び約1～10 Torr程度の圧力に維持される。又、強誘電体層135は、前記反応チャンバー内に有機金属前駆体及び酸化剤を供給した後、前記有機金属前駆体と酸化剤を反応させて第2下部電極膜125上に形成される。この場合、前記有機金属前駆体は、鉛又は鉛を含む第1化合物、ジルコニウム、又はジルコニウムを含む第2化合物、そしてチタニウム又はチタニウムを含む第3化合物からなる。又、前記酸化剤は、酸素( $O_2$ )、オゾン( $O_3$ )、二酸化窒素( $NO_2$ )、酸化二窒素( $N_2O$ )等を含む。

10

### 【0036】

強誘電体層135上には、上部電極層140が形成される(段階S60)。上部電極層140は、強誘電体層135上に金属酸化物又は金属をスパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程で蒸着して形成される。例えば、上部電極層140は、イリジウム、白金、ルテニウム、パラジウム、金、白金-マンガン合金、イリジウム-ルテニウム合金、イリジウム酸化物( $IrO_x$ )、ストロンチウムルテニウム酸化物( $SrRuO_3 : SRO$ )、ストロンチウムチタニウム酸化物( $STO$ )、ランタンニッケル酸化物( $LaNiO_3 : LNO$ )、又はカルシウムルテニウム酸化物( $CaRuO_3 : CRO$ )等を使用して形成される。上部電極層140は、強誘電体層135の上面から約100～1200程度の厚さに形成される。上部電極層140を形成する段階において、基板100が収容された反応チャンバーは約20～350程度の温度及び約3～10 mTorr程度の圧力に維持される。ここで、上部電極層140は不活性ガス雰囲気下で約300～1000W程度の電力を印加することによって形成される。

20

### 【0037】

本発明の他の実施例によると、強誘電体層135上に上部電極層140を形成した後、強誘電体層135及び上部電極層140を酸素ガス、窒素ガス、又はこれらの混合ガス雰囲気下で急速熱処理工程(Rapid Thermal Process: RTP)で熱処理することにより、上部電極層140及び強誘電体層135を構成する物質を結晶化させる。この場合、前記急速熱処理工程は、約500～650程度の温度で約30秒～3分間行われる。

30

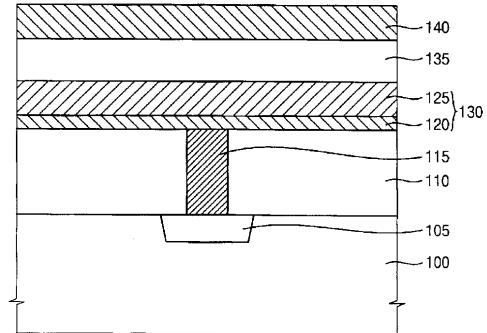

### 【0038】

図5及び図10を参照すると、上部電極層140上に第1ハードマスク層145を形成する(段階S70)。第1ハードマスク層145は、上部電極層140の上面から約100～300程度の厚さに形成される。第1ハードマスク層145は、上部電極層140、強誘電体層135、及び下部電極層130に対してエッチング選択比を有する物質を使用して形成される。例えば、第1ハードマスク層145は、ストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、カルシウムルテニウム酸化物、シリコン窒化物、又はシリコン酸窒化物を使用して形成される。好ましくは、第1ハードマスク層145は、ストロンチウムルテニウム酸化物を使用して形成される。又、第1ハードマスク層145は、スパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程を利用して形成される。

40

### 【0039】

本発明の一実施例において、上部電極層140がストロンチウムルテニウム酸化物からなる場合、第1ハードマスク層145は、シリコン窒化物、シリコン酸窒化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、又はカルシウムルテニウム酸化物を使用して形成される。本発明の他の実施例によると、上部電極層140がイリジウム、白金、ルテニウム、パラジウム、金、白金-マンガン合金、イリジウム-ルテニウム合金、

50

又はイリジウム酸化物からなる場合、第1ハーデマスク層145は、ストロンチウムルテニウム酸化物を使用して形成される。

#### 【0040】

図6及び図10を参照すると、第1ハーデマスク層145上には、第2ハーデマスク層150が形成される(段階S80)。第2ハーデマスク層150は、第1ハーデマスク層145の上面から約300~1000程度の厚さに形成される。これによって、第1ハーデマスク層145と第2ハーデマスク層150の厚さの比は、約1:1~1:10程度になる。第2ハーデマスク層150は、化学気相蒸着工程、プラズマ化学気相成長工程、パルスレーザー蒸着工程、又は原子層積層工程を利用して形成される。第2ハーデマスク層150は、第1ハーデマスク層145、上部電極層140、及び強誘電体層135に対してエッティング選択比を有する物質を使用して形成される。例えば、第2ハーデマスク層150は、ドーピングされないポリシリコン、シリコン酸化物、シリコン窒化物のような窒化物、又はシリコン酸窒化物のような酸窒化物を使用して形成される。好ましくは、第2ハーデマスク層150は、シリコン窒化物を使用して形成される。

#### 【0041】

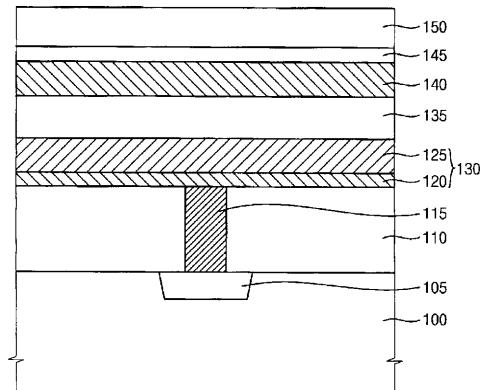

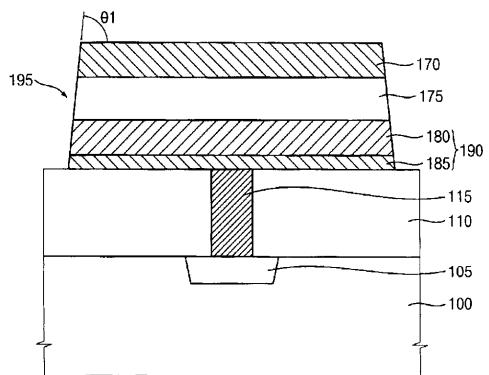

図6及び図11を参照すると、第2ハーデマスク層150上にフォトレジストパターン(図示せず)を形成した後、前記フォトレジストパターンをエッティングマスクとして利用して、第2ハーデマスク層150を部分的にエッティングすることにより、第1ハーデマスク層145上に第2ハーデマスク155を形成する(段階S90)。

#### 【0042】

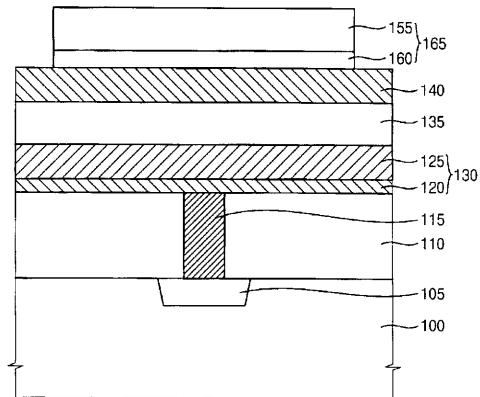

前記フォトレジストパターンをアッシング工程及び/又はストリッピング工程を利用して除去した後、第2ハーデマスク155をエッティングマスクとして利用して、第1ハーデマスク層145を部分的にエッティングすることにより、上部電極層140上に第1ハーデマスク160を形成する(段階S100)。これによって、上部電極層140上には、第1ハーデマスク160及び第2ハーデマスク155を具備するハーデマスク構造物165が形成される。ここで、スピンスクラッピング工程(spin scrubbing process)を利用して、前記エッティング工程を通じて形成された第2ハーデマスク160の表面を改善することができる。

#### 【0043】

本発明の他の実施例によると、前記フォトレジストパターンをエッティングマスクとして利用して、第2ハーデマスク層150及び第1ハーデマスク層140を連続的にパターニングすることにより、上部電極170上にハーデマスク構造物165を形成することができる。

#### 【0044】

図6及び図12を参照すると、ハーデマスク構造物165をエッティングマスクとして利用して上部電極層140を部分的にエッティングすることによって、強誘電体層135上に上部電極170を形成する(段階S110)。この場合、上部電極170は、下部の面積より若干狭い上部面積を有するように形成される。即ち、上部電極170の側壁は、実質的に約80~90°の傾斜角度を有する。第2及び第1ハーデマスク155、160を含むハーデマスク構造物165をエッティングマスクとして利用して、上部電極層140をパターニングするエッティング工程の間、第2ハーデマスク155もある程度消耗されるので、第2ハーデマスク155の厚さが薄くなる。

#### 【0045】

強誘電体層135上に上部電極170を形成した後、第2ハーデマスク155を第1ハーデマスク160から除去する(段階S120)。これによって、上部電極170の上には、第1ハーデマスク160のみが残留することになる。本発明の他の実施例によると、スピンスクラッピング工程を利用して、第2ハーデマスク155の除去によって露出された第1ハーデマスク160の表面状態を改善することができる。

#### 【0046】

図6及び図13を参照すると、第1ハーデマスク160をエッティングマスクとして利用

10

20

30

40

50

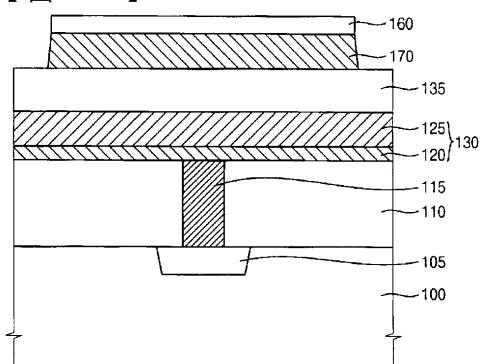

して、強誘電体層 135 をエッティングして第 2 下部電極膜 125 上に強誘電体層パターン 175 を形成する（段階 S130）。強誘電体層 135 を低温でエッティングする場合には、強誘電体層パターン 175 が低い側壁傾斜角度を有することになる。これによって、強誘電体キャパシタ 195 が要求される高い側壁傾斜角度を有するために、強誘電体層 135 を高温でエッティングして強誘電体層パターン 175 を形成する。例えば、強誘電体層 135 は、約 200 ~ 400 ° 程度の温度でエッティングされる。

#### 【0047】

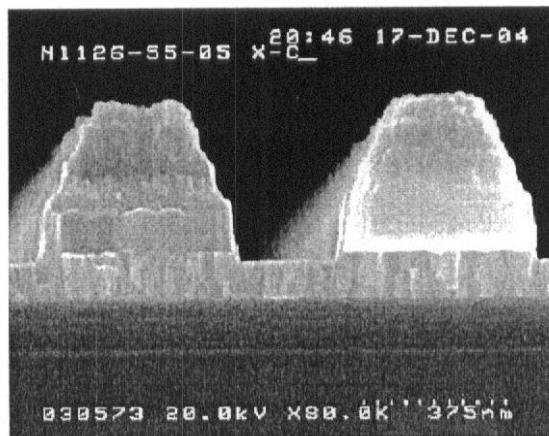

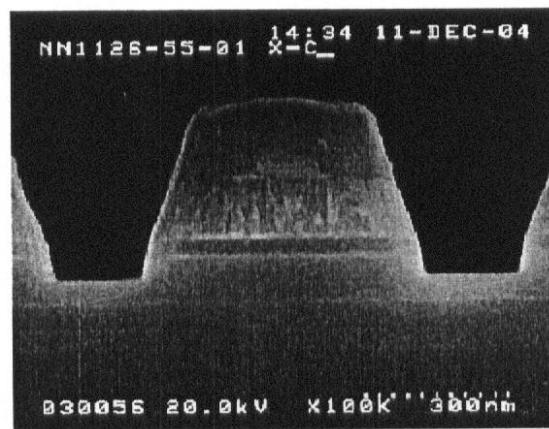

図 14 は、本発明の一実施例によって強誘電体層パターン 175 を形成した状態を示す断面電子顕微鏡写真である。

#### 【0048】

図 14 に示すように、第 1 ハードマスク 160 を利用して強誘電体層 135 をパターニングすることにより得られる強誘電体層パターン 175 は、約 80 ~ 90 ° 程度の高い側壁傾斜角度を有する。又、前述したように、高温で強誘電体層 135 をエッティングするエッティング工程の間、第 1 ハードマスク 160 が上部電極 170 を効果的に保護するので、上部電極 170 の側壁も実質的に約 80 ~ 90 ° 程度の高い側壁傾斜角度をそのまま維持する。

#### 【0049】

継続して、第 1 ハードマスク 160 をエッティングマスクとして利用するエッティング工程を通じて第 2 下部電極膜 125、及び第 1 下部電極膜 120 を順次にパターニングすることによって、絶縁構造物 110 上に下部電極 190 を形成する（段階 S140）。

#### 【0050】

上部電極 170 から第 1 ハードマスク 160 を除去して、基板 100 の上部に下部電極 190、強誘電体層パターン 175、及び上部電極 170 を具備する強誘電体キャパシタ 195 を形成する。下部電極 190 は、絶縁構造物 110 及びパッド 115 上に形成された第 1 下部電極膜パターン 185 と第 1 下部電極膜パターン 185 上に形成された第 2 下部電極膜パターン 180 を含む。第 1 下部電極膜パターン 185 は、強誘電体層パターン 175 から酸素が拡散されることを防止し、第 2 下部電極膜パターン 180 は強誘電体層パターン 175 を構成する強誘電体の結晶性を向上させる役割を果たす。又、第 1 下部電極膜パターン 185 は、絶縁構造物 110 上に前記接着膜が形成されない場合、絶縁構造物 110 と第 2 下部電極膜パターン 180 との間の接着力を向上させる機能も果たす。

#### 【0051】

本発明の他の実施例によると、第 2 ハードマスク 155 を除去することなく、第 2 ハードマスク 155 及び第 1 ハードマスク 160 を共にエッティングマスクとして利用して、強誘電体層パターン 175 及び下部電極 190 を形成することができる。ここで、強誘電体層 135、第 2 下部電極膜 125、及び第 1 下部電極膜 120 を部分的にエッティングする間、第 2 ハードマスク 155 は実質的に殆ど消耗されるので、強誘電体キャパシタ 195 を形成した後、第 2 ハードマスク 155 を除去するための別の工程を必要としない。

#### 【0052】

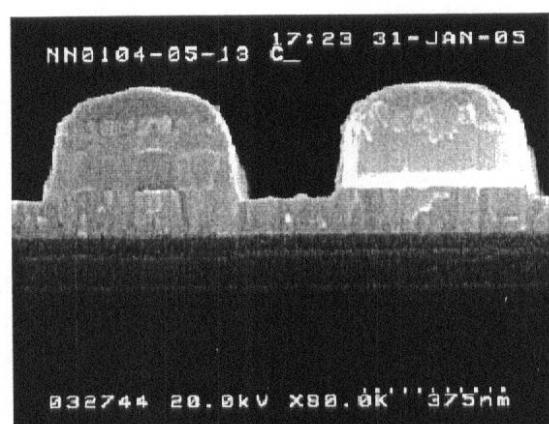

図 15 は、本発明の一実施例によって製造された強誘電体キャパシタの断面電子顕微鏡写真を示す図である。

#### 【0053】

図 13 及び図 15 に示すように、第 1 及び第 2 ハードマスク 160、155 を具備するハードマスク構造物 165 を利用して形成された強誘電体キャパシタ 195 は、基板 100 に平行な方向に対して約 80 ~ 90 ° 程度の高い側壁傾斜角度（1）を有する。即ち、上部電極 170、強誘電体層パターン 175、及び下部電極 190 を形成する比較的長時間のエッティングの間、第 2 及び第 1 ハードマスク 155、160 が上部電極 170 及び強誘電体層パターン 175 を効果的に保護するので、上部電極 170 と強誘電体層パターン 175 のそれぞれ約 80 ~ 90 ° 程度の高い側壁傾斜角度を維持する。これによって、強誘電体キャパシタ 195 も約 80 ~ 90 ° 程度の高い側壁傾斜角度（1）を有し、結局、強誘電体キャパシタ 195 の有効面積を拡張させることができる。強誘電体層パター

10

20

30

40

50

ン 175 が高い側壁傾斜を有する場合には、強誘電体層パターン 175 に蓄積される電荷量を増加させることができるので、強誘電体層パターン 175 の  $2Pr$  値が向上される。このように、強誘電体層パターン 175 の分極特性が向上されると、強誘電体キャパシタ 195 のデータ保存力乃至分極保存力 (polarization retention) が向上され、結局、強誘電体キャパシタ 195 は大きく増加された電気的及び強誘電的特性を有することになる。又、第 1 ハードマスク 160 が強誘電体層パターン 175 のエッチング損傷を効果的に防止することができるので、強誘電体層パターン 175 から漏洩電流が発生されることを遮断することができると同時に、強誘電体層パターン 175 の劣化を最小化することができる。従って、このような強誘電体層パターン 175 を含む強誘電体キャパシタ 195 の電気的特性をより向上させることができる。

10

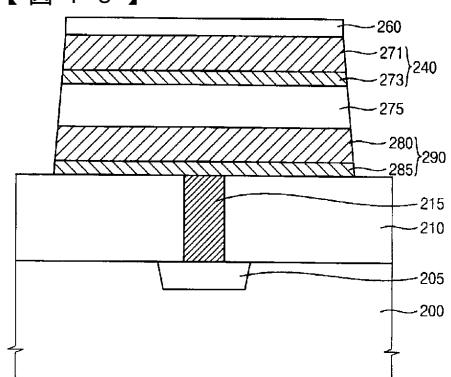

## 【0054】

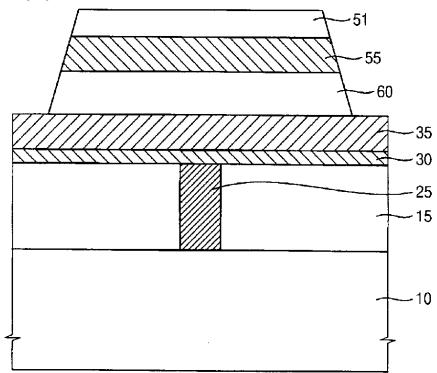

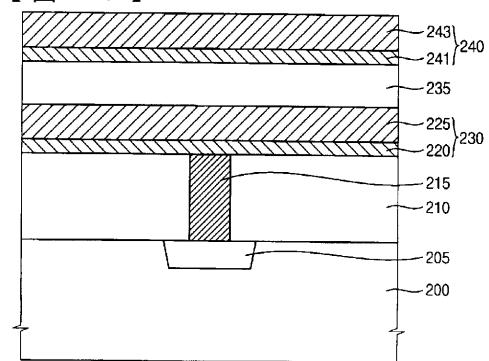

図 16 乃至図 19 は、本発明の他の実施例による強誘電体キャパシタの製造方法を説明するための断面図を示す。

## 【0055】

図 16 を参照すると、基板 200 上にコンタクト領域、パッド、プラグ、導電性配線、導電性パターン、ゲート構造物、又はトランジスタ等を含む下部構造物 205 を形成する。基板 200 は、シリコンウェーハ乃至 SOI 基板のような半導体基板又は金属酸化物単結晶基板を含む。

## 【0056】

下部構造物 205 をカバーしながら、基板 200 上に少なくとも一つの絶縁膜又は層間絶縁膜を含む絶縁構造物 210 を形成する。絶縁構造物 210 は、下部電極 290 (図 18 参照) と下部構造物 205 を電気的に絶縁させる。

20

## 【0057】

絶縁構造物 210 を部分的にエッチングして、下部構造物 205 を露出させるホール ( 図示せず ) を形成した後、前記ホールを満たしながら絶縁構造物 210 上に導電層を形成する。

## 【0058】

絶縁構造物 210 が露出されるまで前記導電層を部分的に除去して、前記ホールを埋め立てるパッド 215 を形成する。パッド 215 は、エッチバック工程、化学機械的研磨工程、又は化学機械的研磨とエッチバックを組合せた工程を利用して形成される。

30

## 【0059】

パッド 215 及び絶縁構造物 210 上に第 1 下部電極膜 220 及び第 2 下部電極膜 225 を順次に形成して、下部電極層 230 を完成する。第 1 下部電極膜 220 は、絶縁構造物 210 の上面から約 50 ~ 300 程度の厚さに形成され、第 2 下部電極膜 225 は、第 1 下部電極膜 220 の上面から約 300 ~ 1200 程度の厚さに形成される。第 1 下部電極膜 220 は、導電性金属窒化物を使用して形成され、第 2 下部電極膜 225 は金属を使用して形成される。

## 【0060】

前述したように、絶縁構造物 210 と第 1 下部電極膜 220 との間の接着力を向上させるために、絶縁構造物 210 と第 1 下部電極膜 220 との間に金属又は導電性金属窒化物からなる接着膜 ( 図示せず ) が更に形成されることができる。

40

## 【0061】

第 2 下部電極膜 225 上に有機金属化学気相蒸着工程、ゾル - ゲル工程、原子層積層工程、又は化学気相蒸着工程を利用して強誘電体層 235 を形成する。強誘電体層 235 は、第 2 下部電極膜 225 の上面から約 200 ~ 1200 程度の厚さに形成される。強誘電体層 135 は、強誘電体、金属がドーピングされた強誘電体又は金属酸化物を使用して形成される。

## 【0062】

強誘電体層 235 上に上部電極層 240 を形成する。上部電極層 240 は、強誘電体層 235 上に順次に形成された第 1 上部電極膜 241 及び第 2 上部電極膜 243 を含む。

50

## 【0063】

第1上部電極膜241は、強誘電体層235の上面から約10～300程度の厚さに形成される。第1上部電極膜241は、金属がドーピングされた金属酸化物を強誘電体層235上にスパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程で蒸着して形成される。例えば、第1上部電極膜241は、銅、鉛、ビスマス等の金属がドーピングされたストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、又はカルシウムルテニウム酸化物等を使用して形成される。好ましくは、第1上部電極膜241は、銅又は鉛がドーピングされたストロンチウムルテニウム酸化物を強誘電体層235上にスパッタリング工程で蒸着して形成する。第1上部電極膜241を形成する間、基板200が位置する反応チャンバーは約20～350程度の温度、及び約3～10mTorr程度の圧力に維持される。又、第1上部電極膜240は不活性ガス雰囲気下で約300～1000W程度の電力を印加することによって形成される。10

## 【0064】

第2上部電極膜243は、第1上部電極膜241の上面から約300～1000程度の厚さに形成される。第2上部電極膜243は、第1上部電極膜241上に金属、合金、又は金属酸化物をスパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程で蒸着して形成する。例えば、第2上部電極膜243は、イリジウム、白金、ルテニウム、パラジウム、金、白金-マンガン合金、イリジウム-ルテニウム合金、又はイリジウム酸化物等を使用して形成される。第2上部電極膜243を形成する間、基板200が収容された反応チャンバーは約20～350程度の温度、及び約3～10mTorr程度の圧力で維持される。この場合、第2上部電極膜243は、不活性ガス雰囲気下で約300～1000W程度の電力を印加することによって形成される。20

## 【0065】

強誘電体層235上に第1及び第2上部電極膜241、243を含む上部電極層240を形成した後、強誘電体層235及び上部電極層240を酸素ガス、窒素ガス、又はこれらの混合ガス雰囲気下で急速熱処理工程(RTP)で熱処理することにより、上部電極層240及び強誘電体層235を構成する物質を結晶化させる。30

## 【0066】

図17を参照すると、第2上部電極膜243上に第1ハードマスク層及び第2ハードマスク層を順次に形成する。前記第1ハードマスク層は、第2上部電極膜243の上面から約100～300程度の厚さに形成され、前記第2ハードマスク層は、前記第1ハードマスク層の上面から約300～1000程度の厚さに形成される。前記第1ハードマスク層は、スパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程を利用して形成され、前記第2ハードマスク層は、化学気相蒸着工程、プラズマ化学気相成長工程、パルスレーザー蒸着工程、又は原子層積層工程を利用して形成される。40

## 【0067】

前記第2ハードマスク層上にフォトレジストパターンを形成した後、前記フォトレジストパターンをエッチングマスクとして利用して、前記第2ハードマスク層及び前記第1ハードマスク層をパターニングすることにより、第2上部電極膜243上にハードマスク構造物265を形成する。ハードマスク構造物265は、上部電極層240上に順次に形成された第1ハードマスク260及び第2ハードマスク255を含む。50

## 【0068】

第1ハードマスク260は、第1及び第2上部電極膜241、243、強誘電体層235、そして第1及び第2下部電極膜220、225に対して高いエッチング選択比を有する物質からなる。例えば、第1ハードマスク260は、ストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、カルシウムルテニウム酸化物、シリコン窒化物、又はシリコン酸窒化物からなる。好ましくは、第1ハードマスク260は、ストロンチウムルテニウム酸化物からなる。第2ハードマスク255は、第1

ハードマスク 260、第1及び第2上部電極膜 241、243、及び強誘電体層 235に對してエッティング選択比を有する物質を使用して形成される。例えば、第2ハードマスク 255は、ドーピングされないポリシリコン、シリコン酸化物、シリコン窒化物のような窒化物、又はシリコン酸窒化物のような酸窒化物からなる。好ましくは、第2ハードマスク 255は、シリコン窒化物からなる。

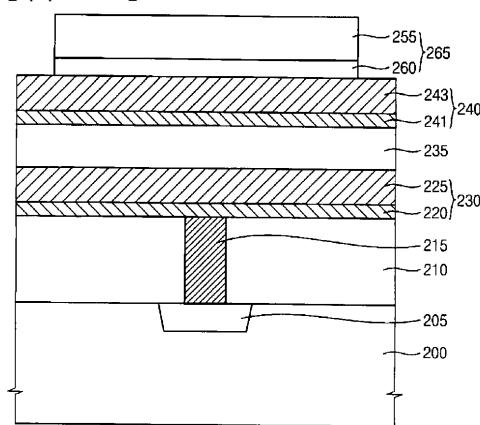

#### 【0069】

図18を参照すると、前記フォトレジストパターンをアッシング工程及び/又はストリッピング工程を利用して除去した後、ハードマスク構造物 265をエッティングマスクとして利用して、第2及び第1上部電極膜 243、241を順次にエッティングすることにより、強誘電体層 235上に上部電極 270を形成する。上部電極 270は、強誘電体層 235上に順次に形成された第1上部電極膜パターン 273、及び第2上部電極膜パターン 271を具備する。第1及び第2上部電極膜パターン 273、271は、それぞれ下部が上部に對して若干広い面積を有するように形成される。これによって、第1及び第2上部電極膜パターン 273、271を含む上部電極 270の側壁は、約80~90°程度の傾斜角度を有する。

#### 【0070】

上部電極 270を形成した後、第2ハードマスク 255を第1ハードマスク 260から除去して、第2上部電極膜パターン 271上に第1ハードマスク 260のみを残留させる。

#### 【0071】

第1ハードマスク 260をエッティングマスクとして利用して高温で強誘電体層 235をエッティングすることにより、第2下部電極膜 225上に強誘電体層パターン 275を形成する。強誘電体層 235をエッティングする高温エッティング工程の間、第1ハードマスク 260が強誘電体層パターン 275を効果的に保護するので、強誘電体層パターン 275は約80~90°程度の高い側壁傾斜角度を有する。

#### 【0072】

第1ハードマスク 260を継続エッティングマスクとして利用するエッティング工程を通じて第2下部電極膜 225及び第1下部電極膜 220を順次にエッティングすることにより、絶縁構造物 210上に下部電極 290を形成する。下部電極 290は、絶縁構造物 210及びパッド 215上に順次に形成された第1下部電極膜パターン 285及び第2下部電極膜パターン 280を含む。ここで、第2及び第1下部電極膜パターン 280、285は、それぞれ下部が上部に對して若干広い面積を有するように形成される。第1ハードマスク 260を利用して下部電極 290を形成するので、下部電極 290の側壁は約80~90°程度の高い傾斜角度を有する。

#### 【0073】

図19を参照すると、上部電極 270から第1ハードマスク 260を除去して、基板 200の上部に下部電極 290、強誘電体層パターン 275、及び上部電極 270を含む強誘電体キャパシタ 295を形成する。強誘電体層 135、第2下部電極膜 225、及び第1下部電極膜 220に對して高いエッティング選択比を有する物質からなる第1ハードマスク 260を使用して強誘電体キャパシタ 295を形成するので、強誘電体キャパシタ 295の側壁は約80~90°程度の高い傾斜角度(2)を有する。

#### 【0074】

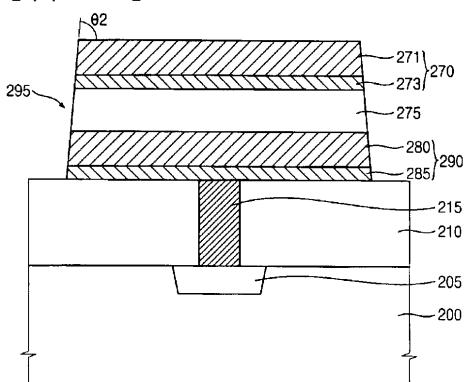

図20乃至図22は、本発明の更に他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

#### 【0075】

図20を参照すると、基板 300上にコンタクト領域、導電性配線、導電性パターン、パッド、プラグ、又はトランジスタ等を含む下部構造物 305を形成する。

#### 【0076】

下部構造物 305をカバーしながら、基板 300上にPSG、USG、SOG、FOX、PE-TEOS、又はHDP-CVD酸化物等を使用して絶縁構造物 310を形成する

10

20

30

40

50

。絶縁構造物310は、化学気相蒸着工程、プラズマ化学気相成長工程、又は高密度プラズマ化学気相蒸着工程で形成される。

#### 【0077】

絶縁構造物310上に第1フォトレジストパターン(図示せず)を形成した後、前記第1フォトレジストパターンをエッチングマスクとして利用して、絶縁構造物310を部分的にエッチングすることによって、絶縁構造物310に下部構造物305を露出させるホールを形成する。

#### 【0078】

スパッタリング工程、化学気相蒸着工程、又は原子層積層工程を利用して前記ホールを満たしながら、絶縁構造物310上にタンゲステン、アルミニウム、銅、又はチタニウム等のような金属や、タンゲステン窒化物、アルミニウム窒化物、又はチタニウム窒化物等のような導電性金属窒化物を使用して導電層を形成する。

#### 【0079】

化学機械的研磨工程、エッチバック工程、又は化学機械的研磨とエッチバックを組合せた工程を利用して、絶縁構造物310が露出されるまで前記導電層を除去することによって、前記ホールを埋め立て露出された下部構造物310に接触されるパッド315を形成する。

#### 【0080】

絶縁構造物310及びパッド315上に約50～300程度の厚さに第1下部電極膜320を形成する。第1下部電極膜320は、金属窒化物を化学気相蒸着工程、スパッタリング工程、又は原子層積層工程で蒸着して形成される。

#### 【0081】

第1下部電極膜310上に約300～1000程度の厚さに第2下部電極膜325を形成する。第2下部電極膜325は、イリジウム、白金、ルテニウム、パラジウム、又は金等の金属をスパッタリング工程、パルスレーザー蒸着工程、又は原子層積層工程で形成する。

#### 【0082】

第2下部電極膜325上に約10～500程度の厚さに第3下部電極膜327を形成して、絶縁構造物310及びパッド315上に下部電極層330を形成する。第3下部電極膜327は、銅、鉛、又はヒ素等の金属がドーピングされたストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、又はカルシウムルテニウム酸化物等のような金属酸化物を使用して形成する。第3下部電極膜327を形成する段階において、基板300が収容された反応チャンバーは約20～350程度の温度、及び約3～10mTorr程度の圧力に維持される。第3下部電極膜327は、アルゴンガス、窒素ガス、又はヘリウムガスを含む不活性ガス雰囲気下で約300～1000W程度の電力を印加することにより形成される。

#### 【0083】

有機金属化学気相蒸着工程、ゾル・ゲル工程、又は原子層積層工程を利用して、第3下部電極膜327上に約200～1000程度の厚さに強誘電体層335を形成する。強誘電体層335は、強誘電性物質やカルシウム、ランタン、マンガン、又はビスマス等の金属がドーピングされた強誘電性物質乃至金属酸化物を使用して形成される。

#### 【0084】

スパッタリング工程、パルスレーザー蒸着工程、又は原子層積層工程を利用して、強誘電体層335上に約10～300程度の厚さに第1上部電極膜341を形成する。第1上部電極膜341は、銅、鉛、又はビスマスのような金属がドーピングされたストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、又はカルシウムルテニウム酸化物等の金属酸化物を使用して形成される。

#### 【0085】

第1上部電極膜341上にイリジウム、白金、ルテニウム、パラジウム、又は金等の金属を使用して第2上部電極膜343を形成する。これによって、強誘電体層335上には

10

20

30

40

50

、第1及び第2上部電極膜341、343を含む上部電極層340が形成される。第2上部電極膜333は、スパッタリング工程、パルスレーザー蒸着工程、又は原子層積層工程を利用して、第1上部電極膜341の上面から約300～1000程度の厚さに形成される。

#### 【0086】

第2上部電極膜343を形成した後、強誘電体層335及び上部電極層340を酸素ガス、窒素ガス、又はこれらの混合ガス雰囲気下で急速熱処理工程で熱処理して、上部電極層340及び強誘電体層335を構成する物質を結晶化させる。

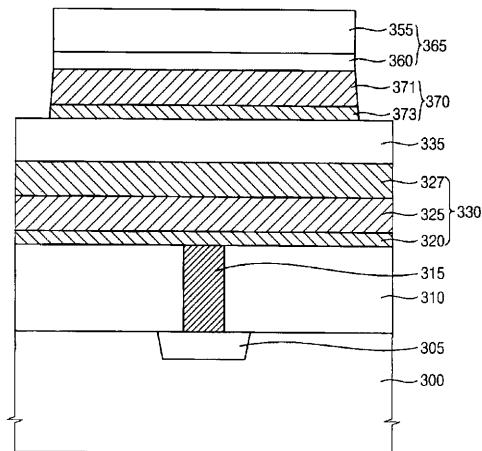

#### 【0087】

図21を参照すると、第2上部電極膜343上に第1ハードマスク層及び第2ハードマスク層を順次に形成する。前記第1ハードマスク層は、第2上部電極膜343の上面から約100～300程度の厚さに形成され、前記第2ハードマスク層は、前記第1ハードマスク層の上面から約300～1000程度の厚さに形成される。前記第1ハードマスク層は、スパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程を利用して形成され、前記第2ハードマスク層は、化学気相蒸着工程、プラズマ化学気相成長工程、パルスレーザー蒸着工程、又は原子層積層工程を利用して形成される。

#### 【0088】

前記第2ハードマスク層上に第2フォトレジストパターンを形成した後、前記第2フォトレジストパターンをエッチングマスクとして利用して、前記第2ハードマスク層及び前記第1ハードマスク層をエッチングすることにより、第2上部電極膜343上にハードマスク構造物365を形成する。ハードマスク構造物365は、上部電極層340上に順次に形成された第1ハードマスク360及び第2ハードマスク355を含む。

#### 【0089】

第1ハードマスク360は、第1及び第2上部電極膜341、343、強誘電体層335、そして第1乃至第3下部電極膜320、325、327に対して高いエッチング選択比を有する物質からなる。例えば、第1ハードマスク360は、ストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、カルシウムルテニウム酸化物、シリコン窒化物、又はシリコン酸窒化物からなる。第2ハードマスク355は、第1ハードマスク360、第1及び第2上部電極膜341、243、及び強誘電体層335に対してエッチング選択比を有する物質を使用して形成される。例えば、第2ハードマスク355はドーピングされないポリシリコン、シリコン酸化物、シリコン窒化物のような窒化物、又はシリコン酸窒化物のような酸窒化物からなる。

#### 【0090】

前記第2フォトレジストパターンをアッシング工程及び／又はストリッピング工程を利用して除去した後、ハードマスク構造物365をエッチングマスクとして利用して、第2及び第1上部電極膜343、341を順次にパターニングすることにより、強誘電体層335上に上部電極370を形成する。上部電極370は、強誘電体層335上に順次に形成された第1上部電極膜パターン373及び第2上部電極膜パターン371を具備する。これによって、第1及び第2上部電極膜パターン373、371を含む上部電極370の側壁は約80～90°程度の傾斜角度を有する。

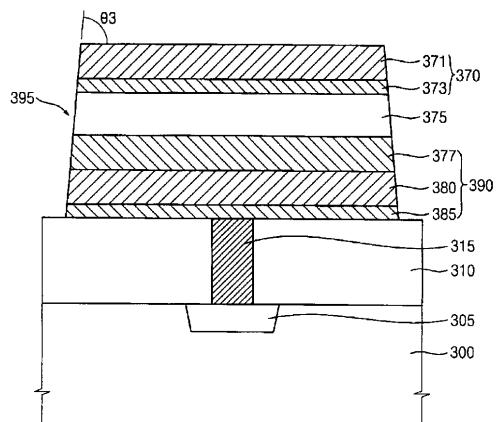

#### 【0091】

図22を参照すると、上部電極370を形成した後、第2ハードマスク355を第1ハードマスク360から除去して、第2上部電極膜パターン371上に第1ハードマスク360のみを残留させる。

#### 【0092】

第1ハードマスク360をエッチングマスクとして利用して、高温で強誘電体層335をエッチングすることにより、第3下部電極膜327上に強誘電体層パターン375を形成する。強誘電体層335をエッチングする高温エッチング工程の間、第1ハードマスク360が強誘電体層パターン375を効果的に保護するので、強誘電体層パターン375

10

20

30

40

50

は約80～90°程度の高い側壁傾斜角度を有する。

#### 【0093】

第1ハードマスク360を継続エッティングマスクとして利用するエッティング工程を通じて第3下部電極膜327、第2下部電極膜325、及び第1下部電極膜320を順次にパターニングすることにより、絶縁構造物310及びパッド315上に下部電極390を形成する。下部電極390は、絶縁構造物310及びパッド315上に順次に形成された第1下部電極膜パターン385、第2下部電極膜パターン380、及び第3下部電極膜パターン377を含む。第3乃至第1下部電極膜パターン377、380、385は、それぞれ下部が上部に対して若干広い面積を有するように形成される。第1ハードマスク360を利用して下部電極390を形成するので、下部電極390の側壁も約80～90°程度の高い傾斜角度を有する。

10

#### 【0094】

上部電極370から第1ハードマスク360を除去して、基板300の上部に下部電極390、強誘電体層パターン375、及び上部電極370を含む強誘電体キャパシタ395を形成する。強誘電体層335、第3下部電極膜327、第2下部電極膜325、及び第1下部電極膜320に対して高いエッティング選択比を有する物質からなる第1ハードマスク360を使用して強誘電体キャパシタ395を形成するので、強誘電体キャパシタ395の側壁も全体的に約80～90°程度の高い傾斜角度(3)を有する。

#### 【0095】

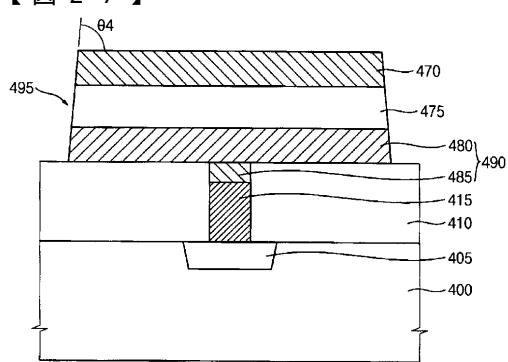

図23乃至図27は、本発明の更に他の実施例による強誘電体キャパシタの製造方法を説明するための断面図を示す。

20

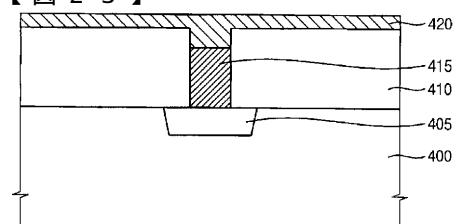

#### 【0096】

図23を参照すると、基板400上に下部構造物405を形成する。基板400は、シリコンウェーハ乃至SOI基板のような半導体基板又は金属酸化物単結晶基板を含む。例えば、基板400は、アルミニウム酸化物単結晶基板、ストロンチウムチタニウム酸化物単結晶基板、又はマグネシウム酸化物単結晶基板等を含む。下部構造物405は、基板400に形成されたコンタクト領域、パッド、プラグ、導電性配線、導電性パッド、ゲート構造物、又はトランジスタ等を具備する。

#### 【0097】

下部構造物405をカバーしながら、基板400上に絶縁構造物410を形成する。絶縁構造物410は、下部電極490(図27参照)と下部構造物405を電気的に絶縁させる。絶縁構造物410は、それぞれ酸化物、窒化物、及び/又は酸窒化物からなる少なくとも一つの絶縁膜又は層間絶縁膜を具備する。例えば、絶縁構造物410は、BPSG、PSG、USG、SOG、FOX、PE-TEOS、HDP-CVD酸化物、シリコン窒化物、又はシリコン酸窒化物等を使用して形成される。絶縁構造物410は、化学気相蒸着工程、プラズマ化学気相成長工程、原子層積層工程、又は高密度プラズマ化学気相蒸着工程を利用して形成される。

30

#### 【0098】

絶縁構造物410を部分的にエッティングして、下部構造物405を露出させるホール(図示せず)を形成した後、前記ホールを満たしながら、絶縁構造物410上に導電層を形成する。前記導電層は、不純物でドーピングされたポリシリコン、金属、又は導電性金属窒化物を使用して形成される。例えば、前記導電層は、タンゲステン、アルミニウム、銅、チタニウム、タンゲステン窒化物、アルミニウム窒化物、又はチタニウム窒化物等を使用して形成される。前記導電層は、スパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程を利用して形成される。

40

#### 【0099】

絶縁構造物410が露出されるまで、前記導電層を部分的に除去して前記ホールを埋め立てるパッド415を形成する。ここで、前記導電層は、エッチバッブ工程、化学機械的研磨工程、又は化学機械的研磨とエッチバッブを組合せた工程を利用して部分的にエッティングされる。前記ホールを埋め立てるパッド415の上部をエッティングして、パッド41

50

5が前記ホールを部分的に満たすようにする。即ち、前記ホールの上部側壁が露出されるようにパッド415を部分的に除去する。

#### 【0100】

本発明の他の実施例によると、前記導電層を部分的に除去する工程をより長時間進行して、前記ホールを部分的に埋め立てるパッド415を形成することができる。

#### 【0101】

前記ホールを完全に満たしながら、パッド415及び絶縁構造物420上に第1下部電極膜420を形成する。第1下部電極膜420は、導電性金属窒化物を化学気相蒸着工程、原子層積層工程、スパッタリング工程、又はパルスレーザー蒸着工程で蒸着して形成される。例えば、第1下部電極膜420は、チタニウムアルミニウム窒化物、アルミニウム窒化物、チタニウム窒化物、チタニウムシリコン窒化物、タンタル窒化物、タンタルシリコン窒化物、又はタンゲステン窒化物等を使用して形成される。好ましくは、第1下部電極膜420は、パッド415及び絶縁構造物410上にチタニウムアルミニウム窒化物を原子層積層工程で蒸着して形成される。10

#### 【0102】

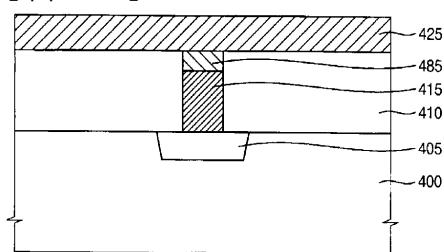

図24を参照すると、化学機械的研磨工程、エッチバック工程、又は化学機械的研磨とエッチバックを組合せた工程を利用して絶縁構造物410が露出されるまで、第1下部電極膜420を部分的に除去して、パッド415上に前記ホールを完全に埋め立てる第1下部電極膜パターン485を形成する。即ち、前記ホールは、パッド415及び第1下部電極膜パターン485によって完全に満たされる。又、第1下部電極膜パターン485は、パッド415上にのみ位置することになる。20

#### 【0103】

絶縁構造物410及び第1下部電極膜パターン485上に第2下部電極膜425を形成する。第2下部電極膜425は、第1下部電極膜パターン485又は絶縁構造物410の上面から約300～1200程度の厚さに形成される。第2下部電極膜425は、イリジウム、白金、ルテニウム、パラジウム、又は金等の金属をスパッタリング工程、パルスレーザー蒸着工程、化学気相蒸着工程、又は原子層積層工程で第1下部電極膜パターン485及び絶縁構造物410上に蒸着して形成される。好ましくは、第2下部電極膜425は、イリジウムをスパッタリング工程で蒸着して形成される。第2下部電極膜425を形成する段階において、基板400が収容された反応チャンバーは、約20～350程度の温度及び約3～10mTorr程度の圧力に維持される。この場合、第2下部電極膜425は、アルゴンガス、窒素ガス、ヘリウムガス、又はこれらが混合されたガスを含む不活性ガス雰囲気下で約300～1000W程度の電力を印加して形成される。30

#### 【0104】

図25を参照すると、第2下部電極膜425上に有機金属化学気相蒸着工程、ゾル・ゲル工程、原子層積層工程、又は化学気相蒸着工程を利用して、強誘電体層435を形成する。強誘電体層135は、第2下部電極膜125の上面から約200～1200程度の厚さに形成される。強誘電体層435は、PZT、SBT、BLT、PLZT、又はBST等の強誘電体を使用して形成される。又、強誘電体層435は、カルシウム、ランタン、マンガン、乃至ビスマスがドーピングされたPZT、SBT、BLT、PLZT、又はBSTを使用して形成される。又、強誘電体層435は、チタニウム酸化物、タンタル酸化物、アルミニウム酸化物、亜鉛酸化物、又はハフニウム酸化物等を使用して形成される。好ましくは、強誘電体層435は、第2下部電極膜425上にPZTを有機金属化学気相蒸着工程で蒸着して形成される。前記強誘電体層435を形成する段階において、基板400が収容された反応チャンバーは約350～650程度の温度及び約1～10Torr程度の圧力に維持される。40

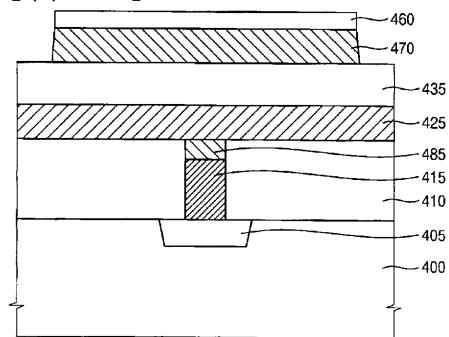

#### 【0105】

強誘電体層435上にスパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程を利用して上部電極層440を形成する。上部電極層440は、イリジウム、白金、ルテニウム、パラジウム、金、白金・マンガン合金、イリジウム・ル

10

20

30

40

50

テニウム合金、イリジウム酸化物、ストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、又はカルシウムルテニウム酸化物等を使用して形成される。上部電極層440は、強誘電体層435の上面から約100～1200程度の厚さに形成される。上部電極層440を形成する段階において、基板400が収容された反応チャンバーは、約20～350程度の温度及び約3～10mTorr程度の圧力に維持される。この場合、上部電極層440は、不活性ガス雰囲気下で約300～1000W程度の電力を印加することにより形成される。

#### 【0106】

強誘電体層435上に上部電極層440を形成した後、強誘電体層435及び上部電極層440を酸素ガス、窒素ガス、又はこれらの混合ガス雰囲気下で急速熱処理工程で熱処理して、上部電極層440及び強誘電体層435を構成する物質を結晶化させる。前記急速熱処理工程は、約500～650程度の温度で約30秒～3分間進行される。

#### 【0107】

上部電極層440上に第1ハードマスク層及び第2ハードマスク層を順次に形成する。前記第1ハードマスク層は、上部電極層440の上面から約100～300程度の厚さに形成される。前記第1ハードマスク層は、上部電極層440、強誘電体層435、及び第2下部電極膜425に対して高いエッチング選択比を有する物質を使用して形成される。例えば、前記第1ハードマスク層は、ストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、カルシウムルテニウム酸化物、シリコン窒化物、又はシリコン酸窒化物を使用して形成される。好ましくは、前記第1ハードマスク層は、ストロンチウムルテニウム酸化物を使用して形成される。又、前記第1ハードマスク層は、スパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程を利用して形成される。上部電極層440がストロンチウムルテニウム酸化物からなる場合、前記第1ハードマスク層は、シリコン窒化物、シリコン酸窒化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、又はカルシウムルテニウム酸化物を使用して形成される。上部電極層440がイリジウム、白金、ルテニウム、パラジウム、金、白金-マンガン合金、イリジウム-ルテニウム合金、又はイリジウム酸化物からなる場合、前記第1ハードマスク層は、ストロンチウムルテニウム酸化物を使用して形成される。

#### 【0108】

前記第2ハードマスク層は、前記第1ハードマスク層の上面から約300～1000程度の厚さに形成される。即ち、前記第1ハードマスク層に対する前記第2ハードマスク層の厚さの比は、約1：1～1：10程度になる。前記第2ハードマスク層は、化学気相蒸着工程、プラズマ化学気相成長工程、パルスレーザー蒸着工程、又は原子層積層工程を利用して形成される。前記第2ハードマスク層は、前記第1ハードマスク層、上部電極層440、及び強誘電体層435に対してエッチング選択比を有する物質を使用して形成される。例えば、前記第2ハードマスク層はドーピングされないポリシリコン、シリコン酸化物、シリコン窒化物のような窒化物、又はシリコン酸窒化物のような酸窒化物を使用して形成される。好ましくは、前記第2ハードマスク層は、シリコン窒化物を使用して形成される。

#### 【0109】

前記第2ハードマスク層上にフォトレジストパターン（図示せず）を形成した後、前記フォトレジストパターンをエッチングマスクとして利用して、前記第2ハードマスク層を部分的にエッチングすることにより、前記第1ハードマスク層上に第2ハードマスク455を形成する。

#### 【0110】

前記フォトレジストパターンをアッティング工程及び/又はストリッピング工程を利用して除去した後、第2ハードマスク455をエッチングマスクとして利用して前記第1ハードマスク層を部分的にエッチングすることにより、上部電極層440上に第1ハードマスク460を形成する。従って、上部電極層440上には、第1ハードマスク460及び第

10

20

30

40

50

2 ハードマスク 455 を含むハードマスク構造物 465 が形成される。この場合、スピニスクラッピング工程を利用して前記エッチング工程を通じて形成された第 2 ハードマスク 460 の表面を改善することができる。一方、前記フォトレジストパターンをエッチングマスクとして利用して、前記第 2 ハードマスク層及び前記第 1 ハードマスク層を連続的にエッチングすることによって、上部電極層 440 上にハードマスク構造物 665 を形成することもできる。

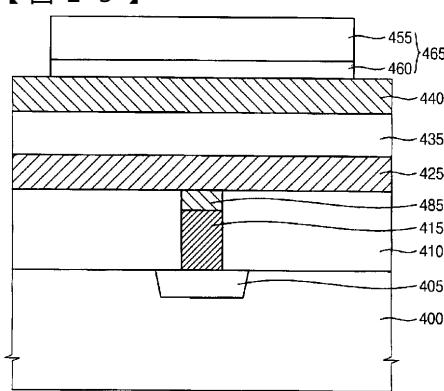

#### 【 0111】

図 26 を参照すると、ハードマスク構造物 465 をエッチングマスクとして利用して上部電極層 440 をパターニングすることにより、強誘電体層 435 上に上部電極 470 を形成する。上部電極 470 は、実質的に約 80 ~ 90° の側壁傾斜角度を有する。第 2 及び第 1 ハードマスク 455、460 を含むハードマスク構造物 465 をエッチングマスクとして利用して上部電極層 440 をエッチングするエッチング工程の間、第 2 ハードマスク 455 もある程度消耗されるので、第 2 ハードマスク 455 の厚さが薄くなる。

#### 【 0112】

第 2 ハードマスク 455 を第 1 ハードマスク 460 から除去して、上部電極 470 上に第 1 ハードマスク 460 のみを残留させる。この場合、スピニスクラッピング工程を利用して、第 2 ハードマスク 455 の除去によって露出された第 1 ハードマスク 460 の表面状態を改善することができる。

#### 【 0113】

図 27 を参照すると、第 1 ハードマスク 460 をエッチングマスクとして利用して強誘電体層 435 をエッチングすることによって、第 2 下部電極膜 425 上に強誘電体層パターン 475 を形成する。ここで、強誘電体層 435 を低温でエッチングする場合には、強誘電体層パターン 175 が低い側壁傾斜角度を有するので、強誘電体層 435 を約 200 ~ 400° 程度の高温でエッチングして強誘電体層パターン 475 を形成する。第 1 ハードマスク 460 を利用して強誘電体層 435 をエッチングすることによって得られる強誘電体層パターン 475 は、約 80 ~ 90° 程度の高い側壁傾斜角度を有する。又、高温で強誘電体層 435 をエッチングするエッチング工程の間、第 1 ハードマスク 460 が上部電極 470 を効果的に保護するので、上部電極 470 の側壁も実質的に約 80 ~ 90° 程度の高い側壁傾斜角度を維持する。

#### 【 0114】

第 1 ハードマスク 460 を継続的にエッチングマスクとして利用するエッチング工程を通じて第 2 下部電極膜 425 をエッチングすることにより、絶縁構造物 410 及び第 1 下部電極膜パターン 485 上に第 2 下部電極膜パターン 480 を形成する。これによって、第 1 下部電極膜パターン 485 及び第 2 下部電極膜パターン 480 を具備する下部電極 490 が形成される。

#### 【 0115】

上部電極 470 から第 1 ハードマスク 460 を除去すると、基板 400 の上部には下部電極 490、強誘電体層パターン 475、及び上部電極 470 を具備する強誘電体キャパシタ 495 が完成される。第 1 及び第 2 ハードマスク 460、455 を含むハードマスク構造物 465 を利用して形成された強誘電体キャパシタ 495 は、基板 400 に平行な方向に対して約 80 ~ 90° 程度の高い側壁傾斜角度 (-3°) を有する。上部電極 470、強誘電体層パターン 475、及び下部電極 490 を形成する比較的長時間のエッチングの間、第 2 及び第 1 ハードマスク 455、460 が上部電極 470 及び強誘電体層パターン 475 を効果的に保護するので、上部電極 470 と強誘電体層パターン 475 がそれぞれ約 80 ~ 90° 程度の高い側壁傾斜角度を維持する。これによって、強誘電体キャパシタ 495 も約 80 ~ 90° 程度の高い側壁傾斜角度 (-3°) を有し、結局、強誘電体キャパシタ 195 の有効面積を拡張させることができる。又、第 1 ハードマスク 460 が強誘電体層パターン 475 のエッチング損傷を効果的に防止することができるので、強誘電体層パターン 475 から漏洩電流が発生されることを遮断できると同時に、強誘電体層パターン 475 の劣化を最小化することができる。

10

20

30

40

50

半導体装置の製造方法

## 【0116】

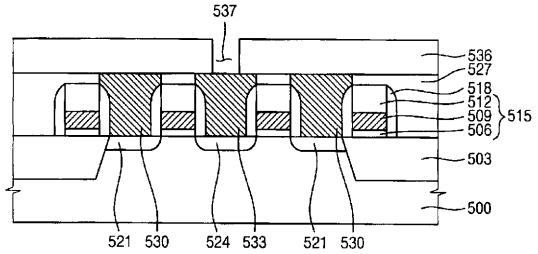

図28乃至図32は、本発明の一実施例による半導体装置の製造方法を説明するための断面図を示す。

## 【0117】

図28を参照すると、シャロートレンチ素子分離工程のような素子分離工程を利用して半導体基板500上に素子分離膜503を形成することにより、半導体基板500にアクティブ領域及びフィールド領域を画定する。熱酸化法や化学気相蒸着工程で素子分離膜503が形成された半導体基板500上に薄い厚さのゲート酸化膜を形成する。

## 【0118】

前記ゲート酸化膜上に第1導電層及び第1マスク層を順次に形成する。前記第1導電層は、不純物でドーピングされたポリシリコンで形成され、前記第1マスク層は、後続して形成される第1層間絶縁膜527に対してエッティング選択比を有する物質を使用して形成される。例えば、第1層間絶縁膜527が酸化物からなる場合に、前記第1マスク層はシリコン窒化物のような窒化物からなる。

## 【0119】

前記第1マスク層上に第1フォトレジストパターン(図示せず)を形成した後、前記第1フォトレジストパターンをエッティングマスクとして利用して前記第1マスク層、第1導電層、及びゲート酸化膜を順次にパターニングすることにより、半導体基板500上にそれぞれゲート酸化膜パターン506、ゲート導電層パターン509、及びゲートマスクパターン512を含むゲート構造物515を形成する。

## 【0120】

本発明の他の実施例によると、前記第1フォトレジストパターンをエッティングマスクとして利用して前記第1マスク層をパターニングすることにより、前記第1導電層上にゲートマスクパターン512をまず形成する。その後、アッシング工程及び/又はストリッピング工程でゲートマスクパターン512上の第1フォトレジストパターンを除去した後、ゲートマスクパターン512をエッティングマスクとして利用して、前記第1導電層及びゲート酸化膜を順次にパターニングすることにより、半導体基板500上にそれぞれゲート酸化膜パターン506、ゲート導電層パターン509、及びゲートマスクパターン512を含むゲート構造物515を形成することができる。

## 【0121】

前記ゲート構造物515が形成された半導体基板500上にシリコン窒化物のような窒化物からなる第1絶縁膜を形成した後、前記第1絶縁膜を異方性エッティングして、各ゲート構造物515の側面にゲートスペーサ518を形成する。

## 【0122】

図28を更に参照すると、ゲートスペーサ518が形成されたゲート構造物515をイオン注入マスクとして利用して、ゲート構造物515の間に露出される半導体基板500にイオン注入工程で不純物を注入した後、熱処理工程を行って半導体基板500にソース/ドレイン領域に該当される第1コンタクト領域521及び第2コンタクト領域524を形成する。ここで、第1及び第2コンタクト領域521、524は、強誘電体キャパシタ580(図32参照)のための第1パッド530とビットラインのための第2パッド533がそれぞれ接触されるキャパシタコンタクト領域及びビットラインコンタクト領域に区分される。例えば、第1コンタクト領域521は、第1パッド530が接触されるキャパシタコンタクト領域に該当され、第2コンタクト領域524は、第2パッド533が接続されるビットラインコンタクト領域に該当される。これによって、半導体基板500上にはそれぞれゲート構造物515、ゲートスペーサ518、及びコンタクト領域521、524を含むトランジスタが形成される。

## 【0123】

本発明の他の実施例によると、各ゲート構造物515の側壁にゲートスペーサ518を形成する前に、ゲート構造物515の間に露出される半導体基板500に低い濃度の不純

10

20

30

40

50

物を1次的にイオン注入する。その後、ゲート構造物515の側壁にゲートスペーサ518を形成した後、前記1次イオン注入された半導体基板500に高い濃度の不純物を2次的にイオン注入して、LDD(Lightly Doped Drain)構造を有する第1及び第2コンタクト領域521、524を形成することができる。

## 【0124】

前記ゲート構造物515をカバーしながら半導体基板500上に酸化物からなる第1層間絶縁膜527を形成する。第1層間絶縁膜527は、BPSG、PSG、SOG、PE-TEOS、USG、又はHDP-CVD酸化物を化学気相蒸着工程、プラズマ化学気相成長工程、高密度プラズマ化学気相蒸着工程、又は原子層積層工程を利用して形成する。

## 【0125】

化学機械的研磨工程、エッチバック工程、又は化学機械的研磨とエッチバックを組合せた工程を利用して第1層間絶縁膜527の上部を除去することにより、第1層間絶縁膜527の上面を平坦化させる。ここで、第1層間絶縁膜527は、ゲートマスクパターン518の上面から所定の高さを有するように形成される。一方、ゲートマスクパターン518の上面が露出されるまで、第1層間絶縁膜527をエッティングして第1層間絶縁膜527の上面を平坦化することができる。

## 【0126】

第1層間絶縁膜527上に第2フォトレジストパターン(図示せず)を形成した後、前記第2フォトレジストパターンをエッティングマスクとして利用して、第1層間絶縁膜527を部分的にエッティングすることにより、第1層間絶縁膜527に半導体基板500に形成された第1及び第2コンタクト領域521、524を露出させる第1コンタクトホール(図示せず)を形成する。好ましくは、酸化物からなる第1層間絶縁膜527をエッティングする時、窒化物からなるゲートマスクパターン518に対して高いエッティング選択比を有するエッティングガスを使用して第1層間絶縁膜527をエッティングする。従って、前記第1コンタクトホールは、ゲート構造物515に対して自己整列されながら、第1及び第2コンタクト領域521、524を露出させる。前記第1コンタクトホールのうち、一部はキャパシタコンタクト領域である第1コンタクト領域521を露出させ、前記第1コンタクトホールのうち、他の部分はピットラインコンタクト領域である第2コンタクト領域524を露出させる。

## 【0127】

前記第2フォトレジストパターンをアッシング及び/又はストリッピング工程を通じて除去した後、第1及び第2コンタクト領域521、524を露出させる前記第1コンタクトホールを満たしながら第1層間絶縁膜527上に第2導電層を形成する。前記第2導電層は、高濃度の不純物でドーピングされたポリシリコン又は金属を使用して形成する。

## 【0128】

化学機械的研磨工程、エッチバック工程、又は化学機械的研磨とエッチバックを組合せた工程を利用して、第1層間絶縁膜527の上面が露出されるまで前記第2導電層を部分的に除去することにより、それぞれ前記第1コンタクトホールを埋め立てる自己整列されたコンタクトパッドである第1パッド530及び第2パッド533を形成する。第1パッド530は、キャパシタコンタクト領域である第1コンタクト領域521上に形成され、第2パッド533は、ピットラインコンタクト領域である第2コンタクト領域524上に形成される。即ち、第1パッド530は、キャパシタコンタクト領域に接触され、第2パッド533はピットラインコンタクト領域に接触される。

## 【0129】

第1及び第2パッド530、533を含む第1層間絶縁膜527上に第2層間絶縁膜536を形成する。第2層間絶縁膜536は、後続して形成されるピットライン539と第1パッド530を電気的に絶縁させる役割を果たす。第2層間絶縁膜536は、BPSG、PSG、SOG、PE-TEOS、USG、又はHDP-CVD酸化物を化学気相蒸着工程、プラズマ化学気相成長工程、高密度プラズマ化学気相蒸着工程、又は原子層積層工程を利用して形成する。本発明の一実施例によると、第1及び第2層間絶縁膜527、536を

10

20

30

40

50

36は、前記酸化物のうち、同じ物質を使用して形成することができる。本発明の他の実施例によると、第1及び第2層間絶縁膜527、536は、前記酸化物のうち、互いに異なる物質を使用して形成することができる。

#### 【0130】

化学機械的研磨工程、エッチバック工程、又は化学機械的研磨とエッチバックを組合せた工程を利用して、第2層間絶縁膜536を部分的に除去することにより、第2層間絶縁膜536の上面を平坦化させる。

#### 【0131】

第2層間絶縁膜536上に第3フォトレジストパターン(図示せず)を形成した後、前記第3フォトレジストパターンをエッティングマスクとして利用して、第2層間絶縁膜536を部分的にエッティングすることにより、第2層間絶縁膜536に第1層間絶縁膜527を埋め立てた第2パッド533を露出させる第2コンタクトホール537を形成する。

10

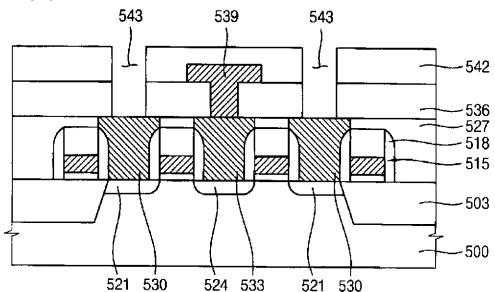

#### 【0132】

図29を参照すると、前記第3フォトレジストパターンをアッシング及び/又はストリッピング工程を利用して除去した後、第2コンタクトホール537を満たしながら第2層間絶縁膜536上に第3導電層を形成する。

#### 【0133】

前記第3導電層上に第4フォトレジストパターン(図示せず)を形成した後、前記第4フォトレジストパターンをエッティングマスクとして利用して前記第3導電層をエッティングすることにより、第2コンタクトホール537を満たしながら第2層間絶縁膜536上にビットライン539を形成する。ビットライン539は、大体が金属/金属化合物で構成された第1層及び金属からなる第2層で構成される。例えば、前記第1層は、チタニウム/チタニウム窒化物(Ti/TiN)からなり、前記第2層はタンクステン(W)からなる。

20

#### 【0134】

化学気相蒸着工程、プラズマ化学気相成長工程、高密度プラズマ化学気相蒸着工程、又は原子層積層工程を利用して、ビットライン439をカバーしながら、第2層間絶縁膜536上に第3層間絶縁膜542を形成する。第3層間絶縁膜542は、BPSG、PSG、SOG、PE-TEOS、USG、又はHDP-CVD酸化物を使用して形成される。第3層間絶縁膜542は、第2層間絶縁膜536と同じ物質を使用するか、異なる物質を使用して形成することができる。好ましくは、低温で蒸着されながらボイド(void)やシーム(seam)を発生させず、ビットライン539間のギャップを埋めることができるHDP-CVD酸化物を利用して第3層間絶縁膜542を形成する。

30

#### 【0135】

化学機械的研磨工程、エッチバック工程、又は化学機械的研磨とエッチバックを組合せた工程で第3層間絶縁膜542を部分的に除去することにより、第3層間絶縁膜542の上面を平坦化させる。本発明の他の実施例によると、隣接するビットライン539の間に位置する第3層間絶縁膜542内にボイドが発生する現象を防止するために、ビットライン539及び第2層間絶縁膜538上に窒化物からなる追加絶縁膜を形成した後、このような追加絶縁膜上に第3層間絶縁膜542を形成することもできる。

40

#### 【0136】

第3層間絶縁膜542上に第5フォトレジストパターン(図示せず)を形成した後、前記第5フォトレジストパターンをエッティングマスクとして利用して第3層間絶縁膜542及び第2層間絶縁膜536を部分的にエッティングすることにより、第1パッド530を露出させる第3コンタクトホール543を形成する。本発明の他の実施例によると、第3コンタクトホール543を形成した後、追加的な洗浄工程を行って第3コンタクトホール543を通じて露出される第1パッド530の表面に存在する自然酸化膜やポリマー又は各種異物質等を除去することができる。

#### 【0137】

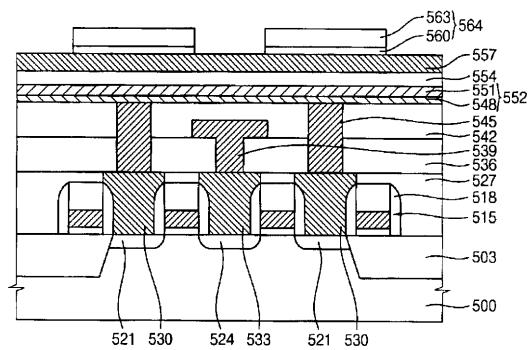

図30を参照すると、第3コンタクトホール543を満たしながら、第3層間絶縁膜5

10

20

30

40

50

42上に第4導電層を形成した後、化学機械的研磨、エッチバック、又はこれらを組合せた工程を利用して第3層間絶縁膜542の上面が露出されるまで、前記第4導電層を部分的に除去することにより、第3コンタクトホール543内にそれぞれ第3パッド545を形成する。第3パッド545は、大体が不純物でドーピングされたポリシリコンで形成され、第1パッド530とこれに後続して形成される下部電極569(図31参照)とを互いに連結させる役割を果たす。下部電極569は、第3パッド545及び第1パッド530を通じて第1コンタクト領域521に電気的に連結される。

#### 【0138】

第3パッド545及び第3層間絶縁膜542上に、約50~300程度の厚さを有する第1下部電極膜548及び約300~1000程度の厚さを有する第2下部電極膜551を順次に形成する。これによって、第3パッド545及び第3層間絶縁膜542上には下部電極層552が形成される。第1下部電極膜548は、金属窒化物を化学気相蒸着工程、スパッタリング工程、又は原子層積層工程で積層して形成され、第2下部電極膜551は金属をスパッタリング工程、パルスレーザー蒸着工程、又は原子層積層工程で積層して形成される。

#### 【0139】

第2下部電極膜551上に約200~1000程度の厚さを有する強誘電体層554を形成する。強誘電体層554は、強誘電性物質や、カルシウム、ランタン、マンガン、又はビスマス等の金属がドーピングされた強誘電性物質乃至金属酸化物を有機金属化学気相蒸着工程、ゾル・ゲル工程、又は原子層積層工程で積層して形成される。本発明の他の実施例によると、強誘電体層554を形成する前に、第2下部電極膜551上に約10~500程度の厚さを有する第3下部電極膜(図示せず)を形成することができる。前記第3下部電極膜は、銅、鉛、又はヒ素等のような金属がドーピングされたストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、又はカルシウムルテニウム酸化物を使用して形成される。前記第3下部電極膜は、約20~350程度の温度、約3~10mTorr程度の低い圧力及び不活性ガス雰囲気下で約300~1000W程度の電力を印加して形成される。

#### 【0140】

強誘電体層554上に約10~1200程度の厚さを有する上部電極層557を形成する。上部電極層557は、スパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程を利用して形成される。上部電極層557は、イリジウム、白金、ルテニウム、パラジウム、金、白金-マンガン合金、イリジウム-ルテニウム合金、イリジウム酸化物、ストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、又はカルシウムルテニウム酸化物等を使用して形成される。上部電極層540は、約20~350程度の温度、約3~10mTorr程度の圧力及び不活性ガス雰囲気下で約300~1000W程度の電力を印加して形成される。

#### 【0141】

強誘電体層554上に上部電極層557を形成した後、強誘電体層554及び上部電極層557を酸素ガス、窒素ガス、又はこれらの混合ガス雰囲気下で急速熱処理工程で熱処理して、上部電極層557及び強誘電体層554を構成する物質を結晶化させる。

#### 【0142】

図30を更に参照すると、上部電極層557上に第1ハードマスク層及び第2ハードマスク層を順次に形成する。前記第1ハードマスク層は、スパッタリング工程、化学気相蒸着工程、原子層積層工程、又はパルスレーザー蒸着工程を利用して上部電極層557の上面から約100~300程度の厚さに形成される。前記第1ハードマスク層は、上部電極層557、強誘電体層554、及び下部電極層552に対して高いエッチング選択比を有する物質を使用して形成される。前記第1ハードマスク層は、ストロンチウムルテニウム酸化物、ストロンチウムチタニウム酸化物、ランタンニッケル酸化物、カルシウムルテニウム酸化物、シリコン窒化物、又はシリコン酸窒化物を使用して形成される。

#### 【0143】

10

20

30

40

50

前記第2ハーダマスク層は、化学気相蒸着工程、プラズマ化学気相成長工程、パルスレーザー蒸着工程、又は原子層積層工程を利用して、前記第1ハーダマスク層の上面から約300～1000程度の厚さに形成される。前記第2ハーダマスク層は、前記第1ハーダマスク層、上部電極層557、及び強誘電体層554に対してエッティング選択比を有する物質を使用して形成される。例えば、前記第2ハーダマスク層は、ドーピングされないポリシリコン、シリコン酸化物、シリコン窒化物のような窒化物、又はシリコン酸窒化物のような酸窒化物を使用して形成される。

#### 【0144】

前記第2ハーダマスク層上に第6フォトレジストパターン(図示せず)を形成した後、前記第6フォトレジストパターンをエッティングマスクとして利用して、前記第2ハーダマスク層を部分的にエッティングすることにより、前記第1ハーダマスク層上に第2ハーダマスク563を形成する。10

#### 【0145】

前記第6フォトレジストパターンをアッシング及び／又はストリッピング工程を利用して除去した後、第2ハーダマスク560をエッティングマスクとして利用して、前記第1ハーダマスク層をパターニングすることにより、上部電極層557上に第1ハーダマスク50を形成する。これによって、上部電極層557上には、第1ハーダマスク560及び第2ハーダマスク563を含むハーダマスク構造物564が形成される。ここで、スピンスクラッピング工程を利用して、前記エッティング工程を通じて形成された第2ハーダマスク563の表面を改善することができる。一方、前記第6フォトレジストパターンをエッティングマスクとして利用して、前記第2ハーダマスク層及び前記第1ハーダマスク層を連続的にエッティングすることにより、上部電極層557上にハーダマスク構造物564を形成することもできる。20

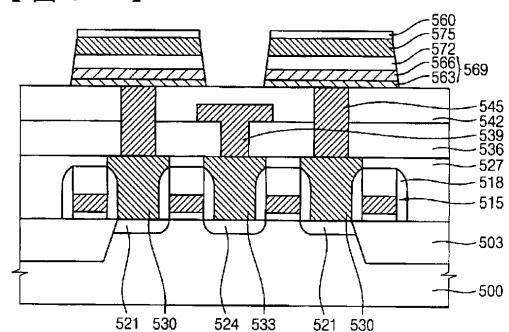

#### 【0146】

図31を参照すると、ハーダマスク構造物564をエッティングマスクとして利用して上部電極層557をエッティングすることにより、強誘電体層554上に上部電極575を形成する。上部電極575は、実質的に約80～90°の側壁傾斜角度を有する。

#### 【0147】

第2ハーダマスク563を第1ハーダマスク560から除去して、上部電極575上に第1ハーダマスク560のみを残留させる。前述したように、スピンスクラッピング工程を利用して第2ハーダマスク563の除去によって露出された第1ハーダマスク560の表面状態を改善することができる。30

#### 【0148】

第1ハーダマスク560をエッティングマスクとして利用して、高温で強誘電体層554をエッティングすることにより、第2下部電極膜551上に約80～90°程度の高い側壁傾斜角度を有する強誘電体層パターン572を形成する。高温で強誘電体層554をエッティングするエッティング工程の間、第1ハーダマスク560が上部電極575を充分に保護するので、上部電極575の側壁は約80～90°程度の高い側壁傾斜角度を維持する。

#### 【0149】

第1ハーダマスク560を継続的にエッティングマスクとして利用するエッティング工程を通じて、第2下部電極膜551及び第1下部電極膜548を順次にエッティングすることにより、第3層間絶縁膜542及び第3パッド545上に下部電極569を形成する。40

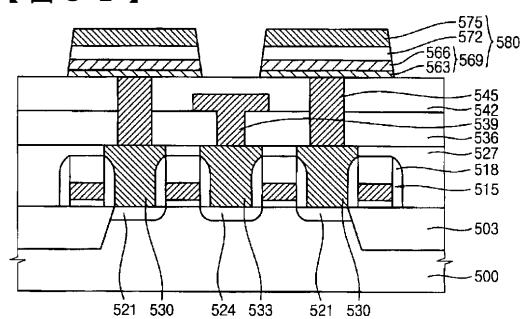

#### 【0150】

図32を参照すると、上部電極575から第1ハーダマスク560を除去して、基板500の上部に下部電極569、強誘電体層パターン572、及び上部電極575を具備する強誘電体キャパシタ580を完成する。第1及び第2ハーダマスク560、563を含むハーダマスク構造物564を利用して形成された強誘電体キャパシタ580は、半導体基板500に平行な方向に対して約80～90°程度の高い側壁傾斜角度を有する。

#### 【0151】

図示していないが、強誘電体キャパシタ580をカバーする追加層間絶縁膜及び前記追

10

20

30

40

50

加絶縁膜を通じて強誘電体キャパシタ580の上部電極575に接触される上部配線を形成してF R A M装置のような半導体メモリ装置を完成する。

【産業上の利用可能性】

【0152】

本発明によると、第1及び第2ハーダマスクを含むハーダマスク構造物を利用して、上部電極、強誘電体層パターン、及び下部電極を形成することにより、高い側壁傾斜角度によって拡張された有効面積を有する強誘電体キャパシタを形成することができる。従って、このような強誘電体層パターンを含む強誘電体キャパシタのデータセンシングマージンをより大きく確保することができ、データ保存力又は分極保存力等のような強誘電的特性が改善された強誘電体キャパシタを形成することができる。又、前記ハーダマスク構造物を利用して強誘電体層パターンのエッティング損傷による劣化を最小化することができるので、強誘電体層パターンから漏洩電流が発生することが防止できるので、強誘電体キャパシタの電気的特性を向上させることができる。又、前記強誘電体キャパシタを具備するF R A M装置のような半導体装置の信頼性を充分に確保することができる。

【0153】

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と趣旨を離れることなく、本発明を修正または変更できる。

【図面の簡単な説明】

【0154】

【図1】従来の強誘電体キャパシタの製造方法を説明するための断面図である。

【図2】従来の強誘電体キャパシタの製造方法を説明するための断面図である。

【図3】従来の強誘電体キャパシタの製造方法を説明するための断面図である。

【図4】従来の強誘電体キャパシタの断面電子顕微鏡写真である。

【図5】本発明の一実施例による強誘電体キャパシタの製造方法を説明するための工程順序図である。

【図6】本発明の一実施例による強誘電体キャパシタの製造方法を説明するための工程順序図である。

【図7】本発明の一実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図8】本発明の一実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図9】本発明の一実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図10】本発明の一実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図11】本発明の一実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図12】本発明の一実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図13】本発明の一実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図14】本発明の一実施例によって強誘電体層パターンを形成した状態を示す断面電子顕微鏡写真である。

【図15】本発明の一実施例による強誘電体キャパシタの断面電子顕微鏡写真である。

【図16】本発明の他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図17】本発明の他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図18】本発明の他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

10

20

30

40

50

面図である。

【図19】本発明の他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図20】本発明の更に他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図21】本発明の更に他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図22】本発明の更に他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図23】本発明の更に他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。 10

【図24】本発明の更に他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図25】本発明の更に他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図26】本発明の更に他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図27】本発明の更に他の実施例による強誘電体キャパシタの製造方法を説明するための断面図である。

【図28】本発明の一実施例による半導体装置の製造方法を説明するための断面図である。 20

【図29】本発明の一実施例による半導体装置の製造方法を説明するための断面図である。

【図30】本発明の一実施例による半導体装置の製造方法を説明するための断面図である。

【図31】本発明の一実施例による半導体装置の製造方法を説明するための断面図である。

【図32】本発明の一実施例による半導体装置の製造方法を説明するための断面図である。

#### 【符号の説明】

|                     |             |    |

|---------------------|-------------|----|

| 【0155】              |             | 30 |

| 100、200、300、400     | 半導体基板       |    |

| 105、205、305、405     | 下部構造物       |    |

| 110、210、310、410     | 絶縁構造物       |    |

| 115、215、315、415     | パッド         |    |

| 120、220、320、420、548 | 第1下部電極膜     |    |

| 125、225、325、425、551 | 第2下部電極膜     |    |

| 130、230、330、552     | 下部電極層       |    |

| 135、235、335、435、554 | 強誘電体層       |    |

| 140、240、340、440、557 | 上部電極層       | 40 |

| 145 第1ハードマスク層       |             |    |

| 150 第2ハードマスク層       |             |    |

| 155、255、355、455、563 | 第2ハードマスク    |    |

| 160、260、360、460、560 | 第1ハードマスク    |    |

| 165、265、365、465、564 | ハードマスク構造物   |    |

| 170、270、370、470、575 | 上部電極        |    |

| 175、275、375、475、572 | 強誘電体層パターン   |    |

| 180、280、380、480、566 | 第2下部電極膜パターン |    |

| 185、285、385、485、563 | 第1下部電極膜パターン |    |

| 190、290、390、490、569 | 下部電極        | 50 |

|                                       |               |

|---------------------------------------|---------------|

| 1 9 5 、 2 9 5 、 3 9 5 、 4 9 5 、 5 8 0 | 強誘電体キャパシタ     |

| 2 4 1 、 3 4 1                         | 第 1 上部電極膜     |

| 2 4 3 、 3 4 3                         | 第 2 上部電極膜     |

| 2 7 1 、 3 7 1                         | 第 2 上部電極膜パターン |

| 2 7 3 、 3 7 3                         | 第 1 上部電極膜パターン |

| 3 2 7                                 | 第 3 下部電極膜     |

| 3 7 7                                 | 第 3 下部電極膜パターン |

| 5 0 3                                 | 素子分離膜         |

| 5 0 6                                 | ゲート酸化膜パターン    |

| 5 0 9                                 | ゲート導電層パターン    |

| 5 1 2                                 | ゲートマスクパターン    |

| 5 1 5                                 | ゲート構造物        |

| 5 1 8                                 | ゲートスペーサ       |

| 5 2 1                                 | 第 1 コンタクト領域   |

| 5 2 4                                 | 第 2 コンタクト領域   |

| 5 2 7                                 | 第 1 層間絶縁膜     |

| 5 3 0                                 | 第 1 パット       |

| 5 3 3                                 | 第 2 パット       |

| 5 3 6                                 | 第 2 層間絶縁膜     |

| 5 3 9                                 | ピットライン        |

| 5 4 2                                 | 第 3 層間絶縁膜     |

| 5 4 5                                 | 第 3 パット       |

【図 1】

【図 3】

【図 2】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

【図22】

【図23】

【図24】

【図26】

【図25】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図4】

【図14】

【図15】

---

フロントページの続き

(72)発明者 高 化永

大韓民国京畿道水原市靈通区靈通洞（番地なし） ピョックチョクゴル8団地アパート846棟5

03号

(72)発明者 朱 石昊

大韓民国ソウル特別市江東区岩寺洞（番地なし） ソンサ現代アパート102棟1001号

(72)発明者 ペ 丙才

大韓民国京畿道水原市八達区靈通洞（番地なし） ピョックチョクゴル8団地宇成アパート824

棟802号

(72)発明者 金 熙錫

大韓民国京畿道城南市盆唐区盆唐洞（番地なし） セッピヨルマウル東成アパート203棟701

号

(72)発明者 邊 キュン 來

大韓民国京畿道水原市靈通区靈通洞（番地なし） ピョックチョクゴル8団地ハンシンアパート8

15棟1104号

(72)発明者 咸 陳煥

大韓民国ソウル特別市江南区道谷2洞（番地なし） 三星レミアンアパート106棟1602号

Fターム(参考) 5F083 FR02 GA21 GA27 HA02 JA02 JA15 JA17 JA36 JA37 JA38

JA39 JA40 JA42 JA43 JA45 MA06 MA17 MA20 PR03 PR06

PR07 PR34 PR40