(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4999323号

(P4999323)

(45) 発行日 平成24年8月15日(2012.8.15)

(24) 登録日 平成24年5月25日(2012.5.25)

(51) Int.Cl.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO1L 29/78   | (2006.01) | HO1L 29/78  | 301S |

| HO1L 21/336  | (2006.01) | HO1L 29/78  | 301L |

| HO1L 29/786  | (2006.01) | HO1L 29/78  | 616L |

| HO1L 21/265  | (2006.01) | HO1L 29/78  | 616V |

| HO1L 21/8238 | (2006.01) | HO1L 21/265 | F    |

請求項の数 7 (全 26 頁) 最終頁に続く

(21) 出願番号

特願2005-349353 (P2005-349353)

(22) 出願日

平成17年12月2日 (2005.12.2)

(65) 公開番号

特開2006-186349 (P2006-186349A)

(43) 公開日

平成18年7月13日 (2006.7.13)

審査請求日 平成20年9月12日 (2008.9.12)

(31) 優先権主張番号 特願2004-352073 (P2004-352073)

(32) 優先日 平成16年12月3日 (2004.12.3)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 田中 幸一郎

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 松嶋 秀忠

前置審査

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

単結晶シリコンでなる半導体基板またはSOI基板上にゲート電極を形成し、前記ゲート電極と所定の間隔離れた前記基板の第1の領域に、第1の不純物元素を導入して、前記第1の領域にソース領域及びドレイン領域を形成し、前記ゲート電極と前記第1の領域との間であり、前記ゲート電極と重ならない前記基板の第2の領域に、ゲルマニウム、アルゴン、クリプトン、キセノン、またはラドンと第2の不純物元素とを同時に導入し、且つ前記導入方向を前記基板の結晶方位に対して傾斜させず、前記基板を回転せずに前記導入を行うことにより、前記第2の領域をアモルファス化するとともに、前記第2の領域をエクステンション領域とし、

前記第2の領域に、パルス幅が1fs以上10ps以下で、波長が370nm以上640nm以下のレーザビームを照射することによって、前記第2の領域を活性化することを特徴とする半導体装置の作製方法。

## 【請求項 2】

単結晶シリコンでなる半導体基板またはSOI基板上にゲート電極を形成し、前記ゲート電極と所定の間隔離れた前記基板の第1の領域に、第1の不純物元素を導入して、前記第1の領域にソース領域及びドレイン領域を形成し、前記ゲート電極と前記第1の領域との間であり、前記ゲート電極と重ならない前記基板の第2の領域に、ゲルマニウム、アルゴン、クリプトン、キセノン、またはラドンと第2の不純物元素とを同時に導入し、且つ前記導入方向を前記基板の結晶方位に対して傾斜さ

10

20

せず、前記基板を回転せずに前記導入を行うことにより、前記第2の領域をアモルファス化するとともに、前記第2の領域をエクステンション領域とし、

前記第2の領域に、パルス幅が1 fs以上10 ps以下で、波長が370 nm以上640 nm以下のレーザビームを照射することによって、前記第2の領域を活性化し、

前記レーザビームは、10 MHz以上の繰り返し周波数を有することを特徴とする半導体装置の作製方法。

【請求項3】

請求項1又は請求項2において、

前記レーザビームは、Sapphir e、YAG、セラミックスYAG、セラミックスY<sub>2</sub>O<sub>3</sub>、KGW、KYW、Mg<sub>2</sub>SiO<sub>4</sub>、YLF、YVO<sub>4</sub>、またはGdVO<sub>4</sub>の結晶に、Nd、Yb、Cr、Ti、Ho、およびErのいずれかのドーパントを添加したレーザ発振器を用いて形成されることを特徴とする半導体装置の作製方法。 10

【請求項4】

請求項1乃至請求項3のいずれか一において、

前記エクステンション領域は、前記ソース領域および前記ドレイン領域よりも浅く形成することを特徴とする半導体装置の作製方法。

【請求項5】

請求項4において、

前記エクステンション領域を0.1 nm以上20 nm以下の深さを有するように形成することを特徴とする半導体装置の作製方法。 20

【請求項6】

請求項1乃至請求項5のいずれか一において、

前記第1の不純物元素及び前記第2の不純物元素としてヒ素またはリンを用いることを特徴とする半導体装置の作製方法。

【請求項7】

請求項1乃至請求項5のいずれか一において、

前記第1の不純物元素及び前記第2の不純物元素としてホウ素を用いることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、レーザ光を被照射物に照射するためのレーザ照射装置を用いた半導体装置の作製方法に関するものである。具体的には、本発明は極浅接合を有する薄膜トランジスタ(以下、TFTと称す)で構成された半導体装置に関するものである。例えば、超大規模集積回路(LSI)、液晶表示パネルに代表される電気光学装置、発光素子を有する発光表示装置、CCD(電荷結合素子)を有する受光装置、SRAMやDRAMなどのメモリ装置、およびこれらの装置を部品として搭載した電子機器に関するものである。

【0002】

なお、本明細書中で半導体装置とは、半導体特性を利用して機能することができる装置全般を指し、電気光学装置、半導体回路、およびこれらを有する電子機器は全て半導体装置である。 40

【背景技術】

【0003】

半導体素子の微細化、高集積化に関して、多くの研究開発が進められている。特に、MOSFET(MOS Field Effect Transistor)と呼ばれる絶縁ゲート電界効果型半導体素子の微細化技術の進歩はめざましい。MOSとは、Metal-Oxide-Semiconductor、すなわち、「金属-酸化物-半導体」の3種類の材料(物質)を組み合わせた構造である。

【0004】

ここで金属とは、純粋な金属だけを意味するのではなく、十分に導電率の大きな半導体

10

20

30

40

50

材料や、半導体と金属の合金なども含めた広い意味で使用される。また、酸化物とは、純粋な酸化物だけではなく、窒化物等の十分に抵抗の大きな絶縁性材料が用いられることがある。これらの場合でも慣用的にMOSと呼ばれている。以下、本明細書では窒化物その他の絶縁物をも含めて、このような構造を有する電界効果型素子をMOSFETと称することとする。

【0005】

MOSFETはnチャネル型導電型およびpチャネル型導電型を問わず、一般的にチャネル形成領域、ゲート絶縁膜、ゲート電極、ソース領域、ドレイン領域を有している。このMOSFETは、高集積化しやすい特徴を持つため、集積回路を有するトランジスタ素子として広く用いられている。

10

【0006】

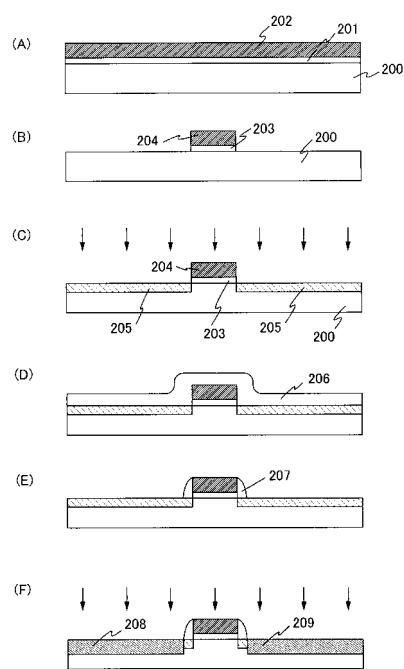

MOSFETの微細化は、ゲート電極の幅を小さくすることによって行われる。MOSFETの微細化に伴って、短チャネル効果やホットエレクトロンの発生を防止するために、ドレイン領域のチャネル形成領域側の不純物を低濃度化したLDD (Lightly Doped Drain) 構造(図2(F))が用いられている。

【0007】

LDD構造を用いることによって、ドレイン領域のチャネル形成領域側への不純物の拡散量を低減し、チャネル長の長さを確保することができる。また、チャネル形成領域と不純物領域(ドレイン領域)の境界に形成されるpn接合部の不純物濃度分布の勾配が緩和されるため、この領域の電界集中を緩和させることができる。これによって素子の動作を安定化させることができた。

20

【0008】

LDD構造を有するMOSFETは、通常、図2で示すように形成される。なお、ここではN型のMOSFETの作製例を示すが、P型のMOSFETであっても同様に作製される。

【0009】

最初に、図2(A)に示すように、p型の半導体基板200の主面上に酸化膜201と導電性膜202を形成する。これらをエッチングすることによって、図2(B)に示すように、それぞれゲート絶縁膜203とゲート電極204を形成する。そして、このゲート電極204をマスクとし、イオン打ち込み法等によって半導体基板の主面に不純物を導入し、自己整合的に比較的不純物濃度の低い不純物領域(以下、エクステンション領域と呼ぶ)205を形成する(図2(C))。なお、この場合、エクステンション領域205は記号ではn<sup>-</sup>と表される。

30

【0010】

次いで、図2(D)に示すように、エクステンション領域205上に絶縁膜206を形成する。そして、この絶縁膜206に対してバイアスプラズマエッチ等の異方性エッチングを用いて処理を行うことによって、サイドウォールスペーサ207を形成する(図2(E))。そして、このサイドウォールスペーサ207をマスクとして、自己整合的に不純物濃度の高い(記号ではn<sup>+</sup>と表される)不純物領域を形成する。その後、それぞれの不純物領域に加熱処理を行って添加した不純物を活性化することによって、ソース領域208、ドレイン領域209が形成される(図2(F))。

40

【発明の開示】

【発明が解決しようとする課題】

【0011】

MOSFETにおいてもさらなる微細化が要求されている。問題になるのはドレイン電流の減少である。これを解決するためには、エクステンション領域の低抵抗化が有効である。エクステンション領域の低抵抗を図るために、半導体基板の主面の極浅い領域に、高濃度の不純物をイオン注入し、注入した不純物の活性化を行う必要がある。

【0012】

従来では、不純物を活性化するための加熱処理として、RTA(Rapid Thermal Processing)

50

mall Annealing) 法が用いられてきたが、この R T A には以下の問題がある。

【 0 0 1 3 】

R T A 法では加熱時間が数秒と長く、この間にエクステンション領域内の不純物が深く拡散してしまう。不純物が深く拡散すると、接合が深くなり、ゲート電極とソース領域およびドレイン領域の重なりが増大する。このため、実効的なチャネル長が短くなり、電界集中や短チャネル効果が起きてしまう。従って、R T A による加熱時間よりも短い時間で加熱処理ができる新規なアニール方法が必要とされている。

【課題を解決するための手段】

【 0 0 1 4 】

そこで本発明は、短時間で局所的に高温の熱を加えることができるアニール方法、及びこのアニール方法によって作製された半導体装置を提供することを目的とする。

【 0 0 1 5 】

具体的には、後にエクステンション領域になる部分に、n 型または p 型の不純物を導入するとともに単結晶格子を崩してアモルファス化させる。そして、パルス幅が 1 f s ~ 10 p s、波長が 370 nm 以上 640 nm 以下のレーザビームをアモルファス化したエクステンション領域を含む半導体基板に照射し、エクステンション領域を活性化する。

【 0 0 1 6 】

また、具体的には、後にエクステンション領域になる部分に、n 型または p 型の不純物を導入した後、Ge や 0 族の元素 (Ar、Kr、Xe、Rn など) のような重い元素を打ち込むことによって、単結晶格子を崩してアモルファス化させる。そして、パルス幅が 1 f s ~ 10 p s、波長が 370 nm 以上 640 nm 以下のレーザビームをアモルファス化したエクステンション領域を含む半導体基板に照射し、エクステンション領域を活性化する。

【 0 0 1 7 】

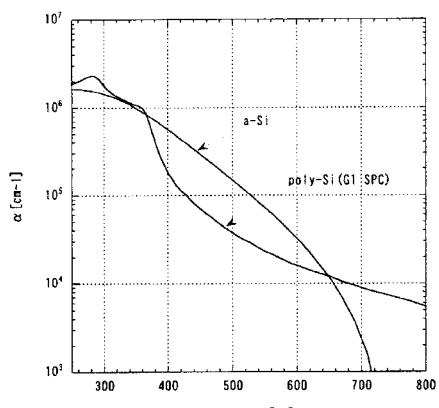

上記構成において、370 nm 以上 640 nm 以下の波長域のレーザを選ぶ理由は、その波長域が単結晶半導体よりもアモルファス化した半導体によく吸収されるからである。図 3 はアモルファスシリコン膜および多結晶シリコン膜における、波長と吸収係数との関係を示すグラフである。このグラフより、アモルファスシリコンと多結晶シリコンとでは、370 nm 以上 640 nm 以下、特に 400 nm 以上 540 nm 以下において吸収係数に差が見られる。つまり、この波長領域のレーザビームを照射すると、エクステンション領域には吸収されやすいが、単結晶シリコン膜には吸収されにくい。本発明では、この波長域内のレーザビームを用いてアニールをすることにより、レーザビームによるエネルギーをエクステンション領域のみに選択的に与えるものである。

【 0 0 1 8 】

また本発明ではパルス幅が 1 f s 以上 10 p s 以下と超短パルスのレーザを用いるため、エクステンション領域が熱を受ける時間を非常に短くできる。したがって、R T A 法に比べて不純物の拡散を大幅に抑えることができる。結果的に、電界集中の緩和や短チャネル効果の抑制といった効果を得ることができる。

【 0 0 1 9 】

さらに、本発明では、発振周波数が 10 MHz 以上のレーザを用いて照射を行うことにより、処理時間を短縮し、スループットよく半導体装置を作製することが可能になる。

【 0 0 2 0 】

上記構成において、エクステンション領域になる部分に上記の重い元素を打ち込んで単結晶格子を崩してアモルファス化させてから、n 型または p 型を与える原子を導入してエクステンション領域を形成するようにしても良いし、逆に n 型または p 型を与える原子を導入してから上記の重い原子を打ち込んでも良いし、または n 型または p 型を与える原子とともに上記の重い元素を打ち込んでも良い。ここで、n 型を与える不純物元素としてリン、ヒ素、アンチモンを挙げることができる。また、p 型を与える不純物元素として、ホウ素、アルミニウムを挙げることができる。

## 【0021】

また、上記構成において、不純物や重い元素を半導体基板に導入する際、半導体基板を連続して回しながら導入することや、不純物や質量数が大きい元素を半導体基板に対して相対的に斜めにして導入することによって、導入された不純物が結晶の隙間を通り、奥深くまで到達してしまう現象（チャネリング現象）や、表面の凹凸部分が存在することによって不純物や質量が重い元素が導入されない領域が生じやすくなる現象（シャドー効果という）を防止することができるため、エクステンション領域を良好に形成することができる。

## 【0022】

また、上記の構成を用いることによって、エクステンション領域の深さを0.1nm以上20nm以下にすることができる。 10

## 【0023】

また、上記構成において、半導体基板とは、（1）単結晶シリコン基板または化合物半導体基板、（2）SOI（Silicon on Insulator）基板を指す。（1）、（2）はそれぞれ代表的には、（1）N型またはP型の単結晶シリコン基板、GaAs基板、InP基板、GaN基板、SiC基板、サファイア基板、ZnSe基板、（2）貼り合わせ法またはSIMOX（Separation by Implanted Oxygen）法を用いて作製された基板、を挙げることができる。なお、ガラス、石英、合成樹脂などの絶縁性物質に単結晶半導体膜を形成した基板を用いることも可能である。 20

## 【0024】

また、半導体基板を用いて集積回路を形成した半導体素子としては、代表的には、CPU、メモリ、ICを挙げることができる。

## 【0025】

以上の構成を用いることにより、短チャネル効果より生じるソース領域とドレイン領域との間のリーク電流を低減する半導体装置を作製することが可能となる。

## 【発明の効果】

## 【0026】

本発明を用いることによって、短時間で局所的に高温加熱することができるため、エクステンション領域の形成を浅く保つことができる。エクステンション領域が浅く形成できること、短チャネル効果の抑制や電界集中の緩和などの効果が得られる。 30

## 【発明を実施するための最良の形態】

## 【0027】

以下に本発明の実施の様態を、図面を用いて説明する但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

## 【0028】

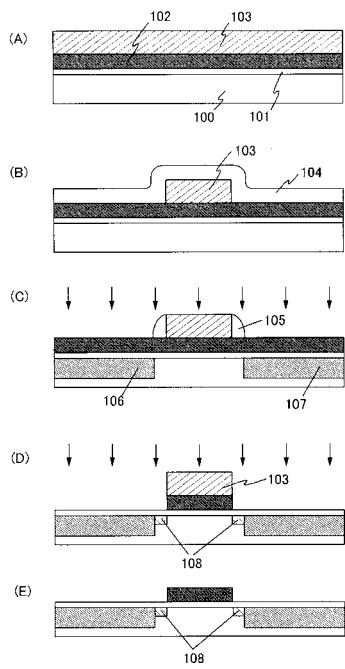

本発明の一例を、図1を用いて説明する。

## 【0029】

まず、図1(A)に示すように、単結晶半導体基板100上に、ゲート絶縁膜101、半導体膜102、さらに被膜103を形成する。 40

## 【0030】

本実施の形態では、ゲート絶縁膜101は単結晶半導体基板100を熱酸化して形成した酸化膜を用いる。なお、ゲート絶縁膜101は、熱酸化法に限らず、CVD法を用いて形成してもよい。ゲート絶縁膜101の材質は、酸化窒化珪素膜、窒化珪素膜、またはこれらの積層膜、またはタンタル酸化物などの高誘電率物質を用いることができる。さらには、ゲート絶縁膜101の形成方法は1つに限定されない。例えば、熱酸化により得られる膜厚5nmの酸化珪素膜とCVD法で得られる膜厚10nm～15nmの酸化窒化珪素膜の積層膜によって形成することができる。 50

## 【0031】

次に、半導体膜102と被膜103を全面に形成する。なお、被膜103はイオン注入の際のマスクとして機能させてゲート電極を保護する必要があるので、十分な厚みが必要である。従って、被膜103は十分に厚い窒化珪素膜、窒化珪素膜と酸化珪素膜との積層膜、薄い窒化珪素膜の上部にフォトレジスト等の有機材料膜や炭素膜等を積層した被膜などを用いることができる。本実施の形態では、被膜103は窒化珪素膜を用いる。

## 【0032】

次に、図1(B)に示すように、リソグラフィ技術およびドライエッティング技術に基づき、窒化珪素膜103を所定の形状に整形する。さらに、常圧CVD法、減圧CVD法、プラズマCVD法、光CVD法等の方法を用いて酸化珪素膜104を一様に形成する。この際、窒化珪素膜103が有機材料を含む場合、成膜時の温度が高いと有機材料が変質したり、有機材料が蒸発したりする。そこで、窒化珪素膜103を成膜する際には、含まれる材料を考慮する必要がある。

10

## 【0033】

その後、図1(C)に示すように、公知の異方性エッティング技術を用いることによって、酸化珪素によるサイドウォール105を形成する。この状態でイオン注入法等によって不純物を導入し、ソース領域106、ドレイン領域107を形成する。なお、本実施の形態はn型FETを形成する場合であるので、n型不純物であるヒ素(As)、リン(P)またはアンチモン(Sb)を導入する。また、p型FETを作製する場合は、p型不純物のホウ素(B)を導入する。

20

## 【0034】

さらに、選択的にサイドウォール106を除去し、レーザアニール法やRTA法などによってソース領域106、ドレイン領域107に導入された不純物の活性化を行うと同時に、不純物の導入によって崩されたソース領域106およびドレイン領域107の結晶性を改善する。

## 【0035】

次に、図1(D)に示すように、プラズマドーピング法やイオン注入法などにより極浅の不純物導入を行い、エクステンション領域108を形成する。本実施の形態はn型FETを形成する場合であるので、n型不純物であるヒ素(As)、リン(P)またはアンチモン(Sb)を導入する。p型FETを作製する場合は、p型不純物のホウ素(B)を導入する。ここでエクステンション領域108に注入される不純物の濃度は、ソース領域106およびドレイン領域107の不純物濃度よりも低い場合もあるし、同等の場合もあるし、高い場合もある。即ち、エクステンション領域108の不純物濃度は、半導体装置に要求される特性に基づいて決定すればよい。

30

## 【0036】

さらに、ゲルマニウム(Ge)や0族の元素(Ar、Kr、Xe、Rnなど)などの質量が重い原子を打ち込み、エクステンション領域108の部分の単結晶の格子を崩す。この際、打ち込む速度を下げ、20nm程度までアモルファス化する。不純物の導入と重い原子の打ち込みの順番は限定されるものではない。どちらを先にしても良いし、同時に打っても良い。

40

## 【0037】

なお、単結晶半導体基板100は原子が整然と配列している。特に珪素の<100>面や<111>面の場合では、導入された不純物が結晶の隙間を通り、奥深くまで到達してしまう現象(チャネリング現象)が起きる。そこで、単結晶半導体基板100の結晶方位に対して不純物の導入方向を傾斜させて注入すると、原子間の隙間を少なくすることができるため、導入された不純物が結晶の表面近傍でとどまり、奥深くに到達することを予防する。

## 【0038】

また、エクステンション領域108になる部分の周囲には、窒化珪素膜103などの凹凸部分が存在するため、不純物や質量が重い元素が導入されない領域が生じやすくなる(

50

シャドー効果という）。その防止策として、（1）単結晶半導体基板100を回転させながら不純物や質量が重い元素の導入を行う、（2）所定の時間や角度毎に回転を中断し、そのときに不純物や質量の重い元素の導入を行う、などの方法をとることができる。単結晶半導体基板100を回転させながら不純物や質量の重い元素の導入を行うと、チャネリング現象とシャドー効果の予防が同時にできるため、より好ましい。

【0039】

不純物および質量が重い元素を導入した後、導入した不純物元素を極浅かつ高濃度のプロファイルのまま活性化するために、本発明によるレーザアニールを行う。この後、エッティングにより窒化珪素膜103を選択的に除去する（図1（E））。

【0040】

本発明のレーザアニールでは、パルス幅は1fs～10psとし、波長は370～640nmの範囲内から選択する。その理由は、図3にも示すように、この波長域が単結晶半導体よりもアモルファス化した半導体によく吸収されるからである。

【0041】

レーザ発振器は安定形共振器とし、TEM<sub>00</sub>（シングル横モード）の発振モードであることが望ましい。TEM<sub>00</sub>モードの場合、レーザビームはガウス型の強度分布を持ち、集光性に優れているため、ビームスポットの加工が容易となる。レーザ発振器から発振されたレーザビームの基本波長が赤外領域にある場合は、非線形光学素子により第2高調波（532nm程度）に変換し用いることができる。本実施の形態では、エネルギー10W、TEM<sub>00</sub>の発振モード、第2高調波（532nm）、発振周波数160MHz、パルス幅10psのYVO<sub>4</sub>レーザを用いる。なお、被照射物上に形成されるビームスポットは、光学系を用いることによって所望の形状にすることが可能である。なお本発明は、本実施例で示した照射条件に限定されない。

【0042】

以上のようにレーザアニールを行い、添加した不純物元素を活性化させると同時に、不純物添加によって形成された結晶欠陥を低減する。本実施の形態では532nmの波長を選択することでアモルファス化したエクステンション領域にのみレーザビームのエネルギーが吸収され、選択的に加熱することができる。また、パルス幅が1fs～10psの超短パルスであるため、不純物の拡散を抑えることができる。さらに、発振周波数が10MHzを超えるレーザを用いているため、処理時間を短縮することが可能である。

【0043】

以上より、エクステンション領域108を浅く保つことができ、本発明を用いて作製した半導体装置は、短チャネル効果の抑制及び電界集中の緩和などの効果が得られる。

【0044】

さらに、この後に適宜工程を行うことで半導体装置を作製することができる。本発明を用いて作製された半導体装置は、その電気的特性が良好なものとなり、動作特性も大幅に向上する。

【0045】

本実施の形態は、他の実施例と組み合わせることが可能である。また、ガラス基板、石英基板、有機樹脂製基板などの絶縁基板上に形成された半導体膜を用いた薄膜トランジスタにも同様に用いることが可能である。

【実施例1】

【0046】

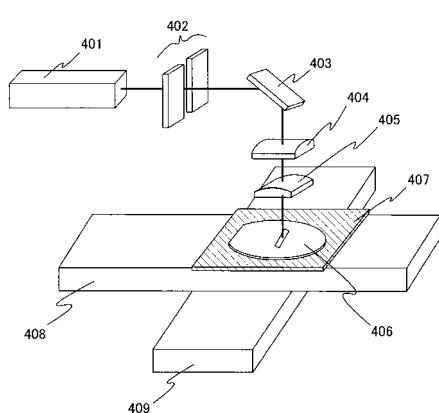

本実施例では、本発明に用いるレーザ照射装置の例を示し、図を用いて説明する。

【0047】

図4に示すレーザ発振器401は、パルス幅がフェムト秒（10<sup>-15</sup>秒）台で発振するレーザ（フェムト秒レーザともいう）のレーザ発振器を用いる。また、レーザ発振器401は、370～640nm、好ましくは400～540nmの波長のいずれかで射出するように、必要に応じて非線形光学素子を用いて高調波に変換する。

【0048】

10

20

30

40

50

本発明で用いるレーザとしては、例えば、Sapph i r e、YAG、セラミックスYAG、セラミックス $Y_2O_3$ 、KGW、KYW、 $Mg_2SiO_4$ 、YLF、 $YVO_4$ 、 $GdVO_4$ などの結晶に、Nd、Yb、Cr、Ti、Ho、Erなどのドーパントを添加したレーザを挙げることができるが、これに限らない。上記のパルス幅と波長の条件を満たすことができるレーザであれば、どのようなレーザを用いてもよい。なお、上記の条件に加えて、発振周波数が10MHzを超えるレーザを用いることにより、処理時間を短縮することが可能となるため、より好ましい。

#### 【0049】

まず、レーザ発振器401から射出したレーザビームは、スリット402を通る。スリット402は、レーザビームにおけるエネルギーの弱い部分を遮断することができ、照射面におけるレーザビームの長軸方向の長さを調節することができる。本発明においてスリット402については特に制限されることはなく、スリットを通過した際に強度の弱い部分を遮断することができる構造あるいは形状のものを使用することができる。

#### 【0050】

本実施例ではスリット402を用いているが、スリット402の代わりにシリンドリカルレンズやシリンドリカルレンズアレイ、フライアイレンズ、ライトパイプ、ディフラクティブオプティクスなどを用いたビームホモジナイザによってビームのエネルギー密度を均一化すると、照射面に均一にエネルギーを与えることができる。また、ビームホモジナイザとスリットの両方を用いてもよい。

#### 【0051】

次に、スリット402を通ったレーザビームはミラー403で方向を変えられて、半導体基板406の方向に偏向される。なお、方向を変えた後のレーザビームの方向は、半導体基板に対して垂直方向でも構わない。

#### 【0052】

続いて、ミラー403で方向を変えられたレーザビームは、一方向にのみ作用する第1のシリンドリカルレンズ404によって集光される。さらに、レーザビームは、第1のシリンドリカルレンズ404と90度回転した一方向にのみ作用する第2のシリンドリカルレンズ405によって集光され、半導体基板406に照射される。第1のシリンドリカルレンズ404および第2のシリンドリカルレンズ405によって、照射面にて線状、楕円状、または矩形状のビーム照射領域が得られる。

#### 【0053】

シリンドリカルレンズ404、405を用いる利点は、ビームの長軸方向と短軸方向の集光をそれぞれ独立して行うことができる点である。なお、元のビームのビーム径、出力、ビームの形状をそのまま用いることができる場合は、シリンドリカルレンズを必ずしも2つ用いなくても良い。また、元のビームの長軸と短軸の長さの比を保ったまま集光を行う場合は、シリンドリカルレンズ404、405の代わりに球面レンズを用いても良い。

#### 【0054】

そして、半導体基板406を適度な速度で移動させてレーザ照射を行う。半導体基板406は、レーザ照射の際に基板が落ちないように、吸着手段または機械的に固定する手段によって基板固定ステージ407に固定されている。また、基板固定ステージ407は、Xステージ408、Yステージ409を用いて、半導体基板の表面と平行な面上をX方向またはY方向に移動させることができるようにになっている。Xステージ408、およびYステージ409は、基板固定ステージ407に固定された半導体基板を100～1000mm/secの速度で移動させることができる。ここでは、固定されたレーザビームの照射領域に対して、半導体基板が設置されたステージをX方向（またはY方向）に移動させてレーザビームを照射する方式としている。なお、本発明人らの経験から予想される最適な走査の速度は、400mm/sec前後である。

#### 【0055】

また、レーザビームの走査は、被処理物である基板を固定してレーザビームの照射位置を移動させる照射系移動型、レーザビームの照射位置を固定して基板を移動させる被処理

10

20

30

40

50

物移動型、または上記 2 つの方法を組み合わせた方法を用いることができる。例えば、Xステージ 408 や Yステージ 409 を動かす代わりに、ガルバノミラー や ポリゴンミラー によってレーザビームを照射させてもよい。

【0056】

また、レーザのパルス幅に対する熱拡散距離を以下の式で求めることができる。

【0057】

【数 1】

$$L_D \approx (D_F \tau_L)^{\frac{1}{2}}$$

10

【0058】

ここで  $\tau_L$  は時間、すなわちレーザのパルス幅を表す。また、 $D_F$  は材料の熱拡散係数であり、以下の式で求めることができる。ここで、 $K_T$  は熱伝導率、 $\rho$  は密度、 $C_p$  は比熱容量である。

【0059】

【数 2】

$$D_F = K_T / \rho C_p$$

20

【0060】

結晶シリコンの熱伝導率  $K_T$  は  $148 \text{ W/m}\cdot\text{K}$ 、密度  $\rho$  は  $2330 \text{ kg/m}^3$ 、比熱容量  $C_p$  は  $700 \text{ J/kg}\cdot\text{K}$  である。これらの値より、熱拡散係数  $D_F$  は  $9.074 \times 10^{-5} \text{ m}^2/\text{s}$  と求めることができる。

【0061】

この結果を式 1 に代入することにより、シリコンの熱拡散距離を求めることができる。例えば、レーザのパルス幅が 1 ps のとき、結晶シリコンの熱拡散距離  $L_D$  は  $9.525 \text{ nm}$  と算出できる。このように、パルス幅がフェムト秒台 ( $10^{-15} \text{ 秒}$ ) からピコ秒台であるレーザビームを用いた場合、結晶シリコンの熱拡散距離は非常に小さく、レーザビームで照射された部分のみが高温高密度エネルギー状態となり、熱拡散による熱影響層がほとんどでない。すなわち、パルス幅がフェムト秒台 ( $10^{-15} \text{ 秒}$ ) からピコ秒台であるレーザビームを半導体に添加された不純物の活性化に用いると、接合深さの浅い極浅接合を形成することができる。

30

【0062】

また、本発明において、レーザのパルス幅などの照射条件を適宜設定することで、接合深さを自由に調節することができる。

【実施例 2】

【0063】

本実施例では、実施の形態とは別の FET の作製手順を示す。

【0064】

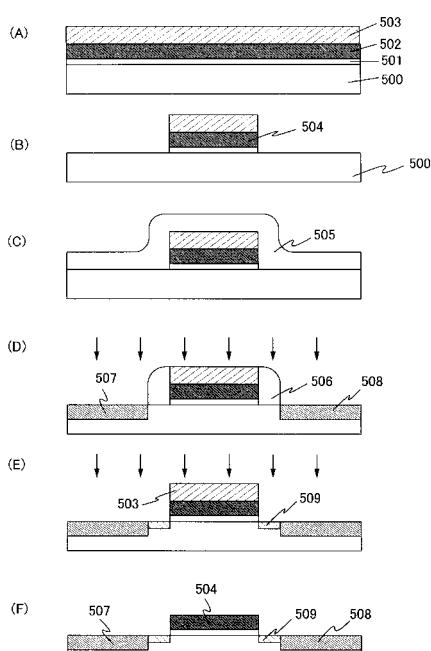

まず、図 1 (A) と同様に、単結晶半導体基板 500 上に、ゲート絶縁膜 501、導電膜 502、さらに被膜 503 を形成する。

40

【0065】

単結晶半導体基板 500 は、例えば貼り合わせ法または SIMOX (Separation by Implanted Oxygen) 法を用いて作製された SOI (Silicon on Insulator) 基板、シリコンウェハーなどを用いることができる。SOI 基板を用いて半導体素子を作製すると、隣接する素子を完全に分離することができ、リーコ電流が流れるのを防ぐことができる。

【0066】

本実施例では、ゲート絶縁膜 501 は単結晶半導体基板 500 を熱酸化して形成した酸化膜を用いる。なお、ゲート絶縁膜 501 は、本実施例で用いた熱酸化法に限らず、プラ

50

ズマ C V D 法やスパッタ法などを用いて形成してもよい。

【 0 0 6 7 】

なお、ゲート絶縁膜 501 の形成方法は 1 つに限定されない。例えば、熱酸化により得られる膜厚 5 nm の酸化珪素膜と C V D 法で得られる膜厚 10 nm ~ 15 nm の酸化窒化珪素膜の積層膜によって形成してもよいし、ゲート絶縁膜 501 として窒化酸化珪素膜と酸化窒化珪素膜の積層膜を用いる場合には、C V D 法を用いて、ガスを切り替えることによって連続的に成膜を行うこともできる。

【 0 0 6 8 】

ゲート絶縁膜 501 の材質は、(1)酸化珪素膜、窒化酸化珪素膜 ( $\text{SiN}_x\text{O}_y$  (x と y は  $x > y$  を満たす 1 以上の自然数))、酸化窒化珪素膜 ( $\text{SiN}_x\text{O}_y$  (x と y は  $x < y$  を満たす 1 以上の自然数))、窒化珪素膜、またはこれらの積層膜、(2)高誘電率物質 (high-k 材料ともいう) のタンタル酸化物、酸化ハフニウム ( $\text{HfO}_2$ )、窒化ハフニウムシリゲート ( $\text{HfSiON}$ )、酸化ジリコニウム ( $\text{ZrO}_2$ )、酸化アルミニウム ( $\text{Al}_2\text{O}_3$ )、または酸化ランタン ( $\text{La}_2\text{O}_3$ ) などの希土類酸化物、などを用いることができる。

【 0 0 6 9 】

導電膜 502 は、ゲート絶縁膜 501 上に非晶質半導体膜や金属膜を公知の方法 (スパッタリング法、L P C V D 法、プラズマ C V D 法など) によって形成する。導電膜 502 は、珪素やシリコンゲルマニウムなどの半導体材料や、金 (Au)、銀 (Ag)、銅 (Cu)、白金 (Pt)、アルミニウム (Al)、モリブデン (Mo)、タンゲステン (W)、チタン (Ti)、タンタル (Ta) から選ばれた元素、またはこれらの元素を主成分とする合成材料または化合物材料を用いることができる。さらには、これらの材料の積層物を用いることができる。例えば、タンゲステン (W) と窒化タンタル (TaN) の積層膜やアルミニウム (Al) とモリブデン (Mo) の積層膜を用いることができる。本実施例では導電膜 502 の材料として珪素を用いる。

【 0 0 7 0 】

なお、ゲート絶縁膜 501 に高誘電率物質 (high-k 材料) を用いた場合には、導電膜 502 には金属元素または金属元素を主成分とする材料を用いることが望ましい。この組み合わせを用いることによって、ゲート電極の空乏化を解消し、大量の電流を流すことができるようになり、半導体素子の低電力化に貢献するからである。

【 0 0 7 1 】

また、本実施例では、被膜 503 は窒化珪素膜を用いる。なお、被膜 503 はイオン注入の際のマスクとしても機能する必要があるので、十分な厚みが必要である。従って、被膜 503 は十分に厚い窒化珪素膜、窒化珪素膜と酸化珪素膜との積層膜、薄い窒化珪素膜の上部にフォトレジスト等の有機材料膜や炭素膜等を積層した被膜などを用いることができる。

【 0 0 7 2 】

次に、図 5 (B) に示すように、リソグラフィ技術およびドライエッティング技術に基づき、これらの積層膜を所定の形状に整形することによって、ゲート電極 504 を形成する。ゲート電極 504 を低抵抗化するために、予め  $10^{21} \text{ atoms/cm}^3$  程度の濃度でリン (P) をドープしておいても良いし、導電膜 502 を形成した後に濃い n 型不純物を拡散させてもいい。

【 0 0 7 3 】

さらに、図 5 (C) に示すように、常圧 C V D 法、減圧 C V D 法、プラズマ C V D 法、光 C V D 法等の方法を用いて酸化珪素膜 505 を一様に形成する。

【 0 0 7 4 】

その後、図 5 (D) に示すように、公知の異方性エッティング技術を用いることによって、酸化珪素によるサイドウォール 506 を形成する。この状態でイオン注入法等によって不純物を注入し、ソース領域 507、ドレイン領域 508 を形成する。なお、本実施例は n 型 F E T を形成する場合であるので、n 型不純物であるヒ素 (As)、リン (P) また

10

20

30

40

50

はアンチモン (Sb) を導入する。また、p型FETを作製する場合は、p型不純物のホウ素 (B) を導入する。なお、さらに、イオン注入された不純物の活性化と、イオン注入によって発生したシリコン基板の結晶欠陥を回復するために、第一回目の活性化処理を行う。なお、第1回目の活性化処理はRTA法、レーザアニール法などの公知の方法にて行ってよい。

#### 【0075】

次に、図5(E)に示すように、プラズマドーピング法などにより極浅の不純物導入を行い、エクステンション領域509を形成する。本実施例はn型FETを形成する場合であるので、n型不純物であるヒ素 (As)、リン (P)、またはアンチモン (Sb) を導入する。また、p型FETを作製する場合は、p型不純物のホウ素 (B) を導入する。ここでエクステンション領域509に注入される不純物の濃度は、ソース領域507およびドレイン領域508の不純物濃度よりも低い場合もあるし、同等の場合もあるし、高い場合もある。即ち、エクステンション領域509の不純物濃度は、半導体装置に要求される特性に基づいて決定すればよい。

10

#### 【0076】

なお、この際にゲルマニウム (Ge) や0族の元素 (Ar、Kr、Xe、Rnなど) などの質量が重い原子を打ち込み、単結晶の格子を崩す。この際、打ち込む速度を下げ、20nm程度までアモルファス化する。不純物の導入と質量が重い原子の打ち込みの順番は限定されるものではない。どちらを先にしても良いし、同時にあっても良い。不純物と質量が重い原子の打ち込む領域が同じであればよい。

20

#### 【0077】

また、単結晶半導体基板500は原子が整然と配列している。特に珪素の<100>面や<111>面の場合では、導入された不純物が結晶の隙間を通り、奥深くまで到達してしまう現象 (チャネリング現象) が起きる。そこで、単結晶半導体基板500に対して不純物の導入方向を傾斜させて注入すると、原子間の隙間を少なくすることができるため、導入された不純物が結晶の表面近傍でとどまる。

#### 【0078】

ゲート電極504の周囲には凹凸部分が存在するため、不純物や質量が重い元素が導入されない領域が生じやすくなる (シャドー効果という) ため、その防止策として、(1) 単結晶半導体基板500を回転させながら不純物や質量が重い元素の導入を行う、(2) 所定の時間や角度毎に回転を中断し、そのときに不純物や質量が重い元素の導入を行うなどの方法をとることができる。単結晶半導体基板500に対して不純物や質量の重い原子の注入方向を相対的に斜めにし、さらに単結晶半導体基板500を回転させながら不純物や質量の重い元素の注入を行うと、チャネリング現象とシャドー効果の予防が同時にできるため、より好ましい。

30

#### 【0079】

その後、導入した不純物元素を極浅かつ高濃度のプロファイルのまま活性化するために、本発明によるレーザアニールを行う。

#### 【0080】

本実施例では、エネルギー10W、TEM<sub>00</sub>の発振モード、第2高調波 (532nm)、発振周波数160MHz、パルス幅10psのYVO<sub>4</sub>レーザを用いる。なお、この照射条件に限定されるものではなく、本発明は、パルス幅は1fs～10psとし、波長は370～640nm、好ましくは400～540nmの範囲内で射出するレーザを用いることができる。この理由は、図3に示すように、370～640nmの波長領域において、単結晶半導体の吸収係数よりもアモルファス化した半導体の吸収係数の方が大きい。特に、400～540nmでは、単結晶半導体とアモルファス化した半導体の吸収係数には大きな差が見られる。このため、この波長領域のレーザを用いることによって、アモルファス化した半導体に選択的にレーザが吸収されやすくなる。

40

#### 【0081】

本発明のレーザ発振器として用いることができるのは、例えば、Sapphire、Y

50

AG、セラミックスYAG、セラミックスY<sub>2</sub>O<sub>3</sub>、KGW、KYW、Mg<sub>2</sub>SiO<sub>4</sub>、YLF、YVO<sub>4</sub>、GdVO<sub>4</sub>などの結晶に、Nd、Yb、Cr、Ti、Ho、Erなどのドーパントを添加したレーザなどが挙げられる。

【0082】

なお、レーザ発振器は、370～640nmの範囲内、好ましくは400～540nmで発振するように、必要に応じて非線形光学素子を用いて第2高調波、または第3高調波以上の高調波に変換する。例えば、レーザ発振器から発振されたレーザビームの基本波長が1μm程度の赤外領域にある場合は、非線形光学素子により第2高調波(532nm程度)に変換し用いることができる。

【0083】

レーザ発振器は安定形共振器とし、TEM<sub>00</sub>(シングル横モード)の発振モードであることが望ましい。TEM<sub>00</sub>モードの場合、レーザビームはガウス型の強度分布を持ち、集光性に優れているため、ビームスポットの加工が容易となる。

【0084】

なお、TEM<sub>00</sub>の発振モードはガウス型の強度分布を持つため、ビームの両端部分は中心部に比べて強度が弱い。そこで、この強度の弱い部分をスリットで遮断するとよい。スリットを用いることによって、強度の弱い部分を遮断することができ、照射面におけるレーザビームの長軸方向の長さを調節することができる。本発明において、スリットの有無、材質などについては特に制限されることはない。スリットを使用する場合は、スリットを通してした際に強度の弱い部分を遮断できる構造または形状のものを使用することができる。

【0085】

また、シリンドリカルレンズやシリンドリカルレンズアレイ、フライアイレンズ、ライトパイプ、回折光学素子(ディフラクティブオプティクス)などを用いたビームホモジナイザを用いることによって、ビームを均一化しても良い。また、ビームホモジナイザとスリットと組み合わせても良い。

【0086】

なお、被照射物上に形成されるビームスポットは、光学系を用いることによって所望の形状にすることが可能であるが、ビームの形状をアスペクト比の高い線状、矩形状、または橢円状にすると、スループット良くビームを照射することができるため、より好ましい。

【0087】

こうしてレーザアニールを行い、添加した不純物元素を活性化させると同時に不純物添加によって形成された結晶欠陥を低減する。本実施例では532nmの波長を選択することでアモルファス化したエクステンション領域509にのみレーザビームのエネルギーが吸収され、選択的に加熱することができる。また、パルス幅が1fs～10psの超短パルスであるため、不純物の拡散を抑えることができる。さらに、発振周波数が10MHzを超えるレーザを用いているため、処理時間を短縮することが可能である。

【0088】

以上より、エクステンション領域509を浅く保つことができ、本発明を用いて作製した半導体装置は、短チャネル効果の抑制及び電界集中の緩和などの効果が得られる。

【0089】

この後、図5(F)に示すように、エッチングにより窒化珪素膜503を選択的に除去する。さらに、この後に適宜工程を行うことで半導体装置を作製することができる。本発明を用いて作製された半導体装置は、その電気的特性が良好なものとなり、動作特性も大幅に向上する。

【0090】

本実施例は、他の実施例と組み合わせることが可能である。また、ガラス基板、石英基板、有機樹脂製基板などの絶縁物質上に半導体膜を形成した基板を用いて薄膜トランジスタを作製する際にも、同様に用いることが可能である。

10

20

30

40

50

## 【実施例3】

## 【0091】

本実施例では、半導体素子の作製方法について、図面を参照して説明する。なお、本実施例では、単結晶シリコン基板を用い、CMOS型のICを作製する例を示す。

## 【0092】

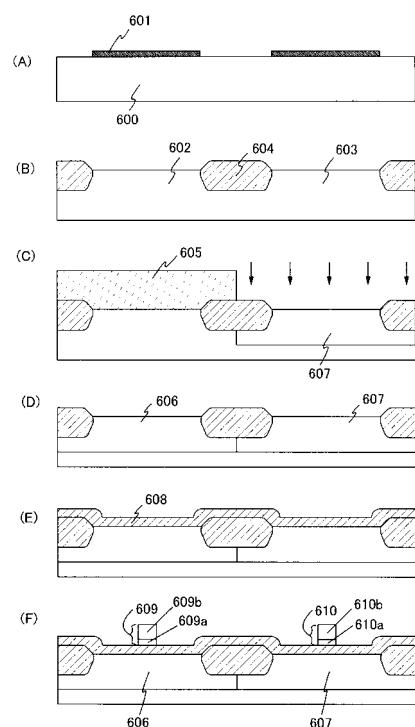

まず、単結晶シリコンからなる基板600を用意し、公知のLOCOS法またはシャロートレンチ分離法(STI法: Shallow Trench Isolation)を用いて、第1の素子形成領域602と第2の素子形成領域603を形成する。

## 【0093】

具体的には、単結晶シリコン基板600を上に窒化珪素膜601を堆積する。後に活性領域となる部分を残して窒化珪素膜601を除去する(図6(A))。

## 【0094】

そして、窒化珪素膜602をマスクにして、熱酸化法により厚い分離用の酸化珪素膜(フィールド酸化膜)604を形成する。次に、窒化珪素膜を熱リン酸で除去することによって、フィールド酸化膜604によって分離された第1の素子領域602および第2の素子領域603が形成される(図6(B))。

## 【0095】

ここで用いる単結晶半導体基板600は、例えば貼り合わせ法またはSIMOX(Separation by Implanted Oxygen)法を用いて作製されたSOI(Silicon on Insulator)基板、シリコンウエハーなどを用いることができる。SOI基板を用いて半導体素子を作製すると、隣接する素子を完全に分離することができ、リーク電流が流れるのを防ぐことができる。

## 【0096】

次に、第1の素子形成領域602にレジスト605で覆い、後にPチャネル型MOSトランジスタが形成される部分である第2の素子形成領域603にリンをイオン注入し、p型ウェル607を形成する。同様にして、後にNチャネル型MOSトランジスタが形成される部分である第1の素子形成領域602にn型ウェル606を形成させる。(図6(C))。

## 【0097】

次に、レジスト605を剥離し、第1の素子形成領域602、第2の素子形成領域603の表面を露出させる(図6(D))。その後、この表面に熱酸化法で酸化珪素を材料とする薄いゲート絶縁膜608を形成させる(図6(E))。

## 【0098】

ゲート絶縁膜608の形成方法は、プラズマCVD法やスパッタ法などを用いればよい。例えば、熱酸化法によって得られる膜厚5nmの酸化珪素膜と、CVD法で得られる膜厚10~15nmの酸化窒化珪素膜の積層膜を形成してもよい。また、ガスを切り替えることによって連続的に成膜を行うこともできる。

## 【0099】

なお、ゲート絶縁膜608は上記の材料に限らず、(1)酸化珪素膜、窒化酸化珪素膜(Si<sub>x</sub>N<sub>y</sub>(xとyはx>yを満たす1以上の自然数))、酸化窒化珪素膜(Si<sub>x</sub>O<sub>y</sub>(xとyはx>yを満たす1以上の自然数))、窒化酸化膜、またはこれらの積層膜、(2)高誘電率物質(high-k材料ともいう)のタンタル酸化物、酸化ハフニウム(HfO<sub>2</sub>)、窒化ハフニウムシリゲート(HfSiON)、酸化ジリコニウム(ZrO<sub>2</sub>)、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、または酸化ランタン(La<sub>2</sub>O<sub>3</sub>)などの希土類酸化物を用いることができる。

## 【0100】

次に、ポリシリコン層とシリサイド層との積層膜を全面に形成し、リソグラフィ技術とドライエッチング技術を用いて、この積層膜を所定の形状に整形する。この処理によって、ゲート絶縁膜608上にポリサイド構造を有するゲート電極609、610が形成される(図6(F))。ポリシリコン層609a、610aは低抵抗化するために、予め1×

10

20

30

40

40

50

$10^{21}$  atoms/cm<sup>3</sup> 程度の濃度でリン(P)をドープしておいてもよいし、シリコン層を形成する際にリンなどのn型不純物を添加してもよい。また、シリサイド層609b、610bを形成する材料は、モリブデンシリサイド(MoSi<sub>x</sub>)、タングステンシリサイド(WSi<sub>x</sub>)、タンタルシリサイド(TaSi<sub>x</sub>)、チタンシリサイド(TiSi<sub>x</sub>)などを適用することが可能であり、公知の方法に従って形成することができる。

#### 【0101】

なお、ゲート絶縁膜608を先述の高誘電率物質(high-k材料)を用いて形成した場合、ゲート電極609、610には、金属、または金属を主成分とした材料を用いることが望ましい。金(Au)、銀(Ag)、銅(Cu)、白金(Pt)、アルミニウム(Al)、モリブデン(Mo)、タングステン(W)、チタン(Ti)、タンタル(Ta)から選ばれた元素、またはこれらの元素を主成分とする合成材料または化合物材料を用いることができる。さらには、これらの材料の積層物を用いてもよい。その一例として、タングステン(W)と窒化タンタル(TaN)の積層膜、アルミニウム(Al)とモリブデン(Mo)の積層膜を挙げることができる。これらの材料を用いてゲート絶縁膜608とゲート電極609、610を形成することによって、ゲート電極の空乏化を解消し、大量の電流を流すことができるようになり、半導体素子の低電力化に貢献する。

#### 【0102】

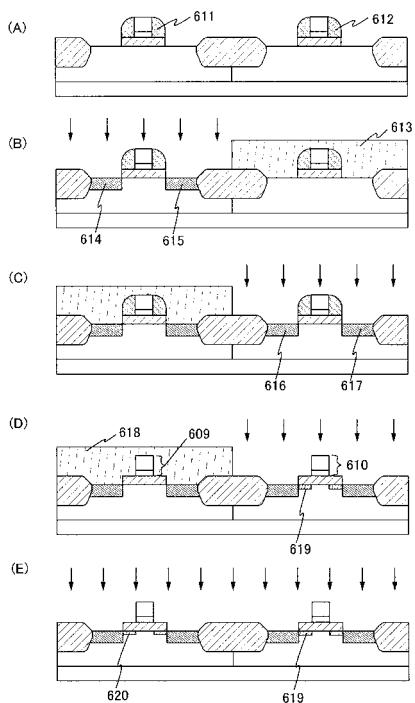

次に、図7(A)に示すように、ゲート電極609、610の側壁にサイドウォール611、612を形成する。例えば酸化珪素からなる絶縁膜を基板全面にCVD法にて形成する。この絶縁膜に異方性エッティングを行うことによって、サイドウォールを形成すればよい。

#### 【0103】

次いで、ソース領域およびドレイン領域を形成するために、シリコン基板にイオン注入を行う(図7(B))。CMOSを形成する場合であるので、pチャネル型FETを形成する第2の素子形成領域603をレジスト613で覆い、n型不純物のヒ素(As)、リン(P)、またはアンチモン(Sb)を第1の素子形成領域602に注入する。この操作によって、ソース領域614、ドレイン領域615が形成される。また、同様にしてnチャネル型FETを形成する第1の素子形成領域602をレジストで覆い、p型不純物であるホウ素(B)を第2の素子形成領域603に注入し、ソース領域616、ドレイン領域617を形成する(図7(C))。

#### 【0104】

さらに、イオン注入された不純物の活性化および、イオン注入によって発生したシリコン基板の結晶欠陥を回復するために、第1回目の活性化処理を行う。なお、第1回目の活性化処理はRTA法、レーザアニール法などの公知の方法にて行ってよい。

#### 【0105】

次に、サイドウォール611、612を、エッティング処理などを用いて選択的に除去する。次に、n型FETになる部分をレジスト618で覆い、p型の導電性を示すイオンの注入を行う(図7(D))。ここで、リン、ヒ素、またはアンチモンのいずれかのイオンをイオン注入に用いることができる。この処理により、エクステンション領域619を形成する。同様にして、p型FETになる部分をレジストで覆い、n型の導電性を有するイオンの注入を行い、エクステンション領域620を形成する。ホウ素イオンをイオン注入に用いることができる。ここで、チャネル領域と、ソース領域またはドレイン領域との間に形成された不純物領域をエクステンション領域という。エクステンション領域619および620は、ソース領域614、616やドレイン領域615、617よりもごく浅く形成する。エクステンション領域619、620の不純物濃度は、ソース領域やドレイン領域の不純物濃度より低い場合も高い場合も同等の場合もある。すなわち、エクステンション領域の不純物濃度は、半導体装置に要求される特性に基づいて決定すればよい。

#### 【0106】

ここで、不純物元素を注入するのと同時に、ゲルマニウム(Ge)や0族の元素(Ar)

10

20

30

40

50

、K r、X e、R nなど)などの質量が重い原子を打ち込み、単結晶の格子を崩す。この際、打ち込む速度を下げ、20 nm程度までアモルファス化する。不純物の導入と重い原子の打ち込みの順番は限定されるものではない。どちらを先にしても良いし、同時に行つても良い。

【0107】

シリコン基板600は原子が整然と配列している。特に<100>面や<111>面の場合では、導入された不純物が結晶の隙間を通り、奥深くまで到達してしまう現象(チャネリング現象)が起きる。そこで、シリコン基板600に対して不純物の導入方向を傾斜させて注入すると、原子間の隙間を少なくすることができるため、導入された不純物が結晶の表面近傍でとどまりやすくなる。

10

【0108】

また、ゲート電極609、610の周囲には凹凸部分が存在するため、不純物や質量が重い元素が導入されない領域が生じやすくなる(シャドー効果という)。その防止として、(1)シリコン基板600を回転させながら不純物や質量が重い元素の導入を行う、(2)所定の時間や角度毎に回転を中断し、そのときに不純物や質量が重い元素の導入を行う、などの方法をとることができる。シリコン基板600に対して不純物や質量の重い原子の注入方向を相対的に斜めにし、さらにシリコン基板600を回転させながら不純物や質量の重い元素の注入を行うと、チャネリング現象とシャドー効果の予防が同時にできるため、より好ましい。

【0109】

20

次に、イオン注入された不純物の活性化およびイオン注入によって発生したシリコン基板の結晶欠陥を回復するために、第2回目の活性化処理を行う(図7(E))。第2回目の活性化処理は、パルス幅が1 fs ~ 10 ps、波長が370 ~ 640 nm、好ましくは400 ~ 540 nmの波長を持つレーザビームをアモルファス化したエクステンション領域を含む半導体基板に照射することによってエクステンション領域を活性化する。

【0110】

この理由は、370 ~ 640 nm、特に400 ~ 540 nmの波長領域では、単結晶の半導体の吸収係数よりアモルファス化した半導体の吸収係数の方が高く、その吸収係数の差も大きい。そのため、アモルファス化した半導体にほぼ選択的に吸収されるからである。従って、ソース領域やドレイン領域よりごく浅く形成されたアモルファス化したシリコン膜、すなわちエクステンション領域619、620の部分を含むごく浅い領域にレーザが吸収される。

30

【0111】

また、本実施例で用いるレーザは、パルス幅が1 fs ~ 10 psと非常に短いため、エクステンション領域が加熱される時間を非常に短くすることができる。そのため、RTA法と比較して不純物の拡散を大幅に抑えることができる。このような構成によって、ごく浅くエクステンション領域を形成することが可能になるため、電界集中が緩和され、短チャネル効果が抑制される。

【0112】

また、発振周波数が10 MHz以上のレーザを用いて照射を行うことにより、処理時間を短縮することができる。

40

【0113】

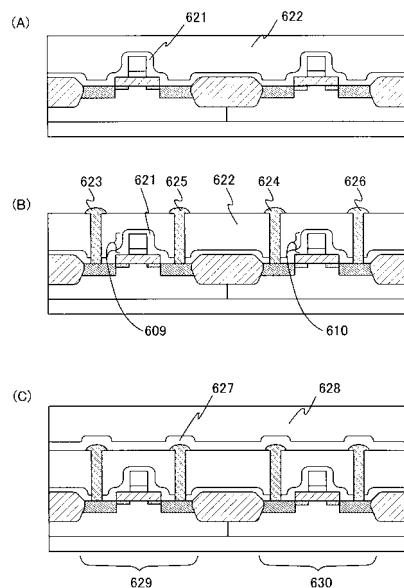

次に、活性化後に層間絶縁膜や配線などを形成する。図8(A)に示すように、第1の層間絶縁膜621は、プラズマCVD法や減圧CVD法を用いて、酸化シリコン膜や酸化窒化シリコン膜などで、100 ~ 2000 nmの厚さに形成する。さらにその上にリンガラス(PSG)、ボロンガラス(BSG)、またはリンボロンガラス(PBSG)からなる第2の層間絶縁膜622を形成する。第2の層間絶縁膜622は、平坦性を上げるため、スピンドル法や常圧CVD法を用いて作製する。

【0114】

続いて、図8(B)に示すように、第1の層間絶縁膜621および第2の層間絶縁膜6

50

22に、それぞれFETのソース領域およびドレイン領域に達するコンタクトホール（開口）を形成し、ソース電極623、624およびドレイン電極625、626を形成する。ソース電極623、624およびドレイン電極625、626の材料は、低抵抗材料として通常用いられるアルミニウム（A1）、アルミニウムとチタン（Ti）の積層物などを用いることができる。

【0115】

また、ここでは図示していないが、ソース電極623、624およびドレイン電極625、626を形成するためのコンタクトホールを開口する際に、第1の層間絶縁膜621および第2の層間絶縁膜622に、ゲート電極609、610に達するコンタクトホールも同時に設け、第1の層間絶縁膜621上に設けられている配線と電気的に接続する電極が設けられる。

10

【0116】

最後に、図8（C）に示すように、パッシベーション膜627と第3の層間絶縁膜628を形成する。図8において、向かって左側がNチャネル型FET629であり、右側がPチャネル型FET630である。

【0117】

パッシベーション膜627は、プラズマCVD法で窒化シリコン膜、酸化シリコン膜、または窒化酸化シリコン膜で形成されている。さらに、第3の層間絶縁膜628は、有機樹脂材料で1~2μmの厚さに形成する。ここで用いる有機樹脂材料とは、ポリイミド、ポリアミド、アクリル、ベンゾシクロブテン（BCB）などを用いることができる。有機樹脂膜を用いる利点は、膜の形成が容易である点や、比誘電率が低いため寄生容量を低減できる点、膜の平坦化が容易である点などがある。なお、上述した以外の有機樹脂膜を用いてもよい。

20

【0118】

本発明を用いることにより、エクステンション領域をごく浅く形成することによって、短チャネル効果が抑制され、電界集中が緩和される。従って、高速で動作し、良好な性能を持つ小型の半導体装置を作製することができる。

【0119】

なお、本実施例は実施の形態および他の実施例と組み合わせて用いることが可能である。

30

【実施例4】

【0120】

本発明を用いて作製したMOSFETを用いて、さまざまな半導体装置を完成させることができる。本実施例では、本発明のMOSFETを用いたCPUの例を示す。

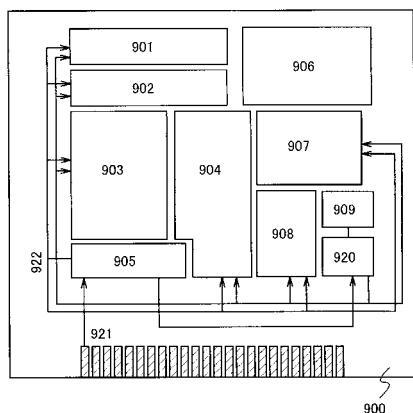

【0121】

図9に示すCPUは、基板900上に、演算回路（ALU：Arithmetic logic unit）901、演算回路用の制御部（ALU Controller）902、命令解析部（Instruction Decoder）903、割り込み制御部（Interrupt Controller）904、タイミング制御部（Timing Controller）905、レジスタ（Register）906、レジスタ制御部（Register Controller）907、バスインターフェース（Bus I/F）908、書き換え可能なROM909、ROMインターフェース（ROM I/F）920を主に有している。またROM909及びROMインターフェース（ROM I/F）920は、別チップに設けても良い。

40

【0122】

勿論、図9に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

【0123】

バスインターフェース908を介してCPUに入力された命令は、命令解析部903に入力され、デコードされた後、演算回路用の制御部902、割り込み制御部904、レジ

50

スタ制御部 907、タイミング制御部 905 に入力される。

【0124】

演算回路用の制御部 902、割り込み制御部 904、レジスタ制御部 907、タイミング制御部 905 は、デコードされた命令に基づき、各種制御を行う。具体的に演算回路用の制御部 902 は、演算回路 901 の動作を制御するための信号を生成する。また、割り込み制御部 904 は、CPU のプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタ制御部 907 は、レジスタ 906 のアドレスを生成し、CPU の状態に応じてレジスタ 906 の読み出しや書き込みを行う。

【0125】

また、タイミング制御部 905 は、演算回路 901、演算回路用の制御部 902、命令解析部 903、割り込み制御部 904、レジスタ制御部 907 の動作のタイミングを制御する信号を生成する。例えば、タイミング制御部 905 は、基準クロック信号 CLK1 (921) を元に、内部クロック信号 CLK2 (922) を生成する内部クロック生成部を備えており、クロック信号 CLK2 を上記各種回路に供給する。

【0126】

本発明を用いて CPU を構成する MOSFET を形成する際に、エクステンション領域の深さを浅く作ることができる。そのため、短チャネル効果の抑制や電界集中の緩和が得られ、安定した CPU の動作を得ることができる。また、CPU のさらなる微細化を進展させることができになる。

【0127】

なお、本実施例は、実施の形態や他の実施例と自由に組み合わせることができる。

【実施例 5】

【0128】

本発明を用いて作製した MOSFET を集積化した CPU として搭載し、さまざまな電子機器を完成させることができる。

【0129】

そのような電子機器として、デジタルビデオカメラ、デジタルカメラ、反射型プロジェクター、テレビ（ディスプレイ）、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（オーディオ）、携帯端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機、電子書籍）、ゲーム機器、記録媒体を備えた画像再生装置（具体的には Digital Versatile Disk (DVD) やハードディスクドライブ (HDD) 等の記録媒体に記録された情報を再生し、その画像を表示することができるディスプレイと CPU を供えた機器などを挙げることができる。

【0130】

本発明の電子機器の一つである携帯電話を例に挙げ、以下に説明する。

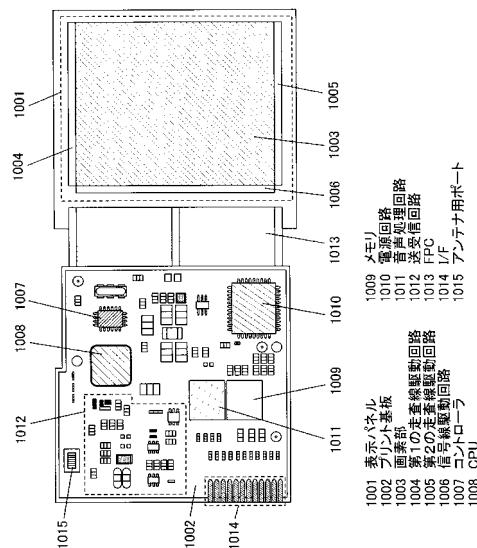

【0131】

図 10 は表示パネル 1001 とプリント配線基板 1002 を組み合わせたモジュールを示している。表示パネル 1001 は、発光素子が各画素に設けられた画素部 1003 と、第 1 の走査線駆動回路 1004、第 2 の走査線駆動回路 1005 と、選択された画素にビデオ信号を供給する信号線駆動回路 1006 を備えている。また、表示パネルに用いる素子は、発光素子に限らず、液晶素子を用いてもよい。

【0132】

プリント基板 1002 には、コントローラ 1007、中央処理装置（CPU）1008、メモリ 1009、電源回路 1010、音声処理回路 1011 及び送受信回路 1012 などが備えられている。プリント基板 1002 と表示パネル 1001 は、フレキシブル配線基板（FPC）1013 により接続されている。プリント配線基板 1013 には、容量素子、バッファ回路などを設け、電源電圧や信号にノイズが入ったり、信号の立ち上がりが鈍ったりすることを防ぐ構成としても良い。また、コントローラ 1007、音声処理回路 1011、メモリ 1009、CPU 1008、電源回路 1010 などは、COG (Chi

10

20

30

40

50

p on Glass) 方式を用いて表示パネル 1001 に実装することもできる。CO G 方式により、プリント基板 1002 の規模を縮小することができる。

【0133】

プリント基板 1002 に備えられたインターフェース (I/F) 部 1014 を介して、各種制御信号の入出力が行われる。また、アンテナとの間の信号の送受信を行うためのアンテナ用ポート 1015 が、プリント基板 1002 に設けられている。

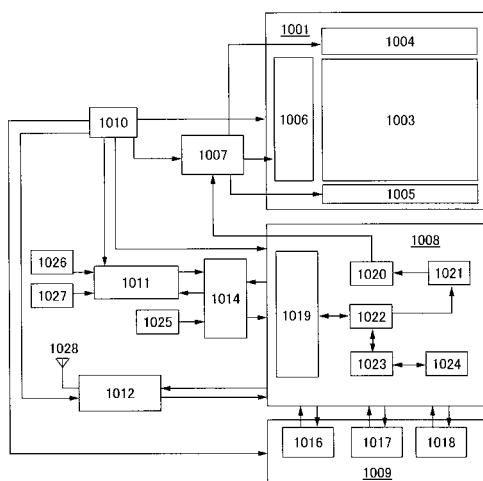

【0134】

図 11 は、図 10 に示したモジュールのブロック図を示す。このモジュールは、メモリ 1009 として VRAM 1016、DRAM 1017、フラッシュメモリ 1018 などが含まれている。VRAM 1016 にはパネルに表示する画像のデータが、DRAM 1017 には画像データまたは音声データが、フラッシュメモリには各種プログラムが記憶されている。

【0135】

電源回路 1010 は、表示パネル 1001、コントローラ 1007、CPU 1008、音声処理回路 1011、メモリ 1009、送受信回路 1012 を動作させる電力を供給する。またパネルの仕様によっては、電源回路 1010 に電流源が備えられている場合もある。

【0136】

CPU 1008 は、制御信号生成回路 1020、デコーダ 1021、レジスタ 1022、演算回路 1023、RAM 1024、CPU 1008 用のインターフェース 1019 などを有している。インターフェース 1019 を介して CPU 1008 に入力された各種信号は、一旦レジスタ 1022 に保持された後、演算回路 1023、デコーダ 1021 などに入力される。演算回路 1023 では、入力された信号に基づき演算を行い、各種命令を送る場所を指定する。一方デコーダ 1021 に入力された信号はデコードされ、制御信号生成回路 1020 に入力される。制御信号生成回路 1020 は入力された信号に基づき、各種命令を含む信号を生成し、演算回路 1023 において指定された場所、具体的にはメモリ 1009、送受信回路 1012、音声処理回路 1011、コントローラ 1007 などに送る。

【0137】

メモリ 1009、送受信回路 1012、音声処理回路 1011、コントローラ 1007 は、それぞれ受けた命令に従って動作する。以下その動作について簡単に説明する。

【0138】

入力手段 1025 から入力された信号は、インターフェース 1014 を介してプリント基板 1002 に実装された CPU 1008 に送られる。制御信号生成回路 1020 は、ポインティングデバイスやキーボードなどの入力手段 1025 から送られてきた信号に従い、VRAM 1016 に格納してある画像データを所定のフォーマットに変換し、コントローラ 1007 に送付する。

【0139】

コントローラ 1007 は、パネルの仕様に合わせて CPU 1008 から送られてきた画像データを含む信号にデータ処理を施し、表示パネル 1001 に供給する。またコントローラ 1007 は、電源回路 1010 から入力された電源電圧や CPU 1008 から入力された各種信号をもとに、H sync 信号、V sync 信号、クロック信号 CLK、交流電圧 (AC Cont)、切り替え信号 L/R を生成し、表示パネル 1001 に供給する。

【0140】

送受信回路 1012 では、アンテナ 1028 において電波として送受信される信号が処理されており、具体的にはアイソレータ、バンドパスフィルタ、VCO (Voltage Controlled Oscillator)、LPF (Low Pass Filter)、カプラ、バランなどの高周波回路を含んでいる。送受信回路 1012 において送受信される信号のうち音声情報を含む信号が、CPU 1008 からの命令に従って、音声処理回路 1011 に送られる。

10

20

30

40

50

## 【0141】

CPU1008の命令に従って送られてきた音声情報を含む信号は、音声処理回路1011において音声信号に復調され、スピーカー1027に送られる。またマイク1026から送られてきた音声信号は、音声処理回路1011において変調され、CPU1008からの命令に従って、送受信回路1012に送られる。

## 【0142】

コントローラ1007、CPU1021、電源回路1010、音声処理回路1011、メモリ1009を、本実施例のパッケージとして実装することができる。本実施例は、アイソレータ、バンドパスフィルタ、VCO(Voltage Controlled Oscillator)、LPF(Low Pass Filter)、カプラ、バランなどの高周波回路以外であれば、どのような回路にも応用することができる。10

## 【0143】

本発明を用いて作製した半導体素子は、短チャネル効果の抑制及び電界集中の緩和などの効果を持つ。従って、この半導体素子を集積してCPUを作製すると、省電力で動作が良好な小型のCPUを作製することができる。そのため、限られた領域に配置する必要性が小さな電子機器に用いることが可能である。

## 【0144】

また、本実施例は実施の形態および他の実施例と組み合わせて用いることが可能である。20

## 【実施例6】

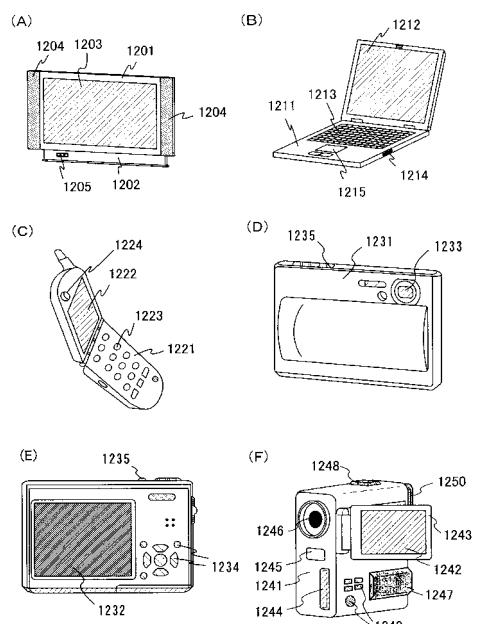

## 【0145】

本発明を用いて作製したFETを集積したICチップとして搭載し、様々な電子機器を完成させることができる。その具体例を、図を用いて説明する。

## 【0146】

本発明を用いることによって、基板上のFETが有するエクステンション領域を浅く作ることができるため、短チャネル効果の抑制や電界集中の緩和を達成できる。従って、本発明を用いて作製した半導体装置の電気特性は良好であり、動作特性も大幅に向上する。

## 【0147】

図12(A)は表示装置であり、筐体1201、支持台1202、表示部1203、スピーカー部1204、ビデオ入力端子1205などを含む。この表示装置は、他の実施例で示した作製方法により形成したFETを駆動ICに用いることにより作製される。なお、表示装置には液晶表示装置、発光表示装置などがあり、具体的にはコンピュータ用、テレビ受信用、広告表示用などの全ての情報表示用表示装置が含まれる。30

## 【0148】

図12(B)はコンピュータであり、筐体1211、表示部1212、キーボード1213、外部接続ポート1214、ポインティングマウス1215などを含む。本発明によって形成されたFETは表示用の駆動IC、本体内部のCPU、メモリなどの半導体装置にも適用が可能である。

## 【0149】

また、図12(C)は携帯電話であり、携帯端末の1つの代表例である。この携帯電話は筐体1221、表示部1222、操作キー1223などを含む。本発明によって形成されたFETは表示用の駆動IC、メモリ、音声処理回路などに用いることができる。さらに、センサ部1224は光センサ素子を有しており、センサ部1224で得られる照度に合わせて表示部1222の輝度コントロールを行ったり、センサ部1224で得られる照度に合わせて操作キー1223の照明制御を抑えたりすることによって、携帯電話の消費電力を抑えることができる。40

## 【0150】

上記の携帯電話を始めとして、PDA(Personal Digital Assistants、情報携帯端末)、デジタルカメラ、小型ゲーム機などの電子機器に、本発明のレーザ照射を行った半導体材料を用いることもできる。例えば、CPU、メモリ、セ50

ンサなどの機能回路を形成することができ、小型・軽量を図ることができる。また、それぞれの機能回路において短チャネル効果の抑制や電界集中を緩和する効果を持つため、省電力化に大きく寄与する。

【0151】

また、図12(D)、(E)はデジタルカメラである。なお、図12(E)は、図12(D)の裏側を示す図である。このデジタルカメラは、筐体1231、表示部1232、レンズ1233、操作キー1234、シャッター1235などを有する。本発明によって形成されたFETは、表示部1232を駆動する駆動ICやメモリなどに用いることができる。

【0152】

図12(F)はデジタルビデオカメラである。このデジタルビデオカメラは、本体1241、表示部1242、筐体1243、外部接続ポート1244、リモコン受信部1245、受像部1246、バッテリー1247、音声入力部1248、操作キー1249、接眼部1250などを有する。本発明を用いて形成されたFETは、表示部2242を制御する駆動IC、メモリ、デジタル入力処理装置などに用いることができる。

【0153】

また、本発明を用いて作製したFETを薄膜集積回路、または非接触型薄膜集積回路装置(無線ICタグ、RFID(無線認証、Radio Frequency Identification)とも呼ばれる)として用いることもできる。他の実施例で示した作製方法を用いることにより、薄膜集積回路および非接触型薄膜集積回路は、タグとしての利用やメモリとしての利用が可能である。

【0154】

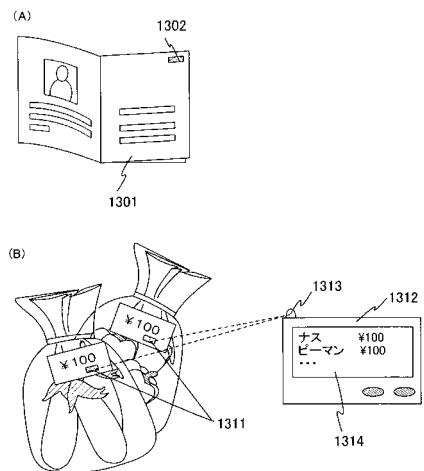

図13(A)は、パスポート1301に無線ICタグ1302を貼り付けている状態を示している。また、パスポート1301に無線ICタグ1302を埋め込んでもよい。同様にして、運転免許証、クレジットカード、紙幣、硬貨、証券、商品券、チケット、トラベラーズチェック(T/C)、健康保険証、住民票、戸籍謄本などへの無線ICタグの貼り付けや埋め込みができる。この場合、本物であることを示す情報を無線ICタグに入力しておき、不正に情報を読み取ったり書き込んだりできないようにアクセス権を設定する。これは、他の実施例で示したメモリを用いることにより実現できる。このようにタグとして利用することによって、偽造されたものと区別することが可能になる。

【0155】

このほかに、無線ICタグをメモリとして用いることも可能である。図13(B)は、無線ICタグ1311を野菜の包装に貼り付けるラベルに埋め込んだ例を示している。また、包装そのものに無線ICタグを貼り付けたり埋め込んだりしても構わない。無線ICタグ1311には、生産地、生産者、製造年月日、加工方法などの生産段階のプロセスや、商品の流通プロセス、価格、数量、用途、形状、重量、賞味期限、各種認証情報などを記録することができる。無線ICタグ1311からの情報は、無線式のリーダ1312のアンテナ部1313で受信して読み取り、リーダ1312の表示部1314に表示することによって、卸売り業者、小売り業者、消費者が把握することが容易になる。また、生産者、取引業者、消費者のそれぞれに対してアクセス権を設定することによって、アクセス権を有しない場合は読み込み、書き込み、書き換え、消去ができない仕組みになっている。

【0156】

また、無線ICタグは以下のように用いることができる。会計の際に無線ICタグに会計を済ませたことを記入し、出口にチェック手段を設け、会計済みであることを無線ICタグに書き込まれているかをチェックする。会計を済ませていないで店を出ようとすると、警報が鳴る。この方法によって、会計のし忘れや万引きを予防することができる。

【0157】

さらに、顧客のプライバシー保護を考慮すると、以下に記す方法にすることも可能である。レジで会計をする段階で、(1)無線ICタグに入力されているデータを暗証番号など

10

20

30

40

50

でロックする、(2)無線ICタグに入力されているデータそのものを暗号化する、(3)無線ICタグに入力されているデータを消去する、(4)無線ICタグに入力されているデータを破壊する、のいずれかを行う。これらは、他の実施例にて挙げたメモリを用いることによって実現することができる。そして、出口にチェック手段を設け、(1)~(4)のいずれかの処理が行われたか、または無線ICタグのデータに何も処理が行われていない状態であるかをチェックすることによって、会計の有無をチェックする。このようにすると、店内では会計の有無を確認することが可能であり、店外では所有者の意志に反して無線ICタグの情報を読み取られることを防止することができる。

#### 【0158】

なお、(4)の無線ICタグに入力されているデータを破壊する方法をいくつか挙げることができる。例えば、(a)無線ICタグが有する電子データの少なくとも一部に「0(オフ)」若しくは「1(オン)」、または「0」と「1」の両方を書き込んでデータのみを破壊する方法や、(b)無線ICタグに電流を過剰に流し、無線ICタグが有する半導体素子の配線の一部を物理的に破壊する方法などを用いることができる。

10

#### 【0159】

以上に挙げた無線ICタグは、従来用いているバーコードより製造コストが高いため、コスト低減を図る必要がある。本発明を用いることによって、短チャネル効果を抑えつつ、さらなる微細化を図ることができ、無線ICタグに設けられたICチップの小型化を実現することができる。ICチップは大きさが小さくなるほど耐衝撃強度が増すため、信頼性が向上する。さらに、本発明を用いることにより、どの無線ICタグも品質が高く、性能のばらつきがないように製作することができる。

20

#### 【0160】

以上のように、本発明により作製された半導体装置の適用範囲は極めて広く、本発明により作製された半導体装置をあらゆる分野の電子機器に用いることができる。

#### 【0161】

また、本発明により、半導体集積回路のさらなる微細化を進めることができるために、ICの高度集積化を進めることができる。そのため、ウェハー1枚あたりのチップ数を増やすことができる。

#### 【0162】

また、本実施例は実施の形態および他の実施例と組み合わせて用いることが可能である。

30

#### 【図面の簡単な説明】

#### 【0163】

【図1】本発明の実施の形態を表す図である。

【図2】従来例を表す図である。

【図3】単結晶シリコンとアモルファスシリコンの吸収係数の波長依存性を示すグラフである。

【図4】本発明に用いるレーザ照射装置の一例を示す図である。

【図5】本発明の実施の形態を示す図である。

【図6】本発明の実施の形態を示す図である。

40

【図7】本発明の実施の形態を示す図である。

【図8】本発明の実施の形態を示す図である。

【図9】本発明の実施の形態を示す図である。

【図10】本発明の実施の形態を示す図である。

【図11】本発明の実施の形態を示す図である。

【図12】本発明を用いて作製した電子機器の例を示す図である。

【図13】本発明を用いて作製した電子機器の例を示す図である。

【図1】

【図2】

【図3】

a-Siとpoly-Siの吸収係数 (測定: 分光エリブソメトリー)

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

|     |          |     |             |

|-----|----------|-----|-------------|

| 900 | 基板       | 907 | レジスタ制御部     |

| 901 | 演算回路     | 908 | バスインターフェイス  |

| 902 | 演算回路用制御部 | 909 | ROM         |

| 903 | 命令解析部    | 920 | ROMインターフェイス |

| 904 | 割り込み制御部  | 921 | CLK1        |

| 905 | タイミング制御部 | 922 | CLK2        |

| 906 | レジスタ     |     |             |

【図10】

|      |            |      |          |

|------|------------|------|----------|

| 1001 | 表示パネル      | 1009 | メモリ回路    |

| 1002 | プリント基板     | 1010 | 電源回路     |

| 1003 | センサ部       | 1011 | 電源処理回路   |

| 1004 | 第1の走査線駆動回路 | 1012 | 送受信回路    |

| 1005 | 第2の走査線駆動回路 | 1013 | FPC      |

| 1006 | 信号線駆動回路    | 1014 | J/F      |

| 1007 | コントローラ     | 1015 | アンテナ用ポート |

| 1008 | CPLD       |      |          |

【 1 1 】

|      |            |      |          |

|------|------------|------|----------|

| 1001 | 表示パネル      | 1017 | DRAM     |

| 1003 | 画素部        | 1018 | フラッシュメモリ |

| 1004 | 第1の走査線駆動回路 | 1019 | インターフェース |

| 1005 | 第2の走査線駆動回路 | 1020 | 制御信号生成回路 |

| 1006 | 信号線駆動回路    | 1021 | DCモータ    |

| 1007 | コントローラ     | 1022 | レジスタ     |

| 1008 | CPU        | 1023 | 演算回路     |

| 1009 | メモリ        | 1024 | RAM      |

| 1010 | 電源回路       | 1025 | 入力手段     |

| 1011 | 音声処理回路     | 1026 | マイク      |

| 1012 | 送受信回路      | 1027 | スピーカー    |

| 1014 | I/F        | 1028 | アンテナ     |

| 1016 | VRAM       |      |          |

【 义 1 2 】

## 【図 1 3】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/092 (2006.01) H 01 L 21/265 602C

H 01 L 27/08 321C

(56)参考文献 特開2002-329864 (JP, A)

特開2004-152888 (JP, A)

特開2004-063924 (JP, A)

特開2004-342875 (JP, A)

特開2004-343093 (JP, A)

特開2001-338894 (JP, A)

特開昭63-046774 (JP, A)

特開2003-282697 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29/78

H 01 L 21/265

H 01 L 21/336

H 01 L 21/8238

H 01 L 27/092

H 01 L 29/786