(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-26625

(P2013-26625A)

(43) 公開日 平成25年2月4日(2013.2.4)

(51) Int.Cl.

F 1

テーマコード (参考)

**H01L 25/065** (2006.01)

**H01L 25/07** (2006.01)

**H01L 25/18** (2006.01)

**H01L 21/60** (2006.01)

H01L 25/08

H01L 21/60 321E

審査請求 未請求 請求項の数 36 O L (全 28 頁)

(21) 出願番号 特願2012-159378 (P2012-159378)

(22) 出願日 平成24年7月18日 (2012.7.18)

(31) 優先権主張番号 10-2011-0071016

(32) 優先日 平成23年7月18日 (2011.7.18)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2012-0029739

(32) 優先日 平成24年3月23日 (2012.3.23)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】半導体パッケージ及びその製造方法

## (57) 【要約】

【課題】配線自由度を増加させ得る半導体パッケージ及びその製造方法が提供される。

【解決手段】本発明による半導体パッケージは、基板接続端子を含む基板と、前記基板の上に積層されチップ接続端子を含む少なくとも1つの半導体チップと、前記基板と前記半導体チップとの少なくとも一部を覆う絶縁膜と、前記絶縁膜を貫通して前記基板接続端子と前記チップ接続端子とを連結させる配線を含む。したがって、半導体パッケージの信頼性を向上させる同時に配線自由度を増加させ得る。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

基板接続端子を含む基板と、

前記基板の上に積層され、チップ接続端子を含む少なくとも1つの半導体チップと、

前記基板と前記半導体チップとの少なくとも一部を覆う第1絶縁膜と、

前記第1絶縁膜を貫通して前記基板接続端子と前記チップ接続端子とを連結させる配線と、を含む半導体パッケージ。

**【請求項 2】**

前記第1絶縁膜は高分子膜と前記高分子膜の中に分散された金属含有粒子とを含むことを特徴とする請求項1に記載の半導体パッケージ。 10

**【請求項 3】**

前記配線は無電解鍍金膜を含むことを特徴とする請求項1に記載の半導体パッケージ。

**【請求項 4】**

前記第1絶縁膜はリセスされた領域と、前記基板接続端子と、前記チップ接続端子とを露出させるホールを含み、

前記配線は前記リセスされた領域と前記ホールとの間に配置されることを特徴とする請求項1に記載の半導体パッケージ。

**【請求項 5】**

前記リセスされた領域の側面と底、そして前記ホールの側面の表面粗さは前記第1絶縁膜の上部面の表面粗さより大きいことを特徴とする請求項4に記載の半導体パッケージ。 20

**【請求項 6】**

前記半導体チップは、

前記チップ接続端子を一部露出させる開口部を含む保護膜と、

前記開口部の内に配置され、前記チップ接続端子と接するレーザー阻止パターンをさらに含むことを特徴とする請求項1に記載の半導体パッケージ。

**【請求項 7】**

前記レーザー阻止パターンは金、ニッケル、鉛を含むグループから選択される少なくとも1つを含むことを特徴とする請求項1に記載の半導体パッケージ。

**【請求項 8】**

前記半導体チップの個数は2つ以上であり、前記基板の上で前記半導体チップの端部は階段形態をなし、 30

前記第1絶縁膜は延長されて前記半導体チップの上部面、側面、及び下部面と前記基板の上部面とをコンフォーマルに覆うことを特徴とする請求項1に記載の半導体パッケージ。

**【請求項 9】**

前記半導体チップは、前記第1絶縁膜の下部で前記配線と垂直的に重畠されるように位置し、前記配線と絶縁されたダミーチップ接続端子をさらに含むことを特徴とする請求項1に記載の半導体パッケージ。

**【請求項 10】**

1つの半導体チップは、複数個のチップ接続端子を含み、

前記第1絶縁膜は延長されて隣接するチップ接続端子と同時に接することを特徴とする請求項1に記載の半導体パッケージ。 40

**【請求項 11】**

前記基板接続端子は第1基板接続端子と第2基板接続端子とを含み、

前記チップ接続端子は第1チップ接続端子と第2チップ接続端子とを含み、

前記配線は前記第1基板接続端子と前記第1チップ接続端子を連結させる第1配線と、

前記第2基板接続端子と前記第2チップ接続端子とを連結させる第2配線と、を含み、

前記第1絶縁膜は前記第1配線下部に配置される下部絶縁膜と、前記第1配線と前記第2配線との間に配置される中間絶縁膜と、を含むことを特徴とする請求項1に記載の半導体パッケージ。 50

**【請求項 1 2】**

前記配線に隣接する前記第1絶縁膜、前記少なくとも1つの半導体チップ及び前記基板を覆う第2絶縁膜をさらに含むことを特徴とする請求項1に記載の半導体パッケージ。

**【請求項 1 3】**

前記半導体チップの個数は2つ以上であり、前記基板の上で前記半導体チップの端部は階段形態をなし、前記チップ接続端子は前記半導体チップの端部に配置されて露出され、

前記第1絶縁膜は前記半導体チップの端部を覆い、前記チップ接続端子を露出させ、

前記配線は前記第1絶縁膜の上に配置され、前記チップ接続端子を連結し、

前記第2絶縁膜は前記配線に覆わない前記第1絶縁膜と前記半導体チップの上部面、側面、及び下部面と前記基板の上部面とをコンフォーマルに覆うことを特徴とする請求項1

10 2に記載の半導体パッケージ。

**【請求項 1 4】**

前記第1絶縁膜はリセスされた領域と前記基板接続端子と前記チップ接続端子を露出させるホールを含み、

前記第2絶縁膜は前記リセスされた領域の側壁と整列される側壁を含むことを特徴とする請求項1

3に記載の半導体パッケージ。

**【請求項 1 5】**

前記第2絶縁膜の側面の表面粗さは前記第2絶縁膜の上部面の表面粗さより大きいことを特徴とする請求項1

4に記載の半導体パッケージ。

**【請求項 1 6】**

前記第2絶縁膜は金属含有粒子を包含しないことを特徴とする請求項1

2に記載の半導体パッケージ。

**【請求項 1 7】**

前記第2絶縁膜はパリレン(parylene)、テフロン(登録商標)(t e f l o n)、エポキシモールド化合物(Epoxy mold compound)の中で少なくとも1つであることを特徴とする請求項1

6に記載の半導体パッケージ。

**【請求項 1 8】**

端部が階段形態をなるように積層され、各々のチップ接続端子を含む複数の半導体チップと、

前記複数の半導体チップの少なくとも端部を覆う一層の絶縁膜と、

前記少なくとも一層の絶縁膜を貫通して前記各々の半導体チップの前記チップ接続端子を連結させる配線と、を含む半導体パッケージ。

**【請求項 1 9】**

基板接続端子を含む基板を準備する段階と、

前記基板の上にチップ接続端子を含む少なくとも1つの半導体チップを積層する段階と、

前記基板接続端子と前記チップ接続端子とを覆うように、第1絶縁膜を形成する段階と、

前記第1絶縁膜を貫通して前記チップ接続端子と前記基板接続端子とを電気的に連結させる配線を形成する段階と、を含む半導体パッケージの製造方法。

**【請求項 2 0】**

前記配線を形成する段階は無電解鍍金法を利用することを特徴とする請求項1

9に記載の半導体パッケージの製造方法。

**【請求項 2 1】**

前記第1絶縁膜は高分子膜と前記高分子膜の内に分散された金属含有粒子を含み、

前記配線を形成する前に、レーザーを照射して前記高分子膜を一部除去して前記第1絶縁膜の表面にリセスされた領域と前記チップ接続端子と前記基板接続端子を露出させるホールを形成する同時に、前記金属含有粒子を前記リセスされた領域と前記ホールと内に残す段階をさらに含むことを特徴とする請求項2

0に記載の半導体パッケージの製造方法。

**【請求項 2 2】**

10

20

30

40

50

前記レーザーは前記金属含有粒子で非金属原子と金属との間の結合環を切って前記金属に構成されたシード膜を形成することを特徴とする請求項21に記載の半導体パッケージの製造方法。

**【請求項23】**

前記配線を形成する前に、

前記金属含有粒子の絶縁性物質を除去する前処理工程を進行して前記金属含有粒子を構成する金属に構成されたシード膜を形成する段階をさらに含むことを特徴とする請求項22に記載の半導体パッケージの製造方法。

**【請求項24】**

前記第1絶縁膜を形成する段階は、化学的気相蒸着工程を進行して前記半導体チップの上部面、側面、及び下部面と前記基板の上部面とをコンフォーマルに覆う前記第1絶縁膜を形成する段階を含み、10

前記高分子はパリレン(parylene)を含むことを特徴とする請求項23に記載の半導体パッケージの製造方法。

**【請求項25】**

前記レーザーは赤外線レーザーであることを特徴とする請求項22に記載の半導体パッケージの製造方法。

**【請求項26】**

前記チップ接続端子の上にレーザー阻止パターンを形成する段階をさらに含み、前記レーザーを照射して前記チップ接続端子の上の前記レーザー阻止パターンが露出されることを特徴とする請求項22に記載の半導体パッケージの製造方法。20

**【請求項27】**

前記方法は前記基板、前記少なくとも1つの半導体チップ、及び前記第1絶縁膜を覆う第2絶縁膜を形成する段階をさらに含み、

前記配線は前記第2絶縁膜と前記第1絶縁膜を貫通して形成されることを特徴とする請求項19に記載の半導体パッケージの製造方法。

**【請求項28】**

前記第2絶縁膜は金属含有粒子を包含しないことを特徴とする請求項27に記載の半導体パッケージの製造方法。

**【請求項29】**

前記第1絶縁膜は高分子膜と前記高分子膜の中に分散された金属含有粒子を含み、30

前記方法は、前記配線を形成する前に、レーザーを照射して前記第2絶縁膜と前記高分子膜を一部除去して前記第1絶縁膜の表面にリセスされた領域と前記チップ接続端子と前記基板接続端子を露出させるホールを形成する同時に、前記金属含有粒子を前記リセスされた領域と前記ホールとの中に残す段階をさらに含むことを特徴とする請求項28に記載の半導体パッケージの製造方法。

**【請求項30】**

第1チップ接続端子を含む第1半導体チップの上に第2チップ接続端子を含む第2半導体チップを積層する段階と、

前記第1チップ接続端子と前記第2チップ接続端子とを覆うように、少なくとも一層の絶縁膜を形成する段階と、40

前記少なくとも一層の絶縁膜を貫通して前記第1チップ接続端子と前記第2チップ接続端子とを電気的に連結させる配線を形成する段階と、を含む半導体パッケージの製造方法。

**【請求項31】**

基板と、

前記基板の上の少なくとも1つの半導体チップと、

前記基板と前記少なくとも1つの半導体チップの上の第1絶縁膜と、

前記第1絶縁膜を貫通する配線と、を含み、

前記基板は基板連結端子を含み、50

前記少なくとも 1 つの半導体チップはチップ連結端子を含み、

前記第 1 絶縁膜は少なくとも前記基板連結端子と前記チップ連結端子とを覆い、

前記配線は前記基板連結端子と前記チップ連結端子とを電気的に連結させる半導体パッケージ。

**【請求項 3 2】**

前記基板の上の 2 つ以上の半導体チップをさらに含み、

前記 2 つ以上の半導体チップの各々はチップ連結端子を含み、

前記第 1 絶縁膜は少なくとも前記基板連結端子と前記チップ連結端子とを覆い、

前記配線は前記基板連結端子と前記チップ連結端子とを電気的に連結させる請求項 3 1

に記載の半導体パッケージ。

10

**【請求項 3 3】**

請求項 3 1 に記載の前記半導体パッケージを 1 つ以上含むパッケージモジュール。

**【請求項 3 4】**

請求項 3 1 に記載の前記半導体パッケージを 1 つ以上含む電子装置。

**【請求項 3 5】**

請求項 3 1 に記載の前記半導体パッケージを 1 つ以上含むメモリシステム。

**【請求項 3 6】**

基板を準備する段階と、

前記基板の上に 2 つ以上の半導体チップを積層する段階と、

前記基板と前記 2 つ以上の半導体チップとの上に第 1 絶縁膜を形成する段階と、

前記第 1 絶縁膜を貫通する配線を形成する段階と、を含み、

前記基板は基板連結端子を含み、

前記 2 つ以上の半導体チップの各々はチップ連結端子を含み、

前記第 1 絶縁膜は少なくとも前記基板連結端子と前記チップ連結端子とを覆い、

前記配線は前記基板連結端子と前記チップ連結端子とを電気的に連結させる半導体パッケージの形成方法。

20

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は半導体パッケージ及びその製造方法に関する。

30

**【背景技術】**

**【0 0 0 2】**

電子産業の発達によって電子部品の高機能化、高速化及び小型化の要求が増大している。このような趨勢に対応して単一の種類の半導体チップではなく、様々な種類の半導体チップを 1 つの半導体パッケージの内に実装させることが要求されている。しかし、半導体チップの種類が互いに異なるので、その大きさ及び機能も全て異なり、1 つの基板の上に実装すると水平的な大きさの増加や、ワイヤスイーピング (w i r e s w e e p i n g ) 等の問題が発生する。また、ワイヤに使用される金の価格が高く、ワイヤ工程の時には長い時間が必要とされるので、生産性が低下する。

40

**【先行技術文献】**

**【特許文献】**

**【0 0 0 3】**

【特許文献 1】米国特許第 7 , 2 0 8 , 3 4 7 号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0 0 0 4】**

本発明が解決しようとする課題は配線の自由度を増加させ得る半導体パッケージを提供することにある。

**【0 0 0 5】**

本発明が解決しようとする他の課題は生産性を向上させることができる半導体パッケー

50

ジの製造方法を提供することにある。

【課題を解決するための手段】

【0006】

前記課題を達成するための本発明の半導体パッケージは、基板接続端子を含む基板と、前記基板の上に積層されチップ接続端子を含む少なくとも1つの半導体チップと、前記基板と前記半導体チップとの少なくとも一部を覆う第1絶縁膜と、前記第1絶縁膜を貫通して前記基板接続端子と前記チップ接続端子とを連結させる配線と、を含む。

【0007】

前記第1絶縁膜は高分子膜と前記高分子膜の中に分散された金属含有粒子とを包含できる。

10

【0008】

前記配線は無電解鍍金膜を包含できる。

【0009】

前記第1絶縁膜はリセスされた領域と、前記基板接続端子と前記チップ接続端子とを露出させるホールとを含み、前記配線は前記リセスされた領域および前記ホールの中に配置され得る。

【0010】

前記リセスされた領域の側面と底、そして前記ホールの側面の表面粗さは前記第1絶縁膜の上部面の表面粗さより大きくなり得る。

【0011】

前記半導体チップは、前記チップ接続端子を一部露出させる開口部を含む保護膜と、前記開口部の中に配置され、前記チップ接続端子と接するレーザー阻止パターンと、をさらに包含できる。

20

【0012】

前記レーザー阻止パターンは金、ニッケル及び鉛を含むグループから選択される少なくとも1つを包含できる。

【0013】

一実施形態において、前記半導体チップの個数は2つ以上であり、前記基板の上で前記半導体チップの端部は階段形態をなし、前記第1絶縁膜は延長されて前記半導体チップの上部面、側面及び下部面と前記基板の上部面をコンフォーマルに覆うことができる。

30

【0014】

前記半導体チップは、前記第1絶縁膜下部で前記配線と垂直的に重畠されるように位置し、前記配線と絶縁されたダミーチップ接続端子をさらに包含できる。

【0015】

1つの半導体チップは複数個のチップ接続端子を包含でき、前記第1絶縁膜は延長されて隣接するチップ接続端子と同時に接することができる。

【0016】

他の実施形態において、前記基板接続端子は第1基板接続端子と第2基板接続端子を含み、前記チップ接続端子は第1チップ接続端子と第2チップ接続端子を含み、前記配線は前記第1基板接続端子と前記第1チップ接続端子を連結させる第1配線と、前記第2基板接続端子と前記第2チップ接続端子を連結させる第2配線を含み、前記第1絶縁膜は前記第1配線下部に配置される下部絶縁膜と、前記第1配線と前記第2配線との間に配置される中間絶縁膜を包含できる。

40

【0017】

その他の実施形態において、前記半導体パッケージは前記配線に隣接する前記第1絶縁膜、前記少なくとも1つの半導体チップ及び前記基板を覆う第2絶縁膜をさらに包含できる。

【0018】

具体的な実施形態において、前記半導体チップの個数は2つ以上であり、前記基板の上で前記半導体チップの端部は階段形態をなし、前記チップ接続端子は前記半導体チップの

50

端部に配置されて露出され、前記第1絶縁膜は前記半導体チップの端部を覆い、前記チップ接続端子を露出させ、前記配線は前記第1絶縁膜の上に配置され、前記チップ接続端子を連結し、前記第2絶縁膜は前記配線によって覆われない前記第1絶縁膜と前記半導体チップの上部面、側面及び下部面と前記基板の上部面をコンフォーマルに覆うことができる。

【0019】

前記第2絶縁膜は前記リセスされた領域の側壁と整列される側壁を包含できる。前記第2絶縁膜の側面の表面粗さは前記第2絶縁膜の上部面の表面粗さより大きくなり得る。

【0020】

前記第2絶縁膜は望ましくは金属含有粒子を包含しない。

10

【0021】

前記第2絶縁膜はパリレン (parylene)、テフロン (登録商標) (t e f l o n)、エポキシモールド化合物 (Epoxy mold compound) の中の少なくとも1つであり得る。

【0022】

本発明の一実施形態による半導体パッケージは、端部が階段形態をなすように積層され、各々チップ接続端子を含む半導体チップと、前記半導体チップの少なくとも端部を覆う少なくとも一層の絶縁膜と、前記少なくとも一層の絶縁膜を貫通して前記各々の半導体チップの前記チップ接続端子を連結させる配線を含む。

【0023】

前記他の課題を達成するための本発明による半導体パッケージの製造方法は、基板接続端子を含む基板を準備する段階と、前記基板の上にチップ接続端子を含む少なくとも1つの半導体チップを積層する段階と、前記基板接続端子と前記チップ接続端子を覆うよう、第1絶縁膜を形成する段階と、前記第1絶縁膜を貫通して前記チップ接続端子と前記基板接続端子を電気的に連結させる配線を形成する段階を含む。

20

【0024】

前記配線を形成する段階は無電解鍍金法を利用することができる。

【0025】

前記第1絶縁膜は高分子膜と前記高分子膜の中に分散された金属含有粒子を包含でき、前記方法は前記配線を形成する前に、レーザーを照射して前記高分子膜を一部除去して前記第1絶縁膜の表面にリセスされた領域と前記チップ接続端子と前記基板接続端子を露出させるホールを形成すると同時に、前記金属含有粒子を前記リセスされた領域と前記ホールの中に残す段階をさらに包含できる。

30

【0026】

前記レーザーは前記金属含有粒子の非金属原子と金属との間の結合環を切って前記金属に構成されたシード膜を形成できる。

【0027】

前記方法は、前記配線を形成する前に、前記金属含有粒子の絶縁性物質を除去する前処理工程を進行して前記金属含有粒子を構成する金属に構成されたシード膜を形成する段階をさらに包含できる。

40

【0028】

前記第1絶縁膜を形成する段階は、化学的気相蒸着工程を進行して前記半導体チップの上部面、側面及び下部面と前記基板の上部面をコンフォーマルに覆う前記第1絶縁膜を形成する段階を包含でき、前記高分子はパリレン (parylene) を包含できる。

【0029】

前記レーザーは望ましくは赤外線レーザーである。

【0030】

前記方法は、前記チップ接続端子の上にレーザー阻止パターンを形成する段階をさらに包含でき、前記レーザーを照射して前記チップ接続端子の上の前記レーザー阻止パターンが露出され得る。

50

## 【0031】

前記方法は前記基板、前記少なくとも1つの半導体チップ及び前記第1絶縁膜を覆う第2絶縁膜を形成する段階をさらに包含でき、前記配線は前記第2絶縁膜と前記第1絶縁膜を貫通して形成され得る。

## 【0032】

前記レーザーを照射して前記第2絶縁膜と前記高分子膜を一部除去して前記第1絶縁膜の表面にリセスされた領域と前記チップ接続端子と前記基板接続端子を露出させるホールを形成する同時に、前記金属含有粒子を前記リセスされた領域と前記ホールの中に残留させ得る。

## 【0033】

本発明の一実施形態による半導体パッケージの製造方法は、第1チップ接続端子を含む第1半導体チップの上に第2チップ接続端子を含む第2半導体チップを積層する段階と、前記第1チップ接続端子と前記第2チップ接続端子を覆うように、絶縁膜を形成する段階と、前記絶縁膜を貫通して前記第1チップ接続端子と前記第2チップ接続端子を電気的に連結させる配線を形成する段階を包含できる。

10

## 【発明の効果】

## 【0034】

本発明の一実施形態による半導体パッケージで、絶縁膜のリセスされた領域の側壁と底、そして前記ホールの内壁の表面が粗さを有するので、配線と前記絶縁膜との間の接着力が向上され得る。また、前記絶縁膜は延長されて隣接するチップ接続端子及び基板接続端子を全て連結するように、半導体チップ及びパッケージ基板の端部を覆って保護するので、半導体パッケージの信頼性を向上させ得る。また、前記配線が前記絶縁膜の上に配置されるので、配線自由度を増加させ得る。また、ワイヤを使用しないので、ワイヤに主に使用される金を使用しなくて経済的である。

20

## 【0035】

また、本発明で配線が無電解鍍金で形成されるので、ストリップ／パネルレベルの配置工程 (strip / panel - level batch process) が可能であり生産性を最大化できる。

## 【0036】

本発明の他の実施形態による半導体パッケージは、金属含有粒子を含む第1絶縁膜と、前記第1絶縁膜を覆うが、金属含有粒子を包含しない第2絶縁膜を含む。前記第2絶縁膜によって前記第1絶縁膜の金属含有粒子が露出されない。無電解鍍金の時前記金属含有粒子が望まない領域の表面に露出される場合、僅かに金属が析出される可能性があり、金属が析出された領域に望まない鍍金層が形成される恐れがある。しかし、前記第2絶縁膜が前記第1絶縁膜を覆うので、前記金属含有粒子が表面に露出される恐れが無くなり、ブリッジ (bridge) 又はショート (short) 不良を防止することができる。また前記第2絶縁膜が前記半導体チップと前記基板を全て覆って、無電解鍍金の時、化学的アタック (attack) から前記半導体チップと前記基板とを全て保護することができる。

30

## 【図面の簡単な説明】

## 【0037】

40

【図1】本発明の実施形態1による半導体パッケージのレイアウトである。

【図2】図1をI-I'線に沿って切断した断面図である。

【図3A】図2の‘A’部分を拡大した断面図である。

【図3B】図2の‘B’部分を拡大した断面図である。

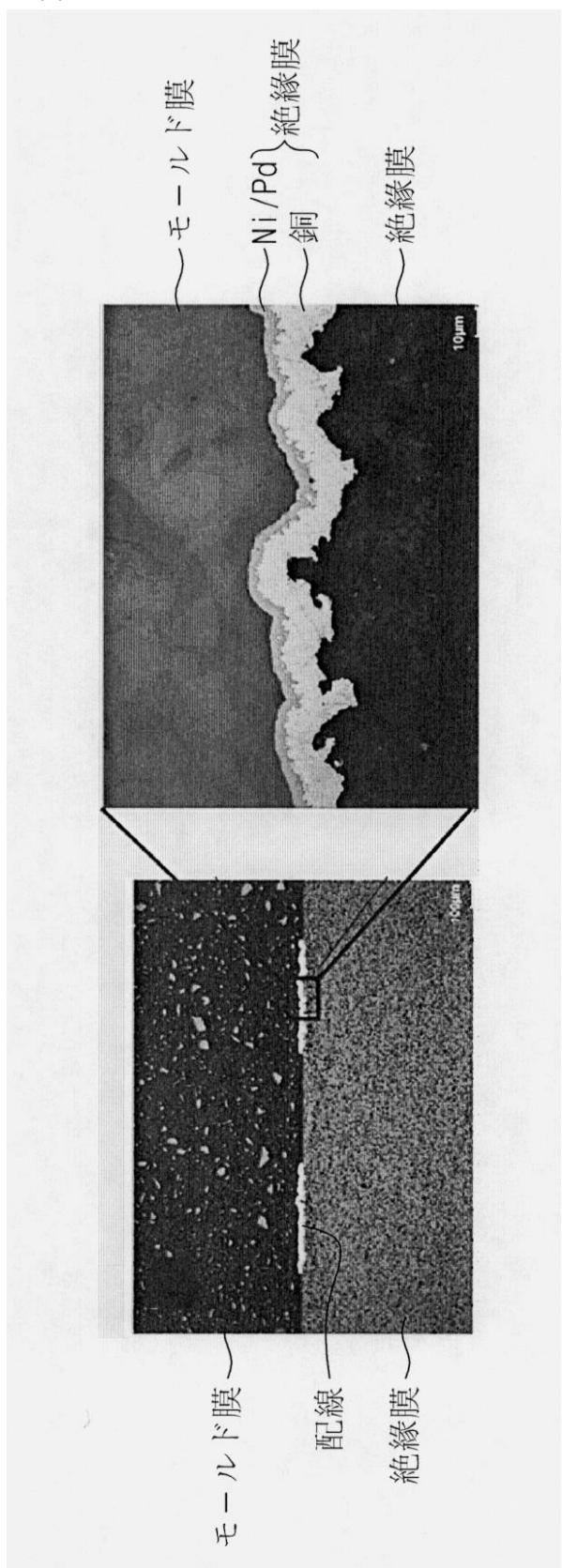

【図4】本発明の一実験例にしたがって製造された半導体パッケージの一部分を拡大した断面写真を示す。

【図5】図2の断面を有する半導体パッケージの製造方法を示す。

【図6】図2の断面を有する半導体パッケージの製造方法を示す。

【図7】図2の断面を有する半導体パッケージの製造方法を示す。

【図8】図2の断面を有する半導体パッケージの製造方法を示す。

50

- 【図 9】図 2 の断面を有する半導体パッケージの製造方法を示す。

- 【図 10】図 2 の断面を有する半導体パッケージの製造方法を示す。

- 【図 11】図 2 の断面を有する半導体パッケージの製造方法を示す。

- 【図 12】図 2 の断面を有する半導体パッケージの製造方法を示す。

- 【図 13A】図 12 の ‘A’ 部分を拡大した断面図である。

- 【図 13B】図 12 の ‘B’ 部分を拡大した断面図である。

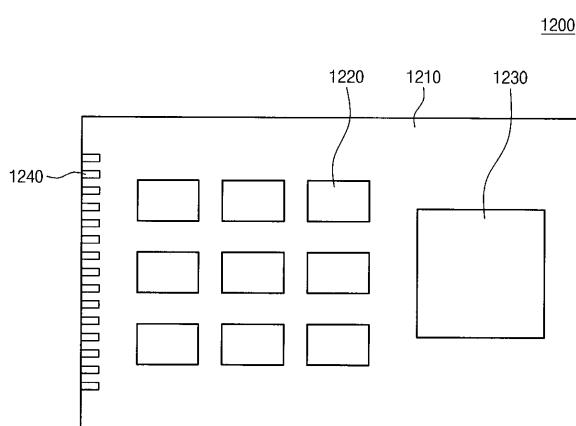

- 【図 14】本発明の実施形態 2 による半導体パッケージのレイアウトである。

- 【図 15】図 14 を I - I' 線に沿って切断した断面図である。

- 【図 16】本発明の実施形態 3 による半導体パッケージの断面図である。

- 【図 17】本発明の実施形態 4 による半導体パッケージのレイアウトである。 10

- 【図 18】図 17 を I - I' 線に沿って切断した断面図である。

- 【図 19】本発明の実施形態 5 による半導体パッケージの断面図である。

- 【図 20】本発明の実施形態 6 による半導体パッケージの断面図である。

- 【図 21】本発明の実施形態 7 による半導体パッケージの平面図である。

- 【図 22A】図 21 を I - I' 線に沿って切断した断面図である。

- 【図 22B】図 21 を I I - I I' 線に沿って切断した断面図である。

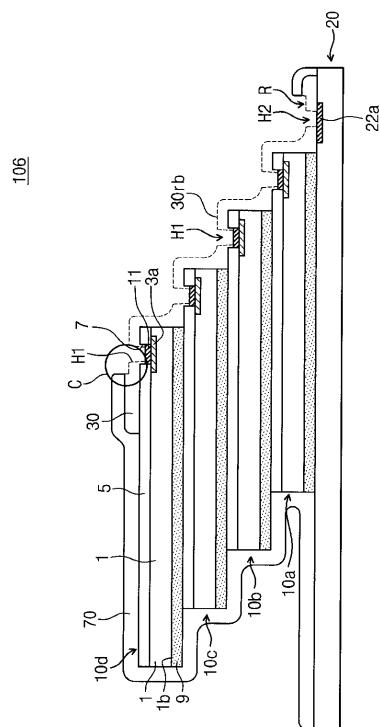

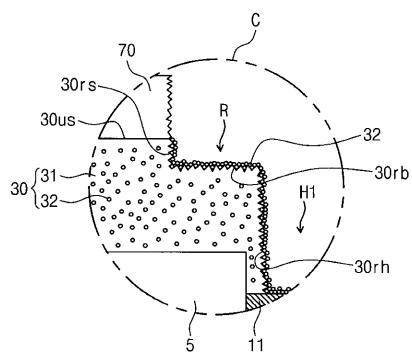

- 【図 23】図 22A の ‘C’ 部分を拡大した拡大図である。

- 【図 24】図 22A の断面を有する半導体パッケージを製造する過程を順次的に示す断面図である。 20

- 【図 25】図 22A の断面を有する半導体パッケージを製造する過程を順次的に示す断面図である。

- 【図 26】図 22A の断面を有する半導体パッケージを製造する過程を順次的に示す断面図である。

- 【図 27】図 26 の ‘C’ 部分を拡大した拡大図である。

- 【図 28】本発明の技術が適用された半導体パッケージを含むパッケージモジュールの例を示す図面である。 30

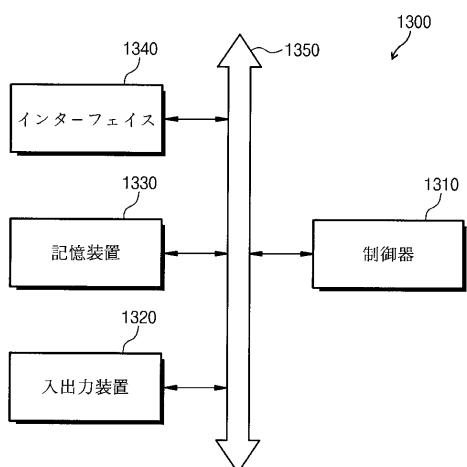

- 【図 29】本発明の技術が適用された半導体パッケージを含む電子装置の例を示すブロック図である。

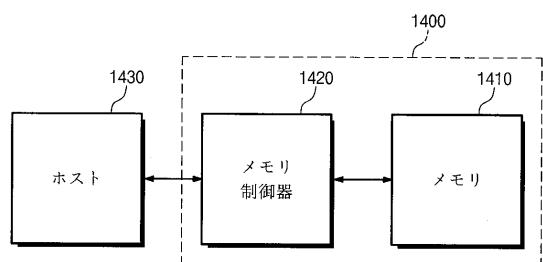

- 【図 30】本発明の技術が適用された半導体パッケージを含むメモリシステムの例を示すブロック図である。 30

- 【発明を実施するための形態】**

- 【0038】**

- 以下、添付した図面を参照して本発明の望ましい実施形態を詳細に説明する。しかし、本発明はここで説明される実施形態に限定されず、他の形態に具体化されることもあり得る。むしろ、ここで紹介される実施形態は開示された内容が徹底であり完全になるように、そして当業者に本発明の思想が十分に伝達され得るように下記に提供されるものである。図面において、複数の層及び領域の厚さは明確性を期するために誇張されている。また、層が他の層又は基板 “上” にあると言及される場合にそれは他の層又は基板の上に直接形成されるか、又はそれらの間に第 3 の層が介在されることもあり得る。明細書全体にわたって同一の参照番号は同一の構成要素を示す。 40

- 【0039】**

- <実施形態 1>

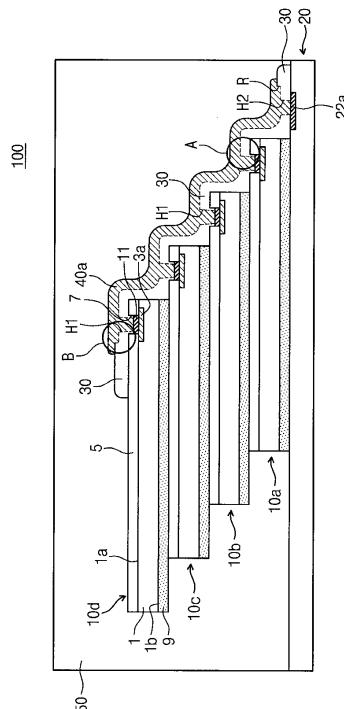

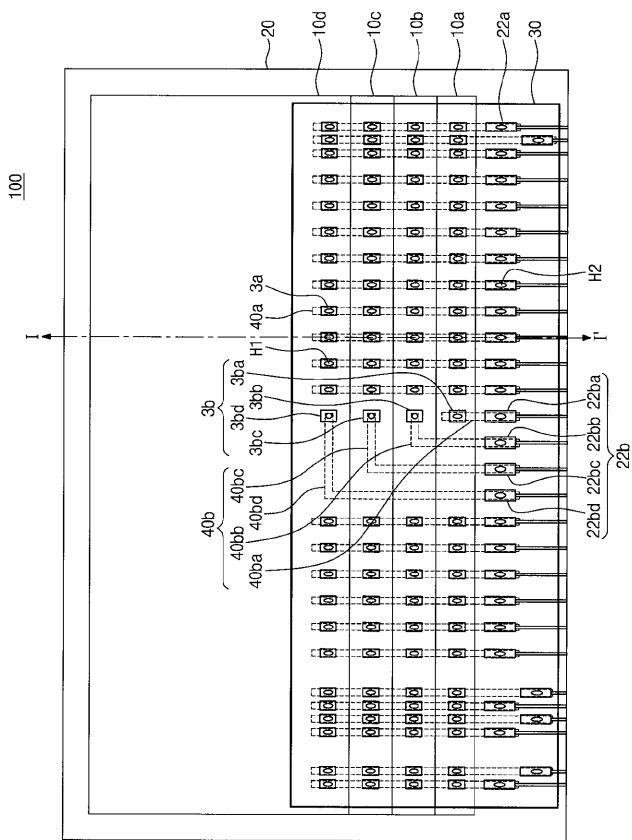

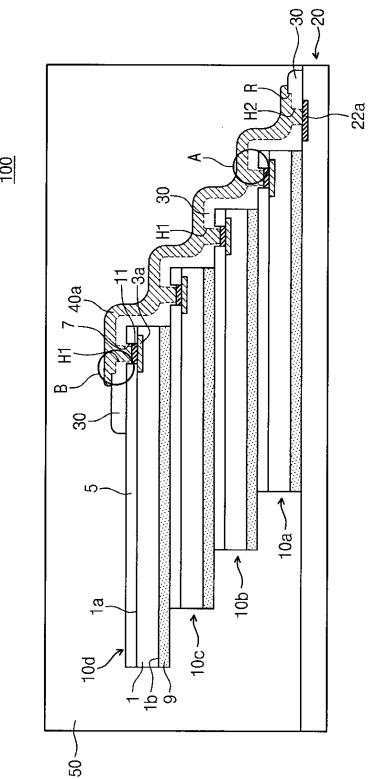

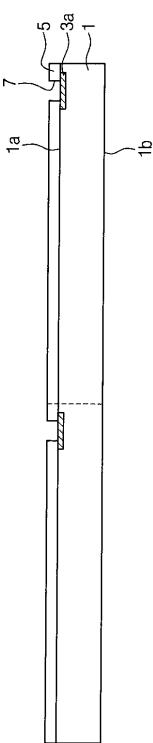

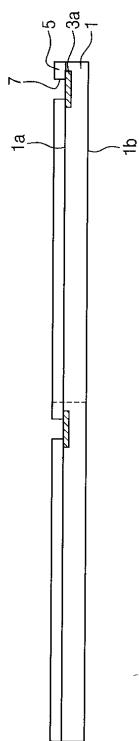

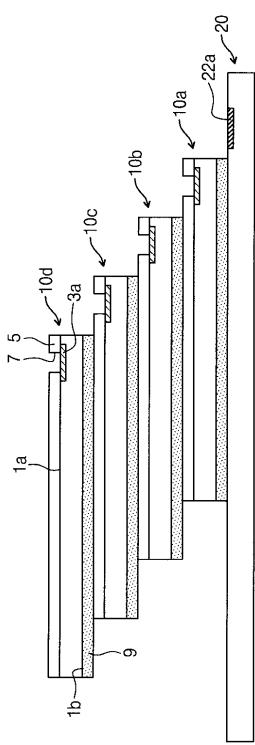

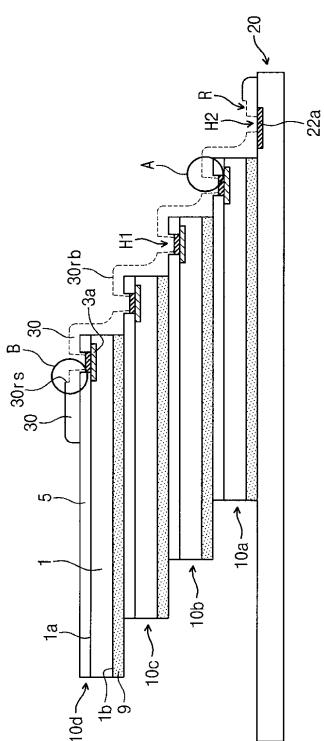

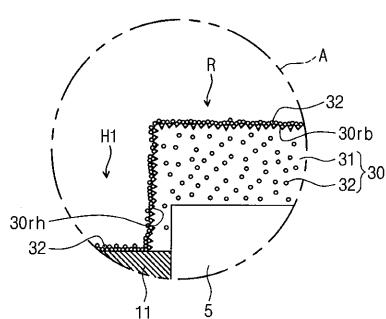

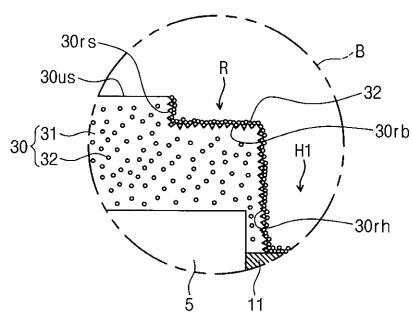

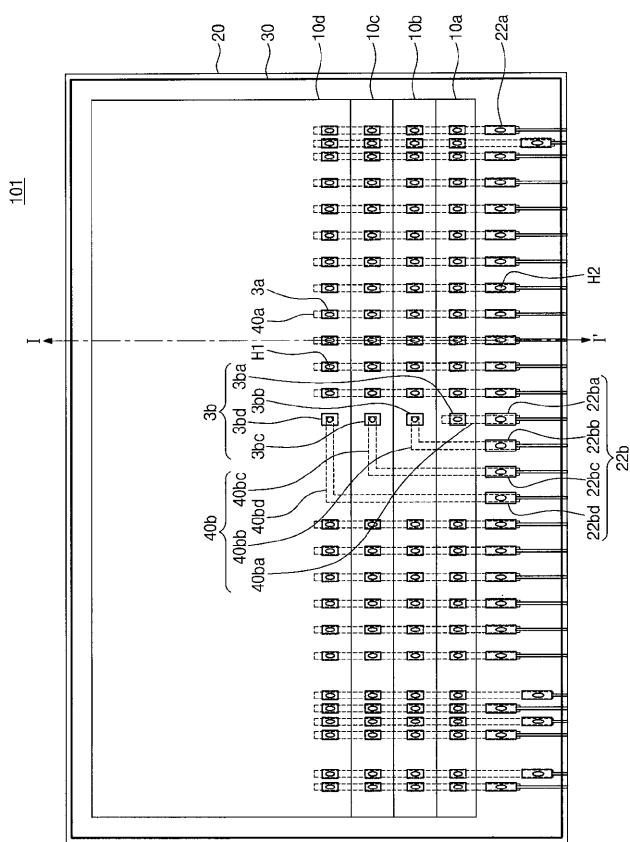

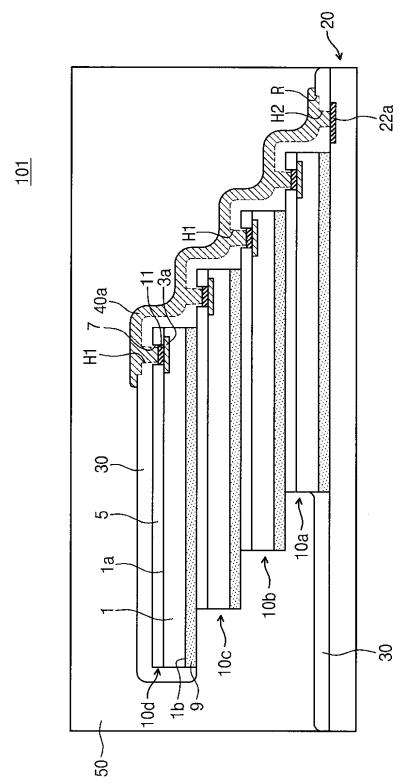

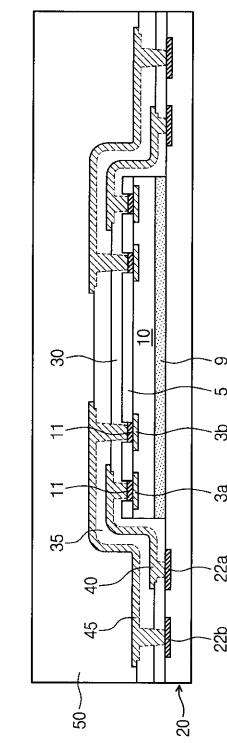

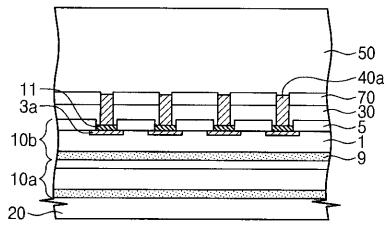

- 図 1 は本発明の実施形態 1 による半導体パッケージのレイアウトである。図 2 は図 1 を I - I' 線に沿って切断した断面図である。図 3A 及び図 3B は各々図 2 の ‘A’ 部分と ‘B’ 部分とを拡大した断面図である。

- 【0040】**

- 図 1 及び図 2 を参照すれば、本実施形態 1 による半導体パッケージ 100 では、パッケージ基板 20 の上に複数個の半導体チップ 10a、10b、10c、10d が積層される。前記半導体チップ 10a、10b、10c、10d は下から上に第 1 半導体チップ 10a、第 2 半導体チップ 10b、第 3 半導体チップ 10c、及び第 4 半導体チップ 10d を 50

包含できる。本実施形態で前記半導体チップ 10 a、10 b、10 c、10 d は互いに同一であり得る。前記半導体チップ 10 a、10 b、10 c、10 d は各々のチップボディー 1 を含む。前記チップボディー 1 は半導体基板と、その上に形成された回路パターン及びこれを覆う層間絶縁膜を包含できる。前記チップボディー 1 は互いに対向された第 1 面 1 a と第 2 面 1 b とを含む。前記第 1 面 1 a には複数の第 1 チップ接続端子 3 a と第 2 チップ接続端子 3 b とが配置される。前記第 1 チップ接続端子 3 a と前記第 2 チップ接続端子 3 b とは前記チップボディー 1 で前記層間絶縁膜の最上端に配置される導電パッドに対応され得る。前記第 1 チップ接続端子 3 a は接地ピン (Ground pin)、電源ピン (Power pin)、データピン (data pin)、アドレスピン (Address pin)、及びコマンドピン (Command pin) 等を包含できる。前記第 2 チップ接続端子 3 b はチップ作動ピン (Chip enable pin) に対応され得る。前記第 1 半導体チップ 10 a の前記第 2 チップ接続端子 3 b は第 1 チップ作動ピン 3 b a に対応され得る。前記第 2 半導体チップ 10 b の前記第 2 チップ接続端子 3 b は第 2 チップ作動ピン 3 b b に対応され得る。前記第 3 半導体チップ 10 c の前記第 2 チップ接続端子 3 b は第 3 チップ作動ピン 3 b c に対応され得る。前記第 4 半導体チップ 10 d の前記第 2 チップ接続端子 3 b は第 4 チップ作動ピン 3 b d に対応され得る。

10

## 【0041】

前記第 1 面 1 a には保護膜 5 が配置される。前記保護膜 5 は前記チップ接続端子 3 a、3 b を露出させる第 1 ホール 7 を含む。前記第 1 ホール 7 の中には前記チップ接続端子 3 a、3 b と接するレーザー阻止パターン 11 が配置される。前記レーザー阻止パターン 11 はレーザーのエネルギーを吸収せず、反射させると同時に導電性を有する物質で形成され得る。例えば、前記レーザー阻止パターン 11 はニッケル Ni、鉛 Pb、金 Au 等を含むグループから選択される少なくとも 1 つの物質を包含できる。前記第 2 面 1 b には接着膜 9 が配置される。前記接着膜 9 は前記半導体チップ 10 a、10 b、10 c、10 d と前記パッケージ基板 20 とを互いに接着させる役割を果たす。

20

## 【0042】

前記パッケージ基板 20 には第 1 基板接続端子 22 a と第 2 基板接続端子 22 b とが配置される。前記第 1 基板接続端子 22 a と第 2 基板接続端子 22 b とは望ましくは前記レーザー阻止パターン 11 と同一である物質を包含できる。前記第 1 基板接続端子 22 a は前記第 1 チップ接続端子 3 a と連結され得る。前記第 2 基板接続端子 22 b は第 1 半導体チップ 10 a を選択する第 1 チップ作動基板ピン 22 b a、第 2 半導体チップ 10 b を選択する第 2 チップ作動基板ピン 22 b b、第 3 半導体チップ 10 c を選択する第 3 チップ作動基板ピン 22 b c、及び第 4 半導体チップ 10 d を選択する第 4 チップ作動基板ピン 22 b d を包含できる。

30

## 【0043】

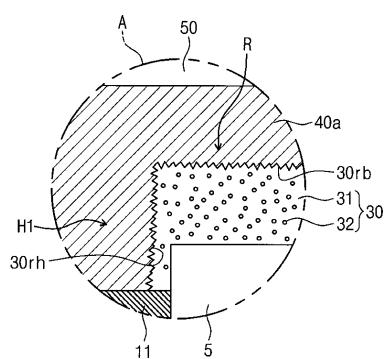

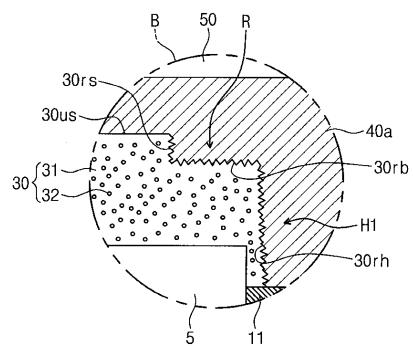

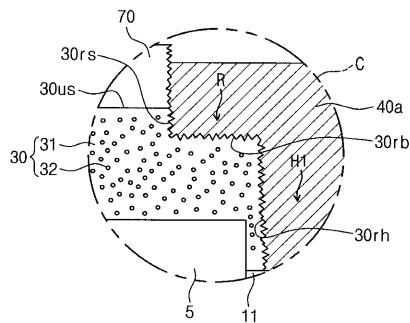

図 1、図 2、図 3 A、及び図 3 B を参照すれば、前記半導体チップ 10 a、10 b、10 c、10 d の端部と前記パッケージ基板 20 の端部とは絶縁膜 30 で覆われる。前記絶縁膜 30 は延長されて隣接する前記チップ接続端子 3 a、3 b 及び前記基板接続端子 22 a、22 b を全て連結することができる。前記絶縁膜 30 は高分子膜 31 と前記高分子膜 31 に分散された金属含有粒子 32 とを包含できる。前記高分子膜 31 は多様であり、例えばエポキシモールド化合物 (Epoxy mold compound)、又はパリレン (parylene) 等であり得る。前記金属含有粒子 32 は金属酸化物、金属窒化物、金属炭化物、又は金属硫化物であるか、又は絶縁性物質でコーティングされた金属粒子であり得る。前記金属含有粒子 32 に含まれる金属は、例えばアルミニウム、マグネシウム、鉄、マンガン、銅、クロム、コバルト、ニッケル等多様であり得る。

40

## 【0044】

前記絶縁膜 30 は前記チップ接続端子 3 a、3 b を一部露出させる第 1 ホール H1 と前記基板接続端子 22 a、22 b を一部露出させる第 2 ホール H2 とを含む。また、前記絶縁膜 30 は上部面 30 us と段差になったリセスされた領域 R とを有する。前記リセスされた領域 R は前記第 1 ホール H1 と前記第 2 ホール H2 とを連結するライン形態に形成さ

50

れる。前記リセスされた領域 R の側壁 30r s と底 30r b、そして前記ホール H1、H2 の内壁 30r h の表面は粗さを有する(図2で、点線で示す)。即ち、前記リセスされた領域 R の側壁 30r s と底 30r b、そして前記ホール H1、H2 の内壁 30r h の表面は平らでなく、凸凹形状で屈曲されている。前記リセスされた領域 R の側壁 30r s と底 30r b、そして前記ホール H1、H2 の内壁 30r h の表面粗さは前記絶縁膜 30 の前記上部面 30us の表面粗さより大きい。

#### 【0045】

前記リセスされた領域 R と前記ホール H1、H2 との内には配線 40a、40b が配置される。前記配線 40a、40b は前記絶縁膜 30 の上部面 30us より突出され得る。前記配線 40a、40b は少なくとも無電解鍍金で形成された銅を包含できる。前記配線 40a、40b は前記銅膜の上に配置されるニッケル／鉛膜をさらに包含できる。前記配線 40a、40b は第1配線 40a と第2配線 40b とを含む。前記第1配線 40a は1つの第1基板接続端子 22a とこれに対応する各半導体チップ 10a、10b、10c、10d の第1チップ接続端子 3a とを連結させ得る。前記第2配線 40b は第1チップ選択配線 40ba、第2チップ選択配線 40bb、第3チップ選択配線 40bc、及び第4チップ選択配線 40bd を含む。前記第1チップ選択配線 40ba は第1チップ作動基板ピン 22ba と第1チップ作動ピン 3ba とを連結させる。前記第2チップ選択配線 40bb は第2チップ作動基板ピン 22bb と第2チップ作動ピン 3bb とを連結させる。前記第3チップ選択配線 40bc は第3チップ作動基板ピン 22bc と第3チップ作動ピン 3bc とを連結させる。前記第4チップ選択配線 40bd は第4チップ作動基板ピン 22bd と第2チップ作動ピン 3bd とを連結させる。前記半導体チップ 10a、10b、10c、10d 及び前記パッケージ基板 20 はモールド膜 50 で覆われ得る。

10

20

30

30

#### 【0046】

前記半導体パッケージ 100 で、前記リセスされた領域 R の側壁 30r s と底 30r b、そして前記ホール H1、H2 の内壁 30r h の表面が粗さを有するので、前記配線 40a、40b と前記絶縁膜 30 との間の接着力が向上され得る。また、前記絶縁膜 30 は延長されて隣接する前記チップ接続端子 3a、3b 及び前記基板接続端子 22a、22b を全て連結するように、前記半導体チップ 10a、10b、10c、10d 及び前記パッケージ基板 20 の端部を覆って保護するので、前記半導体パッケージ 100 の信頼性を向上させ得る。また、前記配線 40a、40b が前記絶縁膜 30 の上に配置されるので、ワイヤボンディング方式でワイヤスイーピングに伴う問題を解決でき、配線自由度を増加させ得る。また、前記半導体パッケージ 100 ではワイヤを使用しないので、ワイヤとして主に使用される金を必要としないので、経済的である。

#### 【0047】

前記絶縁膜 30 と前記配線 40a、40b との間には前記金属含有粒子 32 を構成する金属で成されるシード膜が配置される。しかし、前記金属含有粒子 32 の大きさは非常に小さい(概ね金属原子の大きさに該当する)。

#### 【0048】

図4は本発明の一実験例にしたがって製造された半導体パッケージの一部分を拡大した断面写真を示す。図4を参照すれば、絶縁膜の表面が非常に荒く形成されていることが分かる。図4でもシード膜を区別するのが難しいことが分かる。したがって、図3A及び図3Bで、前記シード膜に対する図示を省略した。

40

#### 【0049】

図5乃至図12は図2の断面を有する半導体パッケージの製造方法を示す。図13A及び図13Bは各々図12の‘A’部分と‘B’部分とを拡大した断面図である。

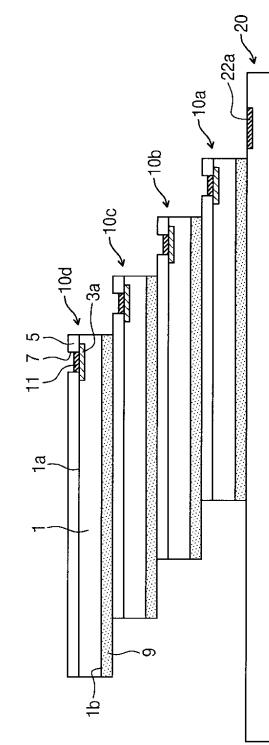

#### 【0050】

図5を参照すれば、ウエハーの上にトランジスター、配線、及び層間絶縁膜を形成してチップボディー1を形成する。前記チップボディー1は互いに対向される第1面 1a と第2面 1b とを含む。前記第1面 1a にチップ接続端子 3a、3b を形成する。前記第1面 1a の上に前記チップ接続端子 3a、3b を露出させる開口部 7 を含む保護膜 5 を形成す

50

る。前記チップ接続端子 3 a、3 b はアルミニウム膜で形成され得る。

【0051】

図 6 を参照すれば、グラインド (grind) 工程を進行して前記チップボディー 1 の第 2 面 1 b に隣接するウエハーを一部除去する。したがって、前記チップボディー 1 の厚さを薄くすることができる。

【0052】

図 7 を参照すれば、前記チップボディー 1 の第 2 面 1 b に接着膜 9 を形成する。そして、前記ウエハーを切断してチップ別に分離させるウエハー切断 (wafer sawing) 工程を進行する。したがって、半導体チップ 10 a、10 b、10 c、10 d が形成される。

10

【0053】

図 8 を参照すれば、パッケージ基板 20 の上に前記半導体チップ 10 a、10 b、10 c、10 d を積層する。前記パッケージ基板 20 はストリップレベル (strip level) 又はパネルレベル (panel level) 基板であるか、又はこれを切断した単位パッケージ基板に該当され得る。前記パッケージ基板 20 には基板接続端子 22 a、22 b が配置される。前記基板接続端子 22 a、22 b は金、ニッケル、鉛を含むグループから選択される少なくとも 1 つの物質を包含できる。前記半導体チップ 10 a、10 b、10 c、10 d の端部が階段形態をなすように積層して前記チップ接続端子 3 a、3 b 及び前記基板接続端子 22 a、22 b を露出させる。前記接着膜 9 によって、前記半導体チップ 10 a、10 b、10 c、10 d 及び前記パッケージ基板 20 は互いに分離されず、接着される。

20

【0054】

図 9 を参照すれば、無電解鍍金を実施して前記開口部 7 によって露出された前記チップ接続端子 3 a、3 b の上にレーザー阻止パターン 11 を形成する。前記レーザー阻止パターン 11 は、例えば金、ニッケル、鉛を含むグループから選択される少なくとも 1 つの物質で形成され得る。前記レーザー阻止パターン 11 を形成するために前記パッケージ基板 20 を無電解鍍金用バッチ式反応槽に浸漬してよい。前記レーザー阻止パターン 11 は前記ウエハー切断工程の前に形成され得る。前記無電解鍍金はストリップレベル又はパネルレベルで実施できる。即ち、前記パッケージ基板 20 がストリップ又はパネルレベルのパッケージ基板に該当するか、又は単位パッケージ基板であってもストリップ又はパネルレベルで一緒に付けて実施できる。これと同様に、前記半導体チップ 10 a、10 b、10 c、10 d を前記パッケージ基板 20 の上に積層した後に、ストリップ / パネルレベルで前記レーザー阻止パターン 11 を形成する場合が、前記ウエハー切断工程を進行する前に形成する場合より、収率を増大させ得る。前記基板接続端子 22 a、22 b が金で形成された場合、前記基板接続端子 22 a、22 b の上で前記レーザー阻止パターン 11 は形成されないこともあり得る。

30

【0055】

図 10 を参照すれば、前記半導体チップ 10 a、10 b、10 c、10 d 及び前記パッケージ基板 20 の端部を覆うように絶縁膜 30 を形成する。前記絶縁膜 30 は隣接する前記チップ接続端子 3 a、3 b 及び前記基板接続端子 22 a、22 b を全て連結するよう広く形成され得る。本実施形態で前記絶縁膜 30 はインクジェッティング (inkjetting) やスプレーコーティング (spray coating) 方式で形成され得る。前記絶縁膜 30 がインクジェッティングやスプレーコーティング方式で形成される場合、望む領域のみを選択的に形成するのが容易である。前記絶縁膜 30 は高分子膜とこれに分散された金属含有粒子とを包含できる。前記高分子膜は、例えばエポキシモールド化合物 (Epoxy mold compound) 又はパリレン (parylene) 等であり得る。前記金属含有粒子は金属酸化物、金属窒化物、金属炭化物、又は金属硫化物であるか、又は絶縁性物質でコーティングされた金属粒子であり得る。前記金属含有粒子に含まれる金属は例えば、アルミニウム、マグネシウム、鉄、マンガン、銅、クロム、コバルト、ニッケル等多様であり得る。前記絶縁膜 30 をインクジェッティングやスプレー

40

50

コーティング方式で形成するために前記高分子を溶解させる溶媒等を包含できる。また前記溶媒を蒸発させるための乾燥過程が遂行できる。

#### 【0056】

図11、図12、図13A、及び図13Bを参照すれば、レーザーを照射して前記絶縁膜30の表面を活性化させると同時に、前記チップ接続端子3a、3b及び前記基板接続端子22a、22bを露出させるホールH1、H2を形成する。前記絶縁膜30の表面を活性化し、前記ホールH1、H2を形成する過程では前記レーザーで前記絶縁膜30に含まれた高分子膜31を燃焼させて除去できる。したがって、図11の絶縁膜の上部の一部30wが除去される。前記レーザーは望ましくは赤外線(infrared)レーザー(波長約1064nm)であり得る。前記レーザーは約5W(ワット)以下の強度で照射されてよく、前記高分子膜31の燃焼が可能である程度の温度になるように照射され得る。前記高分子膜31がエポキシモールド化合物である場合、前記高分子膜31が約300~500温度になるように前記レーザーが照射され得る。前記レーザーによって前記高分子膜31が燃焼して前記絶縁膜30の上部にはリセスされた領域RとホールH1、H2とが形成される。前記リセスされた領域Rの側壁30rsと底32b、そして前記ホールH1、H2の側壁30rhは粗さを有するように形成される。そして、前記リセスされた領域Rの側壁30rsと底32rb、そして前記ホールH1、H2の側壁30rhと底とは前記レーザーによって燃焼されない金属含有粒子32が残る。前記レーザーによって前記金属含有粒子32で金属とこれに結合された非金属原子(酸素、窒素、炭素又は硫黄原子)との間の結合環が切れられ得る。この時、前記非金属原子を含む化合物は蒸発され得、金属が露出された状態で残ることができる。又は、前記金属含有粒子32が絶縁性物質でコーティングされた金属粒子である場合、絶縁性物質でコーティングされた前記金属含有粒子32が残ることができる。このように、レーザーで高分子膜31の一部を燃焼させて除去し、金属含有粒子32を露出させる過程を、前記絶縁膜30を活性化させることと称する。前記残った金属含有粒子32は後続の配線40a、40bを無電解鍍金で形成するためのシード膜になり得る。

#### 【0057】

再び、図2、図3A、及び図3Bを参照すれば、前記金属含有粒子32が露出された状態で無電解鍍金を実施して配線40a、40bを形成する。これを行うために前記パッケージ基板20を無電解鍍金用バッチ式反応槽に浸漬してよい。前記無電解鍍金はストリップレベル又はパネルレベルで実施できる。即ち、前記パッケージ基板20がストリップ又はパネルレベルのパッケージ基板に該当するか、又は単位パッケージ基板であってもストリップ又はパネルレベルで一緒に付けて実施できる。このように、ストリップ/パネルレベルの配置工程(strip/panel-level batch process)が可能なので、収率が増加され、生産性を最大化できる。

#### 【0058】

前記無電解鍍金を実施する前の前処理過程で前記金属含有粒子32の絶縁性物質を除去できる。仮に、前記金属含有粒子32が酸化膜でコーティングされた金属粒子である場合、フッ酸を利用して前記酸化膜を除去できる。したがって、前記金属含有粒子32の絶縁性物質は除去され、純粋な金属のみが残って無電解鍍金のためのシード膜が形成され得る。そして、前記無電解鍍金を実施して前記リセスされた領域Rと前記ホールH1、H2の中に選択的に前記配線40a、40bを形成する。後続的にモールド膜50を形成して図2の半導体パッケージ100を形成できる。前記パッケージ基板20がストリップ/パネルレベルである場合、後続過程として単位パッケージに分離する工程が追加され得る。

#### 【0059】

図13A及び図13Bで前記金属含有粒子32は理解を助けるために拡大図示された。しかし、前記金属含有粒子32の大きさは非常に小さいので(概ね金属原子の大きさに該当する)、最終拡大構造である図3A及び図3Bで前記金属含有粒子32に対する図示は省略された。

#### 【0060】

10

20

30

40

50

ワイヤボンディング工程はワイヤをボンディングすることに多くの時間を要するが、本発明ではワイヤボンディング工程を適用せず、前記配線 40a、40b が無電解鍍金で形成されるので、ストリップ／パネルレベルの配置工程 (strip / panel - level batch process) が可能であり、ワイヤボンディングに比べて相対的に短い時間が必要とされ、生産性を最大化できる。

#### 【0061】

##### <実施形態2>

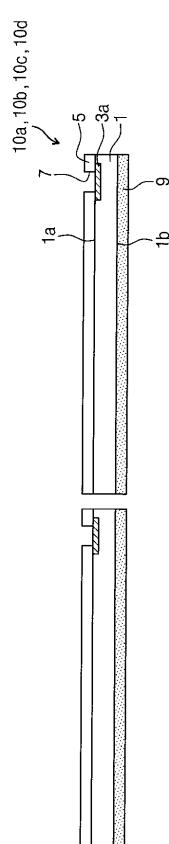

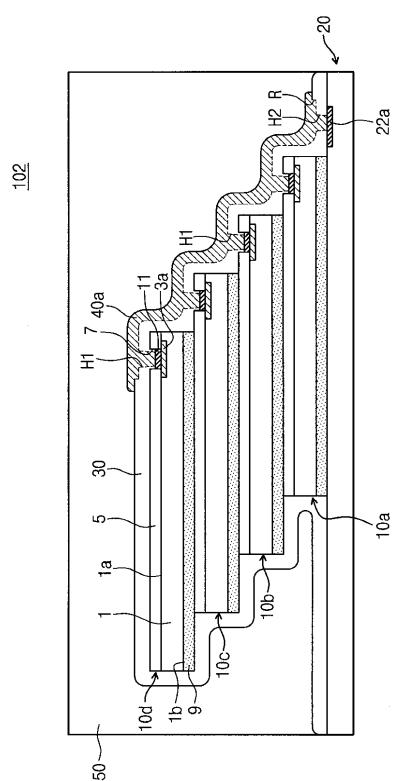

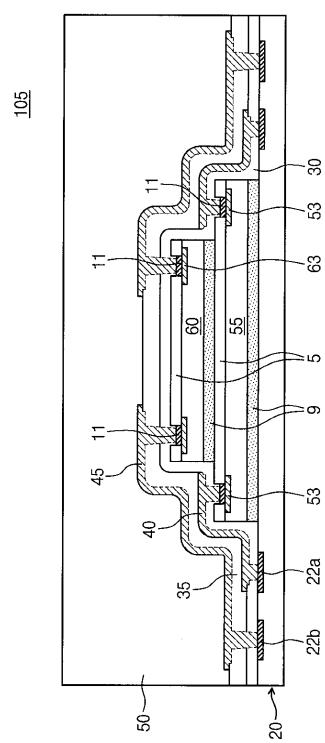

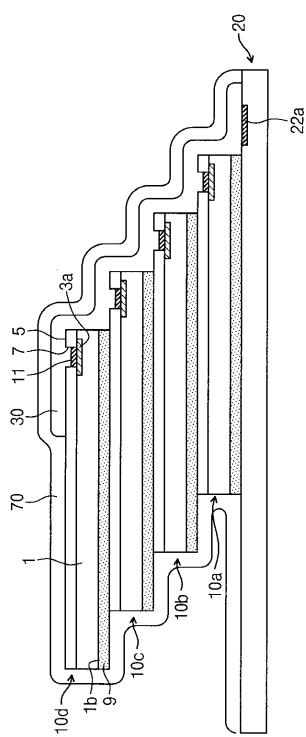

図14は本発明の実施形態2による半導体パッケージのレイアウトである。図15は図14をI-I'線に沿って切断した断面図である。

#### 【0062】

図14及び図15を参照すれば、本実施形態2による半導体パッケージ101で絶縁膜30がスピンドルコーティング (spin coating) 方式で形成され得る。前記絶縁膜30がスピンドルコーティング方式で形成されるので、前記絶縁膜30は半導体チップ10a、10b、10c、10dの側面を全て覆い、最も高く位置する前記第4半導体チップ10dの上部面を全て覆うことができる。さらに、前記絶縁膜30は前記第4半導体チップ10dの下部のパッケージ基板20の上部面も覆うことができる。前記絶縁膜30が前記半導体チップ10a、10b、10c、10d及び前記パッケージ基板20を覆う面積が広くなるほど、前記半導体チップ10a、10b、10c、10d及び前記パッケージ基板20をさらに保護することができる。例えば、配線を形成するための無電解鍍金工程で電解槽の中に前記パッケージ基板20を沈める時、電解液による化学的な攻撃から前記絶縁膜30は前記半導体チップ10a、10b、10c、10d及び前記パッケージ基板20を保護することができる。その他の構造及び形成過程は実施形態1と同一／類似であり得る。

#### 【0063】

##### <実施形態3>

図16は本発明の実施形態3による半導体パッケージの断面図である。

#### 【0064】

図16を参照すれば、本実施形態2による半導体パッケージ102で絶縁膜30は半導体チップ10a、10b、10c、10dの側面及び下部面及び上部面とパッケージ基板20の上部面とをコンフォーマルに覆う。前記絶縁膜30はスピンドルコーティングで形成されることもあり得るが、この時、望ましくは化学的気相蒸着方式で形成され得る。この時、前記絶縁膜30に含まれる高分子膜はパリレン (parylene) で形成され得る。前記絶縁膜30が前記半導体チップ10a、10b、10c、10d及び前記パッケージ基板20の露出される面を全てコンフォーマルに覆うので、無電解鍍金工程で電解液による化学的な攻撃から安全に前記半導体チップ10a、10b、10c、10d及び前記パッケージ基板20を保護することができる。その他の構造及び形成過程は実施形態1と同一／類似であり得る。

#### 【0065】

##### <実施形態4>

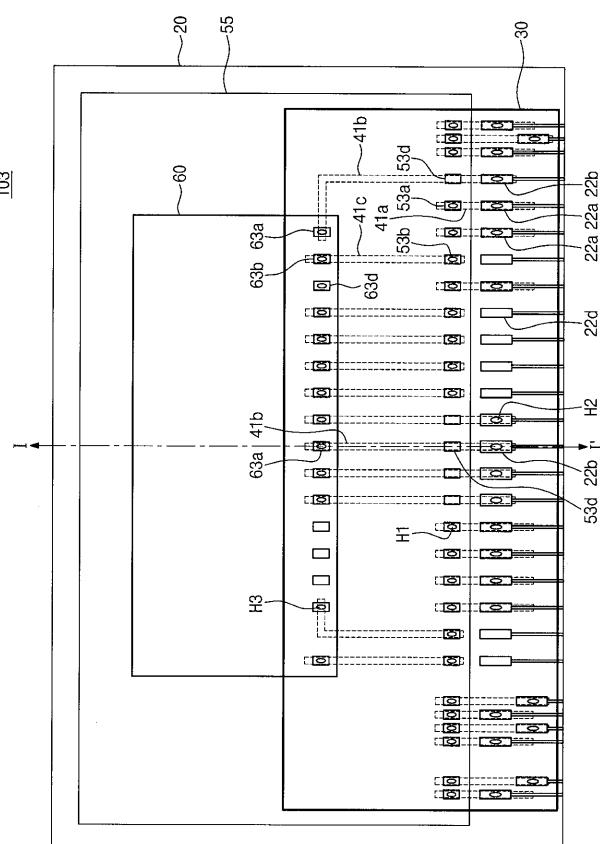

図17は本発明の実施形態4による半導体パッケージのレイアウトである。図18は図17をI-I'線に沿って切断した断面図である。

#### 【0066】

図17及び図18を参照すれば、本実施形態4による半導体パッケージ103では互いに異なる種類の半導体チップが積層される。パッケージ基板20の上に第1半導体チップ55と第2半導体チップ60とが積層される。前記第2半導体チップ60の大きさは第1半導体チップ55の大きさより小さい。前記第1半導体チップ55は前記第2半導体チップ60と異なる種類のチップであり得る。例えば、前記第1半導体チップ55はメモリチップであり、前記第2半導体チップ60はロジックチップであり得る。また、前記第1半導体チップ55はロジックチップであり、前記第2半導体チップ60はメモリチップであり得る。前記第1半導体チップ55は第1チップ接続端子53a、第2チップ接続端子5

10

20

30

40

50

3 b、及び第1ダミーチップ接続端子53dを包含できる。前記第2半導体チップ60は第3チップ接続端子63a、第4チップ接続端子63b、及び第2ダミーチップ接続端子63dを包含できる。前記パッケージ基板20は第1基板接続端子22a、第2基板接続端子22b、及びダミー基板接続端子22dを包含できる。前記第1半導体チップ55と前記第2半導体チップ60とは各々チップ接続端子53a、53b、63a、63bとダミーチップ接続端子53d、63dとを露出させる開口部7を有する保護膜5を包含できる。前記開口部7の内にはレーザー阻止パターン11が配置される。前記保護膜5と反対になる面に接着膜9が配置される。

#### 【0067】

続いて、前記半導体チップ55、60の端部と前記パッケージ基板20の端部とは絶縁膜30で覆われる。前記絶縁膜30は実施形態1で説明したようにリセスされた領域RとホールH1、H2、H3とを含む。前記ホールH1、H2、H3は前記第1及び第2チップ接続端子53a、53bの上の前記レーザー阻止パターン11を露出させる第1ホールH1、前記基板接続端子22a、22bを露出させる第2ホールH2、及び前記第3及び第4チップ接続端子63a、63bの上の前記レーザー阻止パターン11を露出させる第3ホールH3を含む。前記リセスされた領域Rの側壁30rsと底30rb及び前記ホールH1、H2、H3の側壁の表面は粗さを有する。そして、前記リセスされた領域Rと前記ホールH1、H2、H3の中に配線41a、41b、41cが配置されて前記チップ接続端子53a、53b、63a、63bと前記基板接続端子22a、22bを連結させる。前記配線41a、41b、41cは第1配線41a、第2配線41b及び第3配線41cを含む。前記第1配線41aは前記第1チップ接続端子53aと前記第1基板接続端子22aとを連結させる。前記第2配線41bは前記第3チップ接続端子63aと前記第2基板接続端子22bとを連結させる。前記第3配線41cは前記第2チップ接続端子53bと第4チップ接続端子63bとを連結させる。図18を参照すれば、前記第2配線41bは前記絶縁膜30の上に配置され、前記第2ホールH2と第3ホールH3を通じて前記第2基板接続端子22bと第3チップ接続端子63aとを連結させる。この時、前記第2配線41bの下部に第1ダミーチップ接続端子53dが配置される。しかし、前記第1ダミーチップ接続端子53dは前記絶縁膜30によって前記第2配線41bと連結されない。このように、異種チップが積層される場合、前記絶縁膜30によって配線自由度が増加され得る。

#### 【0068】

##### <実施形態5>

図19は本発明の実施形態5による半導体パッケージの断面図である。

#### 【0069】

図19を参照すれば、本実施形態5による半導体パッケージ104ではパッケージ基板20の上に1つの半導体チップ10が実装される。前記パッケージ基板20は側面に並べて配置された第1基板接続端子22aと第2基板接続端子22bとを有することができる。前記半導体チップ10の上部面には側面に並べて第1チップ接続端子3aと第2チップ接続端子3bとが配置される。前記半導体チップ10の上部面と側面、及び前記パッケージ基板20の上部面は第1絶縁膜30で覆われる。第1配線40は前記第1絶縁膜30の上に配置され、前記第1絶縁膜30を貫通して前記第1チップ接続端子3aと前記第1基板接続端子22aとを連結させる。前記第1配線40と前記第1絶縁膜40とは第2絶縁膜35で覆われる。第2配線45は前記第2絶縁膜35の上に配置され、前記第2絶縁膜35と前記第1絶縁膜30とを貫通して前記第2基板接続端子22bと前記第2チップ接続端子3bとを連結させる。前記第1絶縁膜30と前記第2絶縁膜40とは実施形態1の絶縁膜30と同様に高分子膜とこれに分散された金属含有粒子とを含む。前記第1配線40と前記第2配線45とは無電解鍍金で形成される。前記第1配線40と前記第1絶縁膜30との間、前記第2配線45と前記第2絶縁膜35との間、そして前記第2配線45と前記第1絶縁膜30との間には前記金属含有粒子を構成する金属でなされたシード膜が配置され得る。前記第1配線40と前記第2配線45は垂直的に重畠され得るが、それらの

10

20

30

40

50

間に介在された前記第2絶縁膜40によって互いに電気的に絶縁される。したがって、配線自由度を増加させ得る。その他の構成及び製造過程は実施形態1と同一類似であり得る。

### 【0070】

<実施形態6>

図20は本発明の実施形態6による半導体パッケージの断面図である。

### 【0071】

図20を参照すれば、本実施形態6による半導体パッケージ105ではパッケージ基板20の上に互いに異なる第1半導体チップ55と第2半導体チップ60とが積層されて実装される。前記第1半導体チップ55は前記第2半導体チップ60より広くて前記第2半導体チップ60の下部に配置される。前記パッケージ基板20は側面に並べて配置された第1基板接続端子22aと第2基板接続端子22bとを有することができる。前記第1半導体チップ55は第1チップ接続端子53を含む。前記第2半導体チップ60は第2チップ接続端子63を含む。第1絶縁膜30は前記第2半導体チップ60の上部面と側面、前記第1半導体チップ55の上部面と側面、そして前記パッケージ基板20の上部面をコンフォーマルに覆う。第1配線40は前記第1絶縁膜30の上に配置され、前記第1絶縁膜30を貫通して前記第1基板接続端子22aと前記第1チップ接続端子53とを連結させる。前記第1配線40と前記第1絶縁膜40とは第2絶縁膜35で覆われる。第2配線45は前記第2絶縁膜35の上に配置され、前記第2絶縁膜35と前記第1絶縁膜30とを貫通して前記第2基板接続端子22bと前記第2チップ接続端子3bとを連結させる。前記パッケージ基板20は側面に並べて配置された第1基板接続端子22aと第2基板接続端子22bとを有することができる。したがって、配線自由度を増加させ得る。その他の構成及び製造過程は実施形態5と同一類似であり得る。

10

20

30

40

50

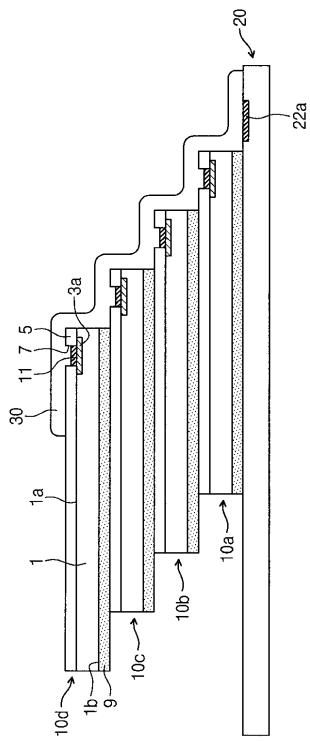

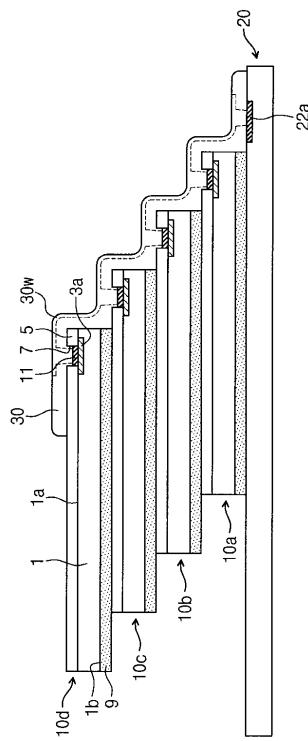

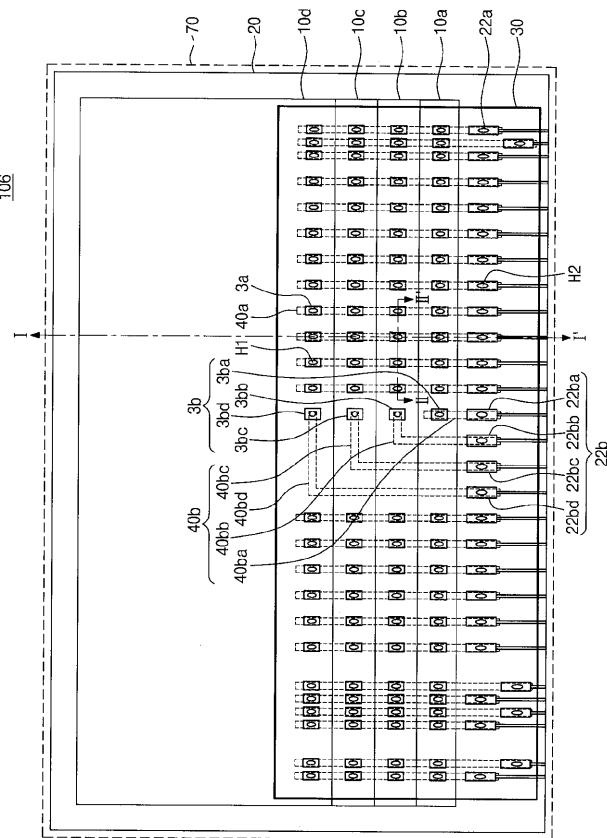

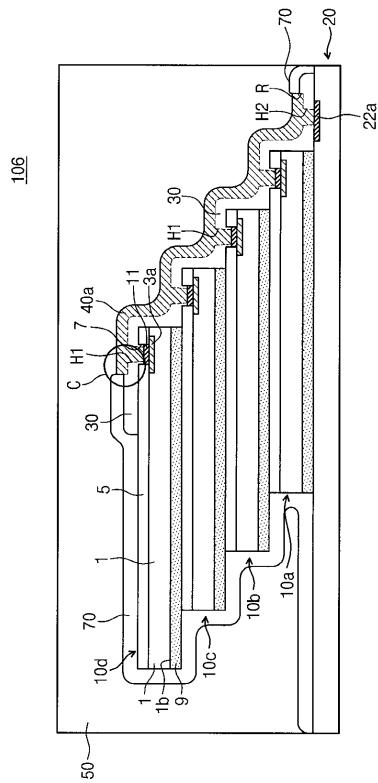

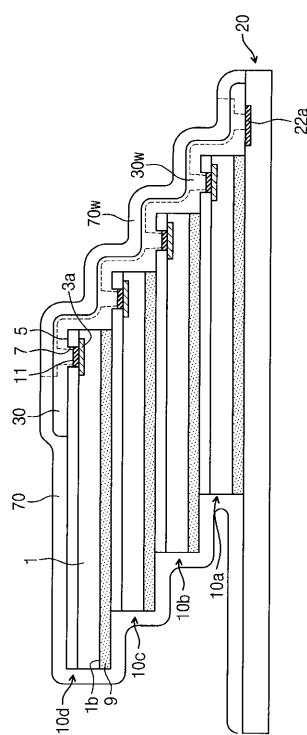

### 【0072】

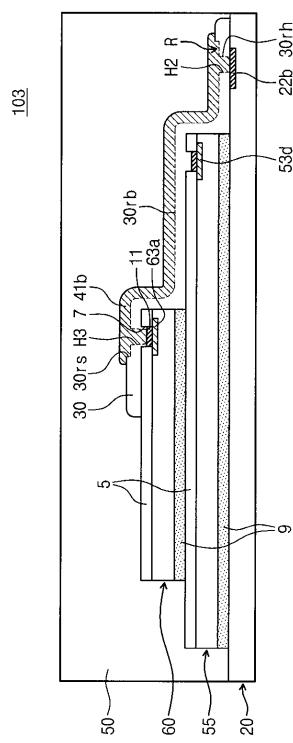

<実施形態7>

図21は本発明の実施形態7による半導体パッケージの平面図である。図22A及び図22Bは図21を各々I-I'線及びII-II'線に沿って切断した断面図である。図23は図22Aの'C'部分を拡大した拡大図である。

### 【0073】

図21、図22A、図22B、及び図23を参照すれば、本実施形態7による半導体パッケージ106は、図2の半導体パッケージ100に第2絶縁膜70が追加で配置された構造を有する。この時、図2の半導体パッケージ100の絶縁膜30は第1絶縁膜30であると称され得る。

### 【0074】

具体的には、本実施形態7による半導体パッケージ106では基板20の上に半導体チップ10a、10b、10c、10dの端部が階段形態をなし、積層され得る。前記半導体チップ10a、10b、10c、10dの端部にはチップ接続端子3aとレーザー阻止パターン11とが配置され得る。前記半導体チップ10a、10b、10c、10dの端部は第1絶縁膜30で覆われる。前記基板20の上部面、前記半導体チップ10a、10b、10c、10dの上部面、側面及び下部面、そして前記第1絶縁膜30は第2絶縁膜70で覆われる。配線40aは前記第2絶縁膜70と前記第1絶縁膜30とを貫通して前記レーザー阻止パターン11と接する。前記第1絶縁膜30は高分子膜31と金属含有粒子32とを含む。前記第2絶縁膜70は金属含有粒子32を包含しない。前記第2絶縁膜70は絶縁性物質で、例えばパリレン(parylene)、テフロン(登録商標)(teflon)、エポキシモールド化合物(epoxy mold compound)の中の少なくとも1つを包含できる。前記第1絶縁膜30はリセスされた領域RとホールH1とを包含できる。前記第2絶縁膜70の側壁は前記リセスされた領域Rの側壁と整列される。前記第2絶縁膜70の側壁の表面粗さは前記第2絶縁膜70の表面粗さより大きくなり得る。前記配線40aの上部面は前記第2絶縁膜70の上部面と同一であるか、或いは低いか、又は高い高さを有することができる。しかし、望ましくは前記配線40aの上

部面は前記第2絶縁膜70の上部面と同一であるか、或いはより低いことがあり得る。図22Bを見れば、隣接する配線40aの間の空間は第1絶縁膜30と第2絶縁膜70とで満たされ得る。

#### 【0075】

その外の構成は実施形態1と同一／類似であり得る。

#### 【0076】

図24乃至図26は図22Aの断面を有する半導体パッケージを製造する過程を順次的に示す断面図である。図27は図26の‘C’部分を拡大した拡大図である。

#### 【0077】

図24を参照すれば、図10の状態で、前記基板20の全面の上に第2絶縁膜70を形成する。前記第2絶縁膜70はコンフォーマルに形成され得る。前記第2絶縁膜70は金属含有粒子32を包含しない。前記第2絶縁膜70は絶縁性物質で、例えばパリレン(parylene)、テフロン(登録商標)(t e f l o n)、エポキシモールド化合物(Epoxy mold compound)の中で少なくとも1つに形成され得る。前記第2絶縁膜70はCVD、スピンドルコートィング(spin coating)、スプレー コートィング(spray coating)及びディッピング(dipping)等多様な方法で形成され得る。

10

#### 【0078】

図25、図26、及び図27を参照すれば、レーザーを照射して前記第2絶縁膜70の一部70wと前記第1絶縁膜30の一部30wとを除去して前記チップ接続端子3a、3b及び前記基板接続端子22a、22bを露出させるホールH1、H2を形成し、前記絶縁膜30の表面を活性化させる。前記レーザーは望ましくは赤外線(infrared)レーザー(波長約1064nm)であり得る。前記レーザーは約5W(ワット)以下の強度で照射されてよく、前記第2絶縁膜70と高分子膜31とを燃焼することができる程度の温度になるように照射され得る。前記高分子膜31がエポキシモールド化合物である場合、前記高分子膜31が約300～500温度になるように前記レーザーが照射され得る。前記レーザーによって前記高分子膜31が燃焼されて前記第1絶縁膜30の上部にはリセスされた領域RとホールH1、H2が形成される。この時、前記第2絶縁膜70の側壁、前記リセスされた領域Rの側壁30rsと底32b、そして前記ホールH1、H2の側壁30rhは粗さを有するように形成される。そして、前記リセスされた領域Rの側壁30rsと底32rb、そして前記ホールH1、H2の側壁30rhと底には前記レーザーによって燃焼されない金属含有粒子32が残る。前記レーザーによって前記金属含有粒子32で金属とこれに結合された非金属原子(酸素、窒素、炭素又は硫黄原子)との間の結合環が切れられる。この時前記非金属原子を含む化合物は蒸発され得、金属が露出された状態で残る。又は前記金属含有粒子32が絶縁性物質でコーティングされた金属粒子である場合、絶縁性物質でコーティングされた前記金属含有粒子32が残る。このように、レーザーで高分子膜31の一部を燃焼して除去し、金属含有粒子32を露出させる過程を、前記絶縁膜30を活性化させることと称する。前記残った金属含有粒子32は後続の配線40a、40bを無電解鍍金で形成するためのシード膜になり得る。前記第2絶縁膜70は前記金属含有粒子70を包含しないので、前記第2絶縁膜70のいずれの表面の上にも前記金属含有粒子32が存在しない。

20

30

40

#### 【0079】

再び図21、図22A、及び図22Bを参照すれば、実施形態1と同一／類似な方法で無電解鍍金を実施して配線40a、40bを形成する。この時、前記第2絶縁膜70が前記配線40a、40bが形成される部分を除いて全て前記基板20の上部面、前記半導体チップ10a、10b、10c、10dの上部面、側面及び下部面、そして前記第1絶縁膜30を覆う。したがって、無電解鍍金の時、化学的アタック(attack)から前記半導体チップ10a、10b、10c、10dと前記基板20とを全て保護することができる。また、無電解鍍金の時前記第2絶縁膜70無しで前記第1絶縁膜30が露出される場合、前記第1絶縁膜30の他の領域(前記配線40a、40bが形成されない領域)の

50

表面の上に前記金属含有粒子 32 が露出され得る。このように前記金属含有粒子 32 が露出される場合、僅かに金属が析出される可能性があり、金属が析出された領域に望まない鍍金層が形成される恐れがある。しかし、前記第2絶縁膜 70 が前記第1絶縁膜 30 を覆うので、前記金属含有粒子 32 が表面に露出される恐れが無くなつて、ブリッジ (bridge) 又はショート (short) 不良を防止することができる。

## 【0080】

それ以外の製造方法は実施形態 1 と同一 / 類似であり得る。

## 【0081】

上述した半導体パッケージ技術は多様な種類の半導体素子及びこれを具備するパッケージモジュールに適用され得る。

10

## 【0082】

図 28 は本発明の技術が適用された半導体パッケージを含むパッケージモジュールの例を示す図面である。図 28 を参照すれば、パッケージモジュール 1200 は半導体集積回路チップ 1220 及び QFP (Quad Flat Package) パッケージされた半導体集積回路チップ 1230 のような形態に提供され得る。本発明による半導体パッケージ技術が適用された半導体素子 1220, 1230 を基板 1210 に設置することによって、前記パッケージモジュール 1200 が形成され得る。前記パッケージモジュール 1200 は基板 1210 の一側に具備された外部連結端子 1240 を通じて外部電子装置と連結され得る。

20

## 【0083】

上述した半導体パッケージ技術は電子システムに適用され得る。図 29 は本発明の技術が適用された半導体パッケージを含む電子装置の例を示すプロック図である。図 29 を参照すれば、電子システム 1300 は制御器 1310、入出力装置 1320、及び記憶装置 1330 を包含できる。前記制御器 1310、入出力装置 1320、及び記憶装置 1330 はバス (1350, bus) を通じて結合され得る。前記バス 1350 はデータが移動する通路であり得る。例えば、前記制御器 1310 は少なくとも 1 つのマイクロプロセッサー、デジタル信号プロセッサー、マイクロコントローラ、及びこれらと同一な機能を遂行できる論理素子の中で少なくともいずれか 1 つを包含できる。前記制御器 1310 及び記憶装置 1330 は本発明による半導体パッケージを包含できる。前記入出力装置 1320 はキーパッド、キーボード及び表示装置 (display device) 等から選択された少なくとも 1 つを包含できる。前記記憶装置 1330 はデータを格納する装置である。前記記憶装置 1330 はデータ及び / 又は前記制御器 1310 によって実行される命令語等を格納できる。前記記憶装置 1330 は揮発性記憶素子及び / 又は不揮発性記憶素子を包含できる。又は、前記記憶装置 1330 はフラッシュメモリで形成され得る。例えば、モバイル機器やデスクトップコンピュータコンピューターのような情報処理システムに本発明の技術が適用されたフラッシュメモリが装着され得る。このようなフラッシュメモリは半導体ディスク装置 (SSD) で構成され得る。この場合、電子システム 1300 は大容量のデータを前記フラッシュメモリシステムに安定的に格納できる。前記電子システム 1300 は通信ネットワークへデータを伝送するか、或いは通信ネットワークからデータを受信するためのインターフェイス 1340 をさらに包含できる。前記インターフェイス 1340 は有線形態であり得る。例えば、前記インターフェイス 1340 はアンテナ又は有線トランシーバー等を包含できる。そして、図示しないが、前記電子システム 1300 には応用チップセット (Application Chipset)、カメライメージプロセッサー (Camera Image Processor : CIS)、そして入出力装置等がさらに提供されることはこの分野の通常的な知識を習得した者に明確である。

30

## 【0084】

前記電子システム 1300 はモバイルシステム、個人用コンピューター、産業用コンピューター又は多様な機能を遂行するロジックシステム等に具現され得る。例えば、前記モバイルシステムは個人携帯用情報端末機 (PDA; Personal Digital

40

50

Assistant)、携帯用コンピューター、ウェブタブレット(web tablet)、モバイルフォン(mobile phone)、無線フォン(wireless phone)、ラップトップ(laptop)コンピューター、メモリカード、デジタルミュージックシステム(digital music system)そして情報伝送/受信システムの中のいずれか1つであり得る。前記電子システム1300が無線通信を遂行できる装備である場合に、前記電子システム1300はCDMA、GSM(登録商標)、NADC、E-TDMA、WC DAM、CDMA2000のような3世代通信システムのような通信インターフェイスプロトコルで使用され得る。

#### 【0085】

上述した本発明の技術が適用された半導体素子はメモリカードの形態で提供され得る。

図30は本発明の技術が適用された半導体パッケージを含むメモリシステムの例を示すブロック図である。図30を参照すれば、メモリカード1400は不揮発性記憶素子1410及びメモリ制御器1420を包含できる。前記不揮発性記憶装置1410及び前記メモリ制御器1420はデータを格納するか、或いは格納されたデータを読み出せる。前記不揮発性記憶装置1410は本発明による半導体パッケージ技術が適用された不揮発性記憶素子の中の少なくともいずれか1つを包含できる。前記メモリ制御器1420はホスト(host)の読み出し/書き込み要請に応答して格納されたデータを読み出せるか、或いは、データを格納するように前記フラッシュ記憶装置1410を制御することができる。

#### 【0086】

以上の詳細な説明は本発明を例示することを目的とする。また、前述した内容は本発明の望ましい実施形態を示し説明するに過ぎず、本発明は多様な他の組み合わせ、変更及び環境で使用することができる。即ち、本明細書に開示された発明の概念の範囲、前述した開示内容と均等な範囲及び/又は当業界の技術又は知識の範囲の内で変更又は修正が可能である。前述した実施形態は本発明を実施するのにあて、最良の状態を説明するためのものであり、本発明のような他の発明を利用するのに当業界に公知された他の状態での実施、そして発明の具体的な適用分野及び用途で要求される多様な変更も可能である。したがって、以上の発明の詳細な説明は開示された実施状態に本発明を制限しようとする意図ではない。また、添付された請求の範囲は他の実施状態も含むものとして解釈されなければならない。

#### 【符号の説明】

#### 【0087】

- 1 . . . チップボディー

- 3 a、3 b、53 a、53 b、53 d、63 a、63 b、63 d . . . チップ接続端子

- 5 . . . 保護膜

- 7 . . . 開口部

- 9 . . . 接着膜

- 10、10 a、10 b、10 c、10 d、55、60 . . . 半導体チップ

- 11 . . . レーザー阻止パターン

- 20 . . . パッケージ基板

- 22 a、22 b、22 d . . . 基板接続端子

- 30、30 w . . . 絶縁膜、第1絶縁膜

- 31 . . . 高分子膜

- 32 . . . 金属含有粒子

- 40、40 a、40 b、41 a、41 b、41 c、45 . . . 配線

- 50 . . . モールド膜

- 70 . . . 第2絶縁膜

10

20

30

40

【図1】

【図2】

【図3A】

【図5】

【図3B】

【図6】

【図7】

【図8】

【図9】

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 3 A】

【図 1 3 B】

【 図 1 4 】

【図15】

【 図 1 6 】

【 図 17 】

【図 18】

【図 19】

【図 20】

【図 21】

【図 2 2 A】

【図 2 2 B】

【図 2 3】

【図 2 4】

【図 2 5】

【図 2 6】

【図 2 7】

【図 2 8】

【図 2 9】

【図 3 0】

【図4】

---

フロントページの続き

(72)発明者 金 泳龍

大韓民国京畿道軍浦市光亭洞（番地なし） セジョンアパート 638 - 401

(72)発明者 金 泰勳

大韓民国京畿道城南市盆唐區亭子洞（番地なし） ハンソルマウルジュゴン 6 團地アパート 607

- 1404

(72)発明者 張 チュル 容

大韓民国京畿道華城市盤松洞 93 - 7 トリンファパート 606 號

(72)発明者 李 種昊

大韓民国京畿道華城市盤松洞 74 番地 ウーリンフィルユータウンハウスアパート 112 - 505