(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4892447号

(P4892447)

(45) 発行日 平成24年3月7日(2012.3.7)

(24) 登録日 平成23年12月22日(2011.12.22)

(51) Int.CI.

H04N 1/19 (2006.01)

F 1

H04N 1/04 103E

請求項の数 8 (全 17 頁)

(21) 出願番号 特願2007-258886 (P2007-258886)

(22) 出願日 平成19年10月2日 (2007.10.2)

(65) 公開番号 特開2009-89248 (P2009-89248A)

(43) 公開日 平成21年4月23日 (2009.4.23)

審査請求日 平成22年10月1日 (2010.10.1)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 菊池 明年

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】画像読み取り装置及び画像読み取り方法

## (57) 【特許請求の範囲】

## 【請求項1】

D C モータを駆動源として複数の受光画素を有するリニアイメージセンサと原稿とを相対的に移動させて、前記原稿を読み取る画像読み取り装置であって、

前記 D C モータの回転に応じてパルスを出力するエンコーダと、

前記パルスに基づき前記リニアイメージセンサの読み取り同期信号を生成する生成手段と、

前記リニアイメージセンサの少なくとも2つの蓄積時間に対応する第1のシェーディングデータを記憶する記憶手段と、

前記記憶手段に記憶された第1のシェーディングデータに基づいて、前記読み取り同期信号をもとに設定される前記リニアイメージセンサの蓄積時間に対応する第2のシェーディングデータを求める演算を行う演算手段と、

を有することを特徴とする画像読み取り装置。

## 【請求項2】

前記第1のシェーディングデータは、前記受光画素ごとに記憶されることを特徴とする請求項1に記載の画像読み取り装置。

## 【請求項3】

前記第1のシェーディングデータは、受光画素ごとに取得した複数のシェーディングデータの、平均値を含むことを特徴とする請求項1に記載の画像読み取り装置。

## 【請求項4】

前記演算は、線形関数による演算であることを特徴とする請求項1に記載の画像読み取

10

20

置。

【請求項 5】

前記演算により求められた第2のシェーディングデータに基づいて、前記原稿を読み取ったデータを補正する補正手段と、をさらに有することを特徴とする請求項1に記載の画像読取装置。

【請求項 6】

前記第1のシェーディングデータは、黒シェーディングデータであることを特徴とする請求項1に記載の画像読取装置。

【請求項 7】

前記第1のシェーディングデータは、白シェーディングデータであることを特徴とする請求項1に記載の画像読取装置。 10

【請求項 8】

D Cモータを駆動源として複数の受光画素を有するリニアイメージセンサと原稿とを相対的に移動させて、前記原稿を読み取る画像読取方法であって、

少なくとも2つの蓄積時間に対応する前記リニアイメージセンサの第1のシェーディングデータを取得する取得工程と、

前記D Cモータの回転に応じたパルスを出力する出力工程と、

前記パルスに基づいて前記リニアイメージセンサの読み取り同期信号を生成する生成工程と

、

前記第1のシェーディングデータに基づいて、前記読み取り同期信号をもとに設定される前記リニアイメージセンサの蓄積時間に対応する第2のシェーディングデータを求める演算を行なう演算工程と、 20

を有することを特徴とする画像読取方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、読み取りデバイスにより読み取られる画像データを順次、画像処理を施しながら印刷していく画像読取装置および画像読取方法に関する。

【背景技術】

【0002】

近年、印刷機能以外にコピー機能やFAX機能を有する複合機（MFP：マルチファンクションプリンタ）が普及してきている。MFPにおいて、原稿の画像を読み取る読み取りセンサは従来ステッピングモータで駆動していた。ステッピングモータを使用する第1の理由としては、低速駆動時の安定性とフィードバック制御が不要なパルス制御の容易性がある。システムメモリが一杯になった場合、読み取った画像データの蓄積動作を停止し、モータを減速制御し、読み取り再開位置までモータのスイッチバック制御を行い読み取りを再開する。そのため、スイッチバック動作及び高精度の画像読み取り制御には、フィードバック制御が必要なDCモータは不向きであった。そこで、追従性と一定した停止位置、読み取り位置を出力パルスで制御できる等の優位性からステッピングモータを使用してきた。

【0003】

一方で、更に記録される画像の高画質化・高速化が進み、写真調の画質の画像をA4サイズで1分以内の速度でコピー処理することが可能となってきている。高速化に伴い、フラットベッドスキャン系のイメージセンサ搬送、シートスキャン系の原稿搬送時の静粛性の面で、ステッピングモータよりDCモータの方が優位性が出てきている。

【0004】

しかし、DCモータをエンコーダ同期で、読み取り画像の1ラインに相当する読み取り同期信号を生成し、読み取り動作を行うシステムを形成した場合、フィードバック制御により速度変動が発生する。速度変動量は、駆動速度、負荷によって異なるが、一般的に低速駆動時に速度変動が大きくなることが知られている。速度変動があると読み取り同期信号の周期も変動することになる。位置ズレを避けるためには、読み取り同期信号でイメージセンサの蓄積時 40

50

間隔も設定することになる。

【0005】

蓄積時間が変動すると一般的にイメージセンサの暗電流により黒レベルデータが変化する。また、センサ光源の点灯幅も影響を受け、変化する場合、白レベルデータも変化する。

【0006】

DCモータを使用した装置と別に蓄積時間の変化によりCCDの黒レベルデータを補正するものとして、特許文献1に記載のイメージスキャナの黒レベル補正装置が知られている。

【0007】

また、蓄積時間に対応した暗出力補正用データテーブルに基づいて暗出力補正を行うものとして、特許文献2に記載の画像読取装置が知られている。

【特許文献1】特開平8-237480公報

【特許文献2】特開平11-69162公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

特許文献1には、DCモータを使用した装置とは別に、蓄積時間の変化により黒レベルデータが変動するのを防止する装置が記載されている。まず蓄積時間設定部によって設定されている蓄積時間データをD/A変換回路によってアナログ信号に変換する。次に補正データメモリに記憶されている第1の黒レベル補正データもD/A変換回路によってアナログ信号に変換し、乗算処理を行い、画像データの黒レベル補正を行うための第2の黒レベル補正データを得るものとして記載されている。

【0009】

しかしながら、D/A変換回路が2回路とアナログ乗算回路、補正データメモリと蓄積時間設定をD/A変換部へ渡す構成が必要であり、部品点数、エリアの面でコストアップ等が考えられる。

【0010】

また、アナログ補正なので、アナログデバイスのタイミング制約及び調整等が必要になる。更に、ライン単位のアナログ補正なので、画素単位の補正ができないという問題がある。

【0011】

特許文献2には、設定した蓄積時間に対し、所定の蓄積時間範囲に対応する補正テーブルを選択し、暗出力補正を行う画像読取装置が記載されている。

【0012】

しかしながら特許文献2では、蓄積時間に対し、複数の補正テーブルから1つを選択することで補正是画素単位で可能であるが、画素単位で蓄積時間にバラツキのあるシェーディング補正はできないという問題がある。

【0013】

また、DCモータのエンコーダ同期の読取同期装置においては、蓄積時間はDCモータの速度変動の影響を受け、無段階で変化する。そのため任意の蓄積時間に対して前記の補正を適用しても有効ではない。

【0014】

本発明は、DCモータのエンコーダに同期して読取動作を行う画像読取装置において、イメージセンサの暗電流、白レベルの変動要因を基準レベルに補正できるDCモータの画像読取制御装置を提供することを目的とする。

【0015】

更に、各種イメージセンサの特性及びバラツキ要因を吸収できるDCモータの画像読取装置を提供することを目的とする。

【課題を解決するための手段】

10

20

30

40

50

## 【0016】

本発明は、DCモータを駆動源として複数の受光画素を有するリニアイメージセンサと原稿とを相対的に移動させて、前記原稿を読み取る画像読み取り装置であって、前記DCモータの回転に応じてパルスを出力するエンコーダと、前記パルスに基づき前記リニアイメージセンサの読み取り同期信号を生成する生成手段と、前記リニアイメージセンサの少なくとも2つの蓄積時間に対応する第1のシェーディングデータを記憶する記憶手段と、前記記憶手段に記憶された第1のシェーディングデータに基づいて、前記読み取り同期信号をもとに設定される前記リニアイメージセンサの蓄積時間に対応する第2のシェーディングデータを求める演算を行う演算手段と、を有することを特徴とする画像読み取り装置。

## 【発明の効果】

10

## 【0017】

以上説明した様に本発明によれば、DCモータのエンコーダ同期読み取り構成でも、任意の蓄積時間に対する暗電流成分を画素単位で正確に補正できるという効果を有する。また、DCモータのエンコーダ同期の画像読み取り制御構成でも、任意の蓄積時間に対する暗電流成分やデータ変動を正確に補正できるという効果を有する。

## 【発明を実施するための最良の形態】

## 【0018】

本発明を実施するための最良の形態について、以下に図面を参照して説明する。

## 【0019】

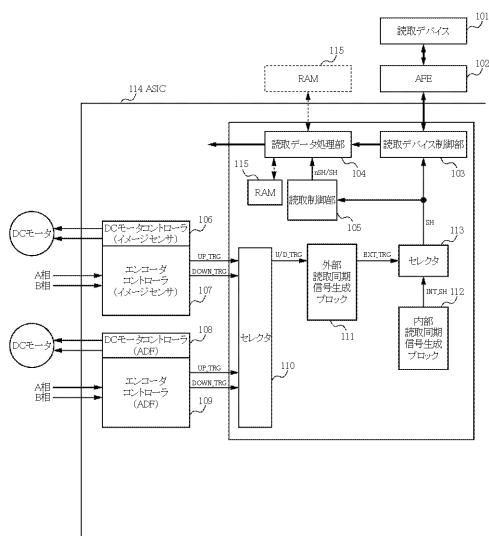

図1は本発明を適用できる画像読み取り制御装置のブロック図である。

20

101は読み取りデバイスで、原稿からの反射光を光電変換しRGBのアナログ信号を出力するCCD(電荷結合素子)やCIS(コンタクトイメージセンサ)といった複数の受光画素から成る。それらが一列に配置されているリニアイメージセンサである。102は前記アナログ信号をデジタル信号にA/D変換するAFE(アナログフロントエンド)デバイスから構成される。

## 【0020】

103は読み取りデバイス制御部であり、読み取りデバイス101及びAFE102へ制御信号を出力する。読み取りデバイス制御部103は、読み取りデバイス101からのRGBのアナログ信号をAFE102経由でデジタル信号として取り込み、データの並べ替え、パッキング等を行う読み取りデータ処理部104に画像データを転送する。さらに読み取りデバイス制御部103では、センサー光源の調光制御、入力される画像信号を基にフィードバックPWM制御等を行う。

30

## 【0021】

読み取りデータ処理部104では、後述するエンコーダブロックからの出力信号に同期して生成されるライン単位又は蓄積時間単位の外部読み取り同期信号周期を計測する手段により、蓄積時間を毎ライン計測する。前記計測結果に基づき、シェーディングデータを画素単位又はライン単位で、蓄積時間で線形補間後、本来のシェーディング補正を行う。

## 【0022】

読み取り制御部105では、画像データの取り込み(読み込み)のスタート、終了の制御を行う。106はイメージセンサ用の第1のDCモータコントローラである。116はイメージセンサ駆動用の第1のDCモータである。第1のDCモータコントローラ106は、第1のDCモータ116の駆動制御を行う。107はイメージセンサ用の第1のエンコーダコントローラであり、第1のDCモータ116の回転に応じて位相の異なるA相、B相のパルスを発生するものである。108は不図示のADF(オートドキュメントフィーダ)用の第2のDCモータコントローラである。117はADF駆動用の第2のDCモータである。109はADF用の第2のエンコーダコントローラであり、第1のエンコーダコントローラ107と同様の制御を行う。すなわち、第2のDCモータ117の回転に応じて位相の異なるA相、B相のパルスを発生する。なお、パルス発生機構としてはロータリーエンコーダが用いられるのが一般的である。

40

## 【0023】

50

D C モータコントローラ 106、108 はそれぞれ、エンコーダコントローラ 107、109 での処理に従い、D C モータ 116、117 への E n a b l e 信号、速度と回転方向の情報を持つ P h a s e 信号を出力し、D C モータのフィードバック制御を行う。D C モータ 116 は原稿台の上に載置された原稿に対してイメージセンサを走査するための駆動源である。また D C モータ 117 は不図示のオートドキュメントフィーダー( A D F )の駆動源としてするものである。A D F はイメージセンサに対して原稿を移動させる機構である。セレクタ 110 は、D C モータ 116 と D C モータ 117 の 2 つの D C モータ制御の切り換えを行う。これは回路規模を縮小するために選択できるようにした 1 例を示している。エンコーダブロック含め D C モータ制御部が同じ場合、更に外側でセレクトする構成も考えられる。また、図 1 の例ではエンコーダパルスから位相が正転方向か反転方向かを選択して出力する機能を有する構成を示している。1 つの D C モータのみ制御する場合、セレクタ無しの構成も当然考えられる。

#### 【 0 0 2 4 】

外部トリガから読み取同期信号を生成する外部読み取同期信号生成ブロック 111 は、正転位相パルス、反転位相パルス、片エッジ、両エッジの情報からパルス数をカウントする。そのカウント値に基づいて、読み取解像度の 1 ライン又は複数ラインとなる基準の外部読み取同期信号を生成する。内部読み取同期信号生成ブロック 112 は、不図示の内部タイマから読み取解像度の 1 ライン又は複数ラインとなる基準の内部読み取同期信号を生成する。内部読み取同期信号生成ブロック 112 は、非読み取動作時においてイメージセンサに発生する暗電流を除くために周期的に読み取同期信号( S H )を発生させるものである。

#### 【 0 0 2 5 】

セレクタ 113 は、イメージセンサの空送り量を確保したい場合や、D C モータを一定速で制御している以外は、読み取デバイスへの同期信号が可変、又は出力されない状況になる。そのため内部生成された読み取同期信号と切り替え可能な構成であることを示している。

#### 【 0 0 2 6 】

R A M 115 は、通常のシェーディングデータ及び画素単位補正用の複数のシェーディングデータを格納するためのメモリで、A S I C 114 内に S R A M 等で内蔵メモリとして構成する場合、D R A M 等で外部メモリとして構成する場合も考えられる。

#### 【 0 0 2 7 】

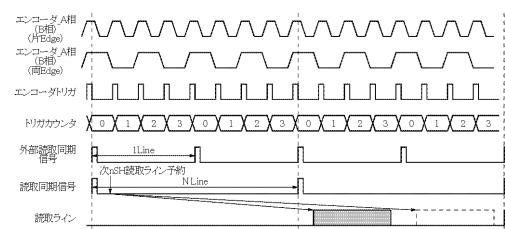

図 2 は本発明を適用できる画像読み取制御装置のエンコーダ等の外部パルスを基に読み取同期信号を生成するタイミングの一例を示す図である。

#### 【 0 0 2 8 】

エンコーダ A 相( B 相 )は、図 1 のエンコーダブロック 107、109 へ入力されるエンコーダ信号出力を表している。例えば、立ち上がりの片エッジサンプリングの場合には、立ち上がりをエンコーダブロックでフィルタリングして、ノイズ除去後、エンコーダパルス U P / D O W N \_ T R G として出力する。または、両エッジサンプリングの場合も同様に、フィルタリングして、ノイズ除去後、エンコーダパルス U P / D O W N \_ T R G として出力する。図 2 では、片エッジ、両エッジサンプリングも同一図で示すために、合わせて示してあるが、特に各々の相関関係は無い。U P / D O W N \_ T R G の U P と D O W N は、A 相、B 相のエンコーダの位相情報を D C モータの回転方向を判別し、U P と D O W N に分けた信号を表す。

#### 【 0 0 2 9 】

トリガカウンタ( T R G \_ c o u n t e r )はエンコーダパルスをカウントするものである。前記エンコーダパルス U P / D O W N \_ T R G をカウントし、本例では 0 から 3 までカウントすることにより副走査読み取解像度の 1 ラインとなる基準の外部読み取同期信号( E X T \_ S H )を生成する。更に外部読み取同期信号( E X T \_ S H )をカウントし、副走査読み取解像度の N ラインとなる n S H 信号を図 1 の読み取制御部( r e a d \_ c t r l \_ b l o c k ) 105 で生成し、出力する。これは、複数ラインの同期信号を生成し、ファームで割り込み制御することで、ファームの割り込み処理の負荷を軽減する一例である。例

10

20

30

40

50

えば、Nライン毎に読み取り蓄積ラインを制御したり、モータ等の駆動制御もNライン単位で、トリガ予約型で処理することで、ファームの割り込み処理を軽減した構成を一例として示す。

#### 【0030】

ここで、副走査とは、読み取りデバイスを移動する方向または読み取り対象となる原稿を搬送する方向を指す。

#### 【0031】

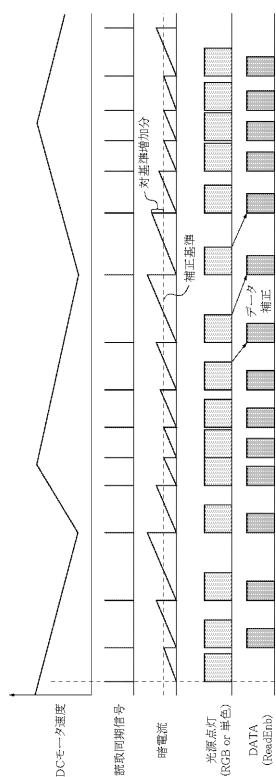

図3は本発明を適用できる画像読み取り制御装置のモータ速度変動に対する読み取り同期信号と暗電流データの増加の一例を模式的に示す図である。

#### 【0032】

DCモータのサーボ制御により、モータ速度が変動することがある。速度変動に伴い、エンコーダからのパルスに基づいて生成されるライン単位の外部読み取り同期信号(SHDIV)の生成タイミングも変動する。モータ速度が早ければ、SHDIVの時間間隔が短くなり、逆にモータ速度が遅ければその間隔は長くなることを示している。ここで、光電変換にあたって必要な最小の蓄積時間を $T_{typ}$ (= $T_{min}$ )とすると、 $T_{typ}$ に対応する黒シェーディングデータは、点線のレベルとなる。暗電流は蓄積時間が延びるほど増加する特性がある。蓄積時間が延びたことで点線で示す補正基準レベルを超える増加分が、補正が必要な暗電流成分等の増加データ分になる。この例では、光源にはLEDを使用しており、図3において光源点灯時間は各SHDIVの間隔に関わらず一定になっている。ある読み取り同期信号区間での光源点灯によりイメージセンサで蓄積されたそのデータを光源点灯の次の同期タイミングで補正用シェーディングデータに反映しながらデータ補正を行う場合を示している。

10

20

#### 【0033】

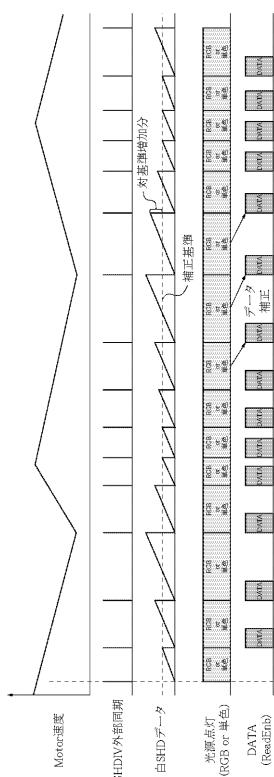

図4は本発明を適用できる画像読み取り制御装置のモータ速度変動に対する読み取り同期信号と白シェーディングのデータ増加の一例を示す図である。

#### 【0034】

図3における説明同様、DCモータのサーボ制御により、モータ速度が変動する。速度変動に伴い、エンコーダからのパルスに基づいて生成されるライン単位の外部読み取り同期信号(SHDIV)の生成タイミングも変動する。最小の蓄積時間を $T_{typ}$ (= $T_{min}$ )とすると、その時の白シェーディングデータは、点線のレベルが補正基準となる。例えば、光源点灯幅が基準となる蓄積時間 $T_{typ}$ を超えるような場合、蓄積時間が延びたことで補正基準レベルを超える増加分が、補正が必要な白レベルの増加データ分になる。そのデータを光源点灯の次の同期タイミングで補正用シェーディングデータに反映しながらデータ補正を行う場合を示している。

30

#### 【実施例1】

#### 【0035】

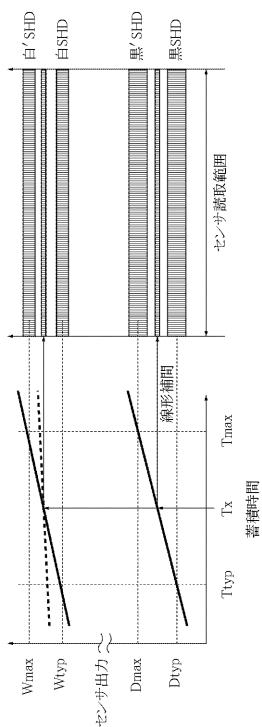

以下、実施例1として、受光画素ごとの黒および白シェーディングデータ補正について説明する。図5は実施例1にかかる蓄積時間と黒及び白のシェーディングデータの線形補間法の関係の一例を示す図である。図5の右側において、イメージセンサの主走査方向の位置をセンサ読み取り範囲として横軸にとり、縦軸はセンサの出力を表している。また、黒SHD、黒'SHD、白SHD、白'SHDに対応するハッチのかけられた領域はそれぞれ、各受光画素のシェーディングデータのバラツキがあることを表している。ここで、光電変換に必要な最小または基準となる蓄積時間を $T_{typ}$ とし、 $T_{typ}$ に対応する白シェーディングデータを $W_{typ}$ 、黒シェーディングデータを $D_{typ}$ とする。また最大の蓄積時間を $T_{max}$ とし、 $T_{max}$ に対応する白シェーディングデータを $W_{max}$ 、黒シェーディングデータを $D_{max}$ とする。左側の図は、それらの蓄積時間 $T_{typ}$ 、 $T_{max}$ を設定してそれぞれのシェーディングデータ $D_{typ}$ 、 $D_{max}$ 、 $W_{typ}$ 、 $W_{max}$ をもとに線形関数により任意の蓄積時間 $T_x$ に対応するシェーディングデータを求めるこことを示している。このように、イメージセンサの受光画素ごとでその特性にバラツキがある。そのため、同じ蓄積時間が設定されても受光画素ごとに見ると発生する暗電流に差が

40

50

50

生じる。本実施例では、個々の受光画素ごとにシェーディングデータを取得して補正を行う例を示している。まず、蓄積時間  $T_{t y p}$  に対する黒シェーディングデータ  $D_{t y p}$  、白シェーディングデータ  $W_{t y p}$  が読取モードに応じた解像度分取得し内蔵メモリまたは外部メモリに保持する。それら複数のシェーディングデータは、圧縮した形で保持しても構わない。そして、蓄積時間  $T_{m a x}$  として、モータの速度変動により変動する蓄積時間の最大値又はそれ以上の値になる蓄積時間に設定する。これら複数の蓄積時間に対するシェーディングデータは、内部タイマーや外部同期信号を起動し、取得する。最大の蓄積時間  $T_{m a x}$  に対する黒シェーディングデータ  $D_{m a x}$  、白シェーディングデータ  $W_{m a x}$  も読取モードに応じた解像度の有効画素  $\times$  分、取得する。

## 【0036】

10

これにより、2つの異なる蓄積時間に対応するシェーディングデータが取得される。

## 【0037】

ここで、蓄積時間  $T_x$  は、実際の読取動作におけるDCモータ駆動中の任意の蓄積時間を示している。

## 【0038】

取得した2つの異なる蓄積時間に対応するシェーディングデータに基づいて、蓄積時間  $T_x$  におけるシェーディングデータの補正手順の一例を下記に示す。

- (1) 蓄積時間  $T_{t y p}$  時の黒シェーディングデータ  $D_{t y p} (x)$  をメモリに格納する。

- (2) 蓄積時間  $T_{t y p}$  時の白シェーディングデータ  $W_{t y p} (x)$  をメモリに格納する。

- (3) 蓄積時間  $T_{m a x}$  時の黒シェーディングデータ  $D_{m a x} (x)$  をメモリに格納する。

- (4) 蓄積時間  $T_{m a x}$  時の白シェーディングデータ  $W_{m a x} (x)$  をメモリに格納する。

- (5) 任意の蓄積時間に対応する黒シェーディングデータを  $D' (x)$  として、それを求める関数は以下で示される。

$$D' (x) = D_{t y p} (x) + (D_{m a x} (x) - D_{t y p} (x)) \times (T_x - T_{t y p}) / (T_{m a x} - T_{t y p})$$

すなわち、 $D_{t y p} (x)$ 、 $D_{m a x} (x)$ 、 $T_{m a x}$ 、 $T_{t y p}$  それぞれの値から導かれる線形関数により補正された黒シェーディングデータが求まる。

## 【0039】

30

こうして求められた  $D' (x)$  により黒シェーディングデータ補正を画素単位で全有効画素に対して行う。

- (6) 任意の蓄積時間に対応する白シェーディングデータを  $W' (x)$  とすると、(5) と同様に

$$W' (x) = W_{t y p} (x) + (W_{m a x} (x) - W_{t y p} (x)) \times (T_x - T_{t y p}) / (T_{m a x} - T_{t y p})$$

となり、 $W_{t y p} (x)$ 、 $W_{m a x} (x)$ 、 $T_{m a x}$ 、 $T_{t y p}$  それぞれの値から導かれる線形関数により補正されたシェーディングデータが求まる。この  $W' (x)$  により白シェーディングデータ補正を画素単位で全有効画素に対して行う。

## 【0040】

40

上記より、下記に示すように補正後の画像読取信号出力を  $V_{out}$ 、読み取った画像データの入力信号を  $V_{in}$ 、 $Const$  を補正係数、 $Offset$  を微調整用の値とする。

## 【0041】

そして、上記式より求めたシェーディングデータ  $D'$  により補正を施す。

$$V_{out} = Const * (V_{in} - D') / (W' - D') + Offset$$

(5)、(6) の演算回路は、ファームウェア構成、ハードウェア構成、又はファーム / ハードウェアの混在構成の場合も同様に考えられる。また、圧縮データ形式でメモリに格納されている場合は、逐次デコードしながら補正演算を行う。

50

## 【0042】

更に、全有効画素に対して、シェーディングデータの補正を行うが、実際は、画素単位で補正した黒及び白、黒又は白の補正データで、通常のシェーディング補正も同時に行う場合が、一般的である。但し、前記処理手順以外は、システムにより任意であり限定されないため、省略する。

## 【0043】

データ補正の線形性が任意の蓄積時間間に制限される場合、複数の蓄積時間間に上記の同様の処理を行うことで、対応できることが容易に考えられる。

## 【0044】

蓄積時間の  $T_{typ}$  を  $T_{n-1}$ 、 $T_{max}$  を  $T_n$  として、任意の蓄積時間  $T_x$  が、2点の蓄積時間の格納データ間にあることだけを判別する手段があれば可能である。 10

## 【0045】

また、前記補正が、黒シェーディングデータに対してのみ、有効である場合、黒シェーディングに対する(1)、(3)、(5)の処理だけで構成しても構わない。同様に、前記補正が、白シェーディングデータに対してのみ、有効である場合、白シェーディングに対する(2)、(4)、(6)の処理だけで構成しても構わない。

## 【0046】

このように、異なる2つの蓄積時間に対応する黒、白シェーディングデータをそれぞれ受光画素ごとに取得し、任意の蓄積時間に対応する黒、白の補正したシェーディングデータを線形関数により求める。これにより、蓄積時間に適したシェーディングデータを適用して読み取った画像データを適切に補正することができる。 20

## 【0047】

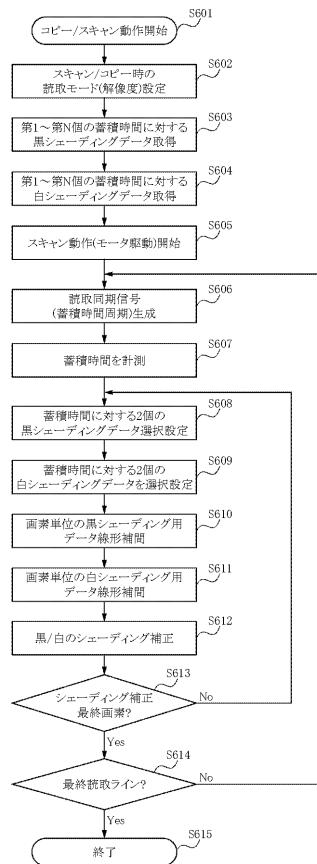

図6は、実施例1における黒及び白のシェーディングデータの画素単位の線形補間のデータ補正の一例を示すフローチャートである。

## 【0048】

操作キーにより、コピー又はスキャン動作を開始する(S601)。選択されたスキャン/コピー時の読取モード(解像度)を設定する(S602)。第1と第2の蓄積時間に対する黒シェーディングデータを取得する(S603)。ここでは、更に複数の蓄積時間に対応するシェーディングデータが必要な場合について示しており、第Nまでの蓄積時間に対する黒シェーディングデータを取得する。例えば、蓄積時間の短い方から  $T_1 < T_2 < T_3 < \dots < T_n$  で、左記に対応したシェーディングデータの関係で取得する。(S603)の黒シェーディングの場合と同様に白シェーディングデータも複数取得する(S604)。続いて、スキャン動作に移行して、DCモータ駆動を開始する(S605)。モータ駆動が開始されると図2にあるようにエンコーダ信号により、予め設定されたパルス数に基づいて読取同期信号が生成される(S606)。読取同期信号が蓄積時間周期に相当しており、イメージセンサへの駆動信号と読み取った画像のデータ入力が開始される。前記読取同期信号を毎ライン、CIS系は、LED等の単色ラインに対して計測し、蓄積時間を内部レジスタやメモリに保持する(S607)。続いて、第1と第2の蓄積時間に対する黒シェーディングデータのメモリ等からの読み出しを設定し(S608)、画素単位で、2点の黒シェーディングデータを読み出す。更に複数必要な場合は、蓄積時間がどの蓄積時間内にあるかを判別して、前後の蓄積時間に対する黒シェーディングデータのメモリ等からの読み出しを設定し(S608)、画素単位で、選択設定された2点の黒シェーディングデータを読み出す。(S608)の黒シェーディングの場合と同様に白シェーディングデータも選択設定する(S609)。続いて、図5の説明にあるようにシェーディングデータの補正手順に従い、画素単位の黒シェーディングデータを線形補間する(S610)。(S610)の黒シェーディングの場合と同様に白シェーディングデータも選択設定する(S611)。続いて、前記により補正された黒及び白、黒又は白のシェーディングデータを用いて、例えば下記に示すシェーディング補正を実施する(S612)。

。

$V_{out} = Const * (V_{in} - D') / (W' - D') + Offset$

10

20

30

40

50

ここで、 $V_{out}$ ：出力データ、 $V_{in}$ ：入力データ、 $Const$ ：補正係数、 $OffSet$ ：微調整用、 $D'$ ：補正後の黒シェーディングデータ、 $W'$ ：補正後の白シェーディングデータをそれぞれ示す。

#### 【0049】

1ラインのシェーディング補正が最終画素であるかを判別し(S613)、最終画素でない場合(No)、ステップ(S608)に戻り、次の画素の補正を繰り返す。ステップ(S613)で、最終画素である場合(Yes)、更に最終読み取りラインであるかを判別し(S614)、最終読み取りラインでない場合(No)、ステップ(S606)に戻り、次のラインの読み取り同期信号の生成と蓄積時間の計測を繰り返す。ステップ(S614)で、最終読み取りラインである場合(Yes)、コピー／スキャン動作を終了する(S615)。

10

#### 【0050】

また、前記補正が、黒シェーディングデータに対してのみ、有効である場合、黒シェーディングに対するフロー処理だけで構成しても構わない。同様に、前記補正が、白シェーディングデータに対してのみ、有効である場合、白シェーディングに対するフロー処理だけで構成しても構わない。

#### 【実施例2】

#### 【0051】

以下、実施例2として、受光画素ごとの黒および白シェーディングデータを取得し、それらの平均値を採用してシェーディングデータを補正する例について説明する。

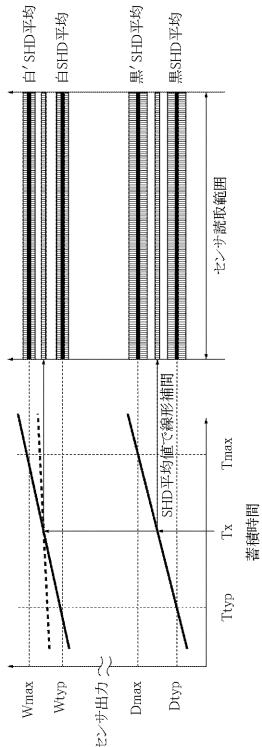

#### 【0052】

図7は実施例2における蓄積時間と黒及び白のシェーディングデータの平均と線形補間の関係の一例を示す図である。図6の右側において、イメージセンサの主走査方向をセンサ読み取り範囲として横軸にとり、縦軸はセンサの出力を表している。また、黒SHD平均、黒'SHD平均、白SHD平均、白'SHD平均に対応するハッチのかけられた領域はそれぞれ、各受光画素のシェーディングデータのバラツキを表している。ここで、光電変換に必要な最小または基準となる蓄積時間を $T_{typ}$ とし、 $T_{typ}$ に対応する白シェーディングデータを $W_{typ}$ 、黒シェーディングデータを $D_{typ}$ とする。また最大の蓄積時間を $T_{max}$ とし、 $T_{max}$ に対応する白シェーディングデータを $W_{max}$ 、黒シェーディングデータを $D_{max}$ とする。左側の図は、それらの蓄積時間 $T_{typ}$ 、 $T_{max}$ を設定してそれぞれのシェーディングデータ $D_{typ}$ 、 $D_{max}$ 、 $W_{typ}$ 、 $W_{max}$ から線形関数により任意の蓄積時間 $T_x$ に対応するシェーディングデータを求ることを示している。

20

#### 【0053】

本実施例2では、受光画素ごとに補正をかけるのではなく、受光画素ごとのばらつきに起因するシェーディングデータの平均値を保持する。これにより処理負荷低減やメモリ容量の削減を図った例を示している。最小又は基準となる蓄積時間 $T_{typ}$ に対する黒シェーディングデータ $D_{typ}$ 、白シェーディングデータ $W_{typ}$ が読み取りモードに応じた解像度分、取得する。前記シェーディングデータは、圧縮した形で、内蔵メモリや外部メモリに保持しても構わない。蓄積時間 $T_{max}$ は、モータの速度変動により変動する蓄積時間の最大値又はそれ以上の値になる蓄積時間に設定する。複数の蓄積時間に対するシェーディングデータは、内部タイマーや外部同期信号を起動し、取得する。蓄積時間 $T_{max}$ に対する黒シェーディングデータ $D_{max}$ 、白シェーディングデータ $W_{max}$ も読み取りモードに応じた解像度の有効画素×分、取得しながら平均データ又は加算データのみ記憶する。

30

#### 【0054】

蓄積時間 $T_x$ は、DCモータ駆動中の任意の蓄積時間を示している。

#### 【0055】

取得したシェーディングデータの補正手順の一例を下記に示す。

(1) 蓄積時間 $T_{typ}$ 時の黒シェーディングデータ $D_{typ}$ ( $\times$ )をメモリに格納する。

40

及び $D_{typ}$ ( $\times$ )の平均データをメモリ、レジスタ等に記憶する。

50

(2) 蓄積時間  $T_{typ}$  時の白シェーディングデータ  $W_{typ}(x)$  をメモリに格納する。

。

及び  $W_{typ}(x)$  の平均データをメモリ、レジスタ等に記憶する。

(3) 蓄積時間  $T_{max}$  時の黒シェーディングデータ  $D_{max}(x)$  の平均データ  $D_{max\_ave}$  をメモリ、レジスタ等に記憶する。  $D_{max\_ave}$  : 蓄積時間  $T_{max}$  に対応する受光画素ごとの黒シェーディングデータを平均した値

(4) 蓄積時間  $T_{max}$  時の白シェーディングデータ  $W_{max}(x)$  の平均データ  $W_{max\_ave}$  をメモリ、レジスタ等に記憶する。  $W_{max\_ave}$  : 蓄積時間  $T_{max}$  に対応する受光画素ごとの白シェーディングデータを平均した値

(5) 任意の蓄積時間に対応する黒シェーディングデータを  $D'(x)$  として、それを求める関数は以下で示される。  $D'(x) = D_{typ}(x) + (D_{max\_ave} - D_{typ\_ave}) \times (T_x - T_{typ}) / (T_{max} - T_{typ})$  10

すなわち、  $D_{typ}(x)$  、  $D_{max\_ave}$  、  $T_{max}$  、  $T_{typ}$  それぞれの値から導かれる線形関数により補正された黒シェーディングデータが求まる。この  $D'(x)$  により、黒シェーディングデータ補正を一律平均データで全有効画素に対して行う。

(6) 任意の蓄積時間に対応する白シェーディングデータを  $W'(x)$  とすると、(5) と同様に

$$W'(x) = W_{typ}(x) + (W_{max\_ave} - W_{typ\_ave}) \times (T_x - T_{typ}) / (T_{max} - T_{typ})$$

となり、  $W_{typ}(x)$  、  $W_{max\_ave}$  、  $T_{max\_ave}$  、  $T_{typ}$  それぞれの値から導かれる線形関数により補正されたシェーディングデータが求まる。この  $W'(x)$  により白シェーディングデータ補正を一律平均データで全有効画素に対して行う。 20

#### 【0056】

(5)、(6) の演算回路は、ファームウェア構成、ハードウェア構成、又はファーム / ハードウェアの混在構成の場合も同様に考えられる。また、圧縮データ形式でメモリに格納されている場合は、逐次デコードしながら補正演算を行う。

#### 【0057】

更に、全有効画素に対して、シェーディングデータの補正を行うが、実際は、画素単位で補正した黒及び白、黒又は白の補正データで、通常のシェーディング補正も同時に行う場合が、一般的である。但し、前記処理手順以外は、システムにより任意であり限定されないため、省略する。 30

#### 【0058】

図5の場合と同様にデータ補正の線形性が任意の蓄積時間間に制限される場合、複数の蓄積時間間に上記の同様の処理を行うことで、対応できることが容易に考えられる。

#### 【0059】

蓄積時間の  $T_{typ}$  を  $T_{n-1}$  、  $T_{max}$  を  $T_n$  として、任意の蓄積時間  $T_x$  が、2点の蓄積時間の格納データ間にあることだけを判別する手段があれば可能である。

#### 【0060】

また、平均データを用いた上記の構成の場合は、入力データを補正しても同様の構成で考えることができ、シェーディングブロックに手を入れなくても回路追加で構成できる利点がある。 40

#### 【0061】

また、前記補正が、黒シェーディングデータに対してのみ、有効である場合、黒シェーディングに対する(1)、(3)、(5)の処理だけで構成しても構わない。

#### 【0062】

また(1)、(3)、(5)の蓄積時間でのデータ補正が、黒シェーディングデータに対する補正でよい場合、(5)の右辺の蓄積時間補正分

$$Ddc = (D_{max\_ave} - D_{typ\_ave}) \times (T_x - T_{typ}) / (T_{max} - T_{typ})$$

を入力データ  $V_{in}$  から減算することで、例えば下記に示すような蓄積時間のシェーディ 50

ング補正に書き換えることができる。ここで、補正後の画像読取信号出力を  $V_{out}$ 、読み取った画像データの入力信号を  $V_{in}$ 、Const を補正係数、Offset を微調整用の値とする。 $V_{out} = Const * \{ (V_{in} - Ddc) - Dtype \} / (Wtyp - Dtype) + Offset$

上記演算方法でも同様に、蓄積時間での黒シェーディング補正を実現することができる。

#### 【0063】

同様に、前記補正が、白シェーディングデータに対してのみ、有効である場合、白シェーディングに対する(2)、(4)、(6)の処理だけで構成しても構わない。

#### 【0064】

前記同様、(6)の右辺の蓄積時間補正分

$$Wdc = (Wmax\_ave - Wtyp\_ave) \times (Tx - Ttyp) / (Tmax - Ttyp)$$

を入力データ  $V_{in}$  から減算することで、例えば下記に示すような蓄積時間のシェーディング補正に書き換えることができる。

$$V_{out} = Const * \{ (V_{in} - Wdc) - Dtype \} / (Wtyp - Dtype) + Offset$$

上記演算方法でも同様に、蓄積時間での白シェーディング補正を実現することができる。

#### 【0065】

更に、黒と白の両方で処理しても同様に蓄積時間でのシェーディング補正が実現できることが容易に考えられる。

#### 【0066】

このように、異なる2つの蓄積時間に対応する黒、白シェーディングデータをイメージセンサ単位で見た平均値を取得し、任意の蓄積時間に対応する黒、白の補正したシェーディングデータを線形関数により求める。これにより、蓄積時間に適したシェーディングデータを適用して読み取った画像データを適切に補正することができる。

#### 【0067】

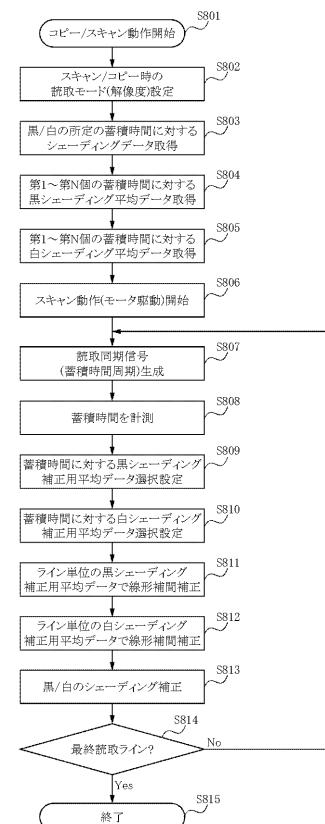

図8は、実施例2における黒及び白のシェーディングデータのライン単位の平均データでの線形補間法によるデータ補正の一例を示すフローチャートである。

#### 【0068】

操作キーにより、コピー又はスキャン動作を開始する(S801)。選択されたスキャン/コピー時の読み取りモード(解像度)を設定する(S802)。黒及び白、黒又は白の基準になる所定の蓄積時間に対するシェーディングデータを取得する(S803)。続いて、第1(例えば前記基準の場合)と第2の蓄積時間に対する黒シェーディングデータの平均値を取得する(S804)。更に複数の蓄積時間に対するシェーディングデータが必要な場合について示しており、第Nまでの蓄積時間に対する黒シェーディングデータの平均値を取得する。例えば、蓄積時間の短い方から  $T_1 < T_2 < T_3 < \dots < T_n$  で、左記に対応したシェーディングデータの平均値の関係で取得する。(S804)の黒シェーディングの場合と同様に白シェーディングデータも複数取得する(S805)。続いて、スキャン動作に移行してDCモータ駆動を開始する(S806)。モータ駆動が開始されると図2のようにエンコーダ信号により、予め設定されたパルス数で読み取り同期信号が生成される(S807)。読み取り同期信号が蓄積時間周期になっており、イメージセンサへの駆動信号とデータ入力が開始される。前記読み取り同期信号を毎ライン、CIS系は、LED等の単色ラインに対して計測し、蓄積時間を内部レジスタやメモリに保持する(S808)。続いて、第1と第2の蓄積時間に対する黒シェーディングデータの平均値をレジスタ又はメモリ等から読み出し可能に設定し(S809)、画素単位で、基準の黒シェーディングデータを読み出す。更に複数必要な場合は、蓄積時間がどの蓄積時間内にあるかを判別して、前後の蓄積時間に対する黒シェーディングデータの平均値をレジスタ又はメモリ等から読み出し可能に設定する(S809)。そして選択設定された2点の黒シェーディングデータを読み出す。

10

20

30

40

50

イングデータの平均値と画素単位で基準の黒シェーディングデータを読み出す。(S809)の黒シェーディングの場合と同様に白シェーディングデータの平均値も選択設定する(S810)。続いて、図6の説明にあるようにシェーディングデータの補正手順に従い、ライン単位の黒シェーディングデータを線形補間する(S811)。(S811)の黒シェーディングの場合と同様に白シェーディングデータも線形補間する(S812)。続いて、前記により補正された黒及び白、黒又は白のシェーディングデータを用いて、例えば前述に示すシェーディング補正を実施する(S813)。補正值はライン単位で取得し、基準のシェーディングデータを基に全有効画素に対して補正を行う。続いて、最終讀取ラインであるかを判別し(S814)、最終讀取ラインでない場合(No)、ステップ(S807)に戻り、次のラインの讀取同期信号の生成と蓄積時間の計測を繰り返す。ステップ(S814)で、最終讀取ラインである場合(Yes)、コピー／スキャン動作を終了する(S815)。

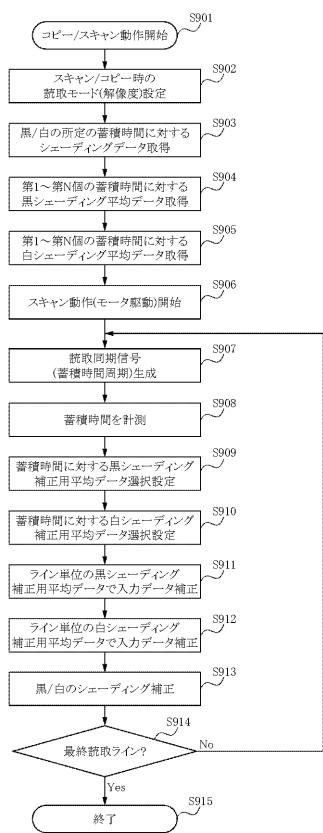

#### 【0069】

図9は、本発明を適用できる黒及び白のシェーディングデータのライン単位の平均データでの線形補間の入力データ補正の一例を示すフローチャートである。

#### 【0070】

操作キーにより、コピー又はスキャン動作を開始する(S901)。選択されたスキャン／コピー時の讀取モード(解像度)を設定する(S902)。黒及び白、黒又は白の基準になる所定の蓄積時間に対するシェーディングデータを取得する(S903)。続いて、第1(例えば前記基準の場合)と第2の蓄積時間に対する黒シェーディングデータの平均値を取得する(S904)。更に複数必要な場合は、第Nまでの蓄積時間に対する黒シェーディングデータの平均値を取得する。例えば、蓄積時間の短い方から  $T_1 < T_2 < T_3 < \dots < T_n$  で、左記に対応したシェーディングデータの平均値の関係で取得する。(S904)の黒シェーディングの場合と同様に白シェーディングデータも複数取得する(S905)。続いて、スキャン動作のDCモータ駆動を開始する(S906)。モータ駆動が開始されると図2のようにエンコーダ信号より設定されたパルス数で讀取同期信号が生成される(S907)。讀取同期信号が蓄積時間周期になっており、イメージセンサへの駆動信号とデータ入力が開始される。前記讀取同期信号を毎ライン、CIS系は、LED等の単色ラインに対して計測し、蓄積時間を内部レジスタやメモリに保持する(S908)。続いて、第1と第2の蓄積時間に対する黒シェーディングデータの平均値をレジスタ又はメモリ等から読み出し可能に設定し(S909)、画素単位で、基準の黒シェーディングデータを読み出す。更に複数必要な場合は、蓄積時間がどの蓄積時間内にあるかを判別して、前後の蓄積時間に対する黒シェーディングデータの平均値をレジスタ又はメモリ等から読み出し可能に設定する。そして選択設定された2点の黒シェーディングデータの平均値と画素単位で基準の黒シェーディングデータを読み出す(S909)。(S909)の黒シェーディングの場合と同様に白シェーディングデータの平均値も選択設定する(S910)。続いて、図6の説明にあるようにシェーディングデータの補正手順に従い、ライン単位の黒シェーディングデータの線形補間分入力データを補正する(S911)。(S911)の黒シェーディングの場合と同様に白シェーディング補正分、入力データを補正する(S912)。補正值はライン単位で取得し、入力データに対してデータ補正を行い、その後、例えば前述に示すシェーディング補正を実施する(S913)。続いて、最終讀取ラインであるかを判別し(S914)、最終讀取ラインでない場合(No)、ステップ(7)に戻り、次のラインの讀取同期信号の生成と蓄積時間の計測を繰り返す。ステップ(S914)で、最終讀取ラインである場合(Yes)、コピー／スキャン動作を終了する(S915)。

#### 【0071】

以上のように、本発明では、黒レベル又は白レベルのデータに対し、画素単位又はライン単位で、必要に応じて前記補正方法を選択、組み合わせる。これにより、DCモータのエンコーダ同期の画像讀取装置において、任意の蓄積時間に対するイメージセンサの暗電流成分やデータ変動を最適に補正できる。

10

20

30

40

50

**【図面の簡単な説明】****【0072】**

【図1】本発明における画像読取制御装置のブロック図である。

【図2】本発明における画像読取制御装置のエンコーダ等の外部パルスを基に読取同期信号を生成するタイミングの一例を示す図である。

【図3】本発明におけるモータ速度変動に対する読取同期信号と暗電流データの増加の一例を示す図である。

【図4】本発明におけるモータ速度変動に対する読取同期信号と白シェーディングのデータ増加の一例を示す図である。

【図5】第1の実施例である蓄積時間と黒及び白のシェーディングデータの画素単位の線形補間の関係の一例を示す図である。 10

【図6】第1の実施例に対応する黒及び白のシェーディングデータの画素単位の線形補間のデータ補正の一例を示すフローチャートである。

【図7】第2の実施例である蓄積時間と黒及び白のシェーディングデータのイメージセンサのライン単位の平均と線形補間の関係の一例を示す図である。

【図8】第2の実施例に対応する黒及び白のシェーディングデータのイメージセンサのライン単位の平均データでの線形補間のデータ補正の一例を示すフローチャートである。

【図9】本発明を適用できる黒及び白のシェーディングデータのライン単位の平均データでの線形補間の入力データ補正の一例を示すフローチャートである。

**【符号の説明】****【0073】**

101 読取デバイス

102 AFE (アナログフロントエンド)

103 読取デバイス制御部

104 読取データ処理部

105 読取制御部

106 第1のDCモータコントローラ

107 第1のエンコーダブロック

108 第2のDCモータコントローラ

109 第2のエンコーダブロック

110 セレクタ

111 外部SH生成ブロック

112 内部SH生成ブロック

113 セレクタ

114 ASIC

115 RAM

10

20

30

【図1】

【図2】

【 図 3 】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(56)参考文献 特開平11-252335(JP,A)

特開2000-004333(JP,A)

特開平11-069162(JP,A)

特開平08-237480(JP,A)

特開平06-046254(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 1/19