(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4029595号

(P4029595)

(45) 発行日 平成20年1月9日(2008.1.9)

(24) 登録日 平成19年10月26日(2007.10.26)

(51) Int.C1.

F 1

|             |           |             |      |

|-------------|-----------|-------------|------|

| HO1L 21/314 | (2006.01) | HO1L 21/314 | A    |

| HO1L 21/336 | (2006.01) | HO1L 29/78  | 658F |

| HO1L 29/78  | (2006.01) | HO1L 29/78  | 301B |

| HO1L 29/12  | (2006.01) | HO1L 29/78  | 652F |

HO1L 29/78 652K

請求項の数 5 (全 19 頁) 最終頁に続く

(21) 出願番号

特願2001-317022(P2001-317022)

(22) 出願日

平成13年10月15日(2001.10.15)

(65) 公開番号

特開2003-124208(P2003-124208A)

(43) 公開日

平成15年4月25日(2003.4.25)

審査請求日

平成16年1月26日(2004.1.26)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 100100022

弁理士 伊藤 洋二

(74) 代理人 100108198

弁理士 三浦 高広

(74) 代理人 100111578

弁理士 水野 史博

(72) 発明者 久田 祥之

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

(72) 発明者 奥野 英一

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

最終頁に続く

(54) 【発明の名称】 SiC半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板(1、41、101)に備えられたSiC層(5、48、102)の表面に酸化膜(7、49、105)を成膜してなるSiC半導体装置の製造方法において、

前記SiC層の表面をSi終端された清浄面とする工程と、

前記清浄面とされたSiC層の表面に酸化膜を成膜したのち、800以上かつ1000以下の熱処理を施し、前記SiC層の表面で終端しているSiと前記酸化膜中のSiO<sub>2</sub>とを電気的に活性化させる工程とを有することを特徴とするSiC半導体装置の製造方法。

## 【請求項2】

前記熱処理温度を1000とすることを特徴とする請求項1に記載のSiC半導体装置の製造方法。

## 【請求項3】

前記熱処理雰囲気を不活性ガス雰囲気とすることを特徴とする請求項1又は2に記載のSiC半導体装置の製造方法。

## 【請求項4】

前記酸化膜をLPCVDにより、5nm/mi<sup>n</sup>以下の堆積レートで形成することを特徴とする請求項1乃至3のいずれか1つに記載のSiC半導体装置の製造方法。

## 【請求項5】

基板(1、41、101)に備えられたSiC層(5、48、102)の表面に酸化膜

10

20

(7、49、105)を成膜してなるSiC半導体装置の製造方法において、

前記SiC層の表面をSi終端された清浄面とする工程と、

前記SiC層の表面で終端しているSiや前記SiC層中のSi及びCを酸素を含むガスと反応させると共に、この反応による生成物を除去することにより、SiC層の表面をSiCを構成するSi及びC原子のみが周期的に並んだ1×1構造とする工程と、

前記表面が1×1構造とされたSiC層の表面に前記酸化膜を成膜する工程とを含み、

前記酸化膜を成膜する工程では、前記SiC層の表面にデポジションによって前記酸化膜を成膜することを特徴とするSiC半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【0001】

10

##### 【発明の属する技術分野】

本発明は、炭化珪素(SiC)からなる半導体装置の製造方法に関するもので、例えば、SiCからなるMOSFET等に用いて好適である。

##### 【0002】

##### 【従来の技術および発明が解決しようとする課題】

SiCの上に形成した酸化膜をゲート酸化膜として用いる場合、特に4H-SiCにおいては、界面準位密度が極めて高く、チャネル移動度を低下させている原因の一つとなっていた。この界面準位密度の増加は、ゲート酸化膜とSiCとから形成されるSiO<sub>2</sub>/SiC界面に残留している炭素等の不純物が起因して発生していると予測される。すなわち、ゲート酸化膜をSiCの熱酸化によって形成する場合、酸化反応の過程でSiO<sub>2</sub>/SiC界面に炭素が残留し、ゲート酸化膜を蒸着する場合、SiCをHF処理した後に大気に開放すると大気中の炭素等の不純物が表面に付着するため、その表面にSiO<sub>2</sub>を蒸着するとSiO<sub>2</sub>/SiC界面に不純物が残留する。このような不純物のために、界面準位密度が増加していると考えられる。

20

##### 【0003】

これに基づき、本発明者らは、先に、特願2001-17263号において、高温熱酸化法を用いることにより、SiCとゲート酸化膜によるSiO<sub>2</sub>/SiC界面に残留している炭素を低減し、界面準位密度を低減することを提案している。

##### 【0004】

しかしながら、この方法によっても残留炭素を完全に除去することが困難であり、十分に界面準位密度を低減することができなかった。

30

##### 【0005】

本発明は上記点に鑑みて、SiCとゲート酸化膜との界面における残留炭素を除去し、界面準位密度を低減させ、チャネル移動度を向上させることを目的とする。

##### 【0006】

##### 【課題を解決するための手段】

上記目的を達成するため、請求項1に記載の発明では、SiC層の表面をSi終端された清浄面とする工程と、清浄面とされたSiC層の表面に酸化膜を形成したのち、800

以上かつ1000以下での熱処理を施し、SiC層の表面で終端しているSiと酸化膜中のSiO<sub>2</sub>とを電気的に活性化させることで、酸化膜とSiC層との界面をSiO<sub>2</sub>/SiC清浄界面とする工程とを有することを特徴としている。

40

##### 【0010】

このように、SiC層の表面で終端したSiと酸化膜中のSiO<sub>2</sub>とを結合させることで、これらを電気的に活性化させることができる。このような構成も、SiCを酸化させることによって発生する残留炭素が生成されないため、酸化膜とSiC層との界面における残留炭素を低減することができる。

##### 【0011】

請求項2に示すように、熱処理温度としては1000が好ましい。また、請求項3に示すように、熱処理雰囲気としては不活性ガス雰囲気と/orすることができる。

##### 【0034】

50

請求項4に記載の発明では、SiC層の表面をSi終端された清浄面とする工程と、SiC層の表面で終端しているSiやSiC層中のSi及びCを酸素を含むガスと反応させると共に、この反応による生成物を除去することにより、SiC層の表面をSiCを構成するSi及びC原子のみが周期的に並んだ $1 \times 1$ 構造とする工程と、表面が $1 \times 1$ 構造とされたSiC層の表面に酸化膜を成膜する工程とを含み、SiC層の表面にデポジションによって酸化膜を成膜することを特徴としている。

## 【0035】

このように、SiC層の表面をSiで終端させたのち、Si終端のSiやSiC層中のSiやCを酸素ガス中のOと反応させることで、SiC層の表面を清浄面とすることができる。そして、このような清浄面となったSiC層の表面に酸化膜をデポジションすることで、酸化膜とSiC層との界面の残留炭素を低減することができる。これにより、請求項1と同様の効果を得ることができる。10

## 【0036】

なお、SiC層の表面をSiで終端していなくても、同様の効果を得ることができる。

## 【0042】

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示すものである。

## 【0043】

## 【発明の実施の形態】

## (第1実施形態)

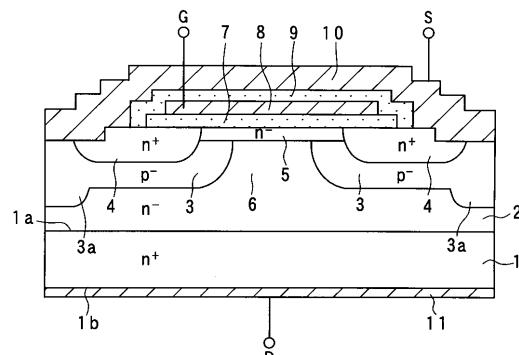

図1に、本発明の一実施形態を適用して形成したnチャネルタイプのプレーナ型MOSFET(以下、縦型パワーMOSFETという)の断面構成を示す。以下、図1に基づいて、縦型パワーMOSFETの構成について説明する。20

## 【0044】

上面を主表面1aとし、主表面1aの反対面となる下面を裏面1bとした、SiCからなるn<sup>+</sup>型基板1が用いられている。このn<sup>+</sup>型基板1の主表面1a上には、n<sup>+</sup>型基板1よりも低いドーパント濃度を有するSiCからなるn<sup>-</sup>型ドリフト層2が積層されている。これらn<sup>+</sup>型基板1の主表面1a及びn<sup>-</sup>型ドリフト層2の上面は、(0001)面とされ、表面状態密度が低くなる面方位が選択されている。

## 【0045】

n<sup>-</sup>型ドリフト層2の表層部における所定領域には、所定深さを有するp型ベース領域3が形成されている。このp型ベース領域3はBをドーパントとして形成されており、約 $1 \times 10^{17} \text{ cm}^{-3}$ 以上の濃度となっている。なお、p型ベース領域3のうち部分的に接合深度が深くされた部分は、ディープベース領域3aであり、縦型パワーMOSFETのアバランシェ耐量向上のために備えられている。また、p型ベース領域3の表層部の所定領域には、該ベース領域3よりも浅いn<sup>+</sup>型ソース領域4が形成されている。30

## 【0046】

さらに、n<sup>+</sup>型ソース領域4とn<sup>-</sup>型ドリフト層2のうちのドリフト領域6とを繋ぐように、p型ベース領域3の表面部にはn<sup>-</sup>型SiC層5が延設されている。このn<sup>-</sup>型SiC層5は、エピタキシャル成長にて形成されたものであり、エピタキシャル膜の結晶が4H、6H、3Cもしくは15Rのもので構成され、その表面がSi終端の洗浄面とされた $3 \times 3$ 構造、 $2 \cdot 3^{1/2} \times 2 \cdot 1 3^{1/2}$ 構造、 $3^{1/2} \times 3^{1/2}$ 構造もしくは $6 \times 6$ 構造等のSiC面となっている。このn<sup>-</sup>型SiC層5がデバイスの動作時にチャネル形成層として機能する。以下、n<sup>-</sup>型SiC層5を表面チャネル層という。40

## 【0047】

なお、ここでいう $3 \times 3$ 構造、 $2 \cdot 3^{1/2} \times 2 \cdot 1 3^{1/2}$ 構造、 $3^{1/2} \times 3^{1/2}$ 構造もしくは $6 \times 6$ 構造とは、それぞれ3倍周期構造、 $2 \cdot 3^{1/2} \times 2 \cdot 1 3^{1/2}$ 倍周期構造、 $3^{1/2}$ 倍周期構造、6倍周期構造のことを意味する。例えば、 $3 \times 3$ 構造の場合には、SiCの結晶構造の周期に対して、3周期毎にSiが配置されているようなものを示す。

## 【0048】

10

20

30

40

50

表面チャネル層 5 は、N（窒素）をドーパントとして形成されており、そのドーパント濃度は、例えば  $1 \times 10^{15} \text{ cm}^{-3}$  ~  $1 \times 10^{17} \text{ cm}^{-3}$  程度の低濃度で、かつ、n<sup>-</sup>型ドリフト層 2 及び p 型ベース領域 3 のドーパント濃度以下とされている。これにより、低オン抵抗化が図られている。

#### 【0049】

表面チャネル層 5 の上面および n<sup>+</sup>型ソース領域 4 の上面にはゲート酸化膜 7 が形成されている。さらに、ゲート酸化膜 7 の上にはドープトポリシリコンからなるゲート電極 8 が形成されており、このゲート電極 8 を覆うように LTO 膜からなる絶縁膜 9 が形成されている。この絶縁膜 9 の上にはソース電極 10 が形成され、ソース電極 10 は n<sup>+</sup>型ソース領域 4 および p 型ベース領域 3 と接した状態となっている。そして、n<sup>+</sup>型基板 1 の裏面 1 b にドレイン電極 11 が形成され、図 1 に示すプレーナ型 MOSFET が構成されている。

10

#### 【0050】

このように構成されたプレーナ型 MOSFET は、表面チャネル層 5 の導電型を反転させることなくチャネルを誘起する蓄積モードで動作するため、導電型を反転させる反転モードの MOSFET に比べチャネル移動度を大きくすることができ、オン抵抗を低減させることができる。

#### 【0051】

そして、本実施形態における縦型パワー MOSFET では、後述する方法により、表面チャネル層 5 とゲート酸化膜 7 の界面における残留炭素が低減されている。このため、さらに高いチャネル移動度を実現できると共に、オン抵抗のさらなる低減を図ることができる。

20

#### 【0052】

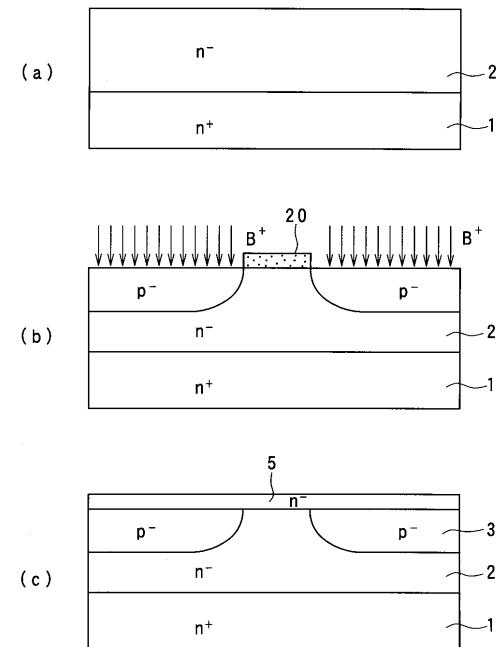

以下、本実施形態における縦型パワー MOSFET の製造方法について説明する。図 2 ~ 図 4 に、本実施形態の縦型パワー MOSFET の製造工程を示し、これらの図に基づいて説明する。

#### 【0053】

##### 〔図 2 (a) に示す工程〕

まず、n 型 4 H、6 H、3 C もしくは 15 R - SiC からなる n<sup>+</sup>型基板 1 を用意する。このとき、n<sup>+</sup>型基板 1 として、その厚さが 400 μm、主表面 1 a が (0001) 面のものを用いている。そして、この n<sup>+</sup>型基板 1 の主表面 1 a に厚さ 5 μm の n<sup>-</sup>型ドリフト層 2 をエピタキシャル成長させる。このようにすれば、n<sup>-</sup>型ドリフト層 2 は下地の基板 1 と同様の結晶となり、4 H、6 H、3 C 又は 15 R - SiC で構成される。

30

#### 【0054】

##### 〔図 2 (b) に示す工程〕

n<sup>-</sup>型ドリフト層 2 の上の所定領域に LTO 膜 20 を配置し、これをマスクとして B<sup>+</sup>（若しくはアルミニウム）をイオン注入して、p 型ベース領域 3 を形成する。このときのイオン注入条件は、温度が 700 、ドーズ量が  $1 \times 10^{16} \text{ cm}^{-2}$  となるようにしている。

#### 【0055】

##### 〔図 2 (c) に示す工程〕

LTO 膜 20 を除去した後、n<sup>-</sup>型ドリフト層 2 の表面部及び p 型ベース領域 3 の表面部に、化学気相成長法（CVD 法）により表面チャネル層 5 をエピタキシャル成長させる。

40

#### 【0056】

このとき、縦型パワー MOSFET をノーマリオフ型にできる程度に、表面チャネル層 5 の厚み（膜厚）が設定されるようとする。すなわち、縦型パワー MOSFET をノーマリオフ型とするためには、ゲート電圧を印加していない状態の際に、表面チャネル層 5 に広がる空乏層が電気伝導を妨げるように十分なバリア高さを有している必要があるため、この条件を満たすような厚みで表面チャネル層 5 を形成する。このようなノーマリオフ型の縦型パワー MOSFET は、故障などによってゲート電圧を印加できないような状態となつても、電流が流れないようにすることができるため、ノーマリオン型のものと比べて安

50

全性を確保することができる。

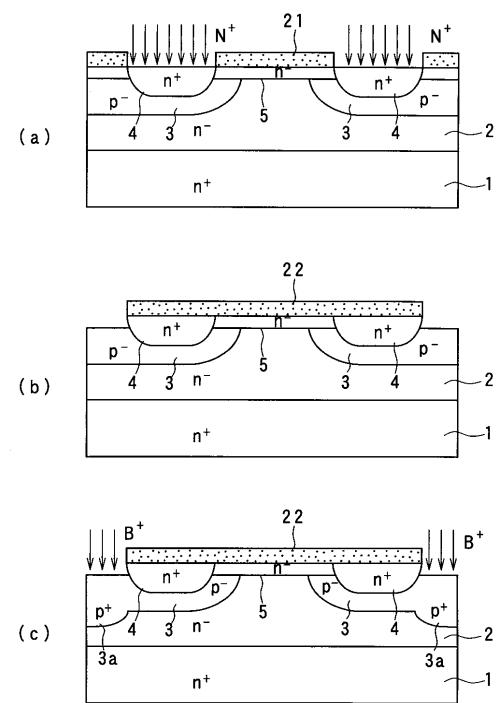

**【0057】**

**[図3(a)に示す工程]**

表面チャネル層5の上の所定領域にLTO膜21を配置し、これをマスクとしてN(窒素)等のn型不純物をイオン注入し、n<sup>+</sup>型ソース領域4を形成する。このときのイオン注入条件は、温度が700、ドーズ量が1×10<sup>15</sup>cm<sup>-2</sup>となるようにしている。

**【0058】**

**[図3(b)に示す工程]**

LTO膜21を除去した後、フォトレジスト法を用いて表面チャネル層5の上の所定領域にLTO膜22を配置し、これをマスクとしてRIEによりp型ベース領域3上の表面チャネル層5を部分的にエッチングする。

10

**【0059】**

**[図3(c)に示す工程]**

そして、LTO膜22をマスクにしてB<sup>+</sup>をイオン注入し、ディープベース領域3aを形成する。これにより、p型ベース領域3の一部が厚くなつたものとなる。このディープベース領域3aは、n<sup>+</sup>型ソース領域4と重ならない部分に形成される。

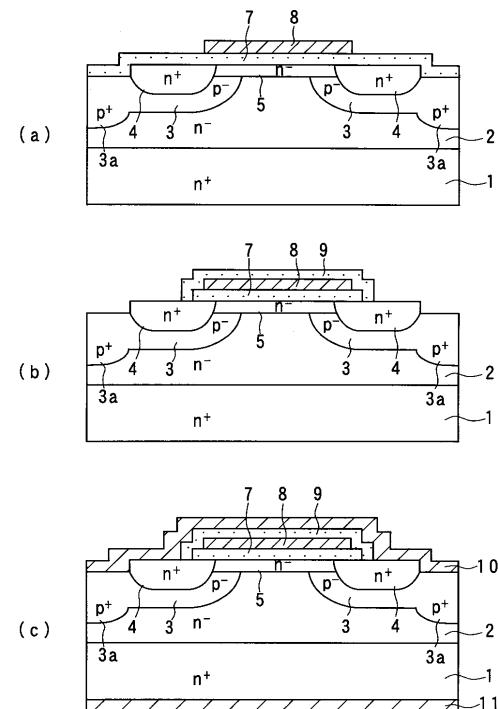

**【0060】**

**[図4(a)に示す工程]**

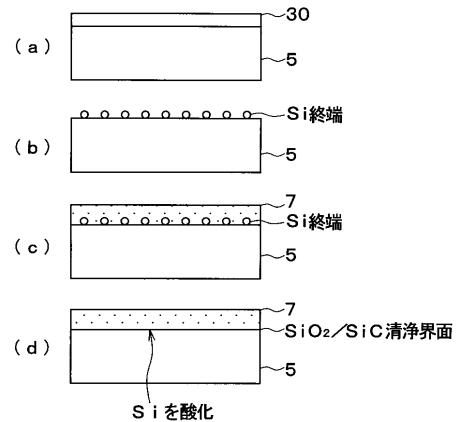

マスクとして用いたLTO膜22を除去したのち、基板表面を洗浄する。続いて、n<sup>+</sup>型基板1を超高真空チャンバー内に収容し、表面チャネル層5の表面がSi終端の清浄面となるようにする。この工程について図5を参照して説明する。

20

**【0061】**

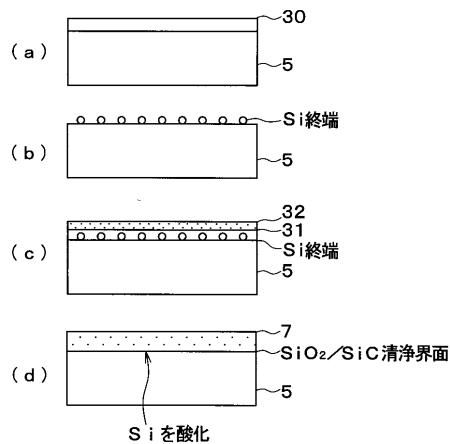

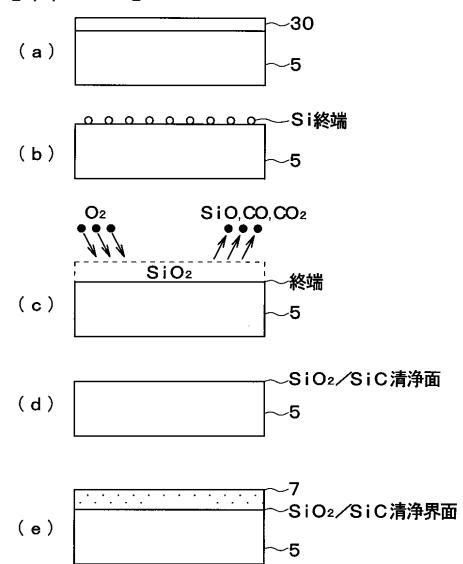

図5は、本工程における表面チャネル層5の表面の様子を示したものである。まず、LTO膜22を除去した後、基板表面を洗浄したのち、図5(a)に示すように表面チャネル層5の表面にSi層30を約5nmの厚さで蒸着等によって成膜する。そして、超高真空チャンバー内を500~1100(好ましくは1000)に高温化させる。これにより、図5(b)に示すようにSi層30のうちの大部分のSiが蒸発する。このとき、高温化の際の温度プロファイルの設定条件等に応じて、表面チャネル層5の表面にSiが2~3原子層残り、表面チャネル層5の表面がSi終端の清浄面とされた3×3構造、2·3<sup>1/2</sup>×2·13<sup>1/2</sup>構造、3<sup>1/2</sup>×3<sup>1/2</sup>構造もしくは6×6構造等となる。

30

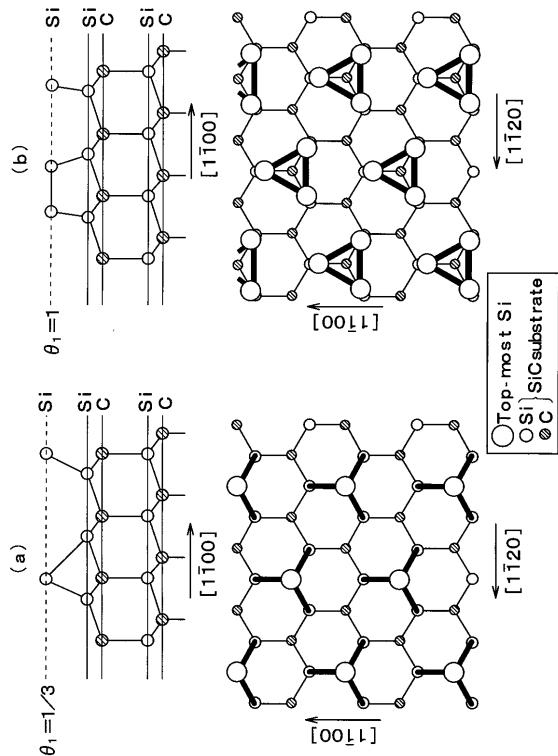

**【0062】**

なお、Si終端の場合の3<sup>1/2</sup>×3<sup>1/2</sup>構造として、例えば図6(a)、(b)に示すような2つの構造が挙げられる。図6(a)、(b)のうちの紙面上方に結晶構造を横方向から見たときの詳細が示してあり、紙面下方に結晶構造を上方向から見たときの詳細が示してある。図6(a)の構造は、任意のC原子と結合された3つのSiそれぞれに結合するようにSi原子が配置されたもので、図6(b)の構造は、任意のC原子と結合された3つのSiそれぞれに1つづつSi原子が結合され、その結合された3つのSi原子が互いに結合された配置のものである。これら両方の構造共に本実施形態を適用することができる。

**【0063】**

続いて、図5(c)に示すように、表面チャネル層5の表面にLTO膜からなるゲート酸化膜7をデポジションする。例えば、LPCVD法で酸化膜を堆積させ、その堆積レートが5nm/mind以下となるようにし、信頼性の高い良質な酸化膜が形成されるようにしている。なお、ここではデポジションによって行っているが、エピタキシャル成長によってゲート酸化膜7を形成しても良い。

40

**【0064】**

その後、700以上かつ900以下、好ましくは875の熱酸化処理を行う。このとき、表面チャネル層5の表面で終端したSiのみが酸化するように、ドライO<sub>2</sub>雰囲気とする。なお、このときの熱酸化は、酸素ガス、オゾン、ラジカル(酸素にUV照射を行って酸素を活性化させたもの)のいずれを用いててもよい。

**【0065】**

このような熱酸化処理により、表面チャネル層5の表面で終端しているSiが酸化されてSiO<sub>2</sub>となり、図5(d)に示すように、ゲート酸化膜7と表面チャネル層5との界面が残留炭素をほぼ含まないSiO<sub>2</sub>/SiC清浄界面となる。

**【0066】**

なお、熱酸化温度は少なくとも700以上であればSiを酸化させられるが、表面チャネル層5中のSiCが酸化してしまわないように、上限を900としている。

**【0067】**

その後、ゲート酸化膜7の上にLPCVDによりドープトポリシリコン層を成膜する。このとき、成膜温度を600としている。この後、ドープトポリシリコン層をパターニングしてゲート電極8を形成する。10

**【0068】****[図4(b)に示す工程]**

引き続き、ゲート酸化膜7の不要部分を除去した後、LTOよりなる絶縁膜9を形成してゲート電極8及びゲート酸化膜7を覆う。このとき、成膜温度を425とし、成膜後に1000のアニールを行うようにしている。

**【0069】****[図4(c)に示す工程]**

そして、室温での金属スパッタリングによりソース電極10及びドレイン電極11を配置する。また、成膜後に1000のアニールを行う。このようにして、図1に示すプレナ型MOSFETが完成する。20

**【0070】**

以上説明したように、表面チャネル層5の表面で終端したSiのみを酸化させるようにすれば、SiCを酸化させることによって発生する残留炭素が生成されないため、ゲート酸化膜7と表面チャネル層5との界面における残留炭素を低減することができる。これにより、さらに高いチャネル移動度を実現できると共に、オン抵抗のさらなる低減を図ることができる。

**【0071】****(第2実施形態)**

上記第1実施形態において、図4(a)の工程で、表面チャネル層5の表面をSi終端にしたのち、その後の工程に移行する前に、超高真空中で表面チャネル層5の表面にSiO<sub>x</sub>膜や窒化膜を保護膜としてデポジションするようにしても良い。30

**【0072】**

図3(c)の工程から図4(a)の工程に移行するに際し、違うチャンバーに代えて行う場合があるため、一旦、n<sup>+</sup>型基板1を外部に取り出す可能性がある。このような場合、表面チャネル層5の表面に不純物が付着しかねないが、SiO<sub>x</sub>膜を形成しておくことにより不純物が付着することを保護することができる。これにより、不純物に起因する界面準位密度を低減することができる。

**【0073】**

なお、窒化膜を保護膜として用いれば、表面チャネル層5の表面に形成されるSiO<sub>2</sub>膜と保護膜(窒化膜)とによるONON膜をゲート酸化膜7の代りに用いることもできる。40

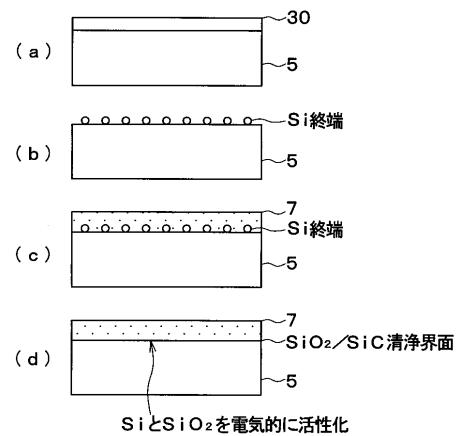

**【0074】****(第3実施形態)**

本実施形態も、第1実施形態の図4(a)の工程を変更することで、ゲート酸化膜7と表面チャネル層5との界面における残留炭素を低減する。このときの変更した工程中の表面チャネル層5の表面の様子を図7に示す。まず、LTO膜22を除去した後、基板表面を洗浄する。この後、図7(a)、(b)では、上記第1実施形態と同様の方法により、表面チャネル層5の表面をSi終端の清浄面とされた3×3構造、2·3<sup>1/2</sup>×2·13<sup>1/2</sup>構造、3<sup>1/2</sup>×3<sup>1/2</sup>構造もしくは6×6構造等にする。

**【0075】**

続いて、図7(c)に示すように、表面チャネル層5の表面にLTO膜からなるゲート酸化膜7をデポジションする。例えば、LPCVD法で酸化膜を堆積させ、その堆積レートが5nm/min以下となるようにし、信頼性の高い良質な酸化膜が形成されるようにしている。

#### 【0076】

その後、800以上かつ1000以下、好ましくは1000の熱処理を行う。このとき、表面チャネル層5の表面での酸化が行われないようにAr等の不活性ガス雰囲気とする。

#### 【0077】

このような熱処理により、図7(d)に示すように表面チャネル層5の表面で終端しているSiとゲート酸化膜7中のSiO<sub>2</sub>とを結合させることができ、電気的に活性化させ、MOS動作可能とすることができます。

#### 【0078】

なお、熱処理温度は少なくとも800以上であれば良いが、熱的に表面チャネル層5の表面で終端したSiとゲート酸化膜7中のSiO<sub>2</sub>とが結合する温度となるように温度範囲を設定している。

#### 【0079】

その後、ゲート酸化膜7の上にゲート電極8を形成したのち、第1実施形態に示す図4(b)以降の工程を行うことで、本実施形態における縦型パワーMOSFETが完成する。

#### 【0080】

以上説明したように、表面チャネル層5の表面で終端したSiとゲート酸化膜7中のSiO<sub>2</sub>とを結合させることで、これらを電気的に活性化させ、MOS動作可能とすることができます。このような構成も、SiCを酸化させることによって発生する残留炭素が生成されないため、ゲート酸化膜7と表面チャネル層5との界面における残留炭素を低減することができ、第1実施形態と同様の効果を得ることができる。

#### 【0081】

なお、本実施形態においても、第2実施形態に示すように、表面チャネル層5の表面にSiO<sub>x</sub>膜を形成するようにすることで、表面チャネル層5の表面に不純物が付着することを防止することができ、第2実施形態と同様の効果を得ることができる。

#### 【0082】

また、SiO<sub>x</sub>膜を形成する代りに、図4(a)の工程で、表面チャネル層5の表面をSi終端にしたのち、その後の工程に移行する前に、表面チャネル層5のSi終端面にH<sub>2</sub>を照射したりHを供給することでH終端面を形成するようにしても良い。このようにしても、表面チャネル層5の表面に不純物が付着することを防止することができると共に、HTerminalizationとすることで、ダンギングボンドを無くして界面準位密度を減らすことができる。

#### 【0083】

参考として、真空チャンバー内で3×3構造を形成し、その上にSiO<sub>2</sub>膜を堆積して電気特性(C-V特性)を実験により測定した。具体的な試料作成方法は以下のように行つた。

#### 【0084】

まず、Siiflux中において約1000で加熱することで、一旦、SiC表面に3<sup>1/2</sup>×3<sup>1/2</sup>構造を形成しておき、その後、Siiflux中において約900で加熱することにより3×3構造を得た。このようにすることで、SiC表面にシリコンドロップレットが残ることを防止することができる。なお、ここでは3<sup>1/2</sup>×3<sup>1/2</sup>構造を形成したのちに3×3構造を形成したが、約1100程度まで加熱して6・3<sup>1/2</sup>×6・3<sup>1/2</sup>構造とした後に例えば約900程度とすることで3×3構造としても良い。

#### 【0085】

その後、試料を真空チャンバーから取り出したときに、試料表面の3×3構造が大気に触れることによって変質してしまわないように、試料を取り出す前に3×3構造上にSiO

10

20

30

40

50

$\times$  膜からなる保護膜を形成した。例えば、保護膜として、酸素ガスと Si flux を同時に供給することで数 nm の酸化珪素膜を形成した。

#### 【0086】

次に、試料を真空チャンバーから取り出し、別のチャンバーで SiC 表面上に SiO<sub>2</sub> 膜を堆積させた。例えば、LPCVD により 5 nm / min 以下の堆積レートで SiO<sub>2</sub> 膜を約 80 nm 堆積させた。その後、SiO<sub>2</sub> 膜と SiC 基板との電気的接合を得るため、875 で 30 分間加熱した。そして、この加熱を酸素ガス雰囲気と窒素ガス雰囲気いずれの場合も行ったところ、どちらの条件においても良好な電気特性を得ることができた。

#### 【0087】

このように、本実施形態に示す方法を適用することにより、高いチャネル移動度を実現できると共に、オン抵抗のさらなる低減を図ることが可能になるといえる。なお、ここでは真空チャンバーから取り出した後に SiO<sub>2</sub> 膜を堆積させる場合について説明したが、真空チャンバーから取り出さずに真空チャンバー内で SiO<sub>2</sub> を堆積させるようにしても良い。この場合、保護膜を形成せずに、SiC 表面上に SiO<sub>2</sub> 膜を堆積させるようにしても良い。

#### 【0088】

##### (第4実施形態)

本実施形態も、第1実施形態の図4(a)の工程を変更することで、ゲート酸化膜7と表面チャネル層5との界面における残留炭素を低減する。このときの変更した工程中の表面チャネル層5の表面の様子を図8に示す。まず、LTO膜22を除去した後、基板表面を洗浄する。次に、図8(a)、(b)では、第1実施形態と同様の方法により、表面チャネル層5の表面を Si 終端の清浄面とされた  $3 \times 3$  構造、 $2 \cdot 3^{1/2} \times 2 \cdot 1 3^{1/2}$  構造、 $3^{1/2} \times 3^{1/2}$  構造もしくは  $6 \times 6$  構造等にする。

#### 【0089】

続いて、図8(c)に示すように、表面チャネル層5の表面に残った Si 等を O<sub>2</sub>、H<sub>2</sub>O、O<sub>3</sub> もしくは酸素ラジカルのいずれかによる酸化プロセスを用いて熱酸化することでゲート酸化膜7を形成する。このとき、熱酸化の温度を 1000 ~ 1400 としている。このようにすれば、表面チャネル層5の表面における C の露出量が少ない状態で熱酸化が行われることになる。従って、表面チャネル層5の表面の C が核となって増加する残留炭素の量を、その核となる C を少なくすることによって低減することが可能となる。なお、熱温度は少なくとも 1000 以上であれば良いが、ゲート酸化膜7のクリストバル化を防止するために、上限を 1400 としている。

#### 【0090】

その後、ゲート酸化膜7の上にゲート電極8を形成したのち、第1実施形態に示す図4(b)以降の工程を行うことで、本実施形態における縦型パワーMOSFETが完成する。

#### 【0091】

以上説明したように、表面チャネル層5の表面を Si で終端させた状態で、つまり表面チャネル層5の表面における C の露出量を少なくした状態で熱酸化を行い、表面チャネル層5の表面にゲート酸化膜7を形成すれば、ゲート酸化膜7と表面チャネル層5との界面の残留炭素を低減することができる。これにより、第1実施形態と同様の効果を得ることができる。

#### 【0092】

なお、本実施形態においても、第2実施形態に示すように、表面チャネル層5の表面に SiO<sub>x</sub> 膜や窒化膜からなる保護膜を形成するようにすることで、表面チャネル層5の表面に不純物が付着することを防止することができ、第2実施形態と同様の効果を得ることができる。

#### 【0093】

また、SiO<sub>x</sub> 膜を形成する代りに、図4(a)の工程で、LTO膜22を除去したのち、その後の工程に移行する前に、表面チャネル層5の Si 終端面に H<sub>2</sub> を照射したり H を供給することで H 終端面を形成するようにしても良い。このようにしても、表面チャネル

10

20

30

40

50

層5の表面に不純物が付着することを防止することができると共に、Hターミネーションとすることで、ダンギングボンドを無くして界面準位密度を減らすことができる。

#### 【0094】

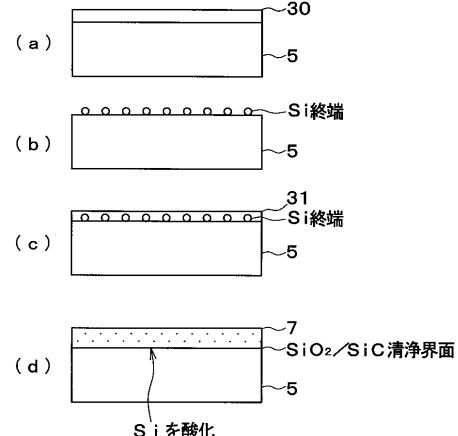

##### (第5実施形態)

本実施形態も、第1実施形態の図4(a)の工程を変更することで、ゲート酸化膜7と表面チャネル層5との界面における残留炭素を低減する。このときの変更した工程中の表面チャネル層5の表面の様子を図9に示す。まず、LTO膜22を除去した後、基板表面を洗浄する。次に、図9(a)、(b)では、第1実施形態と同様の方法により、表面チャネル層5の表面をSi終端の清浄面とされた $3 \times 3$ 構造、 $2 \cdot 3^{1/2} \times 2 \cdot 13^{1/2}$ 構造、 $3^{1/2} \times 3^{1/2}$ 構造もしくは $6 \times 6$ 構造等にする。

10

#### 【0095】

続いて、図9(c)に示すように、表面チャネル層5の表面にSi層31をエピタキシャル成長させる。その後、図9(d)に示すように、Si層31をドライ雰囲気にて熱酸化することでゲート酸化膜7を形成する。このとき、熱酸化の温度を700~900とすることで、Si層31のみが熱酸化され、表面チャネル層5中のSiCは熱酸化されないようにしている。このようにすれば、表面チャネル層5の表面におけるSiCが熱酸化されることによる残留炭素の発生を抑制することができる。なお、熱酸化温度は少なくとも700以上であればSiを酸化させられるが、表面チャネル層5中のSiCが酸化してしまわないように、上限を900としている。

#### 【0096】

20

その後、ゲート酸化膜7の上にゲート電極8を形成したのち、第1実施形態に示す図4(b)以降の工程を行うことで、本実施形態における縦型パワーMOSFETが完成する。

#### 【0097】

以上説明したように、表面チャネル層5の表面をSiで終端させると共に、表面チャネル層5の表面にSi層31を成膜し、このSi層31のみを熱酸化することで、ゲート酸化膜7と表面チャネル層5との界面の残留炭素を低減することができる。これにより、第1実施形態と同様の効果を得ることができる。

#### 【0098】

##### (第6実施形態)

本実施形態も、第1実施形態の図4(a)の工程を変更することで、ゲート酸化膜7と表面チャネル層5との界面における残留炭素を低減する。このときの変更した工程中の表面チャネル層5の表面の様子を図10に示す。まず、LTO膜22を除去した後、基板表面を洗浄する。次に、図10(a)、(b)では、第1実施形態と同様の方法により、表面チャネル層5の表面をSi終端の清浄面とされた $3 \times 3$ 構造、 $2 \cdot 3^{1/2} \times 2 \cdot 13^{1/2}$ 構造、 $3^{1/2} \times 3^{1/2}$ 構造もしくは $6 \times 6$ 構造等にする。

30

#### 【0099】

40

続いて、図10(c)では、表面チャネル層5の表面にSi層31をエピタキシャル成長させる。次いで、Si層31の表面にSiO<sub>2</sub>膜32をデポジションしたのち、熱処理を施し、Si層31をドライ雰囲気にて熱酸化する。これにより、図10(d)に示すように、Si層31で形成された酸化層とSiO<sub>2</sub>膜32とによりゲート酸化膜7が形成される。このとき、熱処理の温度を700~900とすることで、Si層31のみが熱酸化され、表面チャネル層5中のSiCは熱酸化されないようにしている。このようにすれば、表面チャネル層5の表面におけるSiCが熱酸化されることによる残留炭素の発生を抑制することができる。なお、熱酸化温度は少なくとも700以上であればSiを酸化させられるが、表面チャネル層5中のSiCが酸化してしまわないように、上限を900としている。

#### 【0100】

その後、ゲート酸化膜7の上にゲート電極8を形成したのち、第1実施形態に示す図4(b)以降の工程を行うことで、本実施形態における縦型パワーMOSFETが完成する。

#### 【0101】

50

以上説明したように、表面チャネル層5の表面をSiで終端させると共に、表面チャネル層5の表面にSi層31を成膜し、このSi層31のみを熱酸化することで、ゲート酸化膜7と表面チャネル層5との界面の残留炭素を低減することができる。これにより、第1実施形態と同様の効果を得ることができる。

#### 【0102】

なお、ここでは図10(c)に示す工程において、熱処理温度を上記温度とすることにより、Si層31が熱酸化されて酸化層となるようにしているが、Si層31をSiC化させることも可能である。

#### 【0103】

(第7実施形態)

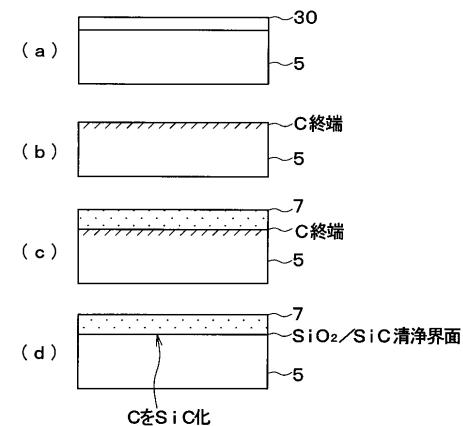

本実施形態も、第1実施形態の図4(a)の工程を変更することで、ゲート酸化膜7と表面チャネル層5との界面における残留炭素を低減する。このときの変更した工程中の表面チャネル層5の表面の様子を図11に示す。まず、LTO膜22を除去した後、基板表面を洗浄する。次に、図11(a)に示すように、表面チャネル層5の表面にSi層30を約5nmの厚さで蒸着等によって成膜する。そして、超高真空チャンバー内を500~1100(好ましくは1000)に高温化させる。これにより、図11(b)に示すようにSi層30のうちの大部分のSiが蒸発し、高温化の際の温度プロファイルの設定条件等を第1実施形態と異ならせるようにすれば、表面チャネル層5の表面がC終端の清浄面とされた $1 \times 1$ 構造(1倍周期構造)、 $3^{1/2} \times 3^{1/2}$ 構造もしくは $6 \times 6$ 構造等となる。

10

#### 【0104】

続いて、図11(c)に示すように、表面チャネル層5の表面にLTO膜からなるゲート酸化膜7をデポジションする。例えば、LPCVD法で堆積させ、その堆積レートが5nm/min以下となるようにすることで、信頼性の高い良質なゲート酸化膜7が形成されるようにしている。なお、このときのゲート酸化膜7の形成方法としては、TEOSを緻密にデポジションする方法であっても良いし、スピンドルコートによって酸化膜を形成する方法であっても良い。

#### 【0105】

その後、1200以上かつ1400以下、好ましくは1250の熱処理を行う。この熱処理温度は少なくとも1200以上であれば良いが、酸化珪素の結晶化によるクリストバル化を抑制するために、上限を1400としている。また、このとき、表面チャネル層5の表面での酸化が行われないようにAr等の不活性ガス雰囲気と共に、熱処理時に発生するCOやCO<sub>2</sub>を引き抜けるように雰囲気圧力を $6.65 \times 10^4$ Pa( $500\text{mTorr}$ )以下の減圧状態としている。

30

#### 【0106】

このような熱処理により、図11(d)に示すように、表面チャネル層5の表面で終端しているCと表面チャネル層5の上に形成されたゲート酸化膜7中のSiO<sub>2</sub>とをSiC化させることができ、ゲート酸化膜7と表面チャネル層5との界面が残留炭素をほぼ含まないSiO<sub>2</sub>/SiC清浄界面となる。

#### 【0107】

その後、ゲート酸化膜7の上にゲート電極8を形成したのち、第1実施形態に示す図4(b)以降の工程を行うことで、本実施形態における縦型パワーMOSFETが完成する。

40

#### 【0108】

以上説明したように、本実施形態では、C終端とした表面チャネル層5の表面にLTO膜をデポジションしたのち、高温熱処理を行うことで表面チャネル層5とLTO膜の界面をSiO<sub>2</sub>/SiC清浄界面とし、このような構造とされたLTO膜をゲート酸化膜7として用いるようにしている。このため、ゲート酸化膜7と表面チャネル層5との界面が残留炭素をほぼ含まない状態となるようにすることができ、さらに高いチャネル移動度を実現できると共に、オン抵抗のさらなる低減を図ることができる。

#### 【0109】

50

なお、本実施形態においても、第2実施形態に示すように、表面チャネル層5の表面にSiO<sub>x</sub>膜や窒化膜からなる保護膜を形成するようにすることで、表面チャネル層5の表面に不純物が付着することを防止することができ、第2実施形態と同様の効果を得ることができる。

#### 【0110】

##### (第8実施形態)

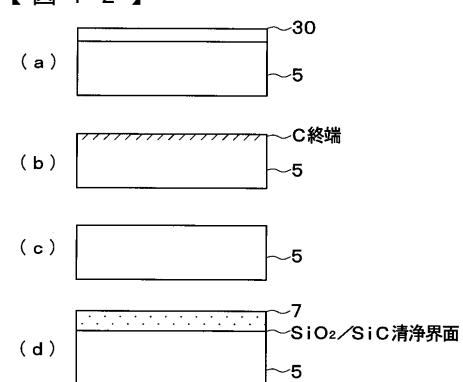

本実施形態も、第1実施形態の図4(a)の工程を変更することで、ゲート酸化膜7と表面チャネル層5との界面における残留炭素を低減する。このときの変更した工程中の表面チャネル層5の表面の様子を図12に示す。まず、LTO膜22を除去した後、基板表面を洗浄する。続いて、図12(a)、(b)では、第7実施形態と同様の方法により、表面チャネル層5の表面をC終端の清浄面とされた1×1構造、3<sup>1/2</sup>×3<sup>1/2</sup>構造もしくは6×6構造等にする。10

#### 【0111】

続いて、図12(c)に示すように、表面チャネル層5の表面で終端したC層を除去する。具体的には、水素処理(水素によるエッチング)により、C層を除去する。このように、表面チャネル層5の表面で終端したC層を除去することにより、表面チャネル層5の表面が清浄面となる。

#### 【0112】

そして、図12(d)に示すように、表面チャネル層5の表面にLTO膜からなるゲート酸化膜7をデポジションする。例えば、LPCVD法で酸化膜を堆積させ、その堆積レートが5nm/min以下となるようにし、信頼性の高い良質な酸化膜が形成されるようしている。20

#### 【0113】

その後、ゲート酸化膜7の上にゲート電極8を形成したのち、第1実施形態に示す図4(b)以降の工程を行うことで、本実施形態における縦型パワーMOSFETが完成する。

#### 【0114】

以上説明したように、表面チャネル層5の表面で終端したC層を除去しておくことで、表面チャネル層5の表面を清浄面とし、その清浄面の上にゲート酸化膜7を形成することで、ゲート酸化膜7と表面チャネル層5との界面をSiO<sub>2</sub>/SiC清浄界面とすることができる。これにより、第1実施形態と同様の効果を得ることができる。30

#### 【0115】

なお、ここでは表面チャネル層5の表面にゲート酸化膜7をデポジションしているが、表面チャネル層5の表面を熱酸化することでゲート酸化膜7を形成しても、上記と同様の効果を得ることができる。

#### 【0116】

##### (第9実施形態)

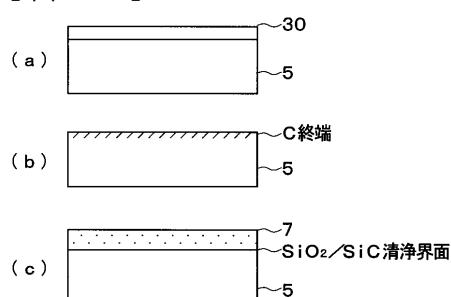

本実施形態も、第1実施形態の図4(a)の工程を変更することで、ゲート酸化膜7と表面チャネル層5との界面における残留炭素を低減する。このときの変更した工程中の表面チャネル層5の表面の様子を図13に示す。まず、LTO膜22を除去した後、基板表面を洗浄する。続いて、図13(a)、(b)では、第1実施形態と同様の方法により、表面チャネル層5の表面をC終端の清浄面とされた1×1構造、3<sup>1/2</sup>×3<sup>1/2</sup>構造もしくは6×6構造等にする。40

#### 【0117】

続いて、図13(c)に示すように、表面チャネル層5の表面にLTO膜からなるゲート酸化膜7をデポジションする。例えば、LPCVD法で酸化膜を堆積させ、その堆積レートが5nm/min以下となるようにし、信頼性の高い良質な酸化膜が形成されるようしている。そして、熱処理を施すことで、表面チャネル層5の表面に存在するダングリングボンドを除去する。例えば、水素雰囲気内の熱処理を施し、ダングリングボンドを水素終端とさせることで除去する。このように、表面チャネル層5の表面におけるダングリングボンドを除去することにより、ゲート酸化膜7と表面チャネル層5との界面をSiO<sub>x</sub>膜や窒化膜からなる保護膜を形成する。50

$\text{SiO}_2 / \text{SiC}$  清浄界面とすることができる。

【0118】

その後、ゲート酸化膜7の上にゲート電極8を形成したのち、第1実施形態に示す図4(b)以降の工程を行うことで、本実施形態における縦型パワーMOSFETが完成する。

【0119】

以上説明したように、表面チャネル層5の表面のダングリングボンドを除去しておくことで、表面チャネル層5の表面を清浄面とし、その清浄面の上にゲート酸化膜7を形成することで、ゲート酸化膜7と表面チャネル層5との界面を $\text{SiO}_2 / \text{SiC}$  清浄界面とすることができる。これにより、第1実施形態と同様の効果を得ることができる。

【0120】

なお、本実施形態では、ダングリングボンド除去のための水素処理をゲート酸化膜7の形成後に行なうようにしたが、形成前、形成途中に行なうようにしても、上記と同様の効果を得ることができる。

【0121】

(第10実施形態)

本実施形態も、第1実施形態の図4(a)の工程を変更することで、ゲート酸化膜7と表面チャネル層5との界面における残留炭素を低減する。このときの変更した工程中の表面チャネル層5の表面の様子を図14に示す。まず、LTO膜22を除去した後、基板表面を洗浄する。次に、図14(a)、(b)では、第3実施形態と同様の方法により、表面チャネル層5の表面をSi終端の清浄面とされた $3 \times 3$ 構造、 $2 \cdot 3^{1/2} \times 2 \cdot 1 3^{1/2}$ 構造、 $3^{1/2} \times 3^{1/2}$ 構造もしくは $6 \times 6$ 構造等にする。

【0122】

続いて、超高真空チャンバー内を $500 \sim 1000$ 、好ましくは $1000$ としたまま、雰囲気圧力を $1 \times 10^{-2} \text{ Pa}$  ( $1 \times 10^{14} \text{ Torr}$ )とし、超高真空チャンバー内に酸素ガスを供給する。このとき、表面チャネル層5への酸素の暴露量が $10 \sim 10^2 \text{ Pa} \cdot \text{s}$ 程度、好ましくは $10 \text{ Pa} \cdot \text{s}$ となるように酸素を吸着させる。なお、このとき超高真空チャンバー内の温度が低温になると表面チャネル層5の表面上にシリコン酸化膜(図中点線で示す)が形成されてしまう可能性があるため、これが形成されないように上記温度設定をしている。

【0123】

これにより、図14(c)に示すように、 $3 \times 3$ 構造等を構成しているSiや表面チャネル層5中のSi及びCが酸素ガス中のO(酸素)と反応し、 $\text{SiO}$ 、 $\text{CO}$ 、 $\text{CO}_2$ となって除去され、Si及びC原子のみが周期的に並んだ $1 \times 1$ 構造となる。このようにすることで、表面チャネル層5の表面は、図14(d)に示すような大気中のC等で汚染されていない清浄面となる。

【0124】

続いて、図14(e)に示すように、表面チャネル層5の表面を熱酸化することでゲート酸化膜7を形成する。このとき、表面チャネル層5の表面が上述したような清浄面となっていることから、表面チャネル層5の表面における残留炭素がほとんど無い状態で熱酸化が行われることになる。従って、表面チャネル層5の表面のCが核となって増加する残留炭素の量を、その核となるCを少なくすることによって低減することが可能となる。なお、熱温度は少なくとも $1000$ 以上であれば良いが、ゲート酸化膜7のクリストバル化を防止するために、上限を $1400$ とするのが好ましい。

【0125】

その後、ゲート酸化膜7の上にゲート電極8を形成したのち、第1実施形態に示す図4(b)以降の工程を行うことで、本実施形態における縦型パワーMOSFETが完成する。

【0126】

以上説明したように、表面チャネル層5の表面をSiで終端させたのち、Si終端のSiや表面チャネル層5中のSiやCを酸素ガス中のOと反応させることで、表面チャネル層5の表面を清浄面とすることができる。そして、このような清浄面となった表面チャネル

10

20

30

40

50

層5の表面を熱酸化することで、ゲート酸化膜7と表面チャネル層5との界面の残留炭素を低減することができる。これにより、第1実施形態と同様の効果を得ることができる。

【0127】

なお、表面チャネル層5とゲート酸化膜7の界面に残留炭素が発生したり、ダングリングボンドが発生しないように、熱酸化前、熱酸化途中もしくは熱酸化後に、第4実施形態で示したような方法によるHターミネーションとしても良い。

【0128】

また、ここでは表面チャネル層5の表面を熱酸化することによってゲート酸化膜7を形成しているが、表面チャネル層5の表面にSiO<sub>2</sub>をデポジションすることでゲート酸化膜7を形成しても、上記と同様の効果を得ることができる。

10

【0129】

(第11実施形態)

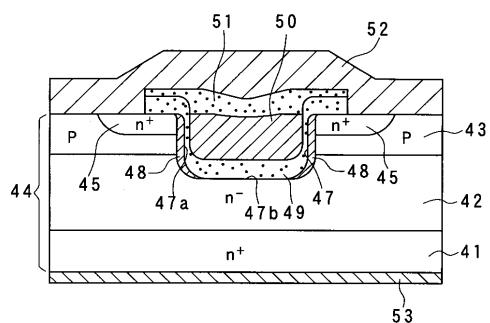

上記第1実施形態ではプレーナ型の縦型パワーMOSFETに本発明を適用した場合を示したが、本実施形態では、溝ゲート型の縦型パワーMOSFETに本発明を適用する場合を示す。

【0130】

図15に溝ゲート型のMOSFETを示す。溝ゲート型のMOSFETには、例えばn<sup>+</sup>型半導体基板41上にn<sup>-</sup>型エピ層42とp型ベース層43とが積層された基板44が用いられる。

【0131】

p型ベース層43の表層部にはn<sup>+</sup>型ソース領域45が形成され、基板44の表面からn<sup>+</sup>型ソース領域45およびp型ベース層43を貫通するように溝47が形成されている。この溝47の側面47aには、表面チャネル層48が形成され、表面チャネル層48の表面及び溝47の底面47bを含む溝47の内壁には、ゲート酸化膜49を介してゲート電極50が形成されている。

20

【0132】

ゲート電極50上には、ソース領域45及びp型ベース層43に接続されるソース電極52が層間絶縁膜51を介して形成されている。そして、基板44の裏面側にドレイン電極53が備えられ、図15に示す溝ゲート型のMOSFETが構成されている。

【0133】

このような構成を有する溝ゲート型のMOSFETのゲート酸化膜49と表面チャネル層48に関しても、第1～第10実施形態と同様の方法を適用することにより、上記各実施形態と同様の効果を得ることができる。

30

【0134】

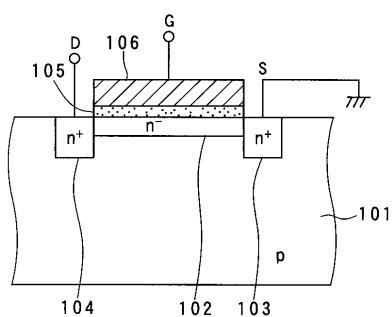

(第12実施形態)

本実施形態では、ラテラルMOSFETに本発明を適用した場合を示す。図16にラテラルMOSFETを示す。ラテラルMOSFETの基板としてp型半導体基板101が用いられている。この基板101の所定領域には、イオン注入等によって表面チャネル層102が形成されており、この表面チャネル層102の両側にはソース層103、ドレイン層104が形成されている。また、表面チャネル層102上にはゲート酸化膜105を介してゲート電極106が備えられている。

40

【0135】

このように構成されたラテラルMOSFETのゲート酸化膜105と表面チャネル層102に関しても、第1～第10実施形態と同様の方法を適用することにより、上記各実施形態と同様の効果を得ることができる。

【0136】

(他の実施形態)

上記各実施形態では、MOSFETのゲート絶縁膜に本発明を適用する場合を述べているが、フィールドプレートや層間絶縁膜として使用される絶縁膜とSiCとの界面において上記実施形態を適用しても良い。

50

**【0137】**

また、上記各実施形態において、表面チャネル層5の表面やSi層31を熱酸化することによってゲート酸化膜7を形成する場合、熱酸化の方法としては、第3実施形態で示したように、酸素ガス、オゾン、ラジカルのいずれを用いても良い。また、上記各実施形態において、表面チャネル層5の表面にゲート酸化膜7形成したり、Si層31の表面にSiO<sub>2</sub>膜32を形成する場合、それらをLPSVD、TEOS、スピンドルによって形成することが可能である。

**【0138】**

また、上記各実施形態では、n型チャネルタイプのSiC半導体装置を例に挙げて説明しているが、勿論、各構成要素の導電型を逆にしたp型チャネルタイプのものについても本発明を適用することができる。

10

**【0139】**

なお、上記各実施形態では、n<sup>-</sup>型層を表面チャネル層5、48、102とするnチャネルタイプのMOSFETに本発明を適用した場合について説明したが、もちろん各構成要素の導電型を反転させたpチャネルタイプのMOSFETに適用することも可能である。

**【図面の簡単な説明】**

【図1】本発明の第1実施形態におけるSiC半導体装置の断面構成を示す図である。

【図2】図1に示すSiC半導体装置の製造工程を示す図である。

【図3】図2に続くSiC半導体装置の製造工程を示す図である。

【図4】図3に続くSiC半導体装置の製造工程を示す図である。

20

【図5】本発明の第2実施形態におけるSiC半導体装置の製造工程を示す図である。

【図6】Si終端の場合の $3^{1/2} \times 3^{1/2}$ 構造を示した図である。

【図7】本発明の第3実施形態におけるSiC半導体装置の製造工程を示す図である。

【図8】本発明の第4実施形態におけるSiC半導体装置の製造工程を示す図である。

【図9】本発明の第5実施形態におけるSiC半導体装置の製造工程を示す図である。

【図10】本発明の第6実施形態におけるSiC半導体装置の製造工程を示す図である。

【図11】本発明の第7実施形態におけるSiC半導体装置の製造工程を示す図である。

【図12】本発明の第8実施形態におけるSiC半導体装置の製造工程を示す図である。

【図13】本発明の第9実施形態におけるSiC半導体装置の製造工程を示す図である。

【図14】本発明の第10実施形態におけるSiC半導体装置の製造工程を示す図である

30

。

【図15】本発明の第11実施形態におけるSiC半導体装置の断面構成を示す図である

。

【図16】本発明の第12実施形態におけるSiC半導体装置の断面構成を示す図である

。

**【符号の説明】**

1...n<sup>+</sup>型基板、2...n<sup>-</sup>型エピ層、3...p型ベース領域、4...n<sup>+</sup>型ソース領域、5...表面チャネル層、7...ゲート酸化膜、8...ゲート電極、9...絶縁膜、10...ソース電極、11...ドレイン電極。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 29/78 6 5 2 T

H 0 1 L 29/78 6 5 3 A

(72)発明者 長谷川 健

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

審査官 今井 拓也

(56)参考文献 特開平08-051110 (JP, A)

特開平11-274487 (JP, A)

特開2001-210637 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/205

H01L 21/31

H01L 21/365

H01L 21/469

H01L 21/314

H01L 21/336

H01L 29/12

H01L 29/78