(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-72166

(P2008-72166A)

(43) 公開日 平成20年3月27日(2008.3.27)

(51) Int.Cl.

HO3L 7/093 (2006.01)

F 1

HO3L 7/08

E

テーマコード(参考)

5J106

審査請求 未請求 請求項の数 14 O L (全 79 頁)

(21) 出願番号

特願2006-246327 (P2006-246327)

(22) 出願日

平成18年9月12日 (2006.9.12)

(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100086298

弁理士 船橋 國則

(72) 発明者 松本 智宏

東京都品川区北品川6丁目7番35号 ソニーブルーバード内

(72) 発明者 植野 洋介

東京都品川区北品川6丁目7番35号 ソニーブルーバード内

F ターム(参考) 5J106 AA04 CC01 CC24 CC31 CC41

CC45 DD32 DD35 EE01 EE10

FF09 GG07 GG15 HH03 KK05

KK11

(54) 【発明の名称】位相同期回路および電子機器

## (57) 【要約】

【課題】位相同期回路において、発振回路の周波数変換ゲインのばらつきに起因する帯域やダンピングファクタのばらつきの発生を防止する。

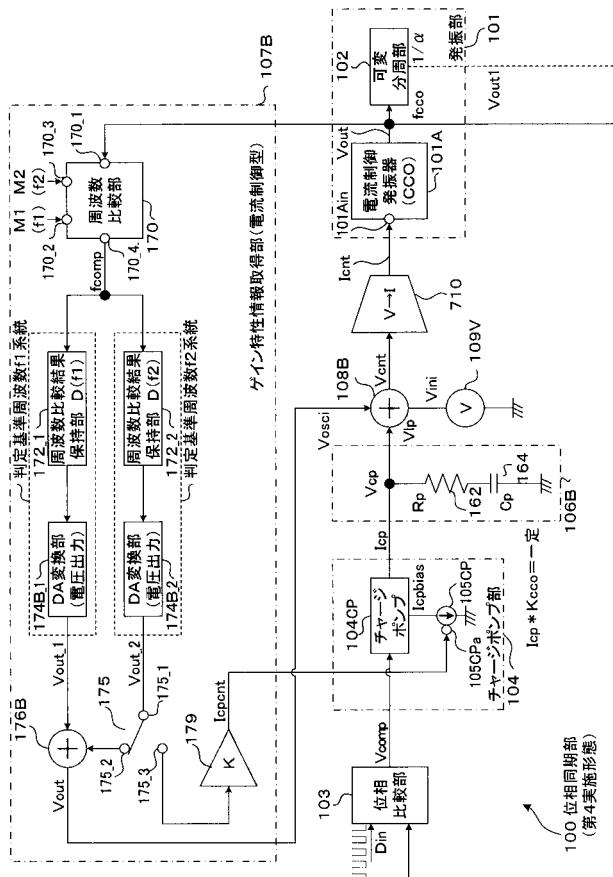

【解決手段】ゲイン特性情報取得部 107A は、判定基準周波数  $f_1$ ,  $f_2$  を使って、初期電流  $I_{ini}$  と各周波数で発振させるための周波数制御電流  $I_{osci}$  とを合成して電流制御発振部 101A に供給しながら、実動時の電流制御発振部 101A の周波数変換ゲイン  $K_{cco}$  を規定する判定基準周波数  $f_1$ ,  $f_2$  の各発振制御信号  $I_{osci\_1}$ ,  $I_{osci\_2}$  の差の情報 ( $I_{out\_2}$ ) を測定し、そのデータを周波数比較結果保持部 172\_2に記憶しておく。位相同期動作時には、周波数比較結果保持部 172\_2に記憶しておいた周波数比較結果  $f_{comp}$  のデータ  $D(f_2)$  に基づく制御電流  $I_{cpcnt}$  を補正信号として使って、周波数変換ゲイン  $K_{cco}$  のばらつきが相殺されるように駆動部 104Z を制御する。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

発振制御信号に基づいて所定周波数の出力発振信号を出力する発振部と、前記発振部から出力された前記出力発振信号と外部から入力される入力信号の位相を比較する位相比較部と、ループフィルタ部と、前記位相比較部から出力された位相比較結果を示す信号に基づいて駆動信号を生成し当該駆動信号で前記ループフィルタ部を駆動する駆動部と、前記ループフィルタ部から出力されたループフィルタ出力信号に基づき、前記出力発振信号の位相が前記入力信号の位相に同期するように前記発振制御信号を生成する発振制御信号生成部とを備えた位相同期回路であって、

2種類の目標周波数を使って、所定の大きさの規定信号と前記発振部を各周波数で発振させるための補正分とを前記発振制御信号として供給しつつ実際の発振周波数と前記目標周波数との差を比較することで、実動時の前記発振部の入力信号 - 発振周波数変換ゲイン特性を規定するゲイン特性情報を取得して記憶しておくゲイン特性情報取得部を備え、

通常の位相同期動作時には、前記ゲイン特性情報取得部で取得されたゲイン特性情報に基づいて補正信号を生成し、実動時の前記入力信号 - 発振周波数変換ゲインと前記駆動部が前記ループフィルタ部を駆動する前記駆動信号との積が一定となるように、前記補正信号で前記駆動部を制御する

ことを特徴とする位相同期回路。

**【請求項 2】**

前記ゲイン特性情報取得部は、

前記第1の目標周波数および前記第2の目標周波数のそれぞれについて、前記発振部から出力された前記出力発振信号の周波数と目標周波数との大小を比較する周波数比較部と、

前記第1の目標周波数および前記第2の目標周波数のそれぞれについて、前記周波数比較部による周波数比較結果を順次ピットの重付け順にピット別に記憶する周波数比較結果保持部と、

前記第1の目標周波数および前記第2の目標周波数のそれぞれについて、前記周波数比較結果保持部に記憶されているピット別の周波数比較結果に基づいて、周波数制御信号を順次生成する周波数制御信号生成部と、

前記第1の目標周波数についての前記周波数制御信号生成部で生成された周波数制御信号と前記第2の目標周波数についての前記周波数制御信号生成部で生成された周波数制御信号とを加算して最終的な周波数制御信号として前記発振制御信号生成部に供給する加算部と、

前記第2の目標周波数についての前記周波数制御信号生成部で生成された周波数制御信号を、ゲイン特性情報取得時には前記加算部に供給し、通常の位相同期動作時には前記駆動部側に供給されるように切り替える経路選択部と

を具備することを特徴とする請求項1に記載の位相同期回路。

**【請求項 3】**

前記ゲイン特性情報取得部は、前記第2の目標周波数についての前記周波数制御信号生成部にて取得される前記第2の周波数制御信号をK倍することで前記補正信号を取得する信号変換部を具備し、

前記Kは、標準の前記入力信号 - 発振周波数変換ゲインと標準の前記駆動信号との積を、前記第1の目標周波数と前記第2の目標周波数との差分で除算した値に設定されていることを特徴とする請求項2に記載の位相同期回路。

**【請求項 4】**

前記周波数制御信号生成部は前記周波数制御信号を電流モードで出力する構成を有しており、

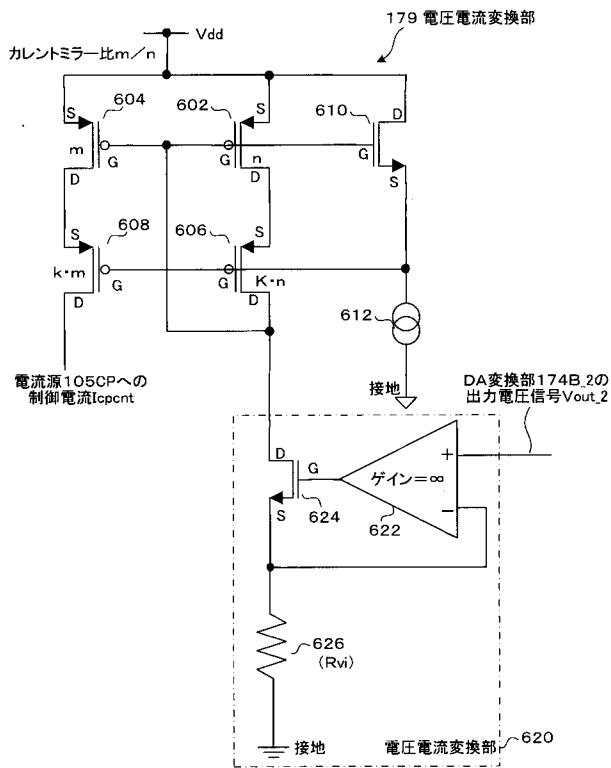

前記信号変換部は、電流モードの第2の前記周波数制御信号を処理対象として、前記K倍をカレントミラー回路によって実現する構成を具備している

ことを特徴とする請求項3に記載の位相同期回路。

10

20

30

40

50

**【請求項 5】**

前記周波数制御信号生成部は前記周波数制御信号を電圧モードで出力する構成を有しており、

前記信号変換部は、前記電圧モードの周波数制御信号を電流モードの前記周波数制御信号に変換する電圧電流変換部と、電圧電流変換部から出力された電流モードの第2の前記周波数制御信号を処理対象として、前記K倍をカレントミラー回路によって実現する構成とを具備している

ことを特徴とする請求項3に記載の位相同期回路。

**【請求項 6】**

前記駆動部は、

前記駆動信号をチャージポンプ電流として出力するチャージポンプと、当該チャージポンプのバイアス電流であって前記チャージポンプ電流の1/倍の電流を生成する電流源とを具備し、

前記ゲイン特性情報取得部で取得されたゲイン特性情報に基づいて前記電流源で生成されるバイアス電流の大きさを制御する

ことを特徴とする請求項4または5に記載の位相同期回路。

**【請求項 7】**

前記ゲイン特性情報取得部は、

ゲイン特性情報取得時には、前記ビットの重付けが低下する方向に制御しながら、前記周波数比較部により順次所定のビット数に達するまで周波数比較を行ない、この周波数比較の都度、その周波数比較結果を前記周波数比較結果保持部の対応するビットに保持するように、周波数2分探索を実行する

ことを特徴とする請求項2に記載の位相同期回路。

**【請求項 8】**

前記周波数比較部は、第1の目標周波数に対して分周比M1でかつ前記第2の目標周波数に対して分周比M2の前記第1および第2の目標周波数よりも低い周波数fLowを持つ判定基準信号の所定周期内における各目標周波数のクロック数をカウントし、そのカウント結果と前記分周比に応じた判定値との大小を比較することで、前記周波数比較を行なうものであり、

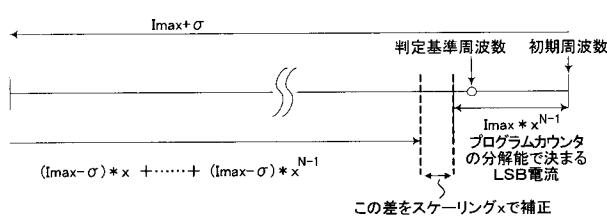

ばらつきによって取り得る前記入力信号 - 発振周波数変換ゲインの最大値をKosciimax、最上位ビットの周波数制御信号を規定する値をS、最上位ビットの周波数制御信号のばらつきをとしたとき、前記所定のビット数Nと前記ビットの重付けを規定するスケーリング×とが、下記式(A)を満たす

ことを特徴とする請求項7に記載の位相同期回路。

**【数A】**

$$\left. \begin{aligned} x^{N-1}S &< \frac{2f_{Low}}{K_{osci\ max}} \quad \cdots (A1) \\ \frac{\sigma}{S} &< \frac{2x - 2x^N + x^{N-1} - 1}{1 - x^N} \cdots (A2) \end{aligned} \right\} (A)$$

**【請求項 9】**

前記発振部は、発振制御信号としての発振制御電流に基づいて発振する電流制御発振部であり、

前記周波数制御信号生成部は、前記周波数制御信号を電流モードで生成することを特徴とする請求項1に記載の位相同期回路。

**【請求項 10】**

前記発振部は、発振制御信号としての発振制御電圧に基づいて発振する電圧制御発振部

10

20

30

40

50

であり、

前記周波数制御信号生成部は、前記周波数制御信号を電流モードで生成することを特徴とする請求項1に記載の位相同期回路。

#### 【請求項11】

前記周波数比較結果保持部は、入力されたクロック信号をカウントする2進カウンタ部を具備し、前記2進カウンタ部のカウント出力を使って、ビットの重付けの切替えタイミングを規定するビット別のビット切替信号を順次生成するビット切替信号生成部と、前記ビット切替信号生成部により生成された前記ビット切替信号の前記ビットの重付けの切替えタイミングで、前記周波数比較部からの周波数比較結果を取り込み記憶するビット別に設けられたデータ保持部とを有する

10

ことを特徴とする請求項2に記載の位相同期回路。

#### 【請求項12】

前記周波数制御信号生成部は、ビットの重付けに応じたソース電流もしくはシンク電流を発生するビット別に設けられた1ビット電流源と、前記1ビット電流源が前記ソース電流および前記シンク電流の何れを発生するのかを前記周波数比較結果保持部に保持されているデータに応じて切り替える切替部とを具備し、ビット別の前記1ビット電流源の入出力電流を合成して出力することで、電流モードの前記周波数制御信号を生成する

ことを特徴とする請求項2に記載の位相同期回路。

#### 【請求項13】

前記周波数制御信号生成部は、前記電流モードの周波数制御信号を電圧信号に変換することで、電圧モードの前記周波数制御信号を生成する電流電圧変換部をさらに具備することを特徴とする請求項12に記載の位相同期回路。

20

#### 【請求項14】

発振制御信号に基づいて所定周波数の出力発振信号を出力する発振部と、前記発振部から出力された前記出力発振信号と外部から入力される入力信号の位相を比較する位相比較部と、ループフィルタ部と、前記位相比較部から出力された位相比較結果を示す信号に基づいて駆動信号を生成し当該駆動信号で前記ループフィルタ部を駆動する駆動部と、前記ループフィルタ部から出力されたループフィルタ出力信号に基づき、前記出力発振信号の位相が前記入力信号の位相に同期するように前記発振制御信号を生成する発振制御信号生成部とを有する位相同期回路を備えた電子機器であって、

30

前記位相同期回路は、2種類の目標周波数を使って、所定の大きさの規定信号と前記発振部を各周波数で発振させるための補正分を前記発振制御信号として供給しつつ実際の発振周波数と前記目標周波数との差を比較することで、実動時の前記発振部の入力信号 - 発振周波数変換ゲイン特性を規定するゲイン特性情報を取得して記憶しておくゲイン特性情報取得部を備え、

通常の位相同期動作時には、前記ゲイン特性情報取得部で取得されたゲイン特性情報に基づいて補正信号を生成し、実動時の前記入力信号 - 発振周波数変換ゲインと前記駆動部が前記ループフィルタ部を駆動する前記駆動信号との積が一定となるように、前記補正信号で前記駆動部を制御する

ことを特徴とする電子機器。

40

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、たとえばテレビジョン装置や携帯電話などの受信用や送信用の通信装置や光ディスク装置などに使用される位相同期(PLL:Phase Locked Loop)回路と、この位相同期回路を具備した電子機器に関する。

##### 【背景技術】

##### 【0002】

たとえば、各種の通信装置や送受信機、あるいは、光ディスク装置などの電子機器においては、位相同期(PLL:Phase Locked Loop)回路が組み込まれることがある。

50

## 【0003】

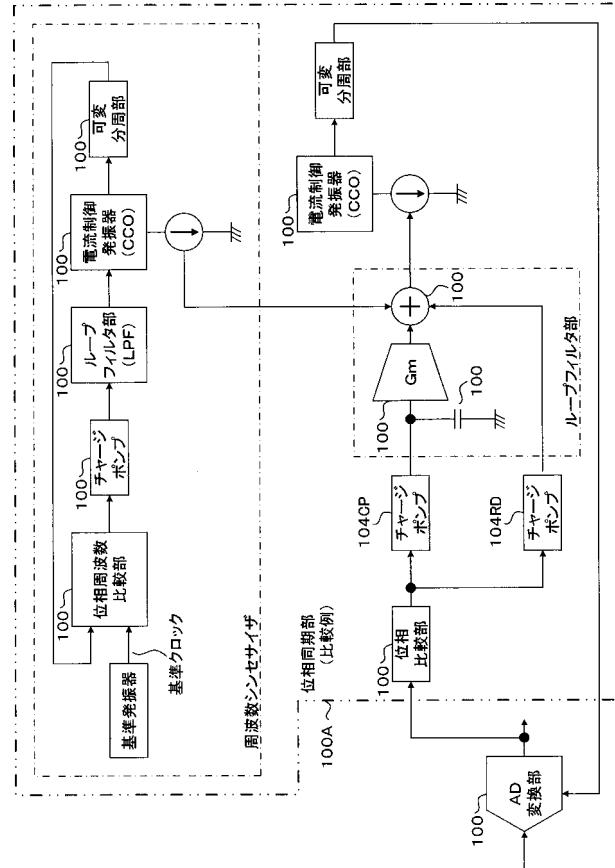

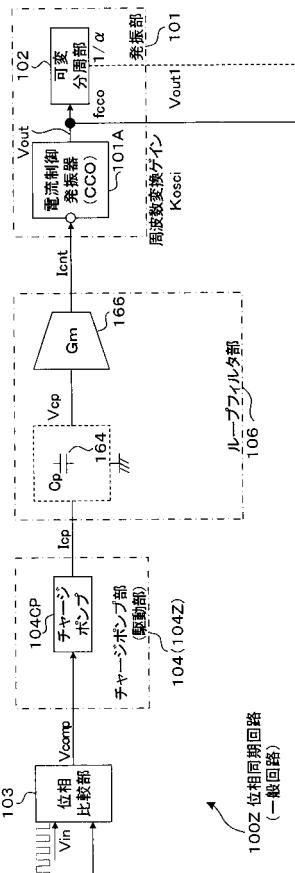

図40は、位相同期回路を一般的に表わした回路ブロック図である。この図40に示す位相同期回路100Zの構成は、後述する非特許文献1～3に記載の構成を一般化して示したものもある。

## 【0004】

図示のように、位相同期回路100Zは、発振制御信号CNに基づき発振周波数fosciの出力発振信号Voutを生成する発振部101と、発振部101から出力された出力発振信号Voutの発振周波数fosciを1/に分周して分周発振信号Vout1を取得する分周部102とを備える。

## 【0005】

また、位相同期回路100Zは、入力信号Vinと発振部101からの出力発振信号Voutもしくは分周部102からの分周発振信号Vout1の位相を比較し、比較結果である位相差を示す誤差信号を比較結果信号Vcompとして出力する位相比較部103と、位相比較部103から出力された比較結果信号Vcompに応じたチャージポンプ電流Icpを入出力する電流出力型の駆動部104Z（以下チャージポンプ部104と称する）と、少なくともループフィルタ容量Cpのコンデンサ（容量素子）164を備え、チャージポンプ部104からのチャージポンプ電流Icpに基づくコンデンサ164の充電電圧Vcpを利用して発振部101の発振周波数fosciを制御するための発振制御信号CNを生成するループフィルタ部106とを備えている。なお、本構成例では、ループフィルタ部106は、発振部101が電流制御発振部101Aであることに対応するように、コンデンサ164の充電電圧Vcpを発振制御電流Icntに変換する電圧電流変換部166も具備している。

10

20

20

## 【0006】

このような構成の位相同期回路100Zにおいては、入力信号Vinと発振部101からの出力発振信号Vout（もしくは分周部102による分周発振信号Vout1）が位相比較部103に入力され、その位相誤差を示す比較結果信号Vcompを元にして、チャージポンプPLLの手法によって発振部101を発振させ、入力信号Vinに位相ロックした出力発振信号Voutを得る。

## 【0007】

ここで、チャージポンプPLLの解析には、線形化した閉ループ伝達関数が一般的に用いられ、チャージポンプ電流Icp、発振部101の入力信号・発振周波数変換ゲインKosci、コンデンサ164のループフィルタ容量Cp、ループフィルタ部106の変換ゲインKIp、ループフィルタ部106のダンピング効果FIp、分周部102の分周比nのとき、その帯域（自然角周波数） $\omega_n$ およびダンピングファクタ $\zeta$ は、式(1-1)および式(1-2)のように表すことができる。なお、ループフィルタ部106の変換ゲインKIpとループフィルタ部106のダンピング効果FIpは、ループフィルタ部106の構成に応じたものとなる（詳細は実施形態で示す）。

30

## 【0008】

なお、ここでは、駆動部104Zの一例としてループフィルタ部106を電流モードで駆動するチャージポンプ104CPの場合で示しているが、回路理論上は、電流と電圧との間には「双対の理」が成立するので、チャージポンプ電流Icpに注目して電流モードで解析した式(1-1)および式(1-2)は、ループフィルタ部106を駆動する駆動電圧Vdrに注目して電圧モードで解析すれば式(1-3)および式(1-4)で示すことができる。なお、この式(1)の各々は、公知のものであるので、式の導出過程については説明を割愛する。

40

## 【0009】

## 【数1】

$$\omega_n = \sqrt{\frac{I_{cp} \cdot K_{osci} \cdot K_{lp}}{C_p \cdot \alpha}} \dots (1-1)$$

$$\zeta = \frac{C_p \cdot F_{lp}}{2} \omega_n \dots (1-2)$$

$$\omega_n = \sqrt{\frac{V_{dr} \cdot K_{osci} \cdot K_{lp}}{C_p \cdot \alpha}} \dots (1-3)$$

$$\zeta = \frac{C_p \cdot F_{lp}}{2} \omega_n \dots (1-4)$$

(1)

10

## 【0010】

20

しかしながら、実際に位相同期回路 100Z が I C ( Integrated Circuit; 半導体集積回路 ) で製造されると、チャージポンプ電流  $I_{cp}$  や変換ゲイン  $K_{lp}$  や入力信号 - 発振周波数変換ゲイン  $K_{osci}$  など、帯域  $n$  やダンピングファクタ  $\zeta$  を決めるパラメータが設計値からばらつくため、所望の値に帯域  $n$  やダンピングファクタ  $\zeta$  を設定することが困難となる。さらに、通常、様々な場所で使われることを考えると、温度によっても各パラメータは変動するため、さらに帯域  $n$  やダンピングファクタ  $\zeta$  は設定値からずれてしまうことになる。

## 【0011】

30

帯域  $n$  が設定値から大きくずれてしまうと、出力発振信号  $V_{out}$  が入力信号  $V_{in}$  に位相ロックするまでの期間、すなわちアライジション時間も設定値から変動するため、位相同期回路 100Z を利用した全体システムの設計が難しくなり、さらに帯域  $n$  が低くずれてしまった場合はジッタが増加してしまう。この問題を回避するためには、入力信号 - 発振周波数変換ゲイン  $K_{osci}$  の製造ばらつきや温度特性を補償する技術が必要不可欠になる。

## 【0012】

40

このような要求に応え得る仕組みとして、非特許文献 1 ~ 3 に提案されている仕組みがある。

## 【0013】

【非特許文献 1】 ZHI-MING LIN, KUEI-CHEN HUANG, JUN-DA CHEN, and MEI-YUAN LIAO, "A CMOS VOLTAGE-CONTROLLED OSCILLATOR WITH TEMPERATURE COMPENSATED", The Second IE EE Asia Pacific Conference on ASICs / Aug 28-30, 2000, p85 ~ 86

【非特許文献 2】 Soon-Seob Lee, Tae-Geun Kim, Jae-Tack Yoo and Soo-Won Kim, "Process-and-temperature compensated CMOS voltage-controlled oscillator for clock generators", ELECTRONICS LETTERS 16th October 2003, Vol. 39, No. 21, p1484 ~ 1485

【非特許文献 3】 Takashi Morie, Shiro Dosho, Kouji Okamoto, Yuji Yamada and Kazuaki Sogawa, "A-90dBc@10kHz Phase Noise Fractional-N Frequency Synthesizer with Accurate Loop Bandwidth Control Circuit", 2005 Symposium on VLSI Circuits Digest of Technical Papers, p52 ~ 55

## 【0014】

50

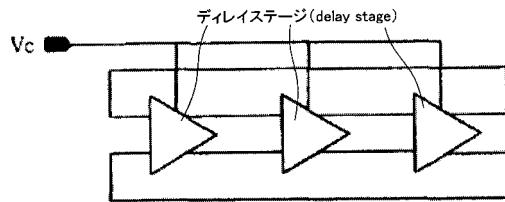

たとえば、非特許文献 1 には、複数段のディレイステージ ( delay stage ) を利用して電圧制御発振器 ( VCO ; Voltage Controlled Oscillator ) を構成しつつ ( 同文献 1 の

Fig.1 と同様の図 4 1 (A) を参照)、ディレイステージのコモン出力電圧が常に一定になるように PMOS トランジスタと NMOS トランジスタのダイオード接続を直列につないだものを負荷とすることで(同文献 1 の Fig.3 と同様の図 4 1 (B) を参照)、温度特性を補正する仕組みが提案されている。

#### 【0015】

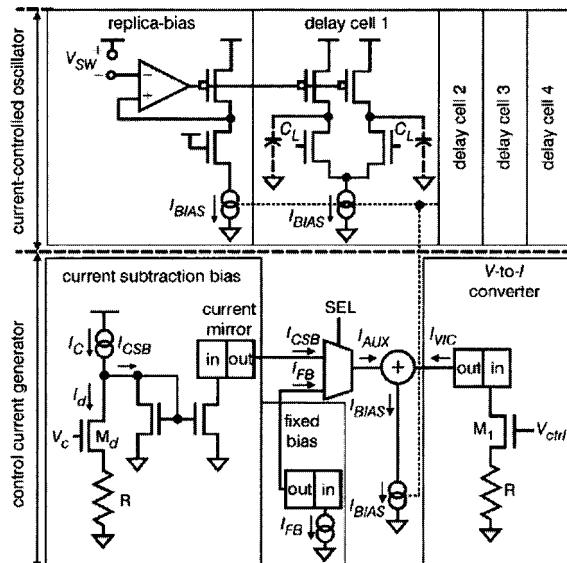

また、非特許文献 2 には、複数段のディレイセル (delay cell) を利用して電圧制御発振器 (VCO) を構成しつつ、温度や製造ばらつきに依存しない電流を回路で作り出し、その電流をディレイセルのバイアス電流とする仕組み(同文献 2 の Fig.1 と同様の図 4 2 を参照)が提案されている。

#### 【0016】

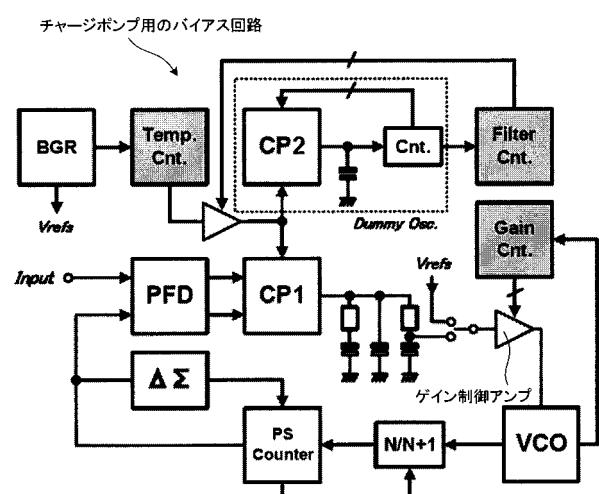

また、非特許文献 3 には、チャージポンプ電流を一定にするための温度変化に依存しない高精度なバイアス回路を設けるとともに、電圧制御発振器 (VCO) の入力側に、発振制御信号 CN に対するゲインを調整するゲイン制御アンプを設け、かつ、電圧制御発振器 (VCO) のゲインを測定し、その結果に応じた補正值でゲイン制御アンプを制御することで、電圧制御発振器の入力にフィードバックする仕組み(同文献 3 の Fig.1 と同様の図 4 3 を参照)が提案されている。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0017】

しかしながら、非特許文献 1, 2 に記載の仕組みでは、電圧制御発振器の入力信号 - 発振周波数変換ゲイン  $K_{osci}$  が非線形な場合には、完全に補正をすることは非常に困難である。また、非特許文献 1 に記載の仕組みでは、ディレイステージの構成に工夫をするので、そのディレイステージの回路設計が複雑になる。また、非特許文献 2 に記載の仕組みでは、温度や製造ばらつきに依存しない電流を作り出す回路が必要になり、また、作り出された電流をディレイセルのバイアス電流とする仕組みも必要となるので、電圧制御発振器の回路設計が複雑になる。

#### 【0018】

また、非特許文献 3 に記載の仕組みでは、チャージポンプ電流を一定にするための温度変化に依存しない高精度なバイアス回路や、発振制御信号 CN に対するゲインを電圧制御発振器の入力前で調整するゲイン制御アンプが新たに必要になってしまう。

#### 【0019】

さらに、非特許文献 3 に記載の仕組みでは、それぞれの補正回路にも製造ばらつきが存在し、このばらつきを考慮しても電圧制御発振器のゲインを補正可能にするように補正回路を設計しなければいけないため、補正回路の設計が非常に困難になってしまふ。測定結果に基づきゲイン制御アンプのゲイン値を絶対的に調整する、つまりゲインの絶対値の管理を行なうようにしているが、デバイス特性や回路構成上、絶対値の管理では、ばらつきを回避することは事実上不可能であるからである。

#### 【0020】

本発明は、上記事情に鑑みてなされたものであり、特許文献 1 ~ 3 に記載の仕組みとは異なる新たな回路構成によって、入力信号 - 発振周波数変換ゲイン  $K_{osci}$  の製造ばらつきや温度変化に起因する帯域  $n$  やダンピングファクタ  $\zeta$  のばらつきの発生を防止することのできる仕組みを提供することを目的とする。

#### 【0021】

また、さらに好ましくは、チャージポンプに対するバイアス回路の精度管理を緩和でき、あるいは、補正の製造ばらつきを小さくすることのできる仕組みを提供することを目的とする。

#### 【0022】

また、さらに好ましくは、発振回路に対するバイアス回路を不要にし、あるいは、発振回路を特殊な回路構成にする必要がなく一般的な回路を使用できるような仕組みを提供することを目的とする。

10

20

30

40

50

## 【課題を解決するための手段】

## 【0023】

本発明に係る位相同期回路やこの位相同期回路を備えた電子機器は、発振制御信号に基づいて所定周波数の出力発振信号を出力する発振部と、発振部から出力された出力発振信号と外部から入力される入力信号の位相を比較する位相比較部と、ループフィルタ部と、位相比較部から出力された位相比較結果を示す信号に基づいて駆動信号を生成し当該駆動信号でループフィルタ部を駆動する駆動部と、ループフィルタ部から出力されたループフィルタ出力信号に基づき、出力発振信号の位相が入力信号の位相に同期するように発振制御信号を生成する発振制御信号生成部とを備えた位相同期回路であって、先ず、2種類の目標周波数を使って、所定の大きさの規定信号と発振部を各周波数で発振させるための補正分とを発振制御信号として供給しつつ、実際の発振周波数と前記目標周波数との差を比較することで、実動時の発振部の入力信号 - 発振周波数変換ゲイン特性を規定するゲイン特性情報を取得し、この取得したゲイン特性情報を所定の記憶媒体に記憶しておくゲイン特性情報取得部を具備するようにした。

## 【0024】

そして、ゲイン特性情報取得後の通常の位相同期動作時には、ゲイン特性情報取得部で取得されたゲイン特性情報（記憶されている情報で表わされる）に基づいて補正信号を生成し、実動時の入力信号 - 発振周波数変換ゲイン（省略して周波数変換ゲインとも称する）と駆動部がループフィルタ部を駆動する駆動信号との積が一定となるように、補正信号で駆動部を制御するようにした。

## 【0025】

実動状態の入力信号 - 発振周波数変換ゲインに関する情報を測定し、その結果を位相同期動作時に反映させるという点では、非特許文献3に記載の仕組みと似通っているが、補正に当たっての制御手法は、全く異なる。すなわち、本発明では、式(1)における  $I_{cp} \cdot K_{osci}$  や  $V_{dr} \cdot K_{osci}$  に着目してなされたものであり、周波数変換ゲインとループフィルタ用の駆動信号との積が一定となるように、ゲイン特性情報（詳しくはゲイン特性情報に基づく補正信号）を使って、ループフィルタ用の駆動部を制御する。 $K_{osci}$  がばらつきを持ったままであっても、そのばらつきを相殺するように  $I_{cp}$  や  $V_{dr}$  側を調整することで、 $K_{osci}$  と  $I_{cp}$  や  $V_{dr}$  の積が一定であるようにすることができる。式(1)から分かるように、 $K_{osci}$  がばらつきを持ったままであっても、 $K_{osci}$  と  $I_{cp}$  や  $V_{dr}$  の積が一定であれば、帯域  $n$  やダンピングファクタ は一定である。

## 【0026】

こうすることで、周波数変換ゲインが一定になるように制御する非特許文献1に記載の仕組みで生じる補正ばらつきの影響を緩和する。何故なら、周波数変換ゲインが一定になるように制御するには、補正量の高精度の絶対値管理が必要になり実現が困難になるが、本発明のように、 $K_{osci}$  と  $I_{cp}$  や  $V_{dr}$  の積が一定となるように制御する仕組みを採用することで、管理精度が緩和される「比」による管理ができるようになるからである。

## 【0027】

また従属項に記載された発明は、本発明に係る位相同期回路のさらなる有利な具体例を規定する。

## 【0028】

たとえば、電気（電子）回路においては、電流と電圧は「双対の理」の関係にあり、各機能部に入力する入力信号や制御信号あるいは各機能部から出力される信号は、電圧モードおよび電流モードの何れをも取ることができる。そして、各機能部の接続関係において、電圧モードと電流モードとが不整合になるときには、その整合を探るための信号変換部、たとえば、電流信号を電圧信号に変換する電流電圧変換部や、電圧信号を電流信号に変換する電圧電流変換部を設ければよい。

## 【0029】

ただし、ゲイン特性情報取得部としての大まかな回路構成上は、発振部が発振制御電流で制御される電流制御発振部である場合には発振制御信号を電流モードで出力する電流出

力型の構成とし、発振制御電圧で制御される電圧制御発振部である場合には発振制御信号を電圧モードで出力する電圧出力型の構成とするのがよい。

#### 【0030】

また、ゲイン特性情報取得部において2種類の目標周波数を使って補正信号を取得するに当たっては、補正情報取得時に第2の目標周波数についての周波数制御信号生成部にて取得される第2の周波数制御信号をK倍する構成を採りつつ、標準の入力信号・発振周波数変換ゲインと標準の駆動信号との積を、第1の目標周波数と第2の目標周波数との差分で除算した値に「K」を設定するのがよい。こうすることで、確実に周波数変換ゲインとループフィルタ用の駆動信号の積が一定となるように制御することができるようになる。

10

#### 【0031】

また、このような「K」倍の設定を実現する回路構成としては、電圧モードおよび電流モードの何れをも採用し得るが、電流モードであれば、比較的簡単な構成で、かつ高精度に比の管理を実現できるカレントミラー回路構成を採用できる利点がある。

#### 【0032】

なお、この場合、発振制御信号が電圧モードである場合には、カレントミラー回路の入力側に、電圧モードの周波数制御信号を電流モードの周波数制御信号に変換する電圧電流変換部を介在させればよい。

#### 【0033】

また、ループフィルタ部を駆動する駆動部の構成としても、電圧モードおよび電流モードの何れをも採用し得るが、補正信号が電流モードである場合には、駆動部も同様に電流モードで動作する構成、いわゆるチャージポンプの構成を探るのがよい。この場合、チャージポンプ電流の1/2倍の電流を生成する電流源を用意し、ゲイン特性情報取得部で取得された補正信号に基づいて電流源で生成されるバイアス電流の大きさを制御するようになるのがよい。

20

#### 【0034】

また、ゲイン特性情報取得部において2種類の目標周波数を使ってゲイン特性情報を取得するに当たっては、周波数別に、ビットの重付けを低下する方向に切り替えながら目標周波数と実際の周波数との大小を比較し、その周波数比較結果をデジタルデータとして保持し、そのデータに基づく周波数制御電流で発振部を再度制御しながら所定回数（回数がビット数に対応する）繰り返す周波数2分探索の手法を探るのがよい。

30

#### 【発明の効果】

#### 【0035】

本発明によれば、2種類の目標周波数を使って実動状態の発振部の入力信号・発振周波数変換ゲイン特性を規定するゲイン特性情報を測定しておき、通常の位同期動作時には、そのゲイン特性情報に基づいて、実動時の周波数変換ゲイン（Kosci）とループフィルタ用の駆動信号（IcpやVdr）との積が一定となるように駆動部を制御するようにした。KosciとIcpやVdrの積が一定となるように制御することで、周波数変換ゲインのばらつきに起因する帯域やダンピングファクタのばらつきの発生を防止できるようになる。

#### 【0036】

また、付加的な効果として、KosciとIcpやVdrの積が一定となるように制御する仕組みを採用することで、管理精度が緩和される「比」による管理ができるようになり、周波数変換ゲインの製造ばらつきや温度変化に起因する帯域nやダンピングファクタのばらつきを高精度に補正することができる。その結果、補正の製造ばらつきを小さくすることができる。また、管理精度が緩和される「比」による管理ができるようになるから、補正用の制御を実行する駆動部の構成としても、精度の管理を緩和できる。

40

#### 【0037】

また、別の付加的な効果として、2種類の目標周波数を使って実動状態の周波数変換ゲインを規定するゲイン特性情報を測定するので、非線形な特性を持つ発振部であっても、注目する周波数範囲では線形領域として取り扱うことができる。その結果、発振回路に対する高精度なバイアス回路が不要になるし、また、発振回路を特殊な回路構成にする必要

50

がなく一般的な回路を使用できるようになる。

【0038】

さらに、別の付加的な効果として、2種類の目標周波数を使って、所定の大きさの規定信号と発振部を各周波数で発振させるための補正分を発振制御信号として発振部に供給しながら実動状態の周波数変換ゲインを規定するゲイン特性情報を測定するので、ゲイン特性情報取得後に通常の位相同期動作に戻ると、発振周波数を一方の目標周波数にするようにするための補正分、すなわち規定信号との差分を示す周波数制御信号が、規定信号と合成されて発振部に供給されるので、最初の目標周波数を、通常の位相同期動作でロックさせる周波数にしておけば、切替え時の応答の問題が生じない。

10

【発明を実施するための最良の形態】

【0039】

以下、図面を参照して本発明の実施形態について詳細に説明する。

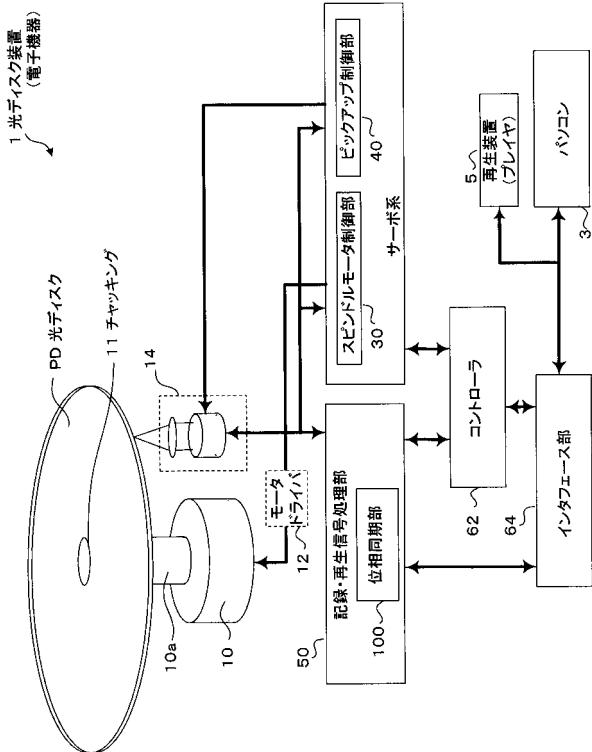

【0040】

<光ディスク装置の概要>

図1は、位相同期回路を具備した電子機器の一例である光ディスク装置の一実施形態を示すブロック図である。

20

【0041】

本実施形態の光ディスク装置1は、光ディスクPD(Photo Disk)に付加情報を記録するあるいは光ディスクPDに記録されている情報を読み取るためのレーザ光源を具備した光ピックアップ14を備える。また、信号処理系として、サーボ系と、記録・再生系と、コントローラ系とを備えている。ここで、サーボ系として、光ディスク装置1は、回転サーボ系とトラッキングサーボ系とフォーカスサーボ系とを有する。トラッキングサーボ系とフォーカスサーボ系とを纏めてピックアップサーボ系とも称する。

20

【0042】

光ディスクPDとしては、CD(コンパクトディスク)やCD-ROM(Read Only Memory)などのいわゆる再生専用の光ディスクのほか、たとえばCD-R(Recordable)のような追記型光ディスクや、CD-RW(Rewritable)のような書き換え可能型光ディスクであってもよい。さらには、CD系の光ディスクに限らず、MO(光磁気ディスク)であってもよいし、通常のDVD(Digital VideoまたはVersatile Disk)や、ブルーレイ(Blu-ray)あるいはHDDVD(High Definition DVD)などの次世代DVDといったDVD系の光ディスクであってもよい。また、現行のCDフォーマットを踏襲しながら、記録密度を現行フォーマットの約2倍とした、いわゆる2倍密度のCD(DDCD; D=Double Density)やCD-RあるいはCD-RWであってもよい。

30

【0043】

光ディスク装置1は、具体的には、回転サーボ系として、音楽などの再生すべき情報が記録された光ディスクPDを回転させるスピンドルモータ10と、スピンドルモータ10を駆動するモータドライバ12と、モータドライバ12を制御する回転制御部(回転サーボ系)の一例であるスピンドルモータ制御部30とを備える。

【0044】

スピンドルモータ制御部30は、図示を割愛するが、ラフサーボ回路、速度(スピード)サーボ回路、位相(フェーズ)サーボ回路、および各サーボ回路の各出力を切り替えて出力するセレクタを有する。

40

【0045】

ラフサーボ回路は、光ディスクPDの回転スピードを大まかに制御する。速度サーボ回路は、同期信号に基づき回転スピードをさらに高精度に合わせる。位相サーボ回路は、再生信号の位相と基準信号の位相を合わせる。セレクタは、ラフサーボ回路、速度サーボ回路、位相サーボ回路の各出力を切り替えてモータドライバ12に出力する。

【0046】

光ディスクPDは、チャッキング11によりスピンドルモータ10の回転軸10aに固定されるようになっている。スピンドルモータ10は、モータドライバ12とスピンドル

50

モータ制御部30とによって線速度が一定になるように制御される。その線速度はモータドライバ12とスピンドルモータ制御部30によって段階的に変更が可能である。

#### 【0047】

また、光ディスク装置1は、トラッキングサーボ系およびフォーカスサーボ系として、光ピックアップ14の光ディスクPDに対する半径方向位置を制御するピックアップ制御部40を備える。図示を割愛するが、ピックアップ制御部40は、たとえば、光ディスクPDに記録されているサブコーディングを読み取るサブコーディング検出回路と、図示しないトラックエラー検出回路により検出されたトラックエラー信号やサブコーディング検出回路により検出されたアドレス情報に基づいて光ピックアップ14の対光ディスクPDに対する半径方向位置を制御するトラッキングサーボ回路とを備える。

10

#### 【0048】

ピックアップ制御部40は、図示しないトラックアクチュエータやシーケモータを制御することで、光ピックアップ14から発せられるレーザ光のレーザスポットを光ディスクPD上の目的の場所（データ記録位置やデータ再生位置）に位置するように制御する。

#### 【0049】

光ピックアップ14は、図示しない公知の半導体レーザ、光学系、フォーカスアクチュエータ、トラックアクチュエータ、受光素子、およびポジションセンサなどを内蔵しており、光ディスクPDの記録面にレーザ光を照射し、また反射光を受光して電気信号に変換するように構成されている。光ピックアップ14の半導体レーザは、図示しないレーザドライバにより駆動されるようになされており、このレーザドライバの駆動によって、データ再生時には所定の再生パワーの光ビームを射出し、情報の記録時には所定の記録パワーの光ビームを射出する。

20

#### 【0050】

また、この光ピックアップ14は、図示しないシーケモータ（スライドモータ）によってスレッジ（半径）方向に移動可能に構成されている。これらのフォーカスアクチュエータ、トラックアクチュエータ、シーケモータは、受光素子やポジションセンサから得られた信号に基づいてモータドライバ12とスピンドルモータ制御部30およびピックアップ制御部40によってレーザ光のレーザスポットを光ディスクPD上の目的の場所（データ記録位置やデータ再生位置）に位置するように制御される。

30

#### 【0051】

また光ディスク装置1は、記録・再生系として、光ピックアップ14を介して情報を記録する情報記録部および光ディスクPDに記録されている情報を再生する情報再生部の一例である記録・再生信号処理部50を備える。記録・再生信号処理部50の詳細構成例については後述するが、少なくとも、位相同期回路の一例である位相同期部100を備えている。

#### 【0052】

また、光ディスク装置1は、コントローラ系として、スピンドルモータ制御部30およびピックアップ制御部40を有するサーボ系や記録・再生信号処理部50の動作を制御するコントローラ62と、当該光ディスク装置1を利用した各種の情報処理を行なう情報処理装置の一例であるパーソナルコンピュータ（以下パソコンと称する）3や音声および／または画像を再生する再生装置（いわゆるCDプレイヤやDVDプレイヤなど）5（パソコン3や再生装置5を纏めて、以下装置本体とも称する）との間のインターフェース（接続）機能をなすインターフェース部64とを備える。

40

#### 【0053】

このような構成の光ディスク装置1においては、再生処理時には、光ディスクPDから光ピックアップ14で読み出された光信号は光ピックアップ14に内蔵の受光素子で電気信号に変換され、その電気信号が、スピンドルモータ10や光ピックアップ14の制御を行なうスピンドルモータ制御部30およびピックアップ制御部40を具備したサーボ系（制御系）と、データの記録・再生を行なう記録・再生信号処理部50とに送られる。

#### 【0054】

50

スピンドルモータ制御部30およびピックアップ制御部40は、コントローラ62の制御の元で、この電気信号を元にしてスピンドルモータ10の回転数や、光ピックアップ14のフォーカシングおよびトラッキングを調整する。

#### 【0055】

これとともに、記録・再生信号処理部50では、取得したアナログの電気信号をデジタルデータに変換し復号化を行ない、パソコン3や再生装置5などの光ディスク装置1を利用する装置本体に渡す。パソコン3や再生装置5では、復号化されたデータに基づき、画像・音声データとして再生する。

#### 【0056】

また、光ディスクPDへデータを記録する記録処理時には、スピンドルモータ制御部30およびピックアップ制御部40は、コントローラ62の制御の元で、一定速度で光ディスクPDを回転させる。これとともに、記録・再生信号処理部50では、再生とは逆に、データを符号化して光ピックアップ14に内蔵のレーザダイオードなどに供給することで、電気信号を光信号へ変換して、光ディスクPDに情報を記録する。

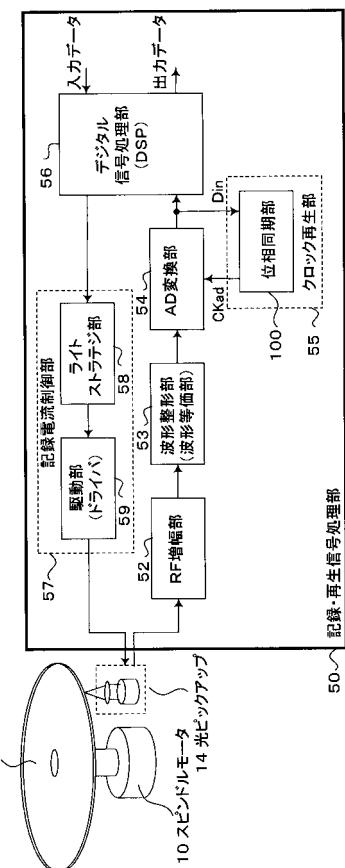

10

#### 【0057】

##### <記録・信号処理部の概要>

図2は、記録・再生信号処理部50の一構成例を示す機能ブロック図である。図示のように、記録・再生信号処理部50は、光ピックアップ14により読み取られた微小なRF(高周波)信号(以下再生RF信号ともいう)を所定レベルに増幅するRF増幅部52と、RF増幅部52から出力された再生RF信号を整形する波形整形部(波形等化器;Equalizer)53と、波形整形部53から出力されたアナログの再生RF信号をデジタルデータに変換するAD変換部(ADC;Analog to Digital Converter)54とを備える。

20

#### 【0058】

光ピックアップ14で読みだされる信号は様々な周波数を持ち、高域で振幅が減少するため、そのままでは符号間干渉を起こしデータを正確に再生することができない。これを補償するために、波形整形部53でRF増幅部52の出力信号の波形等化を行なう。

#### 【0059】

また、記録・再生信号処理部50は、AD変換部54から出力されたデジタルデータ列に基づきクロック信号を再生するクロック再生部55と、AD変換部54から出力されたデジタルデータ列(再生RF信号に対応するもの)を復調し、デジタルオーディオデータやデジタル画像データなどを復号化するなどのデジタル信号処理をするDSP(Digital Signal Processor)で構成されたデジタル信号処理部56と、情報を光ディスクPDに記録するためのレーザ光の記録電流を制御(オンオフ)する記録電流制御部57とを備える。

30

#### 【0060】

クロック再生部55は、詳細は後述するが、AD変換部54からのデジタルデータ(デジタルデータ列Din)にロックしてクロック信号を生成するデータリカバリ型の位相同期部100を有する。クロック再生部55は、再生したクロック信号をAD変換部54へADクロック(サンプリングクロック)CKadとして供給したり、その他の機能部に供給したりする。AD変換部54は、このADクロックCKadに基づいてアナログ信号をデジタルデータに変換する。

40

#### 【0061】

記録電流制御部57は、光ディスクPDの材質と記録速度に応じて光出力パワーをマルチパルス変調するライトストラテジ部(Write Strategy)58と、レーザ光源(光ピックアップ14内にある)から発せられるレーザ光の光出力(光強度、光出力パワー)を一定値に保持するためのAPC(Auto Power Control)制御回路を具備した駆動部(Laser Diode Driver)59とを有する。

#### 【0062】

レーザ光源から出射された記録用光ビームは、光ピックアップ14内の図示しないコリメータレンズにより平行光に変換された後、図示しないビームスプリッタを透過して図示

50

しない対物レンズにより集束され、スピンドルモータ 10 により回転駆動される光ディスク P D に照射される。このとき、記録用光ビームは、記録用の情報に応じて変調されているので、光ディスク P D の所定位置（情報記録エリア）には、情報に対応したピット列が形成され、これにより、光ディスク P D に情報が記録されることになる。このとき、本実施形態では、ライトストラテジ部 58 にて、ピット（記録マーク）の形状歪によるデータ誤りを抑えるようにしている。

#### 【0063】

たとえば、光源として用いるレーザとしては、近年、半導体素子を利用した半導体レーザが、極めて小型で、かつ駆動電流に高速に応答するため、各種装置の光源として広く使用されるようになっている。また、記録や再生の媒体として用いる書換可能な光ディスク P D としては、相変化光ディスクや光磁気ディスクなどが広く知られており、記録、再生、消去する際に照射されるレーザ光の出力が異なる。

10

#### 【0064】

一般的には、記録時は光ディスク P D にピットと呼ばれる記録マークを作るために、レーザビームの出力を高くする（たとえば 30 mW 以上）が、再生時は記録ピットを破壊することなく情報の読み出しを行なうことができるよう、記録時よりも弱い出力（たとえば 3 mW）のレーザビームを光ディスク P D に照射するようにしている。近年の高密度、高転送レートの光ディスク P D において、記録再生が可能なエラーレートを得るために、これらのレーザビームの強度を十分に制御することが必要とされている。

20

#### 【0065】

しかし、半導体レーザは駆動電流・光出力特性の温度特性変化が著しく、その光出力を所望の強度に設定するために、半導体レーザの光出力を一定に制御する回路、いわゆる A P C 制御回路が必要となる。A P C 制御では、情報書き込み時の光信号をモニタリングして得た帰還電流が所定のパワー基準電流となるような負帰還制御ループを構成することで、レーザ発光パワーが一定になるように制御する。

20

#### 【0066】

ここで、近年の書き可能な光ディスク P D では、その高密度化の優位性より記録マークの両端の変化を記録するマークエッジ記録が主流となっている。また、マークエッジ記録でのマークの形状歪によるデータ誤りを抑える技術として、ライトストラテジ部 58 においては、ディスクの材質と記録速度に応じてレーザ出力パワーをマルチパルス変調するライトストラテジ技術を採用する（たとえば特開 2000-244054 号公報参照）。

30

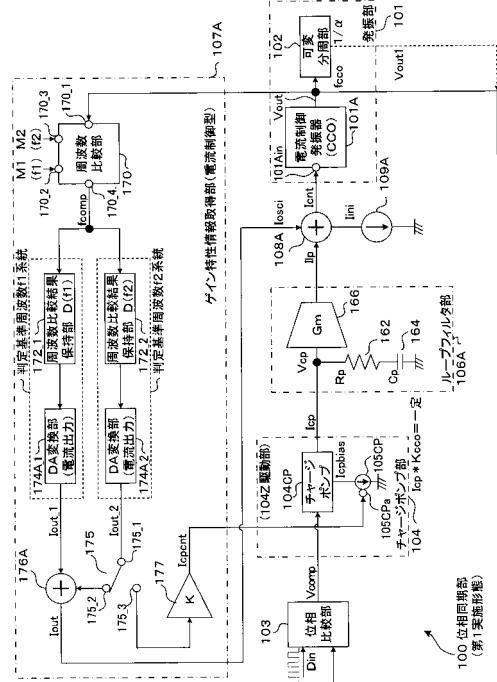

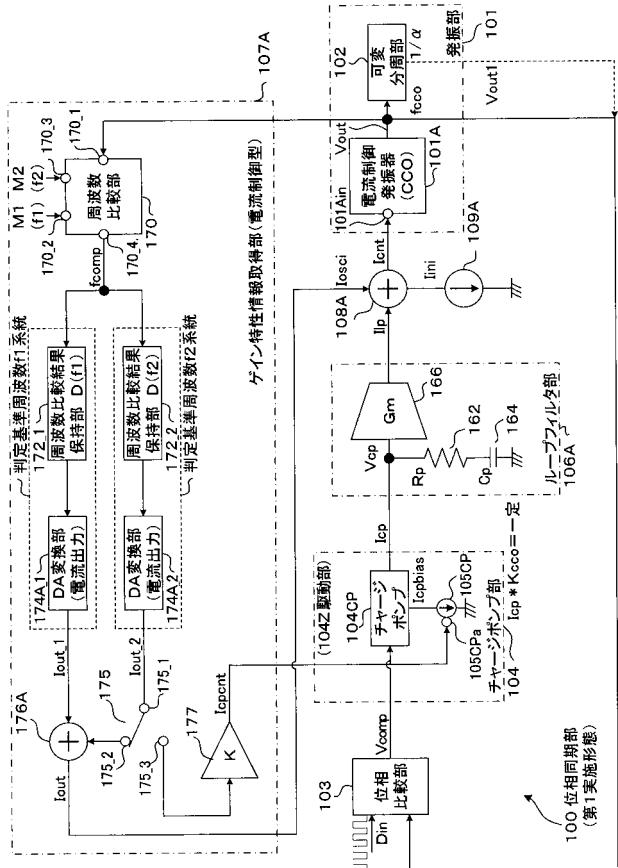

#### 【0067】

<< 位相同期部 ; 第 1 実施形態 >>

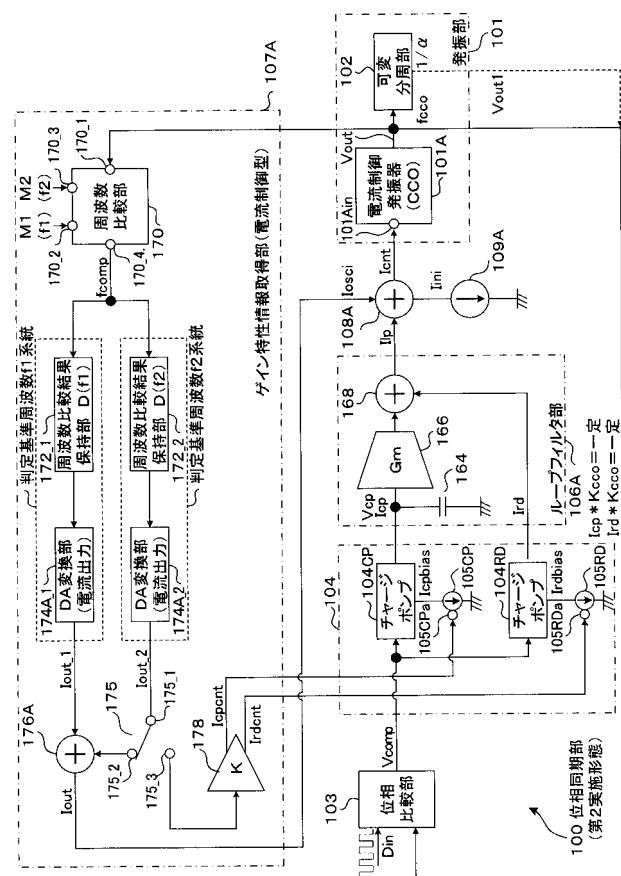

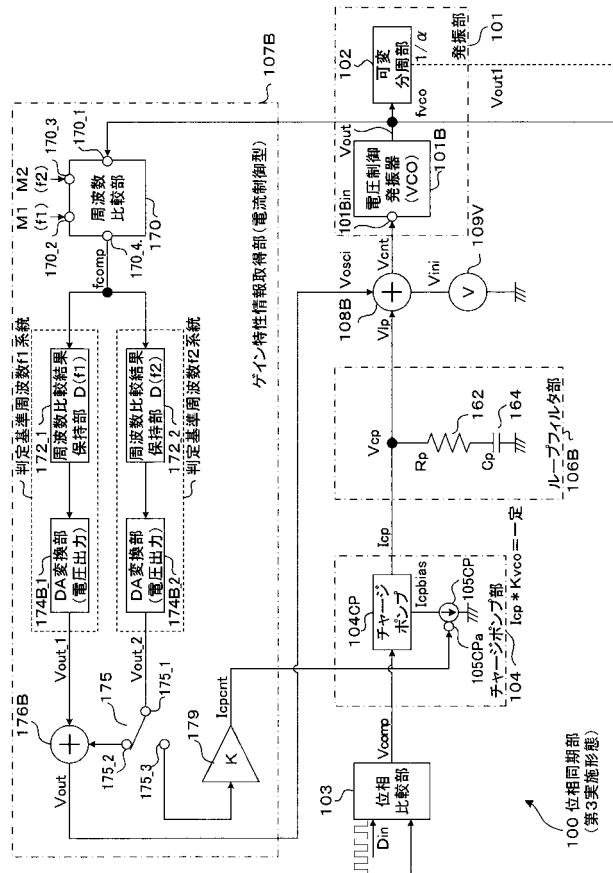

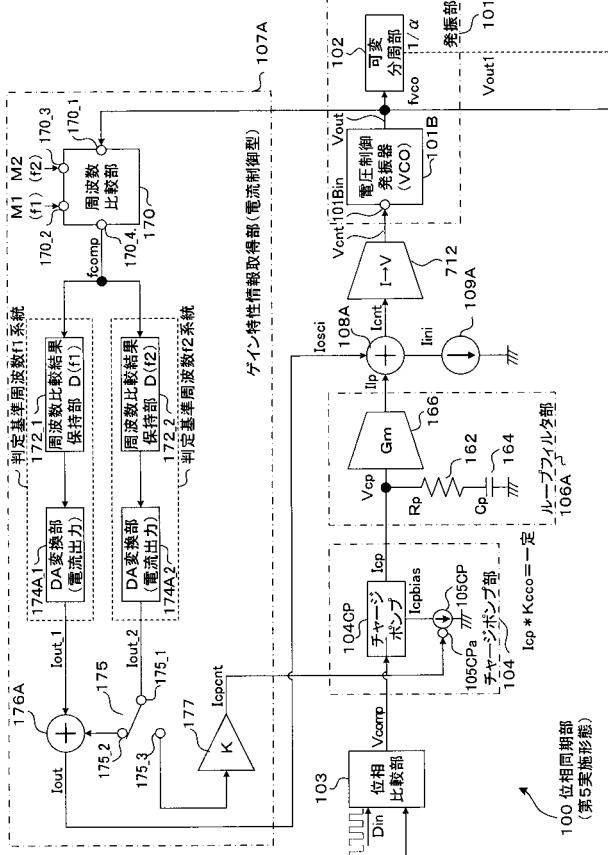

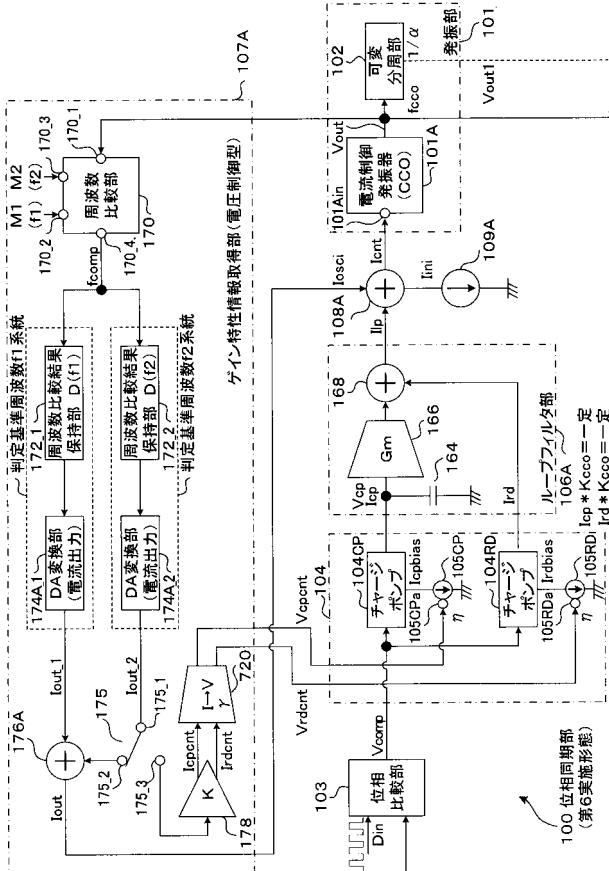

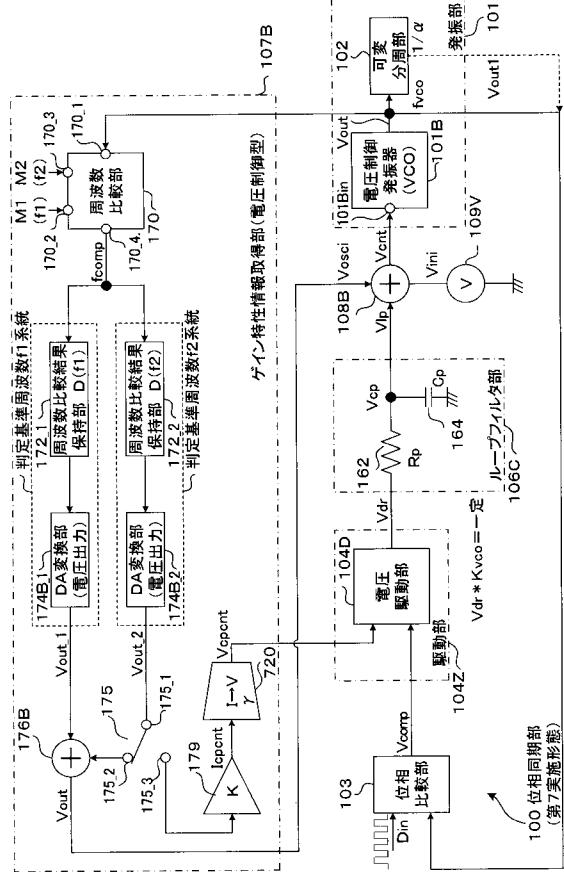

図 3 は、位相同期部（位相同期回路）100 の第 1 実施形態を示す機能ブロック図である。また、図 4 は、比較例としての、ゲイン特性情報取得部を適用しない場合の位相同期部 100 A の構成例を示す図である。なお、この比較例では、後述する第 2 実施形態と同様に、チャージポンプ部 104 に、2 つのチャージポンプ 104 CP , 104 rd を用いた場合で示している。

30

#### 【0068】

本実施形態の位相同期部 100 は、発振部として電流制御発振回路（C C O ; Current Control Oscillator）を採用している点に第 1 の特徴を有するとともに、電流制御発振回路の周波数変換ゲイン特性の製造ばらつきや温度特性を補正するゲイン特性情報取得部 107 として電流出力型のもの（ゲイン特性情報取得部 107 A）を備える点に第 2 の特徴を有する。

40

#### 【0069】

ゲイン特性情報取得部 107 A は、2 種類の目標周波数（判定基準周波数  $f_1$ ,  $f_2$ ）を使って、所定の規定信号  $I_n$  と電流制御発振部 101 A を各周波数で発振させるための補正分とを合成して発振制御電流  $I_{cnt}$  として電流制御発振部 101 A に供給しながら、実動状態の電流制御発振部 101 A の入力電流 - 発振周波数変換ゲイン  $K_{cco}$  を規定する 2 種類の目標周波数の各発振制御信号の差の情報を測定することで、入力電流 - 発振周波

50

数変換ゲイン  $K_{cco}$  のばらつきを補正するための制御電流  $I_{cpcnt}$ （補正信号の一例）を示す情報を取得して所定の記憶媒体に記憶しておく。そして、実際の位相同期動作時には、記憶しておいた情報で示される制御電流  $I_{cpcnt}$  を補正信号として使って、入力電流 - 発振周波数変換ゲイン  $K_{cco}$  のばらつきが相殺されるように駆動部 104Z を制御する。

#### 【0070】

具体的には、第1実施形態の位相同期部 100 は、電流制御発振部（CCO）101A を備える。電流制御発振部 101A は、周波数制御入力端子 101Ain に供給される発振制御電流  $I_{cnt}$  と、自己の入力電流 - 発振周波数変換ゲイン  $K_{cco}$  とに従い、発振制御電流  $I_{cnt}$  に対応した発振周波数  $f_{cco}$  の出力発振信号  $V_{out}$  を出力端子 101Aout から出力する。

10

#### 【0071】

なお、電流制御発振部 101A の後段には、必要に応じて、電流制御発振部 101A の出力端子 101Aout から出力された出力発振信号  $V_{out}$  の発振周波数  $f_{cco}$  を 1 / に分周して分周発振信号  $V_{out1}$  を取得する分周部 102 を設けてもよい。なお、 は、分周比であって、正の整数、好ましくは 2 のべき乗で、かつ可変にする。

#### 【0072】

また、位相同期部 100 は、AD 変換部 54 から出力されたデジタルデータ列  $D_{in}$  と電流制御発振部 101A からの出力発振信号  $V_{out}$  もしくは分周部 102 からの分周発振信号  $V_{out1}$ （以下、断りのない限り出力発振信号  $V_{out}$  で説明する）の位相を比較し、比較結果である位相差を示す誤差信号を比較結果信号  $V_{comp}$  として出力する位相比較部 103 と、位相比較部 103 から出力された比較結果信号  $V_{comp}$  に応じたチャージポンプ電流  $I_{cp}$  を入出力するチャージポンプ部 104 と、チャージポンプ部 104 からのチャージポンプ電流  $I_{cp}$  に基づき電流制御発振部 101A の発振周波数  $f_{cco}$  を制御するためのループフィルタ出力電流  $I_{lp}$  を生成するループフィルタ部 106A とを備えている。

20

#### 【0073】

第1実施形態の位相同期部 100 において、チャージポンプ部 104 は、位相比較部 103 から出力された比較結果信号  $V_{comp}$  に応じた駆動電流（チャージポンプ電流  $I_{cp}$  と称する）を入出力するチャージポンプ 104CP と、チャージポンプ 104CP にバイアス電流  $I_{cpbias}$  を供給する電流値可変型の電流源 105CP とを備えている。

30

#### 【0074】

位相比較部 103 は、デジタルデータ列  $D_{in}$  および出力発振信号  $V_{out}$  の位相を比較し、比較結果である位相差を示す誤差信号を比較結果信号  $V_{comp}$  としてチャージポンプ 104CP に入力する。

#### 【0075】

電流値可変型の電流源 105CP は、電流モードでチャージポンプ電流  $I_{cp}$  を制御可能になっている。具体的には、制御入力端子 105CPa に供給される制御電流  $I_{cpcnt}$  をカレントミラー形式（カレントミラー比は 1 : 1 でよい）で受けてチャージポンプ 104CP にバイアス電流  $I_{cpbias}$  を供給するようになっている。カレントミラー比が 1 : 1 のときには、制御電流  $I_{cpcnt} =$  バイアス電流  $I_{cpbias}$  である。チャージポンプ 104CP は、バイアス電流  $I_{cpbias}$  に対して 倍のチャージポンプ電流  $I_{cp}$  を出力する。

40

#### 【0076】

「制御電流  $I_{cpcnt}$  をカレントミラー形式で受けて」とは、たとえば、N チャネル型の MOS (NMOS) トランジスタをカレントミラー接続し、ゲート端子と共に接続された一方のドレイン端子を制御入力端子 105CPa として制御電流  $I_{cpcnt}$  を供給し、他方のドレイン端子にバイアス電流  $I_{cpbias}$  を得る構成を採ることを意味する。

#### 【0077】

また、第1実施形態の位相同期部 100 は、チャージポンプ 104CP の後段に、ループフィルタ部 106A と、電流制御発振部 101A の周波数変換ゲイン特性の製造ばらつきや温度特性を補正するゲイン特性情報取得部 107A と、各部からの電流信号を加算して電流制御発振部 101A の周波数制御入力端子 101Ain に供給する電流加算部 108A

50

と、電流加算部 108A に所望とする出力発振信号  $V_{out}$  の発振周波数  $f_{cco}$  に適合させた初期電流  $I_{ini}$  を供給する規定電流源 109A とを備えている。

#### 【0078】

電流加算部 108A は、各部からの電流信号を加算することで、出力発振信号  $V_{out}$  の位相がデジタルデータ列  $D_{in}$  の位相に同期するように発振制御電流  $I_{cnt}$  を生成する発振制御信号生成部の一例である。

#### 【0079】

ここで、「所望とする出力発振信号  $V_{out}$  の発振周波数  $f_{cco}$  に適合させた初期電流  $I_{ini}$ 」とは、標準的あるいは理想的な条件下において、電流加算部 108A への他の電流入力（ループフィルタ出力電流  $I_{lp}$  およびゲイン特性情報取得部 107A からの周波数制御電流  $I_{osci}$ ）がなく初期電流  $I_{ini}$  のみで希望とする周波数と同じ発振周波数  $f_{cco}$  が得られるような電流値を意味する。

10

#### 【0080】

希望とする周波数（＝発振周波数  $f_{cco}$ ）が複数種類となる場合には、その希望とする周波数（＝発振周波数  $f_{cco}$ ）の別に最適化させた初期電流  $I_{ini}$  を設定する。このため、デジタルデータ列  $D_{in}$  のデータレート（周波数）が切り替わるごとに、規定電流源 109A の初期電流  $I_{ini}$  を切り替える。

#### 【0081】

このための仕組みとしては、図示を割愛するが、各周波数の別に、その周波数に適合した個別の初期電流  $I_{ini}$  が設定されている周波数別の規定電流源 109A を用意しておき、デジタルデータ列  $D_{in}$  のデータレート（周波数）が切り替わるごとに、その周波数別の規定電流源 109A を、その周波数に適合したものに切り替える構成を探るのがよい。

20

#### 【0082】

こうすることで、ゲイン特性情報取得部 107A によるゲイン補正処理に基づく周波数制御電流  $I_{osci}$  は、初期電流  $I_{ini}$ （およびループフィルタ出力電流  $I_{lp}$ ）下での実動状態の発振周波数  $f_{cco}$  と希望とする周波数とのずれを補正できる分であればよいことになる。その結果、ある希望周波数に適合させた 1 つの初期電流  $I_{ini}$  としておき、複数種類の希望周波数への対応をゲイン特性情報取得部 107A からの周波数制御電流  $I_{osci}$  で対応する場合よりも、ゲイン特性情報取得部 107A が対処すべき補正電流量（＝周波数制御電流  $I_{osci}$ ）を少なくすることができる。

30

#### 【0083】

第 1 実施形態のループフィルタ部 106A は、電流制御発振部 101A に適合するように電流出力に対応した構成となっている。具体的には、ループフィルタ部 106A は、ループフィルタ容量  $C_p$  のコンデンサ（容量素子）164 と、電圧電流変換ゲイン  $G_m$  の電圧電流変換部（トランスコンダクタンス）166 とを有している。

#### 【0084】

チャージポンプ 104CP の出力は、コンデンサ 164 の一方の端子と電圧電流変換部 166 の入力とに共通に接続されている。コンデンサ 164 の他方の端子は基準電位である接地（GND）に接続されている。なお、位相同期部 100 を I C（半導体集積回路）で構成する場合、コンデンサ 164 は、その I C の外部で接続する。

40

#### 【0085】

ループフィルタ部 106A では、チャージポンプ 104CP から出力されたチャージポンプ電流  $I_{cp}$  に基づいてコンデンサ 164 の一方の端子（つまり電圧電流変換部 166 の入力）に電圧信号（チャージポンプ電圧  $V_{cp}$  と称する）が生成される。

#### 【0086】

コンデンサ 164 への充放電動作となるので、ループフィルタ部 106A は、位相比較部 103 からの比較結果信号  $V_{comp}$  中の所定のカットオフ周波数（ロールオフ周波数やポールともいう）以上の周波数成分を減衰させて、電流制御発振部 101A に供給される発振制御電流  $I_{cnt}$  を平滑化するように、少なくとも 1 つのカットオフ周波数を呈する低域通過フィルタとして機能する。

50

## 【0087】

なお、第3実施形態と同様に、コンデンサ164だけでなくループフィルタ抵抗Rpの抵抗素子162を直列に接続することで、低域通過フィルタとしての機能を高めるようにしてもよい。第2実施形態とは異なり、チャージポンプ部104として1つのチャージポンプ104CPを備える構成を探る場合、通常は、この抵抗素子162を備えた構成を採用する。

## 【0088】

電圧電流変換部166は、チャージポンプ104CPから出力されたチャージポンプ電流Icpに基づいてコンデンサ164の一方の端子(つまり電圧電流変換部166の入力)に生成されるチャージポンプ電圧Vcpを電圧電流変換ゲインGmに従って電流信号(ループフィルタ出力電流Ilpと称する)に変換する。

10

## 【0089】

なお、抵抗素子162とコンデンサ164との直列接続にするときには、その抵抗素子162の効果によって、チャージポンプ部104からループフィルタ部106Aまでの全体の電圧電流変換ゲインは、 $Gm(Rp + 1/sC)$ (sはjw)になる。

## 【0090】

第1実施形態のゲイン特性情報取得部107Aは、電流制御発振部101Aから出力された出力発振信号Voutの発振周波数fccoを2種類の判定基準周波数f1, f2と比較する周波数比較部170と、周波数比較部170における第1の判定基準周波数f1との周波数比較結果fcompをNビットのデジタルデータD(f1)として保持する第1の周波数比較結果保持部172\_1と、周波数比較部170における第2の判定基準周波数f2との周波数比較結果fcompをNビットのデジタルデータD(f2)として保持する第2の周波数比較結果保持部172\_2と、周波数比較結果保持部172\_1, 172\_2のそれぞれに保持された各Nビットの周波数比較結果fcompをアナログ信号に変換するDA変換部(DAC; Digital to Analog Converter)174としてのDA変換部174A\_1, 174A\_2とを備える。

20

## 【0091】

周波数比較部170には、電流制御発振部101Aから出力発振信号Voutが信号入力端子170\_1に供給され、また、判定基準周波数f1, f2をそれぞれ指定する情報が判定基準周波数設定端子170\_2, 170\_3に供給され、周波数比較結果fcompを判定結果出力端子170\_4から出力する。

30

## 【0092】

周波数比較部170は、目標周波数としての判定基準周波数f1, f2のそれぞれについて、電流制御発振部101Aから出力された出力発振信号Voutの発振周波数fccoと判定基準周波数f1, f2との大小を比較し、その周波数比較結果fcompを周波数比較結果保持部172\_1, 172\_2に渡す。

40

## 【0093】

ここで、判定基準周波数f1, f2をそれぞれ指定する情報としては、判定基準周波数f1, f2をそれぞれ直接に指定する情報であってもよいし、基準信号との関係における分周比M1, M2など、実質的に判定基準周波数f1, f2をそれぞれ指定することができるようとする情報であってもよい。詳細は後述するが、本実施形態の周波数比較部170では後者を採用する。

## 【0094】

また、詳細は後述するが、周波数比較結果保持部172\_2には、判定基準周波数f1と判定基準周波数f2との差の周波数に対応したNビットのデジタルデータが保持される。判定基準周波数f1と判定基準周波数f2との差の周波数に対応した値であるから、この周波数比較結果保持部172\_2が保持するNビットのデジタルデータは、電流制御発振部101Aの入力電流 - 発振周波数変換ゲインKccoを反映したものとなる。

## 【0095】

また、第1実施形態のDA変換部174A\_1, 174A\_2としては、電流制御発振部1

50

0 1 A の周波数制御入力端子 1 0 1 A in に供給する発振制御信号 CN が発振制御電流 I cnt であることに最適化するように、電流出力型のものを使用する。

#### 【 0 0 9 6 】

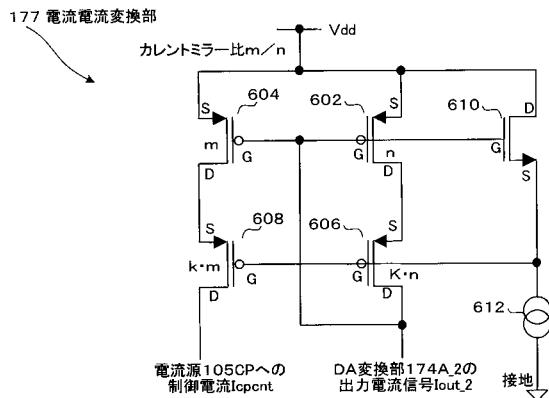

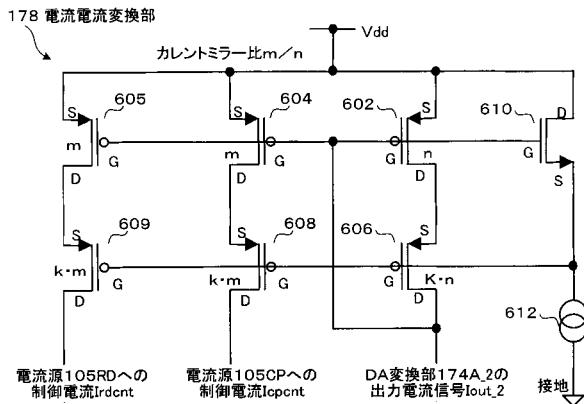

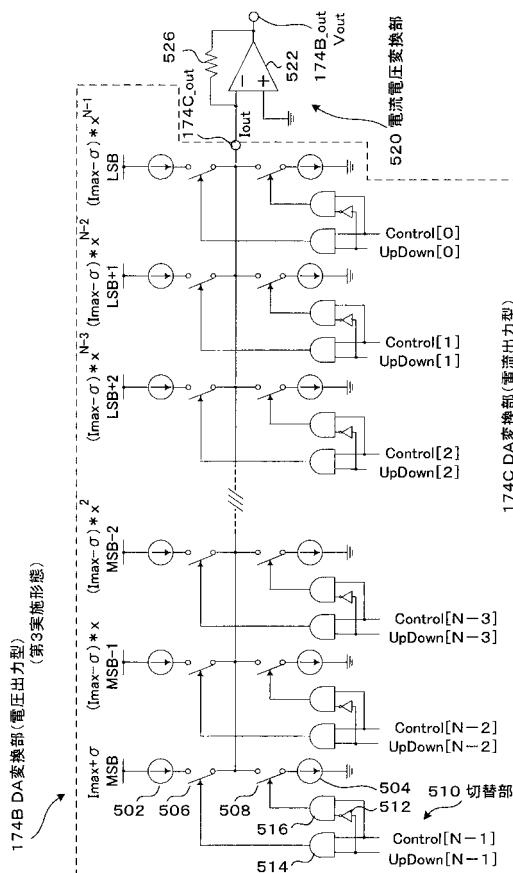

また、第 1 実施形態のゲイン特性情報取得部 1 0 7 A は、入力端子 1 7 5 \_1 に取り込んだ第 2 の DA 变換部 1 7 4 A \_2 の出力電流信号 I out \_2 の経路を切り替える経路選択スイッチ 1 7 5 と、第 1 の DA 变換部 1 7 4 A \_1 の出力電流信号 I out \_1 と経路選択スイッチ 1 7 5 の一方の出力端子 1 7 5 \_2 を介しての第 2 の DA 变換部 1 7 4 A \_2 の出力電流信号 I out \_2 とを加算する電流加算部 1 7 6 A と、経路選択スイッチ 1 7 5 の他方の出力端子 1 7 5 \_3 を介しての第 2 の DA 变換部 1 7 4 A \_2 の出力電流信号 I out \_2 を K 倍（後述するが K はカレントミラー比）に増幅する電流電流变換部 1 7 7 とを備えている。 10

#### 【 0 0 9 7 】

DA 变換部 1 7 4 A \_1 , 1 7 4 A \_2 は、判定基準周波数 f 1 , f 2 のそれぞれについて、周波数比較結果保持部 1 7 2 \_1 , 1 7 2 \_2 に記憶されているビット別の周波数比較結果に基づいて、ビット順に周波数制御信号の一例である出力電流信号 I out \_1 , I out \_2 を順次生成していく。ビット順の途中段階では、発振周波数 f cco を判定基準周波数 f 1 , f 2 にさせることはできていないが、最終的に得られる出力電流信号 I out \_1 , I out \_2 では、ほぼ発振周波数 f cco を判定基準周波数 f 1 , f 2 に一致させる状態になっている。

#### 【 0 0 9 8 】

電流加算部 1 7 6 A は、判定基準周波数 f 1 についての DA 变換部 1 7 4 A \_1 から出力される出力電流信号 I out \_1 と判定基準周波数 f 2 についての DA 变換部 1 7 4 A \_2 から出力される出力電流信号 I out \_2 とを加算して最終的な周波数制御電流 I osci ( 周波数制御信号 ) として発振制御信号生成部の一例である電流加算部 1 0 8 A に供給する。 20

#### 【 0 0 9 9 】

周波数比較結果保持部 1 7 2 \_1 および DA 变換部 1 7 4 A \_1 は、第 1 の目標周波数である判定基準周波数 f 1 の系統であり、周波数比較部 1 7 0 および電流加算部 1 7 6 A とともに、電流制御発振部 1 0 1 A から出力された出力発振信号 V out の発振周波数 f cco が判定基準周波数 f 1 ( 第 1 の目標周波数 ) となるようにするために必要となる規定信号 I n との差分である出力電流信号 I out \_1 を判定基準周波数 f 1 用の第 1 の周波数制御信号として取得する第 1 の周波数制御信号取得部を構成する。

#### 【 0 1 0 0 】

周波数比較結果保持部 1 7 2 \_2 および DA 变換部 1 7 4 A \_2 は、第 2 の目標周波数である判定基準周波数 f 2 の系統であり、周波数比較部 1 7 0 および電流加算部 1 7 6 A とともに、電流制御発振部 1 0 1 A から出力された出力発振信号 V out の発振周波数 f cco が判定基準周波数 f 2 ( 第 2 の目標周波数 ) となるようにするために必要となる規定信号 I n を出力電流信号 I out \_1 ( 第 1 の周波数制御信号 ) で補正した信号との差分である出力電流信号 I out \_2 を判定基準周波数 f 2 用の第 2 の周波数制御信号として取得する第 2 の周波数制御信号取得部を構成する。 30

#### 【 0 1 0 1 】

経路選択スイッチ 1 7 5 は、判定基準周波数 f 2 についての DA 变換部 1 7 4 A \_2 から出力された出力電流信号 I out \_2 を、補正情報取得時には電流加算部 1 7 6 A に供給し、通常の位相同期動作時には駆動部 1 0 4 Z の一例であるチャージポンプ部 1 0 4 側に供給されるように切り替える。 40

#### 【 0 1 0 2 】

ここで、「チャージポンプ部 1 0 4 側に供給」するに当たっては、図示のように、電流電流变換部 1 7 7 を介して制御電流 I cpcnt に変換してから供給するようにしてもよいし、後述する变形例のように、DA 变換部 1 7 4 A \_2 の構成を工夫することで、電流電流变換部 1 7 7 を介すことなく、出力電流信号 I out \_2 を制御電流 I cpcnt として直接に供給するようにすることもできる。

#### 【 0 1 0 3 】

電流加算部 1 7 6 A は、出力電流信号 I out \_1 と出力電流信号 I out \_2 との加算結果 (

50

$I_{out}$ )を周波数制御電流 $I_{osci}$ として電流加算部108Aに供給する。また、電流電流変換部177は、第2のDA変換部174A\_2の出力電流信号 $I_{out\_2}$ をK倍にした電流を制御電流 $I_{cpcnt}$ として、電流値可変型の電流源105CPの制御入力端子105CPaに供給する。

#### 【0104】

ここで、周波数比較部170は、出力発振信号 $V_{out}$ の発振周波数 $f_{cco}$ と判定基準周波数 $f_1, f_2$ の大小を比較して、その周波数比較結果 $f_{comp}$ をデジタルデータ0, 1の何れかで出力する。たとえば、発振周波数 $f_{cco}$ が判定基準周波数 $f_1, f_2$ よりも高ければ“1”を出力し、発振周波数 $f_{cco}$ が判定基準周波数 $f_1, f_2$ よりも低ければ“0”を出力する。よって、周波数比較部170にて出力発振信号 $V_{out}$ の発振周波数 $f_{cco}$ と判定基準周波数 $f_1, f_2$ の大小を比較するだけでは、比較結果としてはNビットのデジタルデータは得られない。10

#### 【0105】

しかしながら、詳細は後述するが、本実施形態では、出力発振信号 $V_{out}$ の発振周波数 $f_{cco}$ が判定基準周波数 $f_1, f_2$ に近づくように周波数比較部170での周波数比較結果 $f_{comp}$ を反映させた周波数制御電流 $I_{osci}$ を電流制御発振部101Aに供給して、再度(最終的にはN回)、同じようにして、周波数比較部170にて、出力発振信号 $V_{out}$ の発振周波数 $f_{cco}$ と判定基準周波数 $f_1, f_2$ の大小を比較する周波数2分探索法を採用する。その結果、N回の繰返しの都度、比較結果の重付けが小さくなるものと考えることができる。20

#### 【0106】

そこで、周波数比較結果保持部172\_1, 172\_2では、周波数比較部170におけるN回の比較処理に連動して、最初の周波数比較結果 $f_{comp}$ をNビットの上位ビットに記憶し、次回以降は、順次下位ビットに記憶するようとする。つまり、周波数比較結果保持部172\_1, 172\_2は、判定基準周波数 $f_1, f_2$ のそれぞれについて、周波数比較部170による周波数比較結果 $f_{comp}$ を順次ビットの重付け順にビット別に記憶していく。

#### 【0107】

これにより、周波数比較結果保持部172\_1, 172\_2には、最終的に、Nビットのデジタルデータが記憶される。N回の探索によって、周波数比較結果保持部172\_1, 172\_2には、出力発振信号 $V_{out}$ の発振周波数 $f_{cco}$ を判定基準周波数 $f_1, f_2$ に順次近づけていくことのできる出力電流信号 $I_{out\_1}, I_{out\_2}$ を示すNビットのデジタルデータが順に保持されていくことになる。30

#### 【0108】

電流加算部108Aは、規定電流源109Aから供給される所望とする出力発振信号 $V_{out}$ の発振周波数 $f_{cco}$ に適合させた初期電流 $I_{ini}$ と、電圧電流変換部166から出力されたループフィルタ出力電流 $I_{lp}$ と、ゲイン特性情報取得部107Aの電流加算部176Aからの周波数制御電流 $I_{osci}$ とを加算して、電流制御発振部101Aの周波数制御入力端子101Ainに供給する発振制御電流 $I_{cnt}$ とする。

#### 【0109】

電流電流変換部177は、ゲイン特性情報取得部107Aにおける補正処理によって取得され周波数比較結果保持部172\_2に保持されたデータに基づくDA変換部174A\_2から出力される出力電流信号 $I_{out\_2}$ をK倍(Kの設定手法については後述する)することで電流源105CPに供給する制御電流 $I_{cpcnt}$ を取得する信号変換部の一例である。40

#### 【0110】

このような構成の第1実施形態の位相同期部100においては、位相比較部103は、AD変換部54から出力されたデジタルデータ列Dinを、電流制御発振部101Aからの出力発振信号 $V_{out}$ (もしくは分周部102から出力された分周発振信号 $V_{out1}$ )と位相比較する。

#### 【0111】

位相誤差情報である位相比較部103の出力電圧 $V_{comp}$ が、チャージポンプ104CP、50

ループフィルタ部 106A、および電流加算部 108A を通じて発振制御電流  $I_{cnt}$  に変換され電流制御発振部 101A に供給されて、電流制御発振部 101A から出力される出力発振信号  $V_{out}$  の発振周波数 (= 発振周波数  $f_{cco}$ ) が制御されるとともに、出力発振信号  $V_{out}$  のデジタルデータ列  $D_{in}$  に位相がロックされる。この出力発振信号  $V_{out}$  は、たとえば、A/D 変換部 54 の A/D クロック  $CK_{ad}$  として利用される。

#### 【0112】

<発振部の構成例>

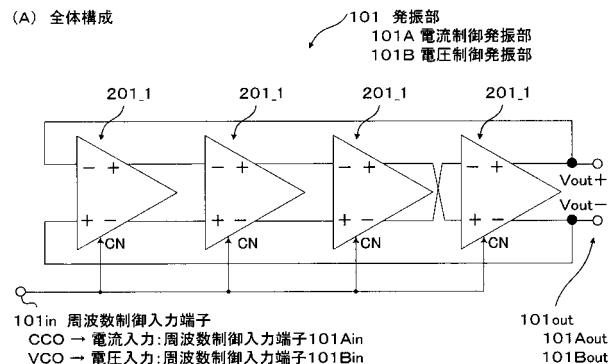

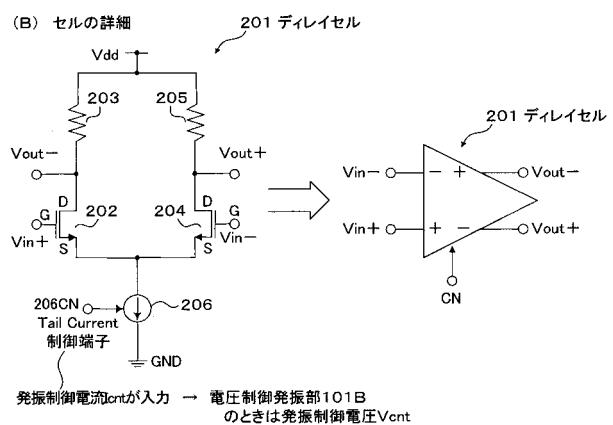

図 5 は、位相同期部 100 で使用する発振部の一構成例を示す図である。なお、回路構成的には、第 1 実施形態の電流制御発振部 101A の一構成例も、後述する第 3 実施形態の位相同期部 100 にて使用する電圧制御発振部 101B の一構成例も、同じように示すことができる。ここでは、電流制御発振部 101A と電圧制御発振部 101B とを纏めて説明する。

10

#### 【0113】

図 5 (A) に示すように、電流制御発振部 101A や電圧制御発振部 101B ( 繁めて発振部 101 と称する ) は、周波数制御入力端子 101in ( 101Ain, 101Bin ) と出力端子 101out ( 101Aout, 101Bout ) との間に、所定数 ( 本例では 4 段で示す ) のディレイセル ( ディレイステージとも称される ) 201 を備えている。

20

#### 【0114】

発振部 101 は、全体として差動リング発振器を構成するように、接続としては負帰還となる。動作時は、内部 R/C による位相ずれで正帰還となる。たとえば、各ディレイセル 201 は縦続配置され、さらに最終段のディレイセル 201\_4 の出力信号を、初段のディレイセル 201\_1 の入力に戻す。

20

#### 【0115】

本例では、1 段目のディレイセル 201\_1 の非反転出力 + を 2 段目のディレイセル 201\_2 の反転入力 - に接続し、かつ 1 段目のディレイセル 201\_1 の反転出力 - を 2 段目のディレイセル 201\_2 の非反転入力 + に接続する。また、2 段目のディレイセル 201\_2 の非反転出力 + を 3 段目のディレイセル 201\_3 の反転入力 - に接続し、かつ 2 段目のディレイセル 201\_2 の反転出力 - を 3 段目のディレイセル 201\_3 の非反転入力 + に接続する。

30

#### 【0116】

これに対して、3 段目のディレイセル 201\_3 の非反転出力 + は 4 段目のディレイセル 201\_4 の非反転入力 + に接続し、かつ 3 段目のディレイセル 201\_3 の反転出力 - は 4 段目のディレイセル 201\_4 の反転入力 - に接続する。このため、全体として正帰還を構成するように、4 段目のディレイセル 201\_4 の非反転出力 + は 1 段目のディレイセル 201\_1 の反転入力 - に接続し、かつ 4 段目のディレイセル 201\_4 の反転出力 - は 1 段目のディレイセル 201\_1 の非反転入力 + に接続する。

30

#### 【0117】

発振部 101 の 2 つの出力端子 101out ( 4 段目のディレイセル 201 の非反転出力 + および反転出力 - ) のうち何れか一方が、電流制御発振部 101A の出力端子 101Aout や電圧制御発振部 101B の出力端子 101Bout として使用される。

40

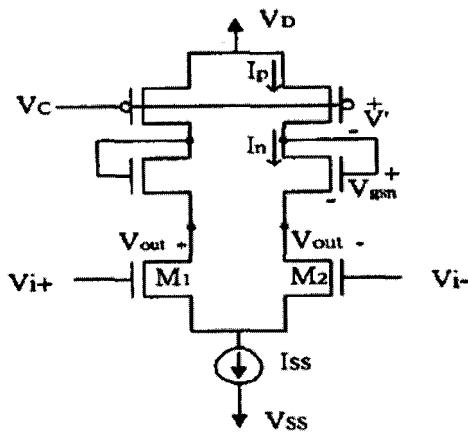

#### 【0118】

図 5 (B) に示すように、各ディレイセル 201 は、2 つのトランジスタ ( ここでは電界効果トランジスタ ) 202, 204 を使用した差動回路で構成されている。具体的には、一方のトランジスタ 202 のゲート G を非反転入力 ( $V_{in+}$ ) とし、そのドレイン D を抵抗素子 203 を介して電源  $V_{dd}$  に接続し、そのドレイン D を反転出力 ( $V_{out-}$ ) とする。また、他方のトランジスタ 204 のゲート G を反転入力 ( $V_{in-}$ ) とし、そのドレイン D を抵抗素子 205 を介して電源  $V_{dd}$  に接続し、そのドレイン D を非反転出力 ( $V_{out+}$ ) とする。また、各トランジスタ 202, 204 のソース S を共通にして、電流値可変型の電流源 206 を介して基準電位 ( 本例では接地電位 GND ) に接続する。

50

#### 【0119】

電流値可変型の電流源 206 は、制御入力端子 206CN に供給される発信制御信号 CN をカレントミラー形式（カレントミラー比は 1 : 1 でよい）で受けてトランジスタ 202, 204 にバイアス電流を供給するようになっている。

#### 【0120】

各ディレイセル 201 の各制御入力端子 206CN は、共通に周波数制御入力端子 101in に接続される。周波数制御入力端子 101in を介して各制御入力端子 206CN に供給される発信制御信号 CN は、電流制御発振部 101A のときは発振制御電流  $I_{cnt}$  であり電圧制御発振部 101B のときには、発振制御電圧  $V_{cnt}$  である。

#### 【0121】

<位相同期部のループ特性；第1実施形態>

ここで、第1実施形態の位相同期部 100 の動作の解析には、いわゆるチャージポンプ PLL の解析として一般的な、線形化した閉ループ伝達関数を用いることができる。

#### 【0122】

第1実施形態の位相同期部 100 の場合、チャージポンプ 104CP のチャージポンプ電流  $I_{cp}$ 、電流制御発振部 101A の入力電流 - 発振周波数変換ゲイン  $K_{cco}$ 、抵抗素子 162 のループフィルタ抵抗  $R_p$ 、コンデンサ 164 のループフィルタ容量  $C_p$ 、分周部 102 の分周比  $\alpha$  のとき、その帯域（自然角周波数） $\omega_n$  およびダンピングファクタ  $\zeta$  は、式(2-1)および式(2-2)のように表すことができる。なお、式(1)との比較から、式(2-3)および式(2-4)に示す関係があることが分かる。また、式(2-1)および式(2-2)から、式(2-5)を導くことができる。

#### 【0123】

#### 【数2】

$$\left. \begin{aligned} \omega_n &= \sqrt{\frac{I_{cp} \cdot K_{cco}}{C_p \cdot \alpha}} \quad \cdots (2-1) \\ \zeta &= \frac{C_p \cdot R_p}{2} \quad \omega_n \quad \cdots (2-2) \\ K_{lp} &= 1 \quad \cdots (2-3) \\ F_{lp} &= R_p \quad \cdots (2-4) \\ \omega_n, \zeta &\propto \sqrt{I_{cp} \cdot K_{cco}} \quad \cdots (2-5) \end{aligned} \right\} (2)$$

#### 【0124】

ここで、たとえば、位相同期部 100 を光ディスク装置 1 に適用する場合において、式(2-1)に基づき帯域  $\omega_n$  を、ブルーレイディスクなどの次世代 DVD、通常の DVD, CD の 3 種類の光ディスク PD の規格で決められている値に設定するには、位相同期部 100 を I C としたときには、その I C 外部で抵抗素子 162 やコンデンサ 164 が接続され、そのループフィルタ抵抗  $R_p$  やループフィルタ容量  $C_p$  は固定値であるため、チャージポンプ電流  $I_{cp}$  や分周比  $\alpha$  あるいは入力電流 - 発振周波数変換ゲイン  $K_{cco}$  を調整しなければならない。なお、第1実施形態では、帯域  $\omega_n$  を変化させると式(2-2)から分かるように、帯域  $\omega_n$  に比例して、ダンピングファクタ  $\zeta$  も変化してしまう。

#### 【0125】

しかしながら、チャージポンプ電流  $I_{cp}$  や分周比  $\alpha$  や入力電流 - 発振周波数変換ゲイン  $K_{cco}$  を調整することで、数多くの光ディスク PD に適合するように帯域  $\omega_n$  の設定を、設計で実現することができたとしても、実際に I C が製造されると、チャージポンプ 100

10

20

30

40

50

4 CPのチャージポンプ電流  $I_{cp}$  や電圧電流変換部 166 の電圧電流変換ゲイン  $G_m$  や電流制御発振部 101A の入力電流 - 発振周波数変換ゲイン  $K_{cco}$  など、帯域  $n$  を決めるパラメータが、設計値からばらつくため、所望の値に帯域  $n$  を設定することが困難となることが起こり得る。さらに、通常、様々な場所で使われることを考えると、温度によってもこれらのパラメータは変動するため、帯域  $n$  はさらに設定値からずれてしまうことになる。

#### 【0126】

したがって、帯域  $n$  やダンピングファクタ  $\zeta$  が、製造ばらつきや温度特性の影響を受けないようにするには、チャージポンプ 104CP のチャージポンプ電流  $I_{cp}$  や電圧電流変換部 166 の電圧電流変換ゲイン  $G_m$  や電流制御発振部 101A の入力電流 - 発振周波数変換ゲイン  $K_{cco}$  などの製造ばらつきや温度特性を補償する必要が生じる。10

#### 【0127】

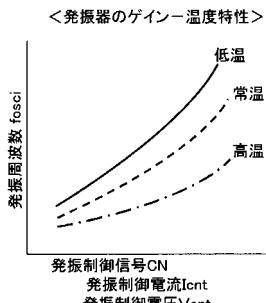

たとえば、製造ばらつきや温度特性を持つパラメータとして、発振部 101 の入力信号 - 発振周波数変換ゲイン  $K_{osci}$  に着目して見る。なお、入力信号 - 発振周波数変換ゲイン  $K_{osci}$  は、電流制御発振部 101A のときは入力電流 - 発振周波数変換ゲイン  $K_{cco}$  であり、電圧制御発振部 101B のときは入力電圧 - 発振周波数変換ゲイン  $K_{vco}$  である。

#### 【0128】

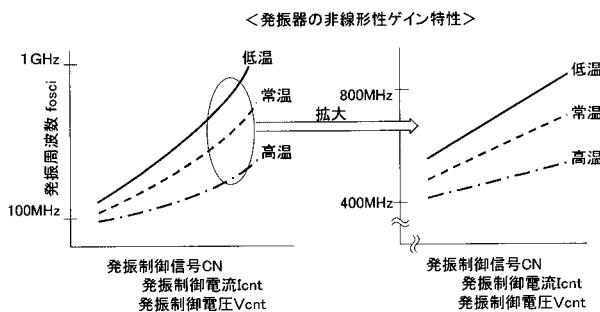

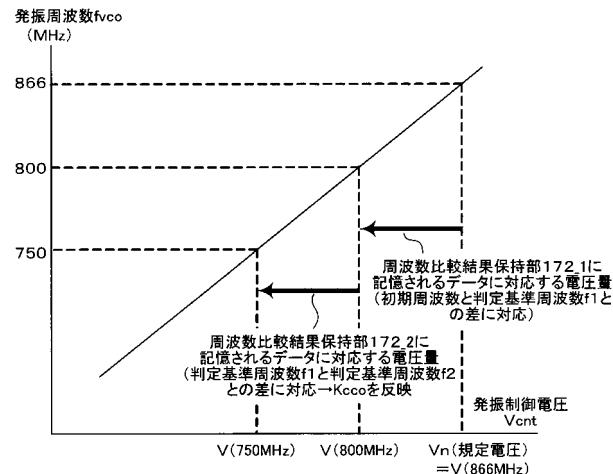

図 6 は、図 5 に示した発振部 101 の入力信号 - 発振周波数変換ゲイン  $K_{osci}$  の特性例を示す図である。

#### 【0129】

発振部 101 の周波数制御入力端子 101in に供給される発信制御信号 CN、すなわち発振制御電流  $I_{cnt}$  や発振制御電圧  $V_{cnt}$  を一定にしたとしても、ディレイセル 201 の差動対のトランスクンダクタンス  $G_m$  の値や負荷の値は製造ばらつきや温度で変化するため、入力信号 - 発振周波数変換ゲイン  $K_{osci}$ 、すなわち入力電流 - 発振周波数変換ゲイン  $K_{cco}$  や入力電圧 - 発振周波数変換ゲイン  $K_{vco}$  は、図 6 に示すように、たとえば設計値の半分から 2 倍に変動することもあり得る。これは、式(2)から、位相同期部 100 (PLL) の帯域  $n$  とダンピングファクタ  $\zeta$  が、 $1/\sqrt{2}$  から  $\sqrt{2}$  まで変動することを意味する。20

#### 【0130】

帯域  $n$  が設定値から大きくずれてしまうと、出力発振信号  $V_{out}$  の位相がデジタルデータ列  $D_{in}$  にロックするまでの期間、すなわちアライジション時間も設定値から変動するためシステム設計が難しくなり、さらに帯域  $n$  が低くずれてしまった場合はジッタが増加してしまう。

#### 【0131】

ここで、式(2-5)から理解されることは、帯域  $n$  やダンピングファクタ  $\zeta$  は、チャージポンプ電流  $I_{cp}$  と入力信号 - 発振周波数変換ゲイン  $K_{osci}$  の積 ( $= I_{cp} \cdot K_{osci}$ ) の (ルート ; 平方根) に比例することを意味するとともに、その積 ( $= I_{cp} \cdot K_{osci}$ ) が一定であれば、帯域  $n$  やダンピングファクタ  $\zeta$  は不变であるということである。30

#### 【0132】

この点に着目すると、位相同期部 100 を光ディスク装置 1 に適用する場合において、式(2-1)に基づきチャージポンプ電流  $I_{cp}$  や入力信号 - 発振周波数変換ゲイン  $K_{osci}$  を調整することで、帯域  $n$  やダンピングファクタ  $\zeta$  を各光ディスク PD の規格で決められている値に設定したとき、入力信号 - 発振周波数変換ゲイン  $K_{osci}$  に製造ばらつきや温度変化が生じたときには、式(2-5)に基づき、その変動分を相殺するように、チャージポンプ電流  $I_{cp}$  を調整して、 $I_{cp} \cdot K_{osci}$  が一定となるようにすれば、帯域  $n$  やダンピングファクタ  $\zeta$  が製造ばらつきや温度特性の影響を受けないようにすることができる。40

#### 【0133】

つまり、入力信号 - 発振周波数変換ゲイン  $K_{osci}$  の製造ばらつきや温度変化などに伴う変動分を相殺するようにチャージポンプゲイン  $I_{cp}$  を調整することで、入力信号 - 発振周波数変換ゲイン  $K_{osci}$  の製造ばらつきや温度特性の補正が可能で、帯域  $n$  およびダンピ50

ングファクタ を希望する値に一定にすることができる。

#### 【0134】

本実施形態のゲイン特性情報取得部 107A は、この点に直目してなされたものであり、入力信号 - 発振周波数変換ゲイン  $K_{osci}$  の変動分をチャージポンプ電流  $I_{cp}$  で相殺すべく、発振部 101 の入力信号 - 発振周波数変換ゲイン  $K_{osci}$  の実動状態の特性を測定し、その測定結果を元にして、チャージポンプ電流  $I_{cp}$  を調整することで、入力信号 - 発振周波数変換ゲイン  $K_{osci}$  の製造ばらつきや温度特性を補正する仕組みを探る。以下、ゲイン特性情報取得部 107A について、詳細に説明する。

#### 【0135】

<ゲイン特性情報取得部の動作の概要>

10

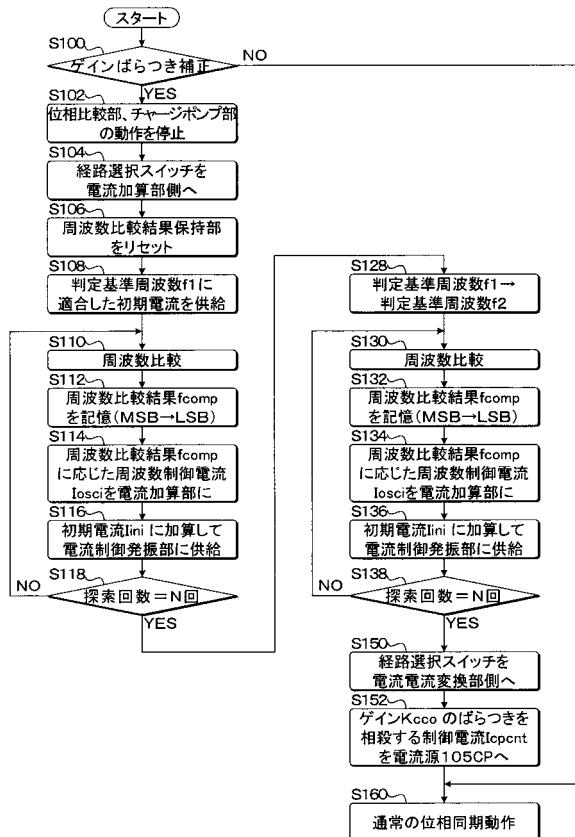

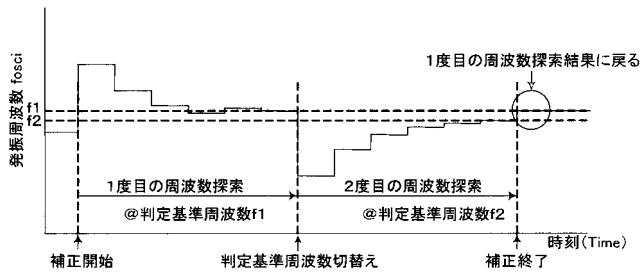

図 7 および図 8 は、ゲイン特性情報取得部 107A の動作の概要を説明する図である。ここで、図 7 は、ゲイン特性情報取得部 107A の動作手順の一例を示すフローチャートであり、図 8 は、ゲイン特性情報取得部 107A の動作のタイミングチャートである。なお、図 8 では、周波数 2 分探索の回数 (= N) を 6 回とする場合で示している。

#### 【0136】

本実施形態の位相同期部 100 では、デジタルデータ列  $D_{in}$  との位相同期動作をさせる前に、電流制御発振部 101A の入力電流 - 発振周波数変換ゲイン  $K_{cco}$  のばらつき補正を以下の手順に従って実行する。

#### 【0137】

この際には、ゲイン特性情報取得部 107A は、実動状態の入力電流 - 発振周波数変換ゲイン  $K_{cco}$  を測定し、その測定結果に基づいて、入力電流 - 発振周波数変換ゲイン  $K_{cc0}$  のばらつきを相殺するようにループフィルタ部 106A を駆動するチャージポンプ部 104 の駆動能力、具体的にはチャージポンプ電流  $I_{cp}$  の大きさを制御する点に特徴を有する。ここで、「入力電流 - 発振周波数変換ゲイン  $K_{cco}$  のばらつきを相殺するように」とは、入力電流 - 発振周波数変換ゲイン  $K_{cco}$  とチャージポンプ電流  $I_{cp}$  の積が一定となるようにすることを意味する。以下、先ず、処理手順の概要について説明する。

20

#### 【0138】

先ず、補正を始めるときには ( $S_{100} - YES$ )、位相比較部 103 およびチャージポンプ 104CP の動作を停止し ( $S_{102}$ )、経路選択スイッチ 175 を出力端子 175\_2 側 (電流加算部 176A 側) にして ( $S_{104}$ )、周波数比較結果保持部 172\_1, 172\_2 のデータをゼロにリセットし ( $S_{106}$ )、さらに、電流制御発振部 101A に最初の周波数 2 分探索における判定基準周波数  $f_1$  に適合した初期電流を発振制御電流  $I_{cnt}$  として与えて発振させるべく、電流加算部 108A に初期電流  $I_{ini}$  を供給する ( $S_{108}$ )。

30

#### 【0139】

周波数比較部 170 は、電流制御発振部 101A から出力された出力発振信号  $V_{out}$  の発振周波数  $f_{cco}$  を判定基準周波数  $f_1$  と比較する ( $S_{110}$ )。周波数比較結果保持部 172\_1 は、その周波数比較結果  $f_{comp}$  を  $N$  (本例では  $N = 6$ ) ビットのデジタルデータで記憶する ( $S_{112}$ )。なお、詳細は後述するが、本実施形態では 2 分探索法を採用するので、最初の周波数比較結果  $f_{comp}$  を  $N$  ビットの上位ビットに記憶し、次回以降は、順次下位ビット (最終的には最下位ビット LSB) に記憶するようとする。

40

#### 【0140】

DA 変換部 174A\_1 は、周波数比較結果保持部 172\_1 の  $N$  ビット目に保持されたデータに従って  $N$  ビット目を動作させ、その出力電流信号  $I_{out\_1}$  を電流加算部 176A に供給する。このときには、DA 変換部 174A\_2 からの出力電流信号  $I_{out\_2}$  はシンク電流もソース電流もなく、出力電流信号  $I_{out\_1}$  が、電流加算部 176A を介して周波数制御電流  $I_{osci}$  として電流加算部 108A に供給される ( $S_{114}$ )。

#### 【0141】

電流加算部 108A は、このときの周波数制御電流  $I_{osci}$  (= 出力電流信号  $I_{out\_1}$ ) と初期電流  $I_{ini}$  とを加算して発振制御電流  $I_{cnt}$  として電流制御発振部 101A に供給

50

する（S 116）。

【0142】

探索回数がN（本例ではN=6）回に達していなければ（S118-N0）、ステップS110に戻って、同様にして、周波数比較と、その結果の周波数比較結果保持部172\_1への保持を行なう。この際には、順次下位ビットに記憶するようとする。

【0143】

このようにして、電流制御発振部101Aの発振周波数 $f_{cco}$ を周波数比較部170で判定基準周波数 $f_1$ と比較し、その結果を周波数比較結果保持部172\_1に上位ビットから順に記憶して、その記憶した値でDA変換部174A\_1を上位ビットから順に動作させ、その出力電流信号 $I_{out\_1}$ を初期電流 $I_{ini}$ に加算していく。実際には、DA変換部174A\_1は、周波数比較結果保持部172\_1のビット別のデータ値（0/1）に応じて、ビット別にシンク動作とソース動作を行なうので、探索の都度、対応するビットに関して、初期電流 $I_{ini}$ への加算と減算とがデータ値に応じて実行される。10

【0144】

そして、探索回数がN回に達すると（S118-YES）、周波数比較結果保持部172\_1には、出力発振信号 $V_{out}$ の発振周波数 $f_{cco}$ が判定基準周波数 $f_1$ にほぼ一致するようなデータが保持されることになる。

【0145】

次に、位相同期部100は、経路選択スイッチ175を出力端子175\_2側にしたままで、判定基準周波数 $f_2$ に変更し（S128）、上記と同様に、出力発振信号 $V_{out}$ の発振周波数 $f_{cco}$ が判定基準周波数 $f_2$ にほぼ一致するようとする。20

【0146】

具体的には、周波数比較部170は、電流制御発振部101Aから出力された出力発振信号 $V_{out}$ の発振周波数 $f_{cco}$ を判定基準周波数 $f_2$ と比較する（S130）。周波数比較結果保持部172\_2は、その周波数比較結果 $f_{comp}$ をNビットのデジタルデータで記憶する（S132）。前述のように、最初の周波数比較結果 $f_{comp}$ をNビットの上位ビットに記憶する。

【0147】

DA変換部174A\_2は、周波数比較結果保持部172\_2のNビット目に保持されたデータに従ってNビット目を動作させ、その出力電流信号 $I_{out\_2}$ を電流加算部176Aに供給する。このときには、DA変換部174A\_1からの出力電流信号 $I_{out\_1}$ が存在するので、電流加算部176Aは、出力電流信号 $I_{out\_1}$ と出力電流信号 $I_{out\_2}$ とを加算して周波数制御電流 $I_{osci}$ として電流加算部108Aに供給する（S134）。30

【0148】

電流加算部108Aは、このときの周波数制御電流 $I_{osci}$ （=出力電流信号 $I_{out\_1}$ +出力電流信号 $I_{out\_2}$ ）と初期電流 $I_{ini}$ とを加算して発振制御電流 $I_{cnt}$ として電流制御発振部101Aに供給する（S136）。

【0149】

探索回数がN回に達していなければ（S138-N0）、ステップS130に戻って、同様にして、周波数比較と、その結果の周波数比較結果保持部172\_2への保持を行なう。この際には、順次下位ビットに記憶するようとする。40

【0150】

このようにして、電流制御発振部101Aの発振周波数 $f_{cco}$ を周波数比較部170で判定基準周波数 $f_2$ と比較し、その結果を周波数比較結果保持部172\_2に上位ビットから順に記憶して、その記憶した値でDA変換部174A\_2を上位ビットから順に動作させ、その出力電流信号 $I_{out\_2}$ を“出力電流信号 $I_{out\_1}$ +初期電流 $I_{ini}$ ”に加算していく。実際には、DA変換部174A\_2は、周波数比較結果保持部172\_2のビット別のデータ値（0/1）に応じて、ビット別にシンク動作とソース動作を行なうので、探索の都度、対応するビットに関して、“出力電流信号 $I_{out\_1}$ +初期電流 $I_{ini}$ ”への加算と減算とがデータ値に応じて実行される。50

## 【0151】

そして、探索回数がN回に達すると(S138-YES)、周波数比較結果保持部172\_2には、出力発振信号Voutの発振周波数fccoが判定基準周波数f2にほぼ一致するようなデータが保持されることになる。

## 【0152】

このようにして、判定基準周波数f1と判定基準周波数f2についての処理が完了すると(S138-YES)、経路選択スイッチ175は、出力端子175\_3側に切り替えることで、DA変換部174A\_2の出力経路を電流電流変換部177側に切り替える(150)。

## 【0153】

電流電流変換部177は、DA変換部174A\_2の出力電流信号Iout\_2をK倍してチャージポンプ104CPの電流源105CPの制御入力端子105CPaに制御電流IcpCntとして供給する(S152)。カレントミラー比が1:1のときには、制御電流IcpCnt=バイアス電流Icpbiasである。

10

## 【0154】

このようにして、一連の補正処理が完了すると、位相同期部100は、ゲイン特性情報取得部107Aでの入力電流-発振周波数変換ゲインKccoの測定結果に基づく大きさのチャージポンプ電流Icpを使用して、通常通り、位相同期動作を行なう(S160)。

## 【0155】

なお、上記の説明から分かるように、周波数比較結果保持部172\_2には、判定基準周波数f1から判定基準周波数f2に切り替えたときに、電流制御発振部101Aから出力される発振信号Voutの発振周波数fccoを、判定基準周波数f1から判定基準周波数f2にするために必要とされる差分が保持される。

20

## 【0156】

判定基準周波数f1と判定基準周波数f2との差分の周波数に対応した差分が保持されるのであるから、この周波数比較結果保持部172\_2が保持するNビットのデジタルデータは、電流制御発振部101Aの入力電流-発振周波数変換ゲインKccoを反映したものとなる。

## 【0157】

加えて、チャージポンプ104CPは、バイアス電流Icpbiasに対してK倍のチャージポンプ電流Icpを出力するが、チャージポンプ104CPのバイアス電流Icpbiasは、入力電流-発振周波数変換ゲインKccoを反映したデータに基づく出力電流信号Iout\_2をK倍したものに対応する。さらに、チャージポンプ電流Icpはバイアス電流Icpbiasに依存するので、電流電流変換部177によるK倍の設定を、入力電流-発振周波数変換ゲインKccoのばらつきを相殺するように適正化することで、入力電流-発振周波数変換ゲインKccoの測定結果に基づいて、補正処理の都度、Icp・Kccoを設計値に一致することができる(詳細は後述する)。

30

## 【0158】

その結果、このようにして、電流制御発振部101Aの入力電流-発振周波数変換ゲインKccoを反映したデータを保持することで、上記処理が完了した時点では、その時点での入力電流-発振周波数変換ゲインKccoの環境(部品ばらつきや環境温度)の影響を補正することができ、PLLの帯域nおよびダンピングファクタを、設計値に一致させることができる。環境変動がない限り、PLLの帯域nおよびダンピングファクタを、一定にすることができる。

40

## 【0159】

温度変化が生じたときには、前述と同様の補正処理を実行することで、入力電流-発振周波数変換ゲインKccoの環境(部品ばらつきや環境温度)の影響を再度補正することができ、PLLの帯域nおよびダンピングファクタを、設計値に一致させることができる。

## 【0160】

50

また、判定基準周波数  $f_1$  と判定基準周波数  $f_2$  についての処理が完了すると (S 1 3 8 - YES)、経路選択スイッチ 175 は、出力端子 175\_3 側に切り替えるので、電流加算部 176A には DA 変換部 174A\_2 からの出力電流信号  $I_{out\_2}$  がなく、図 8 に示すように、補正処理終了時点での電流制御発振部 101A から出力される出力発振信号  $V_{out}$  の発振周波数  $f_{cco}$  は判定基準周波数  $f_1$  に一致している。

#### 【0161】

したがって、この判定基準周波数  $f_1$  を、位相比較部 103 に入力されるデジタルデータ列  $D_{in}$  のデータレート、つまり AD 変換部 54 にて必要とされる AD クロック CKad の周波数に一致させれば、位相同期部 100 は、補正処理が終了すると同時に短時間で電流制御発振部 101A の出力発振信号  $V_{out}$  とデジタルデータ列  $D_{in}$  を同位相にすることができる。

10

#### 【0162】

これに対して、図 4 に示した比較例のデータリカバリ型の位相同期部 100A では、電圧電流変換部 166 (トランスクンダクタンス) の入力レンジが限られるため、周波数シンセサイザ部 180 を別に用意し、電流制御発振部 101A から出力される出力発振信号  $V_{out}$  の発振周波数  $f_{cco}$  がデジタルデータ列  $D_{in}$  のデータレートに一致するようにしてから、出力発振信号  $V_{out}$  の位相をデジタルデータ列  $D_{in}$  の位相にロックさせる。

#### 【0163】

図 3 に示した第 1 実施形態の位相同期部 100 と、図 4 に示した位相同期部 100A との比較から分かるように、第 1 実施形態の位相同期部 100 では、ゲイン特性情報取得部 107A を必要とするものの、周波数シンセサイザ部 180 が不要となる。

20

#### 【0164】

また、位相同期部 100 は、ゲイン特性情報取得部 107A での補正処理が終了した時点の情報を次回の補正処理が実行されるまで固定して (つまり DC 的に) 使用しながら位相同期動作を実行するので、AC 的に動作を継続しないため、低ノイズ、低ジッタを実現することができる。この点は、補正処理を継続的に掛けながら (つまり AC 的に動作させながら)、位相同期動作を実行するのと大きく異なる。

#### 【0165】

##### <周波数比較部の構成例と動作>

図 9 ~ 図 12 は、周波数比較部 170 の詳細を説明する図である。ここで、図 9 は、周波数比較部 170 の詳細な構成例を示す図である。図 10 は、周波数比較部 170 に使用されるプログラマブルカウンタ (Programmable Counter) の動作を説明するタイミングチャートである。図 11 は、計測時間とプログラマブルカウンタの出力の関係を説明する図である。図 12 は、プログラマブルカウンタにおける誤動作を説明する図である。

30

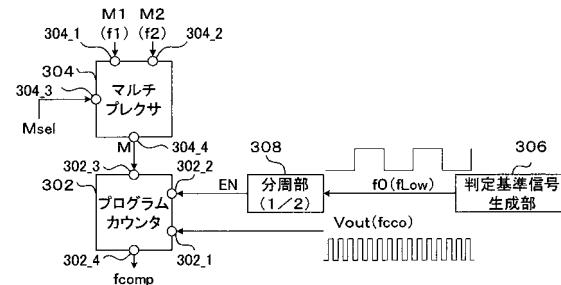

#### 【0166】

先ず、図 9 に示すように、周波数比較部 170 は、分周比を任意に変えることができるプログラムカウンタ 302 と、2 入力 - 1 出力のマルチプレクサ (Multiplexer) 304 と、周波数  $f_{Low}$  の判定基準信号  $f_0$  を生成する判定基準信号生成部 306 と、判定基準信号生成部 306 から供給される周波数  $f_{Low}$  の判定基準信号  $f_0$  を分周する分周部 308 とを有している。

40

#### 【0167】

ここで、判定基準信号  $f_0$  の周波数  $f_{Low}$  は、周波数 2 分探索における 1 つの周波数探索期間 (詳細は図 10 やセット信号生成部 410 の説明を参照) において、前回の探索結果に基づく DA 変換部 174A からの出力電流信号  $I_{out}$  を反映した発振周波数  $f_{cco}$  が安定となるようにできる値とする。これを満たさないと、次回の探索において、電流制御発振部 101A の発振周波数  $f_{cco}$  を周波数比較部 170 で判定基準周波数  $f_1$  と比較したときの判定結果が不適切になるからである。

#### 【0168】

分周部 308 は、入力された判定基準信号  $f_0$  の周波数  $f_{Low}$  を 1 / 2 に分周する。ここで、判定基準信号  $f_0$  としては、図 9 に示すように、電流制御発振部 101A から出力

50

される出力発振信号  $V_{out}$  の発振周波数  $f_{cco}$  よりも低速のクロック (Low Speed Clock) とする。

【0169】

マルチプレクサ304の一方の入力端子304\_1(170\_2に対応)には判定基準周波数  $f_1$  を指定する情報に対応する分周比  $M_1$  が入力され、他方の入力端子304\_2(170\_3に対応)には判定基準周波数  $f_2$  を指定する情報に対応する分周比  $M_2$  が入力される。マルチプレクサ304は、切替制御端子304\_3に入力される分周比切替信号  $M_{sel}$  (事実上、判定基準周波数切替信号に相当する) に従って、入力端子304\_1に入力される分周比  $M_1$  と入力端子304\_2に入力される分周比  $M_2$  の何れか一方を選択して出力端子304\_4から設定すべき分周比  $M$  として出力する。

10

【0170】

本実施形態では、第1の判定基準周波数  $f_1$  での周波数2分探索後に、その終了を示す信号(たとえばLレベルからHレベルに切り替る信号)が分周比切替信号  $M_{sel}$  として入力されることで、判定基準周波数が、判定基準周波数  $f_1$  から判定基準周波数  $f_2$  に切り替るようにする。

【0171】

プログラムカウンタ302は、電流制御発振部101Aから出力された発振周波数  $f_{cc0}$  の出力発振信号  $V_{out}$  がクロック入力端子302\_1(170\_1に相当)に供給され、また、分周部308によって判定基準周波数  $f_{low}$  を2分周した分周出力がイネーブル信号  $EN$  としてイネーブル端子302\_2に供給される。また、マルチプレクサ304の出力端子304\_4からの分周比  $M$  (分周比  $M_1$  または分周比  $M_2$  の何れか一方) が分周比設定端子302\_3に供給される。また、プログラムカウンタ302は、周波数比較結果  $f_{comp}$  を、出力端子302\_4(170\_4に相当)から出力する。

20

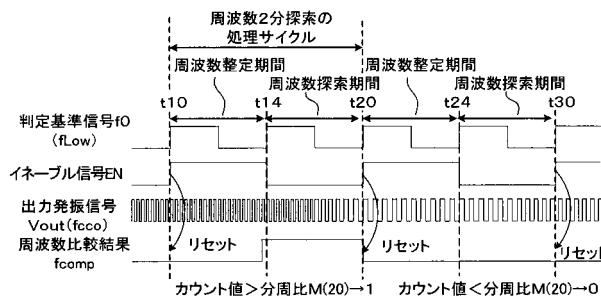

【0172】

図10では、分周比  $M = 20$  の場合で、プログラムカウンタ302は、出力発振信号  $V_{out}$  の立上りエッジをカウントする例で示している。ここで、プログラムカウンタ302は、図10に示すように、イネーブル信号  $EN$  が立ち上がると同時に、プログラムカウンタ302の内部状態はリセットされ、イネーブル信号  $EN$  が有効(本例ではHレベル)になると、電流制御発振部101Aから出力された出力発振信号  $V_{out}$  のエッジをカウントし始める( $t_{10}, t_{20}, t_{30}$ )。つまり、本実施形態の場合、イネーブル信号  $EN$  がHレベルの期間が、周波数2分探索における1つの周波数探索期間に該当する。

30

【0173】

そして、イネーブル信号  $EN$  が立ち下がると同時に( $t_{14}, t_{24}$ )、プログラムカウンタ302は、カウント動作を停止し、その時点のカウント結果を、次のイネーブル信号  $EN$  の立上りエッジまで保持し出力し続ける。そして、イネーブル信号  $EN$  がLレベルの期間(周波数整定期間と称する)内で発振周波数  $f_{cco}$  を変更し、次にイネーブル信号  $EN$  が立ち上ると同時に、プログラムカウンタ302の内部状態はリセットされ、次のカウントを始めることになる。

【0174】

なお、周波数比較を精度よく実行するには、周波数探索期間(イネーブル信号  $EN$  がHレベルのカウント期間)では、出力発振信号  $V_{out}$  の発振周波数  $f_{cco}$  が安定状態にあることが必要である。このことは、カウントを開始するイネーブル信号  $EN$  が立ち上るとときは、つまりイネーブル信号  $EN$  がLレベルの周波数整定期間内に、前回の周波数2分探索結果を反映した発振制御電流  $I_{cnt}$  に基づく出力発振信号  $V_{out}$  の発振周波数  $f_{cco}$  が安定状態に達していることが必要であることを意味する。

40

【0175】

本例で言えば、 $t_{10}$ 以前の前回の周波数比較結果  $f_{comp}$  に基づく発振周波数  $f_{cco}$  の制御によって、 $t_{10}$ 以前のイネーブル信号  $EN$  がLレベルの周波数整定期間内に発振周波数  $f_{cco}$  が安定に達していることが必要である。また、 $t_{10} \sim t_{14}$ にてのカウント動作による1回目の周波数探索の周波数比較結果  $f_{comp}$  に基づく発振周波数  $f_{cco}$  の制御に

50

よって、 $t_{20}$ 以前のイネーブル信号ENがLレベルの周波数整定期間内に発振周波数 $f_{cco}$ が安定に達していることが必要である。

#### 【0176】

なお、本例では、イネーブル信号ENを使って、周波数整定期間と周波数探索期間を合成した周波数2分探索の1つの処理サイクルを判定基準信号 $f_0$ の2クロック分にしているが、これは一例に過ぎない。

#### 【0177】

周波数2分探索の1つの処理サイクルを判定基準信号 $f_0$ の何クロック分にするかは、基本的には、電流制御発振部101Aの発振周波数 $f_{cco}$ が安定になる応答速度に応じて決めればよい。たとえば、判定基準信号 $f_0$ のLレベル期間を周波数整定期間とし、判定基準信号 $f_0$ のHレベル期間を周波数探索期間とすることで、周波数2分探索の1つの処理サイクルを判定基準信号 $f_0$ の1クロック分にすることもできるし、周波数整定期間と周波数探索期間とを均等にしつつ、全体の処理サイクルを3クロック分以上にすることもできる。

10

#### 【0178】

また、周波数整定期間と周波数探索期間とを均等にすることに限らず、不均等にしてもよい。この場合、周波数探索期間は一定にしつつ、発振周波数 $f_{cco}$ が安定になる応答速度に応じて周波数整定期間を決めるといい。たとえば、全体の処理サイクルは判定基準信号 $f_0$ の3クロック分としつつ、前半の2クロック分を周波数整定期間に割り当て、後半の1クロック分を周波数整定期間に割り当てるようにしてもよい。

20

#### 【0179】

ところで、このような動作をするプログラムカウンタ302の周波数判定結果を示す出力信号としては、次のようになる。すなわち、プログラムカウンタ302に入力されるイネーブル信号ENの幅は、判定基準信号 $f_0$ の周波数を $f_{Low}$ とすると $1/f_{Low}$ となる。電流制御発振部101Aから出力される出力発振信号 $V_{out}$ は発振周波数 $f_{cco}$ であるから、発振器周期 $1/f_{cco}$ ごとにエッジがプログラムカウンタ302に入力されるため、プログラムカウンタ302、イネーブル信号ENが有効(Hレベル)である期間(イネーブル信号幅と称する)にカウントされる値(カウント値)は、イネーブル信号幅 = 判定基準信号 $f_0$ の1周期分であるから、発振周波数 $f_{cco} = f_{osci}$ とすると、式(3-1)のように表される。

30

#### 【0180】

ここで、プログラムカウンタ302は、分周比Mが入力されていたとき、式(3-1)で示されるカウント値が、分周比Mよりも大きかった場合は“1:Hレベル”を(式(3-2))、分周比Mよりも小さかった場合は“0:Lレベル”を(式(3-3))、出力端子302\_4から出力する。なお、カウント値が分周比Mよりも大きくなる場合は、イネーブル信号ENが立ち下がる前(たとえば $t_{14}$ の前)に、プログラムカウンタ302の出力がHになる。

30

#### 【0181】

このことは、プログラムカウンタ302は、電流制御発振部101Aから出力される出力発振信号 $V_{out}$ の発振周波数 $f_{cco}$ (=発振周波数 $f_{osci}$ )の大小を判定することを意味し、 $M \cdot f_{Low}$ は判定基準周波数であることが分かる。したがって、分周比Mを分周比M1と分周比M2の何れかに切り替えることで、判定基準周波数を判定基準周波数 $f_1$ と判定基準周波数 $f_2$ の何れかに切り替えることができる。これによって、発振周波数 $f_{cco}$ が判定基準周波数 $f_1, f_2$ よりも高ければプログラムカウンタ302は“1:Hレベル”を周波数比較結果 $f_{comp}$ として出力し、発振周波数 $f_{cco}$ が判定基準周波数 $f_1, f_2$ よりも低ければプログラムカウンタ302は“0:Lレベル”を周波数比較結果 $f_{comp}$ として出力する。

40

#### 【0182】

## 【数3】

$$\text{カウント値} = \frac{\text{イネーブル信号幅}}{\text{発振器周期}} = \frac{1/f_{\text{Low}}}{1/f_{\text{osc}}_i} = \frac{f_{\text{osc}}_i}{f_{\text{Low}}} \dots (3-1)$$

$$\left. \begin{array}{l} \text{if } \left[ \frac{1/f_{\text{osc}}_i}{1/f_{\text{Low}}} > M \right] f_{\text{comp}} = "1" \rightarrow f_{\text{osc}}_i > M \cdot f_{\text{Low}} \dots (3-3) \\ \text{if } \left[ \frac{1/f_{\text{osc}}_i}{1/f_{\text{Low}}} < M \right] f_{\text{comp}} = "0" \rightarrow f_{\text{osc}}_i < M \cdot f_{\text{Low}} \dots (3-3) \end{array} \right\} (3)$$

## 【0183】

ここで、プログラムカウンタ302に対する分周比Mは、図9から分かるように、判定基準周波数f1に対応する分周比M1と判定基準周波数f2に対応する分周比M2を、マルチブレクサ304で切り替えて実行する。

## 【0184】

これは、前述の図7および図8にて説明したように、ゲイン特性情報取得部107Aは、発振周波数fccoを2種類の判定基準周波数f1, f2に一致させるために、マルチブレクサ304にて、判定基準周波数f1, f2を補正処理の中で切り替える必要があるからである。

## 【0185】

ところで、前述のように、プログラムカウンタ302は、図10に示したように、イネーブル信号ENが有効な計測期間（周波数探索時間）にカウントされる値が分周比Mより大きいか、小さいかを判断して結果を出力する。

## 【0186】

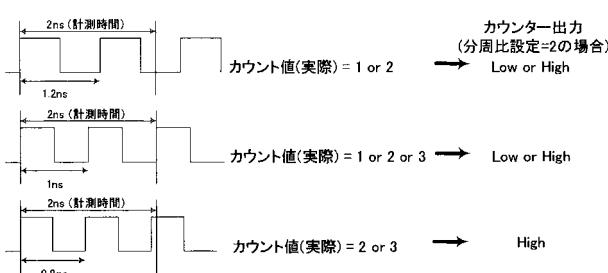

しかしながら、計測時間とプログラムカウンタ302の出力の関係を図11に示すように、たとえ、発振周波数fccoが安定に達していたとしても、イネーブル信号ENが立ち上がる時刻または立ち下る時刻に電流制御発振部101Aのエッジが重なった場合には、プログラムカウンタ302は、その判定を誤る可能性がある。

## 【0187】

たとえば、fLow = 5 MHzで電流制御発振部101Aの発振周波数fccoが800 MHz近傍である場合を考えると、プログラムカウンタ302は、図12に示すようなカウント値を取ることになる。ここで、図12(A)は、分周比M = 160にしたときのプログラムカウンタ302の判定ミス区間と判定基準周波数との関係を示し、図12(B)は、分周比M = 161にしたときのプログラムカウンタ302の判定ミス区間と判定基準周波数との関係を示す。

## 【0188】

具体的には、プログラムカウンタ302の判定基準周波数を800 MHzと設定する場合、fLow = 5 MHzであるので分周比M = 160とすると、図12(A)に示すように、発振周波数fccoが795 MHz, 795 MHz < fcco < 800 MHzのときにプログラムカウンタ302が160をカウントし、800 MHz以上であると間違った判定をする場合もあることが分かる。逆に、800 MHzのときは159をカウントしてしまい、800 MHzよりも低いと判定する場合もある。これは、プログラムカウンタ302の実際の判定基準周波数が795 MHzに移動したと考えることができる。

## 【0189】

また、分周比M = 161とすると、図12(B)に示すように、プログラムカウンタ302が間違った判定をする区間は800 MHz ~ 805 MHzに移動し、発振周波数fccoが800 MHzよりも小さいときに間違った判定をすることはなくなるため、同様に判定基準周波数が800 MHzであると考えることができる。

10

20

30

40

50

## 【0190】

よって、周波数比較部170のマルチプレクサ304にてプログラムカウンタ302に

対して分周比Mを設定をする場合には、判定基準周波数を閾値周波数f<sub>th</sub>(*reshold*)と

すると、式(4)のように分周比Mを設定する必要がある。

## 【0191】

## 【数4】

$$M = \frac{f_{th}}{f_{Low}} + 1 \quad \cdots (4)$$

10

## 【0192】

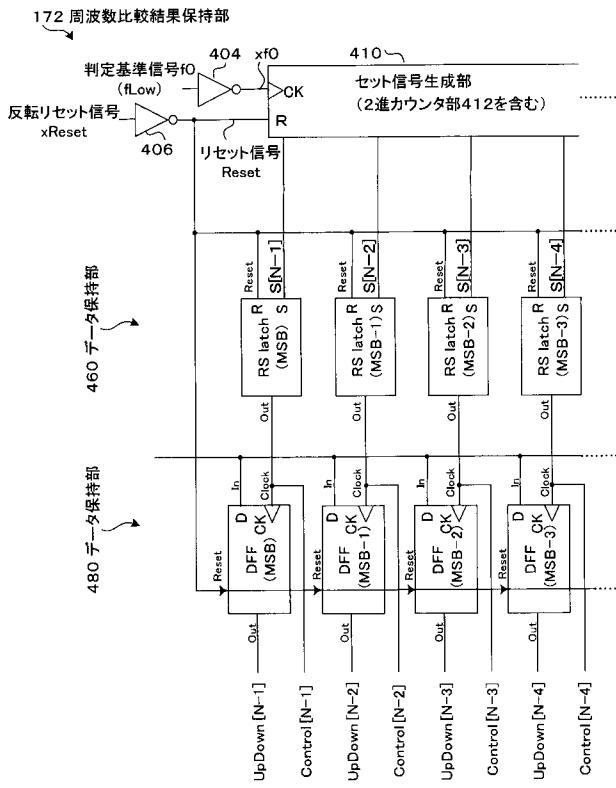

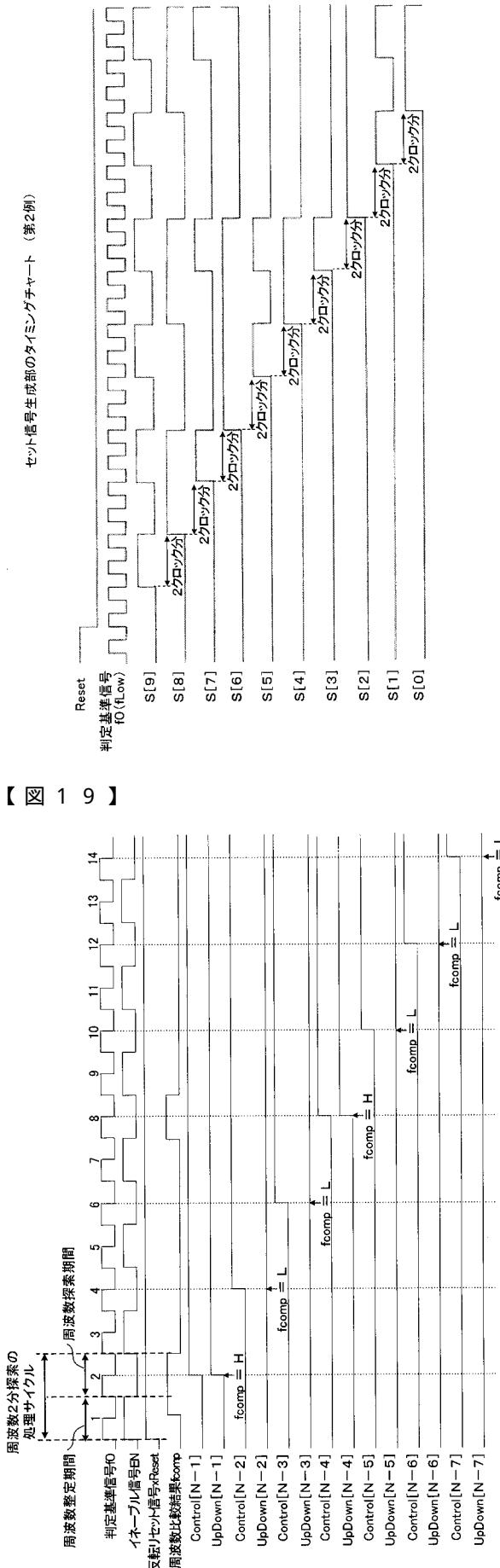

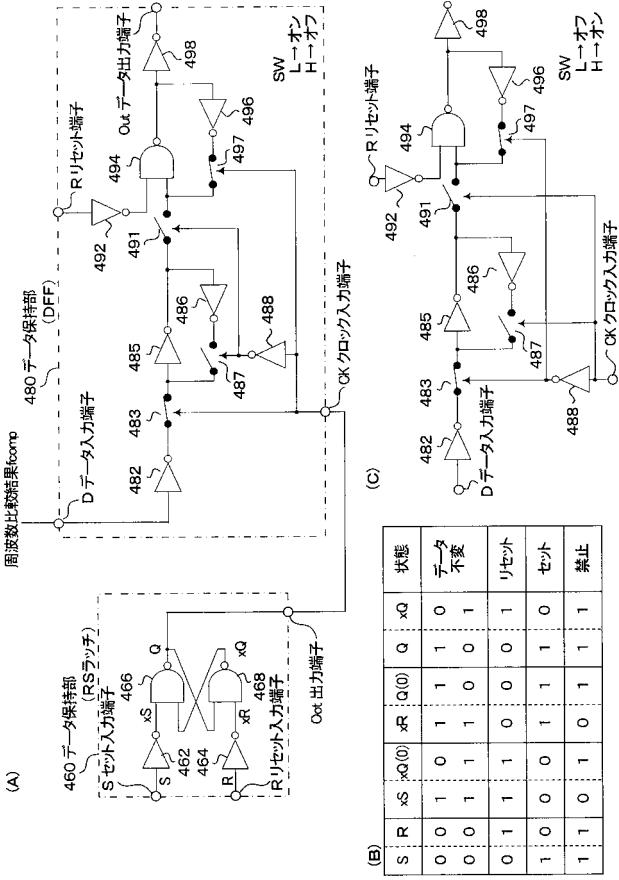

<比較結果保持部の構成例と動作>

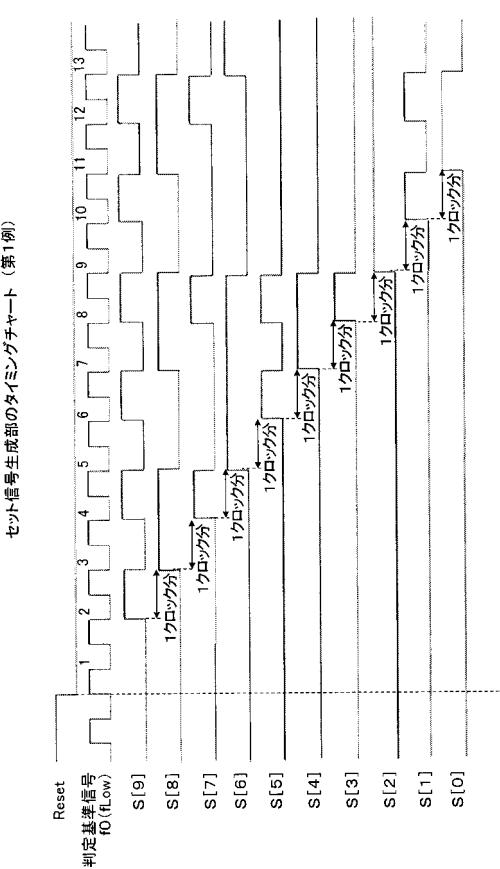

図13～図19は、周波数比較結果保持部172\_1, 172\_2(総て172で記す)

の構成例と動作を説明する図である。ここで、図13は、周波数比較結果保持部172の

詳細な構成例を示す図である。図14は、周波数比較結果保持部172を構成するセット

信号生成部410の詳細な構成例を示す図である。図15は、図14に示すセット信号生

成部410の詳細な構成例において使用されるD型のフリップフロップ(以下DFFとも

記す)の構成例を示す図である。

## 【0193】

図16は、周波数2分探索の処理サイクルを判定基準信号f<sub>0</sub>の1クロック分とする場

合におけるセット信号生成部410の動作を説明するタイミングチャート(N=10で例

示)である。図17は、周波数2分探索の処理サイクルを判定基準信号f<sub>0</sub>の2クロック

分とする場合における図14に示す構成のセット信号生成部410の動作を説明するタイ

ミングチャート(N=10で例示)である。

20

## 【0194】

図18は、周波数比較結果保持部172を構成するデータ保持部460, 480の1ビ

ット分の構成要素の詳細を示す図である。図19は、周波数2分探索の処理サイクルを判

定基準信号f<sub>0</sub>の2クロック分とする場合における周波数比較部170と周波数比較結果

保持部172の全体動作を説明するタイミングチャートである。

30

## 【0195】

図13に示すように、周波数比較結果保持部172は、インバータ404, 406と、

ビットの重付けの切替えタイミングを規定する信号の大元となるビット別のセット信号を

生成するセット信号生成部410とを備えている。セット信号生成部410は、入力され

たクロック信号をカウントする2進カウンタ部412を備えるとともに、2進カウンタ部

412のカウント出力を使って、ビット別のセット信号を順次生成するようになっている。

カウント出力を使ってビット別のセット信号を生成するに当たっては、ゲート回路の組

合せやシフトレジスタ構成や、その他の論理回路を用いる。

## 【0196】

また、周波数比較結果保持部172は、セット信号生成部410から出力されたセット

信号Sを取り込んで記憶するビット別に設けられた1段目のデータ保持部460と、1段

目のデータ保持部460の出力データをビットの重付けの切替えタイミングを規定するビ

ット切替信号として使用し、当該ビット切替信号のビットの重付けの切替えタイミングに

同期して、周波数比較部170からの周波数比較結果f<sub>comp</sub>を取り込み記憶するビット別

に設けられた2段目のデータ保持部480とを備えている。

40

## 【0197】

1段目のデータ保持部460から出力される出力データは、ビットの重付けの切替えタ

イミングを規定するビット切替信号として利用される。すなわち、第1例の周波数比較

結果保持部172の構成では、2進カウンタ部412およびゲート回路420を具備したセ

ット信号生成部410とデータ保持部460とによって、ビットの重付けの切替えタ

イミングを規定するビット別のビット切替信号を順次生成するビット切替信号生成部が構成さ

50

れる。データ保持部 460 は、セット信号生成部 410 から出力されたセット信号 S の最初の立上りエッジでセット信号 S を取り込み記憶し、その後のセット信号 S の立上りエッジを無視することで、ビット切替信号を順次生成する、パルス信号整形部の機能を持つ。

#### 【0198】

インバータ 404 には、図示を割愛した判定基準信号生成部から供給される周波数  $f_{Low}$  の判定基準信号  $f_0$  が入力され、これを論理反転した信号（反転判定基準信号  $\times f_0$  と称する）をセット信号生成部 410 に供給する。インバータ 406 には、図示を割愛した補正処理動作を制御する制御部から供給される外部信号としての反転リセット信号  $xReset$  が入力され、これを論理反転した信号（リセット信号  $Reset$  と称する）をセット信号生成部 410 やデータ保持部 460, 480 に供給する。なお、反転リセット信号  $xReset$  の L レベルから H レベルへの遷移は、判定基準信号  $f_0$  の立上りエッジに同期しているものとする。

10

#### 【0199】

データ保持部 460, 480 は、判定基準周波数ごとの N 回の周波数 2 分探索に対応するように、それぞれ N 個が併設されている。ここで、本実施形態の周波数比較結果保持部 172 においては、1 段目のデータ保持部 460 としては RS ラッチを使用し、2 段目のデータ保持部 480 としては D 型のフリップフロップ（DFF）を使用している。

#### 【0200】

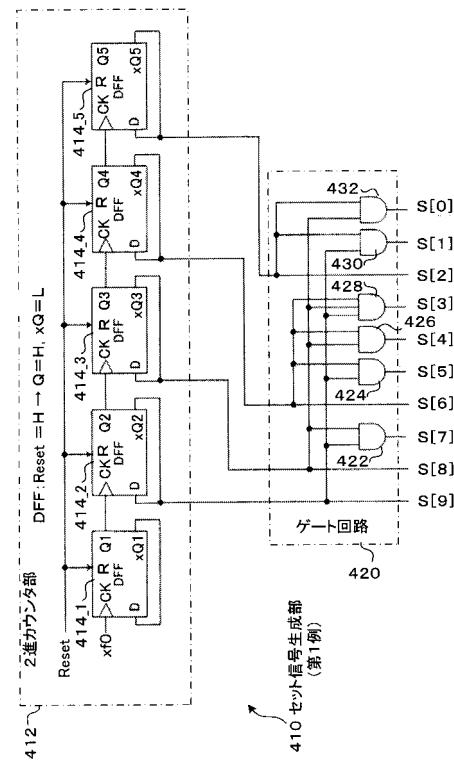

<セット信号生成部の詳細>

セット信号生成部 410 は、たとえば、図 14 にその構成例を示すように、2 進カウンタ部 412 と、2 進カウンタ部 412 のカウント出力を論理演算することで、ビット別のデータ保持部 460 に供給する各セット信号 S [N - #]（# は 1, 2, 3 … : 1 が MSB 側）を生成するゲート回路 420 とを有する。

20

#### 【0201】

2 進カウンタ部 412 は、図示のように、D 型のフリップフロップ（DFF）414 を縦続配置し、ダウンカウント動作をするように段間を接続している。DFF414 の縦続配置数は、ビット数 N に応じて決定するが、たとえば、N = 10 のときには、図示のように、5 段構成にする。

#### 【0202】

具体的には、先ず、各段の DFF414 は、反転出力端子  $\times Q$  とデータ入力端子 D とを直接に接続している。1 段目の DFF414 のクロック入力端子 CK には周波数  $f_{Low}$  の判定基準信号  $f_0$  をインバータ 404 で論理反転した反転判定基準信号  $\times f_0$  を入力する。2 段目以降は、前段の DFF414 の非反転出力端子 Q から出力されたカウント出力を後段の DFF414 のクロック入力端子 CK に供給するようとする。各 DFF414 は、クロック入力端子 CK の立上りエッジでデータ入力端子 D の状態を非反転出力端子 Q に出力し、データ入力端子 D の状態を論理反転したものを反転出力端子  $\times Q$  から出力する。この点は、一般的な DFF の場合と同様である。

30

#### 【0203】

各段の DFF414 のリセット端子 R には、反転リセット信号  $xReset$  がインバータ 406 を介してリセット信号  $Reset$  とされて入力される。各段の DFF414 は、リセット端子 R に入力されたリセット信号  $Reset$  が H レベルのときには、非反転出力端子 Q を H レベル、反転出力端子  $\times Q$  を L レベルにする（リセットする）。この点は、一般的な DFF の場合、リセット時に、非反転出力端子 Q を L レベル、反転出力端子  $\times Q$  を H レベルにするの異なる。

40

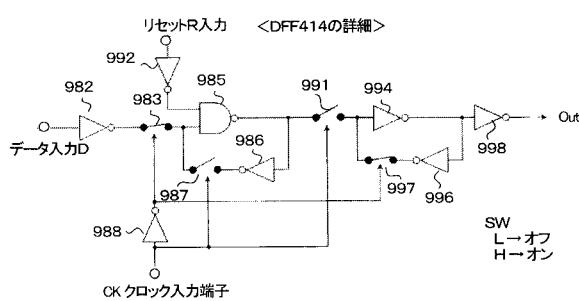

#### 【0204】

たとえば、各段の DFF414 は、図 15 にその詳細構成例を示すように、入力データ D を反転するインバータ 982 と、リセット信号を反転するインバータ 984 と、2 入力型の NAND ゲート 985 と、クロック信号 CK を反転するインバータ 988 と、オン / オフスイッチ（以下単にスイッチと称する）983, 987 とを備える。

#### 【0205】

50

インバータ984の出力はNANDゲート985の一方の入力に接続されている。NANDゲート985の他方の入力は、スイッチ983を介してインバータ982の出力に接続されるとともに、スイッチ987を介してインバータ986の出力に接続される。また、NANDゲート985の出力は、インバータ986の入力に接続される。

#### 【0206】

NANDゲート985のインバータ984側の入力がHレベルで、かつスイッチ987がオンした状態で、NANDゲート985とインバータ986によってメモリ回路(ラッチ)が構成されるようになっている。

#### 【0207】

また、各段のDFF414は、インバータ994, 996, 998と、オン/オフスイッチ991, 997とを備える。インバータ994の出力は、インバータ996, 998の各入力に接続され、インバータ996の出力はスイッチ997を介してインバータ994の入力に接続されている。インバータ998の出力は、非反転出力端子Outに接続される。スイッチ997がオンした状態でインバータ994, 996によってメモリ回路(ラッチ)が構成されるようになっている。

#### 【0208】

クロック入力端子CKは、直接にスイッチ987, 991の制御端子に接続されるとともに、インバータ988を介してスイッチ983, 997の制御端子に接続される。ここで、各スイッチ983, 987, 991, 997は、制御端子がLレベル(つまりクロック入力端子CKがLレベル)のときにオフし、制御端子がHレベル(つまりクロック入力端子CKがHレベル)のときにオンするタイプのスイッチである。

#### 【0209】

なお、各スイッチ983, 987, 991, 997を、制御端子がLレベル(つまりクロック入力端子CKがLレベル)のときにオンし、制御端子がHレベル(つまりクロック入力端子CKがHレベル)のときにオフするタイプのスイッチとしてもよい。この場合、図示を割愛するが、図15に示す構成に対して、クロック入力端子CKは、直接にスイッチ983, 997の制御端子に接続されるとともに、インバータ988を介してスイッチ987, 991の制御端子に接続されるように修正すればよい(後述する図18(A)に示す構成を参照)。

#### 【0210】

このような構成のDFF414においては、先ず、インバータ984へのリセット信号RがHレベルになると、インバータ984の出力(すなわちNANDゲート985の片方の入力)がLレベルとなることで、NANDゲート985のもう片方の入力に拘わらず、その出力がHレベルとなる。クロック信号CKがHとなることでスイッチ991がオンすると、インバータ994, 998を介することで、非反転出力端子OutがHレベルとなる。すなわち、データ出力がHレベルにリセットされる。

#### 【0211】

この後に、クロック入力端子CKがLレベルになると、スイッチ991はオフする。このため、リセットHレベルの供給が停止するが、インバータ984, 996では、リセットHレベルを内部に取り込んでいる。すなわち、スイッチ997がオンすることで、直前のリセットHレベルをインバータ994で反転しさらにインバータ996で反転したデータがスイッチ997を介してインバータ994まで伝達される。つまり、直前のリセットHレベルがインバータ994, 996を介して論理反転されて、元の論理状態で入力に戻される。その結果、直前のリセットHレベルがインバータ994, 996によって保持されることになる。

#### 【0212】

また、この後に、インバータ984へのリセット信号RがHレベルになると、インバータ984の出力(すなわちNANDゲート985の片方の入力)がHレベルとなることで、NANDゲート985の出力が、NANDゲート985のもう片方の入力を反映するようになる。

10

20

30

40

50

## 【0213】

たとえば、この時点ではクロック入力端子CKがLレベルにあると、入力側では、入力データDを内部に取り込んでいる。すなわち、スイッチ983がオンすることで、入力データDをインバータ982で反転したデータがスイッチ983を介してNANDゲート985のもう片方の入力まで伝達され、これがNANDゲート985で論理反転されてNANDゲート985の出力まで伝達されている。このとき、スイッチ991はオフしているので、前述と同様に、直前のリセットHレベルがインバータ994, 996によって保持され、非反転出力Outはリセットされた状態のままである。

## 【0214】

さらに、クロック入力端子CKがHレベルに切り替ると、スイッチ983, 997はオフし、スイッチ987, 991はオンする。これにより、インバータ984へのインバータ982およびスイッチ983を介した入力データDの供給が停止するが、スイッチ987がオンすることで、直前のインバータ984の出力（すなわち直前の入力データDの論理レベル）がインバータ986を介して論理反転されて入力に戻される。その結果、直前の入力データDの論理レベルがインバータ984, 986によって保持されることになる。

10

## 【0215】

また、スイッチ991がオンであるので、インバータ984の出力である直前の入力データDの論理レベルがNANDゲート985の片方の入力に供給される。その結果、直前の入力データDの論理レベルがNANDゲート985によって論理反転され、さらにインバータ998によって論理反転されることで、直前の入力データDの論理レベルが、そのまま非反転出力Outに現われる。

20

## 【0216】

この後に、クロック入力端子CKがLレベルに切り替ると、スイッチ983, 997はオンし、スイッチ987, 991はオフする。これにより、入力データDの論理レベルのNANDゲート985のもう片方の入力への供給が停止する。しかしながら、このときには、スイッチ987がオンすることで、インバータ986は、直前のNANDゲート985の出力状態を反転してNANDゲート985のもう片方の入力に供給するようになる。よって、NANDゲート985の出力は直前のNANDゲート985の出力状態を維持したままとなる。

30

## 【0217】

このとき、スイッチ991がオン、スイッチ997がオフとなっているので、さらにインバータ994, 998を介して、NANDゲート985の直前の出力状態が、そのまま非反転出力Outに現われる。よって、NANDゲート985, インバータ989で保持されたデータ入力の論理レベルが、そのまま非反転出力Outに現われる。

## 【0218】

この後に、クロック入力端子CKがLレベルに切り替ると、スイッチ991はオフし、スイッチ997はオフする。これにより、NANDゲート985の出力状態のインバータ994への供給が停止する。しかしながら、このときには、スイッチ997がオンすることで、インバータ996は、直前のインバータ994の出力状態を反転してインバータ994の入力に供給するようになる。よって、インバータ994の出力は直前のインバータ994の出力状態を維持したままとなる。よって、クロック入力端子CKがLレベルに切り替っても、NANDゲート985, インバータ989で保持された直前のデータ入力の論理レベルが、そのまま非反転出力Outに現われ続ける。

40

## 【0219】

よって、このような構成のDFF414では、クロック入力端子CKがLレベルからHレベルになるエッジに同期して、入力データDを取り込み、リセット端子Rへのリセット信号ResetがHレベルになるまで、そのデータを保持し続ける。

## 【0220】

ゲート回路420は、ANDゲート422, 424, 426, 428, 430, 432を有する。ANDゲート422, 424, 426, 430, 432は、2入力タイプであ

50

り、ANDゲート428は、3入力タイプである。

#### 【0221】

セット信号生成部410は、周波数比較結果保持部172に入力される周波数fLowの判定基準信号f0をカウントクロックとして、その判定基準信号f0の立下りエッジ(反転判定基準信号×f0の立上りエッジ)で2進カウンタ部412により2進カウント動作をし、そのカウント結果を受けて、後段の各データ保持部460の各セット入力端子Sに供給するセット信号S[N-#](#は1, 2, 3...: 1がMSB側)を生成する。

#### 【0222】

データ保持部460では、判定基準信号f0の立下りエッジ(反転判定基準信号×f0の立上りエッジ)に同期し、周波数fLowの判定基準信号f0の所定クロック分ずつ、上位ビットから順にその非反転出力×QをHレベルにしていく。

10

#### 【0223】

このため、セット信号生成部410では、各段のDFF414の出力を利用して、ビット別の各データ保持部460の各セット入力端子Sへのセット信号S[N-#](#は1, 2, 3...: 1がMSB側)の最初のアクティブルベル(本例ではHレベル)が、周波数fLowの判定基準信号f0の所定クロック分ずつシフトしていくようとする。

#### 【0224】

ここで、「所定クロック分ずつシフト」するに当たっての所定クロック数は、周波数2分探索における周波数整定期間と周波数探索期間を合成した1つの処理サイクルを何クロック分にするかに合わせて設定する。たとえば、周波数2分探索の1つの処理サイクルを判定基準信号f0の1クロック分にする場合には1クロック分ずつシフトするし、周波数2分探索の1つの処理サイクルを判定基準信号f0の2クロック分にする場合(図10に示した事例の場合)には2クロック分ずつシフトする。

20

#### 【0225】

一例として、図16のタイミングチャート(図ではN=10)に示すように、リセット信号ResetがLレベルになることでリセットが解除された後の判定基準信号f0の“1+#”個目の立下りエッジに同期して、データ保持部460\_N-#のセット入力端子Sに供給するセット信号S[N-#]がHレベルに遷移するように、セット信号S[N-#]の最初にHレベルになるタイミングを1クロック分ずつシフトする。

30

#### 【0226】

ここで、本実施形態のゲイン特性情報取得部107Aは、周波数2分探索を実行する処理サイクルに合わせて、セット信号S[N-#]の最初にHレベルになるタイミングを合わせればよく(図16に示した例では、判定基準信号f0の1クロック分ずつシフト)、それ以降にHになるパルスがあっても、何ら不都合はない。

#### 【0227】

ただし、本実施形態では、図10に示したように、イネーブル信号EN(判定基準信号f0を1/2分周したもの)の立下りエッジで周波数の高/低を周波数比較部170にて判定し、その結果に応じて目標周波数になるように電流制御発振部101Aを制御し、次のサイクルでのイネーブル信号ENの立下りエッジでその制御結果の周波数の高/低を判定する必要がある。

40

#### 【0228】

このことを踏まえると、周波数2分探索を実行する1サイクルは、判定基準信号f0の1サイクル分ではなく、イネーブル信号ENの1サイクル分とすることが好ましく、結局の所、判定基準信号f0の2サイクル分であることが好ましいことになると考えられる。これに対処するには、セット信号生成部410は、セット信号S[N-#]の最初にHレベルになるタイミングを、1クロック分ずつシフトするのではなく、2クロック分ずつシフトする必要があると考えられる。

#### 【0229】

このための仕組みとして、図14に示すセット信号生成部410において、ゲート回路420は、先ず、2段目のDFF414\_2の反転出力×Q2をそのままセット信号S[N

50

- 1 : 本例では 9 ] として出力する。また、3 段目の D F F 4 1 4 \_3 の反転出力 × Q 3 をそのままセット信号 S [ N - 2 : 本例では 8 ] として出力する。また、2 段目の D F F 4 1 4 \_2 の反転出力 × Q 2 と 3 段目の D F F 4 1 4 \_3 の反転出力 × Q 3 との A N D ゲート 4 2 2 による論理積をセット信号 S [ N - 3 : 本例では 7 ] として出力する。

#### 【 0 2 3 0 】

また、4 段目の D F F 4 1 4 \_4 の反転出力 × Q 4 をそのままセット信号 S [ N - 4 : 本例では 6 ] として出力する。また、2 段目の D F F 4 1 4 \_2 の反転出力 × Q 2 と 4 段目の D F F 4 1 4 \_4 の反転出力 × Q 4 との A N D ゲート 4 2 4 による論理積をセット信号 S [ N - 5 : 本例では 5 ] として出力する。また、3 段目の D F F 4 1 4 \_3 の反転出力 × Q 3 と 4 段目の D F F 4 1 4 \_4 の反転出力 × Q 4 との A N D ゲート 4 2 6 による論理積をセット信号 S [ N - 6 : 本例では 4 ] として出力する。また、2 段目の D F F 4 1 4 \_2 の反転出力 × Q 2 と 3 段目の D F F 4 1 4 \_3 の反転出力 × Q 3 と 4 段目の D F F 4 1 4 \_4 の反転出力 × Q 4 との A N D ゲート 4 2 8 による論理積をセット信号 S [ N - 7 : 本例では 3 ] として出力する。

10

#### 【 0 2 3 1 】

また、5 段目の D F F 4 1 4 \_5 の反転出力 × Q 5 をそのままセット信号 S [ N - 8 : 本例では 2 ] として出力する。また、2 段目の D F F 4 1 4 \_2 の反転出力 × Q 2 と 5 段目の D F F 4 1 4 \_5 の反転出力 × Q 5 との A N D ゲート 4 3 0 による論理積をセット信号 S [ N - 9 : 本例では 1 ] として出力する。また、3 段目の D F F 4 1 4 \_3 の反転出力 × Q 3 と 5 段目の D F F 4 1 4 \_5 の反転出力 × Q 5 との A N D ゲート 4 3 2 による論理積をセット信号 S [ N - 1 0 : 本例では 0 ] として出力する。

20

#### 【 0 2 3 2 】

このような構成のゲート回路 4 2 0 を設けることで、図 1 7 のタイミングチャート（図では N = 1 0 ）に示すように、リセット信号 Reset が L レベルになることでリセットが解除された後の判定基準信号 f 0 の “ 1 + # ” 個目の立下りエッジに同期して、データ保持部 4 6 0 \_N-# のセット入力端子 S に供給するセット信号 S [ N - # ] が H レベルに遷移するように、セット信号 S [ N - # ] の最初に H レベルになるタイミングを 2 クロック分ずつシフトするようになる。

#### 【 0 2 3 3 】

30

< 1 段目のデータ保持部の詳細 >

R S ラッチで構成された各ビット別のデータ保持部 4 6 0 は、セット信号生成部 4 1 0 の N ビットのセット信号が、ビット別に対応するように、セット入力端子 S に入力される。たとえば、セット信号生成部 4 1 0 の最上位ビット ( M S B ) のセット信号は、最上位ビット ( M S B ) を担当するデータ保持部 4 6 0 のセット入力端子 S に入力され、以下順に、セット信号生成部 4 1 0 の下位ビット ( M S B - % : % は 1, 2, ... ) のセット信号は、下位ビット ( M S B - % : % は 1, 2, ... ) を担当するデータ保持部 4 6 0 のセット入力端子 S に入力される。また、各データ保持部 4 6 0 は、反転リセット信号 xReset がインバータ 4 0 6 を介してリセット信号 Reset とされてから各リセット入力端子 R に共通に入力される。

40

#### 【 0 2 3 4 】

1 段目のデータ保持部 4 6 0 として使用される R S ラッチは、図 1 8 ( A ) に示すように、セット信号 S を反転するインバータ 4 6 2 と、リセット信号 R を反転するインバータ 4 6 4 と、2 つの 2 入力型の N A N D ゲート 4 6 6, 4 6 8 とを有する。

#### 【 0 2 3 5 】

N A N D ゲート 4 6 6 は、一方の入力にインバータ 4 6 2 の出力（すなわちセット信号 S の反転信号 × S ）が入力され、他方の入力に N A N D ゲート 4 6 8 の出力（すなわちセット出力の反転信号 × Q ）が入力される。N A N D ゲート 4 6 8 は、一方の入力にインバータ 4 6 4 の出力（すなわち反転出力信号 × R ）が入力され、他方の入力に N A N D ゲート 4 6 6 の出力（すなわち非反転出力信号 Q ）が入力される。

#### 【 0 2 3 6 】

50

ビット別の各データ保持部460の各出力端子Outから出力されるデータ(セット出力)は、対応するビット別の各データ保持部480の各クロック入力端子CKへのクロック信号として使用されるとともに、DA変換部174A\_1, 174A\_2(纏めて174Aと記す)の対応するビット別の各制御信号Control[N-#](#は1, 2, 3...: 1がMSB側)として使用される。

#### 【0237】

このような構成のデータ保持部460の動作における真理値表は、図18(B)に示す通りである。たとえば、セット信号Sおよびリセット信号Rがともに“0; Lレベル”であるときには、非反転出力端子である出力端子Outと反転出力端子は、直前の状態を維持する、つまり、出力データは不变である。また、セット信号Sが“0; Lレベル”であるときにリセット信号Sが“1; Hレベル”になると、非反転出力端子である出力端子Outは“0; Lレベル”、反転出力端子は“1; Hレベル”になり、出力論理状態がリセットされる。10

#### 【0238】

また、リセット信号Sが“0; Lレベル”であるときにセット信号Sが“1; Hレベル”になると、非反転出力端子である出力端子Outは“1; Hレベル”、反転出力端子は“0; Lレベル”になり、出力論理状態がセットされる。なお、セット信号Sおよびリセット信号Rがともに“1; Hレベル”であるときは、非反転出力端子である出力端子Outと反転出力端子がともに、“1; Hレベル”になるが、通常は、この状態を禁止状態として取り扱う。20

#### 【0239】

よって、このようなRSラッチで構成された1段目の各データ保持部460は、リセット入力端子RがHレベルとされることで、セット出力端子OutをLレベルにする(つまりリセットする)。そして、リセット入力端子RがLレベルの状態で、2進カウンタ部412のビット別の出力(Hレベル)を対応するセット入力端子Sに取り込むことで、出力端子OutをHレベルにする。その結果、ビット切替信号の一例である制御信号Control[N-#]がアクティブ(本例ではHレベル)となるタイミングは、セット信号S[N-#]がリセット後に最初にアクティブ(本例ではHレベル)となるタイミングと一致する。

#### 【0240】

<2段目のデータ保持部の詳細>

DFFで構成された各ビット別のデータ保持部480は、ビット別に、1段目のデータ保持部460の出力データがクロック入力端子CKにクロック信号Clockとして入力される。たとえば、最上位ビット(MSB)を担当するデータ保持部460のデータ出力は、最上位ビット(MSB)を担当するデータ保持部480のクロック入力端子CKに入力され、以下順に、下位ビット(MSB-%: %は1, 2, ...)を担当するデータ保持部460のデータ出力は、下位ビット(MSB-%: %は1, 2, ...)を担当するデータ保持部480のクロック入力端子CKに入力される。

#### 【0241】

また、DFDで構成された各データ保持部480は、周波数比較部170からの周波数比較結果fcompが、データ入力端子Dに共通に入力される。また、各データ保持部480は、反転リセット信号xResetがインバータ406を介してリセット信号Resetとされてから各リセット端子Rに共通に入力される。40

#### 【0242】

ビット別の各データ保持部480の各出力端子Outから出力されるデータ(周波数比較結果fcompを反映したもの)は、DA変換部174Aの対応するビット別の各アップ・ダウン信号UpDown[N-#](#は1, 2, 3...: 1がMSB側)として使用される。

#### 【0243】

2段目のデータ保持部480として使用されるDFDは、図18(A)に示すように、周波数比較結果fcompを反転するインバータ482と、インバータ485, 486, 488と、オン/オフスイッチ(以下単にスイッチと称する)483, 487とを備える。50

## 【0244】

インバータ482の出力とインバータ485の入力との間にスイッチ483が配されている。インバータ485の出力は、インバータ486の入力に接続され、インバータ486の出力はスイッチ487を介してインバータ485の入力に接続されている。

## 【0245】

スイッチ487がオンした状態でインバータ485, 486によってメモリ回路(ラッチ)が構成されるようになっている。

## 【0246】

また、データ保持部480は、リセット信号Rを反転するインバータ492と、2入力型のNANDゲート494と、インバータ496, 498と、オン/オフスイッチ(以下単にスイッチと称する)491, 497を備える。10

## 【0247】

インバータ492の出力はNANDゲート494の一方の入力に接続されている。NANDゲート494の他方の入力は、スイッチ491を介してインバータ485の出力に接続されるとともに、スイッチ497を介してインバータ496の出力に接続される。また、NANDゲート494の出力は、インバータ496, 498の各入力に接続される。インバータ498の出力は、データ出力端子Outに接続される。

## 【0248】

NANDゲート494のインバータ492側の入力がHレベルで、かつスイッチ497がオンした状態で、NANDゲート494とインバータ496によってメモリ回路(ラッチ)が構成されるようになっている。20

## 【0249】

クロック入力端子CKは、直接にスイッチ483, 497の制御端子に接続されるとともに、インバータ488を介してスイッチ487, 491の制御端子に接続される。ここで、各スイッチ483, 487, 491, 497は、制御端子がLレベル(つまりクロック入力端子CKがLレベル)のときにオンし、制御端子がHレベル(つまりクロック入力端子CKがHレベル)のときにオフするタイプのスイッチである。

## 【0250】

なお、各スイッチ483, 487, 491, 497を、制御端子がLレベル(つまりクロック入力端子CKがLレベル)のときにオフし、制御端子がHレベル(つまりクロック入力端子CKがHレベル)のときにオンするタイプのスイッチとしてもよい。この場合、図18(C)に示すように、図18(A)に示す構成に対して、クロック入力端子CKは、直接にスイッチ487, 491の制御端子に接続されるとともに、インバータ488を介してスイッチ483, 497の制御端子に接続されるように修正すればよい。30

## 【0251】

このような構成のデータ保持部480においては、先ず、インバータ492へのリセット信号RがHレベルになると、インバータ492の出力(すなわちNANDゲート494の片方の入力)がLレベルとなることで、NANDゲート494のもう片方の入力に拘わらず、その出力がHレベルとなり、インバータ498を介することで、データ出力端子OutがLレベルとなる。すなわち、データ出力がリセットされる。40

## 【0252】

また、この後に、インバータ492へのリセット信号RがLレベルになると、インバータ492の出力(すなわちNANDゲート494の片方の入力)がHレベルとなることで、NANDゲート494の出力が、NANDゲート494のもう片方の入力を反映するようになる。

## 【0253】

たとえば、この時点でクロック入力端子CKがLレベルにあると、スイッチ483, 497はオン/オフスイッチ487, 491はオフしている。よって、先ず、インバータ496は、リセット時のNANDゲート494の出力(Hレベル)を反転してNANDゲート494のもう片方の入力にLレベルを供給するようになる。よって、NANDゲート494の50

出力は H レベルを維持したままとなり、データ出力がリセットされた状態のままである。

【 0 2 5 4 】

このとき、入力側では、周波数比較結果 f comp を内部に取り込んでいる。すなわち、スイッチ 4 8 3 がオンすることで、周波数比較結果 f comp をインバータ 4 8 2 で反転したデータがスイッチ 4 8 3 を介してインバータ 4 8 5 まで伝達されている。スイッチ 4 8 7 , 4 9 1 はオフであるので、周波数比較結果 f comp の論理レベルがそのままインバータ 4 8 5 の出力に現われた状態にある。

【 0 2 5 5 】

この後に、クロック入力端子 CK が H レベルに切り替ると、スイッチ 4 8 3 , 4 9 7 はオフし、スイッチ 4 8 7 , 4 9 1 はオンする。これにより、インバータ 4 8 5 へのインバータ 4 8 2 およびスイッチ 4 8 3 を介した周波数比較結果 f comp の供給が停止するが、スイッチ 4 8 7 がオンすることで、直前のインバータ 4 8 5 の出力（すなわち直前の周波数比較結果 f comp の論理レベル）がインバータ 4 8 6 を介して論理反転されて入力に戻される。その結果、直前の周波数比較結果 f comp の論理レベルがインバータ 4 8 5 , 4 8 6 によって保持されることになる。

10

【 0 2 5 6 】

また、スイッチ 4 9 1 がオンであるので、インバータ 4 8 5 の出力である直前の周波数比較結果 f comp の論理レベルが NAND ゲート 4 9 4 の片方の入力に供給される。その結果、直前の周波数比較結果 f comp の論理レベルが NAND ゲート 4 9 4 によって論理反転され、さらにインバータ 4 9 8 によって論理反転されることで、直前の周波数比較結果 f comp の論理レベルが、そのままデータ出力端子 Out に現われる。

20

【 0 2 5 7 】

この後に、クロック入力端子 CK が L レベルに切り替ると、スイッチ 4 8 3 , 4 9 7 はオンし、スイッチ 4 8 7 , 4 9 1 はオフする。これにより、周波数比較結果 f comp の論理レベルの NAND ゲート 4 9 4 の片方の入力への供給が停止する。しかしながら、このときには、スイッチ 4 9 7 がオンすることで、インバータ 4 9 6 は、直前の NAND ゲート 4 9 4 の出力状態を反転して NAND ゲート 4 9 4 のもう片方の入力に供給するようになる。よって、NAND ゲート 4 9 4 の出力は直前の NAND ゲート 4 9 4 の出力状態を維持したままとなる。よって、クロック入力端子 CK が L レベルに切り替っても、直前の周波数比較結果 f comp の論理レベルが、そのままデータ出力端子 Out に現われ続ける。

30

【 0 2 5 8 】

よって、このような DFF で構成された 2 段目の各データ保持部 4 8 0 は、データ保持部 4 6 0 のセット出力が L レベルから H レベルになるエッジをビットの重付けの切替えタイミングとして取り扱って周波数比較部 1 7 0 からの周波数比較結果 f comp を取り込み、リセット端子 R へのリセット信号 Reset が H レベルになるまで、そのデータを保持し続ける。データ保持部 4 8 0 が保持しているデータは、データ出力端子 Out から出力される。

【 0 2 5 9 】

このように、本実施形態の周波数比較結果保持部 1 7 2 においては、2 段目のデータ保持部 4 8 0 として使用する DFF は、図 18 に示すようなスタティックなラッチ（インバータ 4 8 2 , 4 8 5 で構成されたメモリ回路および NAND ゲート 4 9 4 およびインバータ 4 9 6 で構成されたメモリ回路）を用いるタイプの回路としており、ビットごとにメモリ回路に記憶された周波数比較部 1 7 0 の周波数比較結果 f comp は、リセット信号 R が再び入力されるまで保持され続けるようになっている。

40

【 0 2 6 0 】

図 19 に、図 10 に対応する、周波数 2 分探索の処理サイクルを判定基準信号 f 0 の 2 クロック分とする場合における、周波数比較部 1 7 0 と周波数比較結果保持部 1 7 2 の全体の動作を示すタイミングチャートを示す。図 19 から分かるように、周波数比較結果 f comp を表わすビット別のアップ・ダウン信号 UpDown は、MSB 側から順に出力されて行くことになる。

【 0 2 6 1 】

50

ここで、周波数比較部 170 と周波数比較結果保持部 172 は同じ周波数 F Low の判定基準信号 f0 が入力されて動作するようになっているため、完全に同期して動作するよう 10 している。加えて、前述のように、周波数比較部 170 は、判定基準信号 f0 の立上りエッジに同期して動作するイネーブル信号 EN に合わせて動作するよう 15 しているので判定基準信号 f0 の立上りエッジで動作するようになっており、これに対して周波数比較結果保持部 172 は判定基準信号 f0 の立下りエッジで動作させるよう 20 している。

#### 【0262】

これにより、図 19 に示すように、判定基準信号 f0 の立上りエッジに同期したイネーブル信号 EN の立下りエッジで周波数比較結果 f comp を確定させた後に、判定基準信号 f0 の立下りエッジに同期してデータ保持部 460 から発せられるビット切替信号のエッジで周波数比較結果 f comp の論理状態を取り込むことができ、周波数比較結果 f comp の取り込みに関して、タイミングによる誤動作が起こらないように 25 している。

10

#### 【0263】

なお、ここで示した例は、周波数 2 分探索の処理サイクルを判定基準信号 f0 の 2 クロック分にした例であるが、周波数 2 分探索の処理サイクルを判定基準信号 f0 の 1 クロック分にする場合でも、たとえばゲート遅延を利用するなどしてセット信号が H レベルになる時点を判定基準信号 f0 の立下りエッジよりも少し遅らせることで、周波数比較結果 f comp の取り込みに関してタイミングによる誤動作が起こらないように 30 することができる。

#### 【0264】

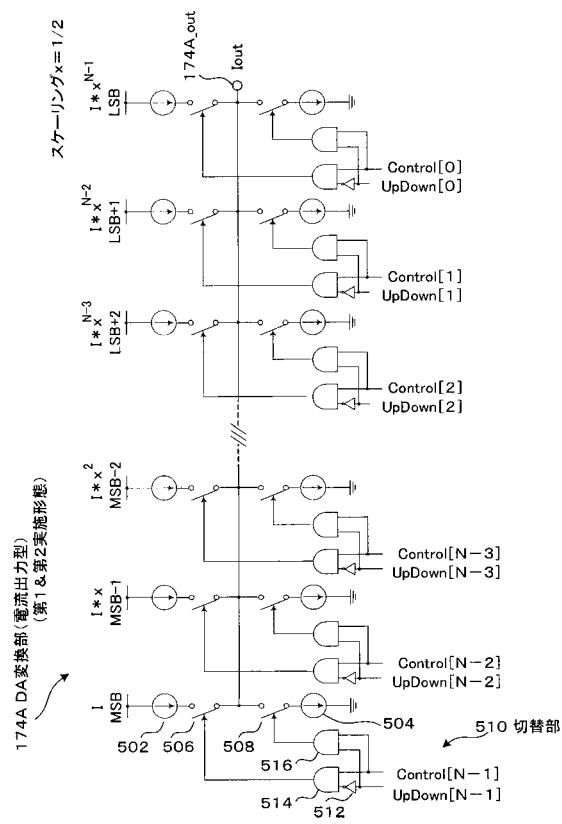

< DA 变換部の構成例と動作 ; 第 1 実施形態 >

20

図 20 は、電流出力型の DA 变換部 174A の詳細な構成例を示す図である。なお、ここでは基本形を示すが、好ましくは、後述の図 24 に示すものを使用する。

#### 【0265】

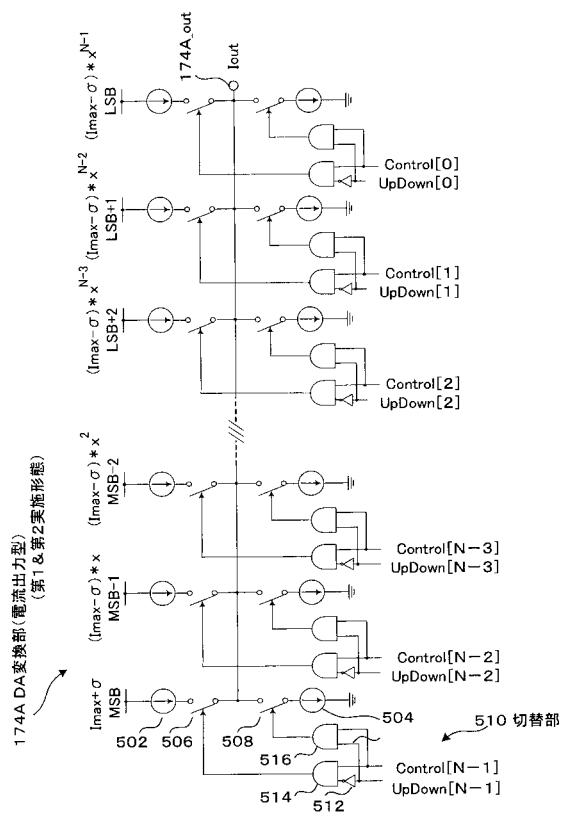

図 20 に示すように、DA 变換部 174A は、ビット別に対応する N (N は、2 分探索の N 回に対応する) 本のソース電流源 502 と N 本のシンク電流源 504 と、各電流源 502, 504 の出力を選択的に合成するための出力スイッチ 506, 508 と、各電流源 502, 504 の出力スイッチ 506, 508 のオン / オフ動作を制御することで、1 ビット電流源 501 がソースおよびシンクの何れの動作モードになるかを切り替える切替部 510 とを備えている (図では最上位ビット MSB についてのみ参照子を付す)。ここで、各出力スイッチ 506, 508 は、制御端子が L レベルのときにオフし、制御端子が H レベルのときにオンするタイプのスイッチである。

30

#### 【0266】

各ソース電流源 502 は、一方が電源側に接続され他方のソース側が出力スイッチ 506 に接続されている。各シンク電流源 504 は、一方が基準電位 ( 接地電位 GND ) に接続され他方のシンク側が出力スイッチ 508 に接続されている。

#### 【0267】

ビット別の各出力スイッチ 506 のソース電流源 502 とは反対側と、対応するビット別の各出力スイッチ 508 のシンク電流源 504 とは反対側とが接続されるとともに、その接続点が、全てのビットで共通に電流输出端子 174A\_out に接続されている。各ビットの電流加算結果が DA 出力信号として電流输出端子 174A\_out から出力されるよう 40 なっている。DA 出力信号は、DA 变換部 174A\_1 であれば出力電流信号 Iout\_1 となるし、DA 变換部 174A\_2 であれば出力電流信号 Iout\_2 となる。

40

#### 【0268】

ビット別の各切替部 510 は、周波数比較結果保持部 172\_1, 172\_2 に保持されているデータに応じて出力スイッチ 506, 508 のオン / オフ動作を制御することで、1 ビット電流源 501 がソース電流およびシンク電流の何れを発生するのかを切り替える。

#### 【0269】

このための構成として、切替部 510 は、周波数比較結果保持部 172 のデータ保持部 480 から出力される対応するビットのアップ・ダウン信号 UpDown [ N - # ] (# は 1, 2, 3 ... : 1 が MSB 側) を論理反転するインバータ 512 と、2 つの 2 入力型の AND

50

ゲート 514, 516 を有している。

【0270】

AND ゲート 514 は、一方の入力端子にアップ・ダウン信号UpDown [ N - # ] をインバータ 512 で論理反転した信号が入力され、他方の入力端子に周波数比較結果保持部 172 の対応するビットの制御信号 Control [ N - # ] (# は 1, 2, 3 … : 1 が MSB 側) が入力され、その出力がソース電流源 502 側の出力スイッチ 506 の制御端子に供給される。AND ゲート 516 は、一方の入力端子にアップ・ダウン信号UpDown [ N - # ] が入力され、他方の入力端子に制御信号 Control [ N - # ] が入力され、その出力がシンク電流源 504 側の出力スイッチ 508 の制御端子に供給される。

【0271】

ビット別に、ソース電流源 502 とシンク電流源 504 とは、ビットの重みに対応した同じ電流量をソースもしくはシンクするようになっている。たとえば、最上位ビットについては最大電流量 I とし、下位側に行くに連れて、1 ビットごとに、その電流量を、 $1/2$  ( $1/2$  以上) に減少させるようとする。好ましくは、MSB を I として、以下順に、 $I / \{2^{\wedge} &\}$  ( $\&$  は、1, 2, …, N-2, N-1) とする。本例では、スケーリング x を  $1/2$  とし、そのべき乗でビットの重みを付けている。

【0272】

また、同じ電流量のソース電流源 502 およびシンク電流源 504 を一組として、制御信号 Control とアップ・ダウン信号UpDown に基づいて出力スイッチ 506, 508 を制御することで、制御信号 Control が有効 (H レベル) であるときのみ、一組の電流源 502, 504 (1 ビット電流源 501 とも称する) は、周波数比較結果保持部 172\_1, 172\_2 から出力されるアップ・ダウン信号UpDown に基づいてソース電流またはシンク電流のどちらかの電流入出力動作を行なう。

【0273】

具体的には、アップ・ダウン信号UpDown が H レベル、すなわち、発振周波数 fcc が判定基準周波数 f1, f2 よりも高ければ、AND ゲート 514 の出力は L レベルとなり AND ゲート 516 の出力は H レベルとなる。これにより、出力スイッチ 506 は、制御端子が L レベルとなることでオフし、出力スイッチ 508 は、制御端子が H レベルとなることでオンするので、一組の各電流源 502, 504 は、シンク動作を行なう。

【0274】

これに対して、アップ・ダウン信号UpDown が L レベル、すなわち、発振周波数 fcc が判定基準周波数 f1, f2 よりも低ければ、AND ゲート 514 の出力は H レベルとなり AND ゲート 516 の出力は L レベルとなる。これにより、出力スイッチ 506 は、制御端子が H レベルとなることでオンし、出力スイッチ 508 は、制御端子が L レベルとなることでオフするので、一組の各電流源 502, 504 は、ソース動作を行なう。

【0275】

また、先に示した図 19 から分かるように、周波数比較結果 fcomp を表わすビット別のアップ・ダウン信号UpDown は、上位ビット (MSB) 側から順に出力されていくので、DA 変換部 174A も、周波数比較部 170 の周波数比較結果 fcomp に応じて、1 ビット電流源 501 (一組の電流源 502, 504) を、上位ビット (MSB) から順番に動作させていく。

【0276】

< 発振ゲイン補正部の動作の詳細 >

図 21 は、ゲイン特性情報取得部 107A の全体動作を説明する図である。ここで、図 21 は、図 19 に示したタイミングチャートに従って動作したときの電流制御発振部 101A の発振周波数 fcc の収束の様子の一例を示す。

【0277】

周波数比較部 170、周波数比較結果保持部 172、DA 変換部 174A の回路動作を纏めると、以下の通りである。すなわち、先ず、周波数比較部 170 により周波数比較が実行される都度、DA 変換部 174A の上位ビットから順に 1 ビット電流源 501 が動作

10

20

30

40

50

し、周波数比較部 170 による周波数比較結果  $f_{comp}$ に基づいて電流制御発振部 101A の発振周波数  $f_{cco}$  が判定基準周波数  $f_1, f_2$  よりも高ければ低くなるように、逆に、低ければ高くなるように、電流制御発振部 101A の周波数制御入力端子 101Ain に供給される発振制御電流  $I_{cnt}$  を調整するべく、周波数制御電流  $I_{osci}$  のソースまたはシンクを行なう。これによって、分周比  $M_1, M_2$  によって決めた判定基準周波数  $f_1, f_2$  に電流制御発振部 101A の発振周波数  $f_{cco}$  は絞り込まれていくことになる。

#### 【0278】

このような周波数調整手法を、周波数 2 分探索法と呼ぶことにする。なお、2 分探索を使つた周波数探索の従来例として以下の非特許文献 4 が存在する。しかしながら、本実施形態の 2 分探索は、基本的な考え方は、この非特許文献 4 と同じであるが、具体的な仕組みにおいて差異がある。

10

#### 【0279】

【非特許文献 4】Kun-Seok Lee, Eun-Yung Sung, In-Chul Hwang, and Byeong-Ha Park, "Fast AFC technique using a code estimation and binary search algorithm for wide band frequency synthesis", Proceedings of ESSCIRC, Grenoble, France, 2005, p181 ~ 184

#### 【0280】

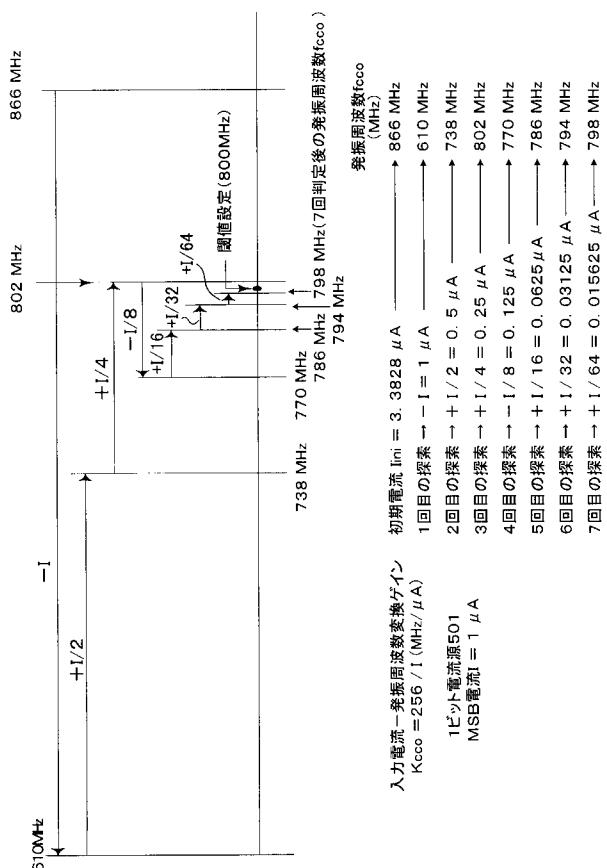

たとえば、本実施形態の仕組みにおいては、図 21 に示すように、先ず、電流制御発振部 101A は、周波数制御入力端子 101Ain に供給される発振制御電流  $I_{cnt}$  が多いほど発振周波数  $f_{cco}$  が高くなる性質を持つものであるとする。

20

#### 【0281】

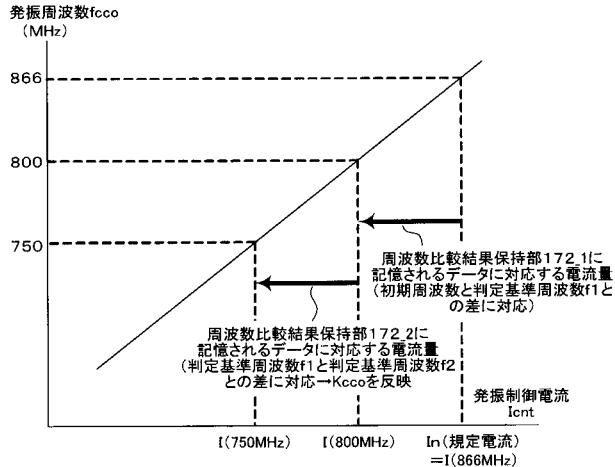

また、後述するように、理想的には、規定電流源 109A からの規定電流  $I_n$  (= 図 3 の初期電流  $I_{ini}$ ) の条件下で求められる周波数 (たとえば 800MHz) となるべきであるが、電流制御発振部 101A の入力電流 - 発振周波数変換ゲイン  $K_{cco}$  のばらつきにより、規定電流  $I_n$  (初期電流  $I_{ini}$ ) のみでは、たとえば 866MHz (初期周波数) で発振しているものとし、このような電流制御発振部 101A の発振周波数  $f_{cco}$  を、目的とする 800MHz に収束させることにする。

#### 【0282】

なお、電流制御発振部 101A の入力電流 - 発振周波数変換ゲイン  $K_{cco}$  は、発振制御電流  $I_{cnt}$  の着目する制御範囲内では非線形な特性ではなく、一例として、256 /  $I$  [MHz /  $\mu A$ ] であるものとする。また、ビット別の 1 ビット電流源 501 の最上位ビットの電流値  $I$  は  $1 \mu A$  であるとする。

30

#### 【0283】

この規定電流源 109A の電流値は、標準状態の一例である理想状態 (ideal), 25 (室温) の条件での、クロック周波数または受信データレートの周波数に CCO の発振周波数が一致する入力電流値である。

#### 【0284】

たとえば、周波数比較部 170 の判定基準周波数  $f_1$  を、収束値の発振周波数  $f_{cco} = 800MHz$  とすると、規定電流  $I_n$  (図 3 の初期電流  $I_{ini}$ ) での発振周波数  $f_{cco} = 866MHz$  (初期周波数) の方が収束値の発振周波数  $f_{cco} = 800MHz$  よりも当然高いため、1 回目の探索における DA 変換部 174A からの出力電流信号  $I_{out}$  は、先ず MSB の 1 ビット電流源 501 による電流  $I$  がシンクされ、電流制御発振部 101A の周波数制御入力端子 101Ain に供給される発振制御電流  $I_{cnt}$  は " $I_n - I$ " となり、発振周波数  $f_{cco}$  は 610MHz になる。

40

#### 【0285】

610MHz は収束値の発振周波数  $f_{cco} = 800MHz$  よりも低いため、2 回目の探索における DA 変換部 174A からの出力電流信号  $I_{out}$  においては、" $MSB - 1$ " の 1 ビット電流源 501 による電流  $I/2$  がソースされ、電流制御発振部 101A の周波数制御入力端子 101Ain に供給される発振制御電流  $I_{cnt}$  は " $I_n - I + I/2$ " となり、発振周波数  $f_{cco}$  は 738MHz になる。

50

## 【0286】

738 MHzは収束値の発振周波数  $f_{cco} = 800 \text{ MHz}$  よりも低いため、3回目の探索におけるDA変換部174Aからの出力電流信号  $I_{out}$  においては、“MSB-2”の1ビット電流源501による電流  $I/4$  がソースされ、電流制御発振部101Aの周波数制御入力端子101Ainに供給される発振制御電流  $I_{cnt}$  は “ $I_n - I + I/2 + I/4$ ” となり、発振周波数  $f_{cco}$  は 802 MHzになる。

## 【0287】

802 MHzは収束値の発振周波数  $f_{cco} = 800 \text{ MHz}$  よりも高いため、4回目の探索におけるDA変換部174Aからの出力電流信号  $I_{out}$  においては、“MSB-3”の1ビット電流源501による電流  $I/8$  がシンクされ、電流制御発振部101Aの周波数制御入力端子101Ainに供給される発振制御電流  $I_{cnt}$  は “ $I_n - I + I/2 + I/4 - I/8$ ” となり、発振周波数  $f_{cco}$  は 770 MHzになる。

10

## 【0288】

このような動作を7回繰り返すと、7回判定後に電流制御発振部101Aの周波数制御入力端子101Ainに供給される発振制御電流  $I_{cnt}$  は “ $I_n - I + I/2 + I/4 - I/8 + I/16 + I/32 + I/64$ ” となり、発振周波数  $f_{cco}$  は 798 MHzとなり、収束値 (= 判定基準周波数) の発振周波数 = 800 MHzにかなり近くなる。7回よりも多く判定を繰り返せば、発振周波数  $f_{cco}$  を限りなく 800 MHzに近づけることも可能となる。

20

## 【0289】

さらに、このときのDA変換部174Aから周波数制御入力端子101Ainに供給される出力電流信号  $I_{out} = (-I + I/2 + I/4 - I/8 + I/16 + I/32 + I/64 + (8\text{回目以降の判定結果}))$  は、デジタルデータ (この場合は 1001000...) としてDA変換部174AのDFFで構成されたデータ保持部480に記憶されているため、電流制御発振部101Aを 800 MHzで発振させるための初期電流  $I_{ini}$  に対する補正分を表わす出力電流信号  $I_{out}$  を、周波数2分探索終了後、ゲイン特性情報取得部107Aの周波数比較結果保持部172は記憶していることを意味する。

## 【0290】

なお、上記の説明では、電流出力型のDA変換部174Aを構成する1ビット電流源501の電流値が、最上位ビットから1ビットごとに  $1/2$  になる例を示した。しかしながら、このままでは1ビット電流源501の電流値がばらつくと、周波数探索精度が大幅に悪化し、ゲイン補正精度も悪化させてしまう。これを回避するために、電流源スケーリングを  $1/2$  より大きくする必要がある。この電流源スケーリングの値は、電流制御発振部101Aの製造ばらつきや温度変化による入力電流 - 発振周波数変換ゲイン  $K_{cco}$  の変化を考慮して決定するのがよい。

30

## 【0291】

<電流源スケーリングについて>

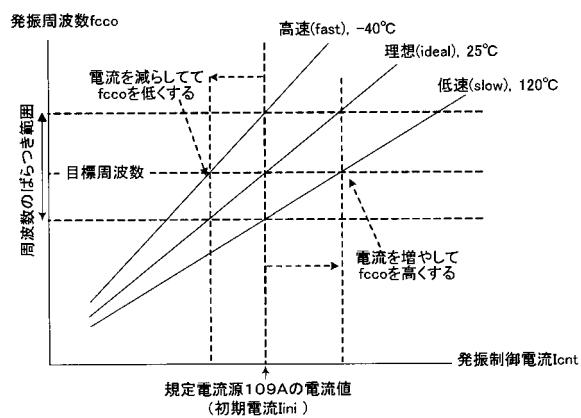

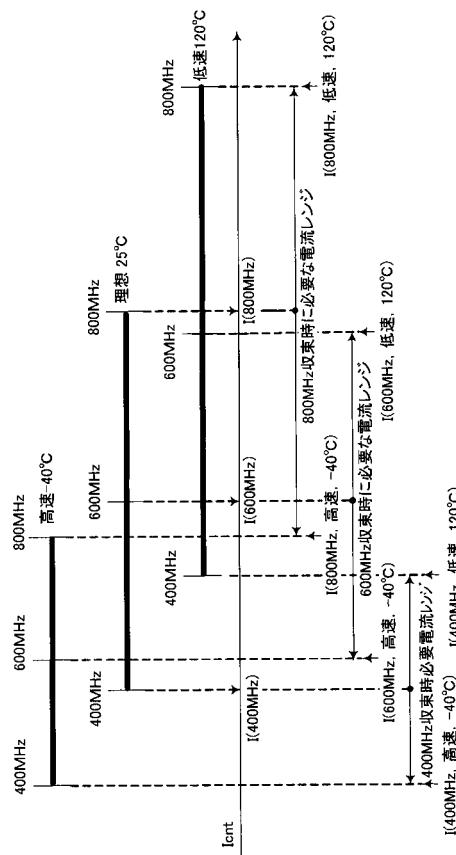

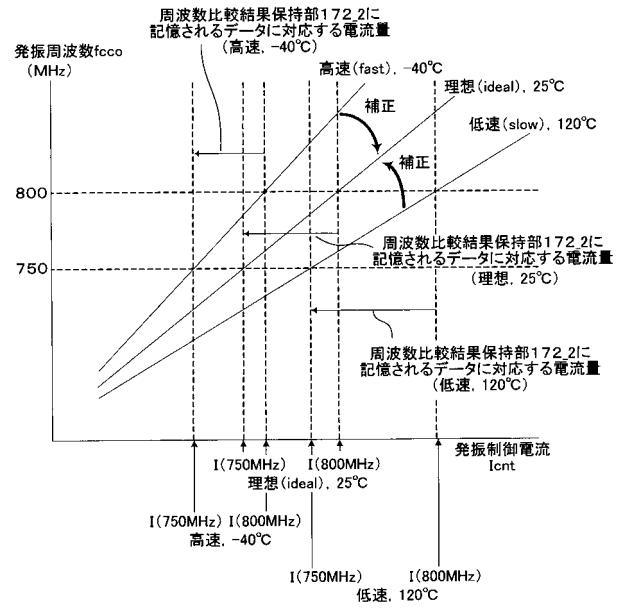

図22～図25は、DA変換部174Aを構成する各1ビット電流源501の電流値に設定する重付けを示す電流源スケーリングの決定方法を説明する図である。ここで、図22は、電流制御発振部101Aの製造ばらつきや温度変化によって、入力電流 - 発振周波数変換ゲイン  $K_{cco}$  が変化する例を示す図である。図23は、DA変換部174Aの必要出力電流レンジを説明する図である。図24は、スケーリングを  $\times$ としたときのDA変換部174Aの構成を示した図である。図25は、スケーリング  $\times$  において周波数探索精度を最も悪化させる事例を示す図である。

40

## 【0292】