(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4451934号

(P4451934)

(45) 発行日 平成22年4月14日(2010.4.14)

(24) 登録日 平成22年2月5日(2010.2.5)

(51) Int.Cl.

H01L 21/3213 (2006.01)

H01L 21/3065 (2006.01)

F 1

H01L 21/88

H01L 21/302 104C

請求項の数 20 (全 17 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願平10-540716                 |

| (86) (22) 出願日 | 平成10年3月17日(1998.3.17)        |

| (65) 公表番号     | 特表2001-517367(P2001-517367A) |

| (43) 公表日      | 平成13年10月2日(2001.10.2)        |

| (86) 國際出願番号   | PCT/US1998/005202            |

| (87) 國際公開番号   | W01998/042020                |

| (87) 國際公開日    | 平成10年9月24日(1998.9.24)        |

| 審査請求日         | 平成17年3月15日(2005.3.15)        |

| (31) 優先権主張番号  | 08/820,533                   |

| (32) 優先日      | 平成9年3月19日(1997.3.19)         |

| (33) 優先権主張国   | 米国(US)                       |

|           |                                                                           |

|-----------|---------------------------------------------------------------------------|

| (73) 特許権者 | ラム・リサーチ・コーポレーション<br>アメリカ合衆国 カリフォルニア州945<br>38 フリモント、クッシング・パークウ<br>エイ、4650 |

| (74) 代理人  | 弁理士 五十嵐 孝雄                                                                |

| (74) 代理人  | 弁理士 下出 隆史                                                                 |

| (74) 代理人  | 弁理士 市川 浩                                                                  |

| (74) 代理人  | 弁理士 加藤 光宏                                                                 |

最終頁に続く

(54) 【発明の名称】導電層をエッチングする方法及び集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

基板加工チャンバ内において、半導体基板の上に配置された導電層を貫いてエッチングすることによって、導電層の下に配置した絶縁層内のビアであって、導電プラグと、導電プラグとビアの内壁との間に配置された層とを有するビアの上に配置される導電機構を形成する方法であって、

前記ビアの直径より狭い幅を有する、前記導電機構の頂部を形成するために、第1のエッチ・レシピを使用して前記導電層を少なくとも部分的に貫いてエッチングする工程と、その後、少なくとも前記ビアの直径と同じ大きさの幅を有する、前記導電機構の底部及び前記ビアの間の界面における前記導電機構の底部を形成するために、前記第1のエッチ・レシピとは異なる第2のエッチ・レシピを使用して前記導電層の残りの厚さを少なくとも部分的に貫いてエッチングする工程と

を有し、前記底部は前記頂部の下に配置され、傾斜エッチ・フットを前記導電機構の底部内に形成すべく前記第2のエッチ・レシピは調製されている方法。

## 【請求項 2】

請求項1に記載の方法において、前記第1のエッチ・レシピは前記第2のエッチ・レシピで達成されるエッチ速度より高いエッチ速度を前記導電層全体にわたって達成すべく調製されている方法。

## 【請求項 3】

請求項1または2に記載の方法において、前記第1のエッチ・レシピはエッチ速度を前記

導電層全体にわたって最大にすべく調製されている方法。

**【請求項 4】**

請求項 1 ないし 3 のいずれかに記載の方法において、前記基板加工チャンバはプラズマ加工チャンバに相当する方法。

**【請求項 5】**

請求項 1 ないし 4 のいずれかに記載の方法において、前記プラズマ加工チャンバはトランスフォーマ・カップルド・プラズマ・エッチ・チャンバに相当する方法。

**【請求項 6】**

請求項 1 ないし 5 のいずれかに記載の方法において、前記導電機構は塩素含有ガスを使用してエッティングする方法。 10

**【請求項 7】**

請求項 1 ないし 5 のいずれかに記載の方法において、前記導電機構はフッ素含有ガスを使用してエッティングする方法。

**【請求項 8】**

請求項 5 ないし 7 のいずれかに記載の方法において、前記トランスフォーマ・カップルド・プラズマ・エッチ・チャンバは前記基板の下に配置された下側電極を有し、前記導電機構の底部をエッティングする間ににおける前記下側電極の DC バイアスは、前記導電機構の頂部を形成する間ににおける前記下側電極の DC バイアスより高い方法。 20

**【請求項 9】**

請求項 1 ないし 8 のいずれかに記載の方法において、前記導電機構の底部をエッティングする間ににおける前記基板の温度は、前記導電機構の頂部を形成する間ににおける前記基板の温度より低く維持される方法。

**【請求項 10】**

請求項 1 ないし 9 のいずれかに記載の方法において、前記導電プラグはチタンを含む方法。 。

**【請求項 11】**

請求項 1 から 10 のいずれかに記載の方法において、前記導電プラグは下に横たわる導電機構へ電気的に接触しており、前記下に横たわる導電機構は前記絶縁層の下に位置する方法。 30

**【請求項 12】**

請求項 1 ないし 11 のいずれかに記載の方法において、前記半導体基板は集積回路の製造に使用する半導体基板に相当する方法。

**【請求項 13】**

半導体基板上に設けられた部品を有する集積回路であって、前記半導体基板の上に配置された第 1 の導電層からエッティングによって形成された第 1 の導電機構と、

前記第 1 の導電機構の上に配置され、かつ、ビアを内部に有する絶縁層と、前記ビア内に配置され、かつ、前記第 1 の導電機構へ電気的に接続されている導電プラグと、

前記導電プラグ及び前記ビアの内壁の間に配置された層と、前記絶縁層の上に配置された第 2 の導電層からエッティングによって形成され、かつ、前記ビアの上に配置された第 2 の導電機構と

を有し、前記第 2 の導電機構は、前記ビア内に配置された導電プラグへ電気的に接続され、かつ、

第 1 のエッチ・プロフィール及び前記ビアの直径より狭い第 1 の幅を有する頂部と、前記第 1 のエッチ・プロフィールとは異なる第 2 のエッチ・プロフィール及び前記ビアの直径より広い第 2 の幅を備え、かつ、前記頂部の下に配置された底部とを有する集積回路。 40

**【請求項 14】**

請求項 13 に記載の集積回路において、前記導電プラグはタンクステンを含む集積回路。 50

**【請求項 15】**

請求項 13 または 14 に記載の集積回路において、前記第 1 のエッチ・プロフィールは前記第 2 のエッチ・プロフィールより異方性が高い集積回路。

**【請求項 16】**

プラズマ加工チャンバ内において、上に横たわる導電層から上に横たわる導電機構を形成する間、下に横たわる導電機構への損傷を防止する方法であって、前記上に横たわる導電層は絶縁層によって前記下に横たわる導電機構から分離されており、前記絶縁層はビア内に配置された導電プラグを有し、前記導電プラグは前記上に横たわる導電機構及び前記下に横たわる導電層を前記絶縁層を貫いて互いに接続し、前記ビアは前記導電プラグとビアの内壁との間に配置された層を有し、前記方法において、

10

前記ビアの直径より狭い第 1 の幅を有する頂部を形成するために、第 1 のエッチ・レシピを使用して前記上に横たわる導電層を少なくとも部分的に貫いてエッチングする工程と、前記第 1 の幅及び前記ビアの直径のいずれよりも大きい第 2 の幅を有する前記上に横たわる導電機構の底部を形成するために、前記第 1 のエッチ・レシピとは異なる第 2 のエッチ・レシピを使用して前記上に横たわる導電層の残りの厚さを少なくとも部分的に貫いてエッティングする工程と

を含む方法。

**【請求項 17】**

請求項 16 に記載の方法において、前記第 1 のエッチ・レシピは前記第 2 のエッチ・レシピより高い速度でエッティングすべく調製されている方法。

20

**【請求項 18】**

請求項 16 または 17 に記載の方法において、前記頂部は前記底部より異方性が高い方法。

**【請求項 19】**

請求項 16 ないし 18 のいずれかに記載の方法において、前記上に横たわる導電層は前記下に横たわる導電層との間に配置されるバリア層を含み、前記第 1 のエッチ・レシピ及び第 2 のエッチ・レシピとは異なる第 3 のエッチ・レシピを使用することによって、前記バリア層を貫いてエッティングする工程をさらに含む方法。

**【請求項 20】**

請求項 16 ないし 19 のいずれかに記載の方法において、前記上に横たわる導電層の前記残りの厚さを貫いてエッティングした後、オーバーエッチを実施する工程を含む方法。

30

**【発明の詳細な説明】****発明の背景**

本発明は半導体デバイスの製造に関する。より詳細には、本発明は半導体デバイスの製造中に積層体のうちの導電層を貫いてエッティングする方法及び装置に関する。

一般的に、半導体集積回路 (IC) またはフラット・パネル・ディスプレイなどの半導体デバイスの製造では、部品トランジスタなどの複数のデバイスをシリコン・ウェハまたはガラス・パネルなどの基板上に形成する。次いで、所望の回路を形成すべくこれら複数のデバイスを互いに接続するために、基板上に位置するメタライゼーション層からエッティングによって形成された金属線などの導電性相互接続線を使用する。メタライゼーション層はアルミニウムまたはその合金の一層などを含むことが可能であり、この合金は銅またはシリコンを含み得る。

40

一部の回路では、相互接続要件を満たすために、複数の導電層を必要とし得る。一般的に、これらの導電層は酸化物中間層などの絶縁層によって互いに分離されている。2つの導電層にそれぞれ設けられた2つの導電機構、即ち、導電線の間の電気的接続を望む場合、前記の絶縁を提供する誘電体中間層を貫通する電気的パスを2つの導電機構の間に提供するために、導電プラグを使用し得る。

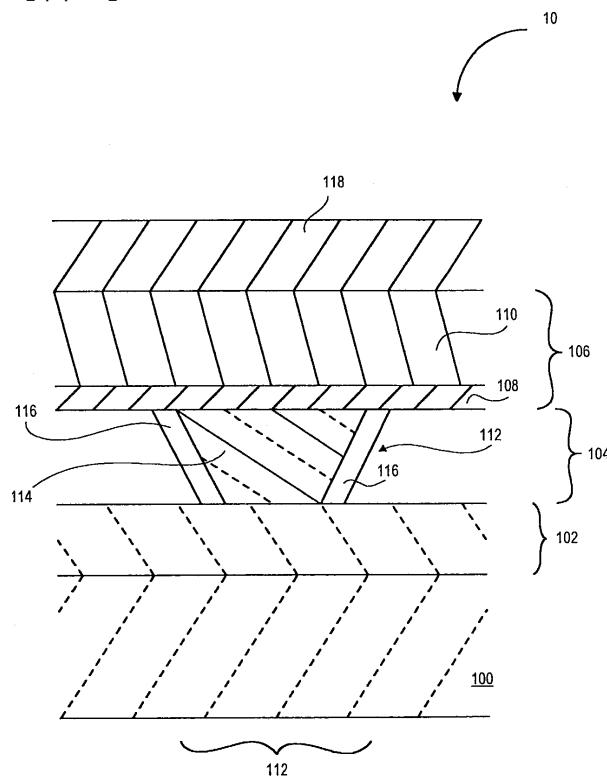

説明を容易にするために、図1は一般的な半導体デバイスの製造中に形成される複数の層に相当する積層体 10 の断面を示す。図1及び他の図面において、複数の層は例示を目的とするのみであり、図示する複数の層の上、下、または間に別の層が存在し得る点に注意

50

する必要がある。更に、図示する全ての層が存在する必要はなく、当業者が一般的に有する知識を使用して、これらの層のうちの幾つかまたは全てを別の層と置換し得る。

積層体 10 の底部には、シリコン・ウェハまたはガラス・パネルなどに相当する基板 100 が表示されている。第 1 の導電層 102 は基板 100 上に設けられている。導電層 102 を所望の形状にパターン化（例えば、従来のフォトレジスト・プロセスを使用）した後、 $\text{SiO}_2$ などを含む絶縁層 104 を導電層 102 の上に形成する。

従来のエッチング・プロセスなどを使用して、ビア 112 を絶縁層 104 内に形成する。導電層 102 内の選択された導電機構と、後から堆積させる導電層 106 内の選択された導電機構とを互いに電気的に接続可能にするために、導電プラグ 114 をビア 112 内に形成する。当業者に周知であるように、導電プラグ 114 はタンゲステンまたはその合金の一種を含み得る。タンゲステンを導電プラグ材料として使用する場合、絶縁層 104 内のビア 112 の壁に対する導電プラグ 114 の更に確実な接合を製造プロセス中及び使用中に可能にするために、接合層 116（図 1 の例では、ビア 112 の内部を覆う環状リングの形態をなす）を使用することが多い。

次いで、導電層 106 を絶縁層 104 上に設け得る。導電層 106 はバリア層 108 を含み得る。一般的に、バリア層 108 は Ti、TiW、TiN または任意の他の適切なバリア材料を含む。任意にて、バリア層 108 を絶縁層 104 及び後から堆積させる相互接続層 110 の間に配置し得る。バリア層 108 を設けた場合、シリコン原子が絶縁層 104 から相互接続層 110 内へ拡散することを、バリア層 108 は防止する。同様に、別のバリア層を導電層 102 及び絶縁層 104 の間に設け得る。一般的に、相互接続層 110 は銅、アルミニウムまたは周知のアルミニウム合金の一種（例：Al-Cu、Al-Si または Al-Cu-Si）を含む。

ビア 112 内の接合層 116 はバリア層 108 に使用する材料と同じ材料若しくは類似する材料（例：Ti、TiW または TiN）または同様に適する他の接合材料を含み得る。積層体 10 の複数の層及び複数の機構を当業者は容易に理解できる。更に、化学蒸着法（chemical vapor deposition、略して、CVD）と、プラズマ強化化学蒸着法（Plasma-enhanced chemical vapor deposition、略して、PECVD）と、スパッタリング、ウェット・エッチング及びプラズマ強化エッチングのうちの少なくともいずれか 1 つに代表される物理蒸着法（physical vapor deposition、略して、PVD）とを含む適切な周知の多数の堆積プロセス及びエッチング・プロセスのうちの任意の 1 つを使用して、積層体 10 の複数の層及び複数の機構を形成できる。

次いで、所望の線パターンを導電層 106 内へエッチングするために、上に横たわるフォトレジスト（PR）層 118 を、プランケット堆積された導電層 106 の頂面に形成する。そして、下に横たわる導電層 106 のエッチングを促進するために、フォトレジスト層 118 をパターン化し得る（例えば、従来のフォトレジスト技術を通じてパターン化する）。例えば、この種のフォトレジスト技術の 1 つは、コントラクト・リソグラフィ・システムまたはステッパー・リソグラフィ・システムへのフォトレジスト材料の露出によるフォトレジスト層 118 のパテーニングと、次のエッチングを促進すべくマスクを形成するためのフォトレジスト材料の現像とを含む。適切なエッチャントを使用することにより、マスクによって保護されていない導電層の領域をエッチングして除去する。これによって、導電性相互接続線、即ち、導電性相互接続機構が後に残される。

更に高い回路密度を実現するために、最近の半導体デバイスは更に細いデザイン・ルールでスケール化されている。この結果、機構サイズ、即ち、導電性相互接続機構の幅または互いに隣接する複数の導電機構間の空間（例：トレンチ）は着実に狭くなっている。例えば、約 0.8 ミクロン（ $\mu\text{m}$ ）の線幅は 4 メガビット（Mb）ダイナミック・ランダム・アクセス・メモリ（DRAM）IC では許容可能と考えられるが、256 Mb DRAM IC は 0.25 ミクロン以下の幅の相互接続線を使用することが好ましい。

十分な電気的接続を保証すべく、上に横たわる導電層（例：導電層 106）内のエッチングによって形成された導電機構をビア 112 へ整合させることは、機構サイズが小さくなるにしたがって困難になってきている。例えば、製造プロセスにおける公差に起因して、

10

20

30

40

50

導電層 106 からエッティングによって形成された上側に横たわる導電線がビア 112 へある程度整合しなくなることがある。これによって、導電層 106 から所望の導電線をエッティングによって形成するために使用するエッチ・プロセスに対して、接合層 116 の一部が露出される。

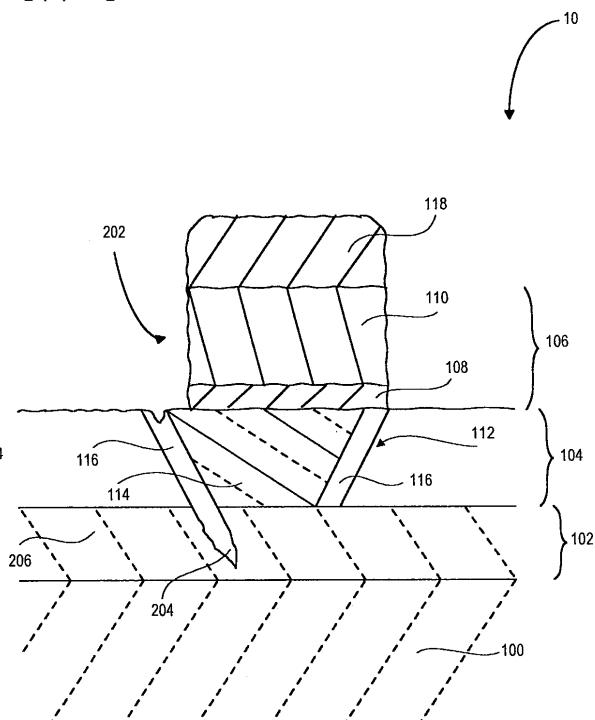

これを示すために、図 2 は導電層 106 を従来のエッチ・プロセスでエッティングした後の図 1 の積層体 10 を示す。図 2 の例では、機構 202 は、導電層 106 からエッティングによって形成され、かつ、紙面に直交する方向（即ち、紙面を貫通する方向）に延びる導電線などを示す。機構 206 は、導電層 102 からエッティングによって形成され、かつ、機構 202 へ直交する方向（即ち、図の左右方向）に延びる導電線などを示す。

図 2において、導電機構 202 はビア 112 の中心に対して水平方向に変位している（例えば、製造プロセスにおける公差に起因する）。この結果、導電機構 202 を形成すべく導電層 106 を貫くエッティングに使用するエッチ・プロセスに対して、接合層 116 の左部分が露出される。前記のように、接合層 116 はバリア層 108 に使用する材料に類似する材料を一般的に含むため、この接合層 116 は、導電層 106 を貫通するエッティングに使用するエッチャントに対して同様に反応する。この結果、接合層 116 の一部が意図せずにエッティングされ、絶縁層 104 内におけるプラグ 114 及びビア 112 の壁の間の接合が弱くなり得る。

一部のケースでは、接合層 116 の一部を導電層オーバーエッチ工程等で導電層エッチ・プロセスへ不適切に露出させることにより、エッチャント材料の一部は、損傷した接合層に沿って下に横たわる導電層 102 内へ浸透し得る。この結果、下に横たわる導電層機構 206 の一部は導電層エッチャント材料へ意図することなく露出され、かつ意図することなくエッティングされる。下に横たわる導電層 102 内に位置する導電機構 206 の損傷部分は図 2 の例の損傷部分 204 として象徴的に示す。下に横たわる導電機構 206 内の十分な量の導電材料が損傷した場合、電流を流す前または後に意図しない断線が生じ得る。

当業者が理解するように、この接合層 116 及び下に横たわる導電層 102 内の機構の意図しないエッティングは、回路の信頼性及び歩留まりを低減し得るので望ましくない。

これらの事情に鑑みて、下に横たわる導電機構及びビア内の接合層の少なくともいずれか一方の意図しない損傷を、上に横たわる導電層内の導電機構のエッティング中に最小限に抑制する改善された技術が望まれる。

#### 発明の概要

1つの実施形態において、本発明は基板加工チャンバ内において、半導体基板の上に配置された導電層を貫いてエッティングすることによって導電機構を形成する方法に関する。導電機構の頂部を形成するために、第 1 のエッチ・レシピを使用して導電層を少なくとも部分的に貫いてエッティングする工程を、この方法は含む。その後、導電機構の底部を形成するために、第 1 のエッチ・レシピとは異なる第 2 のエッチ・レシピを使用して導電層の残りの厚さを少なくとも部分的に貫いてエッティングする工程を、この方法はさらに含む。底部は頂部の下に配置されている。傾斜エッチ・フットを導電機構の底部内に形成すべく第 2 のエッチ・レシピは調製されている。

別の実施形態では、本発明は半導体基板上に設けられた部品を有する集積回路に関する。半導体基板の上に配置された第 1 の導電層からエッティングによって形成された第 1 の導電機構を、集積回路は有する。更に、集積回路は第 1 の導電機構の上に配置された絶縁層を有する。絶縁層はビアを内部に有する。

更に、集積回路はビア内に配置された導電プラグを有する。導電プラグは第 1 の導電機構へ電気的に接続されている。集積回路はビアの上に配置された第 2 の導電機構をさらに有する。第 2 の導電機構は絶縁層の上に配置された第 2 の導電層からエッティングによって形成されている。第 2 の導電機構は、ビア内に配置された導電プラグへ電気的に接続され、かつ、第 1 のエッチ・プロフィール及び第 1 の幅を有する頂部と、頂部の下に配置された底部とを含む。第 1 のエッチ・プロフィールとは異なる第 2 のエッチ・プロフィール及び第 1 の幅より広い第 2 の幅を、底部は有する。

さらに別の実施形態では、本発明は、プラズマ加工チャンバ内において、上に横たわる導

10

20

30

40

50

電層から上に横たわる導電機構を形成する間、下に横たわる導電機構への損傷を防止する方法に関する。上に横たわる導電層は絶縁層によって下に横たわる導電機構から分離されており、絶縁層はピア内に配置された導電プラグを有する。導電プラグは上に横たわる導電機構及び下に横たわる導電層を絶縁層を貫いて互いに接続している。

頂部を形成するために、第1のエッチ・レシピを使用して上に横たわる導電層を少なくとも部分的に貫いてエッティングする工程を、この方法は有する。頂部は第1の幅を有する。更に、上に横たわる導電機構の底部を形成するために、第1のエッチ・レシピとは異なる第2のエッチ・レシピを使用して上に横たわる導電層の残りの厚さを少なくとも部分的に貫いてエッティングする工程を、この方法は有する。底部は第1の幅及びピアの直径のいずれよりも大きい第2の幅を有する。

本発明の前記の効果を含む効果は以下の詳細な説明を読み、かつ、複数の図面を研究することによって明らかになる。

#### 【図面の簡単な説明】

図1は一般的な半導体デバイスの製造中に形成される複数の層に相当する積層体の断面図である。

図2は導電層を従来のエッチ・プロセスでエッティングした後の図1の積層体を示す断面図である。

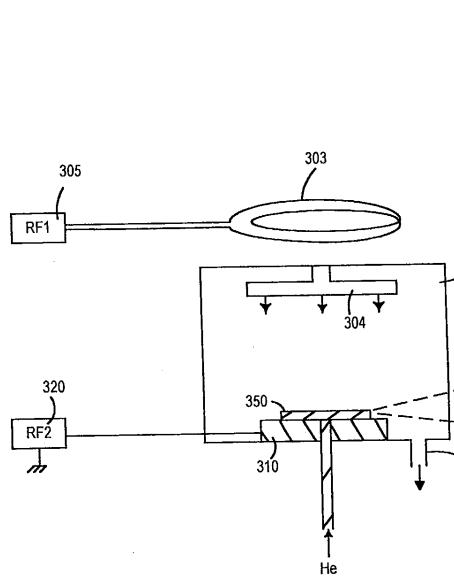

図3は本発明のエッチ技術との併用に適するエッティング反応装置に相当するTCP(商標)9600SEプラズマ反応装置の概略図である。

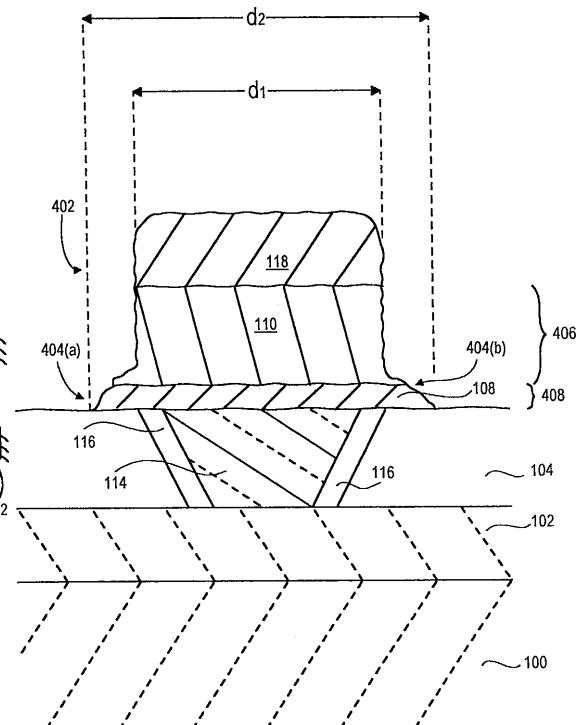

図4は本発明の1つの実施形態に基づくエッチ技術で形成した傾斜エッチ・フットを含む導電機構を示す断面図である。

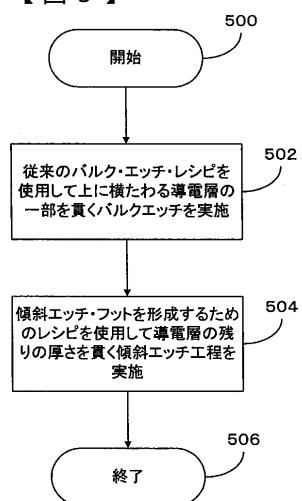

図5は傾斜エッチ・フットを形成するための本発明の1つの実施形態に基づくエッチ技術を示すフローチャートである。

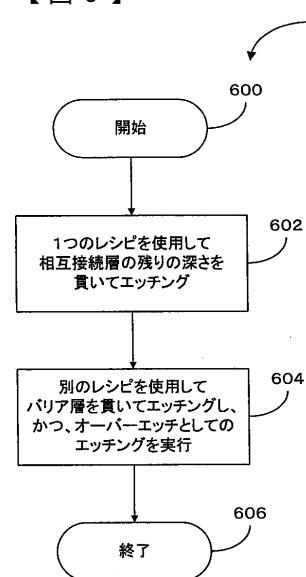

図6はバルク・エッチ工程後に残された導電層の一部を、2つのエッチ工程でエッティングする本発明の1つの実施形態を示すフローチャートである。

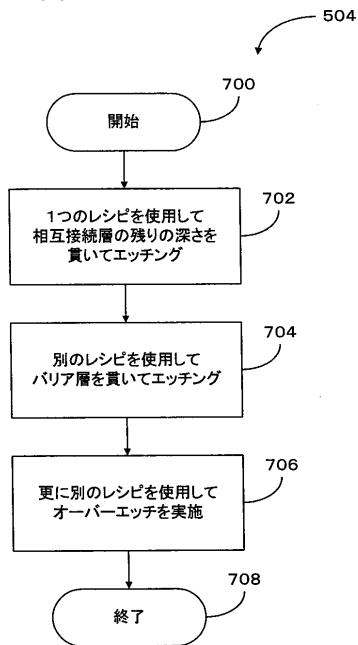

図7はバルク・エッチ工程後に残された導電層の一部を、3つのエッチ工程でエッティングする本発明の1つの実施形態を示すフローチャートである。

#### 好ましい実施形態の詳細な説明

添付図面に示す本発明の幾つかの好ましい実施形態に関連して、本発明を以下に詳述する。以下の説明において、多くの詳細部分は本発明の完全な理解の提供を目的として開示する。しかしながら、これらの詳細部分の幾つかまたは全てを削除した状態で、本発明を実施できることは当業者にとって明白である。別の例では、本発明を必要に不明確にしないために、周知のプロセス工程の詳細を説明しない。

本発明の1つの態様では、導電層を少なくとも2つの工程でエッティングすることによって、前記の歩留まりの減少の問題を軽減する。第1の導電層エッチ工程では、高いエッチ速度(これにより高いウェハ・スループットを実現)及び実質的な異方性エッチ作用の少なくともいずれか一方を達成するために、導電層をバルク・エッチ・レシピでエッティングすることが好ましい。第2の導電層エッチ工程では、傾斜エッチ・フットを出来上がった導電機構内に形成すべく調製したエッチ・レシピによって、導電層の残りの厚さをエッティングする。

エッティングされた導電機構が製造プロセスにおける公差などの原因によってピアと整合していない場合、導電層のうちの異方性の更に高いエッティングを施した部分(バルク導電層エッチ工程、即ち、第1のエッチ工程で形成された部分)より大きい断面を有する傾斜エッチ・フットは、ピア内の損傷しやすい接合層へさらに効果的に重なり得る。関連するデザイン・ルールの増大を要することなく、即ち、更に幅の広いフォトレジスト・マスク機構を指定することによって更に厚い導電機構をバルク・エッチ工程中にエッティングすることを要することなく、これによって、本発明は下に横たわるピア接合層及び下に横たわる導電層内の機構のさらに強力な保護を効果的に促進する。

ドライ・エッティング、プラズマ・エッティング、反応性イオン・エッティング(reactive ion etching、略して、RIE)、磁気強化反応性イオン・エッティング(magnetically enhan

ced reactive ion etching、略して、M E R I E ) または電子サイクロトロン共鳴 (electron cyclotron resonance、略して、E C R ) などに適合したプラズマ加工装置を含む従来の任意のプラズマ加工装置において、本発明の導電層エッチ技術を実施できる。ドライ・エッチングに適合した一般的なプラズマ加工チャンバでは、更に精巧に作り上げるために、ウェハをプラズマで処理する。プロセス・エッチャント・ソース・ガスをチャンバ内部へ供給する入口ポートを、チャンバは含む。プラズマをエッチャント・ソース・ガスから形成するために、適切なR Fエネルギー源をチャンバに関連した電極へ加える。周知のように、プラズマを維持するために、エネルギー自体を誘導結合または容量結合し得る。次いで、ウェハ積層体と反応させ、かつ、ウェハ積層体のうちのプラズマの当たる領域でエッチングするために、化学種をエッチャント・ソース・ガスから形成する。そして、揮發性の副産物を出口ポートを通じて排気する。

プラズマ・エッチングはウェハをその加工中に陽極、即ち、接地電極上へ配置する場面に関連している。その一方、反応性イオン・エッチング (R I E) はウェハをその加工中に陰極、即ち、電源電極上へ配置する場面に関連している。磁気強化反応性イオン・エッチング (M E R I E) はR I E反応装置構造へ変更を加えたものであり、エネルギーを持つ電子が反応装置壁面に奪われることを低減するために、磁界を加える。電極からプラズマ内の電子に対するエネルギー伝達の効率を、M E R I E反応装置が特定の条件下で高め得ることが確認されている。

前記の複数の反応装置及び他の適切なプラズマ加工反応装置のうちの任意の1つで、本発明を実施できることが予想される。容量結合された複数の平行電極板と、E C Rマイクロ波プラズマ・ソースと、ヘリコン、ヘリカル・リゾネータ及びトランス結合プラズマ（これがプレーナ・プラズマであるか否かは関係無い）などの誘電結合されたR F源とのうちのどれを介して、エネルギーをプラズマへ伝播するかとは無関係に、前記の事柄は事実である。数ある中で、E C R加工システム及びT C P（トランス結合プラズマ，transformer coupled plasma：商標）加工システムは商業的に簡単に入手できる。T C P（商標）システムは例えばカリフォルニア州フリーモントに所在するラム・リサーチ・コーポレイションから入手可能である。

前記のように、従来の任意の適切なプラズマ加工システムを効果的に使用できる。しかし、好ましい実施形態では、本発明をラム・リサーチ・コーポレイションから入手可能なT C P（商標）9 6 0 0 S E プラズマ反応装置内で使用する。図3は、基板3 5 0を含むT C P（商標）9 6 0 0 S E プラズマ反応装置の概略と、基板3 5 0を本発明のエッチ・プロセスに基づいてエッチングし、次いで、従来のポストエッチ工程で加工した後、この基板3 5 0からカットしたダイから形成した典型的な集積回路チップ3 5 2とを示す。説明を簡単にするために、I Cウェハを1つの例として使用しているが、本発明のエッチ・プロセスは任意の基板（例：フラット・ディスプレイ・パネル）のエッチングに適用できる点に注意する必要がある。

図3において、反応装置3 0 0はプラズマ加工チャンバ3 0 2を有する。電極（図3の例では、この電極はコイルからなる）3 0 3がチャンバ3 0 2の上側に配置されている。電圧をR Fジェネレータ3 0 5からマッチング・ネットワーク（図3における図示略）を通じてコイル3 0 3へ印加する。

チャンバ3 0 2内には、シャワー・ヘッド3 0 4が設けられている。シャワー・ヘッド3 0 4は、ガス状ソース材料（例：エッチャント・ソース・ガス）をシャワー・ヘッド3 0 4及び基板3 5 0の間のR F誘導プラズマ領域内へ放出するための複数の孔を有することが好ましい。ガス状ソース材料はチャンバ自体の壁に設けられたポートまたはチャンバ内に配置したガス・リング（環状をなし得る）からも放出し得る。基板3 5 0をチャンバ3 0 2内へ挿入し、かつ、チャック3 1 0上へ配置する。チャック3 1 0は第2の電極として機能する。そして、（一般的には、マッチング・ネットワークを通じて）高周波ジェネレータ3 2 0によってチャック3 1 0へバイアスをかけることが好ましい。

均一であって、かつ、反復可能なエッチング結果を保証するために、加工中の基板の温度を正確に制御するための伝熱媒体として機能させるべく、ヘリウム冷却ガスをチャック3

10

20

30

40

50

10及び基板350の間に加圧下で案内する。プラズマ・エッティング中、チャンバ302内の圧力はガスをポート360を通じて逃がすことによって制御できる。エッティングのための適切なチャンバ温度を維持するために、複数のヒーター（図解を簡単にするために図3では省略してある）が備えられ得る。接地への電気的パスを提供するために、一般的には、チャンバ302のチャンバ壁は接地される。

前記のように、エッティングされた導電機構内に傾斜エッチ・フットを意図的に形成することによって、酸化物層内の導電プラグ及びビアの壁の間に位置する接合層に対する損傷（この損傷は図2の機構206などの下に横たわる金属層内の機構の損傷を招来し得る）は、本発明の1つの態様に基づいて効果的に減少する。導電層が絶縁層と交わるポイントに位置するエッティングされた導電機構の傾斜エッチ・フットの更に大きなフットプリントにより、この傾斜エッチ・フットは、公差による不整合がエッティングされた導電機構及びその下に横たわる絶縁層内のビアの間に生じた場合にも、エッティングされた導電機構が更に完全にビアに重なる確率を効果的に増大する。従って、上に横たわる導電層をエッティングするために使用するエッチ・プロセスに対して、ビア内の接合層の環状リングの領域が露出される確率は効果的に最小限に抑制される。これに付随して、接合層及び下に横たわる導電層機構の少なくともいずれか一方が損傷する確率も最小限に抑制される。

導電機構傾斜エッチ・フットを意図的に形成する目立たないエッティング工程をバルク・エッチ工程後に実施することにより、本発明の導電層エッチ技術は接合層及び下に横たわる導電機構の少なくともいずれか一方を損傷する可能性を1つの実施形態において減少する。この傾斜エッチ・フットの意図的な導入は、エッチ機構全体にわたる異方性の更に高いエッティングの実現、即ち、エッティングされた機構の頂面から底面まで達する実質的に垂直な側壁の実現を試みる最近のエッチ・デザインにおける努力とは相反するものである。

前記のように、垂直エッチ側壁の実現を試みる現代のエッチ・プロセスにおいて一般的に望まれない傾斜エッチ・フットは、導電機構の頂部の拡大を要することなく本ケースにおける接合層の保護を効果的に高める。導電機構の頂部の寸法が変更されていないため、導電機構を上に横たわる導電層からエッティングによって作り出すことを促進すべくパターン化されたフォトレジスト機構は、既存のフォトレジスト・パターニング・ツールを使用することによって依然としてパターン化可能である。都合の良いことに、本発明の改善された歩留まりを達成するために、フォトレジスト・パターニング・ツール及びフォトレジスト・パターンのうちの少なくともいずれか一方の変更は必要ない。

本発明の特徴及び効果の説明を容易にするために、図4は本発明の1つの実施形態に基づく導電機構402を示す。この導電機構402は本発明のエッチ技術に基づいて形成された傾斜エッチ・フットを含む。図4において、基板100、下に横たわる導電層102、絶縁層104、バリア層108、プラグ114及び接合層116は図1及び図2に同じ符号で示す構造と実質的に類似している。その上に配置したままのパターン化されたフォトレジスト部分118と一緒に示す導電機構402は、傾斜フット部分404(a), 404(b)を含む。

図4に示すように、導電機構402の頂部406は、パターン化されたフォトレジスト部分118の幅によって決定される幅d1を有する。都合の良いことに、幅d1を有する機構を含むフォトレジスト・マスクは、従来のフォトレジスト・パターニング・ツール及びフォトレジスト・デザイン・ルールの少なくともいずれか一方を使用して形成できる。例えば、幅d1は導電機構402をその上に配置されるビアの直径より狭くできる（但し、これは必ずしも必要ではない）。高いエッチ速度及び実質的に垂直な側壁の少なくともいずれか一方を実現するために最適化したエッチ・プロセスを好ましくは使用して、バルクエッティングした導電層の部分を、頂部406は表している。

接合層116及び下に横たわる導電層102内の機構の少なくともいずれか一方に対する更に強力な保護を提供するために、バリア層108の少なくとも一部を有する導電機構402の底部408は、幅d1より効果的に広い幅d2を有する。底部408は頂部のエッチ・プロフィールと異なるエッチ・プロフィールを有することが好ましい。例えば、1つの実施形態において、頂部は実質的な異方性エッチ・プロフィールを有する一方、第2の

10

20

30

40

50

エッチ・プロフィールは更に大きな傾斜を有するフットプリント、即ち、更に拡大したフットプリントを有する。

1つの実施形態では、幅 d 2 は導電機構 4 0 2 をその上に配置するビアの直径より大きいことが好ましい。但し、幅 d 2 は互いに隣接する複数の機構を互いに短絡させる大きさを有してはならない。幅 d 1 , d 2 の正確な大きさはデバイス間及びプロセス間で異なり得る。図示するように、導電機構 4 0 2 がバターニング及び製造プロセスのうちの少なくともいすれか一方の公差などに起因して絶縁層 1 0 4 内のビアに対して整合していない場合でも、接合層 1 1 6 の保護は底部 4 0 8 ( 底部 4 0 8 の傾斜フット部分 4 0 4 ( a ) , 4 0 4 ( b ) を使用することにより ) によって更に効果的に提供できる。

前記のように、導電機構 4 0 2 の底部 4 0 8 はバリア層 1 0 8 の少なくとも一部を含み得る。勿論、導電層がバリア層を必要としない場合、底部 4 0 8 は導電層全体の一部に相当し得る。1つの実施形態では、バリア層 1 0 8 を提供する場合、頂部 4 0 6 を形成するバルク・エッチ工程は、相互接続層 1 1 0 及びバリア層 1 0 8 の間の界面へ到達する前に終了する。換言するならば、底部 4 0 8 は相互接続層 1 1 0 の少なくとも一部及びバリア層 1 0 8 の全体を含み得る。別の実施形態では、底部 4 0 8 はバリア層 1 0 8 のみを含む。即ち、頂部 4 0 6 を形成するバルク・エッチ工程は相互接続層 1 1 0 及びバリア層 1 0 8 の間の界面で終了する。更に別の実施形態では、底部 4 0 8 はバリア層 1 0 8 の一部のみを含み得る。即ち、頂部 4 0 6 を形成するバルク・エッチ工程は相互接続層 1 1 0 及びバリア層 1 0 8 の間の界面を越えてバリア層の少なくとも一部へ達するまで継続する。バルク・エッチの正確な深度 ( 及びこれに付随する底部 4 0 8 の正確な厚さ ) は、傾斜部分 4 0 2 ( a ) 及び 4 0 2 ( b ) の少なくともいすれか一方の所望の幅 d 2 及び傾斜度に基づくことを理解する必要がある。

1つの実施形態では、底部 4 0 8 を形成するエッティング工程 ( 即ち、バルク・エッチ工程後に実施するエッチ工程 ) は、单一の工程で実施し得る。別の実施形態では、底部 4 0 8 を形成するエッティング工程は複数の工程を含み得る。例えば、相互接続層 1 1 0 の残された部分を貫通してエッティングするために、1つのエッティング工程を使用可能である。次いで、バリア層 1 0 8 を貫通してエッティングし、かつ、バリア層を貫通するオーバーエッチ工程を実施するために、別のエッチ工程を使用し得る。オーバーエッチは当業者に周知の概念であり、導電材料及びバリア材料の少なくともいすれか一方の痕跡を、同材料の存在が望ましくない領域、即ち、保護フォトレジストのない領域から実質的に除去することを保証するために実施するエッティングを指す。更に別の例として、相互接続層 1 1 0 の残された部分を貫通してエッティングするために、1つのエッティング工程を使用し、バリア層 1 0 8 を貫通してエッティングするために、別のエッティング工程を使用し、バリア層を貫通するオーバーエッチ工程を実施するために、更に別のエッチ工程を使用し得る。

本発明の1つの態様に基づき、導電機構 4 0 2 の傾斜エッチ・フットを、バルク・エッチ・レシピに類似するレシピを使用して形成する ( 但し、傾斜エッチ・フットを形成するために、バルク・エッチ・レシピの1つ以上のパラメータを変更して使用する ) 。例えば、エッチ・フットの形成を促進するために、バルク・エッチ・レシピのエッチ速度を低下させ得る。学説に固執することを望むわけではないが、導電層エッティングは保護フォトレジスト機構 ( 例 : 図 4 のフォトレジスト機構 1 1 8 ) を時間の経過とともに侵食すると信じられている。エッティング中、侵食されたフォトレジスト材料の一部は、形成された導電機構 ( 例 : 導電機構 4 0 2 ) の側壁に沿って重合する。導電機構 4 0 2 全体にわたる垂直エッチ速度を低下させた場合、エッティング中の導電機構の側壁と、部分的にエッティングされた導電層の表面とが交差するコーナーなどで堆積する更に長い時間を、ポリマーは有する。この側方におけるポリマー堆積が増大することにより、この領域内の導電層は更に強力に保護される。この結果、エッティングを継続する間、導電層は更に低い異方性でエッティングされる。即ち、エッティングを導電層全体にわたって下方へ継続して行う間に、導電エッチ・フットが形成される。

これに代わるメカニズムまたは追加メカニズムとして、基板を載置した電極の温度が低下され得る。前と同様に学説に固執することを望むわけではないが、電極の温度 ( 及びこれ

10

20

30

40

50

に付随してエッティング中の基板の温度も)を低下させることにより、ポリマー粒子が基板上に凝縮または凝結する速度が増大すると信じられている。ポリマー凝縮の増大によって、ポリマー堆積物が増大する。これによって、エッチ速度の低下に関連して前述した方法に類似する方法でのエッチ・フットの形成が促進される。1つの実施形態では、例えばバックサイド・ヘリウム冷却圧力を増大することによって、基板の温度を低下させ、これによって、加工中の基板及びチャックの間の伝熱速度を増大する。

更に別のメカニズムまたは追加メカニズムとして、エッチ・フットの形成を促進するためには、基板を載置した電極のDCバイアスを増大し得る。この下側電極のバイアスを増大することにより、エッチのスペッタリング・コンポーネントが増大し、これによって、フォトレジスト侵食速度及びポリマー堆積速度がそれぞれ増大する。

図5は傾斜エッチ・フットを形成する本発明の1つの実施形態に基づくエッチ技術を示す。ステップ502では、上に横たわる導電層(例:図1の導電層106)の少なくとも一部をバルク・エッチ・レシピを使用してエッティングする。前記のように、基板スループットを増大するために、バルク・エッチ・レシピは導電層全体にわたるエッチ速度を最大限にすべく調製することが好ましい。これに加えて、またはこれに代えて、幾つかのケースでは、バルク・エッチ工程は実質的な異方性エッチ機構、即ち、実質的に垂直なエッチ側壁を形成するように調製され得る。ステップ504では、傾斜エッチ・フットを形成すべく調製したレシピを使用して、導電層の残された部分をエッティングする。1つの例では、相互接続層(例:図1の相互接続層110)を貫いてエッティングする前に、ステップ502を終了する。別の例では、ステップ502は、相互接続層((例:図1の相互接続層110)を実質的に貫いてエッティングするために使用され得る。そして、ステップ504はバリア層(例:図1のバリア層108)を貫いてエッティングするために使用され得るとともに、オーバーエッチ工程として使用され得る。

1つの実施形態では、ステップ504で使用されるレシピは、ステップ502で使用されるレシピの1つ以上のバルク・エッチ・パラメータを変更してあるが、ステップ502で使用されるレシピと実質的に同じである。前記のように、導電層全体にわたるエッチ速度が低減されたとき、基板が載置された電極の温度が低減されたとき、及び下側電極のDCバイアスが増大されたときのうちの少なくともいずれか1つにおいて、傾斜エッチ・フットが形成される。傾斜エッチ・フットを実現するために、他のパラメータをステップ502のバルク・エッチで使用するパラメータから変更しても良い。

前記のように、傾斜エッチ・フットを形成するために調製したエッティング工程は1つ以上の独立したエッティング工程を含み得る。例えば、バルク・エッチを完了した後、相互接続層(例:図1の相互接続層110)の残された部分を貫いてエッティングするために、別のエッティング・レシピを使用し得る。更に、別のバリア・エッチ・レシピを、バリア層(例:図1のバリア層108)を貫いてエッティングするために使用するとともに、オーバーエッチ・レシピとして使用し得る。図6はこの実施形態を示しており、図5の傾斜エッチ・フット・エッチ・ステップ504を2つの独立したエッティング・ステップ602, 604で達成している。図6において、ステップ602及びステップ604の少なくともいずれか一方は傾斜エッチ・フットを形成するために調製されたエッチ工程に相当することが好ましい。

別の実施形態では、オーバーエッチ工程を実施するために、別のエッチ・レシピを使用し得る。図7は別の実施形態を示しており、図5の傾斜エッチ・フット・エッチ・ステップ504を3つの独立したステップによって達成している。ステップ702では、傾斜エッチ・フットを形成すべく調製したレシピを好ましくは使用して、相互接続層の残された部分(図5のステップ502の後で残された部分)をエッティングする。

ステップ704では、バリア・エッチ・レシピを使用してバリア層(例:図1のバリア層108)がエッティングされる。ステップ702によって傾斜エッチ・フットが既に形成されていることがある。このため、ステップ704で使用されるバリア・エッチ・レシピを、傾斜エッチ機構をバリア層内に形成すべく調製することは常に必要ではない。比較的薄いバリア層を有する積層体の場合、これは特に事実である。しかし、1つの実施形態では

10

20

30

40

50

、傾斜エッチ・フットを更に拡大するか、または実質的に維持するように、ステップ 704で使用されるバリア・エッチ・レシピを調製し得る。ステップ 706では、導電材料の全ての痕跡を、導電材料の存在が望ましくない領域（例：エッティングされた複数の機構の間の領域及びオープン・フィールド領域）から除去するために、別のオーバーエッチ・レシピが使用され得る。

エッティングによって設けられた導電機構上における傾斜エッチ・フットの形成に適した複数のパラメータの大まかな範囲を以下に詳述する。これらのパラメータの範囲は  $T_i$ 、 $T_{iN}$  または  $T_{iW}$  を含むバリア層を有し得るアルミニウム合金導電層のエッティングに適する。フッ素化学のケースでは、任意のバリア層は例えば  $W$  または  $T_{iW}$  を含み得る。パラメータの適切な範囲は T C P 9 6 0 0 S E プラズマ反応装置内の 100 mm ウェハ及び 200 mm ウェハに関連して以下に開示する。しかし、ここに開示するエッチ技術を他の大きさのウェハ及び他のエッチ反応装置（プラズマを使用するか否かは関係ない）の少なくともいずれか一方へ適合させることを当業者が実施できるようにするガイドラインとして、これらの範囲を使用する必要がある。

10

#### T C P 9 6 0 0 S E プラズマ反応装置内で、塩素化学を使用してエッティングした 100 mm ウェハ

塩素化学を使用してエッティングした 100 mm ウェハの場合、エッチャント・ソース・ガス（標準立方センチメートル毎分）の総流量は、約 40 標準立方センチメートル毎分 (sccm) 及び約 150 sccm の間であり、より好ましくは約 40 sccm 及び約 200 sccm の間であり、好ましくは約 70 sccm である。BCl<sub>3</sub>に対するCl<sub>2</sub>の比率は約 0.25 及び約 2.0 の間であり、より好ましくは約 0.5 及び約 1.3 の間であり、好ましくは約 1.0 である。

20

T C P 電力は約 200 WATT (W) 及び約 500 W の間であり、より好ましくは約 350 W 及び約 450 W の間であり、好ましくは約 475 W である。底部電極電力に対する T C P 電力の比率は約 1.15 及び約 3.0 の間であり、より好ましくは約 1.2 及び約 1.45 の間であり、最も好ましくは約 1.35 である。

ミリトリ (mT) で表されるチャンバ内部の圧力は、約 4 mT 及び約 25 mT の間であり、より好ましくは約 8 mT 及び約 15 mT の間であり、最も好ましくは約 10 mT である。トル (T) で表されるバックサイド・ヘリウム冷却圧力は 0 トル (T) 及び約 20 T の間であり、より好ましくは約 8 T 及び約 12 T の間であり、最も好ましくは約 10 T である。

30

更に、ポリマー堆積促進ガスを提供し得る。1つの実施形態では、窒素 (N<sub>2</sub>) を約 3 sccm 及び約 25 sccm の間で、より好ましくは約 5 sccm 及び約 10 sccm の間で、最も好ましくは約 5 sccm で供給する。これに加えて、またはこれに代えて、酸素 (O<sub>2</sub>) を約 3 sccm 及び約 15 sccm の間で、より好ましくは約 3 sccm 及び約 5 sccm の間で、最も好ましくは約 4 sccm で任意にて提供し得る。更に、前記のガスに加えて、または前記のガスに代えて、過フッ化炭化水素ガス（例：任意のフレオン・ガス）を約 3 sccm 及び約 15 sccm の間で、より好ましくは約 3 sccm 及び約 10 sccm の間で、最も好ましくは約 5 sccm で加え得る。更に、前記のガスに加えて、または前記のガスに代えて、炭化水素ガス（例：メタン）を約 3 sccm 及び約 15 sccm の間で、より好ましくは約 3 sccm 及び約 10 sccm の間で、最も好ましくは約 4 sccm で加え得る。

40

#### T C P 9 6 0 0 S E プラズマ反応装置内で、フッ素化学を使用してエッティングした 100 mm ウェハ

1つの実施形態では、塩素化学の代わりに、または塩素化学に加えて、フッ素化学を使用し得る。フッ素化学を使用する場合、塩素化学に関連して述べたパラメータ（例：チャンバ圧力、バックサイド・ヘリウム冷却圧力及びポリマー堆積促進ガス）を適用し得る。しかし、フッ素化学のための R F 電力は約 200 W 及び約 600 W の間であり、より好ましくは約 400 W 及び約 500 W の間であり、最も好ましくは約 500 W である。

底部電極電力に対する T C P 電力の比率は、約 2 及び約 2.4 の間であり、より好ましくは

50

約2.5及び約6の間であり、最も好ましくは約3である。エッチャント・ガスの総量(sccm)は約30sccm及び約100sccmの間であり、より好ましくは約40sccm及び約60sccmの間であり、最も好ましくは約50sccmである。BC1<sub>3</sub>に対するSF<sub>6</sub>の比率は約0.5及び約4.0の間であり、より好ましくは約1.0及び約3.0の間であり、最も好ましくは約1.2である。塩素(Cl<sub>2</sub>)をガス総流量の約1%及び約60%の間で、より好ましくは約10%及び約30%の間で、好ましくは約20%で任意にて加え得る。ポリマー堆積促進ガスをさらに提供し得る。例えば、窒素(N<sub>2</sub>)を約5sccm及び約10sccmの間で、より好ましくは約5sccmで提供し得る。

#### T C P 9 6 0 0 S E プラズマ反応装置内で、塩素化学を使用してエッチングした200mmウェハ

1つの実施形態では、TCPのRF電力は約250W及び約700Wの間であり、より好ましくは約400W及び約550Wの間であり、最も好ましくは約450Wである。底部電極電力に対するTCP電極電力の比率は約1.15及び約3.0の間であり、より好ましくは約1.2及び約1.45の間であり、最も好ましくは約1.2である。

エッチャント・ソース・ガスの総量は約40sccm及び約400sccmの間であり、より好ましくは約40sccm及び約200sccmの間であり、最も好ましくは約100sccmである。BC1<sub>3</sub>に対するCl<sub>2</sub>の比率は約0.25及び約2.0の間であり、より好ましくは約0.5及び約1.3の間であり、最も好ましくは約0.6である。チャンバ内部圧力は約4ミリトル(mT)及び約25mTの間であり、より好ましくは約8mT及び約15mTの間であり、最も好ましくは約10mTである。バックサイド・ヘリウム冷却圧力は約0T及び約20Tの間であり、より好ましくは約8T及び約12Tの間であり、最も好ましくは約12Tである。

更に、ポリマー堆積促進ガスを提供し得る。例えば、窒素(N<sub>2</sub>)を約5sccm及び約10sccmの間で、より好ましくは約5sccmで提供し得る。

#### T C P 9 6 0 0 S E プラズマ反応装置内で、フッ素化学を使用してエッチングした200mmウェハ

100mmウェハの例同様に、塩素化学エッチ工程の代わりに、または塩素化学エッチ工程に加えて、フッ素化学を使用し得る。フッ素化学のケースでは、200mmウェハ塩素エッチの例に関連する特定のパラメータ(例:チャンバ内部圧力及びバックサイド・ヘリウム冷却圧力)を使用し得る。但し、TCPのRF電力は約200W及び約700Wの間であり、より好ましくは約400W及び約600Wの間であり、最も好ましくは約600Wである。底部電極電力に対するTCP電力の比率は約2及び約2.4の間であり、より好ましくは約2.5及び約6の間であり、最も好ましくは約3である。

エッチャント・ソース・ガスの総量は約50sccm及び約150sccmの間であり、より好ましくは約60sccm及び約100sccmの間であり、最も好ましくは約80sccmである。BC1<sub>3</sub>に対するSF<sub>6</sub>の比率は約0.05及び約4.0の間であり、より好ましくは約1.0及び約3.0の間であり、最も好ましくは約2.2である。Cl<sub>2</sub>を約1sccm及び約25sccmの間で、より好ましくは約1sccm及び約15sccmの間で、最も好ましくは約10sccmで任意にて加え得る。

更に、ポリマー堆積促進ガスを提供し得る。例えば、窒素(N<sub>2</sub>)を約3sccm及び約25sccmの間で、より好ましくは約5sccm及び約15sccmの間で、最も好ましくは約10sccmで提供し得る。これに代えて、またはこれに加えて、酸素(O<sub>2</sub>)を約3sccm及び約15sccmの間で、より好ましくは約5sccm及び約10sccmの間で加え得る。他のポリマー堆積促進ガスに代えて、または他のポリマー堆積促進ガスに加えて使用できる任意のフレオン及び炭化水素に関する同様の数値範囲が存在する(例:約3sccm及び約15sccmの間、より好ましくは約5sccm及び約10sccmの間)。

フッ素化学のケースでは、チャンバ圧力は約4ミリトル(mT)及び約25mTの間であり、より好ましくは約8mT及び約15mTの間であり、最も好ましくは約12mTであ

10

20

30

40

50

る。バックサイド・ヘリウム冷却圧力は約 0 T 及び約 20 T の間であり、より好ましくは約 8 T 及び約 12 T の間であり、最も好ましくは約 12 T である。

#### 例

##### 例 1

サンプル・エッチでは、バリア層としての 1,500 オングストロームの TiW と、5,500 オングストロームの Al-Si-Cu を含む上に横たわる相互接続層と、250 オングストロームの TiN を含む上に横たわる反射防止コーティング (ARC) 層とを有する 200 mm ウェハを TCP9600SE プラズマ反応装置内で加工した。バルク・エッチに使用したケミストリは Cl<sub>2</sub> 及び BC<sub>l</sub><sub>3</sub> を含む。傾斜エッチ・フット・エッチ工程に使用したケミストリは SF<sub>6</sub> 及び N<sub>2</sub> をさらに含む。

安定化工程では、チャンバ内の圧力は約 12 ミリトルであり、バックサイド・ヘリウム圧力は約 5 トルである。Cl<sub>2</sub> エッチャント・ソース・ガス及び BC<sub>l</sub><sub>3</sub> エッチャント・ソース・ガスはそれぞれ約 80 sccm 及び約 40 sccm で流した。圧力 (チャンバ圧力及びバックサイド冷却圧力の少なくともいずれか一方) 及びプラズマ反応装置内のガス流量状態が安定化した際、安定化工程は終了する。

突破及びアルミニウム・バルク・エッチ工程では、バックサイド・ヘリウム冷却圧力 (約 5 トル) 同様に、反応装置・チャンバ内の圧力 (約 12 ミリトル) を同じに維持した。頂部 TCP 電極電力は約 500 W であり、底部電極電力は約 350 W である。Cl<sub>2</sub> ガス流量及び BC<sub>l</sub><sub>3</sub> ガス流量はそれぞれ約 80 sccm 及び約 40 sccm である。例えば 261 nm 光エミッションを監視することによって、アルミニウム・エンドポイントが検出された際、この突破及びアルミニウム・バルク・エッチ工程は終了する。

次いで、同じチャンバ内部圧力 (約 12 ミリトル) 及び同じ RF 電力 (TCP 電力及び底部電極電力はそれぞれ約 500 W 及び約 350 W) を使用して、アルミニウム・オーバーエッチ及びクリーンアップ工程を実施する。このアルミニウム・オーバーエッチ / クリーンアップ工程における Cl<sub>2</sub> ガス流量及び BC<sub>l</sub><sub>3</sub> ガス流量はそれぞれ約 50 sccm である。バックサイド・ヘリウム冷却圧力は約 12 トルである。オーバーエッチ工程は 80 % オーバーエッチである。即ち、このオーバーエッチ・エッチング工程の継続時間は突破及びアルミニウム・バルク・エッチ工程の継続時間の約 80 % である。

傾斜エッチ・フットを TiW バリア層内に形成するために、RF 電力、Cl<sub>2</sub> ガス流量及び BC<sub>l</sub><sub>3</sub> ガス流量を変更する。例えば、傾斜エッチ・フット・エッチ工程では、TCP 電力及び底部電極電力はそれぞれ約 600 W 及び 200 W である。Cl<sub>2</sub> ガス流量及び BC<sub>l</sub><sub>3</sub> ガス流量はそれぞれ約 10 sccm 及び約 25 sccm である。更に、SF<sub>6</sub> ガス流量を約 55 sccm で提供する。ポリマー堆積促進 N<sub>2</sub> を約 10 sccm で流す。バックサイド・ヘリウム冷却圧力を約 12 トルに維持し、チャンバ内部の圧力は約 12 ミリトルとする。例えば 703 nm 光エミッションを監視することによって、タンゲステン・エンドポイントを検出した際、傾斜エッチ・フット・エッチ工程は終了する。

TiW オーバーエッチ及びクリーンアップ・エッチ (100 % オーバーエッチ) を実施する。この TiW オーバーエッチ工程では、内部チャンバ圧力を約 12 ミリトルに維持し、バックサイド・ヘリウム冷却圧力を約 5 トルとする。TCP 電極及び底部電極の RF 電力をそれぞれ約 600 W 及び約 200 W で同じに維持する。実質的に、塩素ガスを TiW オーバーエッチ工程で全く流さない。しかし、約 25 sccm の BC<sub>l</sub><sub>3</sub> 及び約 80 sccm の SF<sub>6</sub> を TiW オーバーエッチ工程中にチャンバ内へ流す。

##### 例 2

別のサンプル・エッチでは、バリア層としての 1,000 オングストロームの TiN と、7,500 オングストロームの Al-Si-Cu を含む上に横たわる相互接続層と、250 オングストロームの TiN を含む上に横たわる反射防止コーティング (ARC) 層とを有する 200 mm ウェハを、TCP9600SE プラズマ反応装置内で加工した。

安定化工程では、内部チャンバ圧力は約 10 ミリトルである。Cl<sub>2</sub> 流量及び BC<sub>l</sub><sub>3</sub> 流量はそれぞれ約 90 sccm 及び約 60 sccm である。バックサイド・ヘリウム圧力は約 5 トルである。圧力 (チャンバ圧力及びバックサイド冷却圧力の少なくともいずれか一方

10

20

30

40

50

) 及びプラズマ反応装置内のガス流量状態が安定化した際、安定化工程は終了する。A R C 層を突破し、かつアルミニウム・バルク・エッチを実施するために、別のエッチ工程を使用する。この突破及びアルミニウム・バルク・エッチ工程では、チャンバ内の圧力は約 10 ミリトルである。頂部 T C P 電極及び底部電極の R F 電力はそれぞれ約 500 W 及び 350 W である。塩素エッチャント・ソース・ガス及び B C l<sub>3</sub> エッチャント・ソース・ガスをそれぞれ約 90 sccm 及び約 60 sccm で流す。バックサイド・ヘリウム冷却圧力は約 5 トルである。アルミニウム・エッチ工程のエンドポイントを検出した際、突破及びアルミニウム・バルク・エッチは終了する。

別のエッチ工程では、傾斜エッチ・フットを形成し、かつ、オーバーエッチ工程を実施するため、エッチ・レシピを使用する。この工程では、チャンバ内の圧力は約 10 ミリトルである。T C P 電極及び底部電極の R F 電力の設定はそれぞれ約 450 W 及び約 375 W である。C l<sub>2</sub> エッチャント・ソース・ガス流量及び B C l<sub>3</sub> エッチャント・ソース・ガス流量はそれぞれ約 40 sccm 及び約 60 sccm である。バックサイド・ヘリウム冷却圧力は約 12 トルである。100% オーバーエッチを達成した際、このエッチ工程は終了する。

以上、本発明を幾つかの好ましい実施形態に関連して詳述したが、本発明の範囲に属する置換物、改良物及び等価物が存在する。本発明の方法及び装置を実現する多くの別の方

10 法が存在し得ることに注意する必要がある。従って、本発明の趣旨及び範囲に属する全ての置換物、改良物及び等価物を含むことを以下の請求の範囲は意図している。

【図 1】

FIG. 1

【図 2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

---

フロントページの続き

(72)発明者 アーネット・デビッド・アール .

アメリカ合衆国 カリフォルニア州 94536 フリモント , フリモント・ブルバード , 3776

7 アパートメント #21

(72)発明者 ムッサー・ジェフリー・ブイ .

アメリカ合衆国 アイダホ州 83705 ボイス , イー . · イーストゲイト , 3105

審査官 長谷山 健

(56)参考文献 特開平03-204935 (JP, A)

特開昭56-006454 (JP, A)

特開平05-326722 (JP, A)

特開平06-342850 (JP, A)

特開平06-151382 (JP, A)

特開平07-130744 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

H01L 21/3213

H01L 21/3065