(51) **International Patent Classification:**

*H04B 10/69* (2013.01)

(21) **International Application Number:**

PCT/EP2014/058937

(22) **International Filing Date:**

30 April 2014 (30.04.2014)

(25) **Filing Language:** English

(26) **Publication Language:** English

(30) **Priority Data:**

13166092.0 30 April 2013 (30.04.2013) EP

(71) **Applicant:** SILICON LINE GMBH [DE/DE]; Elsenheimerstr. 48 / II, 80687 Muenchen (DE).

(72) **Inventors:** HIDRI, Ols; c/o SILICON LINE GMBH, Elsenheimerstr. 48 / II, 80687 Muenchen (DE). GROEPL, Martin; Ostrachstr. 7, 87527 Sonthofen Oberallgäu (DE). HOELTKE, Holger; Am Bluetenanger 54C, 80995 Muenchen (DE).

(74) **Agents:** HOFMANN, Andreas et al.; Sendlinger Str. 2 / III, 80331 Muenchen, P.O. Box/Postfach 330211, 80062 Muenchen (DE).

(81) **Designated States** (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) **Designated States** (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

**Published:**

— with international search report (Art. 21(3))

**Published:**

— with international search report (Art. 21(3))

**(54) Title: CIRCUIT ARRANGEMENT AND METHOD FOR RECEIVING OPTICAL SIGNALS**

Fig. 3

**(57) Abstract:** Circuit arrangement (CR; CR') for receiving multilevel optical signals (SI) from at least one optical guide (GU), said multilevel signals resulting from superposing a high speed data signal and a low speed data signal, said circuit arrangement (CR; CR') comprising: • - at least one light-receiving component (PD) for converting the optical signals (SI) into electrical current signals (I<sub>pp</sub>), • - at least one transimpedance amplifier (TA), being provided with the electrical current signals (I<sub>pp</sub>) from the light-receiving component (PD), • - at least one automatic gain controller (AG) for controlling the gain or transimpedance (R) of the transimpedance amplifier (TA), in particular in order to keep the amplitude of the output (V<sub>out</sub>- data-analog) of the transimpedance amplifier (TA) to a desired, for example constant, level for different levels of the electrical current signals (I<sub>PD</sub>), • - at least one integrator (IN) in a feedback path (FP), said integrator (IN) generating a control signal (V<sub>int</sub>), • - at least one voltage-controlled current source (CS), being provided with the control signal (V<sub>int</sub>) from the integrator (IN), • - at least one limiter (LI) acting as a comparator and generating in its output a logic level for positive or negative voltages in its input, • - at least one second transimpedance amplifier (TA2) arranged in parallel to the transimpedance amplifier (TA), and • - at least one automatic offset controller (AO) for setting the voltage (V<sub>offset</sub>) for the second transimpedance amplifier (TA2).

## CIRCUIT ARRANGEMENT AND METHOD FOR RECEIVING OPTICAL SIGNALS

### Technical field

The present invention basically relates to the technical field of optical transmission of signals.

5 More particularly, the present invention relates to a circuit arrangement for receiving optical signals according to the preamble of claim 1 as well as to a corresponding method according to the preamble of claim 14.

10 Within the scope of the present invention, the term optical or light is understood not only as the range of electromagnetic radiation visible to the eye, extending in a wavelength range from about 380 nanometers to about 780 nanometers (which corresponds to a frequency of about 789 terahertz down to about 385 terahertz).

15 Rather, the term light or light-emitting is understood as the entire electromagnetic wavelength or frequency spectrum, including the spectrum not visible to the eye, in particular the I[nfra]R[ed] range (wavelength range up to about 2,000 nanometers or frequency range down to about 150 terahertz), for example a wavelength of about 850 nanometers or a frequency of about 350 terahertz.

### Background of the present invention

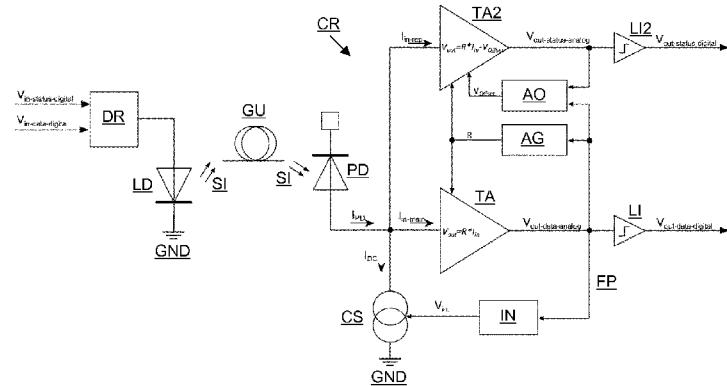

20 A typical optical communication system (cf. Fig. 1: typical optical link; Fig. 2: typical optical link signalling) comprises three components:

- a light-emitting element LD, for example a laser diode, together with its driver DR, which converts the electrical data logic levels to optical power logic levels;

- a light guide GU, for example a fibre, which carries the light; and

- a light-receiving element PD, for example a photodetector, such as a photodiode, together with a transimpedance amplifier TA, which senses the light at the end of the light guide GU and converts the light back to an electrical signal.

30 Such a system typically transmits two-level electrical data pattern  $V_{\text{in-data-digital}}$  and recovers a replica two-level electrical data pattern  $V_{\text{out-data-digital}}$  at the receiver side. Light (optical) power levels  $P_1$  and  $P_0$  (cf. Fig. 2) injected into the light guide GU correspond to each electrical level  $V_{\text{HIGH}}$  and  $V_{\text{LOW}}$ . It follows that, at the receiver side, two different light power levels arrive at the input of the light-receiving element PD. These two different light power levels generate two different current levels, namely  $I_1$  and  $I_0$ .

35 The current signal  $I_{\text{PD}}$  generated at the light-receiving element PD has to be converted to a voltage

signal. The current generated by the light-receiving element PD is converted to voltage by the transimpedance amplifier TA, wherein  $V_{\text{out-data-analog}} = R * I_{\text{in-main}}$ , with R being the gain or transimpedance of the transimpedance amplifier TA.

5 An integrator IN in the feedback path FP generates a control signal  $V_{\text{int}}$  in order to subtract the average input current coming from the light-receiving element PD. This is done in order to generate the zero crossing in the input of a limiter LI. The limiter LI acts as a comparator which generates in its output a  $V_{\text{HIGH}}$  ( $V_{\text{LOW}}$ ) logic level for positive (negative) voltages in its input. The automatic gain control block AG controls the transimpedance amplifier gain R in order to keep the amplitude  $V_{\text{out-data-analog}}$  to a 10 desired level (for example constant) for different  $I_{\text{PD}}$  current levels that might occur as input to the transimpedance amplifier TA.

15 In case another low speed signal is to be transmitted from the transmitter side to the receiver side, a status change in the transmitter side could be transmitted to the receiver side. This could be for example a change from EIOS (Electrical Idle Ordered Set - a type of data link layer packet) state to EIEOS (Electric Idle Exit Ordered Set) state in the PCI Express standard.

20 Another optical link could be dedicated to the new signal. However, this is very costly because extra components and extra power is required. Also in some cases, dedicating a complete extra optical link might not be an option at all.

25 If the slow speed signal is transmitted over the same optical link, which means that the high-speed signals and the low-speed signals share the same optical components (physical medium), a third optical power level  $P_2$  different from  $P_1$  and from  $P_0$  is to be transmitted in order to be able to distinguish between the two signals, making a multi-level signalling necessary.

#### **Disclosure of the present invention: object, solution, advantages**

30 Starting from the above-explained disadvantages and technical problems as well as taking the outlined prior art into account, the object of the present invention is to further develop a circuit arrangement of the above-mentioned type and a method of the above-mentioned type in such a way that a multilevel optical link can be provided.

35 This object is achieved by a circuit arrangement with the features of claim 1 as well as by a method with the features of claim 14. Advantageous embodiments and expedient further developments of the present invention are characterized in the dependent claims.

According to the present invention, a circuit arrangement for receiving optical signals from at least one optical guide comprises:

40 - at least one light-receiving component for converting the optical signals into electrical current signals,

- at least one transimpedance amplifier, being provided with the electrical current signals from the light-receiving component,

- at least one automatic gain controller for controlling the gain or transimpedance of the transimpedance amplifier, in particular in order to keep the amplitude of the output of the transimpedance amplifier to a desired, for example constant, level for different levels of the electrical current signals,

- at least one integrator in a feedback path, said integrator generating a control signal,

- at least one voltage-controlled current source, being provided with the control signal from the integrator,

- at least one limiter acting as a comparator and generating in its output a logic level for positive or negative voltages in its input,

- at least one second transimpedance amplifier arranged in parallel to the transimpedance amplifier, and

- at least one automatic offset controller for setting the voltage for the second transimpedance amplifier.

Correspondingly, the circuit arrangement works according to the following method for receiving optical signals from at least one optical guide, comprising the steps of:

- converting the optical signals into electrical current signals by means of at least one light-receiving component;

- provided the electrical current signals from the light-receiving component to at least one transimpedance amplifier;

- controlling the gain or transimpedance of the transimpedance amplifier by means of at least one automatic gain controller, in particular in order to keep the amplitude of the output of the transimpedance amplifier to a desired, for example constant, level for different levels of the electrical current signals;

- generating a control signal by means of at least one integrator in a feedback path;

- providing the control signal from the integrator to at least one voltage-controlled current source;

- generating in the output of at least one limiter a logic level for positive or negative voltages in its input; and

setting the voltage for at least one second transimpedance amplifier by means of at least one automatic offset controller, said second transimpedance amplifier being arranged in parallel to the transimpedance amplifier.

According to an advantageous embodiment of the present invention, at least one second limiter is assigned to the second transimpedance amplifier and to the automatic offset controller.

According to an expedient embodiment of the present invention, the second transimpedance amplifier

- corresponds to the transimpedance amplifier, or

- is a scaled version of the transimpedance amplifier.

According to a favoured embodiment of the present invention, the automatic gain controller sets the same gain or same transimpedance for both the transimpedance amplifier and the second transimpedance amplifier by sensing the amplitude of the output of the transimpedance amplifier.

5

According to a preferred embodiment of the present invention, at least one peak detector circuit is provided for sensing the amplitude of the output of the transimpedance amplifier.

According to an advantageous embodiment of the present invention, the peak detector circuit is part of 10 the automatic gain control or is shared between the automatic gain controller and the automatic offset controller.

According to an expedient embodiment of the present invention, the amplitude of the output of the transimpedance amplifier is provided to the input of the automatic offset controller.

15

According to a favoured embodiment of the present invention, the transimpedance amplifier is at least one multi-stage amplifier.

20

According to a preferred embodiment of the present invention, the second transimpedance amplifier is at least one multi-stage amplifier.

According to an advantageous embodiment of the present invention, a short is arranged between the output node of the first stage of the transimpedance amplifier and the output node of the first stage of the second transimpedance amplifier.

25

According to an expedient embodiment of the present invention, the light-receiving component is at least one photodetector, in particular at least one photodiode.

According to a favoured embodiment of the present invention, the optical guide is at least one fibre.

30

According to a preferred embodiment of the present invention, the end of the optical guide, which is not assigned to the light-receiving component, is assigned to at least one light-emitting component, which is preceded by at least one driver for converting electrical data logic levels into the optical signals.

35

The present invention finally relates to the use of at least one circuit arrangement according to the type presented hereinbefore and/or of the method according to the type presented hereinbefore for the optical transmission of data signals and of status signals.

40

**Brief explanation of the drawings**

As has already been discussed hereinbefore, there are various possibilities for configuring and further developing the teaching of the present invention in an advantageous manner. For this purpose, on the one hand reference is made to the claims subordinated to claim 1 and on the other hand, further embodiments, features and advantages of the present invention are explained in detail hereinafter inter alia with reference to the exemplary embodiments illustrated by Fig. 3 to Fig. 5.

It is shown in:

10 Fig. 1 in a schematic diagram an example of a circuit arrangement according to the prior art operating according to the method of the prior art;

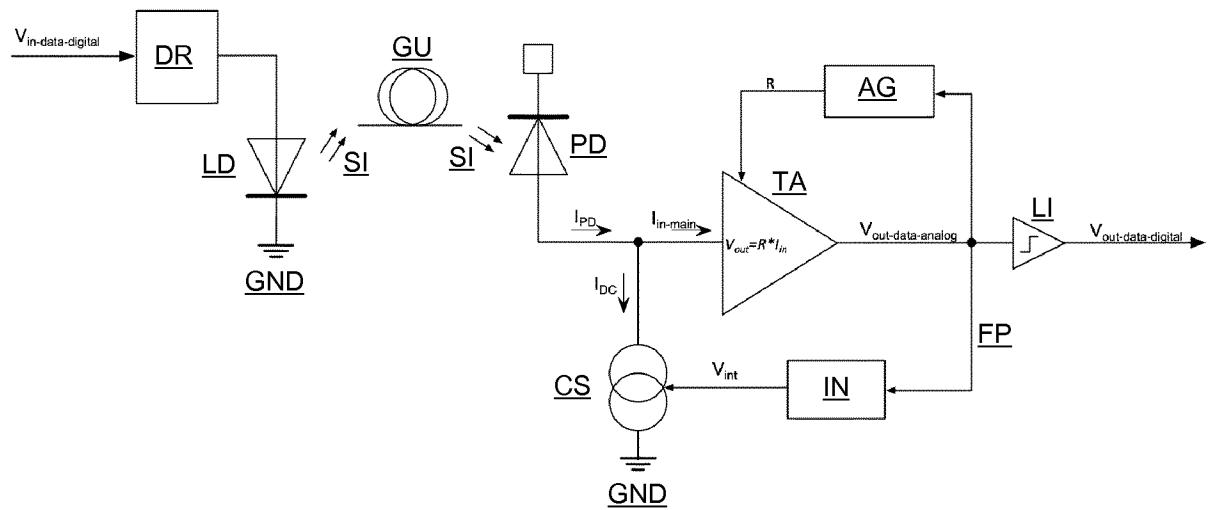

15 Fig. 2 in a comparative diagram an example of the prior art signalling of the circuit arrangement of Fig. 1;

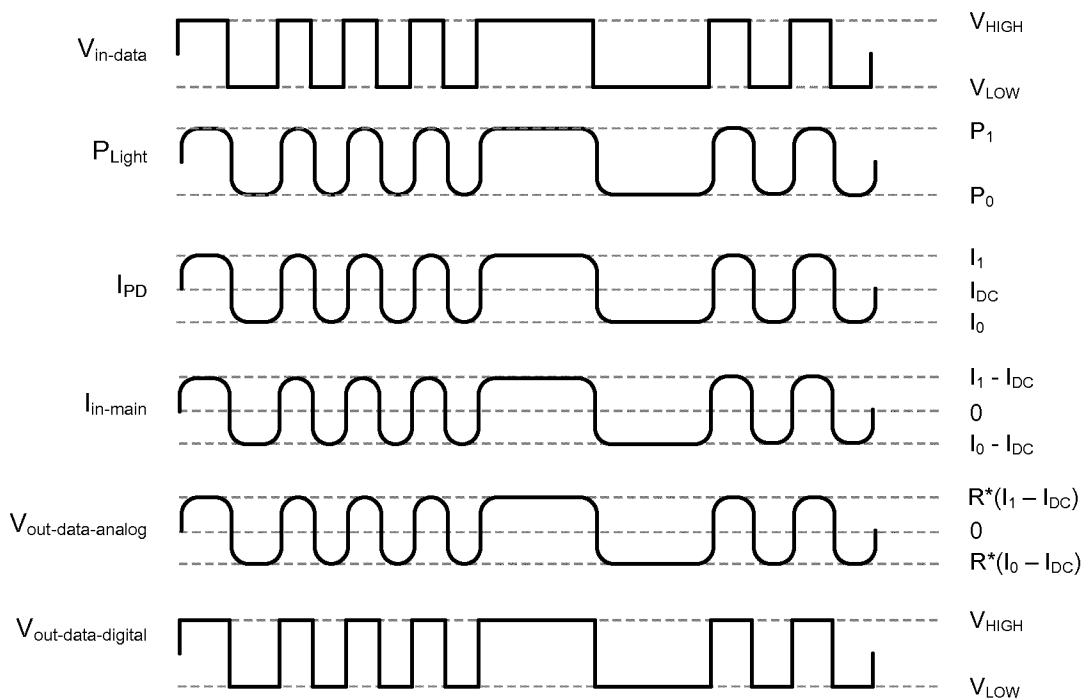

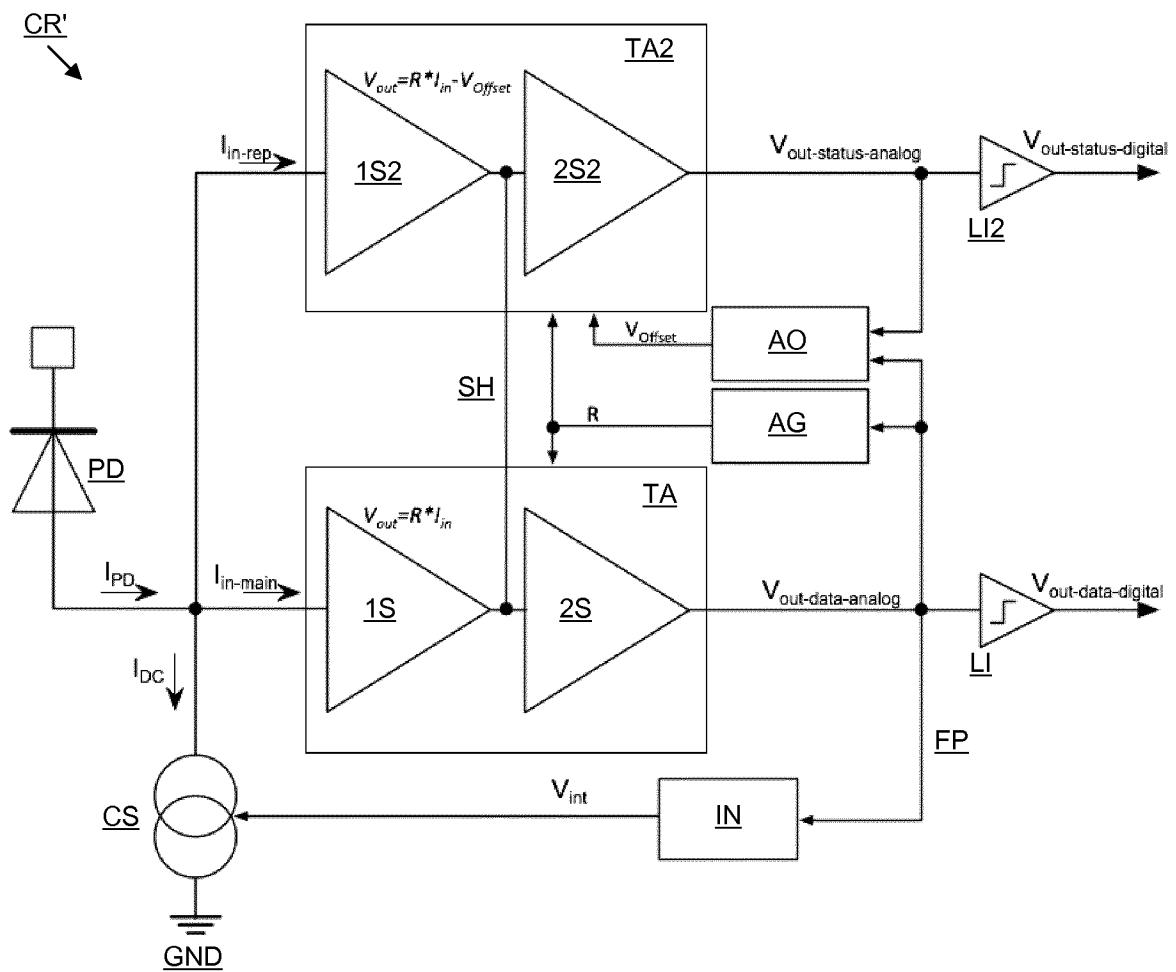

Fig. 3 in a schematic diagram a first exemplary embodiment of a circuit arrangement according to the present invention operating according to the method of the present invention;

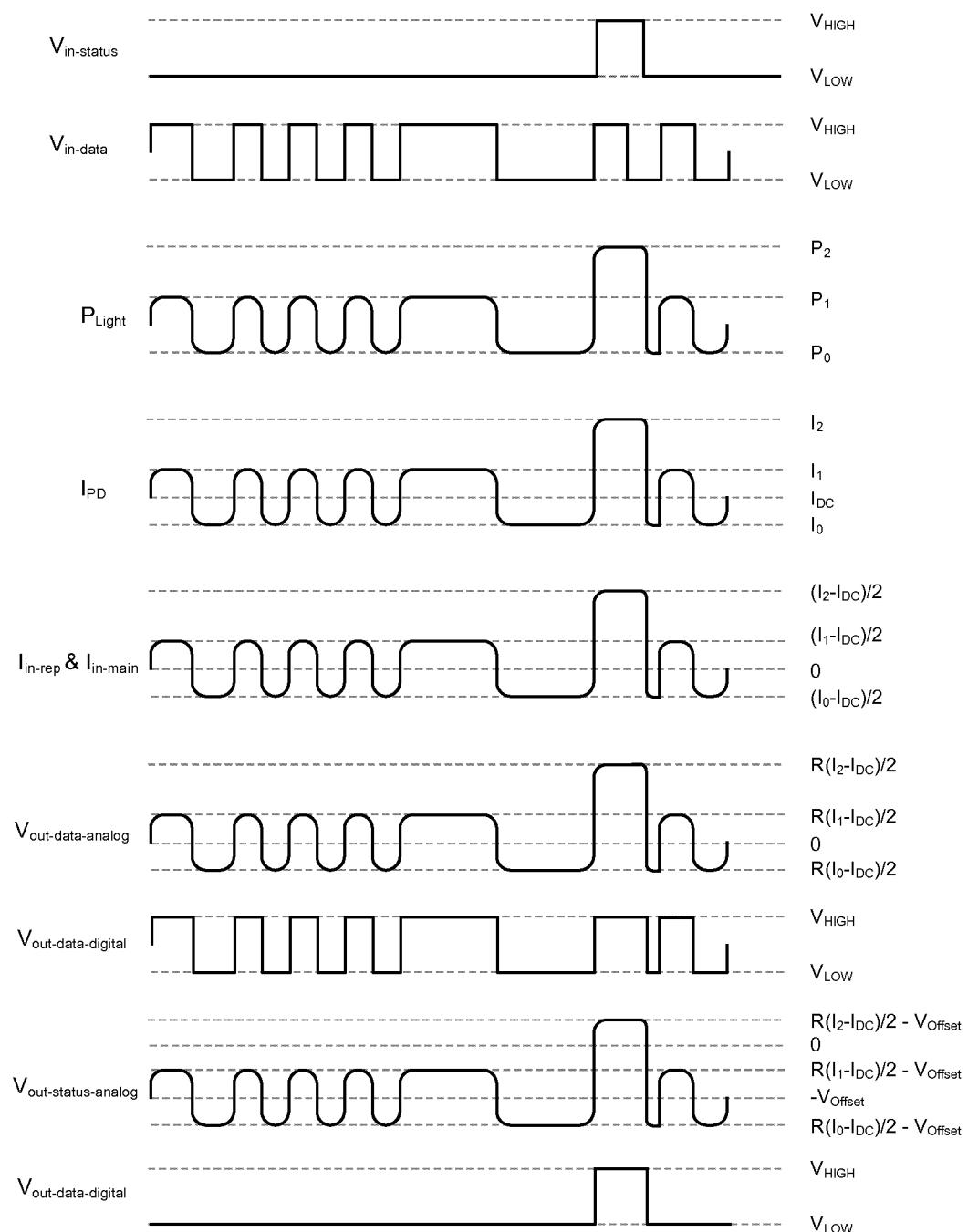

20 Fig. 4 in a comparative diagram an exemplary embodiment of the signalling of the circuit arrangement of Fig. 3; and

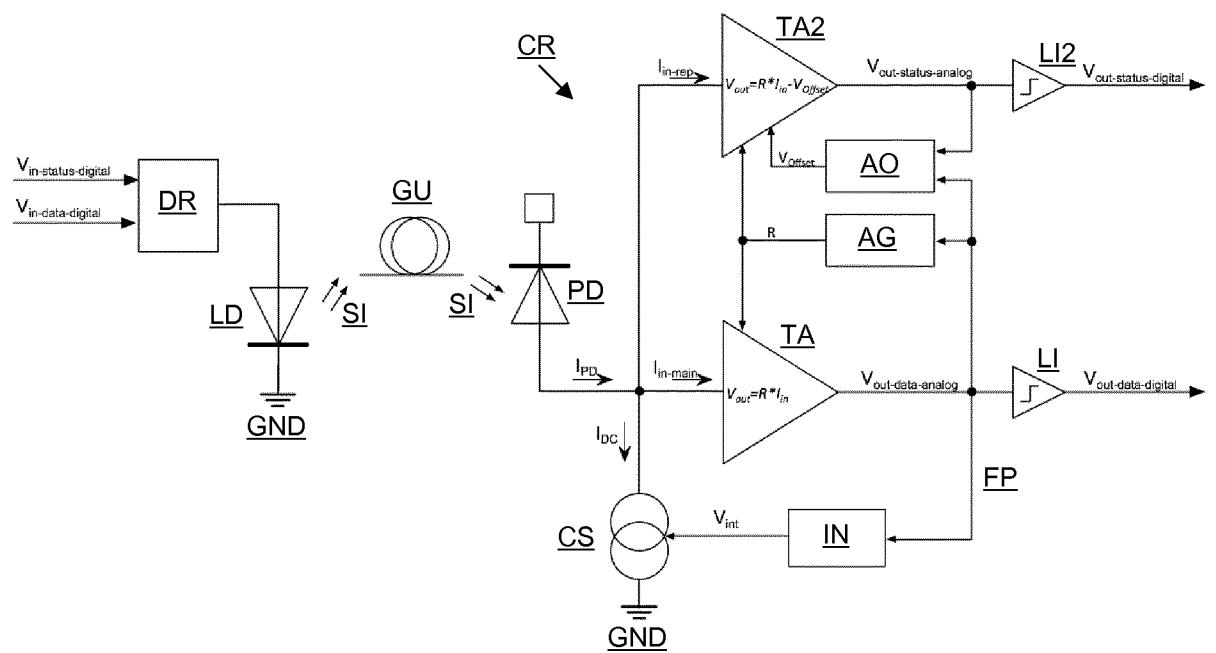

Fig. 5 in a schematic diagram a second exemplary embodiment of a circuit arrangement according to the present invention operating according to the method of the present invention.

25 The same or similar embodiments, elements or features are provided with identical reference numerals in Fig. 1 to Fig. 5.

#### **Best mode of embodying the present invention**

30 In order to avoid unnecessary repetitions, the following explanations regarding the embodiments, features and advantages of the present invention – unless specified otherwise – relate both - to the first exemplary embodiment of a circuit arrangement CR shown in Fig. 3, Fig. 4 and - to the second exemplary embodiment of a circuit arrangement CR' shown in Fig. 5.

35 A typical optical communication system (cf. Fig. 1: typical optical link; Fig. 2: typical optical link signalling) has been explained above in the chapter "Background of the present invention". In order to avoid unnecessary repetitions, these explanations in the chapter "Background of the present invention" are incorporated by reference in the present chapter "Best mode of embodying the present invention" with regard to the present invention; in particular,

40 - the explanations in the chapter "Background of the present invention" with regard to Fig. 1 are

incorporated by reference in the present chapter "Best mode of embodying the present invention" with regard to Fig. 3 and/or to Fig. 5, and

- the explanations in the chapter "Background of the present invention" with regard to Fig. 2 are incorporated by reference in the present chapter "Best mode of embodying the present invention" with regard to Fig. 4.

5

According to the present invention and compared to the typical optical link as shown in Fig. 1, a signal  $V_{in-status-digital}$  is inputted on the transmitter side.  $V_{in-status-digital}$  is a slow signal comprising short pulses widely spaced-in-time. The transition rate of  $V_{in-status-digital}$  is significantly low compared to the 10 transition rate of  $V_{in-data-digital}$ .

10

$V_{in-status-digital}$ , together with the high speed signal  $V_{in-data-digital}$ , modulates the transmitted optical signal as 15 shown in the signal listing in Fig. 4 (= optical link signalling according to a preferred embodiment of the present invention). The optical power  $P_2$  is chosen to be higher than  $P_1$ , such that the received currents  $I_2$  and  $I_1$  fulfill the relation  $I_2 \geq 2*I_1$ .

15

The second transimpedance amplifier TA2 can be a copy of the transimpedance amplifier TA, or the 20 second transimpedance amplifier TA2 can be an exactly scaled version of the transimpedance amplifier TA. The automatic gain control block AG sets the same gain or same transimpedance R for both the transimpedance amplifier TA and the second transimpedance amplifier TA2 by sensing only the  $V_{out-data-analog}$  amplitude with of a peak detector circuit, which can be part of the automatic gain control AG or can be shared between the automatic gain control AG and an automatic offset control AO.

25

The automatic offset control AO sets the voltage  $V_{offset}$  for the second transimpedance amplifier TA2; for example,  $V_{offset}$  can be  $R*(I_1-I_0)/2$ . The value of  $V_{offset}$  is independent of  $I_2$ , and the information about its value is extracted only from  $V_{out-data-analog}$ . For example,  $V_{offset} = R*(I_1-I_0)/2$  is achieved by setting  $V_{offset}$  double the amplitude.

30

Again the amplitude  $V_{out-data-analog}$  can be measured with a peak detector circuit. The peak detector circuit can be part of the automatic offset control AO or can be shared between the automatic offset control AO and the automatic gain control AG. To close the feed-back loop for the  $V_{offset}$  control,  $V_{out-status-analog}$  is used as the feedback signal for the automatic offset control block AO because the  $V_{out-status-analog}$  average value is  $-V_{offset}$ . The averaging circuit is part of the automatic offset control block AO.

35

As to the link operation, during an initial phase, only the high speed  $V_{in-data-digital}$  signal is transmitted. The  $V_{in-status-digital}$  signal is kept low during this phase. Also, during this initial phase, the automatic gain control AG and the automatic offset control AO outputs settle to their final value. The time constant of these two loops is significantly lower than the time distance between the two consecutive pulses on 40 the  $V_{in-status-digital}$  signal.

Only after this first initial phase the  $V_{in\text{-status-digital}}$  signal can be transmitted. When the  $V_{in\text{-status-digital}}$  signal is low, the  $V_{out\text{-data-digital}}$  signal follows the  $V_{in\text{-data-digital}}$  signal. When the  $V_{in\text{-status-digital}}$  signal is high, the optical power transmitted is always  $P_2$ , independently of the value of the  $V_{in\text{-data-digital}}$  signal. As a consequence,  $V_{out\text{-data-digital}}$  will be high independently of the value of  $V_{in\text{-data-digital}}$ . The  $V_{out\text{-status-digital}}$ , as desired, goes high as well.

As to an improvement of the signal-to-noise ratio on the receiver side, in case and the second transimpedance amplifier TA2 are multistage amplifiers, in order to improve the signal-to-noise ratio, a short between the output nodes of the first stage of the first transimpedance amplifier TA and of the first stage of the second transimpedance amplifier TA2 can be provided, as depicted in Fig. 5.

Such shorting does not have any effect on the desired signal. Only the total noise power drops compared to a non-shorted version. Hence an improvement of the signal-to-noise ratio can be achieved in the receiver.

By means of the above-proposed arrangement as well as method, the slow speed signal can be reliably transmitted by sharing the same physical optical link and using multilevel signalling.

#### List of reference numerals

|                      |                                                                                          |

|----------------------|------------------------------------------------------------------------------------------|

| AG                   | automatic gain controller or automatic transimpedance controller                         |

| AO                   | automatic offset controller                                                              |

| CR                   | circuit arrangement (= first embodiment; cf. Fig. 3)                                     |

| CR'                  | circuit arrangement (= second embodiment; cf. Fig. 5)                                    |

| CS                   | current source, in particular voltage-controlled current source                          |

| DR                   | driver                                                                                   |

| FP                   | feedback path                                                                            |

| GND                  | reference potential, in particular earth potential or ground potential or zero potential |

| GU                   | optical guide, in particular fibre                                                       |

| IN                   | integrator                                                                               |

| $I_{DC}$             | input of current source CS                                                               |

| $I_{in\text{-main}}$ | input of transimpedance amplifier TA                                                     |

| $I_{in\text{-rep}}$  | input of second transimpedance amplifier TA2                                             |

| $I_{PD}$             | electrical current signal                                                                |

| LD                   | light-emitting component, in particular laser diode                                      |

| LI                   | limiter, in particular first limiter                                                     |

| LI2                  | second limiter                                                                           |

| PD                   | light-receiving component, in particular photodetector, for example photodiode           |

| R                    | gain of transimpedance amplifier TA or transimpedance of transimpedance amplifier TA     |

|                                 |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| SH                              | short                                                                  |

| SI                              | optical signal                                                         |

| TA                              | transimpedance amplifier, in particular first transimpedance amplifier |

| TA2                             | second transimpedance amplifier                                        |

| $V_{\text{in-data-digital}}$    | input, in particular data input, of driver DR                          |

| $V_{\text{in-status-digital}}$  | input, in particular status input, of driver DR                        |

| $V_{\text{int}}$                | control signal or output of integrator IN                              |

| $V_{\text{offset}}$             | voltage for second transimpedance amplifier TA2                        |

| $V_{\text{out-data-analog}}$    | output of transimpedance amplifier TA                                  |

| $V_{\text{out-data-digital}}$   | output of limiter LI                                                   |

| $V_{\text{out-status-analog}}$  | output of second transimpedance amplifier TA2                          |

| $V_{\text{out-status-digital}}$ | output of second limiter LI2                                           |

| 1S                              | first stage of transimpedance amplifier TA                             |

| 1S2                             | first stage of second transimpedance amplifier TA2                     |

| 2S                              | further or second stage of transimpedance amplifier TA                 |

| 2S2                             | further or second stage of second transimpedance amplifier TA2         |

**Claims**

1. A circuit arrangement (CR; CR') for receiving optical signals (SI) from at least one optical guide (GU), said circuit arrangement (CR; CR') comprising:

- at least one light-receiving component (PD) for converting the optical signals (SI) into electrical current signals ( $I_{PD}$ ),

- at least one transimpedance amplifier (TA), being provided with the electrical current signals ( $I_{PD}$ ) from the light-receiving component (PD),

- at least one automatic gain controller (AG) for controlling the gain or transimpedance (R) of the transimpedance amplifier (TA), in particular in order to keep the amplitude of the output ( $V_{out-data-analog}$ ) of the transimpedance amplifier (TA) to a desired, for example constant, level for different levels of the electrical current signals ( $I_{PD}$ ),

- at least one integrator (IN) in a feedback path (FP), said integrator (IN) generating a control signal ( $V_{int}$ ),

- at least one voltage-controlled current source (CS), being provided with the control signal ( $V_{int}$ ) from the integrator (IN),

- at least one limiter (LI) acting as a comparator and generating in its output a logic level for positive or negative voltages in its input,

- characterized by**

- at least one second transimpedance amplifier (TA2) arranged in parallel to the transimpedance amplifier (TA), and

- at least one automatic offset controller (AO) for setting the voltage ( $V_{offset}$ ) for the second transimpedance amplifier (TA2).

2. The circuit arrangement according to claim 1, further comprising at least one second limiter (LI2) being assigned to the second transimpedance amplifier (TA2) and to the automatic offset controller (AO).

3. The circuit arrangement according to claim 1 or 2, wherein the second transimpedance amplifier (TA2)

- corresponds to the transimpedance amplifier (TA), or

- is a scaled version of the transimpedance amplifier (TA).

4. The circuit arrangement according to at least one of claims 1 to 3, wherein the automatic gain controller (AG) sets the same gain or same transimpedance (R) for both the transimpedance amplifier (TA) and the second transimpedance amplifier (TA2) by sensing the amplitude of the output ( $V_{out-data-analog}$ ) of the transimpedance amplifier (TA).

5. The circuit arrangement according to claim 4, further comprising at least one peak detector circuit for sensing the amplitude of the output ( $V_{out-data-analog}$ ) of the transimpedance amplifier (TA).

6. The circuit arrangement according to claim 5, wherein the peak detector circuit is part of the automatic gain control (AG) or is shared between the automatic gain controller (AG) and the automatic offset controller (AO).

5

7. The circuit arrangement according to at least one of claims 4 to 6, wherein the amplitude of the output ( $V_{out-data-analog}$ ) of the transimpedance amplifier (TA) is provided to the input of the automatic offset controller (AO).

10

8. The circuit arrangement (CR') according to at least one of claims 1 to 7, wherein the transimpedance amplifier (TA) is at least one multi-stage amplifier.

9. The circuit arrangement (CR') according to at least one of claims 1 to 8, wherein the second transimpedance amplifier (TA2) is at least one multi-stage amplifier.

15

10. The circuit arrangement (CR') according to claim 8 and 9, wherein a short (SH) is arranged between the output node of the first stage (1S) of the transimpedance amplifier (TA) and the output node of the first stage (1S2) of the second transimpedance amplifier (TA2).

20

11. The circuit arrangement according to at least one of claims 1 to 10, wherein the light-receiving component (PD) is at least one photodetector, in particular at least one photodiode.

12. The circuit arrangement according to at least one of claims 1 to 11, wherein the optical guide (GU) is at least one fibre.

25

13. The circuit arrangement according to at least one of claims 1 to 12, wherein the end of the optical guide (GU), which is not assigned to the light-receiving component (PD), is assigned to at least one light-emitting component (LD), which is preceded by at least one driver (DR) for converting electrical data logic levels into the optical signals (SI).

30

14. Method for receiving optical signals (SI) from at least one optical guide (GU), comprising the steps of:

- converting the optical signals (SI) into electrical current signals ( $I_{PD}$ ) by means of at least one light-receiving component (PD);

- provided the electrical current signals ( $I_{PD}$ ) from the light-receiving component (PD) to at least one transimpedance amplifier (TA);

- controlling the gain or transimpedance (R) of the transimpedance amplifier (TA) by means of at least one automatic gain controller (AG), in particular in order to keep the amplitude of the output ( $V_{out-data-analog}$ ) of the transimpedance amplifier (TA) to a desired, for example constant, level for different levels of the electrical current signals ( $I_{PD}$ );

- generating a control signal ( $V_{int}$ ) by means of at least one integrator (IN) in a feedback path (FP);

- providing the control signal ( $V_{int}$ ) from the integrator (IN) to at least one voltage-controlled current source (CS);

- generating in the output of at least one limiter (LI) a logic level for positive or negative voltages in

5 its input,

**c h a r a c t e r i z e d b y**

setting the voltage ( $V_{offset}$ ) for at least one second transimpedance amplifier (TA2) by means of at least one automatic offset controller (AO), said second transimpedance amplifier (TA2) being arranged in parallel to the transimpedance amplifier (TA).

10

15. Use of at least one circuit arrangement (CR; CR') according to at least one of claims 1 to 13 and/or of the method according to claim 14 for the optical transmission of data signals and of status signals.

**Fig. 1** (= prior art)

**Fig. 2** (= prior art)

**Fig. 3**

**Fig. 4**

**Fig. 5**

# INTERNATIONAL SEARCH REPORT

International application No

PCT/EP2014/058937

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H04B10/69

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H04B

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data, INSPEC

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                       | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 4 972 408 A (LE BIHAN HERVE [FR] ET AL)<br>20 November 1990 (1990-11-20)<br>the whole document<br>-----                                                                                                                                                               | 1-15                  |

| A         | EP 0 203 757 A2 (INT STANDARD ELECTRIC CORP [US]) 3 December 1986 (1986-12-03)<br>the whole document<br>-----                                                                                                                                                            | 1-15                  |

| A         | ATEF M ET AL: "An Automatic Gain Control Front-End Optical Receiver for Multi-Level Data Transmission", NORCHIP, 2008, IEEE, PISCATAWAY, NJ, USA, 16 November 2008 (2008-11-16), pages 57-60, XP031401107, ISBN: 978-1-4244-2492-4<br>the whole document<br>-----<br>-/- | 1-15                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

"A" document defining the general state of the art which is not considered to be of particular relevance

"E" earlier application or patent but published on or after the international filing date

"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

"O" document referring to an oral disclosure, use, exhibition or other means

"P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

25 July 2014

04/08/2014

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Rolan Cisneros, E

## INTERNATIONAL SEARCH REPORT

|                              |

|------------------------------|

| International application No |

| PCT/EP2014/058937            |

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                   | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 4 763 326 A (KRICK WOLFGANG [DE])<br>9 August 1988 (1988-08-09)<br>the whole document<br>-----                                                                                    | 1-15                  |

| A         | US 2008/309407 A1 (NAKAMURA MAKOTO [JP] ET<br>AL) 18 December 2008 (2008-12-18)<br>abstract<br>paragraphs [0114] - [0123]<br>paragraphs [0185] - [0197]<br>figures 1, 2, 18<br>----- | 1-15                  |

| A         | JP 2009 049488 A (NIPPON TELEGRAPH &<br>TELEPHONE; NTT ELECTRONICS CORP)<br>5 March 2009 (2009-03-05)<br>abstract; figure 6<br>-----                                                 | 1-15                  |

| A         | US 2011/135315 A1 (LIU FRANKIE Y [US] ET<br>AL) 9 June 2011 (2011-06-09)<br>paragraphs [0045] - [0047]<br>figures 2A, 2B<br>-----                                                    | 1-15                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/EP2014/058937

| Patent document cited in search report |    | Publication date |                                                    | Patent family member(s)                                                                                                    |  | Publication date                                                                                                           |

|----------------------------------------|----|------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------|

| US 4972408                             | A  | 20-11-1990       | CA<br>DE<br>DE<br>EP<br>ES<br>FR<br>JP<br>JP<br>US | 1303137 C<br>68904976 D1<br>68904976 T2<br>0339641 A1<br>2039740 T3<br>2630871 A1<br>H071882 B2<br>H0217735 A<br>4972408 A |  | 09-06-1992<br>01-04-1993<br>17-06-1993<br>02-11-1989<br>01-10-1993<br>03-11-1989<br>11-01-1995<br>22-01-1990<br>20-11-1990 |

| EP 0203757                             | A2 | 03-12-1986       | EP<br>ES<br>GB<br>JP<br>US                         | 0203757 A2<br>8707055 A1<br>2175480 A<br>S61267426 A<br>4716563 A                                                          |  | 03-12-1986<br>16-09-1987<br>26-11-1986<br>27-11-1986<br>29-12-1987                                                         |

| US 4763326                             | A  | 09-08-1988       | DE<br>EP<br>JP<br>US                               | 3544393 A1<br>0227164 A2<br>S62144431 A<br>4763326 A                                                                       |  | 19-06-1987<br>01-07-1987<br>27-06-1987<br>09-08-1988                                                                       |

| US 2008309407                          | A1 | 18-12-2008       | US<br>WO                                           | 2008309407 A1<br>2006013893 A1                                                                                             |  | 18-12-2008<br>09-02-2006                                                                                                   |

| JP 2009049488                          | A  | 05-03-2009       | JP<br>JP                                           | 4927664 B2<br>2009049488 A                                                                                                 |  | 09-05-2012<br>05-03-2009                                                                                                   |

| US 2011135315                          | A1 | 09-06-2011       |                                                    | NONE                                                                                                                       |  |                                                                                                                            |