(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3892160号

(P3892160)

(45) 発行日 平成19年3月14日(2007.3.14)

(24) 登録日 平成18年12月15日(2006.12.15)

(51) Int.C1.

F 1

|             |             |                  |      |      |

|-------------|-------------|------------------|------|------|

| <b>HO3F</b> | <b>3/19</b> | <b>(2006.01)</b> | HO3F | 3/19 |

| <b>HO3F</b> | <b>3/45</b> | <b>(2006.01)</b> | HO3F | 3/45 |

| <b>HO3D</b> | <b>7/14</b> | <b>(2006.01)</b> | HO3D | 7/14 |

A

C

請求項の数 4 (全 8 頁)

|              |                         |

|--------------|-------------------------|

| (21) 出願番号    | 特願平10-323403            |

| (22) 出願日     | 平成10年11月13日(1998.11.13) |

| (65) 公開番号    | 特開平11-251845            |

| (43) 公開日     | 平成11年9月17日(1999.9.17)   |

| 審査請求日        | 平成15年7月18日(2003.7.18)   |

| (31) 優先権主張番号 | 9724136.8               |

| (32) 優先日     | 平成9年11月14日(1997.11.14)  |

| (33) 優先権主張国  | 英国(GB)                  |

| (31) 優先権主張番号 | 9816128.4               |

| (32) 優先日     | 平成10年7月24日(1998.7.24)   |

| (33) 優先権主張国  | 英国(GB)                  |

|           |                                                                                                                                  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 592201151<br>ザーリング セミコンダクター リミテッド<br>Zarlink Semiconductor Limited<br>イギリス エヌエヌ2 2キューダブリュー<br>ー ウィルトシャー スウィンドン チェ<br>ニー マナ(番地なし) |

| (74) 代理人  | 100079980<br>弁理士 飯田 伸行                                                                                                           |

| (72) 発明者  | ジェフリー マイケル ホンド スミス<br>イギリス, エヌエヌ2 3ビーュー, ウィ<br>ルトシア, スウィンドン, ホイットワース<br>ロード 227, ウォーカー ハウス<br>6                                  |

最終頁に続く

(54) 【発明の名称】低電圧増幅器

## (57) 【特許請求の範囲】

## 【請求項1】

増幅段に共通に印加されるシングルエンド入力の信号に応ずる少なくとも2つの増幅段での構成を一つ以上有して、差動電流出力信号を選択的に供給する増幅器であって、それぞれの増幅段で、

第1のトランジスタがベース接地構成であり、前記シングルエンド入力からの信号を受信するための接続を成し、

第2のトランジスタがエミッタ接地構成であり、前記シングルエンド入力からの信号を受信するための接続を成し、

前記シングルエンド入力に第1のインダクタを介して接続する、少なくとも2つの前記第1のトランジスタのエミッタ電極と、

負極電源供給ラインに第2のインダクタを介して接続する、少なくとも2つの前記第2のトランジスタのベース電極と、

を具備し、

前記第1及び第2のトランジスタのコレクタ電極から差動出力が取り出されることを特徴とする低電圧増幅器。

## 【請求項2】

前記低電圧増幅器が、さらに、それぞれの増幅段に関連するバイアス手段を有し、いずれかの増幅段の前記第1のトランジスタおよび前記第2のトランジスタのベースエミッタ接続のフォワードバイアスであって、いずれかの前記バイアス手段を選択する請求

項1記載の低電圧増幅器。

【請求項3】

低電圧増幅器に付帯するミキサ回路構成を有する請求項1記載の低電圧増幅器。

【請求項4】

前記ミキサ回路構成を有する無線電話機に組み込まれる請求項3記載の低電圧増幅器。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、低電圧増幅器に関し、特に無線電話機に用いられる低電圧増幅器に関する。

【0002】

【従来の技術】

従来、無線電話機における処理容量の大きい信号、特に低電圧増幅器やミキサ混合器等の携帯電話回路の需要が増加している一方で、それを動作させるために必要な電圧供給量は減少している。例えば、数年前では、4.8ボルトが一般的であったが、現在の携帯電話回路においては、2.7ボルトから作動するものである。

【0003】

通常、電流効率を得るために供給電圧を低くすることにより、供給ライン間に設けられる多数の能動素子を必要とするギルバートセルのような標準IC回路ミキサ構造で大容量の信号を制御するように形成することは難しい。これらの能動素子は、例えば、ミキサセルのトランジスタを動作するために必要な平衡形差動電流出力信号を供給するために、受信した不平衡形のシングルエンド無線周波数信号を増幅そして位相反転する手段を有する入力増幅器のトランジスタ等を含んでいる。

【0004】

また、シングルエンド入力信号を受信し、それぞれのコレクタ電極に差動電流出力信号を供給するためのベース接地トランジスタおよびエミッタ接地トランジスタにより構成されるトランスコンダクタンス増幅器がEP-A-0584870に開示されている。

【0005】

しかしながら、上記従来例に示される増幅器は、低電圧増幅器ではないという問題がある。

【0006】

本発明は、従来の増幅器よりも低電圧で動作するように改良され、転送特性を向上する低電圧増幅器を提供する。

【0007】

【課題を解決するための手段】

本発明の第1の実施形態によれば、シングルエンド入力から差動電流出力を供給する低電圧増幅器において、前記シングルエンド入力からの信号を受信するためにベース接地接続の第1のトランジスタおよびエミッタ接地接続される第2のトランジスタと、前記各トランジスタのベースエミッタ接続をフォワードバイアスするフォワードバイアス手段とを有し、前記第1のトランジスタおよび前記第2のトランジスタのそれぞれのコレクタ電極から前記差動電流出力信号が取り出されるものである。

【0008】

本発明の第2の実施形態によれば、シングルエンド入力から差動電流出力を供給する低電圧増幅器において、前記シングルエンド入力からの信号を受信するためにベース接地の第1のトランジスタとインピーダンスを介して接続し、前記シングルエンド入力からの信号を受信するためにエミッタ接地の第2のトランジスタとキャパシタを介して接続し、前記各トランジスタのベースエミッタ接続をフォワードバイアスするフォワードバイアス手段とを有し、前記第1のトランジスタおよび前記第2のトランジスタのそれぞれのコレクタ電極から前記差動電流出力信号が取り出されるものである。

【0009】

キャパシタは、エミッタ接地接続されるトランジスタのベース電圧と独立してベース接

10

20

30

40

50

地接続されるトランジスタのベース電圧を与えるように直流遮断として動作する。これは、上記增幅器において、より多くの電圧を許容し、従来のベース接地あるいはエミッタ接地されるトランジスタの増幅器のゲインを越え、改良された線型を提供するものである。

#### 【0010】

前記第1のトランジスタおよび前記第2のトランジスタのベースエミッタ接続をフォワードバイアスするフォワードバイアス手段は、電流ミラー構造に接続される第3のトランジスタにより構成されるものである。

#### 【0011】

本発明の第3の実施形態によれば、増幅段に共通に印加されるシングルエンド入力の信号に応じて、少なくとも2つの増幅段の構成を一つ以上有して、その増幅段から差動電流出力信号を選択的に供給する低電圧増幅器において、前記各増幅段は、前記シングルエンド入力からの信号受信を、インピーダンスを介してベース接地の第1のトランジスタに接続を成し、またその信号受信を、キャパシタを介してエミッタ接地の第2のトランジスタに接続を成し、共通の第1のインダクタにより前記シングルエンド入力に接続される少なくとも2つ以上の前記第1のトランジスタのエミッタ電極と、さらに、共通の第2のインダクタにより負極電圧供給ラインに接続される少なくとも2つ以上の前記第2のトランジスタのベース電極とを有し、前記増幅段の前記第1のトランジスタおよび、前記第2のトランジスタのそれぞれのコレクタ電極から増幅段における差動電流出力信号が取り出されるものである。

#### 【0012】

#### 【発明の実施の形態】

次に、添付図面を参照して本発明の実施形態である低電圧増幅器を詳細に説明する。

#### 【0013】

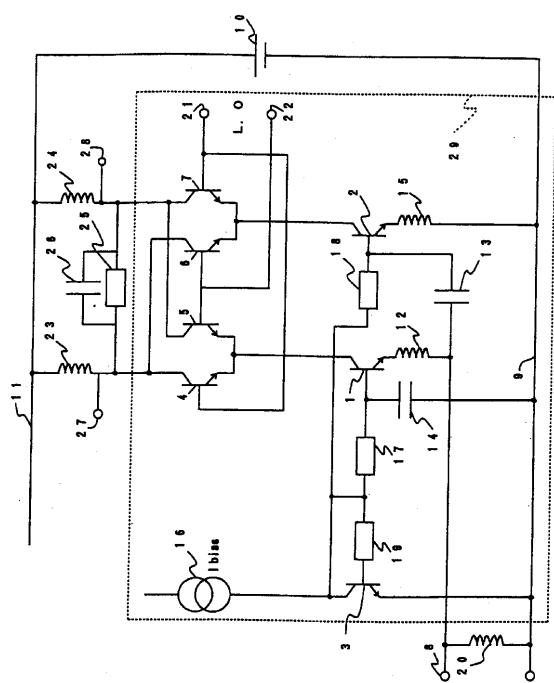

図1は、本発明の第1および第2の実施形態である低電圧増幅器を示す回路図である。

#### 【0014】

図1において、第1のトランジスタ1と、第2のトランジスタ2および第3のトランジスタ3とにより構成される低電圧増幅器は、トランジスタ4、5、6、7により構成されるミキサ段から入力段を形成する。無線周波数入力信号は、入力端子8と共に負極供給ライン9との間で印加される。例えば、2.7ボルトの電圧を供給するバッテリ10は、ライン9と正極供給ライン11との間に接続される。

#### 【0015】

入力端子8は、第1の第1のインダクタンス12を介して第1のトランジスタ1のエミッタ電極に接続され、第1のキャパシタ13を介して第2のトランジスタ2のベース電極に接続され、負極供給ライン9への無線周波数帰還回路は、第1のトランジスタ1のベース電極から第2のキャパシタ14を介して、第2のトランジスタ2のエミッタ電極から第2のインダクタ15を介して帰還するようにライン9に接続されて構成されている。

#### 【0016】

第1のトランジスタ1および第2のトランジスタ2における直流バイアスは、第1のトランジスタ1、第2のトランジスタ2、第3のトランジスタ3のそれぞれのベース電極に設けられた第1のバイアス抵抗17、第2のバイアス抵抗18および第3のバイアス抵抗19を介して、第3のトランジスタ3のコレクタ電極に接続されて形成される電流ミラー構造からなるバイアス手段により供給される。これらのバイアス抵抗値は、第1のトランジスタおよび第2のトランジスタを介する電流量の要求値を設定するために選択され、特定の電流ゲインを調節する。また、第2のバイアス抵抗18は、第1のキャパシタ13が第2のトランジスタ2のベース電極においてバイアスするための直流遮断を提供する一方、第2のトランジスタ2のベース電極において、無線周波数信号からバイアスの抵抗にて無線周波数を分離する方法も提供する。第1のトランジスタ1のエミッタ電流のライン9への直流電流帰還路は、インダクタまたは入力端子8とライン9との間のrfチョーク(高周波チョーク)20を介して供給され、このrfチョーク20のリアクタンスは、通常、入力端子8に供給されるネットワーク適合の設計に起因するものである。

10

20

30

40

50

## 【0017】

無線周波数信号において、第2のトランジスタ2がエミッタ接地接続される一方、第1のトランジスタ1がベース接地接続される。従って、入力端子8における無線周波数信号に応じて、差動電流出力信号が、トランジスタ4、5、6、7からなるミキサ段を駆動するため、第1のトランジスタ1および第2のトランジスタ2のコレクタ電極から供給される。これらの差動電流出力信号は、動作中に、端子21および端子22において印加される局部発振信号と混合され、ミキサトランジスタ4、5、6、7の交差接続されるコレクタ電極からの中間周波数出力信号が、負荷インダクタ23、24により構成される負荷回路と、抵抗25およびキャパシタ26により構成されるフィルタ回路とに印加される。中間周波数出力信号における差動電流出力信号は、第1の出力端子27および第2の出力端子28から取り出される。

## 【0018】

第1のインダクタ12および第2のインダクタ15は、誘導負帰還の尺度を提供するが、これは増幅器の動作において必要なものではない。第1のインダクタ12、第2のインダクタ15およびチョーク20をバイアスする目的は、直流短絡回路の構成に近づけようとするものである。バイアス手段である第3のトランジスタ3、電流源16、キャパシタ14、インダクタ15、インダクタ12が、ライン9の電位とほぼ同じくするように、第1のトランジスタ1および第2のトランジスタ2のエミッタ電位を設定することができる。従って、バイアス手段は、その他の回路構成にて使用可能な供給電圧の割合を最大限にすることができる、すなわち、ミキサ段および負荷回路において、最大電圧振幅が起こり得るものである。

## 【0019】

上述される増幅器とミキサは、点線により示されるICチップ29に形成される。チョーク20および負荷回路を構成する負荷インダクタンス23、24、抵抗25、キャパシタ26は、図示されるICチップ外に設けられる。

## 【0020】

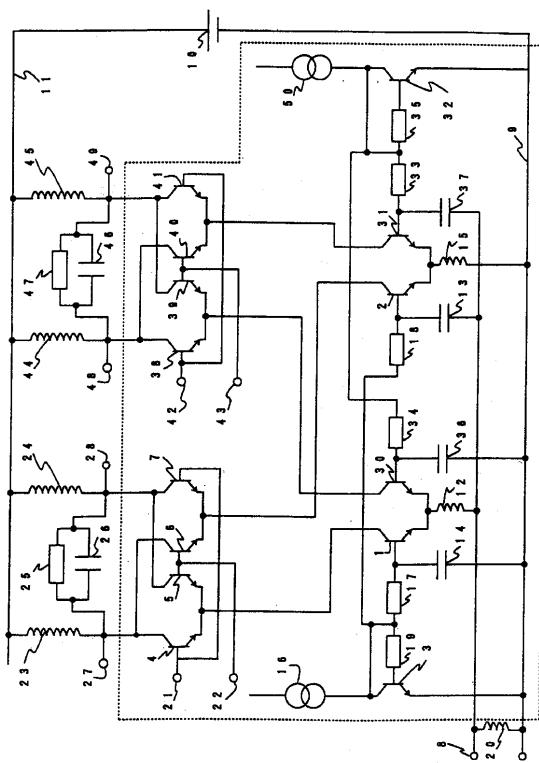

本発明の好適な実施形態ではあるが、第1のインダクタ12および第2のインダクタ15は、IC回路を形成するまでの広域を占めるものである。発明者は、これらのインダクタが、同様の集積回路により形成される1つ以上の増幅回路により用いられることを発見した。図2は、2つの増幅段を備える低電圧増幅器を示す。

## 【0021】

図2において、第1の増幅段は、図1に示される増幅器により構成され、同一要素に関しては同一符号を用いるものである。第1の増幅段は、図1に示されるように、トランジスタ4～7により形成されるミキサコアに接続されている。第2の増幅段は、バイアス抵抗34、33、35のそれぞれによりバイアスされる第4のトランジスタ30、第5のトランジスタ31、第6のトランジスタ32により形成される。第4のトランジスタ30のベース電極は、第3のキャパシタ36を介して負極供給ライン9に接続され、第5のトランジスタ31のベース電極は、第4のキャパシタ37を介して入力端子8に接続されている。第4のトランジスタ30のエミッタ電極は、第1のトランジスタ1と共有するよう第1のインダクタ12を介して入力端子8に接続される。第5のトランジスタ31のエミッタ電極は、同様に第2のトランジスタ2と共有するよう第2のインダクタ15を介して負極供給ライン9に接続される。

## 【0022】

第4のトランジスタ30および第5のトランジスタ31のコレクタ電極は、トランジスタ38～41により形成される第2のミキサコアへのそれぞれの差動電流入力信号により形成される。第2のミキサコアは、局部発振信号入力端子42、43の局部発振信号を受信する。負荷インダクタ44、45により形成される負荷回路と、キャパシタ46および抵抗47により形成されるフィルタとは、第2のミキサコアの出力と正極供給ライン11との間に接続され、第3の出力端子48および第4の出力端子49は、構成要素である負荷インダクタンス23、24、抵抗25、キャパシタ26、第1の出力端子27、第2の

10

20

30

40

50

出力端子 28 により形成される第 1 のミキサコアの負荷回路およびフィルタ回路と同様に供給される。

#### 【0023】

第 1 の増幅段は、図示されない外部制御回路を用いるとともに、電流源 16 を切り換えることにより入力端子 8 に印加される信号を取り扱うために選択される。第 2 の増幅段は、上述されるものと同様に、図示されない外部制御回路または電流源 50 の選択により、入力端子 8 に印加される信号を取り扱うために選択される。第 1 の増幅段および第 2 の増幅段のいずれかが選択されると、その動作は、第 1 のトランジスタ 1 および第 2 のトランジスタ 2、あるいは、第 4 のトランジスタ 30 および第 5 のトランジスタ 31 の接続により中継されない。この場合、これらのトランジスタの高エミッタインピーダンスが原因である。10

#### 【0024】

図 2 に示される低電圧増幅器は、変動周波数局部発振器として使用される際、高価な上、非実用的で、しかも好ましいものではないと考えられている。図 2 の低電圧増幅器は、単一の I C 回路により形成される回路を用いてシングル入力 R F 信号と混合されるため、2 つの異なる固定周波数局部発振信号を許容することができる。第 1 の増幅段と第 2 の増幅段を同時に選択する場合でも、端子 27、28 および端子 48、49 に同時に出力信号を供給することができる。このような出力信号は、同じ入力信号から取り出せるが、それぞれの局部発振入力端子 21、22 および 42、43 に印加される局部発振信号に依存するものである。20

#### 【0025】

任意の時に第 1 の増幅段および第 2 の増幅段の内のいずれか 1 つが選択されたとしても、この回路構成はトランジスタ 4 およびトランジスタ 38 のコレクタ電極の対等な関係と、また、トランジスタ 7 およびトランジスタ 41 の対等な関係から、いずれかが選択され、1 つのミキサコアからの中間周波数出力信号を供給する必要のある単一の負荷回路および単一のフィルタ回路を利用する。

#### 【0026】

図 2 の増幅器において、第 2 の増幅段と異なるゲインを備える第 1 の増幅段を容易に提供することができる。これは、第 1 のトランジスタおよび第 2 のトランジスタの異なる特性をもつように第 4 のトランジスタ 30 と第 5 のトランジスタ 31 を構築することにより達成される。第 1 のインダクタ 12 および第 2 のインダクタ 15 は、同様の効果を得るため、以下に示される方法で接続される。例えば、第 1 のトランジスタ 1 と第 2 のトランジスタ 2 は、それぞれ 5 回巻きのインダクタ 12、15 の最も外側の端部に接続され、入力端子 8 と負極供給ライン 9 は、インダクタ 12、15 の最も内側の端部に接続され、第 2 の増幅段は、第 4 のトランジスタ 30 および第 5 のトランジスタ 31 が 3 回巻きあるいは 4 回巻きのインダクタ 12 および 15 に接続されることにより、高ゲインを提供することができる。30

#### 【0027】

さらに、これらの増幅段、ミキサコア、および負荷回路が必要な場合は、第 2 の増幅段と同様に入力端子 8 に接続することができる。それぞれの増幅段は、各々、電圧バイアス手段が必要で、好ましくは図 2 に示されるように、電流源が第 1 の増幅段と第 2 の増幅段のように電流ミラー構造に接続されていることである。これらの増幅段は、インダクタ 12 およびインダクタ 15 と配分することができ、あるいは別々のインダクタを包含することもできる。40

#### 【図面の簡単な説明】

【図 1】本発明の第 1 および第 2 の実施形態である低電圧増幅器の構成を示す回路図である。

【図 2】本発明の第 1、第 2、および第 3 の実施形態である低電圧増幅器の構成を示す回路図である。

#### 【符号の説明】

10

20

30

40

50

|             |             |    |

|-------------|-------------|----|

| 1           | 第 1 のトランジスタ |    |

| 2           | 第 2 のトランジスタ |    |

| 3           | 第 3 のトランジスタ |    |

| 4、5、6、7     | トランジスタ      |    |

| 8           | 入力端子        |    |

| 9           | 負極供給ライン     |    |

| 10          | バッテリ        |    |

| 11          | 正極供給ライン     |    |

| 12          | 第 1 のインダクタ  | 10 |

| 13          | 第 1 のキャパシタ  |    |

| 14          | 第 2 のキャパシタ  |    |

| 15          | 第 2 のインダクタ  |    |

| 16          | 電流源         |    |

| 17、18、19    | バイアス抵抗      |    |

| 20          | チヨーク        |    |

| 21、22       | 端子          |    |

| 23、24       | 負荷インダクタンス   |    |

| 25          | 抵抗          |    |

| 26          | キャパシタ       |    |

| 27          | 第 1 の出力端子   | 20 |

| 28          | 第 2 の出力端子   |    |

| 29          | I C チップ     |    |

| 30          | 第 4 のトランジスタ |    |

| 31          | 第 5 のトランジスタ |    |

| 32          | 第 6 のトランジスタ |    |

| 33、34、35    | バイアス抵抗      |    |

| 36          | 第 3 のキャパシタ  |    |

| 37          | 第 4 のキャパシタ  |    |

| 38、39、40、41 | トランジスタ      |    |

| 42、43       | 入力端子        | 30 |

| 44、45       | 負荷インダクタ     |    |

| 46          | キャパシタ       |    |

| 47          | 抵抗          |    |

| 48、49       | 出力端子        |    |

| 50          | 電流源         |    |

【 四 1 】

【 図 2 】

---

フロントページの続き

(72)発明者 コリン レズリー ペリー

イギリス,エスエヌ5 6エイピー, ウィルトシア, スウィンドン, グレインジ パーク, ロッチャ

フォード クロウス 33

審査官 伏本 正典

(56)参考文献 特開平06-177655(JP,A)

欧州特許第00853376(EP,B1)

米国特許第00359285(US,A)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00-3/72

H03D 7/14