(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4495865号

(P4495865)

(45) 発行日 平成22年7月7日(2010.7.7)

(24) 登録日 平成22年4月16日(2010.4.16)

(51) Int.Cl.

F 1

|                   |                  |            |      |

|-------------------|------------------|------------|------|

| <b>G06F 17/50</b> | <b>(2006.01)</b> | G06F 17/50 | 652Z |

| <b>G06Q 30/00</b> | <b>(2006.01)</b> | G06F 17/50 | 662D |

| <b>H01L 21/82</b> | <b>(2006.01)</b> | G06F 17/50 | 601Z |

|                   |                  | G06F 17/50 | ZEC  |

|                   |                  | G06F 17/60 | 302E |

請求項の数 30 (全 29 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2000-620508 (P2000-620508)  |

| (86) (22) 出願日 | 平成12年5月26日 (2000.5.26)        |

| (65) 公表番号     | 特表2003-500745 (P2003-500745A) |

| (43) 公表日      | 平成15年1月7日 (2003.1.7)          |

| (86) 國際出願番号   | PCT/US2000/014617             |

| (87) 國際公開番号   | W02000/072185                 |

| (87) 國際公開日    | 平成12年11月30日 (2000.11.30)      |

| 審査請求日         | 平成19年5月15日 (2007.5.15)        |

| (31) 優先権主張番号  | 60/136,127                    |

| (32) 優先日      | 平成11年5月26日 (1999.5.26)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 60/135,902                    |

| (32) 優先日      | 平成11年5月26日 (1999.5.26)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                          |

|-----------|------------------------------------------------------------------------------------------|

| (73) 特許権者 | 501456401<br>ゲット2チップ<br>アメリカ合衆国 カリフォルニア州 95<br>131 サンノゼ エヌ ファースト ス<br>トリート 2107 スイート 350 |

| (74) 代理人  | 100147485<br>弁理士 杉村 慎司                                                                   |

| (74) 代理人  | 100072051<br>弁理士 杉村 興作                                                                   |

| (72) 発明者  | エロフ フランク<br>アメリカ合衆国 カリフォルニア州 94<br>086 サニーベイル アメリカ アヴ<br>ェニュー 378                        |

最終頁に続く

(54) 【発明の名称】業者間アプリケーションサービスプロバイダ

## (57) 【特許請求の範囲】

## 【請求項 1】

ソフトウェアツール環境が、独自のインテレクチュアルプロパティ(I.P.)を創成すべき、システム・オン・チップ設計者にたいし、従量料金制で提供される、業者間アプリケーションサービスプロバイダー装置であって、

少なくとも一人のシステム・オン・チップ設計者にとってアクセス可能であり、かつ、ハードウェア記述言語(H.D.L.)で表わされた電子的設計のアップロードを受容可能な、インターネットウェブサイト；

前記インターネットウェブサイトで提供され、フロントエンド電子的設計自動化(E.D.A.)ツールを供給し、かつ、前記H.D.L.を受容するように接続される、E.D.A.オンデマンド解決手段；および、

シミュレートされ、実証された、前記電子的設計の派生物を、インターネットを通じて、返送ダウンロードすることを条件として、前記システム・オン・チップ設計者に請求書を供給する、申し込みコントローラーを含み、

前記E.D.A.オンデマンド解決手段のユーザーに、独自のインテレクチュアルプロパティ(I.P.)を創成するために、従量制料金を請求する、業者間アプリケーションサービスプロバイダー装置において、

前記E.D.A.オンデマンド解決手段は、電子的設計自動化(E.D.A.)コンピュータプログラムを含み、

該プログラムは、

10

20

元の回路設計を、一組の対応ロジックツリーに分割すること；

前記ロジックツリーの各々を、内部ノードを持たない、簡単化等価ツリーと交換すること；

前記元の回路において、各経路を、ツリーのリーフ（葉）からルート（根）まで分析すること；

前記各経路について、伝達遅延を計算すること；および、

計算された遅延を、前記簡単化ツリーの対応リーフ（葉）に注記すること、

のためであることを特徴とする、業者間アプリケーションサービスプロバイダー装置。

#### 【請求項 2】

前記電子的設計自動化（EDA）コンピュータプログラムは、10

電子回路設計を生成すること；

前記電子回路設計をその成分ブロックおよびプロトコール設計に分割すること；

前記成分ブロックとプロトコール設計をハードウェア記述言語（HDL）にてコード化すること；

前記成分ブロックとプロトコール設計の操作スケジューリングとリソース割り当てのために高レベル合成（HLS）を用いること；

操作スケジューリングとリソース割り当ての後で、前記成分ブロックを最適化して、中間設計を生成する、技術独立性ブールロジック；

前記電子回路設計のハードウェア実行用の特定デバイスを選択する、技術マッピングの前記中間設計；20

前記特定デバイスを、半導体チップの部位に位置付けること；および、

前記特定デバイスの一組の相互接続の経路指定を行うこと、のためにあって、

技術マッピング行程は、

元の回路設計を、一組の、対応ロジックツリーに分割すること；

前記一組の対応ロジックツリーを順序付けし、それを、別順のツリーを駆動する各ツリーTは、その別順ツリーに先行する、かつ、前記ツリーTを駆動する、各順序ツリーは、前記ツリーTに先行する、ように順序付けして、順序化直線性リストを構成すること；

前記順序化直線性リストを前方掃引し、一方、複数のネットノードそれぞれについて、技術ライブラリー要素に適合する、一組のパレート最適負荷／到着曲線を計算すること；

前記順序化直線性リストを後方掃引し、一方、前記ネットノードそれぞれの、前記一組のパレート最適負荷／到着曲線と、容量負荷とを用いて、前記技術ライブラリー要素の内から、最短信号到着時間を持つ、最善要素を選択すること；30

のサブ行程を含み、かつ、

ゲート入力に対応するネットノードのみが考慮され、かつ、容量負荷は全てあらかじめ指定されることを特徴とする、請求項1の業者間アプリケーションサービスプロバイダー装置。

#### 【請求項 3】

前記電子的設計自動化（EDA）コンピュータプログラムが、

前記元の回路設計の伝達遅延が、入力信号の変位速度に依存する場合、それがいずれのものであっても、前記簡単化ツリーの対応リーフ（葉）に注記すること；40

をさらに供給することを特徴とする、請求項1の業者間アプリケーションサービスプロバイダー装置。

#### 【請求項 4】

前記電子的設計自動化（EDA）コンピュータプログラムが、

前記ロジックツリーの全てのリーフにおいてそこに容量負荷値があれば、それがいずれのものであっても、前記簡単化ツリーの対応リーフにコピーすること、

をさらに供給することを特徴とする、請求項1の業者間アプリケーションサービスプロバイダー装置。

#### 【請求項 5】

前記電子的設計自動化（EDA）コンピュータプログラムは、50

前記ロジックツリー頂上の出力ゲートの負荷 / 遅延反応曲線を、前記簡単化ツリーのルートにコピーすること、

をさらに供給することを特徴とする、請求項 1 の業者間アプリケーションサービスプロバイダー装置。

**【請求項 6】**

前記電子的設計自動化 (EDA) コンピュータプログラムは、

全遅延計算を取り潰して、リソースの抽象的タイミングモデルの内部にたいする、単純な、辺縁重み付け最長経路横断への変更すること、

をさらに供給することを特徴とする、請求項 1 の業者間アプリケーションサービスプロバイダー装置。 10

**【請求項 7】**

前記電子的設計自動化 (EDA) コンピュータプログラムは、

回路境界に接触する複雑モデルツリーと、内部的で、回路境界に接触しない単純モデルとの併用によって、電子設計のタイミング遅延を計算すること、

をさらに供給することを特徴とする、請求項 1 の業者間アプリケーションサービスプロバイダー装置。

**【請求項 8】**

前記電子的設計自動化 (EDA) コンピュータプログラムは、技術選択行程をさらに供給し、同技術選択行程は、

元の回路設計を、一組の対応ロジックツリーに分割すること； 20

前記一組の対応ロジックツリーを順序付けし、それを、別順のツリーを駆動する各ツリー T は、その別順ツリーに先行する、かつ、前記ツリー T を駆動する、各順序ツリーは、前記ツリー T に先行する、ように順序付けして、順序化直線性リストを構成すること；

前記順序化直線性リストを前方掃引し、一方、複数のネットノードそれぞれについて、技術ライブラリー要素に適合する、一組のパレート最適負荷 / 到着曲線を計算すること； および、

前記順序化直線性リストを後方掃引し、一方、前記ネットノードそれぞれの、前記一組のパレート最適負荷 / 到着曲線と、容量負荷とを用いて、前記技術ライブラリー要素の内から、最短信号到着時間を持つ、最善要素を選択すること；

のステップを含み、かつ、ここに、

ゲート入力に対応するネットノードのみが考慮され、かつ、容量負荷は全てあらかじめ指定される、

ことを特徴とする、請求項 1 の業者間アプリケーションサービスプロバイダー装置。 30

**【請求項 9】**

前記電子的設計自動化 (EDA) コンピュータプログラムは、

電子回路設計を生成すること；

前記電子回路設計をその成分ブロックおよびプロトコール設計に分割すること；

前記成分ブロックとプロトコール設計をハードウェア記述言語 (HDL) にてコード化すること；

前記成分ブロックとプロトコール設計の操作スケジューリングとリソース割り当てのために高レベル合成 (HLS) を用いること； 40

操作スケジューリングとリソース割り当ての後で、前記成分ブロックを最適化して、中間設計を生成する、技術独立性ブールロジック；

前記電子回路設計のハードウェア実行用の特定デバイスを選択する、技術マッピングの前記中間設計；

前記特定デバイスを、半導体チップの部位に位置付けること； および、

前記特定デバイスの一組の相互接続の経路指定を行うこと、

をさらに供給し、ここに、

技術マッピング行程は、

元の回路設計を、一組の、対応ロジックツリーに分割すること； 50

前記一組の対応ロジックツリーを順序付けし、それを、別順のツリーを駆動する各ツリー-Tは、その別順ツリーに先行する、かつ、前記ツリー-Tを駆動する、各順序ツリーは、前記ツリー-Tに先行する、ように順序付けして、順序化直線性リストを構成すること；

前記順序化直線性リストを前方掃引し、一方、複数のネットノードそれぞれについて、技術ライブラリー要素に適合する、一組のパレート最適負荷／到着曲線を計算すること；

前記順序化直線性リストを後方掃引し、一方、前記ネットノードそれぞれの、前記一組のパレート最適負荷／到着曲線と、容量負荷とを用いて、前記技術ライブラリー要素の内から、最短信号到着時間を持つ、最善要素を選択すること；

のサブ行程を含み、かつ、

ゲート入力に対応するネットノードのみが考慮され、かつ、容量負荷は全てあらかじめ指定されることを特徴とする、請求項1の業者間アプリケーションサービスプロバイダー装置。 10

#### 【請求項10】

前記高レベル合成を用いるステップは、タイミング分析が、個別の操作がスケジュールされる度毎に適用され、かつ、単一の操作がスケジュールされるために多数回呼び出されてもよいように行われる、

ことを特徴とする、請求項9の業者間アプリケーションサービスプロバイダー装置。

#### 【請求項11】

前記技術マッピングステップは、前記電子回路設計のブールロジックゲートを、技術ライブラリー由来の標準セルにマップする。 20

ことを特徴とする、請求項9の業者間アプリケーションサービスプロバイダー装置。

#### 【請求項12】

前記電子的設計自動化(EDA)コンピュータプログラムは、

時系列プログラムを表わすハードウェア記述言語テキストを、その後の操作スケジューリングと技術割り当てに備えて、制御フローグラフに変換することをさらに供給し、同変換は、

時系列プログラムを表わすハードウェア記述言語テキストを減少させて制御フローグラフに変換する減少ステップと；

前記制御フローグラフからワン・ホット・ビット有限状態装置を構築すること；および、 30

電子的設計自動化システムにおける操作スケジューリングの前に、前記ワン・ホット・ビット有限状態装置の操作タイミングを予測すること、

によって実行され、ここに、

前記ハードウェア記述言語テキストと、最終合成設計の間に、サイクル毎のタイミング一致が維持される、

ことを特徴とする、請求項1の業者間アプリケーションサービスプロバイダー装置。

#### 【請求項13】

前記減少ステップは、解析ツリーのステップ毎減少を含み、ここに、特定の解析ツリー構造が認識され、かつ、対応サブグラフが構築されることを特徴とする、請求項12の業者間アプリケーションサービスプロバイダー装置。 40

#### 【請求項14】

前記減少ステップは、1個の僅少自己帰還ループを含む、1個のリセットノードと、1個のジョインノードの構築で始まることを特徴とする、請求項13の業者間アプリケーションサービスプロバイダー装置。

#### 【請求項15】

前記減少ステップは、アークに注記された全ての解析ツリー宣言文について操作を適用することによって、前記単純グラフを、さらに洗練された制御フローグラフに変換することによって続行し、ここに、

1個の宣言文を持つアークは除去され、少なくとも2個の新規アークと、少なくとも1個の新規ノードによって交換されることを特徴とする、請求項14の業者間アプリケーシ 50

ヨンサービスプロバイダー装置。

【請求項 16】

前記減少ステップは、前記全てのアークに注記された前記全ての解析ツリー宣言文にたいして、前記操作を再帰的に適用することによって続行し、ここに、

全ての分解可能な宣言文が処理されることを特徴とする、請求項 15 の業者間アプリケーションサービスプロバイダー装置。

【請求項 17】

前記減少ステップは、全ての表示ブロックの名前を、そのような名前を "end" ノードにマップするテーブルに保存することによって続行し、ここに、

前記 "end" ノードは、全ての Verilog "disable" 宣言文にたいし終着点を供給することを特徴とする、請求項 16 の業者間アプリケーションサービスプロバイダー装置。 10

【請求項 18】

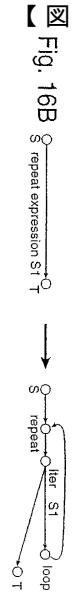

前記減少ステップは、 "repeat" ループの場合、繰り返しカウンター変数を導入することによって続行し、ここに、

前記繰り返しカウンター変数は、前記ループに進入する前に初期化され、かつ、前記ループが一周する度毎に繰り上げられることを特徴とする、請求項 16 の業者間アプリケーションサービスプロバイダー装置。

【請求項 19】

前記減少ステップは、 "repeat" ループ、 "while" ループ、または、 "for" ループにたいする、新規 "inter" ノードの 2 個のアウト-アークのそれぞれに条件を付着させることによって続行することを特徴とする、請求項 16 の業者間アプリケーションサービスプロバイダー装置。 20

【請求項 20】

前記減少ステップは、 "reset" ノードからの前方横断によって到達不能な全てのアークとノードを除去することによって続行することを特徴とする、請求項 16 の業者間アプリケーションサービスプロバイダー装置。

【請求項 21】

前記減少ステップは、さらにそれ以上グラフ構造を含まない分枝から派生する全てのアーク組をまとめて取り潰し、かつ、全ての条件解析ツリーを、前記制御フローグラフに再注記することによって続行することを特徴とする、請求項 16 の業者間アプリケーションサービスプロバイダー装置。 30

【請求項 22】

前記減少ステップは、いずれの条件文も、余分分枝の創設以外に、前記制御フローグラフにたいして何の作用も及ぼすことはないかどうかを検出し、かつ、もしそうなら、減少を適用せず、前記条件文をそのまま注記することによって続行することを特徴とする、請求項 17 の業者間アプリケーションサービスプロバイダー装置。

【請求項 23】

前記減少ステップは、その条件が真となることはあり得ない全ての死んだ分枝を除去することによって続行することを特徴とする、請求項 16 の業者間アプリケーションサービスプロバイダー装置。 40

【請求項 24】

前記減少ステップは、状態としてマークされていない、1 個のイン-アークと 1 個のアウト-アークを含む単純ノードのイン-アーク同士、および、アウト-アーク同士を合流させることによって続行することを特徴とする、請求項 16 の業者間アプリケーションサービスプロバイダー装置。

【請求項 25】

前記減少ステップ後に、前記制御フローグラフの剪定を行って、前記ハードウェア記述言語テキストの中に Verilog "disable" 宣言文を受け入れることをさらに含む、請求項 16 の業者間アプリケーションサービスプロバイダー装置。 50

**【請求項 2 6】**

前記減少ステップ後に、前記制御フローグラフの剪定を行って、前記ハードウェア記述言語テキストの中に"got o"宣言文を受け入れることをさらに含む、請求項16の業者間アプリケーションサービスプロバイダー装置。

**【請求項 2 7】**

前記ワン・ホット・ビット有限状態装置を構築するステップは、前記制御フローグラフの各状態ノードを、対応する単一状態フリップフロップにマップすることを含むことを特徴とする、請求項12の業者間アプリケーションサービスプロバイダー装置。

**【請求項 2 8】**

前記ワン・ホット・ビット有限状態装置を構築するステップは、テーブルMAPを構築することによって続行し、かつ、10

前記制御フローグラフの全てのアークが、前記有限状態装置の対応出力ポートにマップされる、

ことを特徴とする、請求項15の業者間アプリケーションサービスプロバイダー装置。

**【請求項 2 9】**

前記ワン・ホット・ビット有限状態装置を構築するステップは、一組の一次入力と状態フリップフロップによって駆動され、かつ、MAP(C)を駆動する、回路を建設することによって続行することを特徴とする、請求項28の業者間アプリケーションサービスプロバイダー装置。

**【請求項 3 0】**

前記ワン・ホット・ビット有限状態装置を構築するステップは、近似操作を用いることを含むことを特徴とする、請求項29の業者間アプリケーションサービスプロバイダー装置。20

**【発明の詳細な説明】****【0001】****(発明の分野)**

本発明は、電子設計自動化に関し、さらに詳細には、インターネット上で従量料金制に基づいて供給される行動準拠合成ツールに関する。

**【0002】****(発明の背景)**

近年シリコンチップの使用は飛躍的に増加している。数百万ゲートの特定用途向け集積回路(ASSIC)が、あらゆるタイプのアプリケーションに、例えば、携帯電話、ネットワーク装置、DVDプレーヤー等に現在使われている。しかしながら、このような複雑な装置の多くの設計者は、チップサイズが50Kから100Kゲートの範囲にあった、1980年代半ば以来の、時代遅れの電子設計自動化(EDA)ツールや技術を用いている。現在、設計チームは、互いに協力するために、多数の点状ツールを手に入れようと不規則な時間を費やしている。これらの問題は、人力の不足や短い製品サイクルと相俟って、設計要求と、従来技術の能力との間のギャップを広げつつある。30

**【0003】**

このような無効なツールの使用は、市場においては設計時間がさらに長くなり、製品寿命がどんどん短くなることを意味するから、やがて、非常な供給不足を招く。40

**【0004】**

従来のEDAツールが現在、システム-オン-チップ(SoC)設計への移行を妨げている。既存のツールよりも確かに早く、かつ、大きな容量を持つ、新しい、構造的、次世代ロジック合成技術が求められている。設計者は、より高レベルの抽象化へと移動し、百万ゲートRTLや構造レベル設計を取り扱う際の、複雑性・実証性問題を克服しなければならない。

**【0005】**

EDAツールに関する、従来の販売・流通にも問題がある。高度のEDAツールを、設計者が必要とする時に、設計者の前に置き、かつ、そのEDAツールが実際に使用された50

時にのみ、その顧客に料金を請求するには、新しいやり方が必要である。現在、インターネットは、EDAツールを販売・流通させるための新しい方法を提供する。

#### 【0006】

全てのフロントエンド設計相、例えば、構造、RTL、データパス、ロジックの諸相にたいしては、一つのEDAツールを提供する必要がある。構造的合成が実現されるならば、真のシステムレベルの設計が、10倍も大きい容量で実現可能となろう。運転時間が速くなれば、より優れた品質信頼性(QoR)が得られるだろう。なぜなら、普遍的最適化が可能となるからである。コードと設計時間において、2対5の時間短縮をもたらすために新しいEDAツールが求められている。

#### 【0007】

##### (発明の概要)

簡単に言うと、本発明の、業者間アプリケーションサービスプロバイダ実施態様は、システム-オン-チップ設計者にたいして、EDA-オン-デマンド解決法を持つインターネットウェブサイトおよびウェブサーバーを含む。このウェブサイトは、ハードウェア記述言語で表わされた電子設計が、フロントエンドEDA設計環境にアップロードされることを可能にする。ウェブサーバーにおいて私的に宿される、行動モデルシミュレーションツールが、その設計を試験し、その有効性を保証する。このツールは、業者間アプリケーションサービスプロバイダの安全な環境においてのみ実行する。次に、この有効保証された設計解決策はさらに、その他の設計の交換として、他者にダウンロード可能であり、また、技術ライブラリーにおいて入手可能となる。このようにして創成されたインテレクチュアルプロパティ(IP)は、利潤追求の中心同盟センターから、効率的にかつ簡単に、再使用され、販売され、共有され、交換され、かつ、その他のやり方で配給されることが可能である。

#### 【0008】

##### (詳細な説明)

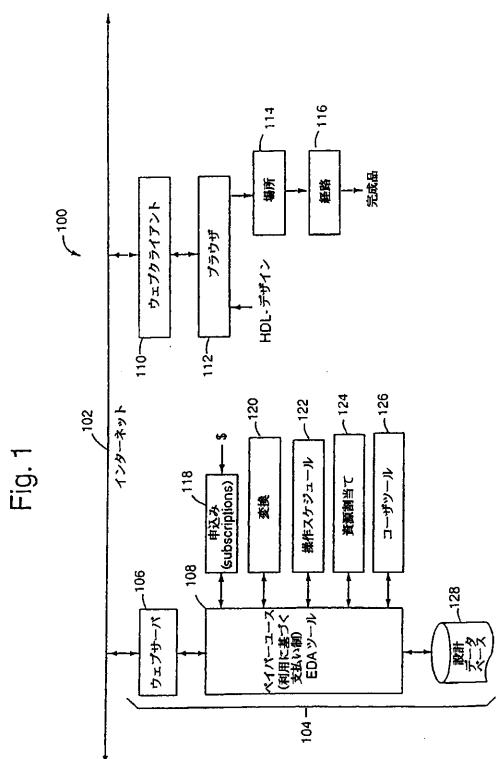

図1は、本発明のインターネットシステム実施態様を表わすが、本明細書では、一般参考番号100と呼ぶことにする。このシステム100は、高レベル合成(HLS)サービスとインテレクチュアルプロパティ(IP)を販売する、業者間アプリケーションサービスプロバイダ104のインターネット接続102を含む。このアプリケーションサービスプロバイダ104は、クライアントのウェブブラウザ訪問を迎るために、例えば、Microsoft社から販売されるソフトウェア、WINDOWS-NT、IISおよびASPを搭載するウェブサーバー106を有する。ペイパーユース即ち従量料金制電子設計自動化(EDA)ツール108が、ソフトウェアアプリケーションとして、ウェブサーバー106に搭載されている。いずれの数であってもよい複数のユーザーおよび顧客が、ウェブクライアント110およびブラウザー112で表わされる。ハードウェア記述言語(HDL)で記述された構造電子設計は、EDAツール108によるシミュレーションと設計証明を求めて、インターネット102を通じてアップロードされる。一旦完了したならば、この証明結果は、場所バックエンド工程114に、また、ルートバックエンド工程116にダウンロードして戻される。

#### 【0009】

EDAツール108は、ユーザーに従量制料金を請求し、かつ、設計のアップロード・ダウンロードを許可する、入会モジュール118によってサポートされる。HDL変換モジュール120は、HDLを翻訳して、制御フロー(CF)グラフに変える。操作スケジュールモジュール122は、各HDLステートメントを、適当なCFグラフノードにマップする。リソース割り当てモジュール124は、スケジュールで要求されるハードウェアを最適化する。一固まりのユーザツール126が、ユーザーが、このウェブサイトをナビゲートし、理解し、かつ、使用するのを助けるために含まれている。

#### 【0010】

この業者間アプリケーションサービスプロバイダ104は、好ましくは、高レベル合成のスケジュール相において、ディジタル設計の浮動時間分析を含む。抽象時間モデルは、

10

20

30

40

50

従来のフルタイミング分析に見られる複雑性という罰をもたらすことなく、成分のビットレベル・タイミングを表出す。各スケジュール決定のタイミング結果について、速やかで、正確な見積もりが供給される。次に、この見積もりを用いて、どれかのスケジュール決定を拒否すべきかどうかを決めることが可能である。

#### 【0011】

高レベル合成（HLS）は、電子設計自動化（EDA）システムにおけるデジタルシステム設計の幾つかのサブタスクを自動化する。システム構築は、導入されるべき全体アルゴリズムを、例えば、C、C++、特殊言語、または、捕捉言語を使って、設計し、有効保証することから始まる。得られた構築仕様を、ボード、チップ、および、ブロックに区分する。各ブロックは、それ自身の制御フローを有する単一工程である。近代の、大規模チップ設計では、通常、数十から数百のこのようなブロックがある。典型的なブロックは、全体フィルター、待ち行列、および、パイプラインのステージを表わす。一旦チップが、その構成ブロックに区分されたならば、必要とされる、何らかの交信プロトコルを構築しなければならない。このようなプロトコルは、ブロック間のサイクル毎交信を用いる。

10

#### 【0012】

いわゆる「スケジューリング」と「割り当て」は、1時に1ブロックに適用される。スケジューリング工程122は、加算や乗算のような演算を、有限状態装置（FSM）の状態（ステータス）に割り当てる。このFSMは、合成されるブロックによって実行される制御フローをアルゴリズムに記述する。幾つかの演算は、特定の状態でロックされて、他のブロックとの交信を表わす。これらの入出力操作は、ある状態から別の状態へ動かしたり、スケジュール変更したりすることはできない。なぜなら、そんなことをすれば、ブロック対ブロックの交信プロトコルを混乱させることになるからである。

20

#### 【0013】

しかしながら、他の幾つかの演算は、ある状態から別の状態への移動が可能である。多数の演算を有する状態から、ほとんど演算を持たない状態へ操作を移動させることは、ハードウェアリソース（資源）が、操作間でより均一に共有されることを可能とする。タイミング問題は、時として、操作を、操作遅延がタイミング問題を引き起こしている状態から、そのような問題の存在しない状態へ移動することによって解決が可能なことがある。

#### 【0014】

30

割り当て工程124は、あるスケジュールされたFSMの操作を、特定のハードウェアリソースにマップする。例えば、3回の加算操作を、单一の加算器のみを必要とするようにスケジュールすることが可能である。適当な加算器を構築し、演算をその加算器に割り当てる。しかしながら、あるビット幅と機能を持つ1個を越えるハードウェアリソースが必要とされる場合、厄介な問題が発生し得る。従って、各演算について、どのリソースを使用すべきかを決めなければならない。考慮しなければならないこととして、多重化コスト、偽似タイミングパスの創成、レジスタ割り当て、さらには、小規模演算用として大きなリソースの使用等が挙げられる。ハードウェアリソースは、多数機能のために使用することが可能である。ある全体工程のために必要な、最小の一組のリソースを計算することは困難ではあるが、困難の価値ある有意味な作業である。時として、別様導入が可能な場合がある。全体タイミング制限に合致し、ゲートカウントを極小にする構築を選ぶことが可能な場合がしばしばある。リソース割り当ては、リソース（抽象機能）を、ゲートレベルの設置成分にマップすることを含む。

40

#### 【0015】

割り当ては、レジスタセットを計算し、データを、後の状態での使用のためにレジスタに割り当てるなどを含む。例えば、一時的変数を使用して、さらに大規模な計算の中間結果を保存する。しかしながら、そのような一時的変数の内容は、異なる状態において、共通レジスタを共有することも可能である。この内容は、1状態について一つだけ必要とされる。従って、保存する必要のあるデータを、そのような保存要素に割り当てるによつて、ハードウェア上にセーブすることが可能になる。しかしながら、データ値が、互い

50

に排除し合うセットを形成したり、または、保存を共有する事が可能な場合は、レジスタおよび保存割り当てが複雑になる可能性がある。データ値はしばしば機能的リソースを駆動するが、逆に、機能的リソースによって生産されることもしばしばある。データを保存に上手に割り当てることは、多重化コストと遅延の縮小をもたらす。割り当てはまた、レジスタと機能的ハードウェアが相互作用を持つ場合、より複雑化される。

#### 【0016】

スケジューリングと割り当ての後には、技術から独立した、または、ブール的最適化が続く。回路設計は、ネットリストに接続された、一般的ANDとORゲートを含む。技術独立的最適化は、ネットリストの中のリテラルの数を最小化する。ブールゲートの抽象化そのものが、ブール代数に基づく高度に数学的な処理となる。例えば、ブールの等式  $A B + A C = A (B + C)$  を用いて、対応するゲートネットワークを減少させることが可能である。10

#### 【0017】

ブール最適化の後には技術マッピングが続く。回路の抽象ブールゲートは、技術ライブラリーから得た標準セルにマップされる。標準ライブラリーセルは、単純なAND、ORまたはNOT機能や、それより遙かに複雑な機能を含む。例えば、全加算器、and/or反転ゲート、および、多重化器である。様々な駆動強度、遅延、インプット負荷等を持つ、技術-ライブラリーゲートが入手可能である。一つの個別ブールゲートをマップするのに多数のやり方があり、かつ、各々のやり方が、それ独自の利点を持っているという事実から、技術マッピングはさらに複雑化される。20

#### 【0018】

時として、技術マッピングを回避し、あらかじめ構築され、特性付与されたセルのライブラリーからセルを選択する代わりに、回路のゲートのために、特注ゲートレイアウトを構築することが可能である。しかしながら、この方法は、自動化合成とは普通は関連しない。

#### 【0019】

技術マッピングの次には、セル設置とネット配線というレイアウト作業が続く。チップ上における各セルの物理的位置が定められ（設置）、かつ、セル同士を相互接続するのに必要なネットがレイアウトされる（経路配置）。アプリケーションサービスプロバイダ104においては、設置や経路配置に関して、設計インテレクチュアルプロパティ（IP）がユーザーにダウンロードされる。30

#### 【0020】

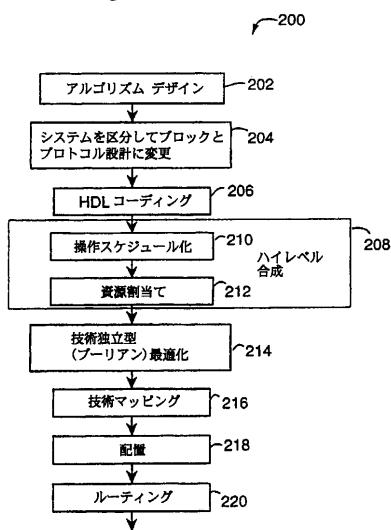

図2は、本発明の電子設計自動化法（EDA）の実施態様を表わすが、本明細書では、これを符号200で示す。EDA法は、アルゴリズム設計工程202から始まる。このシステム設計は、工程204において、複数のブロックとプロトコル設計に区分される。工程206において、Verilog、または、他のハードウェア記述言語（HDL）によるコーディングを実行する。高レベル合成（HLS）工程208は、演算スケジューリング工程210とリソース割り当て工程212とを含む。個々の演算がスケジュールされる度毎に、タイミング分析が適用されるので、单一の演算をスケジュールさせるのに何回も呼び出されることがある。技術-独立（ブール的）最適化工程214が次に続く。技術マッピング工程216は、回路の抽象ブールゲートを、例えば、技術ライブラリーから得た標準セルにマップする。設置工程218は、ゲートを、チップ不動産上に配置し、経路配置工程220は、ゲート同士を配線で相互接続する。40

#### 【0021】

タイミング分析は、状態ダイアグラム、一揃いのリソース、技術ライブラリー、および、少なくとも部分的にスケジュール化され、割り当てられた演算をもって開始する。分析は、設計全体が、そのタイミング要求に合致しているかどうかを判断する。この回路の遅延合計は、有効データが、各クロックサイクルの終了時において、行き先レジスタへのラッチが可能なようになっていなければならない。スケジューリングシステムを用いて、現実スケジュールを構築し、それによって、レイアウト後タイミング合致の確率を良好にす50

る割り当て回路を得ることも可能である。

#### 【0022】

タイミング疑問には、素早く、かつ、効率的に答えなければならない。なぜなら、そのような疑問は、単一設計をスケジュールする工程で度々尋ねられるからである。例えば、リスト-スケジューリングアルゴリズムでは、設計の転移（即ち変更）は個別に、順番に考慮される。各転移について、一組の「スタンバイ」演算が構築される。このスタンバイ演算は、転移のソース状態において利用可能な入力データを含む演算である。これらの演算の内から一つが、何らかの基準 例えは、もっとも緊急なものをもっとも先に を用いて選択され、スタンバイリストから取り出され、現在の転移ではこうしたことがなければ未使用とされるリソースに割り当てられる。次に、得られたデータは、利用可能なデータセットに加算される。次に、その結果に依存する他の演算が、スタンバイリストに加算されてもよい。この工程は、もうこれ以上の演算がスタンバイリストに無くなるまで、または、スタンバイリストの演算を実行するためのリソースがもはや無くなるまで、または、スタンバイリストの演算が、現在の転移ではスケジューリングできなくなるまで、続く。これは、全てのアーク即ち円弧が考慮され、全ての演算がスケジュールされるまで、繰り返される。このタイミング工程は、与えられた一組のリソースを使っては、その設計がスケジュールできない場合は、停止する。10

#### 【0023】

タイミング分析は、個別の演算がスケジュールされる度毎に、実行しなければならない。最初の、候補の、演算-転移-リソーススケジューリング組が受け入れられなかった場合、タイミング分析工程は、一つが受け入れられるまで、繰り返し呼び出されなければならない。タイミング分析工程は、一つの演算のスケジューリング組が考慮される度毎に、設計リソースの全てについてタイミングを評価することができなくてはならない。20

#### 【0024】

さらに、タイミング分析は、ビット塊状ではなく、ビット忠実でなくてはならない。各種リソースの遅延を明らかにする場合、各リソースに関連する、単一数、または、単一負荷 / 機能では不充分である。一つの遅延または負荷 / 遅延機能は、リソースの各アウトプットビットと関連していなければならない。

#### 【0025】

併合リソースについて、高速で、正確なビットレベルのタイミングモデルを構築することは可能である。なぜなら、併合ロジックを表わすグラフは、必ず、一揃いのツリー（ツリー）に区分けすることが可能だからである。ロジックのツリーは、そのノードを使って、ゲートと端子を表わし、その円弧を使って、接点を表わす。電気的ドライバーは、ロジックツリーにおいて、必ず、ドライブするゲートの下に来る、例えは、ルート（ツリーの根）から遠い方に来る、あるいは、そうでなければ、ルートと、ドライバーが駆動するゲートは別のツリーに存在する。ツリーの終末点は、ロジックツリーの外側のゲートにたいする接点を表わす。ネットワークのゲートが、2個以上の扇形広がりを持つ場合、最大ロジックツリーのルートは、そのゲートの出力端子である。他の全てのツリーは、灌ツリー（サブツリー）となる。30

#### 【0026】

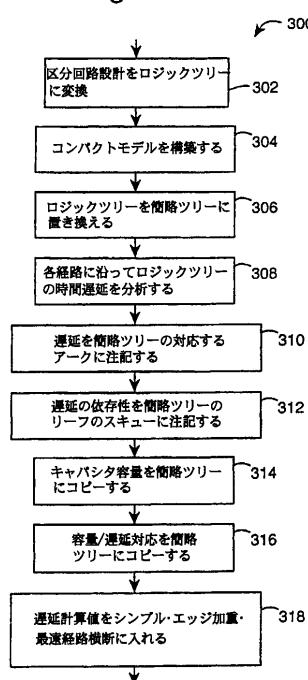

図3は、本発明のタイミング分析法を表わし、本明細書では、一般参照番号300と呼ばれる。この方法300は、回路設計を、対応するロジックツリー（ツリー）に区分する工程302から始まる。一旦回路がロジックツリーに区分されたならば、工程304において、その回路の小型モデルを構築することが可能になる。ロジックツリーは、例えは、工程306において、内部的ノードを持たない等価的ツリーに交換される。この等価ツリーは、しばしば、もとのツリーよりも実質的により単純になっている。工程308において、もとの回路のタイミングが、ツリーの葉からそのルートまで、各経路にそって分析される。工程312において、もとの回路の伝達遅延が、入力信号の変位速度に依存していることが認められた場合、それがいずれものであっても、簡単化ツリーの対応葉の上に注記される。工程314は、ロジックツリーの葉から、容量性負荷を簡単化ツリーの葉にコ4050

ピーする。例えば、ロジックツリーの頂上における出力ゲートの、ロード／遅延反応曲線は、工程 316において、簡単化ツリーのルートにコピーされる。

#### 【0027】

変位や負荷依存性のような、幾つかの辺縁効果は、本発明の実施態様では、経路遅延の中に取り込まれてもよい。これらの追加項は、末端が、全体リソースの境界にあるツリーにたいしてのみ計算する必要があるだけである。従って、工程 318において、全体遅延計算は、リソースの抽象タイミングモデルの内部における、単純な、辺縁重み付け最長横断経路に縮小される。これによって、回路の各セルについて変位速度や遅延を計算するのに比べて、タイミング分析がずっと速くなる。

#### 【0028】

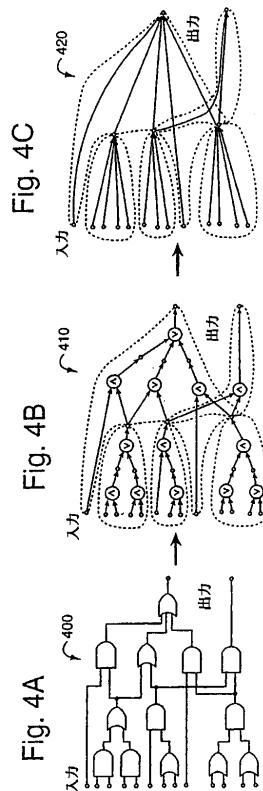

図 4 A、4 B および 4 C は、回路 400 からロジックツリー 410、および、簡単化ツリー 420 への転移を表わす。図 4 B において、ロジックゲートは、ツリー中のノードとして表わされる。AND ゲートは、上を向いたシェブロン記号を持ち、NOR ゲートは、下を向いたシェブロン記号を持つ。図 4 C では、ノードは完全に取り除かれる。本発明の実施態様におけるその後の工程では、簡単化ツリー 420 は、回路 400（図 4 A）における遅延問題について速やかな解答を与える注釈で飾られる。点線による囲みは、サブツリーを示す。

#### 【0029】

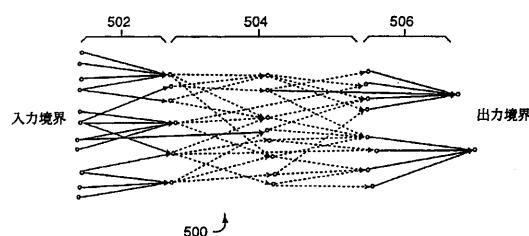

図 5 は、インプット境界に一組の複雑モデルアーク 502、内部に一組の簡単化モデルアーク 504、および、アウトプット境界に、別の一組の複雑モデルアーク 506 を含む設計 500 を表わす。モデル内部の伝達遅延について、このような簡単化モデルを用いているために、正確性において若干の損失があるが、実際には、そのような不正確ではないようである。正確性の損失が問題なら、新たな内部アークにたいしてさらに複雑なモデルを使用することも可能である。この場合、正確度は向上するであろうが、解法運転時間も増大するであろう。回路境界に接触するアークのみが、真に、複雑モデルを必要とする。簡単化モデルを有するアークを破線矢印で示す。

#### 【0030】

回路を表わすロジックツリーの全てが、簡単化ツリーにマップされたなら、もとのリソース回路図は廃棄してもよい。関係タイミング情報の全ては、簡単化ツリーのネットワークに保存される。次に、簡単化ツリーのネットワークに取り込まれたリソースのモデルを、到着時間を計算する、グラフ横断アルゴリズムと一緒に用いることによって、連鎖リソースのタイミングを分析することが可能となる。この簡単化モデルタイミング分析用グラフ横断によって、従来の方法に比べて一桁違う高速分析が可能となる。

#### 【0031】

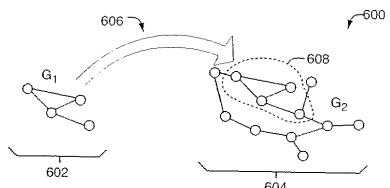

図 6 は、二つのグラフ、パターングラフ 602  $G_1 = (v_1, e_1)$  と標的グラフ 604  $G_2 = (V_2, e_2)$  がある場合の、一般的グラフ適合問題 600 に関わる。目的は、パターングラフ要素から、標的グラフ要素にたいする、1 対 1 マッピングを見つけることである。適合されたノードによって定義されるサブグラフ  $G_2$  は、 $G_1$  と同形でなければならない。そのような適合の例がここに示され、適合されたノードとアークが、囲み 608 の中に示される。

#### 【0032】

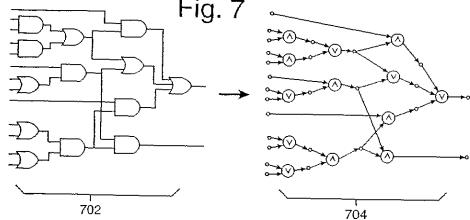

図 7 は、回路 702 と、それに対応する、二つの部分から成るグラフ表示 704 を示す。大体、ゲートはノードに変換され、相互接続はアークに変換される。特定の、技術マッピング適合問題は、比較的一般的な適合問題とは異なる。回路のために抽出されたグラフは、方向性を持つ、2 部分グラフ、例えば、 $G = (v_1, v_2, e)$  である。ここに、"e" の辺縁は、 $v_1$  の要素を  $v_2$  の要素に接続するが、 $v_1$  の要素を  $v_1$  に、または、 $v_2$  の要素を  $v_2$  に接続することは決してない。辺縁は、順序を持つペアで、例えば、方向性を持つ。 $v_2$  のノードはゲートを表わし、 $v_1$  のノードは回路ネットを表わす。2 部分方向性グラフにおけるグラフ適合は、ネットノードはネットノードにのみマップされ、ゲートノードはゲートノードにのみマップされ、かつ、同形性を用いて辺縁の方向性を保存

10

20

30

40

50

するように、行われる。2部分グラフ表示704において、ゲートを表わすノードは、タイプ区分を有する、例えば、AND( )、OR( )、およびNOT( ! )である。これらは、同形構築の一部を形成する。G1におけるタイプXのノードは、G2におけるタイプXのノードにマップされる。

#### 【0033】

従来技術は通常ツリーを適合させる。方向性非サイクルグラフ(DAG)を用いて、幾つかの型の複数出力ゲートを表わすことが可能であるから、併合ロジック回路を、一つのDAGで表わすことも可能である。すなわち、それら併合ロジック回路がサイクルを含まない限りは可能である。DAGはまた、形良く形成され、偽似サイクル経路を含まないようになっていなければならない。

10

#### 【0034】

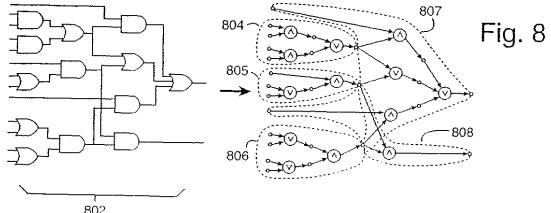

図8は、技術マッピングにおける最初の工程、すなわち、ネットワークグラフ802を区分して、一括りのツリー群804-808、すなわち、DAGに変換する工程を示す。次に、各ツリー804-308を、個別のマッピング問題として、処理する。もっとも簡単な処方はツリーを使用することであるが、DAGへの拡張を行ったとしても難しくはないだろう。一般に、ツリーは、そのルートや葉は全て、ゲートノードではなくして、ネットノードであるというように定義される。ルートやリーフは、必要なだけ多数重複される。でなければ、ルートやリーフは、ツリー間で共有されなければならない。ツリー804-808は、できるだけ大きく、例えば、最大ツリーでなければならない。DAGに拡張する場合、いずれの拡張であっても、一つのDAGのアウトプット端子の数は、2または、他の小さい数に限定されなければならない。でないと、適合計算が複雑になりすぎる。

20

#### 【0035】

典型的な技術ライブラリーは、原始的要素を表わす幾つかのセルを含む。ライブラリーの併合セルは、ブール関数を持つ。各セルについて、選択された一組の2部分方向性グラフ表示が構築される。これらのグラフはそれぞれ、小さな原始的タイプのアルファベットで表現された、セルのブール関数と関連する。ライブラリーの各セルは、ネットノード、2入力NANDノード、および、NOTノードのみを含むツリー(またはDAG)によって記述される。選ばれた正確なアルファベットは、それが比較的単純なものであり、ロジック的に完全である限り、決定的に重要ではない。ブール関数は全て、アルファベットのユニットのみを含むネットワークとして表わすことができる。

30

#### 【0036】

このような分解されたライブラリーを図9に示す。セル名は左のコラムに挙げてある。真中のコラムは、対応するブール関数を挙げる。各セルは、右のコラムに示すような1個以上のパターンツリーで表わされる。

#### 【0037】

技術マッピング工程に委ねられた回路設計は、いずれのものであっても、通常、単純なゲート、例えば、NAND、AND、NOR、OR、XOR、および、NOTのネットワークとして表わされる。各ネットワークは、ライブラリーツリーのゲートタイプおよび扇形インのみを用いて、機能的に等価なネットワークに変換される。図9の例示ライブラリーについて言えば、回路は、インバーターと、2入力NANDゲートのみから成る等価回路に変換される。次に、その等価回路は、2部分方向性グラフ表示に、例えば、ライブラリーパターングラフと同じスタイルのグラフ表示にマップされる。その後、グラフ適合を実行することが可能になる。ライブラリーセルおよびマップされる回路の両方とも、同じグラフ形式を用いて表わされる。

40

#### 【0038】

回路のツリーは、個別適合問題となる。好ましくは、適合結果は全て、各ネットノードNに、適合パターンツリーのリストを付着させることによってコードされる。このリストは、そのルートがNに適合する、一組のパターンツリーを表わす。下記の偽似コードはそのようなリストを設け、かつ、そのリストを適合(N)と呼ぶ。

50

R を回路ツリー T のルートとせよ。

S を、最初は R のみから成る一組とせよ。

( S が非空虚である限り ) {

N を S の一要素とせよ。 S から N を取り出せ。

( ライブラリーの、パターンツリー組の全ての数 P ) について

( 適合 ( ルート ( P ) 、 N ) ) ならば {

M を適合 ( N ) に加えよ。

}

}

}

( N が T のリーフノードでない ) ならば {

G を N のドライバーとせよ。

G の全てのドライバーを S に加えよ。

}

}

【外 1】

Let R be the root of a circuit tree T.

Let S be a set comprising initially only of R.

While (S is nonempty) {

Let N be an element of S. Remove N from S.

For (all members P of the set of pattern trees in the library)

If (matches(root(P), N)) {

Add M to matchings(N).

}

}

if (N is not a leaf node of T) {

Let G be the driver of N.

Add all drivers of G to S.

}

}

## 【0039】

パターン適合アルゴリズムを用いてツリー適合テストを実行するには幾つかの方法がある。例えば、再帰的アルゴリズムは、ある回路ツリーがあるパターンツリーにたいし、ルート同士が適合場合、適合することを認識することが可能である。サブツリーマッピングは、回路ツリーとパターンサブツリーが1対1対応でなければならない。すなわち、回路ツリーの各サブツリーは、正確に、パターンツリーの一つのサブツリーにマップしなければならない。パターンツリーの全てのサブツリーは、回路ツリーの何れかのサブツリーに、例えば、"onto"マッピングを通じて、マップされなければならない。これが行われないと、回路ツリーの1を越えるサブツリーが、パターンツリーの単一サブツリーにマップされたり、あるいは、パターンツリーのいずれのサブツリーにもマップされなくなる可能性がある。

## 【0040】

あるサブツリーとサブツリーの適合が失敗しても、別の適合が成功するかも知れない。このツリーは非対称であってもよい。パターンツリーのサブツリーの順番リストの、全ての順列が、回路ツリーのサブツリーの順番リストにたいしてテストされる。全ての順列が失敗した場合、適合試行全体が放棄される。いずれかの順列が成功した場合、適合が見出されたことになる。

## 【0041】

下記の偽似コードは、適合アルゴリズムを実行する。名前の付けられたノードは全てネットノードである。ゲートノードは、ネットノードのドライバーである。if文の中に挙げられているリスト"U"は、ネットNのドライバリスト、例えば、ネットノードNを駆動するゲートGのドライバリストである。

10

20

30

40

50

```

( M がリーフノードであるならば ) {

真を返せ。

{ でなければ ( N がリーフノードであるならば ) {

偽を返せ。

} でなければ ( M のドライバーのタイプが N のドライバーのタイプと同じであるならば

) {

( M のドライバーのドライバーリストの全ての順列 P について ) {

Temp = 真 ;

U を、 N のドライバーのドライバーリストとせよ。

( P の全ての要素 p 、および、 U の全ての要素 u についてこの順番で ) {

( ( p 、 U ) 適合が偽であるなら ) {

Temp = 偽

Continue ( 続行 ) へ行け。

}

}

Continue ( 続行 ) :

If ( Temp ) {

( P 、 U ) が、成功的 1 対 1 の、 onto マッピングであるなら、

真を返せ。

}

}

}

この地点まで達した場合、 1 対 1 の、 onto マッピングはない。

偽を返せ。

} でなければ {

偽を返せ。

}

【外 2 】

If(M is a leaf node) {

Return true.

{ else if (N is a leaf node) {

Return false.

}else if (the type of the driver of M is the same as the type of the driver of N) {

For (all permutations P of the list of drivers of the driver of M) {

Temp = true;

Let U be the list of drivers of the driver of N.

For (all elements p of P, and u of U, in order) {

If (matches(p, U) is false) {

Temp = false;

Go to Continue.

}

}

Continue:

If (Temp) {

(P, U) is a successful one-to-one and onto mapping.

Return true.

}

}

If you get to this point there is no one-to-one and onto mapping.

Return false.

}else{

Return false.

}

```

この形式では、アルゴリズムは、技術ライブラリーセルの扇形インが増加するにつれて、次第に高価になる。複雑性は指数関数的である。このアルゴリズムはスピードアップが可能であるが、現在の、大抵の技術ライブラリーにたいしては十分に高速である。

#### 【0043】

この適合工程によって、回路のネットノードから、パターンツリーのルートノードにたいして1対1マッピングが生成される。このようなマッピング候補は、ネットノードを引き数とし、一組のパターンツリーを返す関数である。回路の導入は、一組のネットノードとなるが、そのために、前記候補組の内の一員が選ばれる。この選ばれたネットノードの組は、通常、ネットノードの全体組よりも小さい。なぜなら、幾つかのネットノードは、内部ネットノードを持つパターンの内側に「埋められる」からである。

10

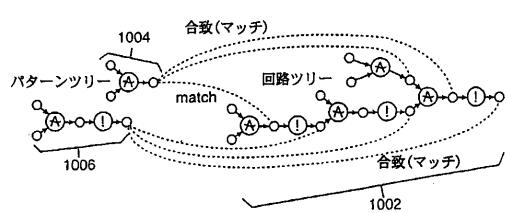

#### 【0044】

図10は、右に回路ツリー1002を示すが、この回路ツリーの全ての部分と適合するのに必要とされるのは、左の、たった2個のパターンツリー1004と1006だけである。1個の、回路ツリーネットノードにたいする、パターンツリーの可能な適合を、破線で示す。従って、全体回路は、6個の適合から成る適当なサブセットが選ばれるならば、僅か4個のゲートで「カバー」することが可能である。言い換えれば、この回路ツリーは、4個の構成ゲートタイプに分解することが可能である。図示の6個の適合から成るサブセットは、冗長なまたは不充分なカバーリングを生成する可能性がある。解決すべき問題は、遅延や冗長を最小にし、かつ、カバーができる適合サブセットを選択することである。

20

#### 【0045】

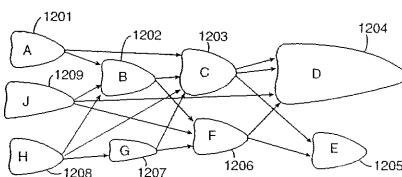

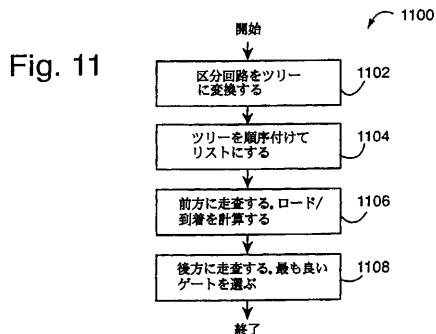

図11は、本発明のカバーリング選択法実施態様を表わし、本明細書では一般参照番号1100と呼ばれる。工程1102で、回路は、ツリーに区分される。工程1104で、それらツリーは、立体位置仕分けアルゴリズムによって順序づけられる。深さ順グラフ横断アルゴリズムを用いることも可能である。順序付けの規則にはこうある「ツリー”T”は、その葉(リーフ)が、ツリー”T”によって駆動される、全てのツリーに先行し、かつ、ツリー”T”のいずれかの葉”L”を駆動する全てのツリーに追随する。このようにして順序付けされたツリーリストは”0”と呼ばれる。

#### 【0046】

工程1106で、順序付け直線リストにおいて前進掃引を実行する一方で、技術ライブラリー要素と適合する複数のネットノードの各々について、一組のパレート至適負荷／到着曲線を計算する。工程1108では、順序付け直線リストにおいて後退掃引を実行する一方で、ネットノードの各々と容量性負荷について、一組のパレート至適負荷／到着曲線を用い、技術ライブラリー要素の内、最短の信号到達時間を持つ最善要素を選択する。ゲート入力に対応するネットノードのみを考慮の対象とし、容量性負荷があれば、それらは必ずあらかじめ指定する。

30

#### 【0047】

回路と順序リストを表わす、そのようなツリー”T”を、図12に示す。”0”とされる第1ツリー1201は、任意に”A”と表示した。他のツリー1202-1209は、”B”から”J”にて表示した。前記規則を満足する、ツリーの立体的順序付けは、A、H、G、J、B、C、F、E、Dとなる。ツリーA、JおよびHは、インプット境界にあるから、他のツリーは、ツリーA、JまたはHのいずれをも駆動できない。従って、前記規則に基づき、ツリーAを、順序リスト”0”的頭に置くのは許される。ツリーA、H、G、J、B、C、F、E、Dのこの順序づけによって、各ツリーが、まだ評価されないインプットツリーを持つツリーがないようなやり方で、順番に、評価されることが可能となる。

40

#### 【0048】

インプット境界において、ツリーAのリーフにたいする信号到着時間は想定可能である。その時間は、回路の併合部分の一次入力を表わすから、信号到着時間は、回路環境やユーザー条件から入手することが可能である。ツリーAの各リーフLは、候補適合を持たない。負荷／遅延曲線を、ツリーAの各リーフに付属させることも可能である。この負荷／

50

遅延曲線は、 $L$  が表わす一次インプットの想定ドライバーに関連する、いずれの負荷 / 遅延曲線であってもよい。

#### 【0049】

ツリー A のルートは、アウトプットネットである。技術ライブラリー由来の少なくとも一つの候補が適合しなければならない。でないと、工程は停止しなければならない。ツリー A のルートについて、例えば、下記のような再帰工程を含むアルゴリズムを用いて、集合負荷 / 遅延曲線を計算することが可能である。

候補適合セット C を持つネットノード N が与えられたとせよ。

N の集合負荷 / 遅延を初期化せよ。

( C の各要素 c について )

10

( c の各リーフノード X について )

Y を X に対応する T のネットノードとせよ。

Y における集合負荷 / 遅延曲線を再帰的に計算せよ。

X に関連する負荷を、ライブラリー中に求め、

かつ、X における信号到着時間を、

X における負荷と、負荷 / 遅延曲線に基づいて計算せよ。

}

c の各リーフにおける到着時間が既知となった。

N における到着時間を、負荷の関数として、

かつ、c の表わすライブラリー要素の電気的特性を、計算せよ。

20

計算された曲線を、N の集合不可 / 到着曲線に加えよ。

}

#### 【外3】

Given net node N with candidate matching set C.

Initialize the aggregate load/delay curve of N.

For (each element c of C) {

For (each leaf node X of c) {

Let Y be the net node of T corresponding to X.

Recursively compute the aggregate load/delay curve at Y.

Look up the load associated with X in the library,

and compute the signal arrival time at X,

based on the load and the load/delay curve at X.

30

}

The arrival times at each of the leaves of c are now known.

Compute the arrival time at N as a function of load

and the electrical characteristics of the library element that c

represents.

Add the curve so computed to the aggregate load/arrival curve of N.

}

#### 【0050】

結局、このアルゴリズムは、N の適合候補を走査し、各候補 "c" について、"c" が選ばれるであろうという仮定の下に、"c" のインプットにおける到着時間を計算する。次に、"c" の既知の特性から、N における負荷 / 到着曲線を、従って、"c" のインプットにおける信号到着時間を計算する。N にたいする可能な適合を持つセルのそれぞれを表わすように、負荷 / 到着曲線の組が生成される。

40

#### 【0051】

この集合負荷 / 遅延曲線表示は、効率的なものとすることが可能である。いずれの負荷にたいしても、ある特定のセル "c" にとって、唯一の至適遅延がある。その負荷にたいしては、"c" の他のいずれの成員も、せいぜい同じ到着時間に適合させることができるだけである。従って、N における負荷 / 到着曲線は、好ましくは、負荷を、"c" の最適成員にマップする関数である。この関数は、集合負荷 / 遅延曲線の、断片的最小値を取ることに

50

よって生成が可能である。

#### 【0052】

ある特定の容量負荷という観点から、最適ゲート選択の実行が必要である。例えば、ゲートG2が最善である負荷範囲は、ゼロ負荷から破断点までである。最善は、最短信号到達時間（最小遅延）を有すると定義される。ゲートG1が最善な負荷範囲は、破断点から無限までである。容量負荷が与えられているならば、Nにおける集合曲線を用いて、到着時間と、Nにマップされる最善ゲートの両方を見つけることが可能である。

#### 【0053】

ツリーの順序リストからスタートした場合、考慮すべき最初のツリーは、一次入力によってのみ駆動されるものである。その後のツリーはいずれも、一次入力によって駆動されるか、または、既に処理されたツリーによって駆動されるかのいずれかである。このようにして、順番に考慮される全てのツリーTは、一次入力か、前に考慮されたツリーか、そのいずれかによってのみ駆動されることが保証される。ツリーTのインプットにおける全てのドライバーは、ツリーTが考慮される時点において既知のパレート最適負荷／到着曲線を持つことになる。パレート最適負荷／到着曲線は、回路の一次出力のそれぞれについて計算される。

10

#### 【0054】

最終工程は、各出力-Oについて負荷を選択する。最初、その負荷は、それが、出力-Oにたいする集合負荷／到着曲線の範囲内に入る限り、任意に選択することが可能である。出力-Oにおける集合曲線は、到着時間と最適ゲートGの両方をマップし、出力-Oを駆動する。負荷を設定することは、出力-Oを駆動するのに、どのライブラリーゲート-Gを選択すべきかを宣言することになる。

20

#### 【0055】

そのルートが出力-Oであるツリーは、ライブラリーゲート-Gから始めて内部を動き回ることが可能である。入力容量は既知である。なぜなら、ライブラリー-Gは、技術ライブラリーにおいて既知の要素であるから。これは、その入力の各々を駆動するのに最適なゲートに関する簡単な探索を可能にする。ツリー-Tが完全にカバーされるまで、これは繰り返される。

#### 【0056】

このカバー工程を、ツリーの順序リストにたいして逆順に適用する場合、その駆動するツリーが全て既にカバーされているのでない限り、いかなるツリーも考慮されない。そのツリーのルートゲートへの負荷は考慮される。このカバー工程は、全てのツリーがカバーされるまで進行する。このようにして、技術マッピングが終了する。

30

#### 【0057】

要約すると、選択工程は、ツリーの順序リストを掃引する。最初は前方に向かって、次ぎは後方に向かって。前方通過の際、ライブラリー要素に適合する各ネットノードについて、一組のパレート最適負荷／到着曲線が計算される。後方通過では、負荷／到着曲線と負荷値を用いて、考慮される各ノードを駆動するのに最善のゲートを選択する。ゲート入力に対応するノードのみが考慮される。このため、負荷は常に既知であり、従ってこの工程も終了が可能である。

40

#### 【0058】

理解と実行を助けることを可能とする、背景ソースが幾つかある。適合ツリーと動的プログラミングを用いる基本概念が、Keutzer, Technology Binding And Local Optimization By DAG Matching, Proceedings of the 24th Design Automation Conference, IEEE, 1987, 341ページに詳細に記述されている。この論文は、適合ツリーの使用と、選択問題における面積最適化处方をカバーしている。この方法は、面積を最適化するが、負荷／到着曲線は用いない。さらに、これは、2回通過ではなく、前方通過しか使わない。遅延／面積曲線を用いるツリー適合の、また別の洗練された方法がChaudhary, A Near Optimal Matc

50

hing Algorithm for Technology Mapping Minimizing Area Under Delay Constraints, 29th Design Automation Conference, IEEE, 1994に記載される。しかしながら、この研究で、Pedramは、面積 / 遅延曲線を用いているので、異なる負荷の作用を計算することができなかった。これは、極めて重要な違いである。

#### 【0059】

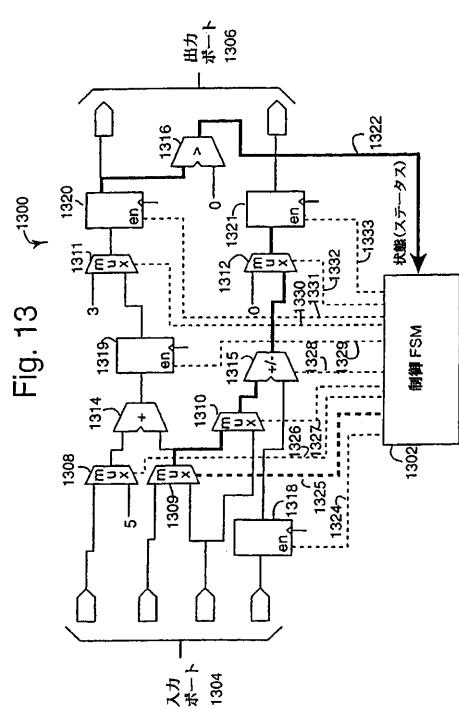

図13は、どのようにして制御信号が、最重要タイミング経路を支配するかを示す実施例である。制御信号は破線で示され、最重要経路は、太実線で示される。回路1300は、司令FSM1302を含む。最重要信号伝達タイミング経路は、一組の入力ポート1304と、一組の出力ポート1306の間に存在する。回路1300は、司令FSM1302に制御される、幾つかの多重化器1308 - 1312、幾つかの加算器1314 - 1316、および、幾つかのラッチ1318 - 1321を含む。状態信号1322が、司令FSM1302によって入力される。多重化器1308 - 1312とラッチ1318 - 1321は、司令FSM1302によって出力される一組の制御信号1324 - 1333に依存する。従って、入力から出力までの信号の波及状態は、何時制御信号1324 - 1333が発せられ、定着するかに、極めて大きく依存する。

#### 【0060】

制御フローグラフは、ソースコードHDLで表わされる制御フローを記述する、方向性グラフである。一つのHDL記述から、一意の制御グラフにたいして、直接的マッピングが存在する。そのような一意の制御フローグラフから、例えば、「バブルグラフ」表示で表わされた有限状態装置にたいしても直接的マッピングが存在する。直接マッピングはさらに、一意の制御フローグラフから、「ワン・ホット」FSM回路にたいして形成することも可能である。従って、司令FSMは、その後に構築される、いずれのスケジュールにも無関係に、2工程で生成が可能である。大事なことは、司令FSMのタイミングは、スケジューリング時に確定することが可能である。

#### 【0061】

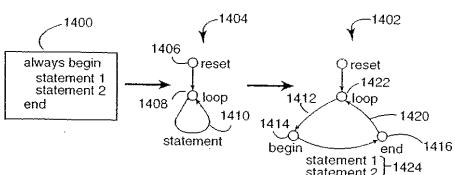

一般に、制御グラフ - Gは、方向性アーケ "E" によって接続されるノード "V" を含む。図14において、制御グラフ - Gの一つのノードVは、"reset"と表示される。このようなノードは、制御フローグラフ - Gの起点を表わす。定義により、"reset"ノードは、イン-アーケを持たず、ただ一つのアウト-アーケ（外に向かうアーケ）を持つだけである。制御フローグラフ - Gにおける、他のノードについては、いずれの数であっても、状態ノードと表示されてよいし、または、表示無しとしてよい。これらのノードは、少なくとも一つのイン-アーケ（内に向かうアーケ）と、少なくとも一つのアウト-アーケを持たなければならない。

#### 【0062】

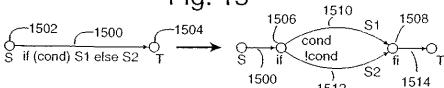

図15に示すように、アーケは、状態および動作による表示が可能である。これらは、解析ツリー、または、解析ツリーのリストであり、FSMの状態および動作と近似する。状態表示は、例えば、"if"で、制御分枝がどちらの道に行くかを明らかにする。動作表示は、制御フローが、動作で表示されるアーケにそって移動する場合、生ずる操作を記述する。

#### 【0063】

"Join nodes"は、1個を越えるイン-アーケを持つノード、例えば、図15の"if"ノードである。"Fork nodes"は、1個を越えるアウト-アーケを持つノード、例えば、図15の"for"ノードである。一般的なプログラミング構築体に一致する、その他の名前や表示、例えば、"begin," "loop" "end"等を用いることも可能である。

#### 【0064】

制御フローグラフ - Gは、典型的には、解析ツリーの段階的減少において分解されたHDLテキストから構築される。特定の解析ツリー構造が認識され、次に、Gの対応サブグ

10

20

30

40

50

ラフが構築される。本明細書では、Verilogが、各種実例HDL・Verilog構築名に使われていが、マッピングは、VHDLや、その他の、辺縁事象を可能とする必須のシミュレーション準拠HDLにたいして実施することも可能である。

#### 【0065】

ここで図14を参照すると、解析ツリーP1400から、制御フローグラフ-G1402への、单一工程の移行は、リセットノード1406とジョインノード1408、および、小さな自己還元ループ1410を持つ単純グラフ1404から始まる。Verilogでは、工程は、"always"キーボードを用いて創成され、その後、単純または複合"statement"が続く。"statement"という言葉は、そのノードの動作または操作として、自己ループ1410に一時的に注記される。分枝がないところでは、"condition"表示もない。10

#### 【0066】

単純グラフ-G1404は、アークに注記された宣言に工程を適用することによって、さらに洗練された制御フローグラフ-G1402に変換が可能である。例えば、一つの宣言を持つアークは、2個以上のアークと1個以上のノードに交換される。次に、この新しいアークは、さらに簡単な宣言、および/または、状態によって装飾される。新しいノードも同様に表示される。この工程が、分解可能な宣言が残らなくなるまで、再帰的に続く。新しいアークに表示される宣言と状態は、宣言の解析ツリーの、特定サブツリーとなる。20

#### 【0067】

例えば、Verilogにおける連続複文は、Backus-Naur形(BNF)語法定義を持つ。

連続文 : : = 始め <宣言文> 終わり

| | 始め - 表示 : <宣言文> 終わり

#### 【外4】

```

sequential-statement ::= begin <statement>* end

|| begin label: <statement>* end

```

#### 【0068】

従って、典型的なVerilog工程は、図14の宣言文1400にあるように"statement1"と"statement2"で表わされることがある。30

#### 【0069】

図14において、Verilogの連続ブロック"begin...end"宣言文は、ソースノード-Sとシンクノード-Tの間の、制御フローアーク-Aに変換することが可能である。アーク-Aは、シンクノード-Tから外され、連続ブロック解析ツリー-Pは、アーク-A1412から取り除かれる。二つの、新しいノード1414と1416"begin"と"end"が構築される。アーク-A1412の矢印の先端は、"begin"ノード1414に接続される。新規アーク-B1418が構築され、その矢羽ルート端が、"begin"ノード1414に接続され、かつ、その矢の先端が、"end"ノード1416に接続される。新規アーク-C1420が構築され、その矢羽ルート端が、"end"ノード1416に接続され、その矢の先端が、"loop"ノード1422に接続される。連続ブロック(例えば、Pのサブツリー)の宣言文は全て、解析ツリー1424の順序リストとして、アーク-B1418に付着される。40

#### 【0070】

表示されるブロックについては、ブロック名を、その名前を、"end"ノードにマップするテーブルの中にセーブしなければならない。このノードは、Verilogの"disabale"宣言文の、ジャンプ目的地となることもある。

#### 【0071】

Verilog条件文"if...else"や"case...endcase"は、ほぼ同じように処理される。Verilogの"if...else"文は、キーワード"i50

*f*"で始まり、その後に、その条件が真であるなら、実行されるべき発言 *E* や宣言 *S* 1 が、さらに、要すればあってもよいキーワード"*e l s e*"、および、条件が偽であるなら、実行されるべき宣言 *S* 2、が続く。全てのオプションをつけた"*i f*"宣言と、その制御フローグラフ減少の例を、図 15 に示す。

#### 【0072】

"*i f*"宣言文は、フォークノード 1506 とジョインノード 1508、および、それらを結ぶアーク 1510 と 1512、および、結合を、T に接続する新しいアーク 1514 を導入することによって、除去される。条件"*c o n d*"とそのブール否定"*! c o n d*"が、条件アーク 1510 と 1512 に注記される。これらアークは、各分枝が通過される条件を指定する。真または偽の分枝のいずれとも関連しない宣言文はないと考えられる。従って、このアークには何も注記されない。真(*S* 1)の分枝と偽(*S* 2)の分枝の宣言は、それぞれ、真のアーク 1510 と偽のアーク 1512 に注記される。場合(*c a s e*)宣言も同様に処理される。違いは、条件はデフォルトを含むことがあること、また、分枝の数が、2 よりも大きいことがあること、である。デフォルトは、他の全ての条件のロジック合計のロジック否定である。10

#### 【0073】

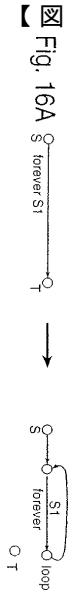

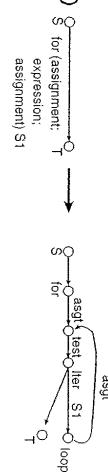

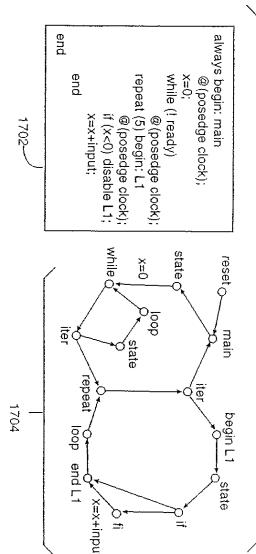

*V e r i l o g* におけるループは、幾つかの形の内のいずれを取ってもよい。それを、対応する制御フローグラフ減少と一緒に、図 16A - 16D に示す。ループを適正に動作させるためには、さらに新たに解析ツリーを構築する必要があるかも知れない。繰り返しループでは、新たな変数、すなわち、繰り返しカウンターが導入される。ループに導入する前に、その値を初期化しなければならない、また、それは、ループが実行する度毎に繰り上げられる。*"r e p e a t . . . w h i l e"* または *"f o r . . . l o o p"* では、条件を、"l t e r" と表示されるノードの、2 個のアウト-アークに付着させなければならない。20

#### 【0074】

*f o r e v e r* (無限) ループへの減少操作は、イン-アークを持たない T を設けることになる。これは、その制御フローグラフは、永久ループの減少操作後、語法的に不適切となることを意味する。しかしながら、これは、リセットノードから前方横断によって到達不能な、全てのアーク・ノードを除去することによって救済可能な一時的状態である。このような刈り込み救済措置は、制御フローグラフが完全に減少された後に、例えば、HDL テキストの制御フロー構築体の全てが減少された後に、実行される。30

#### 【0075】

刈り込み措置を減少操作終了時に行わなければならない理由は、*V e r i l o g* の *d i s a b l e* (無効) 宣言は、永久ループへの出口を強制的に設けることが可能だからである。このような出口は (*V e r i l o g* では)、T のある後続ノードへ行く。*V e r i l o g* の *d i s a b l e* は、結局、*b e g i n - e n d* 表示ブロックのエンドノードへの跳躍である。*d i s a b l e* が、ノード S からノード T へ向かうアーク A にたいして注記されている場合、この *d i s a b l e* は、A の接続を T から外すことによって、除去される。無効とされた (*d i s a b l e d*) ブロックに対応するエンドノード E が、ブロック名を、対応エンドノードにマップするテーブルにおいて求められる。このテーブルは、表示ブロックの減少操作時に構築される。A の矢の先端が E に接続される。*"( p o s e d g e \_ c l o c k )"* という形の事象制御宣言文は、單一ノードを付加し、かつ、それを状態と表示することによって、減少される。制御フローにたいして直接作用を持たない宣言文は除去されず、それぞれのアークに注記される。40

#### 【0076】

高レベル合成に適當な、簡単な *V e r i l o g HDL* テキスト 1702 の例を、図 17 の左に示す。そのテキストに対応する、完全減少制御フローグラフ 1704 を右に示す。一旦グラフ 1704 が完全に構築されたならば、グラフの意味を変えることなく後続ステップの効率の向上を可能とするために、若干の基本的刈り込みが必要になる。リセットノードから到達不能なノードやアークはいずれのものであっても除去が可能である。分枝か50

ら派生し、さらなるグラフ構造を持たないアーケの組も、まとめて取り潰しが可能であり、また、条件解析ツリーは、制御フローグラフに再度注記し直すことが可能である。グラフ構造は、ループ、状態、および、無効を含む。別態様として、これらのものが派生する条件文を、余剰分枝の創成以外に、制御フローグラフにたいしては何の作用も及ぼさないものとして、検出することが可能である。そのような場合、減少操作は単純には適用されず、条件文は、そのまま注記される。その条件が決して真になることはあり得ない、死んだ分枝、例えば、フォークノードのアウト-アーケは、いずれのものであっても除去が可能である。単純ノードは除去が可能であり、その複数のイン-アーケおよびアウト-アーケは合流が可能である。例えば、状態とマークされない、1個のイン-アーケと1個のアウト-アーケを持つノードのようである。

10

## 【0077】

ワン・ホットFSMは、その状態を、単項コードでコードされる。全ての状態は、1ビットを除く全てのビット組を偽とする2進数で表わされる。ワン・ホットコードの例として、0001、0010、0100、1000が挙げられる。一つを除く全てのビットがゼロであり、単一"hot bit"（「ホットビット」）は1である。このようなコードは、ワン・ホット性を失うことなく反転が可能である。例えば、1110、1101、1011、0111である。

## 【0078】

ワン・ホットFSMは、制御フローグラフの各状態ノードは、1対1的に、单一状態フリップフロップにマップすることが可能である、ということに注目して、抽出される。ワン・ホットFSMは、制御フローグラフに見られる状態ノードと同じ数のフリップフロップによって構築される。各フリップフロップ" F "が、一つの状態ノードに割り当てられる。Fの出力が1の場合、対応状態にあると予想する。

20

## 【0079】

制御フローグラフのアーケを、FSMの出力ポートにマップし、しかも、それが1対1マッピングである、テーブルMAPが構築される。制御フローグラフに見られるアーケと同じ数の出力ポートがFSMに構築される。テーブルMAPは、アーケを、FSMの出力ポートにマップすることによって機能する。位置MAP(A)は、制御フローグラファークAを、FSMの出力ピンにマップする。逆関数PAMは、FSMの出力ピンを、対応する制御フローグラファークにマップするのに用いられる。機能FLOPは、状態ノードを、フリップフロップにマップする。

30

## 【0080】

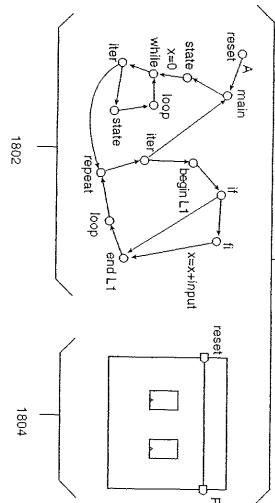

図18は、機能MAPを構築する工程を例示するのに役立つ。リセットアーケをFSM1804にマップした後、制御フローグラフ1802が示される。リセットノードのアウト-アーケは、それがなければ割り当たらないままだった出力ピンPに割り当たられる。"reset"と命名される入力ピンが構築され、直接Pに接続される。MAP(A)からPが設定される。次に、制御フローグラフ1802の状態ノード全てが考慮される。各ノードは、一つのイン-アーケと一つのアウト-アーケを持つ。例えば、状態ノード"N"における"C"と"D"である。ノードNは、割り当たれないフリップフロップFに、MAP(C)は、FのD-ピンに、そして、MAP(D)は、FのQ-ピンに、割り当たられる。FLOP(N)は、Fに設定される。これが、全ての状態ノードが割り当たられるまで繰り返される。こうして、状態ノードの全てのイン-アーケとアウト-アーケ、およびリセットがMAPに収められる。

40

## 【0081】

次ぎのステップは、状態ノードに入るアーケを観察することである。Cをそのようなアーケとしよう。MAP(C)は、状態フリップフロップのD-ピンに接続される。一次入力と状態フリップフロップによって駆動され、かつ、MAP(C)を駆動する回路が構築される。下の表のような再帰工程が、このような回路を構築する。

## 【0082】

## 【外5】

50

TABLE I Recursive Procedure

Procedure cct(c)

```

T = PAM(c);

N = { the node at the feather end of C }

If (N is a state node) {

Connect T to the Q pin of FLOP(N).

} else if (N is a join node with K in-arcs) {

G = a new k-input OR gate

Connect the output of G to T.

for (each in-arc A of N) {

Let P = MAP(A).

If (P is null) {

construct a new output pin named P.

set MAP(A) = P.

call cct(A).

}

connect P to an unconnected input pin of G.

}

} else if (N is a fork node) {

Construct a new 2-input AND gate G.

Connect the output of G to T.

Let A be the in-arc of N.

Let P = MAP(A).

If (P is null) {

Construct a new output pin named P.

Set map(A) = P

Call cct(A).

}

Connect one input of G to P

Make the other input of G a primary status input

Corresponding to the branch condition

That is annotated onto A.

} else if (N is the reset node) {

Connect P to the reset input.

} else{

Let A be the in-arc of N.

Let P = MAP(A).

If (P is null) {

Construct a new output pin named P.

Set map(A) = P

Call cct(A).

}

Connect P to T.

}

end

```

10

20

30

## 【0083】

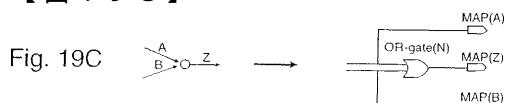

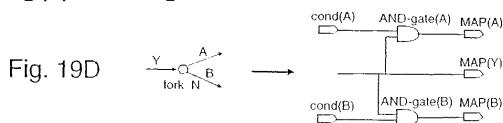

図19A - 19Dは、完全なワン・ホットFSMを、表の工程によって構築可能とする、各種断片構築体を示す。OR - ゲートとフリップフロップは、その関連するノードに因んで命名された。AND - ゲートは、その関連するアークに因んで命名された。分枝アークAとBに関連する状態は、一次入力cond(A)とcond(B)として取り扱った。全ての分枝条件は、他の場所で計算されたものと仮定する。

40

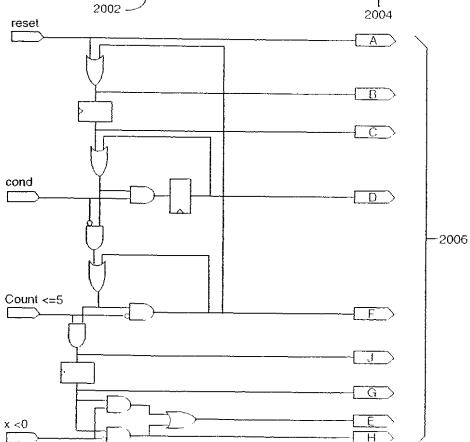

## 【0084】

図20は、Verilogテキストサンプル2002を、その対応する制御フローフラフ2004とワン・ホットFSM2006と共に示す。単純、非状態、非フォーク、非結合、非リセット、ノードによって接続されるアークに関連する冗長出力は取り潰された。簡単明瞭とするため、幾つかの制御出力も取り除いた。

## 【0085】

本発明の実施態様を構築するのに役立つと思われる、優良な一般的参考書が幾つか出版されている。例えば、De Michelis, Synthesis and Optimization of Digital Circuits, McGraw-Hill

50

1, 1994年がある。これは、スケジューリング、割り当て、および、高レベル、ロジック合成のその他の局面をカバーする。B. Gregory et al. 米国特許第5,661,661号、「レジスタおよびラッチ想定」。これは、HDLの使用法、および、制御フローグラフと同様の内部表示をカバーする。D. Knapp and M. Winslett, A Prescriptive Format Model for Data-Path hardware, IEEE Transactions on CAD, 1992年2月、158-184ページ。これは、制御フローグラフと構造と機能が類似の、データバスと制御ハードウェアの表示を記述する。この表示は、レジスタ予想、スケジューリングや割り当てに使用が可能なもので、再現の主要能力の必要サブセットである。これは、ユーザーまたはその他の代行者が、手動編集によって設計を「破壊」した場合、前記全ての補正に必要な情報を供給するものである。D. Knapp, Synthesis from Partial Structure in Design Methodologies for VLSI and Computer Architecture, D.A. Edwards編、Elsevier, 1989年がある。これは、本明細書に記載したものと類似の制御フローグラフを構築するために使用されるハードウェア記述言語について説明する。これも、レジスタ想定、および、他の構造的、行動的情報の想定に使用される。D. Knapp and A.C. Parker, A Unified Representation for Design Information in Proceedings of CHDL-85, Elsevier(1985年)は、本明細書で使用される制御フローグラフの早期版について、構造や行動の、他の再現法、および、設計の物理的レイアウトと一緒に、説明する。

#### 【0086】

本明細書では、本発明は、好ましい実施態様に関連して説明されたが、当業者であれば、本明細書に記載されているものの代わりに、他の運用を、本発明の精神や範囲を逸脱することなく、置換することが可能であることを直ちに認めるであろう。従って、本発明は、上述の請求項のみによって限定されるべきものとする。

#### 【図面の簡単な説明】

- 【図1】 インターネットウェブサイト、および、システム・オン・チップ設計者のためのEDAオンドマンド解決法を有するウェブサーバーを含む、本発明の、業者間アプリケーションサービスプロバイダ実施態様の機能的ブロックダイグラムである。

- 【図2】 本発明の、電子的設計自動化法実施態様のフローチャート図である。

- 【図3】 本発明の、タイミング分析法実施態様のフローチャート図である。

- 【図4】 4A、4Bおよび4Cは、回路から、ロジックツリー、および、簡素化ツリーへの移行を表わす模式図である。

- 【図5】 入力境界に一組の複雑モデルアーク、内部に一組の簡素化モデルアーク、さらに出力境界に別の一組の複雑モデルアークを含む設計をあらわす模式図である。

- 【図6】 電子的設計自動化における、一般的グラフ適合問題を示す模式図である。

- 【図7】 回路と、対応する、2部分グラフ表示の模式図である。

- 【図8】 ネットワークグラフと、一揃いのツリーに分割する、技術マッピングにおける最初のステップの模式図である。

- 【図9】 分解された技術ライブラリーを表わす模式図である。

- 【図10】 右に回路ツリーを示し、左に、その回路ツリーの全ての部分に適合させるのに必要とされる、ただ2個のパターンツリーを示す模式図。

- 【図11】 本発明のカバリング選択法実施態様の模式図である。

- 【図12】 回路のツリーへの分割、および、それらのツリーを順序付けて、基本規則に合致するリストに構成する模式図である。

- 【図13】 制御信号が、どのようにして最重要タイミング経路を支配することが可能なのかを示す実例の模式図である。

- 【図14】 ソースノードSとシンクノードTの間で、Verilogの時系列ブロック

10

20

30

40

50

"begin . . . end"が、制御フローグラフのアーク A に変換されるところを示す模式図である。

【図 15】 全てのオプションを含む"if"宣言文と、その制御フローグラフ減少の実例の模式図である。

【図 16】 16A - 16D は、Verilog における各種ループと、その対応制御フローグラフ減少を表わす模式図である。

【図 17】 左に、高レベル合成に好適な、簡単な Verilog HDL テキストを、右に、そのテキストに対応する、完全に減少された制御フローグラフを掲げる模式図である。

【図 18】 機能的 MAP を構築する手順を示す模式図である。 10

【図 19】 19A - 19D は、それによって、完全なワン・ホット FSM が、表の手順によって構築可能となる、各種断片構築を表わす模式図である。

【図 20】 Verilog のテキスト見本、その制御フローグラフ、および、最終的ワン・ホット FSM 間の一一致を示す模式図である。

【図 1】

【図 2】

Fig. 2

【図3】

Fig. 3

【図4】

【図5】

Fig. 5

【図6】

Fig. 6

【図7】

Fig. 7

【図8】

【図9】

Fig. 9

| inv   | ! a     |  |

|-------|---------|--|

| and2  | a b     |  |

| nand2 | ! (a b) |  |

| and4  | a b c d |  |

【図 10】

Fig. 10

【図 12】

Fig. 12

【図 11】

【図 13】

【図 14】

Fig. 14

【図 15】

Fig. 15

【図 16 A】

【図 16 B】

【図 16 C】

【図 16 D】

【図 17】

Fig. 17

【図 18】

Fig. 18

【図 19 A】

【図 19 B】

【図 19 C】

【図 19 D】

【図 20】

Fig. 20

## フロントページの続き

(51)Int.Cl.

F I

|         |       |       |

|---------|-------|-------|

| G 0 6 F | 17/60 | 3 3 2 |

| H 0 1 L | 21/82 | C     |

- (31)優先権主張番号 60/136,126

(32)優先日 平成11年5月26日(1999.5.26)

(33)優先権主張国 米国(US)

(31)優先権主張番号 09/574,572

(32)優先日 平成12年5月17日(2000.5.17)

(33)優先権主張国 米国(US)

(31)優先権主張番号 09/574,693

(32)優先日 平成12年5月17日(2000.5.17)

(33)優先権主張国 米国(US)

(31)優先権主張番号 09/577,426

(32)優先日 平成12年5月22日(2000.5.22)

(33)優先権主張国 米国(US)

(31)優先権主張番号 09/579,825

(32)優先日 平成12年5月25日(2000.5.25)

(33)優先権主張国 米国(US)

(72)発明者 ベルント ブラウン

アメリカ合衆国 カリフォルニア州 9 4 0 2 5 メンロ パーク フレモント アヴェニュー

6 2 4

(72)発明者 デヴィッド ナップ

アメリカ合衆国 カリフォルニア州 9 5 1 3 1 サンノゼ グース ポイント コモン 1 2 8

1

(72)発明者 ブラディーブ フエルナンデス

アメリカ合衆国 カリフォルニア州 9 5 1 3 2 サンノゼ ミリンダ ドライヴ 3 9 1 8

(72)発明者 ハンス - ヨーアヒム シュミット

ドイツ国 8 1 9 2 5 ミュンヘン ヴァーンフリートアレー 1 ベー

審査官 早川 学

(56)参考文献 特開平09-269957(JP, A)

特開昭62-202268(JP, A)

特開平11-282884(JP, A)

特開昭63-076065(JP, A)

Chakrabarti, D.R. et al., WADE: a Web-based Automated Parallel CAD Environment , PROCEEDINGS Fifth International Conference on High Performance Computing , IEEE , 1998年1月20日 , pp.473-480

長谷川拓己, 外4名, 大規模回路向けタイミング解析システムH E A R T (1)高速化の手法 , 情報処理学会全国大会講演論文集 , 情報処理学会 , 1987年 , Vol.35 , No.3 , p.2275-2276

(58)調査した分野(Int.Cl. , DB名)

G06F 17/50

G06Q 30/00

H01L 21/82