(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7076971号**

**(P7076971)**

(45)発行日 令和4年5月30日(2022.5.30)

(24)登録日 令和4年5月20日(2022.5.20)

(51)国際特許分類

H 01 L 27/146 (2006.01)

H 01 L 31/02 (2006.01)

F I

H 01 L 27/146

H 01 L 27/146

H 01 L 31/02

D

A

A

請求項の数 13 (全21頁)

(21)出願番号 特願2017-188985(P2017-188985)

(22)出願日 平成29年9月28日(2017.9.28)

(65)公開番号 特開2019-67826(P2019-67826A)

(43)公開日 平成31年4月25日(2019.4.25)

審査請求日 令和2年8月3日(2020.8.3)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110003281

特許業務法人大塚国際特許事務所

廣田 克範

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 佐々木 圭一

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 丹下 勉

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 田中 芳栄

最終頁に続く

(54)【発明の名称】 撮像装置およびその製造方法ならびに機器

**(57)【特許請求の範囲】****【請求項1】**

撮像装置であって、

光電変換部を有する基板と、

前記光電変換部の少なくとも一部を覆うように配された窒化シリコン層と、を備え、

前記窒化シリコン層は、シリコン、窒素、水素及び塩素を含み、

前記窒化シリコン層のN/Si組成比は1.05以上かつ1.2以下であり、

前記窒化シリコン層の塩素の組成比は、シリコン、窒素及び水素のそれぞれの組成比よりも低いことを特徴とする撮像装置。**【請求項2】**

撮像装置であって、

光電変換部を有する基板と、

前記光電変換部の少なくとも一部を覆うように配された窒化シリコン層と、を備え、

前記窒化シリコン層は塩素を含み、

前記窒化シリコン層のN/Si組成比は1.05以上かつ1.2以下であり、

前記窒化シリコン層の塩素濃度は2atomm%以上かつ6atomm%以下であることを特徴とする撮像装置。**【請求項3】**

前記撮像装置は、前記光電変換部に蓄積された電荷を転送するためのトランジスタのゲート電極を更に含み、

前記窒化シリコン層のうち前記光電変換部を覆う部分の下面と前記基板の表面との距離は、前記ゲート電極の上面と前記基板の表面との距離よりも小さいことを特徴とする請求項1又は2に記載の撮像装置。

**【請求項4】**

前記窒化シリコン層は、前記ゲート電極の上面及び側面を更に覆うことを特徴とする請求項3に記載の撮像装置。

**【請求項5】**

前記撮像装置は、前記窒化シリコン層と接し、前記光電変換部と前記窒化シリコン層との間に配された酸化シリコン層を更に備え、

前記窒化シリコン層の厚みは、前記酸化シリコン層の厚み以上であることを特徴とする請求項1乃至4の何れか1項に記載の撮像装置。 10

**【請求項6】**

前記窒化シリコン層は、反射防止層として機能することを特徴とする請求項1乃至5の何れか1項に記載の撮像装置。

**【請求項7】**

前記基板は增幅素子を有し、前記窒化シリコン層は前記光電変換部の上から前記增幅素子の上に延在することを特徴とする請求項1乃至6の何れか1項に記載の撮像装置。

**【請求項8】**

請求項1乃至7の何れか1項に記載の撮像装置と、

前記撮像装置から出力される信号を処理する処理部と、

を備えることを特徴とする機器。 20

**【請求項9】**

撮像装置の製造方法であって、

基板に光電変換部を形成する工程と、

前記光電変換部の少なくとも一部を覆う窒化シリコン層を形成する工程と、を有し、

前記窒化シリコン層は、シリコン、窒素、水素及び塩素を含み、

前記窒化シリコン層のN/Si組成比は1.05以上かつ1.2以下であり、

前記窒化シリコン層の塩素の組成比は、シリコン、窒素及び水素のそれぞれの組成比よりも低いことを特徴とする製造方法。 30

**【請求項10】**

撮像装置の製造方法であって、

基板に光電変換部を形成する工程と、

前記光電変換部の少なくとも一部を覆う窒化シリコン層を形成する工程と、を有し、

前記窒化シリコン層は塩素を含み、

前記窒化シリコン層のN/Si組成比は1.05以上かつ1.2以下であり、

前記窒化シリコン層の塩素濃度は2 atomic%以上かつ6 atomic%以下であることを特徴とする製造方法。 40

**【請求項11】**

前記窒化シリコン層はヘキサクロロジシランを含むプロセスガスを用いて形成されることを特徴とする請求項9又は10に記載の製造方法。

**【請求項12】**

前記プロセスガスはアンモニアを更に含み、

前記プロセスガスにおけるアンモニア/ヘキサクロロジシラン比は80以上かつ100以下であることを特徴とする請求項11に記載の製造方法。

**【請求項13】**

撮像装置の製造方法であって、

基板に光電変換部を形成する工程と、

前記光電変換部の少なくとも一部を覆う窒化シリコン層を形成する工程と、を有し、

前記窒化シリコン層はヘキサクロロジシランおよびアンモニアを含むプロセスガスを用いて形成され 50

前記プロセスガスにおけるアンモニア / ヘキサクロロジシラン比は 8.0 以上かつ 1.00 以下であることを特徴とする製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像装置およびその製造方法ならびに機器に関する。

【背景技術】

【0002】

光電変換部に入射した光を効率的に利用するために、光電変換部の上に反射防止層として機能する窒化シリコンを形成することが知られている。特許文献1には、原料ガスとしてヘキサクロロジシラン（HCD）を用いて、減圧CVD（LP-CVD）法によって、光電変換部の上に窒化シリコンを形成することが記載されている。10

【先行技術文献】

【特許文献】

【0003】

【文献】特開2013-84693号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明者は、光電変換部上に形成された窒化シリコン層の組成に応じて、太陽光などの強い光が光電変換部に当たった場合の画素の暗出力の変化量が異なることを見出した。本発明は、撮像装置の特性を向上するのに有利な技術を提供することを目的とする。20

【課題を解決するための手段】

【0005】

上記課題に鑑みて、撮像装置であって、光電変換部を有する基板と、前記光電変換部の少なくとも一部を覆うように配された窒化シリコン層と、を備え、前記窒化シリコン層は、シリコン、窒素、水素及び塩素を含み、前記窒化シリコン層のN/Si組成比は1.05以上かつ1.2以下であり、前記窒化シリコン層の塩素の組成比は、シリコン、窒素及び水素のそれぞれの組成比よりも低いことを特徴とする撮像装置が提供される。

【発明の効果】

【0006】

上記手段により、撮像装置の特性を向上するのに有利な技術が提供される。

【図面の簡単な説明】

【0007】

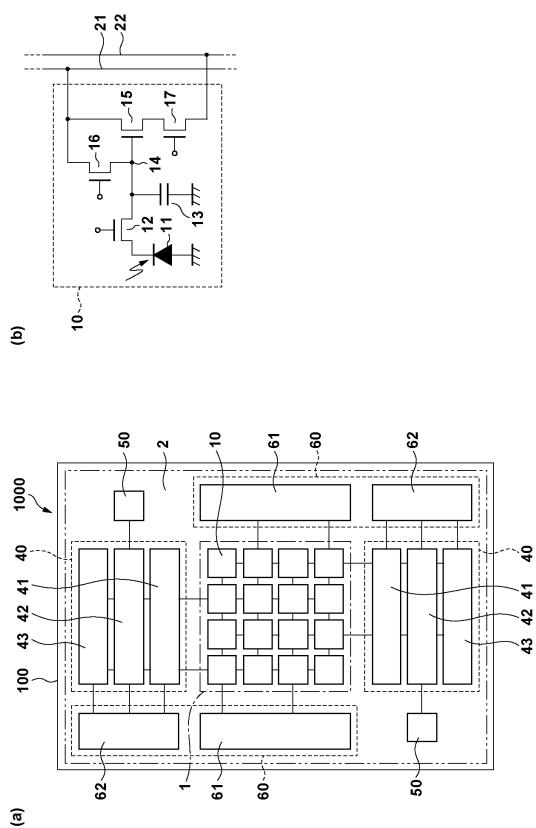

【図1】本発明の実施形態に係る撮像装置の構成例および撮像装置に配される画素の回路構成例を説明する図。

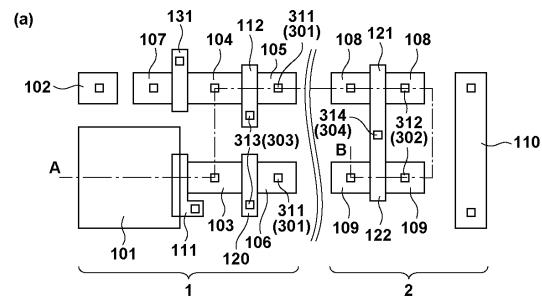

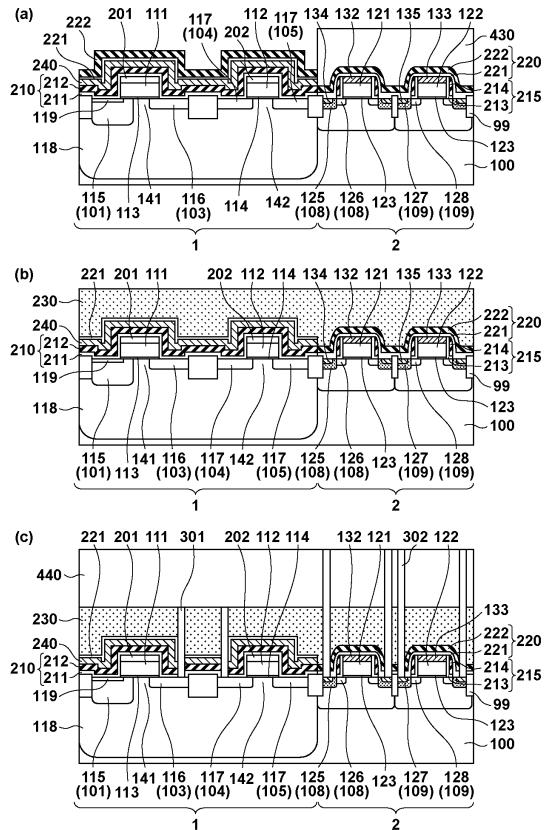

【図2】第1実施形態の撮像装置の構成例を示す平面図および断面図。

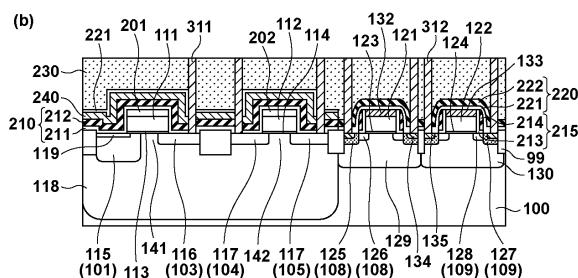

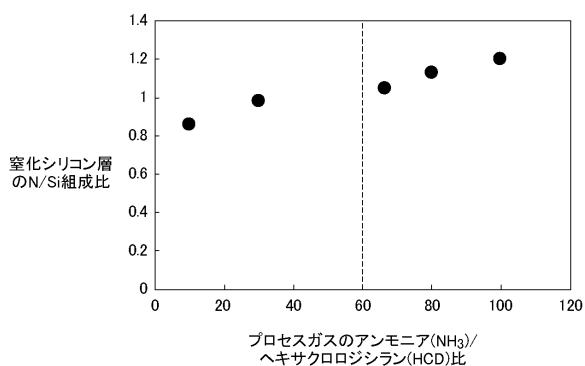

【図3】窒化シリコン層の塩素濃度と暗電流との関係および窒化シリコン層のN/Si組成比と暗出力の変化量との関係を説明する図。

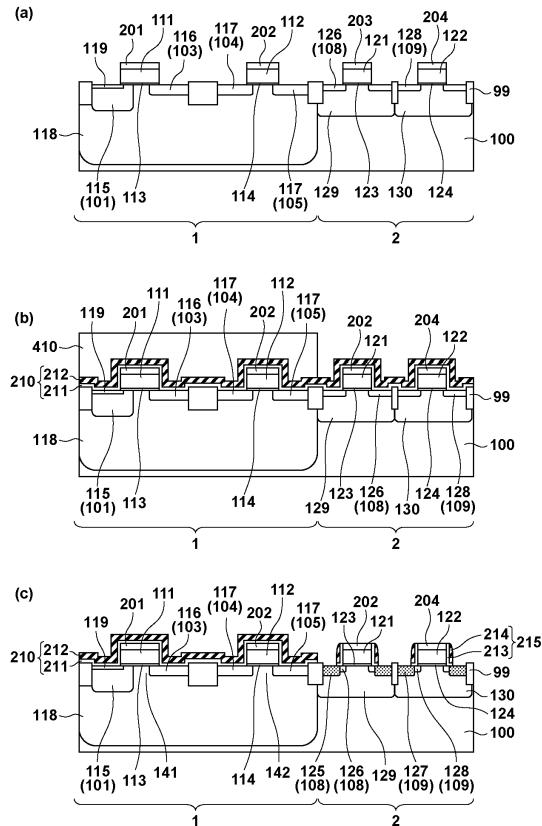

【図4】第1実施形態の撮像装置の製造方法の例を示す断面図。

【図5】第1実施形態の撮像装置の製造方法の例を示す断面図。

【図6】第1実施形態の撮像装置の製造方法の例を示す断面図。

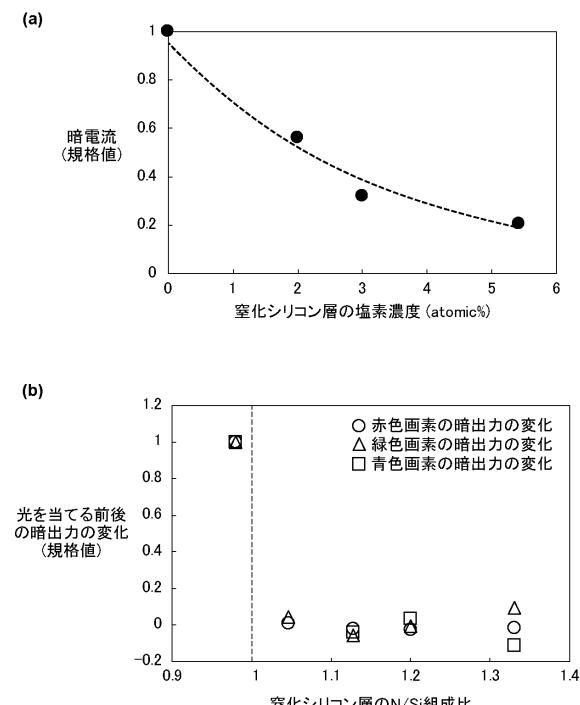

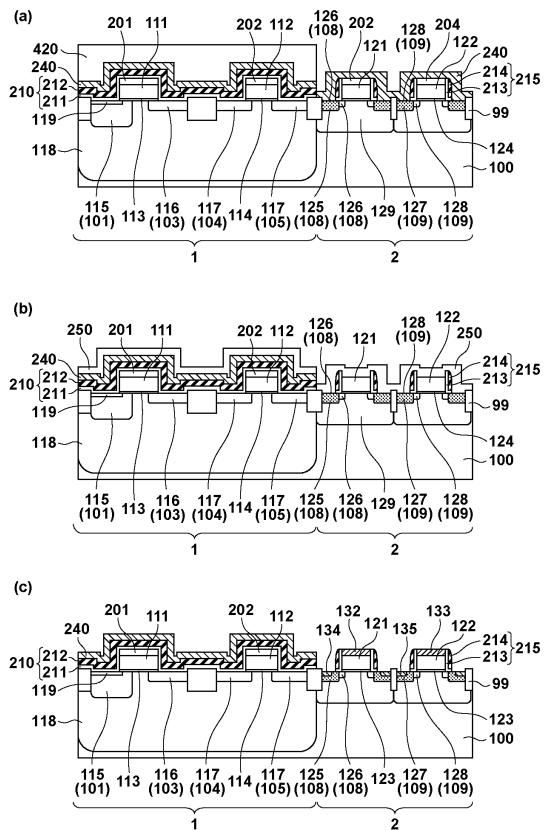

【図7】窒化シリコン層の成膜条件のプロセスガスにおけるアンモニア / ヘキサクロロジシラン比と窒化シリコン層のN/Si組成比との関係を説明する図。

【図8】第2実施形態の撮像装置の断面図。

【発明を実施するための形態】

【0008】

本発明に係る撮像装置の具体的な第1実施形態及び実施例を、添付図面を参照して説明する。以下の説明及び図面において、複数の図面に渡って共通の構成に共通の符号を付している。そのため、複数の図面を相互に参照して共通する構成を説明し、共通の符号を付し40

10

20

30

40

50

た構成については適宜説明を省略する。

#### 【0009】

図1～図6を参照して、本発明の第1実施形態による撮像装置の構成およびその製造方法について説明する。図1(a)は、本発明の第1実施形態における撮像装置1000の構成例を示す図である。撮像装置1000は、複数の画素10が配された画素領域1と、画素10から出力された信号の処理などを行う周辺回路が配された周辺回路領域2と、を備える。画素領域1と周辺回路領域2とは、同じ基板100に形成される。基板100は、例えばシリコンなどの半導体基板である。図1(a)において、一点鎖線で囲まれた領域が画素領域1であり、一点鎖線と二点鎖線との間の領域が周辺回路領域2である。周辺回路領域2は、画素領域1の周囲に位置するとも言え、画素領域1と基板100の縁との間に位置するとも言える。図1(a)に示す画素領域1は、複数の画素10が2次元アレイ状に配されたエリアセンサの例を示す。これに代えて、画素領域1は、複数の画素10が1次元方向に配されたリニアセンサであってもよい。

10

#### 【0010】

図1(b)は、画素領域1に配される個々の画素10の回路構成例を示す図である。画素10は、光電変換部11、転送素子12、容量素子13、増幅素子15、リセット素子16、および、選択素子17を含む。光電変換部11は、入射した光を電気信号に変換する。本実施形態において、基板100に形成されたフォトダイオードが光電変換部11として用いられる。

20

#### 【0011】

増幅素子15、リセット素子16、および、選択素子17として、それぞれ基板100に形成されたトランジスタが用いられる。本明細書において、画素10に配される各トランジスタを画素トランジスタと呼ぶ。画素トランジスタとして、絶縁ゲート型電界効果トランジスタ(Metal-Insulator-Semiconductor Field-Effect Transistor: MISFET)が用いられる。例えば、MISFETのうちゲート絶縁膜に酸化シリコンを用いたMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)を用いてもよい。しかし、ゲート絶縁膜はこれに限られることはなく、例えば、窒化シリコンであってもよい。また例えば、ゲート絶縁膜は、酸化ハフニウムなどのいわゆる高誘電率ゲート絶縁膜であってもよい。また、ゲート絶縁膜は、これらを積層してもよいし、例えば酸窒化シリコンのように化合物であってもよい。

30

#### 【0012】

転送素子12はMOS型ゲート構造を有する。このため、転送素子12をゲート、光電変換部11をソース、容量素子13をドレインとした場合、この構造をトランジスタとみなすことができる。このため、光電変換部11、転送素子12、および、容量素子13は、画素トランジスタと呼ばれる。

#### 【0013】

転送素子12は、光電変換部11で生じた信号電荷を容量素子13に転送する。容量素子13は、その容量と信号電荷の量に応じた電圧をノード14に生じさせる電荷電圧変換素子として機能する。増幅素子15のゲートは、ノード14を介して容量素子13に接続される。また、増幅素子15のドレインは電源線21に接続され、増幅素子15のソースは、選択素子17を介して出力線22に接続される。容量素子13および増幅素子15のゲートは、リセット素子16を介して電源線21に接続される、リセット素子16をオン動作させることによって、ノード14の電位が、電源線21の電位に応じた電位にリセットされる。また、選択素子17をオン動作させることによって、ノード14の電位に応じた信号が、増幅素子15から出力線22に出力される。画素10の構成は、図1(b)に示される構成に限られることではなく、入射した光に応じて光電変換部11で生成される電気信号を周辺回路領域2に出力できればよい。

40

#### 【0014】

本実施形態において、画素トランジスタに、チャネル(反転層)がn型のMOSFET(nMOSFET)をそれぞれ用いるが、チャネルがp型のpMOSFETが含まれてもよ

50

い。また、画素トランジスタにMISFET以外のトランジスタが含まれていてもよい。例えば、増幅素子15が、接合型電界効果トランジスタ(Janction FET: JFET)であってもよいし、バイポーラトランジスタであってもよい。

#### 【0015】

本明細書の以下の説明において、画素領域1において信号電荷として取り扱う電荷を多数キャリアとする導電型と一致する導電型を第1導電型、また、信号電荷として取り扱う電荷を少数キャリアとする導電型に一致する導電型を第2導電型と呼ぶ。例えば、信号電荷として電子を用いる場合、n型が第1導電型、p型が第2導電型となる。

#### 【0016】

再び図1(a)に戻り、周辺回路領域2について説明する。周辺回路領域2には、画素10で生成された電気信号を処理するための信号処理ユニット40が配される。また、周辺回路領域2には、信号処理ユニット40で処理された信号を撮像装置1000の外部に出力するための出力ユニット50や、複数の画素10が配された画素領域1や信号処理ユニット40を制御するための制御ユニット60を含む。信号処理ユニット40、出力ユニット50、および、制御ユニット60は、周辺回路と呼ばれる。

10

#### 【0017】

本実施形態において、信号処理ユニット40は、複数の列アンプを有する增幅回路41、複数のADコンバータを有する変換回路42、および、変換回路42からの出力を選択して出力ユニット50に出力するための水平走査回路43を含む。信号処理ユニット40は、相関二重サンプリング(CDS)処理や、パラレル・シリアル変換処理、アナログ・デジタル変換処理などを行いうる。出力ユニット50は、電極パッドや保護回路を含む。制御ユニット60は、垂直走査回路61やタイミング生成回路62を含む。周辺回路領域2の構成は、これに限られることはなく、画素領域1のそれぞれの画素10で生成された電気信号を適宜処理し、撮像装置1000の外部に出力できればよい。

20

#### 【0018】

周辺回路は、複数のトランジスタ、例えば画素トランジスタと同様にMISFETなどを用いて構成することができ、nMOSFETとpMOSFETとを含む相補型MOS(Complementary MOS: CMOS)回路で構成されうる。本明細書において、周辺回路を構成するトランジスタを周辺トランジスタと呼び、導電型を特定する場合は周辺nMOSFET、周辺pMOSFETと呼ぶ。また、周辺回路には、トランジスタやダイオードのような能動素子だけでなく、抵抗素子や容量素子などの受動素子が含まれてもよい。

30

#### 【0019】

次に、図2を用いて本実施形態の撮像装置1000の構造について説明する。図2(a)、(b)は、それぞれ、画素領域1および周辺回路領域2の一部を示す平面図および断面図である。

#### 【0020】

図2(a)において、領域101は光電変換部11、領域103は容量素子13および電荷を検出するためのノード14、領域106はリセット素子16のドレイン領域にそれ相応する。領域104は増幅素子15のソース領域、領域105は増幅素子15のドレイン領域、領域107は選択素子17のソースにそれ相応する。また、領域103はリセット素子16のソースを兼ね、領域104は選択素子17のドレイン領域を兼ねる。ゲート電極111は転送素子12のゲート、ゲート電極120はリセット素子16のゲート、ゲート電極112は増幅素子15のゲート、ゲート電極131は選択素子17のゲートにそれぞれ相応する。領域108、109は、それぞれ、周辺nMOSFET又は周辺pMOSFETのソース・ドレイン領域に相当する。また、ゲート電極121、122は、周辺nMOSFET又は周辺pMOSFETのゲートに相当する。本実施形態において、それぞれのゲート電極は、ポリシリコン(多結晶シリコン)によって構成される。また、本実施形態において、ゲート電極121およびゲート電極122は、一体で形成されるが、それぞれ独立して形成されてもよい。それぞれのゲート電極、ソース・ドレイン領域に相当する領域103～109は、コンタクトホール301、302、303、304に

40

50

埋め込まれた導電部材 311、312、313、314 を介して配線（不図示）に接続される。

#### 【0021】

図2(a)において、画素領域1には、画素10の基準コンタクト領域102が配される。基準コンタクト領域102は、配線（不図示）を介して画素10に、例えば接地電位などの基準電位を供給する。画素領域1に、複数の基準コンタクト領域102を配することによって、画素領域1において、基準電位がばらつくことを抑制し、撮像された画像にシェーディングが発生することを抑制することができる。

#### 【0022】

また、図2(a)において、周辺回路領域2には、抵抗素子110が配される。抵抗素子110は、基板100に形成された不純物領域であり、不純物領域の両端にコンタクトを設けることによって、不純物濃度、コンタクト間の距離および不純物領域の幅に応じた抵抗を得ることができる。本実施形態において、抵抗素子110の不純物領域は、第2導電型であるp型のウェルに形成された第1導電型であるn型の不純物領域である。これに代えて、抵抗素子110の不純物領域は、n型のウェルに形成されたp型の不純物領域であってもよい。また、n型の不純物領域によって構成される抵抗素子とp型の不純物領域によって構成される抵抗素子とが混在していてもよい。周辺回路領域2には、例えば、ポリシリコンによって構成されたMOS構造を有する容量素子や抵抗素子など、抵抗素子110以外の受動素子が配されてもよい。

10

#### 【0023】

本実施形態において、領域101、103や画素トランジスタのソース・ドレイン領域に相当する領域104、105、106、107、基準コンタクト領域102、周辺nMOSFETのソース・ドレイン領域に相当する領域108は、n型の不純物領域である。また、周辺pMOSFETのソース・ドレイン領域に相当する領域109は、p型の不純物領域である。

20

#### 【0024】

図2(b)は、図2(a)に示すA-B線における断面図を示す。基板100は、上述のようにシリコンなどの半導体基板である。基板100は、素子分離領域99によって複数の活性領域に区分される。素子分離領域99は、シャロートレンチアイソレーション(STI)法や選択酸化(LOCOS)法などによって形成された素子分離用の絶縁物によって構成される。それぞれの活性領域に不純物領域が形成され、それぞれの不純物領域が半導体素子を構成する。このため、素子分離領域として、pn接合分離をするための不純物領域(例えばp型の不純物領域)を設けてもよい。

30

#### 【0025】

基板100の活性領域には、それぞれの素子の導電型に応じた導電型を有するウェルが配される。画素領域1にはp型のウェル118が、周辺回路領域2にはp型のウェル129およびn型のウェル130が、それぞれ配される。また、図2(a)に示す基準コンタクト領域102には、p型のウェル118よりも不純物濃度が高いp型の不純物領域が配される。基準コンタクト領域102に接続された配線から、基準コンタクト領域102を介してウェル118に基準電位が供給される。

40

#### 【0026】

次いで、図2(b)を用いて、画素領域1および周辺回路領域2の断面構造について説明する。図2(b)および後述する図4~6において、説明のため、画素領域1と周辺回路領域2とを隣接させて示す。まず、画素領域1の断面構造について説明する。領域101には、光電変換部11を構成するn型の蓄積領域115が配される。蓄積領域115は、p型のウェル118とともにpn接合を構成し、光電変換部11のフォトダイオードとして機能する。蓄積領域115と基板100の表面との間には、光電変換部11を埋め込み型のフォトダイオードとするためのp型の表面領域119が配される。領域103には、容量素子13を構成する不純物領域116が配される。不純物領域116は、浮遊拡散領域となっている。增幅素子15、リセット素子16、および、選択素子17のソース・ド

50

レイン領域として、それぞれn型の不純物領域117が配される。図2(b)には、増幅素子15の断面が示されているが、リセット素子16および選択素子17も、同様の構成を有しうる。

#### 【0027】

ゲート絶縁膜113、114および画素10の他の画素トランジスタなどの素子のゲート絶縁膜は、酸化シリコンを主たる材料とするが、プラズマ窒化法や熱酸窒化法によって微量(例えば、10%未満)の窒素を含む酸化シリコンであります。窒素を含有する酸化シリコンは、純粋な酸化シリコンと比較して高い誘電率を有するため、トランジスタの駆動能力が向上しうる。しかし、ゲート絶縁膜の構成はこれに限られることはなく、ゲート絶縁膜は、純粋な酸化シリコンであってもよいし、窒化シリコンであってもよい。また、上述のように酸化ハフニウムなどの高誘電率材料を用いてもよいし、これらの材料の化合物や積層膜であってもよい。ゲート絶縁膜113、114を介して基板100の上に配されたゲート電極111、112の上面は、酸化シリコンや窒化シリコンを含む絶縁層201、202によって覆われる。

10

#### 【0028】

画素領域1の上には、酸化シリコン層211および窒化シリコン層212(第1窒化シリコン層)を含む絶縁膜210が配される。絶縁膜210は、絶縁層201、202を介してゲート電極111、112の上面を覆うとともに、絶縁層201、202を介さずにゲート電極111、112側面を覆う。つまり、窒化シリコン層212は、光電変換部11の上から増幅素子15の上に延在する。後述する窒化シリコン層212には、光電変換部11の特性向上だけでなく、増幅素子15の特性の向上にも有利に作用する。また、絶縁膜210は、図2(b)には示されないが、同様にゲート電極120、131の上面および側面を覆う。また、絶縁膜210は、光電変換部11を構成する領域101、それぞれの画素トランジスタのソース・ドレン領域に相当する領域103~107を覆う。この場合に、窒化シリコン層212のうち光電変換部11を構成する領域101を覆う部分の下面と基板100の表面との距離は、画素トランジスタのゲート電極の上面と基板100の表面との距離よりも小さくなる。窒化シリコン層212と基板100との間の距離が小さいほど、窒化シリコン層212の組成による影響が大きくなる。窒化シリコン層212と基板100との間の距離は、相対的には上述のようにゲート電極の上面との比較で規定できるが、窒化シリコン層212と基板100との間の距離は、典型的には100nm未満であり、50nm未満であってもよい、25nm未満であってもよい。

20

#### 【0029】

絶縁膜210は、酸化シリコン層211と窒化シリコン層212との積層膜である。酸化シリコン層211と窒化シリコン層212とは互いに接する界面を有する。本実施形態において、酸化シリコン層211は、ゲート電極111、112、120、131の側面と接しているが、酸化シリコン層211とゲート電極111、112、120、131の側面との間に別の層が挟まっていてもよい。また、酸化シリコン層211は、光電変換部11を構成する領域101、および、それぞれの画素トランジスタのソース・ドレン領域に相当する領域103~107に接し、基板100との界面を構成しているが、間に別の層が介在していてもよい。

30

#### 【0030】

波長が633nmである光に対する屈折率が約1.4~1.5の酸化シリコン層211と、同じ光に対する屈折率が約1.9~2.1の窒化シリコン層212との積層膜である絶縁膜210が、光電変換部11を構成する領域101を覆う。これによって、絶縁膜210は、光電変換部11に入射する光の反射防止層として用いることができる。良好な反射防止特性を得るために、窒化シリコン層212の厚みは、酸化シリコン層211の厚み以上であってもよい。さらに、窒化シリコン層212の厚みは、酸化シリコン層211の厚みよりも大きくてよい。

40

#### 【0031】

絶縁膜210の上には、絶縁膜210を覆うように保護膜240が配される。保護膜24

50

0は、酸化シリコンや窒化シリコンなどの絶縁体の単層膜や積層膜でありうる。保護膜240の上には、保護膜240を覆うように酸化シリコン層221が配される。酸化シリコン層221の上には、酸化シリコン層221を覆うように絶縁膜230が配される。絶縁膜230は、例えばBPSG、BSG、PSGなどのケイ酸塩ガラスや酸化シリコンでありうる。絶縁膜230の上面は、下地の表面の凸凹を実質的に反映しない平坦面である。

#### 【0032】

絶縁膜230、酸化シリコン層221、保護膜240および絶縁膜210には、それぞれを貫通するコンタクトホール301、303が形成される。コンタクトホール301、303には、配線(不図示)と画素トランジスタとの間を電気的に接続するための導電部材311、313が配される。図2(a)に示す構成では、導電部材311は、それぞれ画素トランジスタのソース・ドレイン領域に相当する領域103～107および基準コンタクト領域102に接続され、導電部材313は、ゲート電極111、112、120、131にそれぞれ接続される。導電部材311、313は、例えばタンゲステンなどの金属を主として構成されるコンタクトプラグである。

10

#### 【0033】

ここで、絶縁膜210の窒化シリコン層212に含まれる塩素の濃度について説明する。本発明者らは、窒化シリコン層212に含まれる塩素の濃度に応じて撮像装置の特性が変化することを実験によって見出した。具体的に、塩素を含む窒化シリコン層212が領域101を覆うことによって、窒化シリコン層212に含まれる塩素で光電変換部11のダングリングボンドが終端され、撮像装置1000の暗電流を低下させることができる。窒化シリコン層212は、窒化シリコン層212が覆う増幅素子15に対してもトランジスタのチャネルの界面準位を低減するので、増幅素子15のノイズ特性を向上できる。

20

#### 【0034】

図3(a)を参照して、窒化シリコン層212の塩素濃度と、暗電流との関係を説明する。図3(a)の横軸は窒化シリコン層212の塩素濃度を示し、縦軸は暗電流の値を示す。縦軸の値は、塩素濃度が0 atomic%である場合の暗電流の値が1となるように規格化されている。図3(a)から、窒化シリコン層212の塩素濃度が増加するにしたがって光電変換部11の暗電流が低下することがわかる。したがって、窒化シリコン層212に塩素を含めることによって、窒化シリコン層212に塩素を含めない場合と比較して、暗電流のレベルを低減できる。そこで、本実施形態において、窒化シリコン層212は塩素を含む。窒化シリコン層212に塩素が有意に含まれる場合の典型的な塩素濃度は0.1 atomic%以上であり、より典型的には0.3 atomic%以上である。窒化シリコン層212の塩素濃度は、1 atomic%未満であってもよい。暗電流を低減する上では窒化シリコン層212の塩素濃度は、1 atomic%以上であってもよいし、2 atomic%以上であってもよいし、3 atomic%以上であってもよい。また、窒化シリコン層212の塩素濃度が極端に高くなると、安定性や透過率が低下するため、窒化シリコン層212の塩素濃度は、10 atomic%以下であってもよいし、6 atomic%以下であってもよい。特に、塩素濃度を3 atomic%よりも高くすると、波長450 nmにおける入射光の光吸収係数(k値)が増大するため、塩素濃度は3 atomic%以下であってもよい。

30

#### 【0035】

続いて、絶縁膜210の窒化シリコン層212における窒素とシリコンの組成比(すなわち、N/Si組成比)について説明する。本発明者らは、絶縁膜210の窒化シリコン層212におけるN/Si組成比に応じて撮像装置の特性が変化することを実験によって見出した。具体的に、窒化シリコン層212のN/Si組成比が1.00未満の場合に、光の短波長側の光吸収係数(k値)が増大する。このため、領域101を覆う窒化シリコン層212のN/Si組成比が1.00未満の場合に、窒化シリコン層212によって入射光が吸収され、光電変換部11に入射した光を受光する領域の特性が劣化する。その結果、その後の撮影で撮像装置1000の光を当てる前後における暗出力が変化する。窒化シリコン(Si<sub>3</sub>N<sub>4</sub>)の化学量論組成比はN/Si=1.33であり、N/Si組成比1

40

50

. 0 0 未満の窒化シリコンはシリコンリッチな組成比となる。

#### 【 0 0 3 6 】

図3 ( b ) は、窒化シリコン層212のN / Si組成比と、光を当てる前後における暗出力の変化量との関係を説明する図である。図3 ( b ) の横軸はN / Si組成比を示し、縦軸は光を当てた後の暗出力(電流値)から光を当てる前の暗出力(電流値)を引いた値を示す。縦軸の値はN / Si組成比が0.98である場合の変化量が1になるように規格化されている。丸のプロットが赤色画素(すなわち、赤色光を検出する画素。他の色についても同様。)の暗出力の変化量、三角のプロットが緑色画素の暗出力の変化量、四角のプロットが青色画素の暗出力の変化量をそれぞれ示す。図3 ( b ) から、窒化シリコン層212のN / Si組成比が1.00以上の場合に、N / Si組成比が1.00未満の窒化シリコン層を用いた場合と比較して、暗出力の変化量が大幅に低減することがわかる。具体的に、N / Si組成比が0.98である場合の暗電流の変化量を1とした場合に、N / Si組成比が1以上かつ1.2以下の場合に暗電流の変化量はほぼ0となる。さらに、N / Si組成比が増加し、1.33となると、暗電流の変化量が増加することがわかる。そこで、本実施形態において、窒化シリコン層212のN / Si組成比は1.00以上かつ1.33未満であってもよい。さらに、窒化シリコン層212のN / Si組成比は1.10以上かつ1.30以下であってもよいし、窒化シリコン層212のN / Si組成比は1.15以上かつ1.25以下であってもよい。窒化シリコン層212のN / Si組成比が1.15以上かつ1.25以下である場合、窒化シリコン層212の塩素濃度は例えば0.5 atomic %以上であり、例えば0.7 atomic %以下である。

10

20

30

#### 【 0 0 3 7 】

次に、周辺回路領域2の断面構造について説明する。周辺nMOSFETのソース・ドレイン領域に相当する領域108には、n型の不純物領域125、n型の不純物領域126、シリサイド層134が配される。不純物領域125は、不純物領域126よりも不純物濃度が高い。シリサイド層134は、不純物領域125を覆う。周辺pMOSFETのソース・ドレイン領域に相当する領域109には、p型の不純物領域127、p型の不純物領域128、シリサイド層135が配される。不純物領域127は、不純物領域128よりも不純物濃度が高い。シリサイド層135は、不純物領域127を覆う。このように、周辺トランジスタは、高濃度の不純物領域125、127と、低濃度の不純物領域126、128によって低濃度不純物ドレイン(Lightly Doped Drain: LDD)構造を有する。

#### 【 0 0 3 8 】

ゲート電極121、122は、ゲート絶縁膜123、124を介して基板100の上に配される。本実施形態において、ゲート絶縁膜は画素10の画素トランジスタと同様に、酸化シリコンを主たる材料とし、プラズマ窒化法や熱酸窒化法によって微量(例えば、10%未満)の窒素を含む酸化シリコンである。周辺トランジスタのゲート絶縁膜123、124の厚みは、画素トランジスタのゲート絶縁膜113、114の厚み以下であってもよい。例えば、ゲート絶縁膜113、114の厚みが5.0 nm以上かつ10 nm以下であり、ゲート絶縁膜123、124の厚みが1.0 nm以上かつ5.0 nm以下であってもよい。画素トランジスタと周辺トランジスタとでゲート絶縁膜の厚みを異ならせることによって、画素トランジスタの耐圧向上と周辺トランジスタの駆動速度向上とを両立できる。ゲート電極121、122の上面には、ゲート電極121、122の一部を構成するシリサイド層132、133が配される。このように、周辺トランジスタは、シリサイド層132、133、134、135が形成されたサリサイド(Self Aligned silicide)構造を有することができる。シリサイド層を構成する金属成分として、チタン、ニッケル、コバルト、タングステン、モリブデン、タンタル、クロム、パラジウム、プラチナなどが用いられる。

40

#### 【 0 0 3 9 】

周辺トランジスタのゲート電極121、122の側面は、サイドウォール215に覆われる。サイドウォール215は、領域108、109の低濃度の不純物領域126、128

50

も覆う。本実施形態において、サイドウォール 215 は、酸化シリコン層 213 と窒化シリコン層 214 とを含む積層構造となっている。酸化シリコン層 213 は、窒化シリコン層 214 とゲート電極 121、122との間、および、窒化シリコン層 214 と領域 108、109との間に位置する。酸化シリコン層 213 と窒化シリコン層 214 とは、互いに接する界面を有する。

#### 【0040】

周辺回路領域 2 の上には、酸化シリコン層 221 および窒化シリコン層 222（第 2 窒化シリコン層）を含む絶縁膜 220 が配される。本実施形態において、絶縁膜 220 は、酸化シリコン層 221 と窒化シリコン層 222 との積層膜である。酸化シリコン層 211 と窒化シリコン層 212 とは互いに接する界面を有する。しかし、絶縁膜 220 は、窒化シリコン層 222 の単層膜であってもよい。酸化シリコン層 221 は、窒化シリコン層 214 と窒化シリコン層 222 との間に位置する。窒化シリコン層 214 と酸化シリコン層 221 とは、互いに接する界面を有する。つまり、サイドウォール 215 と絶縁膜 220 とは、互いに接する界面を有する。更に、絶縁膜 220 は、領域 108、109 のシリサイド層 134、135 を覆う。絶縁膜 220 と領域 108、109 のシリサイド層 134、135 とは、互いに接する界面を有する。本実施形態において、シリサイド層 134、135 が配されるが、シリサイド層 134、135 は配されなくてもよい。この場合、絶縁膜 220 は、高濃度の不純物領域 125、127 を覆う。絶縁膜 220 と高濃度の不純物領域 125、127 とは、互いに接する界面を有する。絶縁膜 220 の上には、画素領域 1 と同様に、絶縁膜 230 が配される。絶縁膜 230、酸化シリコン層 221 および窒化シリコン層 222 を含む絶縁膜 220 には、それぞれを貫通するコンタクトホール 302、304 が形成される。コンタクトホール 302、304 には、配線（不図示）と周辺トランジスタのソース・ドレイン領域である領域 108 およびゲート電極 121、122 との間を電気的に接続する導電部材 312、314 が配される。導電部材 312、314 は、導電部材 311、313 と同様に、例えばタングステンなどの金属を主として構成されるコンタクトプラグである。

#### 【0041】

絶縁膜 230 の上には、導電部材 311、312、313、314 と接続される配線を含む配線パターン（不図示）が配される。配線パターンは、層間絶縁層を介して複数の配線パターンが層間絶縁膜を介して積層されうる。配線パターンは、アルミニウムや銅などの金属によって構成されうる。また、基板 100 の光を入射させる受光面の側には、カラーフィルタ（不図示）やマイクロレンズ（不図示）などが配されうる。これらの構成は、既存の技術を用いて形成できるため、ここでは説明を省略する。撮像装置 1000 は、例えばパッケージに収容され、このパッケージを組み込んだ機器や情報端末などの撮像システムを構築することができる。

#### 【0042】

次に、撮像装置 1000 の製造方法について図 4～図 6 を用いて説明する。図 4～図 6 は、撮像装置 1000 のそれぞれの製造過程での断面図である。まず、図 4 (a) に示すように、画素トランジスタおよび周辺トランジスタを形成する。画素トランジスタおよび周辺トランジスタを形成する工程では、基板 100 に、STI 法や LOCOS 法などを用いて素子分離領域 99 を形成する。基板 100 は、シリコンインゴットから切り出したシリコンウェーハでもよいし、シリコンウェーハの上に単結晶シリコン層をエピタキシャル成長させたウェーハでもよい。素子分離領域 99 を形成した後、第 2 導電型（p 型）のウェル 118、129 および第 1 導電型（n 型）のウェル 130 を形成する。

#### 【0043】

ウェル 118、129、130 の形成後、ゲート絶縁膜 113、114、123、124 を形成し、ゲート絶縁膜 113、114、123、124 の上にポリシリコンを成膜する。ゲート絶縁膜 113、114、123、124 は、画素領域 1 と周辺回路領域 2 とで、同時に形成してもよい。また、上述のように、画素領域 1 と周辺回路領域 2 とで、膜厚を異ならせるため、別々の工程を用いて形成してもよい。次いで、対応するトランジスタの

10

20

30

40

50

導電型に合わせ、ポリシリコンのゲート電極となる各部分に、イオン注入法などを用いて不純物を注入する。不純物の注入後、ポリシリコンのゲート電極 111、112、121、122となる各部分の上にハードマスクとなる絶縁層 201、202、203、204を形成する。その後、絶縁層 201、202、203、204をマスクとして開口部のポリシリコンのエッチングを行う。この工程によって、n 型のゲート電極 111、112、121 および p 型のゲート電極 122 が形成される。

#### 【 0 0 4 4 】

次に、n 型の蓄積領域 115 および p 型の表面領域 119 を形成する。また、領域 103 の不純物領域 116、画素トランジスタのソース・ドレイン領域となるシングルドレイン構造の n 型の不純物領域 117 を形成する。更に、周辺トランジスタの LDD 構造の低濃度の n 型の不純物領域 126 および p 型の不純物領域 128 を形成する。画素 10 の不純物領域 116、117 を形成する際のドーズ量は、 $5 \times 10^{12} \sim 5 \times 10^{14}$  (ions / cm<sup>2</sup>) であってもよく、更に、 $1 \times 10^{13} \sim 1 \times 10^{14}$  (ions / cm<sup>2</sup>) であってもよい。また、LDD 構造を構成する低濃度の不純物領域 126、128 を形成する際のドーズ量は、 $5 \times 10^{12} \sim 5 \times 10^{14}$  (ions / cm<sup>2</sup>) であってもよく、更に、 $1 \times 10^{13} \sim 1 \times 10^{14}$  (ions / cm<sup>2</sup>) であってもよい。このため、不純物領域 116、117 および不純物領域 126 の不純物の注入は、並行して行ってよい。また、蓄積領域 115、不純物領域 116、117、126、128、および、表面領域 119 に不純物を注入する順番は、どのような順番で行ってよい。

10

#### 【 0 0 4 5 】

次いで、図 4 (b) に示すように、酸化シリコン層 211 および窒化シリコン層 212 を含む絶縁膜 210 を形成する。絶縁膜 210 は、ゲート電極 111、112、121、122 の上面および側面と、それぞれ画素トランジスタおよび周辺トランジスタのソース・ドレイン領域となる領域 103、104、105、108、109 と、領域 101 と、を覆う。ソース・ドレイン領域には、図 4 (a) に示す工程によって、不純物領域 116、117、126、128 がそれぞれ形成されており、絶縁膜 210 は不純物領域 116、117、126、128 を覆うことになる。

20

#### 【 0 0 4 6 】

絶縁膜 210 は、酸化シリコン層 211 と窒化シリコン層 212 との積層膜であり、酸化シリコン層 211 と窒化シリコン層 212 とが、互いに接するように形成される。絶縁膜 210 を形成する工程は、酸化シリコン層 211 を形成する工程と窒化シリコン層 212 を形成する工程とを含む。上述のように、絶縁膜 210 は、反射防止層として用いるため光電変換部 11 となる少なくとも領域 101 を覆い、良好な反射防止特性を得るために、窒化シリコン層 212 の厚みは、酸化シリコン層 211 の厚み以上であってもよい。例えば、酸化シリコン層 211 の厚みが 5 nm 以上かつ 20 nm 以下、窒化シリコン層 212 の厚みが 20 nm 以上かつ 100 nm 以下であってもよい。

30

#### 【 0 0 4 7 】

本実施形態において、酸化シリコン層 211 および窒化シリコン層 212 は、化学気相成長 (Chemical Vapor Deposition : CVD) 法を用いて形成される。酸化シリコン層 211 は、例えば TEOS などのソースガスを含むプロセスガスの圧力 (成膜圧力) を 20 Pa 以上かつ 200 Pa 以下の範囲とした熱 CVD 法である減圧 CVD (LPCVD) 法を用いて形成される。このとき、成膜温度 (基板温度) は、500 以上かつ 800 以下の範囲であってもよい。ここでプロセスガスとは、少なくともソースガスを含み、必要に応じて添加されたキャリアガスを含む成膜チャンバ内のガス全体を意味する。キャリアガスには、ヘリウムやアルゴンなどの希ガスや窒素などが用いられる。また、成膜圧力とは、成膜チャンバ内のプロセスガスの圧力 (全圧) を意味する。

40

#### 【 0 0 4 8 】

窒化シリコン層 212 は、例えばソースガスとしてアンモニア (NH<sub>3</sub>) とヘキサクロロジシラン (HCD) とを含むプロセスガスを用いて LPCVD 法を用いて形成される。このとき、プロセスガスの圧力 (成膜圧力) を 20 Pa 以上かつ 200 Pa 以下の範囲であ

50

り、成膜温度（基板温度）は、500以上かつ800以下の範囲であってもよい。

#### 【0049】

上述したように、暗電流の低減と暗出力の変化量の低減とを実現するために、本実施形態では、反射防止層として用いる窒化シリコン層212のN/Si組成比は1.00以上かつ1.33未満であり、窒化シリコン層212が塩素を含む。図7は、窒化シリコン層212の成膜条件のプロセスガスにおけるアンモニア/ヘキサクロロジシラン比（以下、NH<sub>3</sub>/HCD比）と、窒化シリコン層212のN/Si組成比の関係を説明する図である。図7の横軸はNH<sub>3</sub>/HCD比を示し、縦軸は窒化シリコン層212のN/Si組成比を示す。図7から、NH<sub>3</sub>/HCD比が増加するにしたがって、N/Si組成比が増加することがわかる。本実施形態では、窒化シリコン層212のN/Si組成比を1.00以上とするために、NH<sub>3</sub>/HCD比を60以上とする。また、窒化シリコン層212のN/Si組成比を1.33未満とするために、NH<sub>3</sub>/HCD比を120未満とする。

10

#### 【0050】

窒化シリコン層212のN/Si組成比を約1.00にするための窒化シリコン層212の成膜条件として、例えば以下の条件を採用することができる。

成膜温度：550～650

HCD：20～40 sccm

NH<sub>3</sub>：1300～2700 sccm

成膜圧力：20～30 Pa

20

#### 【0051】

また、窒化シリコン層212のN/Si組成比を約1.10にするための窒化シリコン層212の成膜条件は、例えば以下の条件を採用することができる。

成膜温度：550～650

HCD：15～35 sccm

NH<sub>3</sub>：1200～2800 sccm

成膜圧力：20～30 Pa

20

#### 【0052】

また、窒化シリコン層212のN/Si組成比を約1.20にするための窒化シリコン層212の成膜条件は、例えば以下の条件を採用することができる。

成膜温度：550～650

30

HCD：10～30 sccm

NH<sub>3</sub>：1000～3000 sccm

成膜圧力：20～30 Pa

#### 【0053】

プロセスガス中のHCDおよびNH<sub>3</sub>の流量を増減させることによって、窒化シリコン層212のN/Si組成比を変更可能である。

#### 【0054】

ここで、ヘキサクロロジシラン（HCD）およびアンモニア（NH<sub>3</sub>）をソースガスに含むプロセスガスを用いて形成された窒化シリコン層212には、シリコン、窒素、塩素に加えて、特許文献1に示されるように、多くの水素が含まれる。このため、窒化シリコン層212は、画素トランジスタのダンギングボンドを終端するための水素供給源となりうる。また、少なくとも窒化シリコン層212を形成した際、窒化シリコン層212の塩素の組成比は、シリコン、窒素および水素のそれぞれの組成比よりも低くてもよい。換言すれば、窒化シリコン層212の水素の組成比は、窒化シリコン層212の塩素の組成比よりも高くてよい。窒化シリコン層212の水素の組成比は、窒化シリコン層212のシリコンの組成比および窒素の組成比よりも高くてよいし、低くてもよい。水素は軽元素であるため、窒化シリコン層212の水素は窒化シリコン層212の化学量論的組成の考慮に含めなくてよい。

40

#### 【0055】

絶縁膜210の形成後、周辺トランジスタのゲート電極121、122の側面にサイドウ

50

オール 215 を形成する。まず、図 4 ( b ) に示すように、絶縁膜 210 の上に例えればフォトレジストを用いてマスクパターン 410 を形成する。マスクパターン 410 は、画素領域 1 の光電変換部 11 となる領域 101 の少なくとも一部を覆うように形成される。マスクパターン 410 が、領域 101 の少なくとも一部を覆うことによって、N / Si 組成比が 1.00 以上かつ 1.33 未満であり塩素を含む窒化シリコン層 212 が、領域 101 の少なくとも一部の上に残存することになる。本実施形態において、マスクパターン 410 は、領域 101、103、104、105 を含む画素領域 1 を覆い、周辺回路領域 2 に開口部を有する。次いで、マスクパターン 410 の開口部の絶縁膜 210 をエッティング（エッチバック）する。エッティング後にマスクパターン 410 を除去することによって、図 4 ( c ) に示される周辺トランジスタのゲート電極 121、122 の側面を覆うサイドウォール 215 が形成される。サイドウォール 215 は、酸化シリコン層 213 および窒化シリコン層 214（第 3 窒化シリコン層）の積層体で構成される。酸化シリコン層 213 は、絶縁膜 210 の酸化シリコン層 211 の一部であり、窒化シリコン層 214 は、絶縁膜 210 の窒化シリコン層 212 の一部である。このため、N / Si 組成比および塩素濃度は、窒化シリコン層 214 と窒化シリコン層 212 とで互いに等しい。

#### 【 0056 】

このサイドウォール 215 を形成するエッティングにおいて、領域 108 のうち不純物領域 125、127 を形成する領域が露出する。また、このエッティング工程において、図 2 ( a ) に示す抵抗素子 110 が形成される領域が露出する。

#### 【 0057 】

サイドウォール 215 を形成するエッティングの間、マスクパターン 410 が領域 101 を覆うことによって、絶縁膜 210 の領域 101 の上の部分が残存する。これによって、光電変換部 11 へのエッティングの際のダメージが抑制され、光電変換部 11 で生じるノイズを低減することができる。また、マスクパターン 410 がゲート電極 111、112 や領域 103、104 を覆うことで、画素トランジスタのチャネル領域 141、142 やソース・ドレイン領域の上に配された絶縁膜 210 が残存する。これによって、画素トランジスタへのエッティングの際のダメージが抑制され、それぞれの画素トランジスタで生じるノイズを低減することができる。

#### 【 0058 】

サイドウォール 215 を形成するエッティングにおいて、領域 108 のうち不純物領域 125、127 を形成する領域が露出させた後、サイドウォール 215 の側面に沿って自己整合された高濃度の不純物領域 125、127 を形成する。画素領域 1 および周辺 pMOSFET を覆うマスクパターンを形成し、当該マスクパターン、ゲート電極 121 およびサイドウォール 215 をマスクとして、イオン注入法などを用いて n 型の不純物を注入する。これによって、周辺 nMOSFET の不純物領域 125 が形成される。また、画素領域 1 および周辺 nMOSFET を覆うマスクパターンを形成し、当該マスクパターン、ゲート電極 122 およびサイドウォール 215 をマスクとして、イオン注入法などを用いて p 型の不純物を注入する。これによって、周辺 pMOSFET の不純物領域 127 が形成される。不純物領域 125 および不純物領域 127 を形成する順序は任意である。LDD 構造を構成する高濃度の不純物領域 125、127 を形成する際のドーズ量は、 $5 \times 10^14 \sim 5 \times 10^{16}$  (ions/cm<sup>2</sup>) であってもよく、更に、 $1 \times 10^{15} \sim 1 \times 10^{16}$  (ions/cm<sup>2</sup>) であってもよい。不純物領域 125、127 を形成する際のドーズ量は、上述の不純物領域 126、128 を形成する際のドーズ量よりも高い。結果として、不純物領域 125、127 の不純物濃度は、不純物領域 126、128 の不純物濃度よりも高くなる。

#### 【 0059 】

不純物領域 125 および不純物領域 127 の少なくとも一方を形成する際、抵抗素子 110 を形成するための領域に、同時に不純物が注入されてもよい。これによって、拡散抵抗としての抵抗素子 110 が形成される。不純物領域 126、128 を形成する際のドーズ量では不純物濃度が低く、抵抗素子 110 の抵抗値を実用的な範囲まで低くできない可能

10

20

30

40

50

性がある。一方、不純物領域 125、127を形成する際のドーズ量は、実用的な抵抗値の抵抗素子110の不純物領域を形成しうる。そこで、サイドウォール215を形成するエッティングの際に抵抗素子110を形成する領域を露出させ、不純物領域125または不純物領域127への不純物の注入と同時に抵抗素子110の不純物領域を形成する。

#### 【0060】

周辺トランジスタのLDD構造を形成した後、図5(a)に示すように、画素領域1および周辺回路領域2を覆うように保護膜240を形成する。保護膜240は、例えば酸化シリコンなどを用い、厚さは30nm以上かつ130nm以下程度である。保護膜240の形成後、フォトレジストなどを用いて画素領域1を覆うマスクパターン420を形成する。マスクパターン420の形成後、マスクパターン420の開口部分の保護膜240をエッティングする。このエッティングによって、保護膜240のうち領域108、109の上に位置する部分およびゲート電極121、122の上に位置する部分が除去される。このとき、保護膜240のうち画素領域1の上に位置する部分および抵抗素子110の上に位置する部分は残存させる。保護膜240のエッティングに続いて、ゲート電極121、122の上面を覆う絶縁層203、204を除去する。絶縁層203、204のエッティングは、保護膜240のエッティングと同時に行ってもよいし、別々に行ってもよい。保護膜240および絶縁層203、204のエッティングの後、マスクパターン420は除去される。

10

#### 【0061】

次いで、図5(b)に示すように、基板100を覆うようにスパッタ法やCVD法などを用いて金属膜250を形成する。金属膜250は、領域108、109およびゲート電極121、122の上面に接するように形成され、領域108、109およびゲート電極121、122の上面をシリサイド化する金属を含む。また、金属膜250は、シリサイド化しない画素領域1や抵抗素子110の上では、保護膜240と接する。金属膜250は、シリサイド化のための金属と、その金属の酸化を抑制するための金属化合物との積層構造であってもよい。例えば、金属膜250は、コバルトとコバルトの酸化を抑制するための窒化チタンとの積層膜であってもよい。

20

#### 【0062】

金属膜250の形成後、基板100を500程度に加熱することによって、金属膜250と金属膜250と接する領域108、109およびゲート電極121、122とを反応させる。これによって、モノシリサイド状態のシリサイド層132、133、134、135が形成される。その後、保護膜240やサイドウォール215の上に位置する未反応の金属膜250を除去する。また、金属膜250に金属の酸化を抑制するための金属化合物の層を形成した場合、この金属化合物の層も除去する。未反応の金属膜250を除去した後、1度目のシリサイド化で用いた温度よりも高い800程度に基板100を加熱し、シリサイド層132、133、134、135をモノシリサイド状態からダイシリサイド状態に変化させる。本実施形態において、温度の異なる2度の加熱を行うが、1度の加熱でシリサイド層132、133、134、135を形成してもよい。シリサイド化の条件は、シリサイドを形成するための金属の種類などによって、適宜選択すればよい。

30

#### 【0063】

シリサイド化の工程において、保護膜240を残存させた画素領域1や抵抗素子110では、金属膜250と基板100やゲート電極とが接しないため、シリサイド層が形成されない。保護膜240は、このようにシリサイドブロックとして機能する。シリサイド層は、画素領域1においてノイズの原因となりうるため、画素領域1はシリサイド化の際に保護膜240によって覆われる。特に、光電変換部11となる領域101、電荷を検出するためのノード14となる領域103、增幅素子15のソース・ドレイン領域となる領域104、105をシリサイド化しない。また、抵抗素子110においても、抵抗値が小さくなりすぎる可能性があるため、保護膜240によって保護する。シリサイド層132、133、134、135を形成した後、保護膜240を除去してもよい。また、画素領域1への不要なダメージを避けるため、保護膜240を除去しなくてもよい。本実施形態において、図5(c)に示すように保護膜240を残存させる。

40

50

**【 0 0 6 4 】**

シリサイド層 132、133、134、135の形成後、図 6 (a) に示すように、酸化シリコン層 221 および窒化シリコン層 222 を含む絶縁膜 220 を形成する。絶縁膜 220 は、ゲート電極 111、112、121、122 の上面と、サイドウォール 215 と、それぞれ画素トランジスタおよび周辺トランジスタのソース・ドレイン領域となる領域 103、104、105、108、109 と、領域 101 と、を覆う。

**【 0 0 6 5 】**

絶縁膜 220 は、酸化シリコン層 221 と窒化シリコン層 222 との積層膜である。酸化シリコン層 221 と窒化シリコン層 222 とは、互いに接するように形成される。絶縁膜 220 を形成する工程は、酸化シリコン層 221 を形成する工程と窒化シリコン層 222 を形成する工程とを含む。窒化シリコン層 222 の厚みは、酸化シリコン層 221 の厚み以上であってもよい。窒化シリコン層 222 の厚みが、酸化シリコン層 221 の厚みの 2 倍以上であってもよい。例えば、酸化シリコン層 211 の厚みが 10 nm 以上かつ 30 nm 以下、窒化シリコン層 212 の厚みが 20 nm 以上かつ 100 nm 以下であってもよい。

10

**【 0 0 6 6 】**

酸化シリコン層 211 は、例えば T E O S などのソースガスを含むプロセスガスの圧力（成膜圧力）を 200 Pa 以上かつ 600 Pa 以下の範囲とした熱 C V D 法である準常圧 C V D ( S A - C V D ) 法を用いて形成される。このとき、成膜温度（基板温度）は、400 以上かつ 500 以下の範囲であってもよい。このように、酸化シリコン層 211 と酸化シリコン層 221 とは、ともに熱 C V D 法を用いて形成されうる。

20

**【 0 0 6 7 】**

窒化シリコン層 222 は、例えばソースガスとしてアンモニア ( N H 3 ) とヘキサクロロジシラン ( H C D ) とを含むプロセスガスを用いて L P C V D 法を用いて形成される。このとき、プロセスガスの圧力（成膜圧力）を 20 Pa 以上かつ 200 Pa 以下の範囲であり、成膜温度（基板温度）は、500 以上かつ 800 以下の範囲であってもよい。

**【 0 0 6 8 】**

窒化シリコン層 222 は、周辺トランジスタに対して塩素を安定的に供給する塩素供給膜としても機能しうる。厚い窒化シリコン層 222 は、塩素を豊富に含むことができ、薄い酸化シリコン層 221 は、塩素を適切に透過させることができる。また、上述したようにヘキサクロロジシラン ( H C D ) およびアンモニア ( N H 3 ) をソースガスに含むプロセスガスを用いて形成された窒化シリコン層 222 は、多くの水素を含む。このため、ノイズ特性の優れた周辺トランジスタを形成することが可能となる。

30

**【 0 0 6 9 】**

絶縁膜 220 の形成後、図 6 (a) に示すように、絶縁膜 220 の周辺回路領域 2 に位置する部分を覆うように、フォトレジストなどを用いてマスクパターン 430 を形成する。次いで、マスクパターン 430 の開口部を介して、窒化シリコン層 212 の画素領域 1 に配された部分をエッティングによって除去する。窒化シリコン層 212 の除去される部分は、窒化シリコン層 212 のうち光電変換部 11、転送素子 12、容量素子 13、増幅素子 15、リセット素子 16、および、選択素子 17 の上に位置する部分を含む。このとき、酸化シリコン層 221 は、画素領域 1 を覆う窒化シリコン層 222 をエッティングによって除去する際のエッティングストップとして機能しうる。また、酸化シリコン層 221 は、画素領域 1 をエッティングによるダメージから保護する保護層としても機能しうる。画素領域 1 のうち少なくとも光電変換部 11 の上に配される窒化シリコン層 222 を除去する。

40

**【 0 0 7 0 】**

次に、画素領域 1 および周辺回路領域 2 を覆うように絶縁膜 230 を形成する。絶縁膜 230 は、例えば、高密度プラズマ ( High Density Plasma : H P D ) C V D 法などのプラズマ C V D 法によって成膜された酸化シリコンの単層膜である。絶縁膜 230 は、B P S G 膜、B S G 膜、P S G 膜などの任意の材料から形成可能である。また、単層膜に限らず複層膜であってもよい。

**【 0 0 7 1 】**

50

次いで、図 6 ( b ) に示されるように、絶縁膜 230 の表面を平坦化する。平坦化の手法としては、化学機械研磨 ( C M P ) 法や、リフロー法、エッチバック法などが用いられる。これらの手法を組み合わせて用いてもよい。平坦化前の絶縁膜 230 の厚みは、例えば、200 nm 以上かつ 1700 nm 以下の範囲でありうる。本実施形態において、窒化シリコン層 222 の画素領域 1 の上に位置する部分が上述の工程によって除去されているため、絶縁膜 230 の下地の画素領域 1 と周辺回路領域 2 との高低差が小さい。このため、平坦化後の絶縁膜 230 の厚みを 1000 nm 以下とすることができる。例えば、絶縁膜 230 の厚みは、450 nm 以上かつ 850 nm 以下であってもよい。絶縁膜 230 の厚みを薄くすることによって、コンタクトプラグの抵抗の低減や感度の向上を図ることができる。ここで、平坦化後の絶縁膜 230 の厚みは、絶縁膜 210 および絶縁膜 220 の厚みよりも大きくてよい。

10

#### 【 0072 】

絶縁膜 230 の平坦化後、画素トランジスタや周辺トランジスタと配線との間を電気的に接続するための導電部材 311、312、313、314 を形成する。まず、画素領域 1 において、絶縁膜 230 を覆うフォトレジストなどを用いたマスクパターンの開口部を介して、絶縁膜 230 を異方性ドライエッティングによって開口し、導電部材 311 を設けるためのコンタクトホール 301 を形成する。コンタクトホール 301 を形成する際、画素領域 1 において絶縁膜 210 の窒化シリコン層 212 をエッティングストップとして用いてもよい。コンタクトホール 301 は、絶縁膜 230、酸化シリコン層 221、保護膜 240、窒化シリコン層 212 および酸化シリコン層 211 を貫通して設けられる。コンタクトホール 301 は、容量素子 13、増幅素子 15、リセット素子 16、選択素子 17 のそれぞれソース・ドレイン領域や基準コンタクト領域 102 を露出する。

20

#### 【 0073 】

コンタクトホール 301 の形成に並行して、容量素子 13、増幅素子 15、リセット素子 16、選択素子 17 のそれぞれゲート電極を露出するコンタクトホール 303 を形成する。導電部材 313 を設けるためのコンタクトホール 303 は、絶縁膜 230、酸化シリコン層 221、保護膜 240、窒化シリコン層 212 および酸化シリコン層 211 を貫通する。更に、導電部材 313 を設けるためのコンタクトホールは、絶縁層 201、202 も貫通する。コンタクトプラグの接触抵抗を低減するために、コンタクトホールを介して基板 100 の不純物領域およびゲート電極に不純物を注入してもよい。

30

#### 【 0074 】

コンタクトホール 301 の形成前に、上述したように画素領域 1 の上に位置する窒化シリコン層 222 は除去される。このため、エッチストップとして用いる窒化シリコン層 212 よりも上の層に窒化シリコン層が存在しない。したがって、コンタクトホール 301 を形成する際、窒化シリコン層 212 以外の窒化シリコン層でコンタクトホール 301 の形成が妨げられることを抑制できる。

#### 【 0075 】

次いで、図 6 ( c ) に示すように、周辺回路領域 2 において、絶縁膜 230 を覆い、コンタクトホール 302、304 を形成する領域に開口部を有するマスクパターン 440 を用いて、絶縁膜 230 を異方性ドライエッティングによって開口する。これによって、導電部材 312、314 を設けるためのコンタクトホール 302、304 が形成される。コンタクトホール 302 を形成する際に、周辺回路領域 2 において絶縁膜 220 の窒化シリコン層 222 をエッティングストップとして用いることができる。コンタクトホール 302、304 は絶縁膜 230、窒化シリコン層 222、および、酸化シリコン層 221 を貫通して設けられる。コンタクトホール 302 は、周辺トランジスタのソース・ドレイン領域となる領域 108、109 に位置するシリサイド層 134、135 を露出する。コンタクトホール 302 の形成に並行して、導電部材 314 を設けるためのゲート電極 121、122 のシリサイド層 132、133 を露出するコンタクトホール 304 を形成する。

40

#### 【 0076 】

コンタクトホール 301、302、303、304 の開口後、コンタクトホール 301、

50

302、303、304に金属などの導電体を充填することによって、コンタクトプラグとして機能する導電部材311、312、313、314が形成される。コンタクトホール301、302、303、304への導電部材の充填は、一括して行うことができる。

#### 【0077】

画素領域1にコンタクトホール301、303を形成し導電部材311、313を充填する工程と、周辺回路領域2にコンタクトホール302、304を形成し導電部材312、314を充填する工程と、を別々の工程としてもよい。コンタクトプラグを形成する工程を画素領域1と周辺回路領域2とで別々にすることによって、シリサイド層132、133、134、135に含まれる金属が、コンタクトホール301、303を介して画素領域1の不純物領域を汚染することを抑制できる。画素領域1と周辺回路領域2とのコンタクトホールの形成および導電部材の充填によってコンタクトプラグを形成する順序は、どちらが先であってもよい。

10

#### 【0078】

以上の工程によって、図2(a)、(b)に示す構造が得られる。その後、配線パターン、カラーフィルタ、マイクロレンズなどを形成し、撮像装置1000が完成する。また、周辺トランジスタが絶縁膜220で覆われた状態で、画素トランジスタおよび周辺トランジスタへの水素供給を促進させるための水素アニール処理を追加してもよい。水素アニール処理とは、水素雰囲気中にて基板100を加熱することによって、基板100の表面を水素終端することを意味する。水素アニール処理は、導電部材311、312、313、314の形成の後、さらに配線パターンを形成してから行ってもよい。

20

#### 【0079】

以上、本発明に係る第1実施形態を示したが、本発明はこれらの第1実施形態に限定されないことはいうまでもなく、本発明の要旨を逸脱しない範囲で、上述した第1実施形態は適宜変更、組み合わせが可能である。例えば、上述の第1実施形態では、半導体装置のうち撮像装置を例に挙げて本発明を説明した。しかし、本発明は、絶縁ゲート型電界効果トランジスタを備える半導体装置であれば、撮像装置に限らず、演算装置や記憶装置、制御装置、信号処理装置、検知装置、表示装置などに適用することができる。

#### 【0080】

以下、上述の第1実施形態に係る撮像装置の応用例として、撮像装置1000が組み込まれた機器について例示的に説明する。機器の概念には、撮影を主目的とする、カメラのような電子機器のみならず、撮影機能を補助的に備える機器、例えば、パソコンコンピュータ、携帯端末などの電子機器や、自動車、船舶、航空機などの輸送機器も含まれる。本発明に係る実施形態の撮像装置1000を輸送機器に用いることによって、日光などの強い光に対して特性の変化を低減できる。よって、輸送機器の設計や製造、販売を行うに当たって、本発明の実施形態に係る撮像装置の搭載を採用することは、輸送機器の価値を高める上で有効である。撮像装置1000が組み込まれた機器は、上記の第1実施形態として例示された本発明に係る撮像装置1000と、撮像装置1000から出力される信号に基づく情報を処理する処理部とを含む。該処理部は、画像データであるデジタルデータを処理するプロセッサを含みうる。該プロセッサは、撮像装置1000の焦点検出機能を有する画素からの信号に基づいてデフォーカス量を計算し、これに基づいて撮像レンズの焦点調節を制御するための処理を行いうる。上記画像データを生成するA/D変換器は、基板100が備えることができる他、A/D変換器を備える基板を基板100に積層し、この積層体を撮像装置1000としてもよいし、A/D変換器を撮像装置1000とは別に設けることもできる。撮像装置1000が組み込まれた機器において、撮像装置1000から得られたデータを、機器が備える表示装置に表示したり、機器が備える記憶装置に記憶したりすることができる。また、撮像装置1000が組み込まれた機器において、撮像装置1000から得られたデータに基づいて、機器が備えるモーター等の機械装置を駆動することができる。

30

#### 【0081】

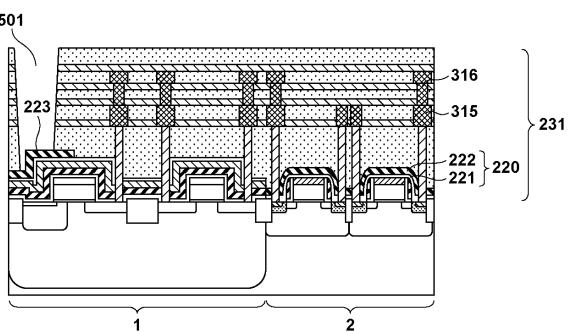

次に、図8を参照して、本発明の第2実施形態の製造方法について説明する。第2実施形

40

50

態は、光電変換部 1 1 に入射する光を増やすために導波路を有する点で第 1 実施形態と相違し、他の点では第 1 実施形態と共通している。第 2 実施形態では、窒化シリコン層 2 2 2 を光電変換部 1 1 上に残し、窒化シリコン層 2 2 3 を導波路の形成のためのエッチングストップ膜として用いる。

#### 【 0 0 8 2 】

絶縁膜 2 2 0 の形成後、絶縁膜 2 2 0 の画素領域 1 の一部と周辺回路領域 2 に位置する部分を覆うように、フォトレジストなどを用いてマスクパターンを形成する。次いで、マスクパターンの開口部を介して、窒化シリコン層 2 1 2 の画素領域 1 に配された部分をエッチングし除去する。画素領域 1 のうち少なくとも光電変換部 1 1 の上に配される窒化シリコン層 2 2 3 が形成される。

10

#### 【 0 0 8 3 】

次いで、複数の層間絶縁膜 2 3 1 と、コントラクトプラグと、第 1 配線層 3 1 5 と、ビアプラグを含む第 2 配線層 3 1 6 とが形成される。複数の層間絶縁膜 2 3 1 は、例えば、酸化シリコン層と窒化シリコン層とを交互に積層して構成される。複数の層間絶縁膜 2 3 1 は、導波路のクラッドとして利用されうる。第 1 配線層 3 1 5 および第 2 配線層 3 1 6 は、例えば、銅を主成分とする材料によってダマシン法によって形成されうるが、例えば、アルミニウムなどの他の材料によって形成されてもよい。

#### 【 0 0 8 4 】

次いで、複数の層間絶縁膜 2 3 1 に開口 5 0 1 が形成される。開口 5 0 1 は、例えば、複数の層間絶縁膜 2 3 1 の上に、光電変換部 1 1 に対応した領域に開口を有するマスクパターンを形成し、それをマスクとして複数の層間絶縁膜 2 3 1 をエッチングすることによって形成される。このエッチングは、例えば異方性エッチングである。具体的には、窒化シリコン層 2 2 3 が露出するまで、プラズマエッチング処理が複数の層間絶縁膜 2 3 1 に対して行われる。窒化シリコン層 2 2 3 は、エッチング時における光電変換部 1 1 へのプラズマダメージを低減するための膜であり、また、エッティングストップ膜としても機能する。

20

#### 【 0 0 8 5 】

次いで、開口 5 0 1 に、クラッドとなる複数の層間絶縁膜 2 3 1 よりも屈折率の高い透明材料を充填し、これにより、光電変換部 1 1 に光を導くための導波路のコアとなる部分を形成する。ここでは、複数の層間絶縁膜 2 3 1 を構成する主な材料である酸化シリコンよりも屈折率の高い窒化シリコンを開口 5 0 1 に形成するが、酸化シリコンでもよい。具体的には、高密度プラズマ C V D 法 ( High Density Plasma - C V D 法 ) によって窒化シリコンを全面に堆積し、これにより開口 5 0 1 に窒化シリコンを充填する。開口 5 0 1 の以外の部分に形成された窒化シリコンは、例えば化学機械研磨 ( Chemical Mechanical Polishing ) あるいはプラズマエッチングによって除去されうる。その後、配線パターン、カラーフィルタ、マイクロレンズなどを形成し、撮像装置が完成する。

30

#### 【 符号の説明 】

#### 【 0 0 8 6 】

1 : 画素領域、 1 1 : 光電変換部、 1 0 0 : 基板、 2 1 2 : 窒化シリコン層、 1 0 0 0 : 撮像装置

40

50

## 【図面】

## 【図 1】

## 【図 2】

10

20

## 【図 3】

## 【図 4】

30

40

50

【図5】

【図6】

【図7】

【図8】

10

20

30

40

50

---

フロントページの続き

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 大谷 章

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 田邊 顕人

(56)参考文献 特開2013-084693(JP,A)

特開2011-151126(JP,A)

特開2015-126114(JP,A)

特開平07-221004(JP,A)

特開平06-349695(JP,A)

特開2016-225432(JP,A)

特開2014-187084(JP,A)

特開2016-015407(JP,A)

特開2008-244490(JP,A)

特開2012-114223(JP,A)

特開平11-330443(JP,A)

特開2015-109343(JP,A)

特開2004-327998(JP,A)

国際公開第2014/041742(WO,A1)

特開2017-107951(JP,A)

特開平08-078719(JP,A)

特開昭57-201089(JP,A)

特開2017-174924(JP,A)

特開昭61-159576(JP,A)

特開2006-054373(JP,A)

米国特許出願公開第2016/0349108(US,A1)

特開昭61-023326(JP,A)

特表2013-524549(JP,A)

特開2011-119711(JP,A)

特表2011-507224(JP,A)

特開平06-005894(JP,A)

特開2018-041836(JP,A)

特開2017-183668(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H01L 27/146

H01L 31/02