**Erfolgspatent für die Schweiz und Liechtenstein**

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

**⑫ PATENTSCHRIFT A5**

②1 Gesuchsnummer: 4975/81

③ Inhaber:

Licentia Patent-Verwaltungs-GmbH, Frankfurt

a.M. (DE)

②2 Anmeldungsdatum: 31.07.1981

③0 Priorität(en): 01.08.1980 DE 3029173

②2 Erfinder:

Albrecht, Werner, Markt Bibart (DE)

Fischer, Klaus, Nürnberg (DE)

Grün, Gerhard, Nürnberg (DE)

②4 Patent erteilt: 15.10.1985

④5 Patentschrift veröffentlicht: 15.10.1985

⑦4 Vertreter:

Kirker & Cie SA, Genève

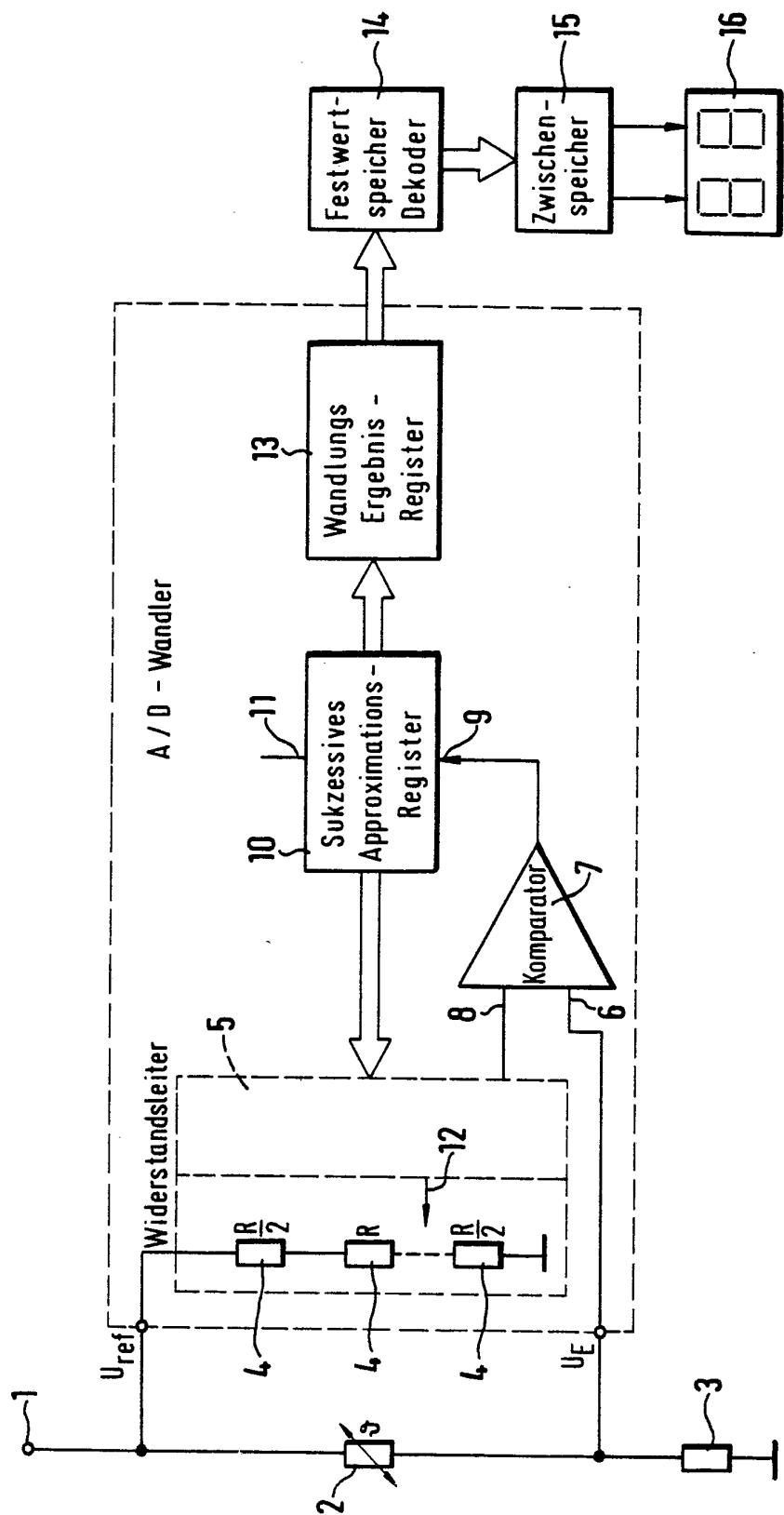

⑤4 Anordnung zur Umwandlung des Widerstandswertes eines veränderbaren Widerstandes in ein digitales Signal.

⑤7 Zur referenzspannungslosen Umwandlung eines veränderbaren Widerstandswertes in ein digitales Signal ist ein temperaturabhängiger Widerstand (2) mit einem Festwiderstand (3) in Serie geschaltet. Parallel zu dieser Serienschaltung liegt eine Widerstandsleiter (4) die mit Hilfe eines sukzessiven Approximationsregister (11) abgefragt wird. Bei Wertegleichheit wird über einen Komparator (7) der Approximationsvorgang abgebrochen und das Ergebnis einem Wandlungsergebnisregister (13) zugeführt. Das dabei gebildete digitale Wort wird als Adresse einem Festwertspeicherdekoder (14) zugeführt, wobei unter jeder Adresse ein digitales Wort gespeichert ist, welches einem zur Eingangsgröße proportionalen Wert beinhaltet. Dieser Wert wird einerseits einer Anzeigeeinrichtung (16) und andererseits als Außentemperaturwert einem Computer zugeführt, der zusammen mit anderen Steuersignalen die Aufladung von Wärmespeichergeräten steuert.

## PATENTANSPRÜCHE

1. Anordnung zur Umwandlung des Widerstandswertes eines veränderbaren Widerstandes in ein digitales Signal, wobei ein Festwertwiderstand in Serie mit dem veränderbaren Widerstand an eine Spannungsquelle angeschlossen ist und der Verbindungspunkt der beiden Widerstände mit einem Eingang einer Schaltrichtung verbunden ist, die ein vom Widerstandswert des veränderbaren Widerstandes abhängiges Steuersignal an eine digitale Schaltanordnung abgibt, insbesondere zur digitalen Eingabe eines der Aussentemperatur entsprechenden Widerstandswertes in einen Computer zur Steuerung der Aufladung von Wärmespeichergeräten, dadurch gekennzeichnet, dass parallel zur Serienschaltung aus dem veränderbaren Widerstand (2) und dem Festwertwiderstand (3) eine aus einer Mehrzahl von in Reihe geschalteten Teilerwiderständen (4) bestehende Widerstandsleiter an die Spannungsquelle angeschlossen ist, dass der Verbindungspunkt des veränderbaren Widerstand (2) und des Festwertwiderstandes (3) an einen Eingang (6) eines Komparators (7) gelegt ist, dessen zweiter Eingang (8) mittels eines sukzessiven Approximationsregisters (10) aufeinanderfolgend an Abgriffe zwischen den Teilerwiderständen (4) angelegt ist und dass der Ausgang des Komparators (7) an den Steuereingang (9) des Approximationsregisters (10) angeschlossen ist, dessen Ausgangssignal einem Wandlungsergebnisregister (13) zugeführt ist.

2. Anordnung nach Anspruch 1, dadurch gekennzeichnet, dass das Ausgangssignal des Wandlungsregisters (13) an einen Adresseneingang eines Festwertspeicherdecoders (14) angeschaltet ist.

3. Anordnung nach Anspruch 2, dadurch gekennzeichnet, dass das Ausgangssignal des Festwertspeicherdecoders (14) über einen Zwischenspeicher (15) auf eine Anzeigevorrichtung (16) geführt ist.

4. Anordnung nach Anspruch 2 oder 3, dadurch gekennzeichnet, dass das Ausgangssignal des Festwertspeicherdecoders (14) einer Recheneinheit in einem Computer zugeführt ist.

---

Die Erfindung betrifft eine Anordnung gemäss dem Oberbegriff des ersten Anspruchs.

Bei einer bekannten Anordnung dieser Art (DE-OS 28 33 583) ist ein temperaturabhängiger Messwiderstand und ein Festwiderstand an eine Spannungsquelle angeschlossen. Vom Verbindungspunkt dieser beiden Widerstände führt eine Leitung zu einem ersten Eingang eines gegengekoppelten Verstärkers, der über einen zweiten, von einem Computer gesteuerten Eingang abschaltbar ist. Das Ausgangssignal dieses Verstärkers wird einem Integrator zugeführt und dessen Ausgangssignal in einem Komparator mit einem festen Schwellensignal verglichen. Überschreitet das Ausgangssignal des Integrators das Schwellensignal, dann wird über einen dem Komparator nachgeschalteten Inverter ein Startsignal an den Computer abgegeben, der ab diesem Zeitpunkt nach einer vorgegebenen Zeitspanne auf den zweiten Eingang des ersten Verstärkers ein denselben abschaltendes Signal abgibt. Bis zu diesem Abschaltzeitpunkt wird das am temperaturabhängigen Messwiderstand anstehende Spannungssignal aufsummiert, danach erfolgt ein Abbau des Integrationssignals, bis die Schaltschwelle überschritten wird. Die Abbauzeit des aufintegrierten Signals wird dabei digitalisiert und als Mass für den Widerstandswert in einem Zählregister zur Weiterverarbeitung im Computer festgehalten. Hierbei ist somit das Zählergebnis abhängig von der Zeit, die für den Abbau des in analoger Weise auf eine bestimmte Höhe angestiegenen

Signals erforderlich ist. Die Höhe dieses Signals ist jedoch abhängig von der Grösse der Versorgungsspannung für den Verstärker und den Integrator sowie auch für den den temperaturabhängigen Messwiderstand enthaltenden Spannungsteiler, so dass auch das Zählergebnis mit der Versorgungsspannung schwankt.

Der Erfundung liegt die Aufgabe zugrunde, eine Anordnung gemäss dem Oberbegriff des ersten Anspruchs zu schaffen, mit der eine referenzspannungslose Analog-Digital-Wandlung des Widerstandswertes eines Messwiderstandes erzielbar ist.

Die Lösung dieser Aufgabe erfolgt gemäss der Erfindung durch die kennzeichnenden Merkmale des ersten Anspruchs.

Bei der erfindungsgemässen Ausgestaltung steht in einer Brückenschaltung dem veränderbaren Widerstand die Widerstandsleiter gegenüber, wobei die Widerstandsleiter in mehreren Schritten abgetastet wird. Bei gleichen Widerstandsverhältnissen in den beiden Brückenzweigen beendet ein Steuersignal eines Komparators das weitere Abfragen der Widerstandsleiter. Das digitale Ergebnis der einzelnen Abfragevorgänge stellt dann unmittelbar ein für die weitere Verarbeitung geeignetes digitales Wort dar. Da somit der Widerstandswert des veränderbaren Widerstandes als Verhältniswert ermittelt und die Grösse ohne analoges Zwischensignal sofort als digitales Signal zur Verfügung steht, geht weder die Versorgungsspannung des veränderbaren Widerstandes noch der Vergleichs- oder Zählregister in das Endergebnis der Umwandlung ein. Eine präzise Stabilisierung der Versorgungsspannungen und der damit verbundene technische Aufwand ist somit nicht erforderlich.

Die Erfindung ist nachfolgend anhand eines Schaltbeispiels näher erläutert.

An einen Anschluss 1 einer Spannungsquelle ist die Serienschaltung aus einem temperaturabhängigen Messwiderstand 2 und einem Festwertwiderstand 3 gegen Massepotential angeschaltet. Parallel zu der Serienschaltung aus den Widerständen 2 und 3 liegt eine Widerstandsleiter aus beispielsweise 256 in Serie geschalteten Teilerwiderständen, deren einzelnen Verbindungspunkte nacheinander mittels einer elektronischen Abgriffssteuerung 5 abfragbar sind. Der Verbindungspunkt des Messwiderstandes 2 und des Festwertwiderstandes 3 ist mit einem Eingang eines Komparators 7 verbunden, dessen zweiter Eingang 8 an die Abgriffssteuerung 5 angeschlossen ist. Das am Ausgang des Komparators 7 anstehende Ausgangssignal wird einem Steuereingang 9 eines sukzessiven Approximationsregisters 10 zugeführt. Das Approximationsregister 10 ist über einen Starteingang 11 in Gang zu setzen und gibt dann Steuersignale auf die Abgriffssteuerung 5 ab. Um dabei einen Brückenabgleich mit einer geringstmöglichen Anzahl von Abfragevorgängen ausführen zu können, wird im ersten Abfragevorgang ein schematisch mit 12 angedeuteter Abgriff durch die Abgriffssteuerung an den Verbindungspunkt der mittleren Teilerwiderstände 4 der Widerstandsleiter, also des 128ten und 129ten Widerstandes 4 angelegt. Die dabei abgegriffene Spannung wird im Komparator 7 mit der am Eingang 6 anliegenden Spannung des dem Messwiderstand 2 enthaltenden Brückenzweiges verglichen. Ist dabei die am Abgriff 12 erfasste und am Eingang 8 anstehende Spannung grösser als die am Eingang 6, dann wird je nach Polarität der Spannungsdifferenz eine logische Null oder eine logische Eins vom Approximationsregister in ein Wandlungs-Ergebnisregister 13 eingespeichert. In einem zweiten nachfolgenden Abfrageschritt wird der Abgriff 12 so um 64 Abgriffe verstellt, dass der im ersten Abfrageschritt festgestellten Polaritätsabweichung entgegengewirkt wird. Die sich danach ergebene Polarität der Differenzspannung aus den Eingangssignalen wird wiederum als logisches Signal im Wandlungs-Ergebnisregister festgehalten. In den weiteren

Abfrageschritten, in welchen der Abgriff 12 um jeweils die Hälfte der vorher abgegriffenen Anzahl von Teilerwiderständen 4 weitergeschaltet wird, erfolgt eine schrittweise Annäherung der Eingangssignale 6 und 8. Bei den für das Ausführungsbeispiel angenommenen 256 Teilerwiderständen 4 sind dabei lediglich 8 Abfragevorgänge erforderlich, um zum Brückenabgleich zu gelangen. Sobald der Brückenabgleich erreicht ist, spätestens also nach 8 Schritten, werden weitere Abfragevorgänge unterbunden und das so erzielte digitale Ergebnis im Wandlungsergebnis Register 13 für weitere Steuervorgänge gespeichert. Dieses digitale Signal kann dann als Adresse auf einen Festwertspeicherdecoder 14 geschaltet werden, in dem unter jeder Adresse ein Wert abgelegt werden kann, der linear mit der den Messwiderstand 2 beeinflussenden Temperatur zusammenhängt. Hierdurch kann trotz nicht

linearer Kennlinie des Messwiderstandes 2 ein exakt lineares Verhältnis zwischen der Eingangsgröße und dem Ausgabewert des Festwertspeicherdecoders 14 erreicht werden. Das im Festwertspeicher niedergelegte und durch die jeweilige Adresse auswählbare Datenwort kann anschliessend über einen Zwischenspeicher auf eine numerische Anzeigeeinrichtung 16 gegeben und dort sichtbar gemacht werden.

Daneben können jedoch die im Festwertspeicherdecoder 14 niedergelegten und durch die Adressen ansteuerbaren digitalen Werte bei einer Steuerung für die Aufladung von Wärmespeicheröfen in einen Computer eingegeben und dort mit anderen digitalisierten Einflussgrößen, wie beispielsweise den Aufladezeiträumen oder Sperrzeiten oder Temperaturabsenkungssignalen zu einem die Ein- und Ausschaltung eines Wärmespeichers steuernden Signal verarbeitet werden.