(19) 日本国特許庁(JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-173291

(P2015-173291A)

(43) 公開日 平成27年10月1日(2015.10.1)

| (51) Int.Cl.  |               | F 1              |        | テーマコード (参考)             |

|---------------|---------------|------------------|--------|-------------------------|

| <b>HO 1 L</b> | <b>29/78</b>  | <b>(2006.01)</b> | HO 1 L | 29/78 6 5 2 K 4 M 1 O 4 |

| <b>HO 1 L</b> | <b>29/739</b> | <b>(2006.01)</b> | HO 1 L | 29/78 6 5 3 C 5 F 1 4 O |

| <b>HO 1 L</b> | <b>21/336</b> | <b>(2006.01)</b> | HO 1 L | 29/78 6 5 5 E           |

| <b>HO 1 L</b> | <b>21/28</b>  | <b>(2006.01)</b> | HO 1 L | 29/78 6 5 2 H           |

|               |               |                  | HO 1 L | 29/78 6 5 2 M           |

審査請求 有 請求項の数 7 O.L. (全 19 頁) 最終頁に続く

|            |                                   |            |                                                                                                                                       |

|------------|-----------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号  | 特願2015-112383 (P2015-112383)      | (71) 出願人   | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号                                                                                                 |

| (22) 出願日   | 平成27年6月2日 (2015.6.2)              | (74) 代理人   | 100108062<br>弁理士 日向寺 雅彦                                                                                                               |

| (62) 分割の表示 | 特願2010-42235 (P2010-42235)<br>の分割 | (72) 発明者   | 北川 光彦<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内                                                                                                   |

| 原出願日       | 平成22年2月26日 (2010.2.26)            | F ターム (参考) | 4M104 BB01 CC05 EE03 EE09 FF02<br>FF27 GG06 GG09 HH14<br>5F140 AC22 BA01 BB05 BB06 BF04<br>BF43 BF53 BH03 BH13 BH30<br>BH47 BJ25 CE07 |

(54) 【発明の名称】 半導体装置

(57) 【要約】

【課題】ゲート構造を微細化してON抵抗を低減しても、アバランシェ耐量を高く維持できる半導体装置を提供する。

【解決手段】半導体装置は、第1電極と、前記第1電極上に設けられた第1導電型の第1半導体領域と、前記第1半導体領域上に設けられた第2導電型の第2半導体領域と、前記第1半導体領域上に位置し、前記第1電極から前記第1半導体領域に向かう第1方向に直交する第2方向において複数設けられた第2電極と、前記第1半導体領域上に位置し、前記第2方向において前記第2電極間に設けられた第3電極と、を有し、前記第1方向における前記第2電極の上面から前記第1電極までの長さが、前記第1方向における前記第3電極の上面から前記第1電極までの長さよりも大きい。

### 【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

第1電極と、

前記第1電極上に設けられた第1導電型の第1半導体領域と、

前記第1半導体領域上に設けられた第2導電型の第2半導体領域と、

前記第1半導体領域上に位置し、前記第1電極から前記第1半導体領域に向かう第1方向に直交する第2方向において複数設けられた第2電極と、

前記第1半導体領域上に位置し、前記第2方向において前記第2電極間に設けられた第3電極と、

を有し、前記第1方向における前記第2電極の上面から前記第1電極までの長さが、前記第1方向における前記第3電極の上面から前記第1電極までの長さよりも大きい半導体装置。 10

**【請求項 2】**

前記第1方向と前記第2方向に直行する第3方向において複数設けられ、前記第2半導体領域上に設けられた第1導電型の第4半導体領域をさらに有する請求項1に記載の半導体装置。 20

**【請求項 3】**

前記第2電極、前記第3電極、及び前記第2半導体領域上に設けられ、且つ前記第2方向における前記第2電極間で前記第2半導体領域と接する部分を有する第4電極をさらに有する請求項1または2に記載の半導体装置。 20

**【請求項 4】**

前記第1方向における前記第2半導体領域と前記第4電極との接触幅は、0.05μm以上である請求項3に記載の半導体装置。

**【請求項 5】**

前記第2方向において、前記第3電極の直上に位置する前記第4電極と前記第2電極との距離が0.05μm以上である請求項3または4に記載の半導体装置。 30

**【請求項 6】**

前記第2半導体領域と前記第3電極との間に位置し、前記第2半導体領域よりも大きい第2導電型のキャリア濃度を有する第3半導体領域をさらに有する請求項1乃至5に記載の半導体装置。

**【請求項 7】**

前記第2半導体領域上に設けられ、前記第3方向において複数設けられた第2導電型の第5半導体領域をさらに有する請求項1に記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置に関し、例えば、IGBT (Insulated Gate Bipolar Transistor)、IEGT (Injection Enhanced Gate Transistor)、MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor)、スーパージャンクション型MOSFET、サイリスタ、GTO (Gate Turn Off) サイリスタなど電力制御用の半導体装置に関する。 40

**【背景技術】****【0002】**

電力制御用の半導体装置には、電力損失を少なくするためにスイッチング動作時のON抵抗が小さいことが求められる。このため、MOSFETやIGBTなどのパワーデバイスでは、ゲート電極をトレンチに埋め込んだトレンチゲート構造が採用されている。

**【0003】**

トレンチゲート構造では、基板に垂直な縦方向に電流チャネルが形成されるため、横方向のゲート間隔を狭くすることができる。これにより、デバイス構造を微細化して実質的なチャネル幅を広くすることが可能となり、横方向にチャネルが形成されるゲート構造よりもON抵抗を小さくすることができる。また、デバイスサイズを小さくできることから

10

20

30

40

50

、スイッチング速度を上げて高性能化する点でも有利である。

**【0004】**

一方、ゲート間隔を狭めてデバイス構造の微細化を進めると、アバランシェ耐量が低下し、また短絡電流が増加する問題がある。これに対し、例えば、特許文献1に開示された技術では、ゲート電極間にベース層へのトレニチコンタクトを形成することにより、ドレンイン・ソース間耐圧を維持したままON抵抗を低減することができる。しかしながら、トレニチコンタクトを形成するスペースを要するため、微細化が制限されるという課題も含んでいる。

**【先行技術文献】**

**【特許文献】**

**【0005】**

**【特許文献1】特開2009-135360号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

ゲート構造を微細化してON抵抗を低減しても、アバランシェ耐量を高く維持できる半導体装置を提供する。

**【課題を解決するための手段】**

**【0007】**

半導体装置は、第1電極と、前記第1電極上に設けられた第1導電型の第1半導体領域と、前記第1半導体領域上に設けられた第2導電型の第2半導体領域と、前記第1半導体領域上に位置し、前記第1電極から前記第1半導体領域に向かう第1方向に直交する第2方向において複数設けられた第2電極と、前記第1半導体領域上に位置し、前記第2方向において前記第2電極間に設けられた第3電極と、を有し、前記第1方向における前記第2電極の上面から前記第1電極までの長さが、前記第1方向における前記第3電極の上面から前記第1電極までの長さよりも大きい。

**【発明の効果】**

**【0008】**

ゲート構造を微細化してON抵抗を低減しても、アバランシェ耐量を高く維持できる半導体装置を実現することができる。

**【図面の簡単な説明】**

**【0009】**

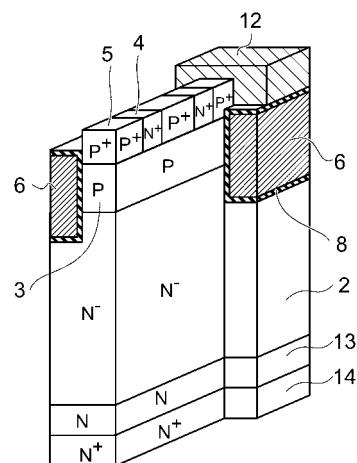

**【図1】第1実施形態に係る半導体装置の構造を模式的に示す部分断面図である。**

**【図2】第1実施形態に係る半導体装置の動作を説明する模式図である。**

**【図3】第1実施形態に係る半導体装置の特性を示すグラフである。**

**【図4】第1実施形態の変形例に係る半導体装置の構造を模式的に示す部分断面図である。**

。

**【図5】第1実施形態に係る半導体装置の特性を示すグラフである。**

**【図6】第1実施形態に係る半導体装置の特性を示すグラフである。**

**【図7】第1実施形態の変形例に係る半導体装置の構造を模式的に示す部分断面図である。**

。

**【図8】第1実施形態の変形例に係る半導体装置の構造を模式的に示す部分断面図である。**

。

**【図9】第2実施形態に係る半導体装置の構造を模式的に示す部分断面図である。**

**【図10】第2実施形態の変形例に係る半導体装置の構造を模式的に示す部分断面図である。**

**【図11】第2実施形態の変形例に係る半導体装置の構造を模式的に示す部分断面図である。**

**【図12】第2実施形態の変形例に係る半導体装置の構造を模式的に示す部分断面図である。**

10

20

30

40

50

【図13】第3実施形態の変形例に係る半導体装置の構造を模式的に示す部分断面図である。

【図14】第3実施形態の変形例に係る半導体装置の構造を模式的に示す部分断面図である。

【図15】第4実施形態に係る半導体装置の構造を模式的に示す部分断面図である。

【図16】従来のMOSFETの例を示す模式図である。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態について図面を参照しながら説明する。なお、以下の実施形態では、図面中の同一部分には同一番号を付してその詳しい説明は適宜省略し、異なる部分について適宜説明する。また、以下の説明において、第1導電型はP型、第2導電型はN型をそれぞれ意味する。

【0011】

[第1実施形態]

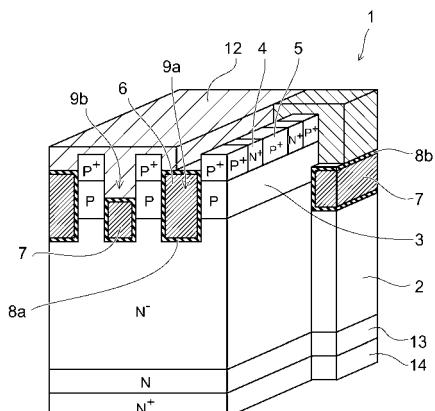

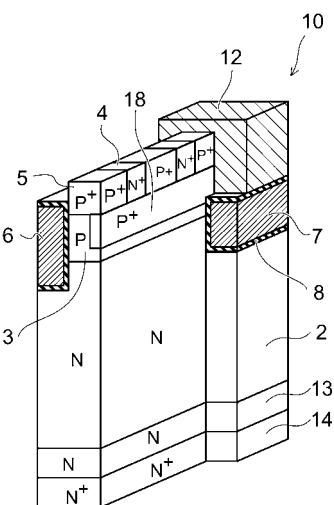

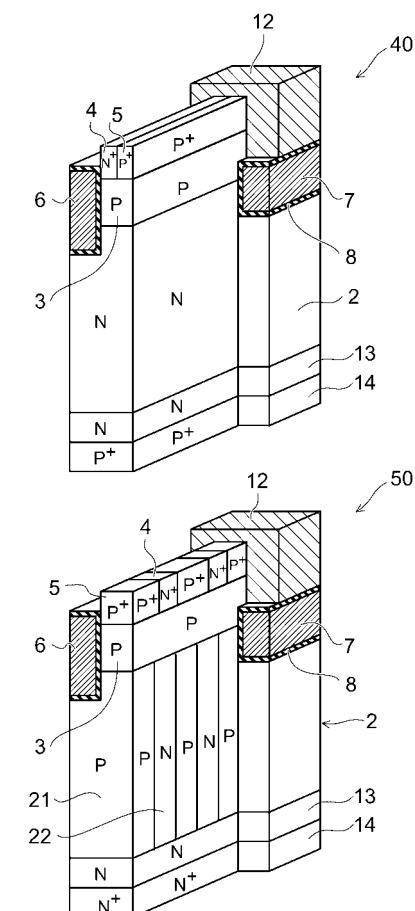

図1は、第1実施形態に係る半導体装置の構造を模式的に示す部分断面図である。ここでは、半導体装置の例としてMOSFET1を取り上げて説明するが、IGBTおよびIGT等、他の半導体装置にも適用可能である。

【0012】

図1に示すように、本実施形態に係る半導体装置は、N型のドリフト領域2と、ドリフト領域2に接して設けられたP型の第1半導体領域であるベース領域3と、を備えている。また、ベース領域3を挟んでドリフト領域2に対向する主電極であるソース電極12が設けられ、ベース領域3に電気的に接続される。一方、ドリフト領域2とベース領域3との境界には、トレンチ構造の複数の第1ゲート電極であるゲート電極6が境界に沿って設けられる。第1ゲート電極は、ドリフト領域2とベース領域3とに第1のゲート絶縁膜であるゲート絶縁膜8aを介して接している。

【0013】

さらに、2つのゲート電極6の間において、トレンチ構造の第2ゲート電極であるゲート電極7が、ドリフト領域2とベース領域3との境界に沿って、ドリフト領域2とベース領域3とに第2のゲート絶縁膜であるゲート絶縁膜8bを介して接するように設けられている。ゲート電極7は、ドリフト領域2とベース領域3との間の境界からソース電極12に向かう方向において、ベース領域3に接する長さがゲート電極6よりも短く設けられている。

【0014】

また、ソース電極12は、2つのゲート電極6の間において、ソース電極からゲート電極7に向かう方向に設けられたトレンチ9bの中に、ゲート電極7に近接した位置まで延在している。さらに、ソース電極12は、ゲート電極6のソース電極12側の端と、ゲート電極7のソース電極12側の端と、の間ににおいて、トレンチ9bの内壁面に露出したベース領域3に接している。

【0015】

さらに、図1のソース電極12を除いた部分に示すように、本実施形態に係るMOSFET1では、ベース領域3とソース電極12との間に、N型の第2半導体領域であるソース領域4とP型のコンタクト領域5とが、選択的に設けられている。トレンチ9aの中に設けられたゲート電極6は、ゲート絶縁膜8aを介してドリフト領域2、ベース領域3およびソース領域4に接しており、ベース領域3とゲート絶縁膜8aとの界面に形成されるチャネルを制御する。一方、トレンチ9bでは、ソース電極12がゲート電極7に向かって延在し、トレンチ9bの内壁面に露出した、ソース領域4とドリフト領域2との間のベース領域3に接している。

【0016】

例えば、図16に示す従来のMOSFETでは、トレンチ内に設けられた全てのゲート電極6が、ゲート絶縁膜8を介してドレイン領域2、ベース領域3およびソース領域4に

10

20

30

40

50

接している。したがって、例えば、ドリフト領域 2 からベース領域 3 に注入される正孔は、ベース領域 3 の上に選択的に設けられたコンタクト領域 5 を介してソース電極 12 に排出される。これに対し、本実施形態に係るMOSFET 1 では、ゲート電極 7 を設けることにより、トレンチ 9b の内壁面に露出したベース領域 3 から直接ソース電極 12 へ正孔を排出できる構成となっている。

#### 【0017】

また、ドリフト領域 2 のベース領域 3 に接する面の反対側には、ドリフト領域 2 よりもN型不純物の濃度が高いN型半導体領域 13 とN型のドレイン領域 14 が設けられている。さらに、図示しないドレイン電極が、ドレイン領域 14 に電気的に接続されて設けられている。ここで、例えば、ドレイン領域 14 をP型不純物がドープされた半導体領域とすれば、図1は、IGBTまたはIGETの構造となる。

10

#### 【0018】

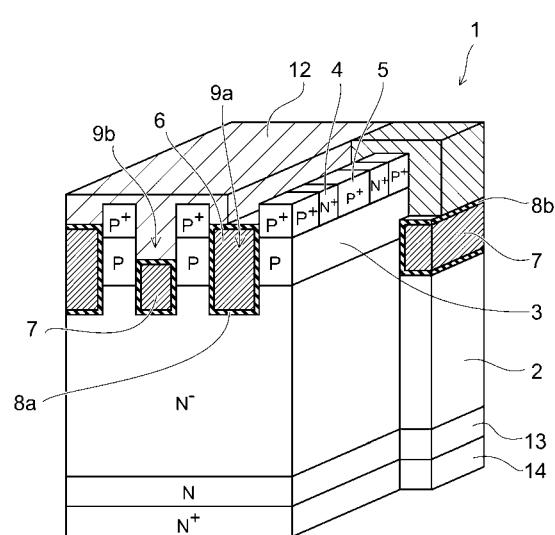

図2は、第1実施形態に係るMOSFET 1 の動作を説明する模式図である。図2(a)は、MOSFET 1 の断面構造の一部を模式的に示している。図2(b)および(c)は、MOSFET の動作を示す断面図である。

#### 【0019】

MOSFET 1 のON抵抗を小さくするためには、図2(a)に示すゲート電極 6 およびゲート電極 7 の間のベース領域 3 の幅  $W_c$  を狭くして、MOSFET 1 に含まれるゲート電極 6 の数を増やすことができる。これにより、ゲート絶縁膜 8 とベース領域 3 との界面に形成される電流チャネルの数を増やすことができ、ON抵抗を低減することが可能となる。

20

#### 【0020】

一方、ベース領域 3 の幅  $W_c$  が狭くなると、ベース領域 3 に含まれるP型不純物の量が少なくなる。例えば、200nm以下まで微細化すると、ベース領域 3 に含まれるP型不純物の量に対して、ドリフト領域 2 からベース領域 3 に注入される正孔の量が無視できなくなる。すなわち、ベース領域 3 とゲート絶縁膜 8 との界面に形成される電流チャネルが影響を受けるという問題が生じる。例えば、プラスチャージを持つ正孔が注入されると、ベース領域 3 のP型のキャリア濃度が実質的に変化し閾値電圧  $V_{TH}$  が変動する。このため、ゲート電極に印加するゲート電圧によってソース - ドレイン間に流れる電流を制御できなくなることがある。

30

#### 【0021】

したがって、ベース領域 3 の幅  $W_c$  を狭く形成する場合には、ベース領域 3 に正孔が蓄積されないように、P型のコンタクト領域 5 を介してソース電極 12 へ正孔をスムーズに排出させる必要がある。例えば、図16に示す従来のMOSFETのように、ゲート電極 6 がソース領域 4 およびコンタクト領域 5 に隣接し、ベース領域 3 を挟んでゲート電極 6 と左右対称に設けられているような構造では、ベース領域 3 に注入された正孔は、コンタクト領域 5 を介してソース電極 12 に移動する。このため、コンタクト領域 5 の幅  $W_p$  を広く設ける必要があるが、そうするとソース領域 4 の幅  $W_N$  が相対的に狭くなりON抵抗が増加してしまう。

#### 【0022】

そこで、本実施形態に係るMOSFET では、ゲート電極 7 がベース領域 3 に隣接する長さが、ゲート電極 6 がベース領域 3 に隣接する長さよりも短くなるように、ゲート電極 7 がゲート絶縁膜 8b を介してドリフト領域 2 とベース領域 3 の一部に隣接するように設ける。これにより、ソース電極 12 がゲート電極 7 とソース領域 4 との間に露出したベース領域 3 の一部に接する構造としている。

40

#### 【0023】

図2(b)に示すように、ドリフト領域 2 からベース領域 3 に注入された正孔は、ゲート電極 7 とソース領域 4 との間のベース領域 3 と、ソース電極 12 と、がコンタクトする部分からソース電極 12 へと排出される。したがって、ソース電極 12 がベース領域 3 にコンタクトする部分の、ソース領域 4 からドリフト領域 2 へ向かう方向の幅  $d_1$  を広くし

50

た方が、正孔の排出がよりスムーズになる。例えば、 $d_1 > 0.05 \mu m$ とすることができる。

#### 【0024】

これにより、正孔がベース領域3に蓄積されることなく、 $V_{TH}$ の変動を抑えることが可能となる。また、ドリフト領域2からベース領域3を介してソース電極12へ排出される正孔の排出抵抗が小さくなることから、ドリフト領域2で発生する正孔をスムーズに排出してアバランシェ耐量を向上させる効果も得られる。

#### 【0025】

一方、本実施形態に係るMOSFETでは、ゲート電極7がソース領域4から離間するため、ゲート電極7とベース領域3の間に形成されるチャネルを介してソース領域4からドリフト層2へ直接流れる電流パスが無くなるという不利な効果も生じる。しかしながら、ベース領域3の幅 $W_c$ を狭くした場合には、図2(b)中に示すように、ゲート電極7側のチャネルを介して流れる電流 $I_{N2}$ も、ゲート電極6側の電流チャネルを流れる電流 $I_{N1}$ に合流して寄与するので、チャネル抵抗が低くなりON抵抗を低減する効果が得られるようになる。

10

#### 【0026】

上記の本実施態様に係るMOSFETの効果を別の観点から見れば、次のように捉えることができる。すなわち、コンタクト領域5とベース領域3とを合わせたP型領域にソース電極12が接触する面積を比較した場合、ゲート電極6が埋め込まれたトレンチ9aよりも、ゲート電極7が埋め込まれたトレンチ9bのほうが、ソース電極12が広い面積でP型領域に接触する。したがって、ソース電極12がP型領域に接触する面積を相対的に広くすることが可能となり、ベース領域3からソース電極12へ正孔を効率良く排出することができる。

20

#### 【0027】

図2(c)は、ゲート電極7とベース領域3との間に形成されるNチャネル16を示す模式図である。ゲート電極7にプラスのゲート電圧が印加されると、ゲート絶縁膜8とベース領域3との界面に電子が引き寄せられた反転層が形成される。同図中に示すように、この反転層は、ゲート電極7のソース領域側の端部でソース電極12方向に広がって形成される。このチャネル端部16aがソース電極12につながると、ソース電極12からドリフト層2に電流パスが形成され、過剰電流が流れてしまう恐れがある。そこで、トレンチ9bの内壁面側のゲート電極7の端部とソース電極との間の間隔 $d_2$ を、ある程度広くしておくと良い。例えば、 $d_2 > 0.05 \mu m$ とすることができる。

30

#### 【0028】

例えば、ゲート電極7の端部とソース電極12との間に $d_2 > 0.05 \mu m$ となるような厚さのゲート絶縁膜8を形成することもできるし、また、ゲート電極7の端部とソース電極12との間に空隙を設けても良い。

#### 【0029】

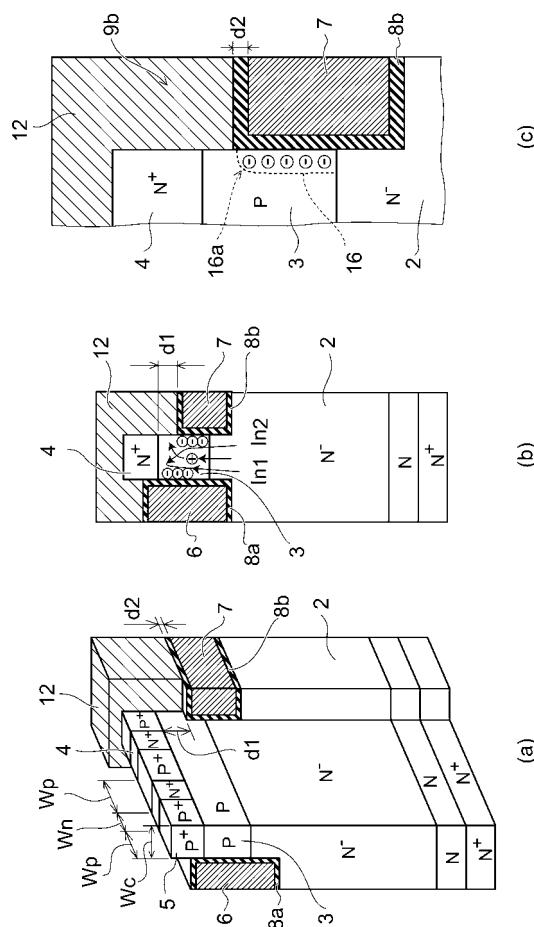

図3は、第1実施形態に係るMOSFET1の特性を示すグラフである。縦軸にソース-ドレイン間に流れるドレイン電流を示し、横軸にゲート電圧を示している。同図中に示すグラフAは、本実施形態に係るMOSFET1の特性を示している。また、グラフBは、ゲート電極7とソース領域4との間でソース電極12がベース領域3と接する部分の幅 $d_1$ が $0.05 \mu m$ よりも狭い場合のドレイン電流を示している。一方、グラフCは、図16に示す従来のMOSFETの特性を示している。

40

#### 【0030】

図3中に示すように、ソース-ドレイン間のバイアス電圧 $V_d$ を44V印加しても、ゲート電圧が0Vであれば、グラフAに示す本実施形態に係るMOSFET1ではドレイン電流は流れない。一方、グラフBおよびCに示すMOSFETではドレイン電流が流れる。すなわち、 $d_1 < 0.05 \mu m$ としたグラフBに示すMOSFET、およびグラフCに示す従来のMOSFETでは、ゲート制御が不能となる場合があることを示している。したがって、 $d_1 > 0.05 \mu m$ として、ベース領域3から直接ソース電極12へ正孔を排

50

出する構造とした、本実施形態に係るMOSFET 1の方が有利であることがわかる。

【0031】

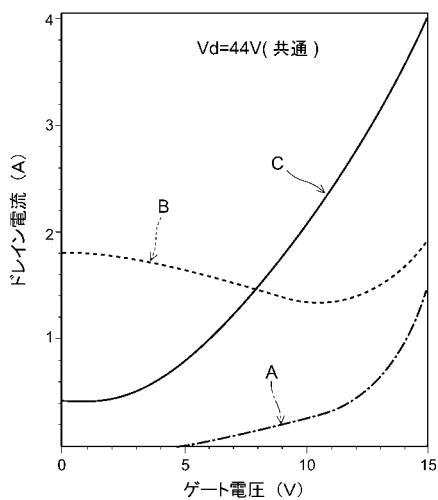

図4は、第1実施形態の変形例に係るMOSFET 10の構造を模式的に示す部分断面図である。ソース領域4とゲート電極7との間に露出したベース領域3と、ソース電極12と、が接する部分に、P型不純物濃度がベース領域3よりも高い第3の半導体領域であるP<sup>+</sup>領域18を設けている点において、図1に示すMOSFET 1と異なる。このP<sup>+</sup>領域18を設けることにより、ソース-ドレイン間に流れる過剰なドレイン電流を抑制することができる。

【0032】

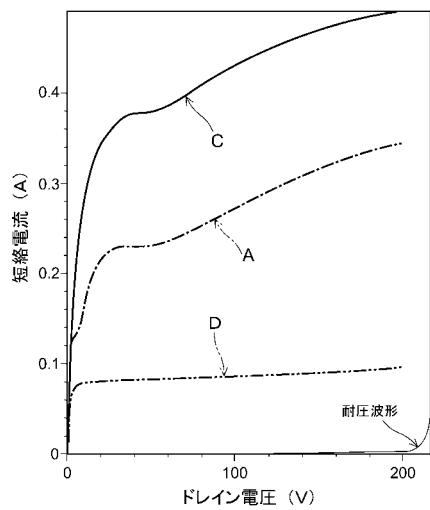

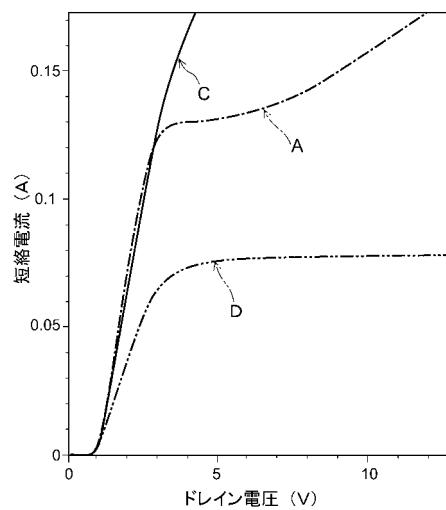

図5および図6は、第1実施形態に係るMOSFET 1およびMOSFET 10の特性を示すグラフである。縦軸にソース-ドレイン間の負荷がショートした時に流れる短絡電流を示し、横軸にドレイン電圧を示している。同図中のグラフAは、MOSFET 1の短絡電流を示し、グラフDは、MOSFET 10の短絡電流を示している。また、グラフCは、図16に示す従来のMOSFETの短絡電流を示している。

10

【0033】

グラフAに示すMOSFET 1では、ゲート電極7側に形成されるチャネル16が直接ソース領域4につながっていないため、短絡電流は、ゲート電極6側の電流チャネルに流れる電流と合流してソース領域2に集中して流れる。したがって、ゲート電極7側のチャネルにも電流が流れる従来のMOSFETに比べて、過剰に流れる短絡電流に対する抵抗が大きくなる。その結果、グラフCに示す従来のMOSFETに比べて、短絡電流が約1/2に制限される。これにより、ゲート電極6および7に印加するゲート電圧を0Vとして、短絡電流を遮断することが可能になる。

20

【0034】

一方、グラフDに示すMOSFET 10では、さらに短絡電流が減少し、従来のMOSFETに比べて約1/5、グラフAに示すMOSFET 1の約1/3になっている。これは、ベース領域3に設けられたP<sup>+</sup>領域18が、電流バスを狭めて短絡電流を制限しているためと考えられる。これにより、ソース-ドレイン間につながれた負荷が短絡したとしても、ゲート電圧によって短絡電流を制御することが容易となる。

30

【0035】

図6は、短絡電流とドレイン電圧と関係を示す図5のグラフの低電圧部を拡大して示している。同図中に示すように、短絡電流が0.12A程度までは、従来のMOSFETの特性を示すグラフCとMOSFET 1の特性を示すグラフAとは、ほぼ一致している。すなわち、0.12A程度までのドレイン電流に対しては、ゲート電極7側のチャネルをソース領域4から離間して設けたMOSFET 1でも、チャネル抵抗は高くならず低いON抵抗を維持できることを示している。

40

【0036】

一方、グラフDに示すMOSFET 10では、ベース領域3にP<sup>+</sup>領域18を設けたことにより、チャネル抵抗がやや高くなっているが、短絡電流の抑制効果が高いことがわかる。

40

【0037】

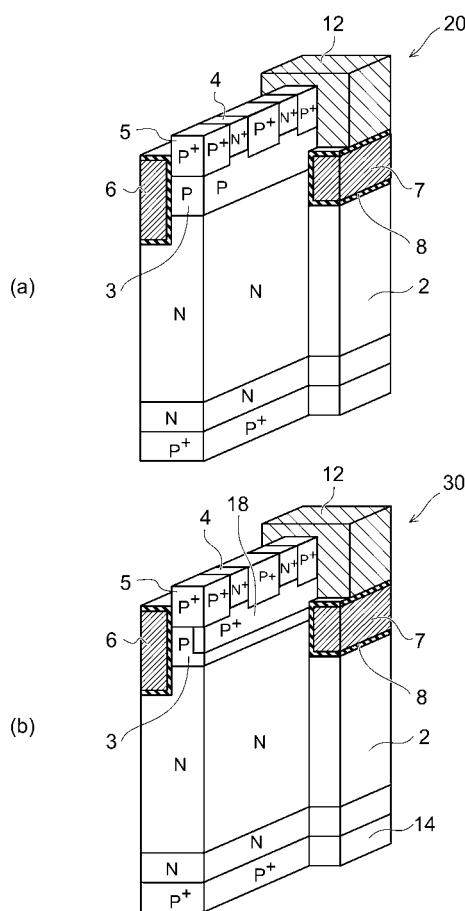

図7は、第1実施形態の変形例に係るMOSFET 20および30の構造を模式的に示す部分断面図である。

【0038】

図7(a)に示すMOSFET 20では、ベース領域3の方向にコンタクト領域5をソース領域4よりも深く形成している。これにより、ドリフト層2からベース領域3に注入された正孔をP型のコンタクト領域5を介して排出する経路の排出抵抗を下げることができる。その結果、ベース領域のP型キャリアの濃度変動を抑制して、ゲート電圧によるドレイン電流の制御性を改善することができ、また、ベース領域3とドリフト層2との間のアバランシェ耐量を向上させることもできる。

【0039】

50

図7( b )に示すMOSFET30では、図7( a )に示すMOSFET20のベース領域3に、P<sup>+</sup>領域18をさらに設けた構造となっている。これにより、短絡電流を抑制して短絡耐量を向上させることができる。

#### 【0040】

図8は、第1実施形態の変形例に係るMOSFET40および50の構造を模式的に示す部分断面図である。

#### 【0041】

図8( a )に示すMOSFET30では、ソース領域4は、ゲート電極6に沿ってベース領域3の表面に設けられている。これにより、ゲート電極6とベース領域3との間に形成される電流チャネルの全てにソース領域4を接続することができ、チャネル抵抗を下げてON抵抗を低減することができる。10

#### 【0042】

一方、コンタクト領域5は、ソース領域4と並列にゲート電極7の側に形成されている。これにより、ベース領域3から排出される正孔のバスは、ゲート電極7の側でコンタクトするソース電極のみとなるが、コンタクト面積を広くして正孔の排出抵抗を低減することができる。

#### 【0043】

図8( b )に示すMOSFET50では、ベース領域3との境界に沿って第5半導体領域であるP型ピラー21と第4半導体領域であるN型ピラー22が交互に配置されたスーパージャンクション構造のドリフト領域2が設けられている。スーパージャンクション構造を用いることにより、N型ピラー22の濃度を上げてON抵抗を低減することが可能となる。20

#### 【0044】

##### [第2実施形態]

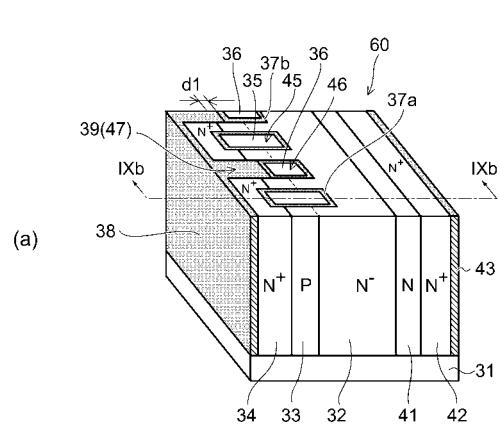

図9は、第2実施形態に係る半導体装置の構造を模式的に示す部分断面図である。本実施形態に係るMOSFET60は、絶縁層31の主面上に設けられた横型構造を有している。なお、絶縁層31は、例えば、基板上に設けられたSiO<sub>2</sub>等の絶縁膜でも良いし、半絶縁性を有する半導体層であっても良い。

#### 【0045】

図9( a )に示すように、MOSFET60は、絶縁層31(または半絶縁層)の主面上に設けられたN型の半導体を含むドリフト領域32と、主面上に平行な横方向にドリフト領域32に隣接して設けられたP型の第1半導体領域であるベース領域33と、ベース領域33の横方向に隣接して設けられたN型の第2半導体領域であるソース領域34と、を備えている。また、ソース領域34のベース領域33に接する側面の反対側の側面に接して主電極であるソース電極38が設けられている。30

#### 【0046】

また、ドリフト領域32とベース領域33とソース領域34とに跨った表面から絶縁層31方向に、ドリフト領域32とベース領域33との境界に沿って、複数のトレンチ45が形成されている。トレンチ45の中には、第1ゲート電極であるゲート電極35が設けられている。さらに、2つのゲート電極35の間には、ドリフト領域32とベース領域33の一部とに跨った表面から、ドリフト領域32とベース領域33との境界に沿って、絶縁層31の方向にトレンチ46が形成されている。トレンチ46の中には、第2ゲート電極であるゲート電極36が設けられている。したがって、ドリフト領域32とベース領域33との境界からソース電極38に向かう方向において、ゲート電極36がゲート絶縁膜37bを介してベース領域33に接する長さは、ゲート電極35がゲート絶縁膜37aを介してベース領域33に接する長さよりも短く設けられている。40

#### 【0047】

さらに、ソース電極38の一部は、2つのゲート電極35の間で、ソース電極38からゲート電極46に向かう方向に形成されたトレンチ47の中に延在して設けられている。トレンチ47は、ソース領域34とベース領域33の一部とに跨る表面から絶縁層31の50

方向に形成されている。また、ソース電極38は、トレンチ47の中に、ゲート電極35のソース電極38側の端の位置を超えてゲート電極46に近接した位置まで延在し、ゲート電極36とソース領域34との間のトレンチ47の内壁面に露出したベース領域33に電気的に接続している。

#### 【0048】

また、ドリフト領域32に隣接して、ドリフト領域32よりもN型不純物濃度の高いN型半導体領域41と、N型半導体領域41に隣接してドレイン領域42と、が設けられている。さらに、ドレイン領域42に電気的に接続するドレイン電極43が設けられている。

#### 【0049】

また、図9(b)は、図9(a)中に示すIXb-IXb断面を示す模式図である。同図中に示すように、トレンチ45は、絶縁層31に連通して設けることができる。また、トレンチ45の内面にはゲート絶縁膜37aが形成され、さらに、トレンチ45の内部は、例えば、導電性のポリシリコンからなるゲート電極35で埋められている。トレンチ46に形成されるゲート電極36も、同様に形成することができる。また、以下、図12までに示す実施形態に係るMOSFETにおいても同様である。

#### 【0050】

本実施形態に係るMOSFET60では、ソース電極38の延在部39が、ソース領域34の表面からベース領域33の表面の一部に跨る表面から絶縁層31に連通するトレンチ47の中に設けられている。これにより、ソース電極38は、ゲート電極36とソース領域34との間のトレンチ47の内面に露出したベース領域33に接触して、ドリフト領域32からベース領域33に注入される正孔を排出することができる。

10

20

#### 【0051】

また、延在部39がベース領域33に接触するコンタクト部分の幅d1を0.05μm以上として、ソース-ドレイン間に流れるドレイン電流がゲート電圧で制御不能となる不具合を防止することが可能である。

#### 【0052】

本実施形態に係るMOSFET60は、絶縁層31の上に形成されるドリフト領域32およびベース領域33、ソース領域34等の厚さが薄い場合には、例えば、絶縁層31の上に設けられた半導体層に、N型およびP型の不純物をイオン注入して形成することができる。また、各半導体領域を厚く設ける場合には、複数回のエピタキシャル成長とイオン注入を組み合わせることにより形成することができる。また、図10に説明する横型のMOSFETにおいても同様である。なお、ここで厚さとは、絶縁層31から各半導体領域の表面方向への層厚を意味するものとする。

30

#### 【0053】

また、本実施形態においても、例えば、ドレイン領域42をP型不純物がドープされたP型半導体領域とすれば、図9は、IGBTまたはIGTの構造を示している。以下、図12までに示す実施形態についても同様である。

#### 【0054】

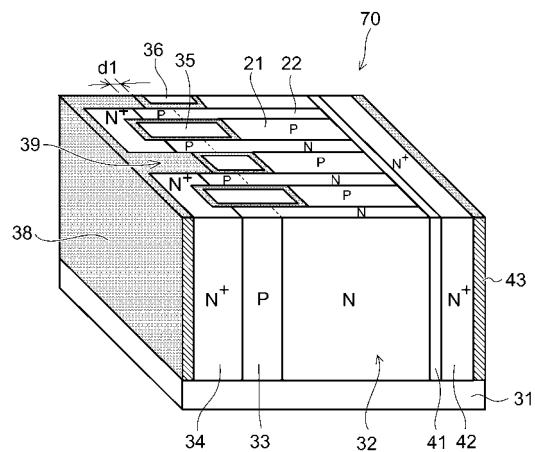

図10は、第2実施形態の変形例に係るMOSFET70の構造を模式的に示す部分断面図である。MOSFET70は、ドリフト領域32において、ドリフト領域32とベース領域33との間の境界に沿って第5の半導体領域であるP型ピラー21と第4の半導体領域であるN型ピラー22とを交互に配置したスーパージャンク構造を有している。

40

#### 【0055】

図9に示すMOSFET60と同様に、本変形例に係るMOSFET70においても、ソース電極38の延在部36がベース領域33に接触するゲート電極36とソース領域34との間のコンタクト部分からベース領域33の正孔をソース電極38に排出することができる。これにより、閾値電圧VTHを安定させることができるので、ゲート電極35とゲート電極36との間のベース領域33の幅を狭くすることが可能となる。したがって、

50

MOSFETのチャネル数を増やしてチャネル抵抗を低減することができる。さらに、スーパージャンクション構造を用いることにより、ベース領域33につながるN型ピラー22の濃度を高くしてドリフト領域の抵抗を低減することができる。これにより、MOSFET70のON抵抗を低減することが可能である。

#### 【0056】

図11は、第2実施形態の変形例に係るMOSFET80の構造を模式的に示す部分断面図である。同図中に示すように、MOSFET80のドリフト領域32は、絶縁層31から上部方向へPピラーとNピラーが交互に積層されたスーパージャンクション構造を有している。

#### 【0057】

本変形例に係るMOSFET80は、絶縁層31（または半絶縁層）の主面上に、N型の第1半導体層であるN型半導体層24と、P型の第2半導体層であるP型半導体層25と、が交互に設けられた積層体27を備え、ドリフト領域32をスーパージャンクション構造としている。また、積層体27の一方の側面には、第1の主電極であるソース電極38が電気的に接続して設けられ、他方の側面には、第2の主電極であるドレイン電極43が電気的に接続して設けられている。

#### 【0058】

さらに、積層体27は、ソース電極38とドレイン電極43との間に、積層体27の表面から絶縁層31の主面に連通して設けられたP型の第1半導体領域であるベース領域33を有している。さらに、ソース電極38とベース領域33とに挟まれたN型の第2半導体領域であるソース領域34と、ベース領域33とドレイン電極43との間にドリフト領域32と、を有している。

#### 【0059】

また、積層体27には、ソース領域34と、ベース領域33と、ドリフト領域32と、に跨った表面から、絶縁層31の主面に向かってトレンチ45が形成されている。さらに、トレンチ45の中には、第1のゲート電極であるゲート電極35が設けられている。また、ベース領域33の一部と、ドリフト領域32と、に跨った表面から、絶縁層31の主面に向かってトレンチ46が設けられ、トレンチ46の中には、第2のゲート電極であるゲート電極36が設けられている。

#### 【0060】

2つのゲート電極35の間には、ソース領域34とベース領域33の一部とに跨る表面から絶縁層31主面に向かってトレンチ47が形成されており、トレンチ47の中には、ソース電極38が延在している。延在39は、ソース領域34とゲート電極36との間のトレンチ47の内壁面に露出したベース領域33に接するように設けられている。

#### 【0061】

これにより、ドリフト領域32からベース領域33へ注入される正孔がソース電極38へ排出されるので、閾値電圧 $V_{TH}$ が安定する。また、アバランシェ耐量および短絡耐量を向上させることができる。

#### 【0062】

一方、ドリフト領域32とドレイン電極43との間には、積層体27の表面から絶縁層31に連通して、N型半導体領域41とドレイン領域42とが設けられている。ドレイン領域42は、N型不純物が高濃度にドープされたN<sup>+</sup>領域である。本変形例においても、ドレイン領域42にP型不純物をドープしてP<sup>+</sup>領域とし、IGBTまたはIGTとすることができる。

#### 【0063】

積層体27は、複数回のエピタキシャル成長により絶縁層31の上に複数の半導体層を設け、さらに、各エピタキシャル成長の間に、P型およびN型の不純物を、選択的に所定の場所にイオン注入することにより形成することができる。

#### 【0064】

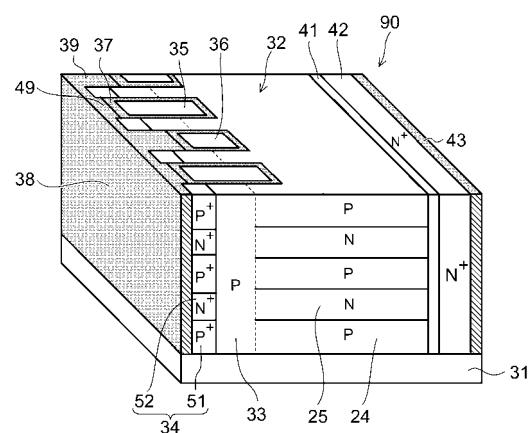

図12は、第2実施形態の変形例に係るMOSFET90の構造を模式的に示す部分断

10

20

30

40

50

面図である。MOSFET90は、図11に示すMOSFET80のソース領域34が、P<sup>+</sup>コンタクト領域51とN<sup>+</sup>ソース領域52の積層構造に置き換えられた構成となっている。これにより、ベース領域33の正孔をP<sup>+</sup>コンタクト領域51を介してソース電極38に排出することができる。P<sup>+</sup>コンタクト領域51とN<sup>+</sup>ソース領域52は、それぞれイオン注入によって形成することができる。

#### 【0065】

また、P<sup>+</sup>コンタクト領域51とN<sup>+</sup>ソース領域52の積層方向の厚さは、イオン注入する不純物のドーズ量により変えることができる。例えば、P<sup>+</sup>コンタクト領域51に注入するP型不純物のドーズ量をN<sup>+</sup>ソース領域52に注入するN型不純物のドーズ量よりも多くすると、図12中に示すように、P<sup>+</sup>コンタクト領域51をN<sup>+</sup>ソース領域52よりも厚くすることができる。これにより、ベース領域33からソース電極38への正孔の排出抵抗を小さくすることができる。また、N<sup>+</sup>ソース領域52に注入するN型不純物のドーズ量を増やせば、N<sup>+</sup>ソース領域52を厚くしてON抵抗を低減することもできる。

10

#### 【0066】

また、MOSFET90では、ゲート絶縁膜37を介してゲート電極35に隣接してソース電極38の延在部49が設けられているが、図10に示すMOSFET70のように、延在部49を設けないで、ゲート電極35とソース電極38との間にP<sup>+</sup>コンタクト領域51とN<sup>+</sup>ソース領域52を介在させても良い。

20

#### 【0067】

##### [第3実施形態]

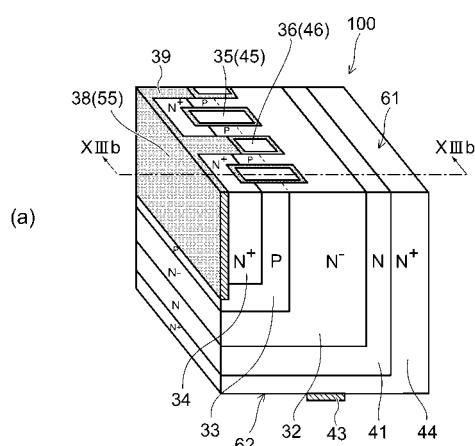

図13は、第3実施形態に係るMOSFET100の構造を模式的に示す部分断面図である。

#### 【0068】

MOSFET100は、N型不純物が高濃度にドープされた半導体層であるドレイン層44の第1の正面61に設けられたN型のドリフト領域32と、ドリフト領域32の中に設けられたP型の第1半導体領域であるベース領域33と、ベース領域33の中に設けられたN型の第2半導体領域であるソース領域34と、を備えている。

30

#### 【0069】

ここでドレイン層44として、例えば、シリコン基板上に形成されたN型半導体層を用いることもできるし、N型不純物が高濃度にドープされたシリコン基板を用いても良い。また、ドレイン層44に代えてP型半導体層を用いると、IGBTまたはIGTとすることができる。

#### 【0070】

図13に示す半導体領域の構成は、例えば、所定の凹部が設けられたドレイン層44の第1の正面61に、N型半導体領域41となる半導体層、およびドリフト領域32となる半導体層、ベース領域33となる半導体層、ソース領域34となる半導体層を順次エピタキシャル成長し、さらに、各半導体層が設けられたドレイン層44の第1の正面61をCMP(Chemical Mechanical Polish)を用いて平坦化することにより形成することができる。

40

#### 【0071】

複数のトレンチ45が、ドリフト領域32とベース領域33との境界に沿ってドレイン層44の第2の正面62に向けて形成されている。また、トレンチ45の中には、第1のゲート電極であるゲート電極35が設けられている。一方、2つのゲート電極35の間には、第トレンチ46が、ドリフト領域32とベース領域33の境界に沿ってドレイン層44の第2の正面62に向けて設けられている。さらに、トレンチ46の中には、第2のゲート電極であるゲート電極36が設けられている。

#### 【0072】

また、主電極であるソース電極38が、ソース領域34に接して設けられている。ソース電極38は、例えば、ゲート電極35の配列に沿ってソース領域34の表面からベース領域33に連通するトレンチ55の中に設けることができる。さらに、2つのゲート電極

50

35の間に、ソース領域34とベース領域33の一部とに跨る表面からソース領域34とベース領域62の境界に沿ってトレンチ55の拡張部分が設けられている。ソース電極38は、ゲート電極36に向かってトレンチ55の拡張部分に延在して設けられている。延在部39は、ソース領域34とゲート電極36との間のトレンチ55の張り出し部の内壁面に露出した、ベース領域33に接して設けられている。

#### 【0073】

図13(b)は、図13(a)中に示されたXIIIb-XIIIb断面の構造を示す模式図である。トレンチ45は、表面からドリフト領域32とベース領域33の境界に沿ってベース領域33およびソース領域34を貫通し、下方のドリフト領域32に達するように形成されている。また、トレンチ45の内面にはゲート絶縁膜37が形成され、ゲート電極35となる、例えば、導電性のポリシリコンが埋め込まれている。10

#### 【0074】

本実施形態に係るMOSFET100においても、ソース電極38の延在部39が、ゲート電極36とソース領域34との間のトレンチ55の拡張部の内面に露出したベース領域33に接触しており、ドリフト領域32からベース領域33に注入される正孔をソース電極38へ排出することができる。

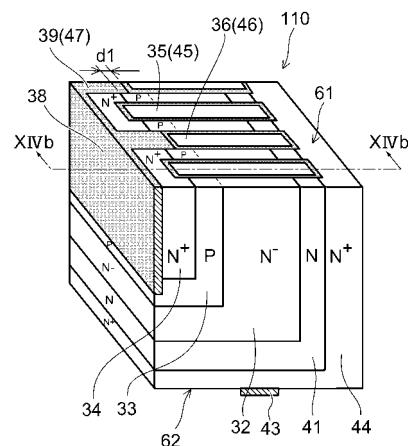

#### 【0075】

図14(a)は、第3実施形態の変形例に係るMOSFET110の構造を模式的に示す部分断面図である。また、図14(b)は、図14(a)中に示したXIVb-XIVb断面の構造を示す模式図である。20

#### 【0076】

MOSFET110は、トレンチ45およびトレンチ46がドレイン層44に達するように設けられ、ゲート電極35およびゲート電極36が埋め込まれている点で、図13に示すMOSFET100と異なる。

#### 【0077】

すなわち、図14(a)に示すように、トレンチ45は、ソース領域34およびベース領域33、ドリフト領域32、N型半導体領域41、ドレイン層44に跨ったドレイン層44の第1の主面61側の表面から、第2の主面62方向に設けられている。また、図14(b)に示すように、トレンチ45は、ソース領域34およびベース領域33、ドリフト領域32、N型半導体領域41、を貫通してドレイン層44に達するように設けられている。さらに、トレンチ45の内面には、ゲート絶縁膜37が形成され、ゲート電極35となる、例えば、導電性のポリシリコンが埋め込まれている。30

#### 【0078】

一方、ゲート電極36が設けられているトレンチ46も、ベース領域33およびドリフト領域32、N型半導体領域41、ドレイン層44に跨ったドレイン層44の第1の主面61側の表面から、第2の主面62側のドレイン層44に達するように設けられている。

#### 【0079】

MOSFET110では、ゲート電極35および36にプラスのゲート電圧が印加されると、ドリフト領域32と、ゲート絶縁膜37との界面に電子が蓄積したチャネルが形成される。これにより、ドリフト領域32の抵抗が下がり、ON抵抗を低減することができる。40

#### 【0080】

##### [第4実施形態]

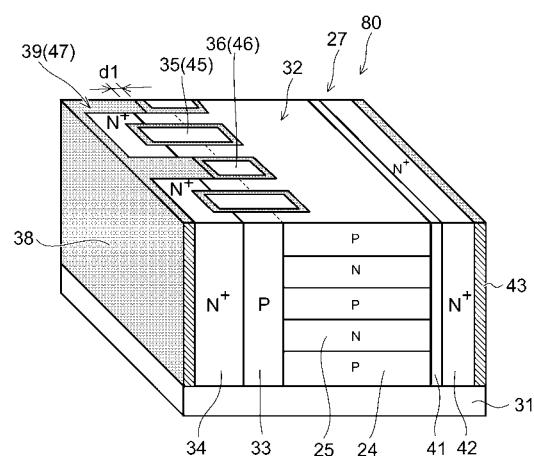

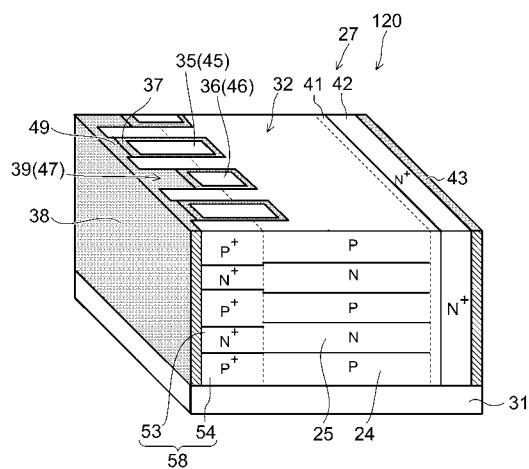

図15は、第4実施形態に係る半導体装置120の構造を模式的に示す部分断面図である。半導体装置120は、絶縁層31の主面上に交互に積層された複数のP型半導体領域24およびN型半導体領域25からなるスーパージャンクション構造を有する電力制御用半導体装置である。

#### 【0081】

半導体装置120は、絶縁層31(または半絶縁層)の主面上に、N型半導体領域25と、P型半導体領域24と、が交互に設けられた積層体27を有している。積層体27の50

一方の側面には、第1の主電極であるソース電極38が電気的に接続して設けられている。また、積層体27の他方の側面には、第2の主電極であるドレイン電極43が電気的に接続して設けられている。

#### 【0082】

さらに、ソース電極38とドレイン電極43との間に、P型半導体領域24とN型半導体領域25とが交互に積層されたスーパージャンクション構造のドリフト領域32が設けられている。ドリフト領域32とソース電極38との間には、P型の不純物がP型半導体領域24よりも高濃度にドープされた第2半導体領域であるP<sup>+</sup>領域54と、N型の不純物がN型半導体領域25よりも高濃度にドープされたN<sup>+</sup>領域53と、を積層したコンタクト領域58が設けられている。10

#### 【0083】

また、コンタクト領域58とドリフト領域32とに跨った表面から、コンタクト領域58とドリフト領域32との境界に沿って、トレンチ45が形成されている。トレンチ45の中には、第1のゲート電極であるゲート電極35が設けられている。さらに、コンタクト領域51の一部と、ドリフト領域32と、に跨った表面から、コンタクト領域58とドリフト領域32との境界に沿ってトレンチ46が形成されている。トレンチ46の中には、第2のゲート電極であるゲート電極36が設けられている。

#### 【0084】

半導体装置120のソース電極38は、コンタクト領域58のP<sup>+</sup>領域54とN<sup>+</sup>領域53に電気的に接続されている。ソース電極38の一部である延在部39は、2つのゲート電極35の間で、ソース電極38からゲート電極36の近傍に至るP<sup>+</sup>領域54の表面から、絶縁層31の正面に向かって形成されたトレンチ47の中に延在して設けられている。また、延在部39は、トレンチ47の内壁面に露出したコンタクト領域58に電気的に接続されている。また、ゲート電極35にゲート絶縁膜37を介して隣接する延在部49も設けられている。20

#### 【0085】

一方、ドリフト領域32とドレイン電極43との間には、N型半導体領域41とドレイン領域42とが、表面から絶縁層31の正面に連通して設けられている。本実施態様に係る半導体装置120では、ドレイン領域42は、N型不純物が高濃度にドープされたN<sup>+</sup>領域であるが、P型不純物をドープしてP<sup>+</sup>領域としても良い。その場合には、半導体装置120は、バイポーラ素子として動作する。30

#### 【0086】

また、積層体27は、絶縁層31の正面に複数回のエピタキシャル成長により、N型半導体領域25とP型半導体領域24とを積層することによって形成することができる。また、各半導体領域のエピタキシャル成長の間に、イオン注入を用いて選択的にP型およびN型の不純物を注入することによって、上記の積層構造とすることができます。

#### 【0087】

次に、半導体装置120の動作について説明する。半導体装置120では、コンタクト領域58において、N<sup>+</sup>領域53の積層方向の幅は、P<sup>+</sup>領域54よりも狭く設ける。さらに、P<sup>+</sup>領域54とN<sup>+</sup>領域53との間のPN接合のビルトインボテンシャルにより、N<sup>+</sup>領域53を空乏化させる。これにより、ドレイン電極43とソース電極38との間にドレイン側がプラスとなるドレイン電圧を印加しても、ゲート電極35および36にゲート電圧が印加されない状態では、ドレイン電流は流れない。40

#### 【0088】

次に、ゲート電極35および36にプラスのゲート電圧を印加すると、N<sup>+</sup>領域53とゲート絶縁膜37との間に電子が蓄積されて電流チャネルが形成される。これにより、ドレイン電極43とソース電極38との間に電流がながれON状態となる。

#### 【0089】

この際、N<sup>+</sup>領域53にドリフト領域32のN型半導体層25から正孔が注入されると、N<sup>+</sup>領域53の実効的な濃度が変化してチャネル抵抗が高くなりON抵抗が上昇してし50

まう場合がある。

【0090】

これに対し半導体装置120では、ソース電極38がトレンチ47の内壁面に露出したコンタクト領域58のN<sup>+</sup>領域53に電気的に接続されているので、N<sup>+</sup>領域53に注入された正孔をソース電極38へスマーズに排出することができる。これにより、N<sup>+</sup>領域53の実効的なキャリア濃度の変動を抑制して、半導体装置120を安定に動作させることができる。また、アバランシェ耐量を向上させることができる。

【0091】

以上、本発明に係る第1～第4の実施形態を参照して本発明を説明したが、本発明はこれらの実施形態に限定されるものではない。例えば、出願時の技術水準に基づいて、当業者がなし得る設計変更や、材料の変更等、本発明と技術的的思想を同じとする実施態様も本発明の技術的範囲に含有される。

10

【符号の説明】

【0092】

2 ドリフト領域

3、33 ベース領域

4、34、52 ソース領域

5、51、58 コンタクト領域

6、7、35、36 ゲート電極

8、8a、8b、37、37a、37b ゲート絶縁膜

20

9a、9b トレンチ

12、38 ソース電極

13 N型半導体層

14 ドレイン層

18、54 P<sup>+</sup>領域

21 P型ピラー

22 N型ピラー

24 P型半導体領域

25 N型半導体領域

30

27 積層体

31 絶縁層

32 ドリフト領域

39、49 張り出し部

41 N型半導体領域

42 ドレイン領域

43 ドレイン電極

44 ドレイン層

45、46、47、55 トレンチ

40

53 N<sup>+</sup>領域

61 第1の正面

62 第2の正面

1、10、20、30、40、50、60、70、80、90 MOSFET

100、110、MOSFET

120 半導体装置

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【 図 1 3 】

【 図 1 4 】

【 図 15 】

【 図 1 6 】

---

フロントページの続き

| (51) Int.Cl. | F I          | テーマコード(参考) |

|--------------|--------------|------------|

|              | H 01 L 29/78 | 6 5 2 D    |

|              | H 01 L 29/78 | 3 0 1 X    |

|              | H 01 L 29/78 | 3 0 1 G    |

|              | H 01 L 21/28 | 3 0 1 A    |