SCHWEIZERISCHE EIDGENOSSENSCHAFT

EIDGENÖSSISCHES INSTITUT FÜR GEISTIGES EIGENTUM

(11) CH 695 808 A5

(51) Int. Cl.: H01L 29/861 (2006.01)

H01L 21/329 (2006.01)

### Erfindungspatent für die Schweiz und Liechtenstein

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

## (12) PATENTSCHRIFT

(21) Gesuchsnummer: 01976/00

(73) Inhaber:

Mitsubishi Denki Kabushiki Kaisha,

No. 2-3, Marunouchi 2-chome, Chiyoda-ku

Tokyo 100-8310 (JP)

(22) Anmeldedatum: 06.10.2000

(30) Priorität: 28.01.2000 JP P2000-20407

(72) Erfinder:

Noritoshi Hirano, Fukuoka-City, 810-0041 (JP)

Katsumi Satoh, Tokyo 100-8310 (JP)

(24) Patent erteilt: 31.08.2006

(74) Vertreter:

Bovard AG Patentanwälte, Optingenstrasse 16

3000 Bern 25 (CH)

(45) Patentschrift veröffentlicht: 31.08.2006

### (54) Halbleiterbauelement.

(57) Es ist ein Ziel, ein Halbleiterbauelement zu erhalten, welches einen pn-Übergang aufweist, welcher Spannungsschwankungen unterdrückt, ohne nachteilige Effekte zu verursachen. Die Schichtdicke der n-Schicht (101) ist so festgelegt, dass sie sowohl eine erste Bedingung, wonach die Sperrsicht, welche sich in der n-Schicht (101) vom pn-Übergang zwischen der n-Schicht (101) und der p-Schicht (102) aus ausbreitet, nicht die n'-Schicht (103) erreicht, wenn eine Rückwärtsspannung von ungefähr 1/2 bis 2/3 der Sperrspannungsfestigkeit der Diode angelegt wird, als auch eine zweite Bedingung erfüllt, wonach die Sperrsicht die n'-Schicht (103) erreicht, wenn eine Rückwärtsspannung angelegt wird, welche ungefähr 2/3 der Sperrspannungsfestigkeit übersteigt. Weiter ist die Störstellenkonzentration (der spezifische Widerstand) der n-Schicht (101) so festgelegt, dass das elektrische Feld, welches auf die Sperrsicht wirkt, wenn die Rückwärtsspannung gleich der Sperrspannungsfestigkeit festgelegt ist, die maximale Durchbruchfestigkeit von Silizium nicht übersteigt.

## **Beschreibung**

### **Technisches Gebiet**

[0001] Die vorliegende Erfindung betrifft Halbleiterbauelemente, namentlich Halbleiterbauelemente wie beispielsweise Dioden, welche einen pn-Übergang haben, und von welchen verlangt wird, dass sie eine hohe Durchbruchspannung und eine schnelle Sperrverzögerungscharakteristik aufweisen.

### **Stand der Technik**

[0002] Von Dioden, wie Rückflussdioden oder Spannungsklemmdiolen, wird verlangt, dass sie eine hohe Durchbruchspannung und eine schnelle Sperrverzögerungscharakteristik zur Verfügung stellen, welche in Anwendungen von Hochspannungsschaltelementen wie beispielsweise IGBTs (Insulated Gate Bipolar Transistoren) und GCTs (Gate Commutated Turn-Off Thyristoren) benötigt werden.

[0003] Fig. 13 ist ein Querschnitt, welcher den Schichtaufbau einer gewöhnlichen herkömmlichen Diode zeigt, welche die oben erwähnten Anforderungen erfüllt. Wie in der Darstellung gezeigt, ist eine n<sup>-</sup>-Schicht 601 als ein Halbleitersubstrat aus Silizium o.Ä. auf einer n<sup>+</sup>-Schicht 603 ausgebildet, und eine p-Schicht 602 ist auf der n<sup>-</sup>-Schicht 601 ausgebildet. Die Konzentration der n-leitenden Störstellen ist in der n<sup>+</sup>-Schicht 603 höher als in der n<sup>-</sup>-Schicht 601.

[0004] Eine Anodenelektrode 604, welche aus einem Metall mit niedrigem Widerstand besteht, ist auf der p-Schicht 602 ausgebildet, und eine Kathodenelektrode 605, welche aus einem Metall mit niedrigem Widerstand besteht, ist unter der n<sup>+</sup>-Schicht 603 ausgebildet.

[0005] Die Lebensdauer in der Nähe des pn-Überganges wird durch Bestrahlung mit Protonen o.Ä. kontrolliert, und es werden Rekombinationszentren für Ladungsträger gebildet. Die Lebensdauer im ganzen Halbleitersubstrat wird durch Techniken wie beispielsweise Diffusion von Edelmetallen, Bestrahlung mit Elektronen o.Ä. kontrolliert und verkürzt.

[0006] Wenn durch plötzliches Schalten eines externen Schaltkreises eine Rückwärtsspannung an eine Diode angelegt wird, in welcher ein Vorwärtsstrom fließt, erreicht der Strom kurz den Wert 0, ohne sich jedoch in Folge der Ansammlung von Minoritätsladungsträgern in der Diode sofort in der Rückwärtsrichtung zu erholen, wobei vorübergehend für eine gewisse Zeit ein grosser Rückwärtsstrom fließt (ein Strom, welcher eine Abnahmerate hat, welche durch den Wert der angelegten Rückwärtsspannung und die Induktanz des externen Schaltkreises bestimmt ist). Dieser Rückwärtsstrom fließt, bis die Überschussladungsträger in der Nähe des pn-Überganges unter eine gewisse Konzentration gesunken sind, und sich eine Sperrsicht gebildet hat.

[0007] Wenn sich eine Sperrsicht bildet, beginnt sich eine Sperrspannung aufzubauen, welche sich allmählich vergrößert, wenn die Sperrsicht sich ausdehnt, wobei der Rückwärtsstrom allmählich abnimmt. Dann wird die Bauelementspannung dauernd gleich der angelegten Rückwärtsspannung, und der Vorgang der Sperrverzögerung ist damit abgeschlossen.

[0008] In einer herkömmlichen Diode, welche einen Aufbau gemäss dem in Fig. 13 gezeigten hat, wird die Lebensdauer in der Nähe des pn-Überganges lokal kontrolliert und verkürzt, um die Kennwerte von niedriger Vorwärtsspannung, niedrigem Sperrverzögerungsstrom (der Spitzenwert des Rückwärtsstromes) und hoher di/dt-Festigkeit (der maximale Wert der Stromabnahmerate di/dt, welcher vorgegeben werden kann, ohne die Diode zu zerstören) zu realisieren.

[0009] Wenn jedoch die Rückwärtsspannung während der Sperrverzögerung hoch ist, schwankt die angelegte Spannung der Diode schnell, was derartige Störungen erzeugt, dass Fehlfunktionen der äusseren elektrischen Einrichtungen verursacht werden können. Es wird angenommen, dass solche Spannungsschwankungen in der Diode wie nachstehend gezeigt entstehen.

[0010] Eine Diode hat während der Sperrverzögerung eine kapazitive Komponente, definiert durch die Sperrsicht und die Überschussladungsträger als Parameter, und eine Widerstandskomponente, definiert durch die angelegte Spannung, den Leckstrom und den Rekombinationsstrom der Überschussladungsträger als Parameter. Die Widerstandskomponente, die kapazitive Komponente und die induktive Komponente des externen Schaltkreises zum Anlegen der Rückwärtsspannung bilden einen LCR-Seriekreis. Die kapazitive Komponente und die Widerstandskomponente der Diode variieren mit der Zeit. Die Widerstandskomponente vergrößert sich schnell, wenn die Überschussladungsträger ausserhalb der Sperrsicht verschwunden sind, wobei die natürlichen Schwingungsbedingungen des LCR-Seriekreises erreicht werden, und Spannungsschwankungen auftreten. Die Widerstandskomponente ändert auch schnell, wenn die Sperrsicht die n<sup>+</sup>-Schicht 603 erreicht, was Spannungsschwankungen verursacht.

### **Darstellung der Erfindung**

[0011] Es ist eine Aufgabe der vorliegenden Erfindung, ein Halbleiterbauelement zu erzeugen, das die obigen erste und zweite Bedingungen erfüllt, das heisst, die Spannungsschwankung unterdrückt und die Durchlassspannung auf einem angemessenen Wert hält.

[0012] Gemäss dem kennzeichnenden Teil von Anspruch 1 umfasst das Halbleiterbauelement:

eine erste Halbleiterschicht von einem ersten Leitfähigkeitsotyp;

eine zweite Halbleiterschicht vom ersten Leitfähigkeitstyp, welche auf der genannten ersten Halbleiterschicht ausgebildet ist, wobei die genannte zweite Halbleiterschicht eine kleinere Störstellenkonzentration des ersten Leitfähigkeitstyps aufweist als die genannte erste Halbleiterschicht;

ein Halbleitergebiet von einem zweiten Leitfähigkeitstyp, welches auf mindestens einem Teil der genannten zweiten Halbleiterschicht ausgebildet ist;

eine erste Hauptelektrode, welche über dem genannten Halbleitergebiet ausgebildet ist;

und eine zweite Hauptelektrode, welche unter der genannten ersten Halbleiterschicht ausgebildet ist;

worin die Schichtdicke der genannten zweiten Halbleiterschicht so festgelegt ist, dass sie sowohl eine erste Bedingung, wonach eine Sperrsicht, welche sich von einem pn-Übergang an der Grenzfläche zwischen der genannten zweiten Halbleiterschicht und dem genannten Halbleitergebiet ausbreitet, nicht die genannte erste Halbleiterschicht erreicht, wenn eine Rückwärtsspannung von 1/2 bis 2/3 der Sperrspannungsfestigkeit des genannten pn-Überganges an die genannte erste und die genannte zweite Hauptelektrode angelegt ist, als auch eine zweite Bedingung erfüllt, wonach die Sperrsicht, welche sich vom genannten pn-Übergang aus ausbreitet, die genannte erste Halbleiterschicht erreicht, wenn eine Rückwärtsspannung, welche ungefähr 2/3 der genannten Sperrspannungsfestigkeit übersteigt, an die genannte erste und die genannte zweite Hauptelektrode angelegt ist.

**[0013]** Gemäss einem zweiten Aspekt der Erfindung schliesst die erste Hauptelektrode im Halbleiterbauelement vorzugsweise eine Hauptelektrode mit ein, welche direkt auf dem Halbleitergebiet ausgebildet ist, und die zweite Hauptelektrode umfasst eine Hauptelektrode, welche direkt auf der Unterseite der ersten Halbleiterschicht ausgebildet ist.

**[0014]** Gemäss einem dritten Aspekt der Erfindung umfasst das Halbleiterbauelement vorzugsweise weiter eine dritte Halbleiterschicht vom zweiten Leitfähigkeitstyp, welche unter der ersten Halbleiterschicht ausgebildet ist, und worin die erste Hauptelektrode eine Hauptelektrode miteinschliesst, welche direkt auf dem Halbleitergebiet ausgebildet ist, und die zweite Hauptelektrode eine Hauptelektrode miteinschliesst, welche direkt auf der Unterseite der dritten Halbleiterschicht ausgebildet ist.

**[0015]** Gemäss einem vierten Aspekt der Erfindung umfasst das Halbleiterbauelement vorzugsweise weiter: eine dritte Halbleiterschicht vom zweiten Leitfähigkeitstyp, welche unter der ersten Halbleiterschicht ausgebildet ist; und eine vierte Halbleiterschicht vom ersten Leitfähigkeitstyp, welche auf dem Halbleitergebiet ausgebildet ist, und worin die erste Hauptelektrode eine Hauptelektrode miteinschliesst, welche direkt auf der vierten Halbleiterschicht ausgebildet ist, und die zweite Hauptelektrode eine Hauptelektrode miteinschliesst, welche direkt auf der Unterseite der dritten Halbleiterschicht ausgebildet ist.

**[0016]** Gemäss einem fünften Aspekt der Erfindung umfasst das Halbleitergebiet im Halbleiterbauelement vorzugsweise mehrere Halbleitergebiete, welche selektiv in der Oberfläche der zweiten Halbleiterschicht ausgebildet sind, und die erste Hauptelektrode umfasst mehrere Teilelektronen, welche jeweils auf den mehreren Halbleitergebieten ausgebildet sind.

**[0017]** Gemäss einem sechsten Aspekt der Erfindung ist die Lebensdauer im Halbleiterbauelement in der Nähe der Grenzschicht zwischen der zweiten Halbleiterschicht und dem Halbleitergebiet vorzugsweise kürzer festgelegt, als die Lebensdauer in der Nähe der Grenzschicht zwischen der ersten und zweiten Halbleiterschicht.

**[0018]** Gemäss einem siebten Aspekt der Erfindung schliesst im Halbleiterbauelement die zweite Bedingung vorzugsweise eine Bedingung mit ein, wonach die Sperrsicht, welche sich vom pn-Übergang aus ausbreitet, die erste Halbleiterschicht erreicht, wenn eine Rückwärtsspannung, welche gleich der Sperrspannungsfestigkeit des pn-Überganges ist, an die erste und zweite Hauptelektrode angelegt wird.

**[0019]** Gemäss einem achten Aspekt der Erfindung wird im Halbleiterbauelement die Störstellenkonzentration der zweiten Halbleiterschicht vorzugsweise so festgelegt, dass sie eine dritte Bedingung erfüllt, wonach das elektrische Feld, welches auf die Sperrsicht wirkt, wenn die Rückwärtsspannung gleich der Sperrspannungsfestigkeit festgelegt ist, auf einem tatsächlichen Einsatzwert ist, welcher nicht grösser ist als eine vorgegebene Feldstärke.

**[0020]** Gemäss einem neunten Aspekt der Erfindung schliesst im Halbleiterbauelement der erste Leitfähigkeitstyp vorzugsweise den n-leitenden Typ mit ein und der zweite Leitfähigkeitstyp den p-leitenden Typ mit ein.

**[0021]** Wie oben beschrieben, wird gemäss dem Halbleiterbauelement des ersten Aspektes der Erfindung die Schichtdicke der zweiten Halbleiterschicht so festgelegt, dass sie die erste Bedingung erfüllt. Folglich ist es sicher möglich, die Spannungsschwankung zu unterdrücken, welche auftreten würde, wenn die Sperrsicht die erste Halbleiterschicht erreicht, wenn eine Rückwärtsspannung von ungefähr 1/2 bis 2/3 der Spannungsfestigkeit, welche im Allgemeinen während der Sperrverzögerung verwendet wird, angelegt wird.

**[0022]** Ausserdem ist die Schichtdicke der zweiten Halbleiterschicht so festgelegt, dass sie auch die zweite Bedingung erfüllt, sodass die Durchlassspannung auf einem angemessenen Wert gehalten werden kann.

**[0023]** Infolgedessen ist es möglich, die Reduktion der Durchlassspannung wünschenswerterweise gegen die Unterdrückung der Spannungsschwankung abzuwagen.

**[0024]** Das Halbleiterbauelement des zweiten Aspektes der Erfindung stellt eine Diode zur Verfügung, welche eine gut ausgewogene Reduktion der Durchlassspannung und Unterdrückung der Spannungsschwankung erzielen kann.

**[0025]** Das Halbleiterbauelement des dritten Aspektes der Erfindung stellt einen Transistor zur Verfügung, welcher eine gut ausgewogene Reduktion der Durchlassspannung und Unterdrückung der Spannungsschwankung erzielen kann.

**[0026]** Das Halbleiterbauelement des vierten Aspektes der Erfindung stellt einen Thyristor zur Verfügung, welcher eine gut ausgewogene Reduktion der Durchlassspannung und Unterdrückung der Spannungsschwankung erzielen kann.

**[0027]** Gemäss dem Halbleiterbauelement des fünften Aspektes bilden die mehreren Halbleiterteilgebiete an ihren jeweiligen seitlichen Begrenzungen pn-Übergänge mit der zweiten Halbleiterschicht, was eine Diode mit verbesserter Durchbruchspannung ergibt.

**[0028]** Gemäss dem Halbleiterbauelement des sechsten Aspektes unterdrückt das Festlegen eines kurzen Wertes der Lebensdauer in der Nähe der Grenzschicht zwischen der zweiten Halbleiterschicht und dem Halbleitergebiet (in der Nähe des pn-Überganges) die Ausbreitung der Sperrsicht vom pn-Übergang aus, was erlaubt, die zweite Halbleiterschicht dünner zu machen.

**[0029]** Das Halbleiterbauelement des siebten Aspektes verwendet für die zweite Bedingung als Rückwärtsspannung eine Spannung, welche gleich der Sperrspannungsfestigkeit ist, was einen Aufbau zur Verfügung stellt, welcher an die tatsächliche Ausführung angepasst ist.

**[0030]** Gemäss dem Halbleiterbauelement des achten Aspektes wird die Störstellenkonzentration der zweiten Halbleiterschicht so festgelegt, dass das elektrische Feld, welches auf die Sperrsicht wirkt, wenn die angelegte Rückwärtsspannung gleich der Sperrspannungsfestigkeit festgelegt ist, einen tatsächlichen Einsatzwert aufweist, welcher nicht höher ist als eine vorbestimmte Feldstärke, und deshalb im aktuellen Betrieb keine Probleme auftreten.

**[0031]** Die vorliegende Erfindung wurde gemacht, um das obige Problem zu lösen, und es ist ein Ziel der Erfindung, ein Halbleiterbauelement zu erhalten, welches einen pn-Übergang aufweist, welcher Spannungsschwankungen unterdrückt, ohne nachteilige Effekte zu verursachen.

**[0032]** Diese und andere Ziele, Merkmale, Aspekte und Vorteile der vorliegenden Erfindung sind besser aus der folgenden detaillierten Beschreibung der vorliegenden Erfindung ersichtlich, wenn sie in Verbindung mit den zugehörigen Zeichnungen betrachtet werden.

### **Kurze Beschreibung der Zeichnungen**

**[0033]**

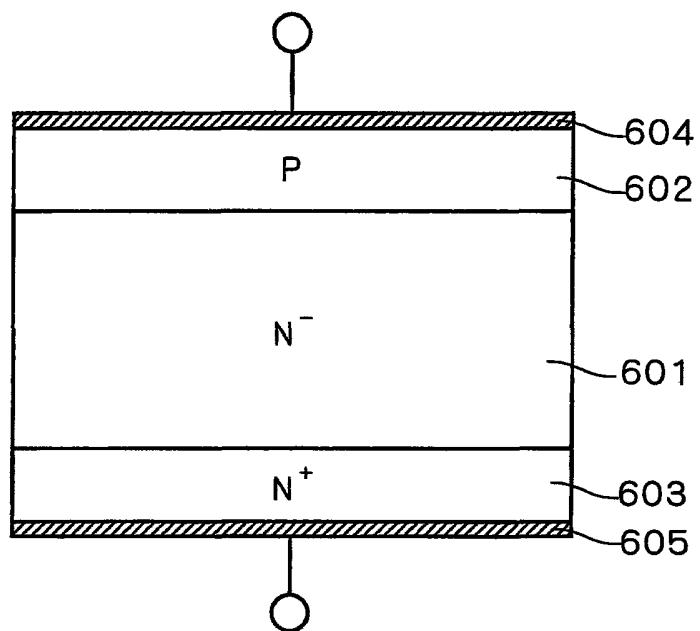

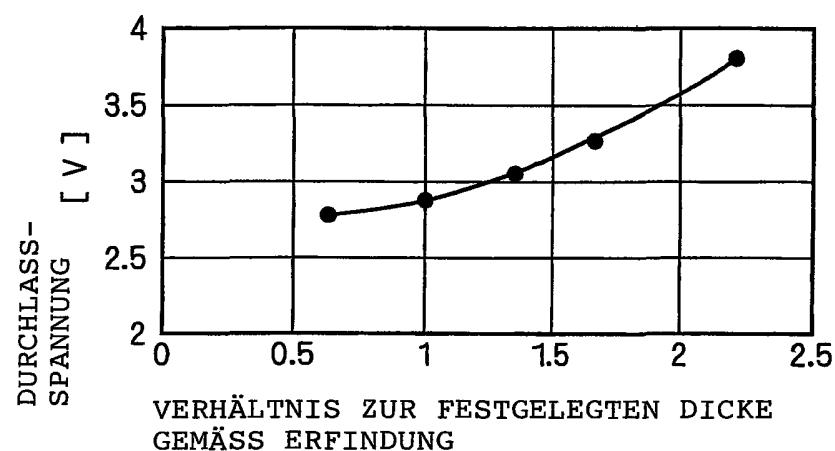

- Fig. 1 ist eine grafische Darstellung, welche die Beziehung zwischen der Schichtdicke der n<sup>-</sup>-Schicht in einem Aufbau gemäss der Erfindung und der Durchlassspannung zeigt;

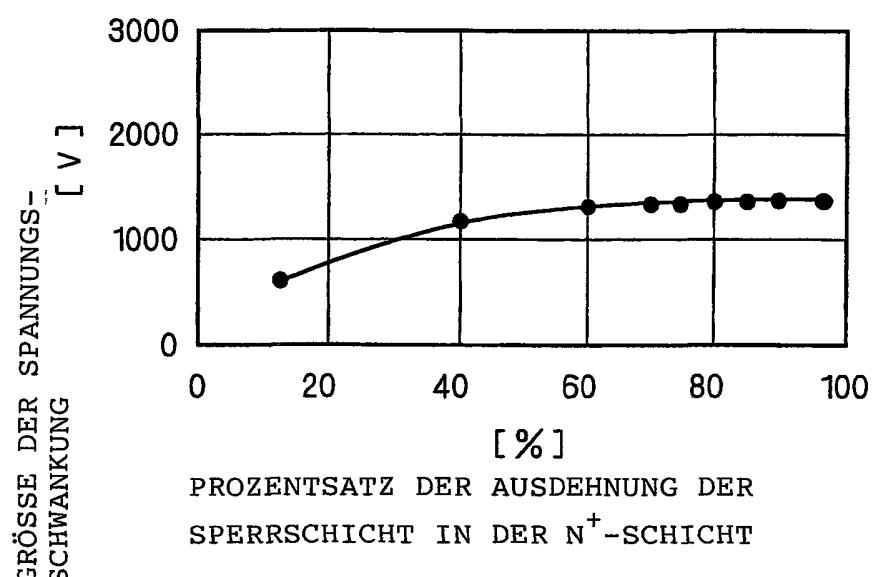

- Fig. 2 ist eine grafische Darstellung, welche den Prozentsatz der Ausbreitung der Sperrsicht in der n<sup>-</sup>-Schicht und die Grösse der Spannungsschwankung zeigt, wenn eine Rückwärtsspannung angelegt ist, welche 2/3 der Sperrspannungsfestigkeit übersteigt;

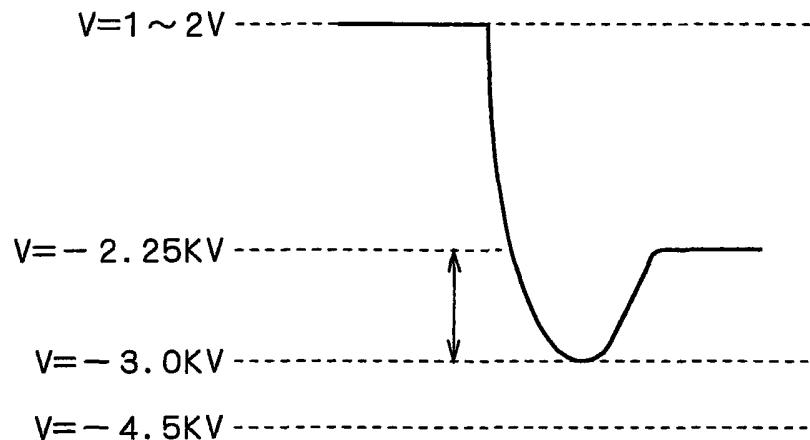

- Fig. 3 ist eine Darstellung einer Wellenform, welche die Änderung der Rückwärtsspannung in einer Diode während der Sperrverzögerung zeigt;

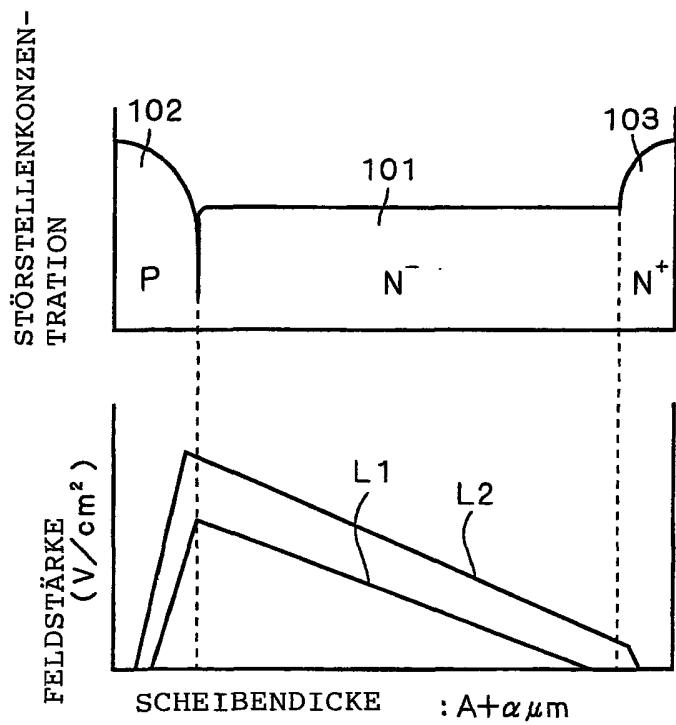

- Fig. 4 ist eine erklärende Darstellung, welche eine charakteristische Eigenschaft des Aufbaus gemäss der Erfindung zeigt;

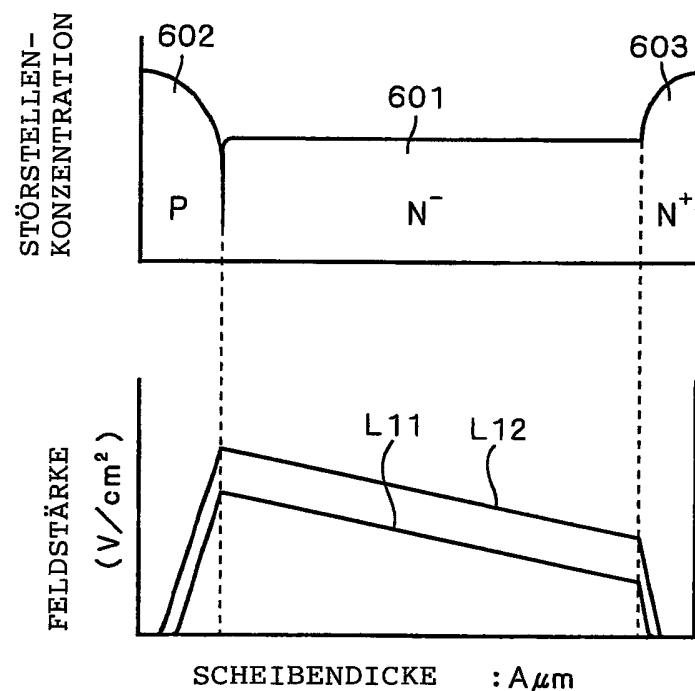

- Fig. 5 ist eine erklärende Darstellung, welche eine charakteristische Eigenschaft einer Diode zeigt, welche einen herkömmlichen PIN-Aufbau aufweist;

- Fig. 6 ist eine erklärende Darstellung, welche eine charakteristische Eigenschaft einer Diode zeigt, welche einen pn-Übergang-Aufbau hat;

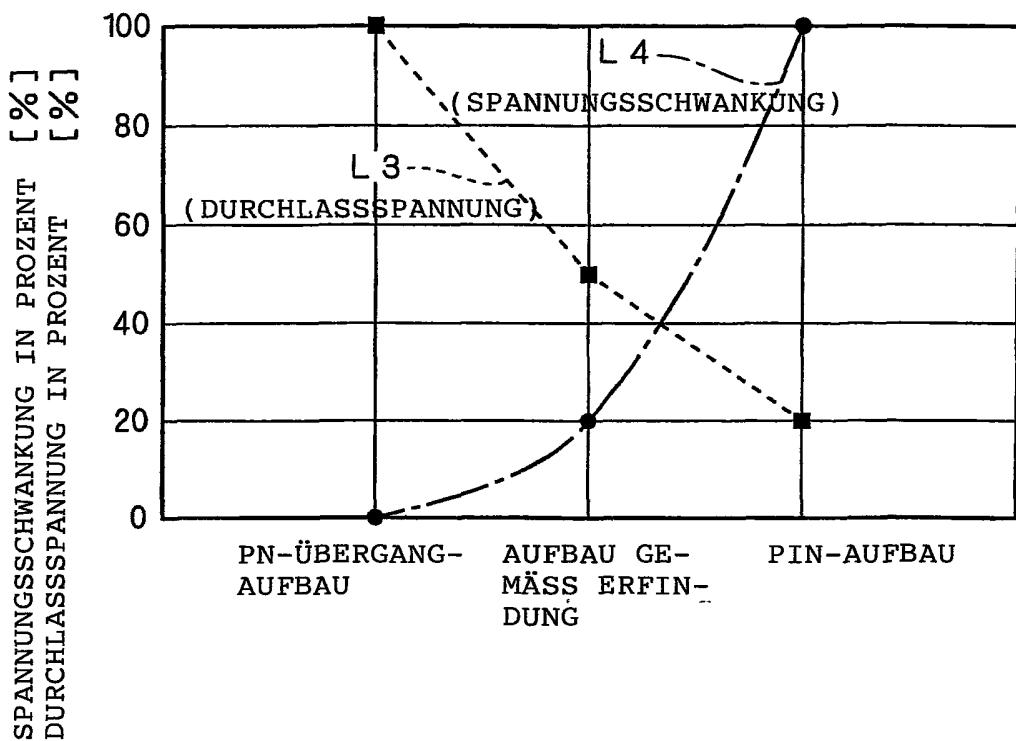

- Fig. 7 ist eine grafische Darstellung, welche den Prozentsatz der Durchlassspannung und den Prozentsatz der Spannungsschwankung im Aufbau der Erfindung, im PIN-Aufbau und im pn-Übergang-Aufbau zeigt;

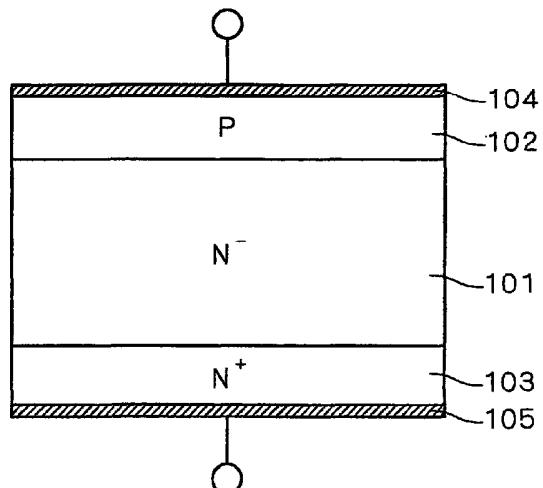

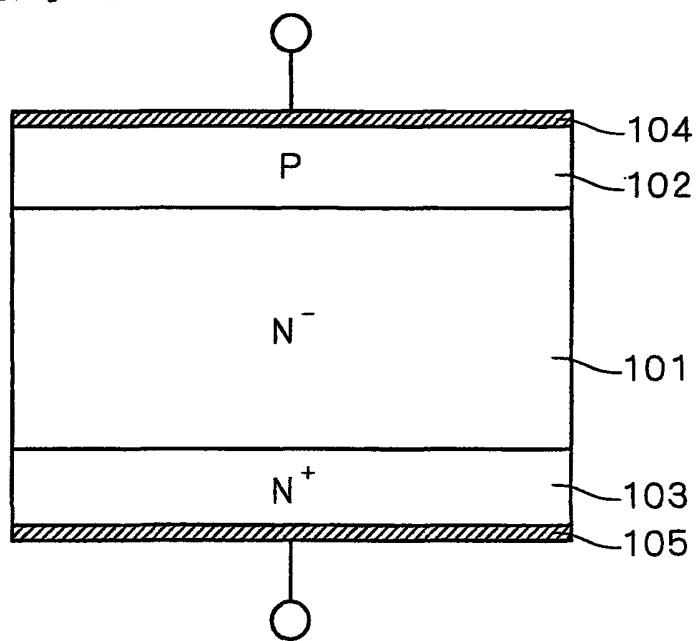

- Fig. 8 ist ein Querschnitt, welcher den Aufbau eines Halbleiterbauelementes gemäss einer ersten bevorzugten Ausführungsform der Erfindung zeigt;

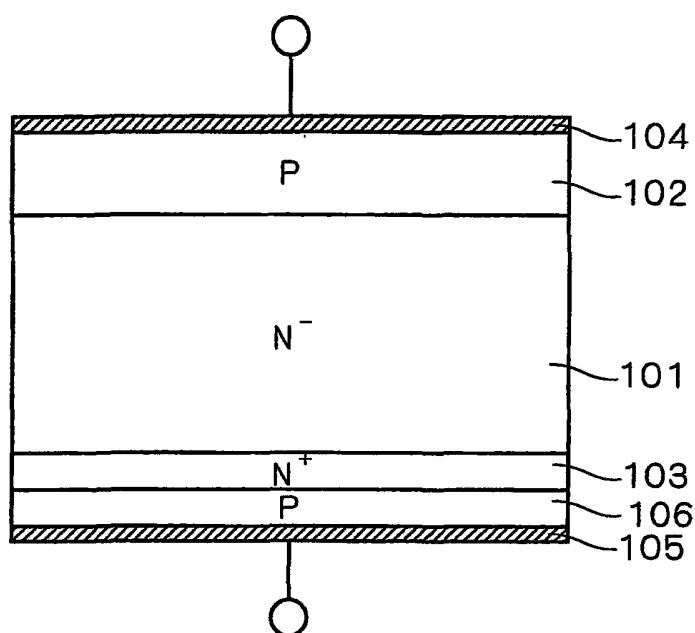

- Fig. 9 ist ein Querschnitt, welcher den Aufbau eines Halbleiterbauelementes gemäss einer zweiten bevorzugten Ausführungsform der Erfindung zeigt;

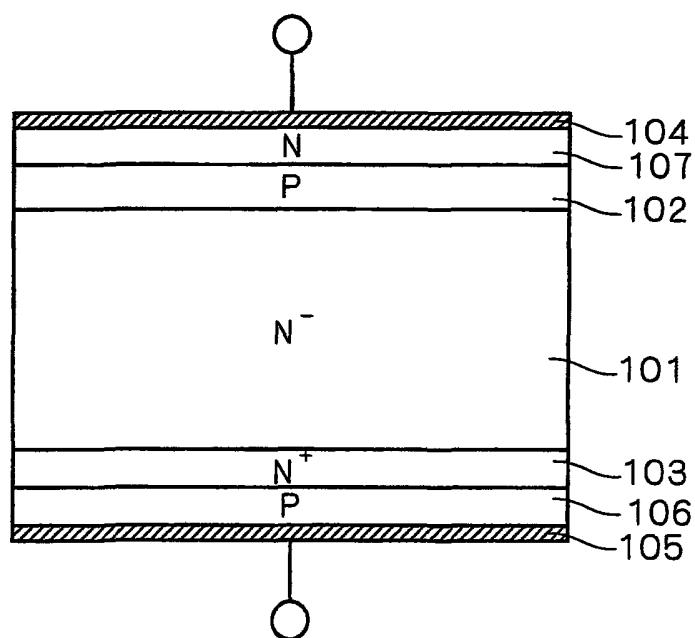

- Fig. 10 ist ein Querschnitt, welcher den Aufbau eines Halbleiterbauelementes gemäss einer dritten bevorzugten Ausführungsform der Erfindung zeigt;

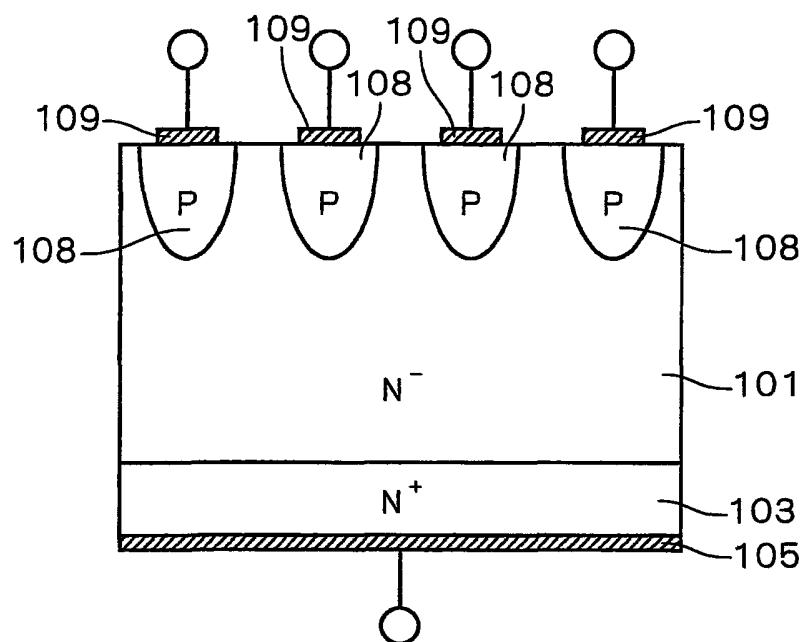

- Fig. 11 ist ein Querschnitt, welcher den Aufbau eines Halbleiterbauelementes gemäss einer vierten bevorzugten Ausführungsform der Erfindung zeigt;

Fig. 12 ist ein Querschnitt, welcher den Aufbau eines Halbleiterbauelementes gemäss einer fünften bevorzugten Ausführungsform der Erfindung zeigt;

Fig. 13 ist ein Querschnitt, welcher einen Schichtaufbau einer allgemeinen herkömmlichen Diode zeigt.

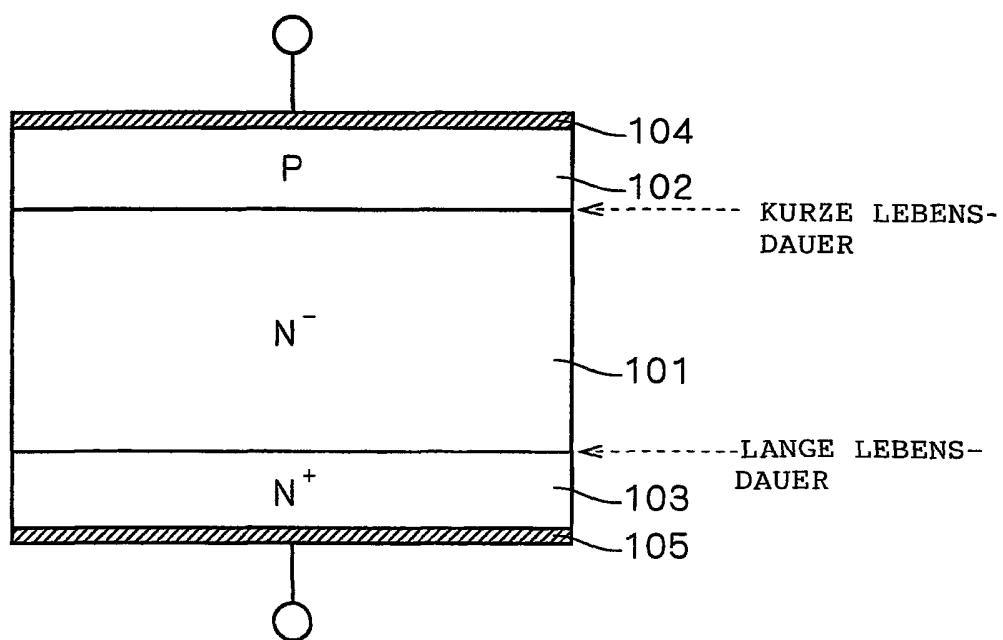

### Wege zur Ausführung der Erfindung

#### Prinzip

[0034] Die Grundanordnung der Erfindung ist ein Dreischichtaufbau, bestehend aus einer p-Schicht, einer n<sup>-</sup>-Schicht und einer n<sup>+</sup>-Schicht. Im Aufbau gemäss der ersten bevorzugten Ausführungsform, welche später beschrieben wird, entsprechen die p-Schicht 102, die n<sup>-</sup>-Schicht 101 und die n<sup>+</sup>-Schicht 103, welche in Fig. 8 gezeigt sind, der p-Schicht, bzw. der n<sup>-</sup>-Schicht, bzw. der n<sup>+</sup>-Schicht.

[0035] Wenn eine Sperrverzögerung (der Betriebszustand der Erholung der Sperrspannungsfestigkeit, wenn der pn-Übergang von einem leitenden Zustand in Vorwärtsrichtung in einen sperrenden Zustand in Rückwärtsrichtung umgeschaltet wird) an den Diodenteil (pn-Übergang) gemäss dieser Grundanordnung angelegt ist, ändert sich die Widerstandskomponente schnell, wenn die Sperrsicht, welche sich in der Grundanordnung bildet, die n<sup>+</sup>-Schicht erreicht, was eine Spannungsschwankung auslöst.

[0036] Diese Spannungsschwankung kann verhindert werden durch Vergrössern der Schichtdicke der n<sup>-</sup>-Schicht in der Grundanordnung, sodass die Sperrsicht, welche sich in der n<sup>-</sup>-Schicht vom pn-Übergang zwischen der p-Schicht und der n<sup>-</sup>-Schicht aus ausbreitet, die n<sup>+</sup>-Schicht nicht erreicht. Wenn jedoch die n<sup>-</sup>-Schicht lediglich dicker gemacht wird, wird die Schichtdicke der n<sup>-</sup>-Schicht (die Scheibendicke) gross und verursacht eine Erhöhung der Durchlassspannung.

[0037] Ein PIN-Aufbau mit einer dünnen Scheibendicke andererseits ergibt eine niedrige Durchlassspannung, kann jedoch sehr grosse Spannungsschwankungen nicht verhindern, da die Sperrsicht während der Sperrverzögerung die n<sup>+</sup>-Schicht erreicht.

[0038] Die vorliegende Erfindung beabsichtigt, eine Grundanordnung zu erzielen, welche wünschenswerterweise die Verminderung der Durchlassspannung und die Unterdrückung der Spannungsschwankung gegeneinander abwägen kann. Es wurde gefunden, dass die Schichtdicke der n<sup>-</sup>-Schicht im Diodenteil gemäss der Grundanordnung so festgelegt werden soll, dass die Sperrsicht, welche sich in der n<sup>-</sup>-Schicht vom pn-Übergang zwischen der p-Schicht und der n<sup>-</sup>-Schicht aus ausbreitet, nicht die n<sup>+</sup>-Schicht erreicht, wenn eine Rückwärtsspannung angelegt wird, welche ungefähr 1/2 bis 2/3 der Sperrspannungsfestigkeit entspricht, und dass die Sperrsicht die n<sup>+</sup>-Schicht erreicht, wenn eine Rückwärtsspannung angelegt wird, welche ungefähr 2/3 der Sperrspannungsfestigkeit übersteigt.

[0039] Fig. 1 ist eine grafische Darstellung, welche die Beziehung zwischen der Schichtdicke der n<sup>-</sup>-Schicht und der Durchlassspannung in einem Aufbau gemäss der Erfindung zeigt. In dieser Darstellung wird die Schichtdicke der n<sup>-</sup>-Schicht, welche gemäss der Erfindung festgelegt ist, als «1» angenommen (diese Schichtdicke wird im Folgenden als «festgelegte Schichtdicke» bezeichnet). Wie in dieser Darstellung gezeigt, steigt die Durchlassspannung, wenn die Schichtdicke der n<sup>-</sup>-Schicht über die festgelegte Schichtdicke hinaus dicker wird; wenn sie beispielsweise auf den zweifachen Wert der festgelegten Schichtdicke erhöht wird, vergrössert sich die Durchlassspannung um ungefähr 0.8 V. Wenn andererseits die Schichtdicke der n<sup>-</sup>-Schicht dünner wird als die festgelegte Schichtdicke, nimmt die Durchlassspannung ab. Sie nimmt jedoch nur noch mit einer kleinen Rate ab; die Durchlassspannung sinkt beispielsweise nur um etwa 0.1 bis 0.2 V, sogar wenn die Schichtdicke auf den halben Wert der festgelegten Schichtdicke gesenkt wird.

[0040] Wenn eine Rückwärtsspannung von ungefähr 2/3 der Sperrspannungsfestigkeit oder weniger angelegt wird, erreicht die Sperrsicht, welche sich vom pn-Übergang aus ausbreitet, nicht die n<sup>+</sup>-Schicht, sodass die Grösse der Spannungsschwankung nahezu auf Null heruntergedrückt werden kann.

[0041] Fig. 2 ist eine grafische Darstellung, welche den Prozentsatz der Ausbreitung der Sperrsicht in der n<sup>-</sup>-Schicht und die Grösse der Spannungsschwankung zeigt, wenn eine Rückwärtsspannung angelegt wird, welche 2/3 der Sperrspannungsfestigkeit übersteigt. Wie in der Darstellung gezeigt, wird die Grösse der Spannungsschwankung innerhalb des zulässigen Bereichs wesentlich unter 2 kV gehalten, wenn eine Rückwärtsspannung angelegt wird, welche 2/3 der Sperrspannungsfestigkeit übersteigt, und die Sperrsicht die n<sup>+</sup>-Schicht erreicht und sich in der n<sup>+</sup>-Schicht ausbreitet.

[0042] Fig. 3 ist eine Darstellung einer Wellenform, welche ein Beispiel für den Verlauf der Rückwärtsspannung während der Sperrverzögerung zeigt. Wie in der Darstellung gezeigt, wird eine Rückwärtsspannung in einem Zustand angelegt, in welchem eine konstante Spannung von ungefähr 1 bis 2 V an der Diode anliegt und ein Vorwärtsstrom fliesst. In diesem Fall wird in der allgemeinen Anwendung der Spitzenwert auf ungefähr 2/3 der Sperrspannungsfestigkeit festgelegt und der stationäre Wert der Spannung auf ungefähr 1/2. In einer Diode, welche beispielsweise eine Sperrspannungsfestigkeit von -4.5 kV hat (die Rückwärtsrichtung wird als «-» dargestellt), liegt der Spitzenwert um -3 kV entsprechend ungefähr 2/3 der Sperrspannungsfestigkeit, und der stationäre Wert der Spannung beträgt -2.25 kV entsprechend ungefähr 1/2.

[0043] Die vorliegende Erfindung berücksichtigt die oben angegebenen Bedingungen und legt die Schichtdicke der n<sup>-</sup>-Schicht im Diodenteil gemäss der Grundanordnung so fest, dass die folgenden beiden Bedingungen erfüllt sind: eine erste Bedingung, wonach die Sperrsicht, welche sich in der n<sup>-</sup>-Schicht ausbreitet, nicht die n<sup>+</sup>-Schicht erreicht, wenn

eine Rückwärtsspannung angelegt wird, welche ungefähr 1/2 bis 2/3 der Sperrspannungsfestigkeit entspricht, und eine zweite Bedingung, wonach die Sperrsicht die  $n^+$ -Schicht erreicht, wenn eine Rückwärtsspannung angelegt wird, welche ungefähr 2/3 der Sperrspannungsfestigkeit übersteigt.

[0044] Wie oben festgehalten, erfüllt die Schichtdicke der  $n^-$ -Schicht die erste Bedingung, wenn die Rückwärtsspannung während der Sperrverzögerung auf ungefähr 1/2 bis 2/3 der Sperrspannungsfestigkeit festgelegt wird, sodass die Sperrsicht, welche sich in der  $n^-$ -Schicht ausbreitet, in dieser Zeit nicht die  $n^+$ -Schicht erreicht. Folglich ist es, wie oben angegeben, möglich, die Spannungsschwankung wirksam zu unterdrücken.

[0045] Weiter wird die Schichtdicke der  $n^-$ -Schicht dünn genug festgelegt, um die zweite Bedingung zu erfüllen, sodass die Durchlassspannung auf einen geeigneten Wert festgelegt werden kann.

[0046] Um eine genügende Spannungsfestigkeit zu erzielen, um den praktischen Einsatz zu überdauern, wird zudem die Störstellenkonzentration (der spezifische Widerstand) der  $n^-$ -Schicht so festgelegt, dass sie eine dritte Bedingung erfüllt, wonach das elektrische Feld, welches auf die Sperrsicht wirkt, wenn die angelegte Rückwärtsspannung auf ungefähr 1/1 der Sperrspannungsfestigkeit festgelegt ist, im Einsatz einen tatsächlichen Wert aufweist, welcher nicht höher ist als die maximale Durchbruchfestigkeit von Silizium (den maximalen Wert der Feldstärke, den Silizium aushalten kann).

[0047] In der Praxis werden die Störstellenkonzentration und die Schichtdicke der  $n^-$ -Schicht bestimmt, indem die wechselseitigen Beziehungen zwischen der ersten bis dritten Bedingung berücksichtigt werden, da die Störstellenkonzentration der  $n^-$ -Schicht mit der Ausdehnung der Sperrsicht verknüpft ist.

[0048] Fig. 4 ist eine erklärende Darstellung, welche eine charakteristische Eigenschaft des Aufbaus gemäss der Erfindung zeigt. Wie in Fig. 4 gezeigt, nimmt die vorliegende Erfindung als Grundanordnung einen Dreischichtaufbau, bestehend aus der p-Schicht 102, der  $n^-$ -Schicht 101 und der  $n^+$ -Schicht 103 an, welcher die als L1 gezeigte elektrische Feldverteilung aufweist, wo die Sperrsicht, welche sich vom pn-Übergang zwischen der  $n^-$ -Schicht 101 und p-Schicht 102 aus bildet, nicht die  $n^+$ -Schicht 103 erreicht, wenn eine Rückwärtsspannung von ungefähr 1/2 bis 2/3 der Sperrspannungsfestigkeit angelegt wird, und welcher die als L2 gezeigte elektrische Feldverteilung aufweist, wo die Sperrsicht die  $n^+$ -Schicht 103 erreicht, wenn eine Rückwärtsspannung angelegt wird, welche ungefähr 2/3 der Sperrspannungsfestigkeit übersteigt.

[0049] Fig. 5 ist eine erklärende Darstellung, welche eine charakteristische Eigenschaft der herkömmlichen PIN-Diode zeigt, welche in Fig. 13 dargestellt ist. Wie in dieser Darstellung gezeigt, ist die Grundanordnung des PIN-Aufbaus ein Dreischichtaufbau bestehend aus der p-Schicht 602, der  $n^-$ -Schicht 601 und der  $n^+$ -Schicht 603, wo die Sperrsicht, welche sich vom pn-Übergang zwischen der  $n^-$ -Schicht 601 und p-Schicht 602 aus bildet, wenn eine Rückwärtsspannung von ungefähr 1/2 bis 2/3 der Sperrspannungsfestigkeit angelegt wird, und die Sperrsicht, welche sich vom pn-Übergang aus bildet, wenn eine Rückwärtsspannung angelegt wird, welche ungefähr 2/3 der Sperrspannungsfestigkeit übersteigt, beide die  $n^+$ -Schicht 603 erreichen. Die Darstellung zeigt die elektrische Feldverteilung, im ersten Fall als L11 und im letzteren Fall als L12.

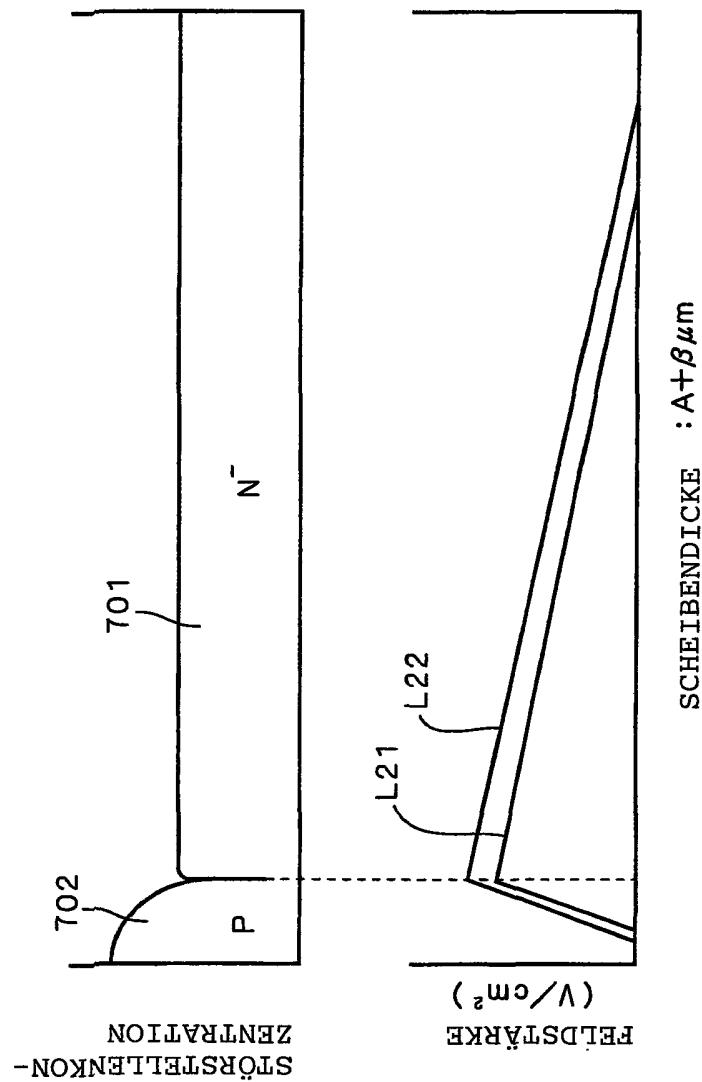

[0050] Fig. 6 ist eine erklärende Darstellung, welche eine charakteristische Eigenschaft einer Diode zeigt, welche einen einfachen pn-Übergang-Aufbau hat. Wie in dieser Darstellung gezeigt, ist die Grundanordnung des einfachen pn-Übergang-Aufbaus ein Zweischichtaufbau, welcher aus einer p-Schicht 702 und einer  $n^-$ -Schicht 701 besteht, wo die Sperrsicht, welche sich vom pn-Übergang zwischen der  $n^-$ -Schicht 601 und p-Schicht 602 aus bildet, wenn eine Rückwärtsspannung von ungefähr 1/2 bis 2/3 der Sperrspannungsfestigkeit angelegt wird, und die Sperrsicht, welche sich bildet, wenn eine Rückwärtsspannung angelegt wird, welche ungefähr 2/3 der Sperrspannungsfestigkeit übersteigt, beide die  $n^+$ -Schicht 603 nicht erreichen. Die Darstellung zeigt die elektrische Feldverteilung, im ersten Fall als L21 und im letzten Fall als L22.

[0051] Wenn alle andern Bedingungen ausser der Schichtdicke der  $n^-$ -Schicht gleich gewählt werden, und die Schichtdicke in der  $n^-$ -Schicht 601 im PIN-Aufbau mit  $A \mu\text{m}$  angenommen wird, dann ist die Schichtdicke in der  $n^-$ -Schicht 101 somit  $(A+\alpha) \mu\text{m}$  mit  $\alpha > 0$  und die Schichtdicke in der  $n^-$ -Schicht 701  $(A+\beta) \mu\text{m}$  mit  $\beta > \alpha$ .

[0052] Fig. 7 ist eine grafische Darstellung, welche den Prozentsatz der Durchlassspannung und den Prozentsatz der Spannungsschwankung im Aufbau der Erfindung, im PIN-Aufbau und im pn-Übergang-Aufbau zeigt. Wie durch die Kurve der Durchlassspannung L3 und die Kurve der Spannungsschwankung L4 gezeigt, kann der Aufbau der Erfindung, verglichen mit dem herkömmlichen PIN-Aufbau und dem pn-Übergang-Aufbau, ein besseres Gleichgewicht zwischen der Verminderung der Durchlassspannung und der Unterdrückung der Spannungsschwankung erzielen.

[0053] Es ist bevorzugt für die tatsächliche Ausführung, dass in der zweiten Bedingung als Spannung, welche 2/3 der Sperrspannungsfestigkeit übersteigt, eine Spannung angenommen wird, welche gleich der Sperrspannungsfestigkeit ist, sodass für die zweite Bedingung in den nachstehend beschriebenen bevorzugten Ausführungsformen als Rückwärtsspannung eine Spannung angenommen wird, welche gleich der Sperrspannungsfestigkeit ist.

#### Erste bevorzugte Ausführungsform

[0054] Fig. 8 ist ein Querschnitt, welcher den Aufbau eines Halbleiterbauelementes gemäss einer ersten bevorzugten Ausführungsform der Erfindung zeigt. Wie in der Darstellung gezeigt, ist eine  $n^-$ -Schicht 101 als Halbleitersubstrat, welches aus Silizium o.Ä. besteht, auf einer  $n^+$ -Schicht 103 ausgebildet, und eine p-Schicht 102 ist auf der  $n^-$ -Schicht 101 ausgebildet, wobei die Störstellenkonzentration in der  $n^+$ -Schicht 103 grösser ist als in der  $n^-$ -Schicht 101.

**[0055]** Eine Anodenelektrode 104, welche aus einem Metall mit niedrigem Widerstand besteht, ist auf der p-Schicht 102 ausgebildet, und eine Kathodenelektrode 105, welche wie die Anodenelektrode 104 aus einem Metall mit niedrigem Widerstand besteht, ist unter der n<sup>+</sup>-Schicht 603 ausgebildet.

**[0056]** Das Halbleiterbauelement gemäss der ersten bevorzugten Ausführungsform bildet somit eine Diode, bestehend aus der p-Schicht 102 (der n<sup>-</sup>-Schicht 101 und der n<sup>+</sup>-Schicht 103).

**[0057]** In diesem Aufbau ist die Schichtdicke der n<sup>-</sup>-Schicht 101, wie oben beschrieben, so festgelegt, dass sie sowohl die erste Bedingung, wonach die Sperrsicht, welche sich in der n<sup>-</sup>-Schicht 101 vom pn-Übergang zwischen der n<sup>-</sup>-Schicht 101 und der p-Schicht 102 ausbreitet, nicht die n<sup>+</sup>-Schicht 103 erreicht, wenn eine Rückwärtsspannung von ungefähr 1/2 bis 2/3 der Sperrspannungsfestigkeit des pn-Überganges dieser Diode angelegt wird, als auch die zweite Bedingung erfüllt, wonach die Sperrsicht die n<sup>+</sup>-Schicht 103 erreicht, wenn eine Rückwärtsspannung von ungefähr 1/1 der Sperrspannungsfestigkeit angelegt wird.

**[0058]** Weiter ist die Störstellenkonzentration (der spezifische Widerstand) der n<sup>-</sup>-Schicht 101 so festgelegt, dass das elektrische Feld, welches auf die Sperrsicht wirkt, wenn die Rückwärtsspannung auf ungefähr 1/1 der Sperrspannungsfestigkeit festgelegt ist, nicht höher ist als die maximale Durchbruchfestigkeit von Silizium.

**[0059]** Der Aufbau gemäss der ersten bevorzugten Ausführungsform stellt eine Diode zur Verfügung, mit welcher die Reduktion der Durchlassspannung wünschenswerterweise gegen die Unterdrückung der Spannungsschwankung abgewogen werden kann.

**[0060]** Konkrete Ausführungen der ersten bevorzugten Ausführungsform umfassen ein Beispiel, in welchem die n<sup>-</sup>-Schicht 101 als Scheibendicke eine Schichtdicke von 600 µm hat, die p-Schicht 102 eine Schichtdicke von 90 µm hat, und die n<sup>+</sup>-Schicht 103 eine Schichtdicke von 40 µm hat, wobei die Störstellenkonzentration der p-Schicht 102 gleich  $5.0 \times 10^{23}$  Atome/m<sup>3</sup> ist, die Störstellenkonzentration der n<sup>-</sup>-Schicht 101 gleich  $2.1 \times 10^{19}$  Atome/m<sup>3</sup> ist (spezifischer Widerstand von  $2.2 \Omega \cdot m$ ), und die Störstellenkonzentration der n<sup>+</sup>-Schicht 103 gleich  $1.0 \times 10^{20}$  Atome/m<sup>3</sup> ist, wobei die Sperrspannungsfestigkeit ungefähr 4.5 kV beträgt.

#### **Zweite bevorzugte Ausführungsform**

**[0061]** Fig. 9 ist ein Querschnitt, welcher den Aufbau eines Halbleiterbauelementes gemäss einer zweiten bevorzugten Ausführungsform der Erfindung zeigt. Wie in dieser Darstellung gezeigt, ist eine p-Schicht 106 zwischen die n<sup>+</sup>-Schicht 103 und die Kathodenelektrode 105 eingefügt. Abgesehen davon ist dieser Aufbau der gleiche wie derjenige in der ersten bevorzugten Ausführungsform, welcher in Fig. 8 gezeigt ist, und wird deshalb hier nicht nochmals im Detail beschrieben.

**[0062]** Das Halbleiterbauelement gemäss der zweiten bevorzugten Ausführungsform bildet somit einen bipolaren PNP-Transistor, bestehend aus der p-Schicht 102 (der n<sup>-</sup>-Schicht 101, der n<sup>+</sup>-Schicht 103), und der p-Schicht 106. Mit dem bipolaren Transistor gemäss dem Aufbau der zweiten bevorzugten Ausführungsform kann eine gut ausgewogene Reduktion der Durchlassspannung und Unterdrückung der Spannungsschwankung erzielt werden.

#### **Dritte bevorzugte Ausführungsform**

**[0063]** Fig. 10 ist ein Querschnitt, welcher den Aufbau eines Halbleiterbauelementes gemäss einer dritten bevorzugten Ausführungsform der Erfindung zeigt. Wie in dieser Darstellung gezeigt, ist eine n-Schicht 107 zwischen die p-Schicht 102 und die Anodenelektrode 104 eingefügt. Abgesehen davon ist dieser Aufbau der gleiche wie derjenige in der zweiten bevorzugten Ausführungsform, welcher in Fig. 9 gezeigt ist, und wird deshalb hier nicht nochmals im Detail beschrieben.

**[0064]** Das Halbleiterbauelement gemäss der dritten bevorzugten Ausführungsform bildet somit einen NPNP-Thyristor, bestehend aus der n-Schicht 107, der p-Schicht 102 (der n<sup>-</sup>-Schicht 101, der n<sup>+</sup>-Schicht 103), und der p-Schicht 106. Mit dem Thyristor gemäss dem Aufbau der dritten bevorzugten Ausführungsform kann eine gut ausgewogene Reduktion der Durchlassspannung und Unterdrückung der Spannungsschwankung erzielt werden.

#### **Vierte bevorzugte Ausführungsform**

**[0065]** Fig. 11 ist ein Querschnitt, welcher den Aufbau eines Halbleiterbauelementes gemäss einer vierten bevorzugten Ausführungsform der Erfindung zeigt. Wie in dieser Darstellung gezeigt, sind an Stelle der in Fig. 8 gezeigten p-Schicht 102 der ersten bevorzugten Ausführungsform mehrere p-Gebiete 108 selektiv in der Oberfläche der n<sup>-</sup>-Schicht 101 ausgebildet. Weiter sind Teilanodenelektroden 109 auf den einzelnen p-Gebieten 108 ausgebildet. Abgesehen davon ist dieser Aufbau der gleiche wie derjenige der ersten bevorzugten Ausführungsform, welcher in Fig. 8 gezeigt ist, und wird deshalb hier nicht nochmals im Detail beschrieben.

**[0066]** Gemäss dem Aufbau des Halbleiterbauelementes gemäss der vierten bevorzugten Ausführungsform bilden die seitlichen Begrenzungen der einzelnen p-Gebiete 108 pn-Übergänge mit der n<sup>-</sup>-Schicht, womit eine Diode zur Verfügung gestellt wird, welche gegenüber der ersten bevorzugten Ausführungsform eine verbesserte Durchbruchspannung aufweist.

**Fünfte bevorzugte Ausführungsform**

[0067] Fig. 12 ist ein Querschnitt, welcher den Aufbau eines Halbleiterbauelementes gemäss einer fünften bevorzugten Ausführungsform der Erfindung zeigt. Der Aufbau der fünften bevorzugten Ausführungsform ist beinahe identisch zu demjenigen der ersten bevorzugten Ausführungsform, welcher in Fig. 8 gezeigt ist. Der Aufbau unterscheidet sich jedoch von letzterem, indem er so kontrolliert ist, dass die Lebensdauer in der Nähe des Überganges zwischen der p-Schicht 102 und der n<sup>-</sup>-Schicht 101 kürzer ist als die Lebensdauer in der Nähe des Überganges zwischen der n<sup>-</sup>-Schicht 101 und der n<sup>+</sup>-Schicht 103.

[0068] Indem im Aufbau gemäss der fünften bevorzugten Ausführungsform die Lebensdauer in der Nähe des pn-Überganges zwischen der n<sup>-</sup>-Schicht 101 und der p-Schicht 102 kürzer festgelegt ist, wird die Ausbreitung der Sperrsicht in der n<sup>-</sup>-Schicht 101 vom pn-Übergang zwischen der n<sup>-</sup>-Schicht 101 und der p-Schicht 102 aus unterdrückt. Folglich können, wenn die andern Bedingungen als gleich angenommen werden, die obige erste bis dritte Bedingung erfüllt werden, sogar wenn die Schichtdicke der n<sup>-</sup>-Schicht 101 dünner festgelegt ist, als in der ersten bevorzugten Ausführungsform.

[0069] Obwohl die Erfindung im Detail beschrieben wurde, ist die obige Beschreibung in allen Aspekten beispielhaft und nicht restriktiv. Es versteht sich, dass zahlreiche andere Modifikationen und Variationen entworfen werden können, ohne von der Idee der Erfindung abzuweichen.

**Patentansprüche**

1. Halbleiterbauelement umfassend:

- eine erste Halbleiterschicht (103) von einem ersten Leitfähigkeitstyp;

- eine zweite Halbleiterschicht (101) vom ersten Leitfähigkeitstyp, welche auf der genannten ersten Halbleiterschicht ausgebildet ist, wobei die genannte zweite Halbleiterschicht eine kleinere Störstellenkonzentration des ersten Leitfähigkeitstyps aufweist als die genannte erste Halbleiterschicht;

- ein Halbleitergebiet (102,108) von einem zweiten Leitfähigkeitstyp, welches auf mindestens einem Teil der genannten zweiten Halbleiterschicht ausgebildet ist;

- eine erste Hauptelektrode (104, 109), welche über dem genannten Halbleitergebiet ausgebildet ist;

- und eine zweite Hauptelektrode (105), welche unter der genannten ersten Halbleiterschicht ausgebildet ist; worin die Schichtdicke der genannten zweiten Halbleiterschicht so festgelegt ist, dass sie sowohl eine erste Bedingung, wonach eine Sperrsicht, welche sich von einem pn-Übergang an der Grenzfläche zwischen der genannten zweiten Halbleiterschicht und dem genannten Halbleitergebiet aus ausbreitet, nicht die genannte erste Halbleiterschicht erreicht, wenn eine Rückwärtsspannung von 1/2 bis 2/3 der Sperrspannungsfestigkeit des genannten pn-Überganges an die genannte erste und die genannte zweite Hauptelektrode angelegt ist, als auch eine zweite Bedingung erfüllt, wonach die Sperrsicht, welche sich vom genannten pn-Übergang aus ausbreitet, die genannte erste Halbleiterschicht erreicht, wenn eine Rückwärtsspannung, welche ungefähr 2/3 der genannten Sperrspannungsfestigkeit übersteigt, an die genannte erste und die genannte zweite Hauptelektrode angelegt ist.

2. Halbleiterbauelement gemäss Anspruch 1, worin die genannte erste Hauptelektrode eine Hauptelektrode miteinschliesst, welche direkt auf dem genannten Halbleitergebiet ausgebildet ist, und die genannte zweite Hauptelektrode eine Hauptelektrode umfasst, welche direkt auf der Unterseite der genannten ersten Halbleiterschicht ausgebildet ist.

3. Halbleiterbauelement gemäss Anspruch 1, weiter umfassend:

- eine dritte Halbleiterschicht (106) vom zweiten Leitfähigkeitstyp, welche unter der genannten ersten Halbleiterschicht ausgebildet ist, worin

- die genannte erste Hauptelektrode eine Hauptelektrode miteinschliesst, welche direkt auf dem genannten Halbleitergebiet ausgebildet ist, und

- die genannte zweite Hauptelektrode eine Hauptelektrode miteinschliesst, welche direkt auf der Unterseite der genannten dritten Halbleiterschicht ausgebildet ist.

4. Halbleiterbauelement gemäss Anspruch 1, weiter umfassend:

- eine dritte Halbleiterschicht (106) vom zweiten Leitfähigkeitstyp, welche unter der genannten ersten Halbleiterschicht ausgebildet ist; und

- eine vierte Halbleiterschicht (107) vom ersten Leitfähigkeitstyp, welche auf dem genannten Halbleitergebiet ausgebildet ist, worin

- die genannte erste Hauptelektrode eine Hauptelektrode miteinschliesst, welche direkt auf der genannten vierten Halbleiterschicht ausgebildet ist, und

- die genannte zweite Hauptelektrode eine Hauptelektrode miteinschliesst, welche direkt auf der Unterseite der genannten dritten Halbleiterschicht ausgebildet ist.

5. Halbleiterbauelement gemäss Anspruch 2, worin

- das genannte Halbleitergebiet mehrere Halbleitereilgebiete (108) umfasst, welche selektiv in der Oberfläche der genannten zweiten Halbleiterschicht ausgebildet sind, und

- die genannte erste Hauptelektrode mehrere Teilelektronen (109) umfasst, welche auf den einzelnen genannten Halbleitereilgebieten (108) ausgebildet sind.

**CH 695 808 A5**

6. Halbleiterbauelement gemäss Anspruch 2, worin die Lebensdauer in der Nähe der Grenzschicht zwischen der genannten zweiten Halbleiterschicht und dem genannten Halbleitergebiet kürzer festgelegt ist, als die Lebensdauer in der Nähe der Grenzschicht zwischen der genannten ersten und der genannten zweiten Halbleiterschicht.

7. Halbleiterbauelement gemäss einem der Ansprüche 1 bis 6, worin die genannte zweite Bedingung eine Bedingung miteinschliesst, wonach die Sperrsicht, welche sich vom genannten pn-Übergang aus ausbreitet, die genannte erste Halbleiterschicht erreicht, wenn eine Rückwärtsspannung, welche gleich der genannten Sperrspannungsfestigkeit ist, an die genannte erste und die genannte zweite Hauptelektrode angelegt ist.

8. Halbleiterbauelement gemäss einem der Ansprüche 1 bis 6, worin die genannte Störstellenkonzentration der genannten zweiten Halbleiterschicht so festgelegt ist, dass sie eine dritte Bedingung erfüllt, wonach das elektrische Feld, welches auf die Sperrsicht wirkt, wenn die Rückwärtsspannung gleich der genannten Sperrspannungsfestigkeit festgelegt ist, einen tatsächlichen Einsatzwert aufweist, welcher nicht grösser ist als eine vorgegebene Feldstärke.

9. Halbleiterbauelement gemäss Anspruch 1, worin der genannte erste Leitfähigkeitstyp den n-leitenden Typ miteinschliesst, und der genannte zweite Leitfähigkeitstyp den p-leitenden Typ miteinschliesst.

*FIG. 1*

*FIG. 2*

*FIG. 3*

*FIG. 4*

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13