(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2018-524859

(P2018-524859A)

(43) 公表日 平成30年8月30日(2018.8.30)

(51) Int.Cl.

H04L 29/06 (2006.01)

H04L 7/04 (2006.01)

F 1

H04L 13/00

H04L 7/04

テーマコード(参考)

5K034

5K047

審査請求 未請求 予備審査請求 未請求 (全 23 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2017-561908 (P2017-561908) |

| (86) (22) 出願日 | 平成28年6月20日 (2016. 6. 20)     |

| (85) 翻訳文提出日   | 平成30年1月16日 (2018. 1. 16)     |

| (86) 國際出願番号   | PCT/US2016/038312            |

| (87) 國際公開番号   | W02016/205776                |

| (87) 國際公開日    | 平成28年12月22日 (2016. 12. 22)   |

| (31) 優先権主張番号  | 62/181,533                   |

| (32) 優先日      | 平成27年6月18日 (2015. 6. 18)     |

| (33) 優先権主張国   | 米国(US)                       |

| (31) 優先権主張番号  | 15/185,257                   |

| (32) 優先日      | 平成28年6月17日 (2016. 6. 17)     |

| (33) 優先権主張国   | 米国(US)                       |

|          |                                                                                                                                          |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| (71) 出願人 | 397050741<br>マイクロチップ テクノロジー インコーポレイテッド<br>MICROCHIP TECHNOLOGY INCORPORATED<br>アメリカ合衆国 85224-6199<br>アリゾナ チャンドラー ウエスト チャンドラー ブルヴァード 2355 |

| (74) 代理人 | 100078282<br>弁理士 山本 秀策                                                                                                                   |

| (74) 代理人 | 100113413<br>弁理士 森下 夏樹                                                                                                                   |

最終頁に続く

(54) 【発明の名称】自動プロトコルを用いたU A R T

## (57) 【要約】

ユニバーサル非同期受信機 / 伝送機 (U A R T ) インターフェースが開示される。U A R T インターフェースは、構成可能な非同期受信機および伝送機ユニットと、構成可能な状態マシンとを含み得、状態マシンは、受信機および伝送機ユニットの構成が種々のボーレートをサポートし、スタートビットおよびストップビット構成を提供することを可能にし、状態マシンはさらに、複数の通信プロトコルを自動的にサポートするように構成可能である。

**【特許請求の範囲】****【請求項 1】**

ユニバーサル非同期受信機／伝送機（U A R T）インターフェースであって、前記U A R Tインターフェースは、

構成可能な非同期受信機および伝送機ユニットと、

構成可能な状態マシンと

を備え、

前記状態マシンは、前記受信機および伝送機ユニットの構成が種々のボーレートをサポートし、スタートビットおよびストップビット構成を提供することを可能にし、前記状態マシンはさらに、複数の通信プロトコルを自動的にサポートするように構成可能である、

U A R Tインターフェース。 10

**【請求項 2】**

前記複数の通信プロトコルは、D M X プロトコルを備える、請求項 1 に記載のU A R Tインターフェース。

**【請求項 3】**

前記複数の通信プロトコルは、D A L I プロトコルを備える、請求項 1 に記載のU A R Tインターフェース。

**【請求項 4】**

前記複数の通信プロトコルは、L I N プロトコルを備える、請求項 1 に記載のU A R Tインターフェース。 20

**【請求項 5】**

動作モードは、構成レジスタを通して設定される、前記請求項のうちの 1 項に記載のU A R Tインターフェース。

**【請求項 6】**

前記状態マシンは、第 2 のモードでブレイク、M A B、フレーム幅、M T B F、およびM T B P のための自動サポートを提供する、前記請求項のうちの 1 項に記載のU A R Tインターフェース。 30

**【請求項 7】**

前記請求項のうちの 1 項に記載のU A R Tインターフェースを備える、マイクロコントローラ。

**【請求項 8】**

前記マイクロコントローラは、8 ビットマイクロコントローラ、16 ビットマイクロコントローラ、および32 ビットマイクロコントローラから成る群から選択される、請求項 7 に記載のマイクロコントローラ。 40

**【請求項 9】**

前記U A R Tインターフェースに結合されたタイマをさらに備える、請求項 7 に記載のマイクロコントローラ。

**【請求項 10】**

前記動作モードは、マンチェスターモードを備える、前記請求項のうちの 1 項に記載のU A R Tインターフェース。

**【請求項 11】**

ユニバーサル非同期受信機／伝送機（U A R T）インターフェースであって、前記U A R Tインターフェースは、構成可能な非同期受信機および伝送機ユニットと、構成可能な状態マシンとを備え、前記状態マシンは、前記受信機および伝送機ユニットの構成が種々のボーレートをサポートし、スタートビットおよびストップビット構成を提供することを可能にし、前記状態マシンはさらに、複数の通信プロトコルを自動的にサポートするように構成可能である、U A R Tインターフェースと、

前記U A R Tインターフェースを備えるマイクロコントローラと、

前記U A R Tインターフェースを介してデータを受信および伝送するように動作可能である、前記マイクロコントローラに結合された複数のコンポーネントと 50

を備える、マイクロコントローラシステム。

【請求項 1 2】

前記複数の通信プロトコルは、D M X プロトコルを備える、請求項 1 1 に記載のマイクロコントローラシステム。

【請求項 1 3】

前記複数の通信プロトコルは、D A L I プロトコルを備える、請求項 1 1 に記載のマイクロコントローラシステム。

【請求項 1 4】

前記複数の通信プロトコルは、L I N プロトコルを備える、請求項 1 1 に記載のマイクロコントローラシステム。

【請求項 1 5】

動作モードは、構成レジスタを通して設定される、請求項 1 1 - 1 4 のうちの 1 項に記載のマイクロコントローラシステム。

【請求項 1 6】

前記状態マシンは、第 2 のモードでブレイク、M A B 、フレーム幅、M T B F 、およびM T B P のための自動サポートを提供する、請求項 1 1 - 1 5 のうちの 1 項に記載のマイクロコントローラシステム。

【請求項 1 7】

前記マイクロコントローラは、8 ビットマイクロコントローラである、請求項 1 1 - 1 6 のうちの 1 項に記載のマイクロコントローラシステム。

【請求項 1 8】

前記U A R T インターフェースに結合されたタイマをさらに備える、請求項 1 1 - 1 7 のうちの 1 項に記載のマイクロコントローラシステム。

【請求項 1 9】

動作モードは、マンチェスタモードを備える、請求項 1 1 - 1 8 のうちの 1 項に記載のマイクロコントローラシステム。

【請求項 2 0】

前記複数のコンポーネントは、複数の視聴覚コンポーネントを備える、請求項 1 1 - 1 9 のうちの 1 項に記載のマイクロコントローラシステム。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

(関連出願への相互参照)

本出願は、同一出願人の、2 0 1 5 年 6 月 1 8 日に出願された米国仮特許出願第 6 2 / 1 8 1 , 5 3 3 号に対して優先権を主張する。上記文献は、全体としてここで参照することによって本明細書において援用される。

【0 0 0 2】

(技術分野)

本開示は、シリアルインターフェース、具体的には、自動プロトコルを用いたユニバーサル非同期受信機 / 伝送機(「U A R T 」)インターフェースに関する。

【背景技術】

【0 0 0 3】

(背景)

U A R T は、周知であり、通信チャネルを提供するためにマイクロコントローラで一般的に使用されている。U A R T インターフェースは、パラレルデータをシリアル伝送形態に変換する。種々のタイプのプロトコルが存在し、E l e c t r o n i c I n d u s t r i e s A l l i a n c e 規格R S - 2 3 2 、R S - 4 2 2 、またはR S - 4 8 5 等の種々の通信規格によって定義されるようにU A R T 通信で使用される。

【発明の概要】

【発明が解決しようとする課題】

10

20

30

40

50

## 【0004】

(要約)

複数の自動プロトコルをサポートするように動作可能なユニバーサル非同期受信機／伝送機インターフェースを提供する必要性が存在する。

## 【課題を解決するための手段】

## 【0005】

ユニバーサル非同期受信機／伝送機（U A R T）インターフェースが開示される。U A R Tインターフェースは、構成可能な非同期受信機および伝送機ユニットと、構成可能な状態マシンとを含み得、状態マシンは、受信機および伝送機ユニットの構成が種々のボーレートをサポートし、スタートビットおよびストップビット構成を提供することを可能にし、状態マシンはさらに、複数の通信プロトコルを自動的にサポートするように構成可能である。

## 【0006】

いくつかの実施形態では、複数の通信プロトコルは、D M X プロトコルを含んでもよい。同一または代替実施形態では、複数の通信プロトコルは、D A L I プロトコルを含んでもよい。同一または代替実施形態では、複数の通信プロトコルは、L I N プロトコルを含んでもよい。

## 【0007】

いくつかの実施形態では、動作モードが、構成レジスタを通して設定される。いくつかの実施形態では、状態マシンは、ブレイク、M A B、フレーム幅、M T B F、およびM T B P のための自動サポートを提供する。

## 【0008】

いくつかの実施形態では、マイクロコントローラシステムも開示される。マイクロコントローラシステムはまた、U A R T を含むマイクロコントローラを含んでもよい。そのような実施形態では、マイクロコントローラは、8ビットマイクロコントローラ、16ビットマイクロコントローラ、および32ビットマイクロコントローラから成る群から選択されてもよい。そのような実施形態では、マイクロコントローラはさらに、U A R Tインターフェースに結合されるタイマを含んでもよい。

## 【0009】

いくつかの実施形態では、動作モードは、マンチェスタモードを含んでもよい。

## 【図面の簡単な説明】

## 【0010】

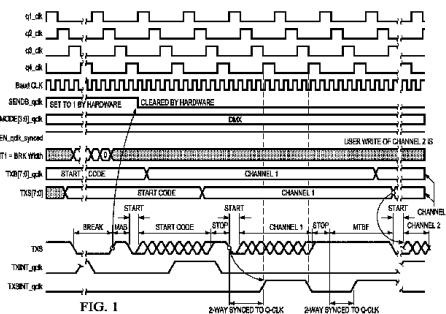

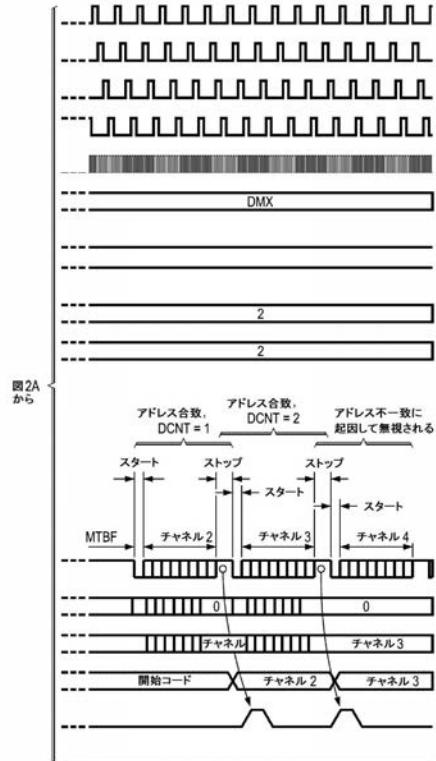

【図1】図1は、本開示のある実施形態による、第1から第512のバイトの例示的伝送を図示する。

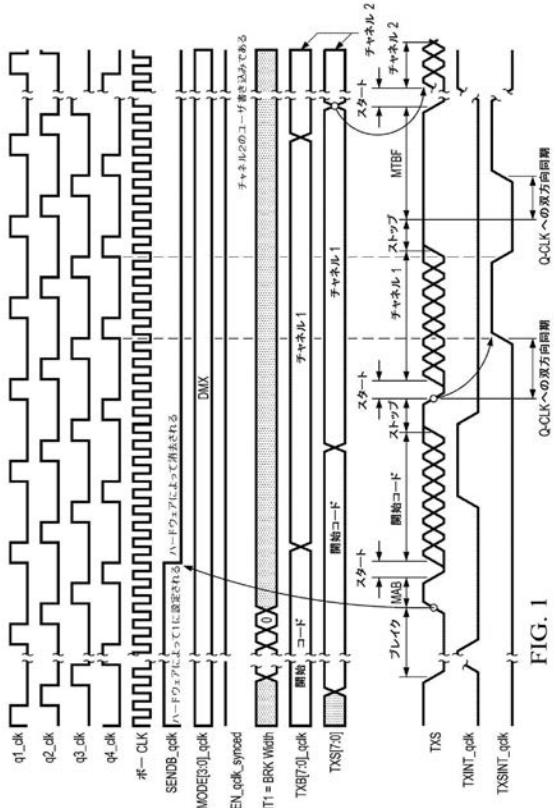

【図2】図2は、本開示のある実施形態による、例示的な対応するD M X 受信プロトコルを図示する。

【図2A】図2は、本開示のある実施形態による、例示的な対応するD M X 受信プロトコルを図示する。

【図2B】図2は、本開示のある実施形態による、例示的な対応するD M X 受信プロトコルを図示する。

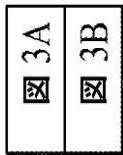

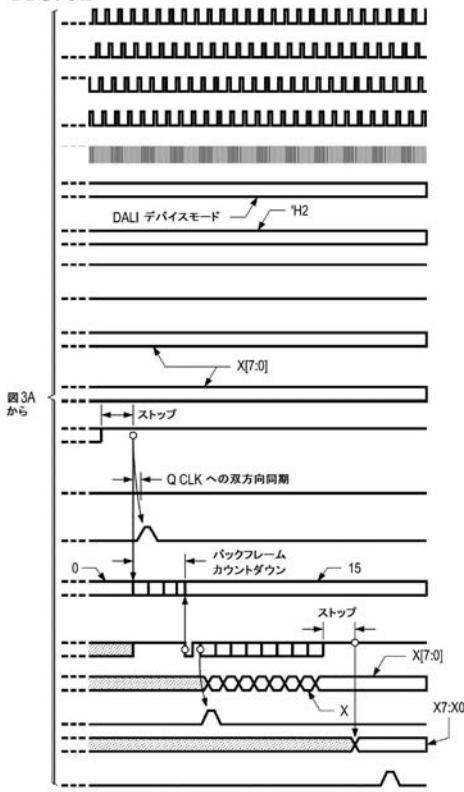

【図3】図3は、本開示のある実施形態による、特定のデータサイズ（例えば、レジスタP 1 = 2（バイト））に設定されたメモリ部分を伴う例示的16ビットD A L I デバイスを図示する。

【図3A】図3は、本開示のある実施形態による、特定のデータサイズ（例えば、レジスタP 1 = 2（バイト））に設定されたメモリ部分を伴う例示的16ビットD A L I デバイスを図示する。

【図3B】図3は、本開示のある実施形態による、特定のデータサイズ（例えば、レジスタP 1 = 2（バイト））に設定されたメモリ部分を伴う例示的16ビットD A L I デバイスを図示する。

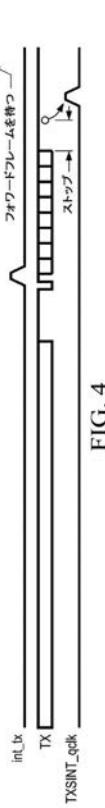

【図4】図4は、本開示のある実施形態による、D A L I 伝送のための例示的タイミング

10

20

30

40

50

図を図示する。

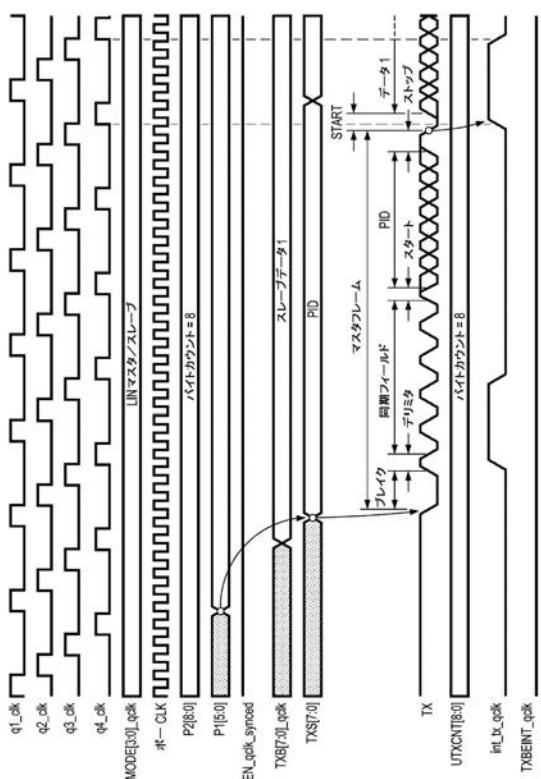

【図 5】図 5 は、本開示のある実施形態による、L I N マスター / スレーブモードの例示的タイミング図を図示する。

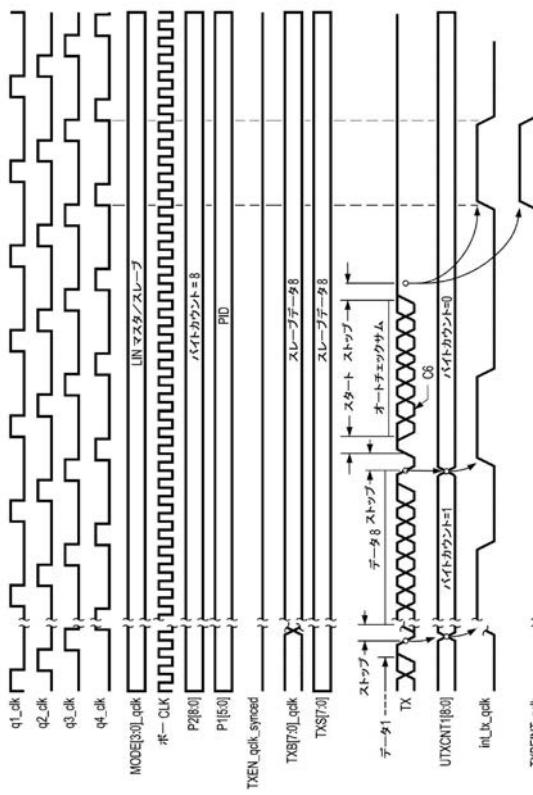

【図 6】図 6 は、本開示のある実施形態による、L I N マスター / スレーブモードの継続的な例示的タイミング図を図示する。

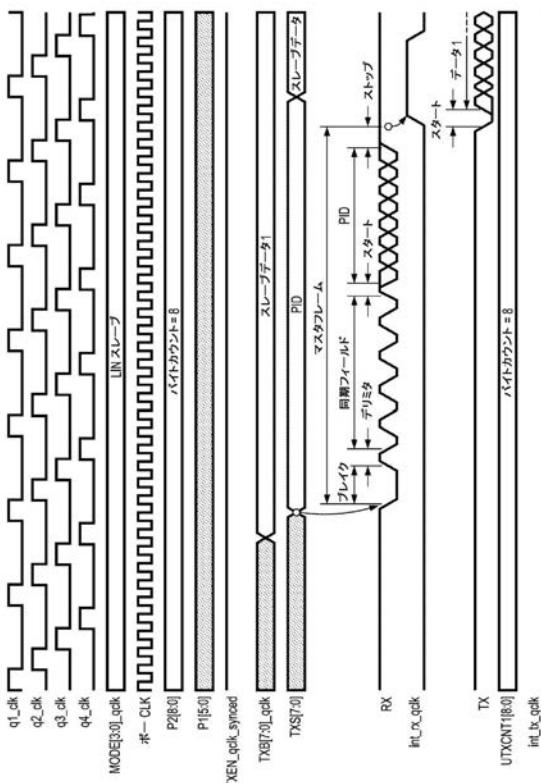

【図 7】図 7 は、本開示のある実施形態による、L I N スレーブ専用モードの例示的タイミング図を図示する。

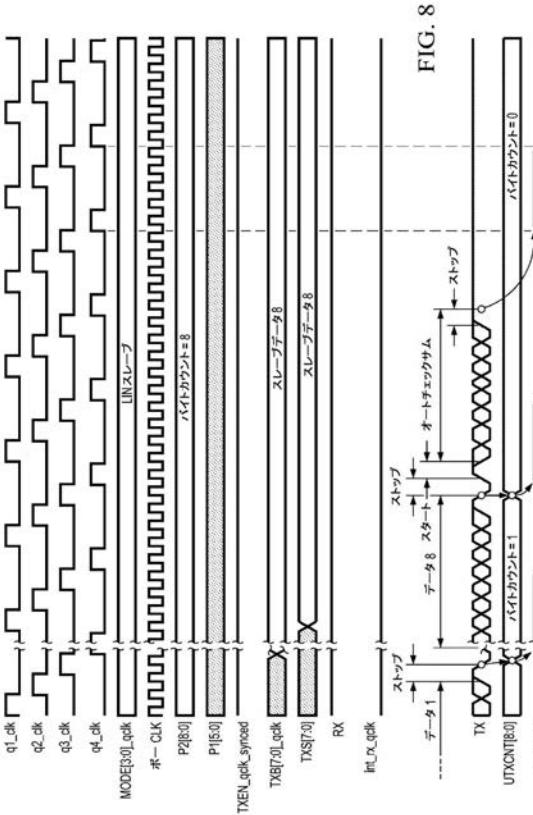

【図 8】図 8 は、本開示のある実施形態による、L I N スレーブ専用モードの継続的な例示的タイミング図を図示する。

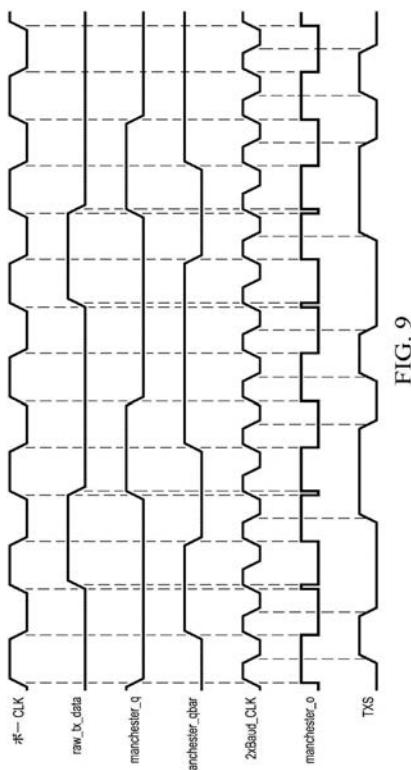

【図 9】図 9 は、本開示のある実施形態による、伝送のための例示的マンチェスタ復号方式を図示する。

10

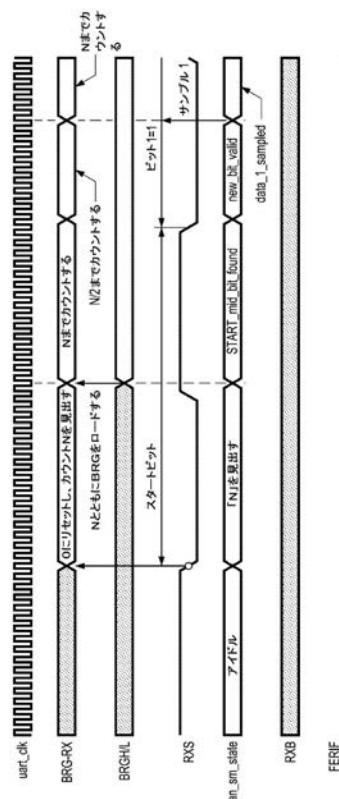

【図 10】図 10 は、本開示のある実施形態による、受信のための例示的マンチェスタ復号方式を図示する。

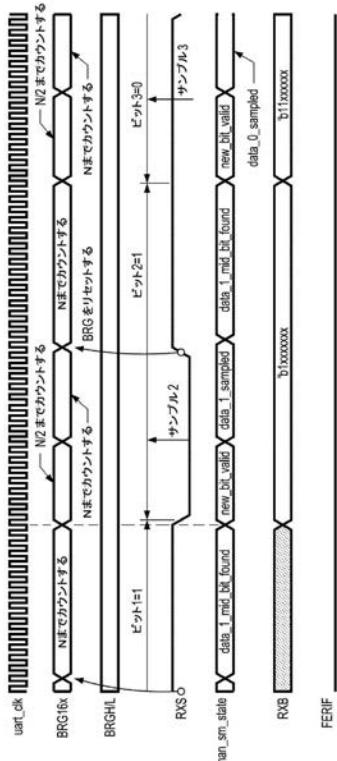

【図 11】図 11 は、本開示のある実施形態による、受信のための継続的な例示的マンチェスタ復号方式を図示する。

【図 12】図 12 は、本開示のある実施形態による、受信のためのさらに継続的な例示的マンチェスタ復号方式を図示する。

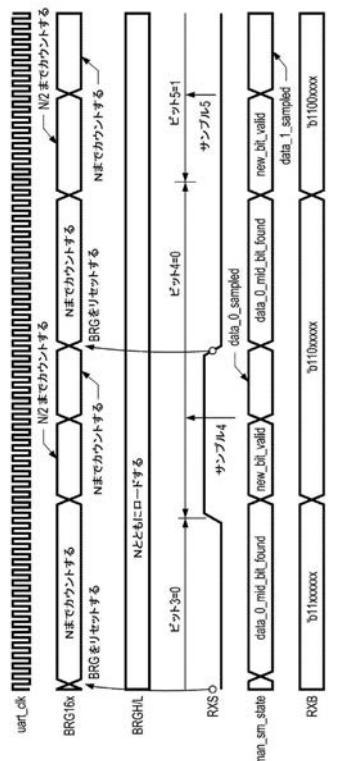

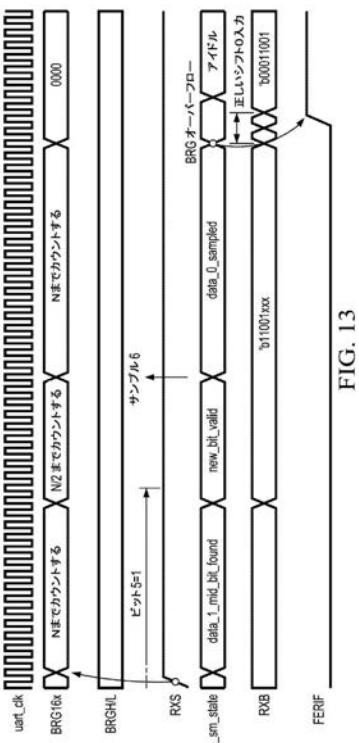

【図 13】図 13 は、本開示のある実施形態による、受信のためのなおもさらなる例示的マンチェスタ復号方式を図示する。

【発明を実施するための形態】

20

【0011】

(詳細な説明)

種々の実施形態によると、データ相互作用のみを使用して、デジタル多重化(「D M X」)、ローカル相互接続ネットワーク(「L I N」)、デジタルアドレス指定可能照明インターフェース(「D A L I」)等のマルチステッププロトコルが実装されることを可能にする、ユニバーサル非同期受信機 / 伝送機(「U A R T」)が、提供されることができる。ソフトウェアが、ブレイク(「B R K」)文字、S T A R T ビット、S T O P ビット、チェックサム等を配置する場所について気にする必要はない。これらの要素の全ての物理層配置は、自動的に対処され得る。ソフトウェアは、リンクを経由してデータを読み取ることおよび書き込むことのみに責任があり得る。

30

【0012】

各プロトコルでは、ユーザは、伝送または受信されるデータを書き込み、かつ読み取ってもよい。本開示の目的のために、「ユーザ」は、任意の適切な電子デバイスおよび / または該デバイスのオペレータを指し得る。次いで、U A R T は、S T A R T 、S T O P 、I D L E 周期、チェックサム計算、データ挿入、パリティビット等を自動的に挿入してもよい。したがって、少なくとも以下のプロトコル、すなわち、自動D M X プロトコル、自動D A L I プロトコル、自動L I N プロトコルが、実装されることができる。

【0013】

ある従来のU A R T は、ビットの比較的低レベルの制御のみを提供し得る。より高レベルの問題(例えば、S T A R T およびS T O P ビット、チェックサム等を配置する場所)は、殆どのマイクロコントローラが利用可能な多数のソフトウェアサイクルを有するため、ソフトウェアで対処される。しかしながら、8ビットマイクロコントローラ等のより小さいソリューションでは、全利用可能ソフトウェアサイクルがより少数であるため、ハードウェアロックが、ソフトウェアから負担を取り除くために活用され得る。

40

【0014】

種々の実施形態によると、一般的なプロトコルソフトウェアセットが提供されてもよい。例えば、ユーザが複数の利用可能なプロトコルモードのうちの1つを選択することを可能にする、複数のビットが提供されてもよい。これは、例えば、U A R T 構成レジスタにおいて制御ビット、例えば、U S E \_ P R O T = 1 を設定することによって、達成されてもよい。さらに、要求されたクロックレートが選択されたクロックから分割されることが

50

できるように、ボーレート値（例えば、ボーレートジェネレータビット「B R G H / L」）が、設定されることができる。これらのクロックレートは、一例のみとして提供される。ハードウェアは、クロックレートにいかなる制限も施行しない場合がある。クロックレートは、異なるプロトコルのために提供されてもよく、例えば、D M Xは、5 ~ 2 5 0 K H zのクロックレートを使用し、D A L Iは、2 1 8 0 ~ 2 6 6 6 H zのクロックレート（ピンにおけるマンチェスター1 0 9 0 ~ 1 3 3 3 ボーに変換する）を使用し、L I Nは、1 0 0 H z ~ 2 0 K H zのクロックレートを使用してもよい。

#### 【0 0 1 5】

いくつかの実施形態では、ウォーターマーク値が、要求されたウォーターマークに設定されてもよい。例えば、伝送先入れ先出し（「FIFO」）が3に達するときに、割込が所望される場合、特定の構成が、T I N T F L G [ 2 : 0 ]を3に設定してもよい。他の構成値もまた、本開示の範囲から逸脱することなく使用されてもよい。例えば、適切な信号ピン上の論理レベルが、プロトコルに応じて、所望の値に設定されることができ、伝送極性ビットが、設定されてもよい、モデル選択信号が、所望のモードに設定されてもよい、伝送イネーブル信号が、設定されてもよい、受信イネーブル信号が、設定されてもよい等である。

10

#### 【0 0 1 6】

B R Kを有するプロトコル（例えば、D M XおよびL I N）を組み込む、いくつかの実施形態では、B R Kがパケットの途中で受信される（予期しない早期B R K）場合、状態マシンは、新しいパケットが開始した場合のように挙動するであろう。受信バッファのコンテンツは、フラッシュされないであろう。ユーザは、これらを読み出さなければならぬ、または（例えば、R X F L S Hビットをアクティブ化することによって）意図的にバッファコンテンツをフラッシュしなければならない。

20

#### 【0 0 1 7】

いくつかの実施形態では、チェックサム値、パリティ内部加算器（およびその稼働レジスタのうちのいずれか）が、全てのプロトコルモードの開始時に消去される。しかしながら、チェックサムおよびパリティステータスピットは、消去されない。これらは、いくつかの実施形態によると、ユーザによって消去されてもよい。

#### 【0 0 1 8】

30

##### D M Xプロトコル状態マシン

種々の実施形態では、自動プロトコルを用いたU A R Tは、D M Xプロトコルを利用してよい。そのような実施形態では、特定のプロトコルは、ユーザが複数の利用可能なプロトコルモードのうちの1つを選択することを可能にする複数のビットによって、選定されてもよい。例えば、特定の構成が、「U S E \_ P R O T」信号を論理高に設定することによって、D M Xプロトコルを選択してもよい。D M Xは、舞台および演劇機器で使用されるプロトコルである。これは、照明、煙霧機等を含む。プロトコルは、コマンドを送出する制御コンソール、およびこれらのコマンドを受信する劇場照明等の機器から成る。プロトコルは、コマンドを伝送するコンソールおよびそれらを受信する機器を伴って一方向性である。機器は、決して何も传送せず、コンソールは、決して何も受信しない。また、D M X構成は、エラー制御または再传送機構を含まない。

40

#### 【0 0 1 9】

D M XまたはD M X - 5 1 2は、公知であり得るように、5 1 2個のチャネルの「領域」から成る。これは、1つのコンソールが单一のD M Xリンク上で最大5 1 2バイトを出力できることを意味する。ライン上の各機器は、これらのバイトのうちの1つ以上をリップスンするようにプログラムされる。例えば、領域のうちの1つに接続される煙霧機は、バイト数1 0から始まって受信し、4バイトカウントを受信するようにプログラムされてもよく、照明ユニットは、バイト数2 2にプログラムされ、1バイトカウントを受信してもよい。

#### 【0 0 2 0】

各D M X传送は、「開始コード」と呼ばれるバイトが後に続く、B R E A Kで始まって

50

もよい。B R E A Kの幅は、特定のレジスタ、例えば、P 1レジスタを用いて設定される。ブレイクの後には、「M a k e A f t e r B r e a k ( M A B )」が続く。図1は、本開示のある実施形態による、第1から第512のバイトの例示的伝送を図示する。伝送される各バイトは、特定の信号（例えば、U S E \_ F I F O）が特定の論理レベル（例えば、0）に設定されるときに、割込イベントを生じるであろう。割込頻度は、その信号が改変されるときに改変してもよい。例えば、信号が反対論理レベル（例えば、1）に設定されるとき、割込頻度は、ウォーターマーク設定に依存し得る。

#### 【0021】

いくつかの実施形態では、U A R Tが受信機として構成されるとき、U A R Tは、所定の長さ（例えば、幅が少なくとも11個のクロック）であるB R E A K文字をリッシュしてもよい。B R E A Kの直後に、U A R Tは、M A Bを確認するであろう。本空間は、U A R Tによって無視されてもよい。次いで、U A R Tは、開始コードを確認するであろう。開始コードは、常に、U A R Tの特定のメモリ部分（例えば、受信バッファ）の中へ時間記録されるであろう。開始コードは、常に、F I F O占有率にかかわらず、割込イベントを生じるであろう。割込頻度信号が特定の論理レベルに設定される（例えば、U S E \_ F I F O = 1）場合、受信割込は、ウォーターマーク設定に従ってフラグを付けられるであろう。

10

#### 【0022】

開始コード後に、U A R Tは、第1から第512のバイトを受信するであろう。受信されたバイトに512回の割込を有するのではなく、U A R Tは、着目されるものが受信されるまで、受信されたバイトを無視することができる。これは、U A R Tの他のメモリ部分（例えば、P 2およびP 3レジスタ）を使用して行われる。1つのメモリ部分（例えば、P 2レジスタ）は、受信プロセスを開始するバイト数の値を保持してもよい。上記に列挙される煙霧機の場合、例えば、ユーザは、P 2レジスタを10にプログラムしてもよい。以前に議論された照明器具は、数22にプログラムされてもよい。別のメモリ部分（例えば、レジスタP 3）は、受信するバイト数の値を保持してもよい。煙霧機の場合、他のメモリ部分（例えば、P 3）は、U A R Tが合計4つのバイトである、バイト10、11、12、および13を受信するように、値4を保持するであろう。図2は、本開示のある実施形態による、例示的な対応するD M X受信プロトコルを図示する。

20

#### 【0023】

30

##### 伝送ソフトウェアモデル

種々の実施形態では、自動D M Xプロトコルを用いたU A R Tはまた、伝送ソフトウェアモデルを含んでもよい。伝送ソフトウェアモデルは、特定の信号をアサートすることによって設定されてもよい。例えば、ピン信号（例えば、P 1 H / L）が、伝送されたB R E A Kの所望の持続時間に設定されてもよい。典型的値は、13である。

#### 【0024】

40

いくつかの実施形態では、次いで、モデルは、開始コードを通信バス（例えば、T X B [ 7 : 0 ]）に書き込んでもよい。これは、最初のワードがF I F Oに書き込まれるときに、U A R TにB R E A Kを伝送させてもよい。B R E A Kは、（例えば、「P 1 H / L」上で設定されるクロックカウントの数によって）所望の持続時間にわたって持続してもよい。次いで、U A R Tは、残りのチャネルを通信バス（例えば、T X B [ 7 : 0 ]）に書き込んでもよい。開始コード後に、次のチャネルが、バスF I F Oから伝送される。伝送割込信号（例えば、i n t \_ t x）が、ウォーターマークに達する（例えば、U S E \_ F I F O = 1）度に、またはバスが満杯である（U S E \_ F I F O = 0）ときに、設定されてもよい。

#### 【0025】

50

残りのチャネルのうちのいずれかが書き込まれていない場合、伝送出力は、高くなり、より多くのバスコンテンツが利用可能になるまで、高いままであってもよい。これは、バス上のさらなる空間が利用可能にされるまで、トグリングしないことから伝送タイマリセット信号（例えば、u a r t \_ t i m e r \_ r e s e t \_ t x）をもたらし得る。タイマ

2等の外部タイマは、本トグル間の時間をカウントし、D M X接続がタイムアウトしたかどうかを判定してもよい。タイムアウトした場合、ソフトウェアは、伝送状態マシンを再始動させるために、(例えば、T X E N = 0、次いで、T X E N = 1を設定することによって)伝送イネーブル信号を交互に入れ替えてよい。これはまた、バスをフラッシュするであろう。いくつかの実施形態では、U A R Tは、M A Bおよび2-S T O Pビットを自動的にハンドリングしてもよい。

#### 【0026】

##### 受信ソフトウェアモデル

種々の実施形態では、自動D M Xプロトコルを用いたU A R Tはまた、受信ソフトウェアモデルを含んでもよい。受信ソフトウェアモデルは、特定の信号をアサートすることによって設定されてもよい。例えば、第1のピン信号(例えば、P 2 H / L)は、データを受信し始める所望のバイトカウントに設定されてもよい。加えて、第2のピン信号(例えば、P 3 H / L)は、第1のピン信号から始まって、受信するバイトの所望のカウントに設定されてもよい。いくつかの実施形態では、U A R Tは、B R E A Kがライン上に出現することを待ってもよい。それが出現するとき、サンプリングクロックが同期化されてもよい。

10

#### 【0027】

いくつかの実施形態では、受信される第1のバイトは、S T A R Tコードであり、常にF I F Oにロードされる。受信ウォーターマーク割込信号(例えば、i n t \_ r x)は、常に、ウォーターマーク/F I F O設定にかかわらず、S T A R Tコードが受信されるときにフラグを付けられる。開始コード後のバイトから始まって、第1のピン信号によって規定されるバイトカウント(アドレス)が、合致される。いったん合致されると、第2のピン信号上の値は、F I F Oにロードされてもよい。受信ウォーターマーク割込信号(例えば、i n t \_ r x)は、ウォーターマークに達する度に割込に設定されてもよい。受信ラインが所定の時間(例えば、1秒)を上回ってアイドル状態である場合、D M Xリンクは、無効と見なされてもよい。U A R Tが所定の時間をカウントするために十分に大きいタイマを有していない場合に、本所定の時間を計測するために、外部タイマが使用されてもよい。

20

#### 【0028】

##### D A L Iプロトコル状態マシン

30

種々の実施形態では、自動プロトコルを用いたU A R Tは、D A L Iプロトコルを利用してよい。そのような実施形態では、特定のプロトコルは、ユーザが複数の利用可能なプロトコルモードのうちの1つを選択することを可能にする複数のビットによって、選定されてもよい。例えば、特定の構成が、「U S E \_ P R O T」信号を論理高に設定することによって、D A L Iプロトコルを選択してもよい。D A L Iは、オフィスおよび工場等の大きな建物の中の照明を制御するために使用されるプロトコルである。これは、2つのモード、すなわち、「デバイス」および「ギヤ」から成る。「デバイス」は、コマンドを照明器具に送出するメインコントローラである。照明器具自体が、「ギヤ」として公知である。全ビット传送は、ハードウェアによって行われる、マンチェスタ符号化で行われてもよい。D A L Iワイヤは、半二重であり、传送および受信ラインは、A C変圧器を通してともに電気的に結び付けられる。

40

#### 【0029】

全ての他のプロトコルと異なり、D A L Iは、最初に最上位ビット(「M S b」)を传送される。U A R Tトランザクションは、「デバイス」が传送を開始するときに始まってもよい。デバイス传送は、D A L I 1 . 0では2つのバイト、D A L I 2 . 0では3つのバイトから成る。最初の1つは、「Y A A A A A A S」によって指定される制御バイトであり、その後に1つまたは2つのデータバイトが続く。デバイスから出てくるこれらのバイトは、「フォワードフレーム」と呼ばれる。図3は、本開示のある実施形態による、特定のデータサイズ(例えば、レジスタP 1 = 2(バイト))に設定されたメモリ部分を伴う例示的16ビットD A L Iデバイスを図示する。传送される各バイトは、U S E \_ F I

50

$\text{FO} = 0$  であるときに、割込イベントを生じるであろう。 $\text{USE\_ FIFO} = 1$  であるとき、割込頻度は、ウォーターマーク設定に依存し得る。いくつかの構成では、 $\text{USE\_ FIFO} = 0$  を設定したデバイスで、1つだけの伝送バス（例えば、「TXB」）および1つのシフタが利用可能であり得るため、3つのワードを立て続けに書き込むことが可能ではない場合がある。したがって、3つのバイトが伝送されなければならない、DALI 2.0 デバイス用のコードを書き込むとき、ソフトウェアは、割込信号（例えば、`int_tx` または `TXBE / TXBF`）および割込衝突信号（例えば、`TXMTIF`）を監視しなければならない。伝送バスが利用可能になるとすぐに、シフタが空になる前に、第3のバイトがバスに書き込まれなければならない。これは、3つのバイトが途切れることなく立て続けに伝送されることを確実にするであろう。

10

#### 【0030】

ライン上の全てのギヤが、本フォワードフレームを受信してもよい。ギヤのうちの1つは、返信として、「バックフレーム」と呼ばれる単一のバイトでこれに応答してもよい。DALIプロトコルは、本バックフレームが11ポークロックサイクル内で受信され始めなければならないことを要求する。バックフレームの開始が受信される場合、デバイスは、バックフレームの終了後にさらに11のクロックサイクルを待つことを要求される。本時間後に、デバイスは、別のフォワードフレームを自由に伝送する。図4は、本開示のある実施形態による、DALI伝送のための例示的タイミング図を図示する。受信される各バイトは、 $\text{USE\_ FIFO} = 0$  であるときに、割込イベントを生じるであろう。 $\text{USE\_ FIFO} = 1$  である場合、受信割込は、ウォーターマーク設定に従ってフラグを付けられるであろう。

20

#### 【0031】

DALIモードであるとき、UARTは、現在のバイトが有効受信と見なされる前に、両方のSTOPビットが正しく受信されることを確認しなければならない。いずれかのSTOPビットが正しく受信されない場合、受信バイトは、シフタから RXB に転送する前に破棄される。UARTハードウェアは、STOPビットの要求された数を検出し、その数が検出されない場合に、エラーでユーザに応答するであろう。

20

#### 【0032】

##### DALIデバイスソフトウェアモデル

種々の実施形態では、自動DALIプロトコルを用いたUARTは、デバイスソフトウェアモデルを含んでもよい。デバイスソフトウェアモデルは、特定の信号をアサートすることによって設定されてもよい。例えば、ピン信号（例えば、P1H/L）は、フォワードフレームの間のクロックサイクルの所望の数に設定されてもよい。典型的には、本値は、11またはそれを上回るであろう。次いで、UARTは、YAAAAAASの直後に、（例えば、X[7:0]上で）データを伝送してもよい。したがって、伝送が始まることができる前に、両方のバイトが利用可能でなければならない。次いで、UARTは、「YAAAAAAS」ヘッダの値を伝送バス（例えば、TXB[7:0]）の一部に書き込んでもよい。これは、バスへの最初の書き込みであるため、伝送シフタの中へ即時にコピーされてもよく、バス上の1つの場所を解放する。

30

#### 【0033】

次いで、UARTは、（例えば、X[7:0]上で）伝送データから伝送バス上に（例えば、TXB[7:0]上に）データバイトの値を書き込んでもよい。24ビットDALI 2.0 伝送が所望される場合、伝送シフタが空になる前に、第3のバイトがバスに書き込まれなければならない。バスが空のままである場合、伝送ラインは、高くなり、高いままあってもよい。次いで、UARTは、伝送タイマリセット信号（例えば、uart\_timer\_reset\_tx 出力）をアサートしてもよい。いくつかの実施形態では、外部タイマが、タイムアウトについて監視するために使用されてもよい。タイムアウトした場合、ソフトウェアは、伝送状態マシンを再始動させるために、（例えば、TXEN = 0、次いで、TXEN = 1を設定することによって）伝送イネーブル信号を切り替えなければならない。ソフトウェアはまた、伝送バスをフラッシュすることを選定してもよい。

40

50

## 【0034】

第1のフレーム後に、U A R Tは、ピン信号（例えば、P 1 H / L）上で規定されるフレームの間のクロックの数を待ってもよい。本時間の間に、伝送出力は、高く保持される。D A L Iに関して、本値は、11であり、バックフレームを待つためにU A R Tに11個のクロックを待たせるであろう。次いで、U A R Tは、伝送バスF I F Oから次のチャネルを伝送してもよい。伝送ウォーターマーク割込信号（例えば、i n t \_ t x）は、ウォーターマークに達する度に割込をトリガしてもよい。いくつかの実施形態では、U A R Tは、各フレームのための传送を開始する前に、ヘッダ・データバイトペアが存在することを確認してもよい。いくつかの実施形態では、U A R Tは、マンチェスタタイミングを自動的に生成してもよい。

10

## 【0035】

## D A L I ギヤソフトウェアモデル

種々の実施形態では、自動D A L Iプロトコルを用いたU A R Tは、ギヤソフトウェアモデルを含んでもよい。ギヤソフトウェアモデルは、特定の信号をアサートすることによって設定されてもよい。例えば、ピン信号（例えば、P 1 H / L）は、バックフレームを開始するように、フォワードフレームの後にクロックサイクルの所望の最大数に設定されてもよい。典型的には、本値は、11未満（例えば、22のハーフビットタイム）でなければならない。U A R Tがギヤモードに設定されるとき、U A R Tは、受信されたフォワードフレームをリッシュし始めてよい。これは、バックフレームが传送される前に、フォワードフレームが受信されなければならないため、必要とされる。フォワードフレームが受信されるとき、これは、アプリケーションソフトウェアによって処理される。バックフレームの値は、传送バス（例えば、T X B [ 7 : 0 ]）の一部に書き込まれる。

20

## 【0036】

バスの一部が空ではないとき、U A R Tは、フォワードフレームの後に所望の最大数よりも少ないクロックサイクルが経過したことを確実にしてもよい。本時間が満了する前にバスワードが利用可能にされる場合、これは、バックフレームとして传送される。それを上回るもののが経過した場合、シフタのコンテンツが破棄される。ワードは、バスから传送シフタの中へ転送されるであろうが、传送されないであろう。次のバックフレームについて、新しいバスワードが、ユーザによってバス上に書き込まれなければならない。

30

## 【0037】

第1のフレーム後に、U A R Tは、別のフォワードフレームを待ってもよい。本時間の間に、传送出力は、高く保持されてもよい。次いで、U A R Tは、次のフォワードフレームが受信されるときに、バスF I F Oから次のチャネルを伝送してもよい。伝送ウォーターマーク割込信号（例えば、i n t \_ t x）は、ウォーターマークに達する度に割込をトリガしてもよい。

## 【0038】

## L I N プロトコル状態マシン

種々の実施形態では、自動プロトコルを用いたU A R Tは、L I Nプロトコルを利用してもよい。そのような実施形態では、特定のプロトコルは、ユーザが複数の利用可能なプロトコルモードのうちの1つを選択することを可能にする複数のビットによって、選定されてもよい。例えば、特定の構成が、「U S E \_ P R O T」信号を論理高に設定することによって、L I Nプロトコルを選択してもよい。L I Nは、自動車アプリケーションで使用されるプロトコルである。L I Nネットワークは、2種類のソフトウェアプロセス、すなわち、「マスタ」プロセスおよび「スレーブ」プロセスから成る。各ネットワークは、1つのマスタプロセスのみを有し、かつ1つ以上のスレーブプロセスを有する。マスタプロセスは、1つのプロセッサU A R T上に常駐する。ネットワーク上の全ての他のU A R Tは、スレーブソフトウェアプロセスによって駆動される。物理層の観点から、1つだけのマスタプロセスが1つのネットワーク上に存在する限り、1つのプロセッサ上のU A R Tマクロが、マスタおよびスレーブプロセスの両方によって駆動されてもよい。

40

## 【0039】

50

いくつかの実施形態では、U A R Tは、マスタプロセスがブレイクを传送することによって传送を開始するときに始まり、その後にデリミタビットが続き、その後に同期フィールドおよび保護識別（「P I D」）バイトが続く。P I Dは、いずれのスレーブプロセスがマスタに応答することを予期されるかを判定する。P I Dバイトの後には、その長さがU A R Tのメモリ部分（例えば、P 3 レジスタ）によって設定される、インターバイトスペースがある。インターバイトスペースが満了する前に、スレーブプロセスのうちの1つ以上が、マスタプロセスに応答してもよい。インターバイトスペース内で何も応答しない場合、マスタは、別の传送を自由に開始する。

#### 【0 0 4 0】

スレーブソフトウェアプロセスは、マスタと同一のU A R Tを駆動してもよい、または完全に別のU A R Tもしくは別のプロセッサデバイス上に常駐してもよい。スレーブプロセスは、マスタフレームを待つことによって開始する。P I Dが合致する場合、スレーブプロセスは、何もしないことによって、または要求された応答を传送することによってのいずれかで、応答する。いくつかの実施形態では、最大8つのバイトが、スレーブによって传送されてもよい。これらのバイトの終了時に、スレーブU A R Tは、传送されたワードのチェックサムを自動的に計算し、これらのバイトの終了時に（例えば、第9のデータバイトにおいて）それをデータバイトとして传送し、L I N T R A N Z A C H O N を完了する。チェックサムは、一度に付加的ビット（例えば、8つのビット）を加算し、キャリービットを結果に加算することによって計算されてもよい。次いで、本チェックサムは、传送データとともに传送されてもよい。

#### 【0 0 4 1】

データが受信U A R Tによって受信されるとき、チェックサムが、同一のアルゴリズムを使用して計算される。传送機によって計算されるチェックサム値である、次のバイト（例えば、第9のバイト）は、逆転させられ、ローカルで計算されたチェックサムに加算される。例えば、結果が全て「1」である場合には、チェックサムがパスしている。以下の表1は、L I N 2 . 2 A仕様からとられた実施例を図示する。表1は、0 x 4 A、0 x 5 5、0 x 9 3、0 x E 5である、計算に関与する4つのデータバイトの例示的値を使用する。

#### 【表1】

表1

| アクション               | 16進法          | キャリー | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---------------------|---------------|------|----|----|----|----|----|----|----|----|

| 0x4A                | 0x4A          |      | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  |

| +0x55<br>キャリーを加算する  | 0x9F<br>0x9F  |      | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 1  |

| +0x93<br>キャリーを加算する  | 0x132<br>0x33 |      | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  |

| +0xE5<br>キャリーを加算する  | 0x118<br>0x19 |      | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  |

| 逆転させる               | 0xE6          |      | 1  | 1  | 1  | 0  | 0  | 1  | 1  | 0  |

| 受信機検証               |               |      |    |    |    |    |    |    |    |    |

| ローカル+受信されたものをチェックする | 0x19<br>+0xE6 |      | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### 【0 0 4 2】

いくつかの実施形態では、2種類のチェックサム、すなわち、レガシーおよび強化が利用可能であり得る。レガシーチェックサムでは、データバイトD 0からD 7のみが、チェックサムを計算するために使用される。強化チェックサムでは、データD 0からD 7およびP I Dが含まれる。いずれのチェックサムが計算で使用されるかは、特定のビット（例えば、C O E N ビット）を使用して、ソフトウェアによって制御ができる。

10

20

30

40

50

## 【0043】

## L I N 伝送ソフトウェアモデル

種々の実施形態では、自動L I Nプロトコルを用いたU A R Tは、伝送ソフトウェアモデルを含んでもよい。伝送ソフトウェアモデルは、特定の信号をアサートすることによって設定されてもよい。例えば、ピン信号（例えば、P 2 H / L）は、伝送する所望のバイト数に設定されてもよい。いくつかの実施形態では、マスタ／スレーブL I Nモードでは、マスタプロセスは、P I Dが伝送されるための値を（例えば、P 1 L [ 5 : 0 ]上で）ロードしてもよい。スレーブプロセスは、伝送バスF I F Oの中へ伝送される最大8つのバイトを書き込んでもよい。いくつかの実施形態では、スレーブ専用モードでは、P I D伝送が必要とされないため、値が無視されてもよい。

10

## 【0044】

いくつかの実施形態では、マスタスレーブモードでは、P I D値を書き込むことが、伝送プロセスを開始してもよい。伝送プロセスは、ブレイクを含んでもよく、その後にS Y N Cバイトが続き、その後に（例えば、P 1 L [ 5 : 0 ]からの）ロードされた値のコンテンツが続く。コンテンツの直後に、P I D値が、ハードウェアによって計算され、伝送されてもよい。この後に、U A R Tは、伝送バス占有率をチェックしてもよい。バスが空ではない場合、これは、スレーブプロセスが、バイトを伝送することを所望するU A R T上に常駐することを意味する。バスの中のバイトは、ピン信号（例えば、P 2 H）上に記憶された伝送バイトの数まで伝送される。バスが空である場合、伝送出力（例えば、T X S）は、どちらが最初であっても、バスが書き込まれるまで、またはロードされた値のコンテンツが書き込まれるまでのいずれかで、高く保持されてもよい。ロードされた値（例えば、P 1 L）が書き込まれる場合、マスタが新しいフレームを開始しており、チェックサム／パリティエンジンがリセットされ、B R E A K - S Y N C伝送プロセス全体が再び開始することが仮定される。

20

## 【0045】

いくつかの実施形態では、スレーブ専用モードでは、S Y N Cを受信することは、バイトを伝送するようにU A R Tを「アーム」する。バスを書き込むことは、伝送プロセスを開始する。S Y N Cが受信される前に伝送バスが書き込まれる場合、伝送は、S Y N Cが完了するまで阻止される。利用可能である場合、次のバイトは、バスが空になる場合に非アクティブ出力を用いて、伝送バス（例えば、T X B [ 7 : 0 ]）F I F Oから伝送される。これは、U A R Tがピン信号（例えば、P 2 H / L）からバイト数を伝送するまで繰り返される。いくつかの実施形態では、伝送ウォーターマーク割込信号（例えば、i n t \_ t x）は、ウォーターマークに達する度に割込をトリガしてもよい。ピン信号（例えば、P 2 H / Lデータワード）からのバイト数の終了時に、U A R Tは、チェックサムビット（例えば、チェックサム0（ビットC 0 E N = 1）またはチェックサム1（ビットC 0 E N = 1）のいずれか）を計算して伝送してもよい。いくつかの実施形態では、マスタ／スレーブモードでは、新しい伝送を開始するために、最後のデータが伝送された後に、ロードされた値（例えば、P 1 L）のコンテンツが書き込まれなければならない。ロードされた値（例えば、P 1 L）を書き込むことが新しいパケットをトリガするため、スレーブ伝送の途中にロードされた値を書き込むことは、無視されるであろう。

30

## 【0046】

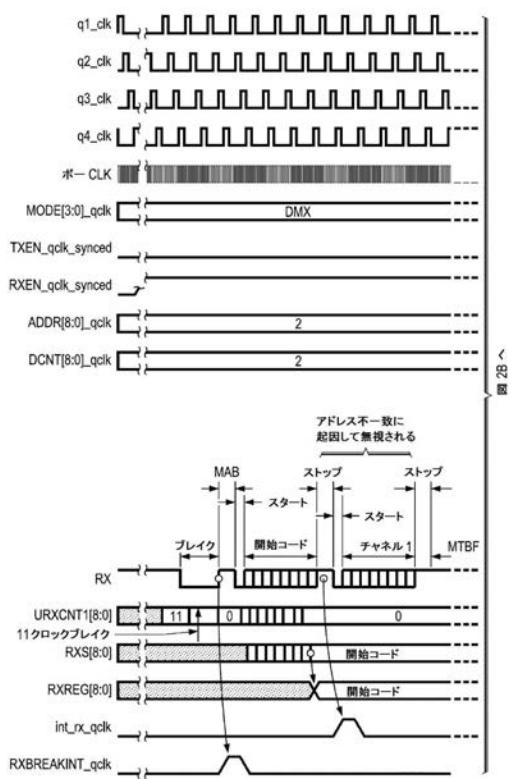

## 2 . 1 4 . 2 L I N受信（スレーブ専用）専用ソフトウェアモデル

種々の実施形態では、自動L I Nプロトコルを用いたU A R Tは、あるスレーブ専用モードのための受信ソフトウェアモデルを含んでもよい。伝送ソフトウェアモデルは、特定の信号をアサートすることによって設定されてもよい。例えば、ピン信号（例えば、P 3 H / L）は、受信する所望のバイト数に設定されてもよい。いくつかの実施形態では、U A R Tは、B R E A Kがライン上に出現することを待ってもよい。それが出現するとき、サンプリングクロックが、同期フレームと同期化される。受信割込衝突信号（例えば、R X B I F）が、フラグを付けられ、チェックサムおよびパリティ計算機が、リセットされる。いくつかの実施形態では、受信される第1のバイトは、P I Dである。受信割込（例

40

50

えば、`int_rx` は、常に、ウォーターマーク / FIFO 設定にかかわらず、PID が受信されるときにフラグを付けられる。UART は、自動的に他の値（例えば、P0 および P1）を計算して検証してもよい。それらが一致しない場合、衝突割込信号（例えば、PERIF）が、フラグを付けられてもよい。ピン信号（例えば、P3H/L）からのバイト数が受信されるまで、入力バイトが受信される。

#### 【0047】

いくつかの実施形態では、あるビット（例えば、C0EN）は、パケット内の最後のバイトのスタートビットが受信される前に、正しい値に設定されなければならない。受信ウォーターマーク割込信号（例えば、`int_rx`）は、ウォーターマークに達する度に割込をトリガするであろう。（例えば、P3H/L からの）所望のデータバイト数が受信されるとき、UART は、自動的にチェックサム（例えば、チェックサム 0 または 1）を計算し、全て 1 を得るように、受信されたチェックサムと排他論理和（XOR）をとってもよい。ローカルで計算されたチェックサムは、メモリ部分（例えば、UXRXCHK レジスタ）の中に記憶されてもよい。受信入力から受信されるチェックサムは、それがデータであった場合のように受信バスの中に記憶されてもよい。

10

#### 【0048】

図 5 は、本開示のある実施形態による、LIN マスター / スレーブモードの例示的タイミング図を図示する。図 6 は、本開示のある実施形態による、LIN マスター / スレーブモードの継続的な例示的タイミング図を図示する。図 7 は、本開示のある実施形態による、LIN スレーブ専用モードの例示的タイミング図を図示する。図 8 は、本開示のある実施形態による、LIN スレーブ専用モードの継続的な例示的タイミング図を図示する。

20

#### 【0049】

##### 非同期アドレス検出モード

いくつかの実施形態では、UART は、非同期アドレス検出モードで動作してもよい。非同期アドレス検出モードは、1 つのバスに接続された複数の受信機がある、モードに使用されてもよい。伝送機が本バス上で传送するとき、全受信機が、それがアドレス指定されているかどうかを把握することが有用である。これは、各受信 UART がその CPU への不必要的割込を排除することを可能にする。

#### 【0050】

いくつかの実施形態では、各トランザクションは、それに先行する BREAK を伴って、または伴わずに、スタートビットを传送する传送機から始まる。本スタートビットの後には、データワードが続く。データがゼロに設定された第 9 のビットを有する場合、全ての UART が、これをデータであると知覚するであろう。传送機が 1 に設定された第 9 のビットとともにバイトを传送するとき、全ての受信 UART が、これをアドレスであると知覚する。次いで、それらは、第 2 のメモリ部分（例えば、レジスタ P3）内のマスクと論理積されたメモリ部分（例えば、P2）の中へプログラムされるアドレスとそれを合致させようとしてもよい。合致がある場合には、データは、受信バッファの中へ時間記録されるであろう。传送および受信される各バイトは、USE\_FIFO = 0 であるときに、割込イベントを生じるであろう。USE\_FIFO = 1 であるとき、割込頻度は、ウォーターマーク設定に依存する。

30

#### 【0051】

##### アドレス検出 TX ソフトウェアモデル

種々の実施形態では、UART は、アドレス検出传送ソフトウェアモデルを含んでもよい。いくつかの実施形態では、本モデルは、MODE 信号を設定することによって設定されてもよい。例えば、MODE は、アドレス検出を用いた非同期 9 ビットモード（「0101」）を選定するように設定されてもよい。いくつかの実施形態では、UART は、BREAK 传送を引き起こしてもよい。例えば、UART は、論理 1 を SENDB ビットに書き込んでもよい。SENDB の直後にメモリ部分（例えば、P1 レジスタ）に書き込むことが、BREAK を传送させるであろう。いったん BREAK 传送が完了すると、SENDB ビットは、自動消去されてもよい。この後には、メモリ部分（例えば、P1）の 8

40

50

ビット値が伝送されてもよい。第9のビットが、1として自動的に伝送されてもよい。これは、アドレス伝送である。SEND Bの直後に伝送バスレジスタに書き込むことが、BREAKを伝送させるであろう。いったんBREAK伝送が完了すると、SEND Bビットは、自動消去されるであろう。この後には、伝送バス値の8ビット値が伝送されるとともに、第9のビットがゼロとして自動的に伝送される。これは、データ伝送である。BREAKの直後に何を伝送するかという決定は、メモリ部分（例えば、P1レジスタ）が書き込まれるかどうかに依存する。メモリ部分（例えば、P1）および伝送バスが両方とも書き込まれる場合、メモリ部分（例えば、P1）のコンテンツが後に続く、BREAKが伝送され、その後に伝送バスの任意のコンテンツが続く。

## 【0052】

BREAK伝送が所望されない場合、SEND Bビットは、無視される、またはゼロに書き込まれることができる。メモリ部分（例えば、P1レジスタ）に書き込むことが、1として自動的に伝送される第9のビットとともに、メモリ部分（例えば、P1）のコンテンツの8ビット値を伝送させてもよい。これは、アドレス伝送である。伝送バスレジスタに書き込むことが、0として自動的に伝送される第9のビットとともに、伝送バスの8ビット値を伝送させるであろう。これは、データ伝送である。最初に何を伝送するかという決定は、メモリ部分（例えば、P1レジスタ）が書き込まれるかどうかに依存する。メモリ部分（例えば、P1）および伝送バスが両方とも書き込まれる場合、メモリ部分（例えば、P1）のコンテンツが伝送され、その後に伝送バスの任意のコンテンツが続く。

## 【0053】

アドレス検出RXソフトウェア

種々の実施形態では、UARTは、アドレス検出受信ソフトウェアモデルを含んでもよい。いくつかの実施形態では、本モデルは、MODE信号を設定することによって設定されてもよい。例えば、MODEは、アドレス検出を用いた非同期9ビットモード（「0101」）を選定するように設定されてもよい。いくつかの実施形態では、UARTは、合致するアドレスを伴って第1のメモリ部分（例えば、P2）を設定してもよい。いくつかの実施形態では、第2のメモリ部分（例えば、P3）は、アドレスマスクとして設定されてもよい。全てのアドレスを受信するために、例えば、「0000 0000」をP3に書き込む。（受信アドレスXOR P2）論理積（AND）P3 = 0000 0000は、「アドレス合致」を意味する。

## 【0054】

アドレス合致が起こるとき、未加工受信アドレスが、受信 FIFOにロードされる。次いで、後に続く任意のデータ（ゼロに設定された第9のビットを伴う8ビットバイト）が、受信 FIFOにロードされる。本プロセスは、第1のメモリ部分（例えば、P2）のコンテンツと合致しない別のアドレス（例えば、1に設定された第9のビットを伴う8ビットバイト）が受信されるまで継続する。

## 【0055】

非同期マンチェスタモード

種々の実施形態では、自動プロトコルを用いたUARTは、非同期マンチェスタプロトコルを利用してよい。そのような実施形態では、特定のプロトコルは、ユーザが複数の利用可能なプロトコルモードのうちの1つを選択することを可能にする複数のビットによって、選定されてもよい。例えば、特定の構成が、「USE\_\_PROT」信号を論理高に設定することによって、マンチェスタプロトコルを選択してもよい。本モードは、全てのビットがハードウェアによってマンチェスタ符号化されることを除いて、一般的UART接続モードである。DALIモードで使用される同一のハードウェアが、ここで再利用されてもよい。

## 【0056】

いくつかの実施形態では、ユーザは、伝送方向に伝送ワードを伝送バス（例えば、TXB <7:0>）に書き込んでもよい。次いで、バスのコンテンツが後に続く、低から高のスタートビットが伝送されてもよい。受信方向に、各ワードが受信されると、受信バス（

10

20

30

40

50

例えば、`R X B < 7 : 0 >`にロードされ、入力マンチェスタから復号される。伝送および受信される各バイトは、`U S E _ F I F O = 0`であるときに、割込イベントを生じるであろう。`U S E _ F I F O = 1`であるとき、割込頻度は、ウォーターマーク設定に依存する。

#### 【0057】

図9は、本開示のある実施形態による、伝送のための例示的マンチェスタ復号方式を図示する。図10は、本開示のある実施形態による、受信のための例示的マンチェスタ復号方式を図示する。図11は、本開示のある実施形態による、受信のための継続的な例示的マンチェスタ復号方式を図示する。図12は、本開示のある実施形態による、受信のためのさらに継続的な例示的マンチェスタ復号方式を図示する。図13は、本開示のある実施形態による、受信のためのなおもさらなる例示的マンチェスタ復号方式を図示する。いくつかの実施形態では、受信データのクロックレートは、伝送データのものと異なり得る。したがって、`B R G`から出てくるクロックをカウントするために別個のレジスタを維持することが必要であり得る。これらのタイミング図では、本レジスタは、`B R G - R X`と呼ばれてもよい。これは、内部レジスタであり、`S F R`空間で読み出す、または書き込むために利用可能ではない。

10

#### 【0058】

いくつかの実施形態では、`U A R T`は、ハードウェアを使用して、マンチェッタ符号化を復号することができる。ソフトウェアは、マンチェスタ復号方式の高から低の遷移をハンドリングするために起動される必要はない。むしろ、`U A R T`は、単純に、回収されたデータビットを受信する。これは、バイトの間にブレイクを必要とすることなく、無限(連続)数のバイトのマンチェスタ传送を可能にする。

20

#### 【0059】

##### T X ソフトウェアモデル

種々の実施形態では、自動プロトコルを用いた`U A R T`は、伝送ソフトウェアモデルを利用してもよい。そのような実施形態では、モデルは、`U A R T`が伝送されるワードを伝送バスに書き込むことから始まってもよい。これは、低から高の遷移である、`S T A R T`を出力させてもよく、その後に1バイトのデータが続く。シフタが空になる前に、伝送ワードが伝送バスに書き込まれる限り、その間に`S T A R T`ビットを伴わずに、ビットが立て続けに伝送される。これは、無限数のバイトが`S T A R T`ビットの後に立て続けに伝送されることを可能にする。シフタが空になるときに、伝送ラインが非アクティブになる。次いで、新しいワードが、伝送バスが空になった後にそれに書き込まれるとき、`U A R T`は、新しい`S T A R T`ビットを伝送し、その後に伝送バスワードが続き、サイクルを繰り返すであろう。

30

#### 【0060】

##### R X ソフトウェアモデル

種々の実施形態では、自動プロトコルを用いた`U A R T`は、受信ソフトウェアモデルを利用してもよい。そのような実施形態では、モデルは、非アクティブ(1)から始まってもよく、その後にマンチェスタ「1」が続く(低から高)。マンチェスタハーフビットタイムが、最初の低遷移から導出される。受信される任意のデータが、マンチェスタから復号され、受信`F I F O`にロードされる。

40

【図1】

【図2】

FIG. 2

【図2 A】

FIG. 2A

【図2 B】

FIG. 2B

【図3】

FIG. 3

【図3A】

FIG. 3A

図3Bへ

【図3B】

FIG. 3B

【図4】

FIG. 4

【 図 5 】

FIG. 5

【図6】

FIG. 6

【 図 7 】

FIG. 7

【 四 8 】

8

EIC

【図 9】

FIG. 9

【図 10】

FIG. 10

【図 11】

FIG. 11

【図 12】

FIG. 12

【 図 1 3 】

FIG. 13

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2016/038312

A. CLASSIFICATION OF SUBJECT MATTER

INV. G06F13/42

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G06F

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                          | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2013/297831 A1 (LAURENTIU BIRSAN [FR])<br>7 November 2013 (2013-11-07)<br>paragraph [0002] - paragraph [0049]<br>figures 1, 3<br>-----                   | 1-20                  |

| X         | US 2015/074306 A1 (AYYAGARI RAVISHANKAR S<br>[IN] ET AL) 12 March 2015 (2015-03-12)<br>paragraph [0061] - paragraph [0070]<br>figures 2-7<br>-----          | 1-20                  |

| X         | US 5 371 736 A (EVAN SHABTAI [US])<br>6 December 1994 (1994-12-06)<br>column 1, line 6 - column 2, line 36<br>column 5, line 36 - page 11, line 62<br>----- | 1-20                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

18 August 2016

01/09/2016

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Rudolph, Stefan

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2016/038312

| Patent document cited in search report | Publication date | Patent family member(s)       | Publication date         |

|----------------------------------------|------------------|-------------------------------|--------------------------|

| US 2013297831 A1                       | 07-11-2013       | NONE                          |                          |

| US 2015074306 A1                       | 12-03-2015       | NONE                          |                          |

| US 5371736 A                           | 06-12-1994       | CA 2112001 A1<br>US 5371736 A | 22-06-1994<br>06-12-1994 |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,ST,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,R0,RS,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,D0,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(72)発明者 サミュエル , ロシャン

アメリカ合衆国 アリゾナ 85249 , チャンドラー , エス . ミンガス プレイス 50

65

(72)発明者 アベルウェット , ジャンマイケル

アメリカ合衆国 アリゾナ 85297 , ギルバート , イー . マーシャル アベニュー 4

477

(72)発明者 ブラウン , ワード アール .

アメリカ合衆国 アリゾナ 85249 , チャンドラー , サウス ビッグ ホーン プレイス

5011

(72)発明者 デサイ , チンタン

アメリカ合衆国 アリゾナ 85286 , チャンドラー , ダブリュー . シーガル ドライブ

1100

(72)発明者 アイビー , ブラント

アメリカ合衆国 アリゾナ 85248 , チャンドラー , ウエスト インディゴ ドライブ

1303

(72)発明者 ドシア , ラズヴァン

ルーマニア国 062057 ブカレスト , トゥルグ ネアムツ 14エー , ブロック ピー

27

F ターム(参考) 5K034 HH63 RR01 SS01

5K047 AA11 JJ03 JJ06