(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-184426

(P2007-184426A)

(43) 公開日 平成19年7月19日(2007.7.19)

| (51) Int.CI.         | F 1                | テーマコード (参考) |

|----------------------|--------------------|-------------|

| H01L 23/02 (2006.01) | H01L 23/02 J 5FO41 |             |

| H01L 33/00 (2006.01) | H01L 33/00 F N     |             |

審査請求 未請求 請求項の数 6 O L (全 13 頁)

|           |                          |          |                                           |

|-----------|--------------------------|----------|-------------------------------------------|

| (21) 出願番号 | 特願2006-1802 (P2006-1802) | (71) 出願人 | 000190688<br>新光電気工業株式会社<br>長野県長野市小島田町80番地 |

| (22) 出願日  | 平成18年1月6日 (2006.1.6)     | (74) 代理人 | 100070150<br>弁理士 伊東 忠彦                    |

|           |                          | (72) 発明者 | 春原 昌宏<br>長野県長野市小島田町80番地 新光電気<br>工業株式会社内   |

|           |                          | (72) 発明者 | 田口 裕一<br>長野県長野市小島田町80番地 新光電気<br>工業株式会社内   |

|           |                          | (72) 発明者 | 白石 晶紀<br>長野県長野市小島田町80番地 新光電気<br>工業株式会社内   |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】基板を個片化する場合のチッピングの発生を抑制し、信頼性の良好な半導体装置を製造する半導体装置の製造方法を提供する。

【解決手段】第1の基板に半導体素子が実装された構造を有する半導体装置の製造方法であって、前記半導体素子が実装された前記第1の基板と、当該第1の基板と異なる材料よりなる第2の基板とを接合して当該半導体素子を封止する第1の工程と、前記第1の基板に第1の溝部を、前記第2の基板に第2の溝部を形成する第2の工程と、前記第1の溝部と前記第2の溝部の間を開くことにより、前記第1の基板と前記第2の基板を個片化する第3の工程と、を有することを特徴とする半導体装置の製造方法。

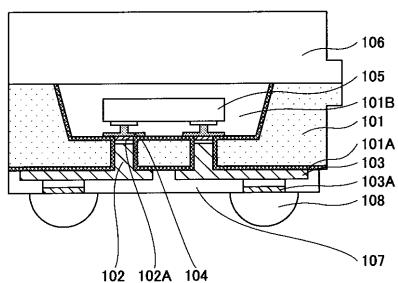

【選択図】図2M

実施例1による半導体装置の製造方法を示す図(その13)

**【特許請求の範囲】****【請求項 1】**

第1の基板に半導体素子が実装された構造を有する半導体装置の製造方法であって、前記半導体素子が実装された前記第1の基板と、当該第1の基板と異なる材料よりなる第2の基板とを接合して当該半導体素子を封止する第1の工程と、前記第1の基板に第1の溝部を、前記第2の基板に第2の溝部を形成する第2の工程と、前記第1の溝部と前記第2の溝部の間をへき開することにより、前記第1の基板と前記第2の基板を個片化する第3の工程と、を有することを特徴とする半導体装置の製造方法。

**【請求項 2】**

前記半導体素子は光機能素子よりなることを特徴とする請求項1記載の半導体装置の製造方法。

**【請求項 3】**

前記第2の基板は光透過性材料よりなることを特徴とする請求項2記載の半導体装置の製造方法。

**【請求項 4】**

前記第1の工程では、前記第1の基板と前記第2の基板は、陽極接合により接合されることを特徴とする請求項1乃至3のうち、いずれか1項記載の半導体装置の製造方法。

**【請求項 5】**

前記第1の基板を貫通するように形成される貫通配線を形成する工程をさらに有し、前記半導体素子は、当該貫通配線と接続されるように実装されることを特徴とする請求項1乃至4のうち、いずれか1項記載の半導体装置の製造方法。

**【請求項 6】**

前記第1の基板には、前記半導体素子を実装する凹部が形成され、該凹部の周囲が前記第2の基板と接合されることで前記半導体素子が封止されることを特徴とする請求項1乃至5のうち、いずれか1項記載の半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、基板に発光素子が実装されてなる半導体装置の製造方法に関する。

**【背景技術】****【0002】**

例えば、基板上に半導体素子が実装されてなる半導体装置を製造する場合、基板上に複数の半導体素子を実装し、当該基板を切断して個片化することにより、複数の半導体装置を形成する方法がとられる場合がある。この場合、基板の切断（個片化）は、例えばダイシングにより行われることが一般的であった（特許文献1参照）。ダイシングとは、高速回転させたブレードにより、基板を切断する方法である。

**【特許文献1】特開2005-129643号公報****【特許文献2】特開2001-345289号公報****【発明の開示】****【発明が解決しようとする課題】****【0003】**

しかし、基板をダイシングにより切断する場合に、高速回転しているブレードを用いるために、基板にチッピングと呼ばれる欠けが発生し、半導体装置の信頼性が低下してしまう問題が生じる場合があった。

**【0004】**

特に、複数の基板が接合された構造を切断する場合には、基板の材料によっては材料ごとに異なるブレードを用いることが必要となる場合があり、切断面に段差が生じるためにチッピングが生じやすくなる場合があった。

10

20

30

40

50

**【 0 0 0 5 】**

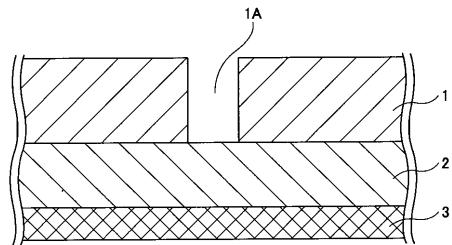

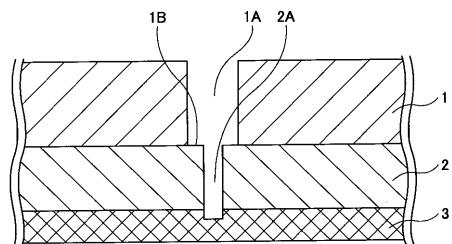

例えば、図1A～図1Bは、接合された基板1と基板2を、ダイシングにより個片化する状態を模式的に示した図である。

**【 0 0 0 6 】**

まず、図1Aに示した状態は、接合された基板1と基板2が、ダイシングテープ3上に載置された状態から、ダイシングによって当該基板1が切断された状態を示す図である。前記基板1には、開口部1Aが形成される。

**【 0 0 0 7 】**

次に、図1Bに示す状態は、例えば前記基板2が前記基板1と異なる材料である場合、図1Aの工程と異なるブレードによって前記基板2が切断されて開口部2Aが形成された状態を示す図である。ここで、基板1と基板2が接合された構造は切断されて個片化される。しかし、本図に示す工程においては、ブレードは前記開口部1Aの幅より小さいものを用いる必要があるため、前記開口部1Aの底面には、角部1Bが形成されてしまう。

**【 0 0 0 8 】**

このため、当該角部1Bがチッピングによって欠けやすくなる場合があった。また、半導体装置にチッピングが生じた場合、当該チッピングを起点として割れや破損が発生して半導体装置の信頼性が低下する場合があった。

**【 0 0 0 9 】**

また、上記の特許文献2（特開2001-345289号公報）には、へき開により半導体装置を個片化する方法が開示されている。しかし、図1A～図1Bに示したように、異なる材料が接合された構造を個片化する場合の問題については、その解決方法はなんら開示されていない。

**【 0 0 1 0 】**

そこで、本発明では、上記の問題を解決した、新規で有用な半導体装置の製造方法を提供することを課題としている。

**【 0 0 1 1 】**

本発明の具体的な課題は、基板を個片化する場合のチッピングの発生を抑制し、信頼性の良好な半導体装置を製造する半導体装置の製造方法を提供することである。

**【 課題を解決するための手段】****【 0 0 1 2 】**

本発明は、上記の課題を、第1の基板に半導体素子が実装された構造を有する半導体装置の製造方法であって、前記半導体素子が実装された前記第1の基板と、当該第1の基板と異なる材料よりなる第2の基板とを接合して当該半導体素子を封止する第1の工程と、前記第1の基板に第1の溝部を、前記第2の基板に第2の溝部を形成する第2の工程と、前記第1の溝部と前記第2の溝部の間をへき開することにより、前記第1の基板と前記第2の基板を個片化する第3の工程と、を有することを特徴とする半導体装置の製造方法により、解決する。

**【 0 0 1 3 】**

当該半導体装置の製造方法によれば、基板を個片化する場合のチッピングの発生を抑制し、信頼性の良好な半導体装置を製造することが可能となる。

**【 0 0 1 4 】**

また、前記半導体素子は光機能素子よりなると、該半導体素子によって発光または受光などを行うことが可能になる。

また、前記第2の基板は光透過性材料よりなると、前記半導体素子による発光または受光が容易となり、好ましい。

**【 0 0 1 5 】**

また、前記第1の工程では、前記第1の基板と前記第2の基板は、陽極接合により接合されると、清浄な状態で前記半導体素子を封止することが可能となり、好ましい。

**【 0 0 1 6 】**

また、前記第1の基板を貫通するように形成される貫通配線を形成する工程をさらに有

10

20

30

40

50

し、前記半導体素子は、当該貫通配線と接続されるように実装されると、前記半導体素子と該半導体素子の接続対象の接続が容易となる。

#### 【0017】

また、前記第1の基板には、前記半導体素子を実装する凹部が形成され、該凹部の周囲が前記第2の基板と接合されることで前記半導体素子が封止されると、当該半導体装置を封止することが容易となり、好ましい。

#### 【発明の効果】

#### 【0018】

本発明によれば、基板を個片化する場合のチッピングの発生を抑制し、信頼性の良好な半導体装置を製造する半導体装置の製造方法を提供することが可能となる。

10

#### 【発明を実施するための最良の形態】

#### 【0019】

本発明による半導体装置の製造方法は、第1の基板に半導体素子が実装された構造を有する半導体装置の製造方法であって、前記半導体素子が実装された前記第1の基板と、当該第1の基板と異なる材料よりなる第2の基板とを接合して当該半導体素子を封止する第1の工程と、前記第1の基板に第1の溝部を、前記第2の基板に第2の溝部を形成する第2の工程と、前記第1の溝部と前記第2の溝部の間をへき開することにより、前記第1の基板と前記第2の基板を個片化する第3の工程と、を有することを特徴としている。

#### 【0020】

従来、基板を切断して個片化する場合には高速回転したブレードを用いたダイシングを用いることが一般的であり、基板にチッピングが生じやすくなっていた。特に、異なる材料からなる基板が接合された構造においては、異なるブレードを用いる必要が生じる場合があるため、チッピングがさらに生じやすくなり、半導体装置の信頼性が低下してしまう場合があった。

20

#### 【0021】

一方、本発明による半導体装置の製造方法では、異なる材料よりなる第1の基板と第2の基板が接合された構造を個片化する場合、前記第1の基板に第1の溝部を、前記第2の基板に第2の溝部を形成し、前記第1の溝部と前記第2の溝部の間をへき開することにより、行っている。

30

#### 【0022】

このため、基板にチッピングが発生することが抑制されるとともに、チッピングが起点となって起こる半導体装置の割れや破損の発生を抑制することが可能となる。このため、信頼性の良好な半導体装置を製造することが可能になっている。

#### 【0023】

本発明による半導体装置の製造方法では、様々な半導体装置を製造することができるがその具体的な一例について図面に基づき、以下に説明する。

#### 【実施例1】

#### 【0024】

図2A～図2Dは、本発明の実施例1による半導体装置の製造方法を手順を追って示す図である。ただし図中、先に説明した部分には同一の参照符号を付し、説明を省略する場合がある。

40

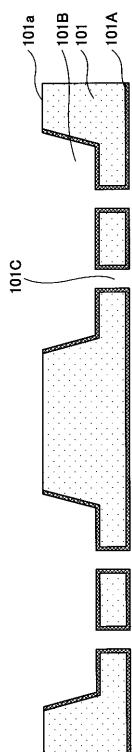

#### 【0025】

まず、図2Aに示す工程において、例えば、Siよりなる基板（第1の基板）101を用意する。また、必要に応じて、前記基板101を研削して所定の厚さ（例えば200μm程度）となるようにしてもよい。

#### 【0026】

次に、図2Bに示す工程において、前記基板101に、後の工程において半導体素子を実装（封止）するための複数の凹部101Bと、該複数の凹部101Bのそれぞれの底部を貫通する、複数のビアホール101Cを形成する。前記凹部101Bと前記ビアホール101Cを形成するにあたっては、例えば、前記基板101上にパターニングされたレジ

50

ストによるマスクを形成した後、R I E (リアクティブ・イオン・エッティング)により、形成する。さらに、前記ビアホール101Cの内壁面を含む、前記基板101の表面を酸化して、シリコン酸化膜よりなる絶縁膜101Aを形成する。また、前記凹部周囲の、後の工程において別の基板(ガラス)が接合される接合面101aの酸化膜101Aは、例えば研磨などにより剥離しておくことが好ましい。また、当該接合面101aの酸化膜の剥離は、後の工程において行ってもよい。

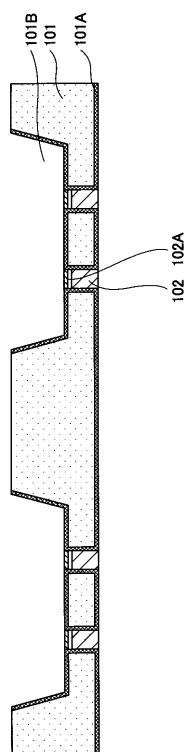

#### 【0027】

次に、図2Cに示す工程において、例えばメッキ法により、前記ビアホール101Cにビアプラグ102と、前記ビアプラグ102上に、Ni/Au層よりなる接続層102Aを形成する。なお、Ni/Auよりなる接続層とは、Auが表面側(接続面)となるように形成された、Au層とNi層が積層されてなる層を意味している(以下同じ)。上記のメッキにあたっては、例えば、まず前記絶縁膜101Aの表面にシード層(給電層、図示せず)を形成し、当該シード層上に、電解メッキ法により前記ビアプラグ102、および前記接続層102Aを形成する。この後、余剰なシード層をエッティングにより除去する。

#### 【0028】

次に、図2Dに示す工程において、例えばメッキ法により、前記基板101の裏面(前記接続層102Aが形成される側の反対側)に、前記ビアプラグ102に接続されるパターン配線103を形成する。

#### 【0029】

前記パターン配線103の形成にあたっては、まず、前記絶縁膜101Aの表面にシード層(図示せず)を形成し、当該シード層上にフォトリソグラフィ法によりパターニングされたレジストパターン(図示せず)を形成する。その後、当該レジストパターンをマスクに電解メッキ法により、前記パターン配線103を形成し、該レジストパターンを剥離する。さらに、該レジストパターンを剥離することで露出するシード層をエッティングにより、除去する。

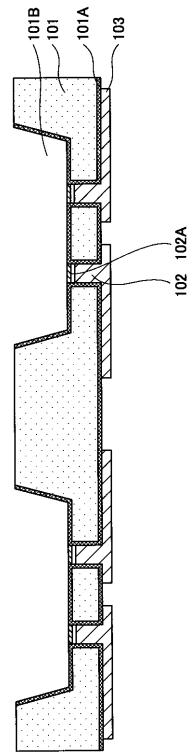

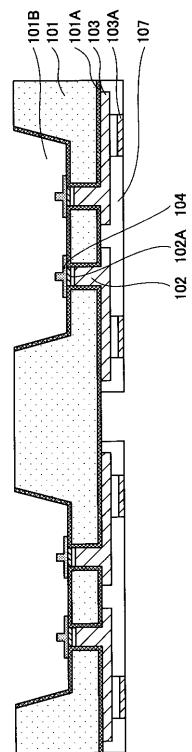

#### 【0030】

次に、図2Eに示す工程において、前記パターン配線103の一部が露出するように、前記基板101の裏面に、ソルダーレジスト層107を形成する。その後、露出した前記パターン配線103に、例えば無電解メッキにより、Ni/Auよりなる接続層103Aを形成する。

#### 【0031】

次に、図2Fに示す工程において、前記接続層103A上に、例えばAuスタッドバンプよりなる、バンプ104を設置する。

#### 【0032】

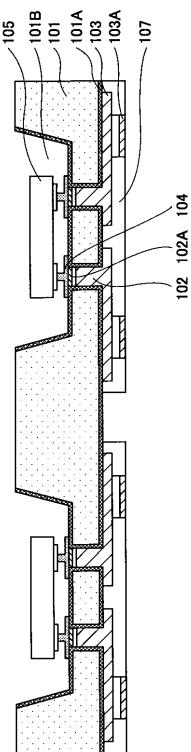

次に、図2Gに示す工程において、前記バンプ104(接続層102A)を介して前記ビアプラグ102に接続されるように、複数形成された前記凹部101Bに、例えば光機能素子よりなる半導体素子105を、それぞれフリップチップ実装する。この場合、前記半導体素子105に形成された、例えばAuまたはAlよりなる接続パッドと、前記バンプ104を超音波により接合する。

#### 【0033】

また、前記半導体素子105として実装される光機能素子の例としては、例えば発光素子または受光素子(光電変換素子)がある。また、当該発光素子としては、例えばLEDを用いると、消費電力を抑制することが可能となり、好適である。

#### 【0034】

次に、図2Hに示した工程において、前記基板101と異なる材料である、例えばガラスなどの光透過性材料よりなる基板(第2の基板)106を接合する。この場合、前記凹部101Bの周囲の接合面101aと、前記基板106を、例えば陽極接合により、接合する。このようにして、前記基板101と前記基板106により画成される複数の空間(凹部101B)に、それぞれ前記半導体素子105が封止され、複数の半導体装置が形成される。また、前記半導体素子105が、発光素子などの光機能素子よりなる場合、前記

10

20

30

40

50

基板 106 は、光透過性材料よりなることが好ましい。

【0035】

また、必要に応じて、前記接続層 103A に半田ボール 108 を形成するが、該半田ボール 108 の形成は省略することも可能である。

【0036】

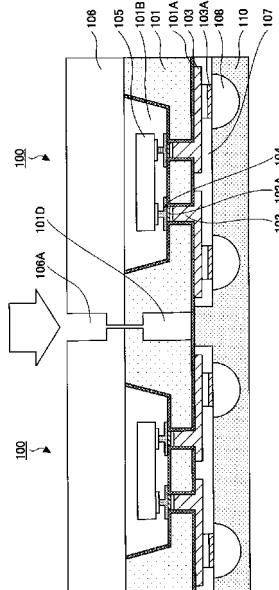

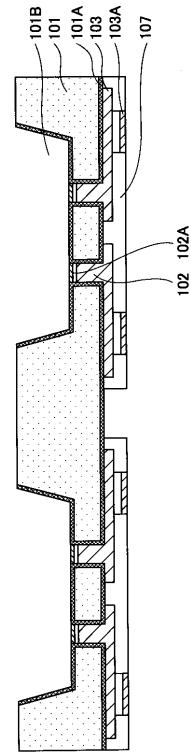

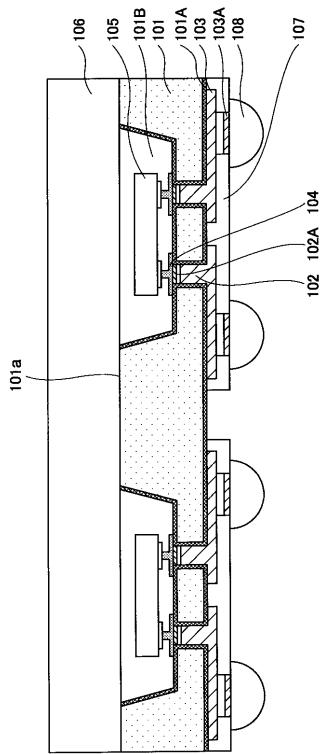

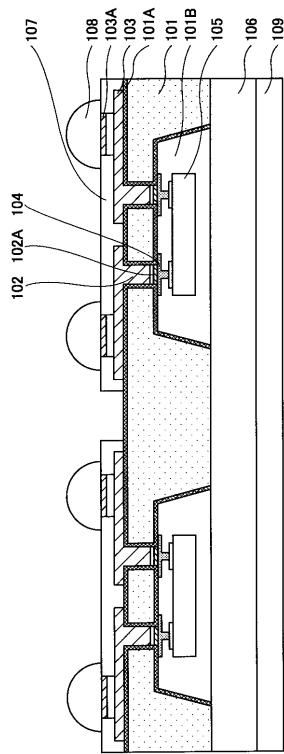

次に、図 2I ~ 図 2O に示す工程において、接合された、異なる材料よりなる前記基板 101 と前記基板 106 を個片化し、半導体装置を個片化する。

【0037】

まず、図 2I に示す工程において、前記基板 106 の外側（基板 101 が接合された側の反対側）にダイシングテープ（粘着性の樹脂材料よりなるテープ）を貼付する。

【0038】

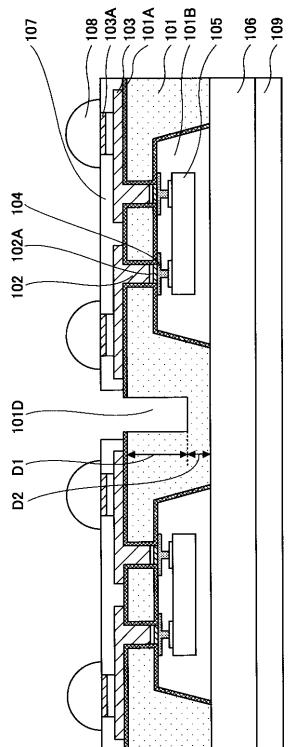

次に、図 2J に示す工程において、前記基板 101 の外側（前記基板 106 が接合された側の反対側）から、ダイシングにより、深さが D1 となる溝部（切り込み）101D を形成する。この場合、前記基板 101 の厚さを 200 μm とすると、前記深さ D1 を、例えば 150 μm 程度となるようにし、前記溝部 101D を除いた該基板 101 の厚さ D2 が 50 μm 程度となるようにする。この後、前記ダイシングテープ 109 を剥離する。

【0039】

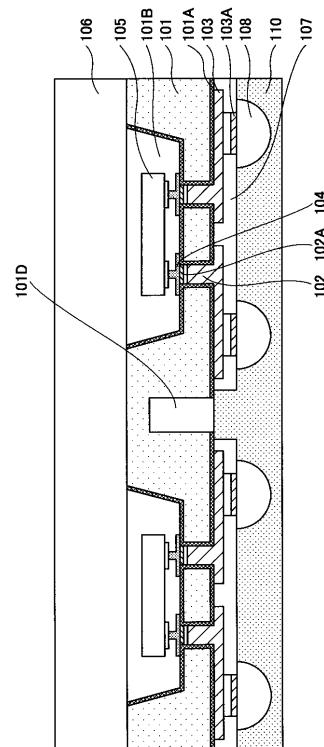

次に、図 2K に示す工程において、前記基板 101 の外側にダイシングテープ 110 を貼付する。

【0040】

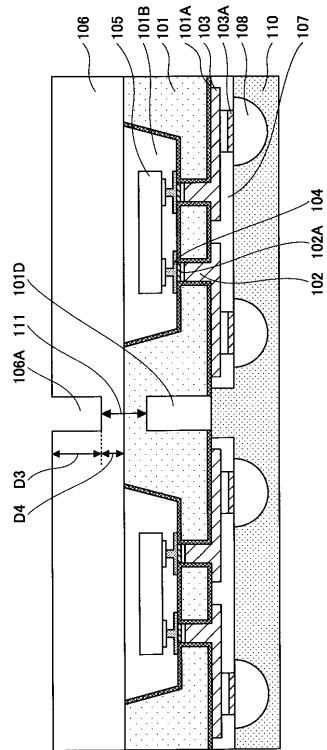

次に、図 2L に示す工程において、前記基板 106 の外側（前記基板 101 が接合された側の反対側）から、ダイシングにより、深さが D3 となる溝部（切り込み）106A を形成する。この場合、前記基板 106 の厚さを 200 μm とすると、前記深さ D3 を、例えば 150 μm 程度となるようにし、前記溝部 D3 を除いた該基板 106 の厚さ D4 が 50 μm 程度となるようになる。すなわち、前記溝部 101D と前記溝部 106A の間には、厚さが 50 μm の基板 101 と、厚さが 50 μm の基板 106 よりなる接続部 111 が残ることになる。

【0041】

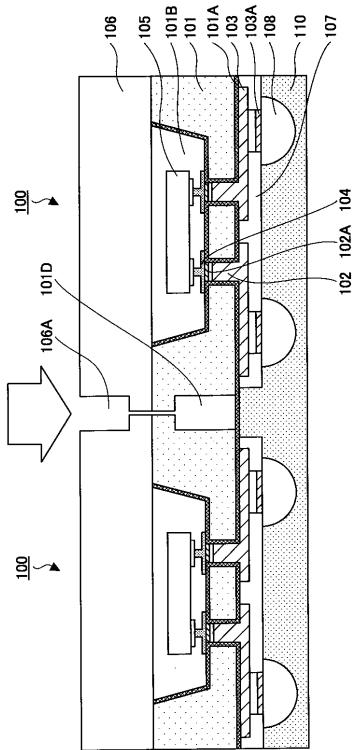

次に、図 2M に示す工程において、前記ダイシングテープ 110 を引っ張って伸ばすか、または、例えばゴムローラなどで前記基板 106（前記基板 101）に応力を印加する。このため、前記溝部 101D と前記溝部 106A の間に残留した接続部 111（前記基板 101 と前記基板 106）がへき開により切断され、前記基板 101 と前記基板 106 が個片化され、半導体装置 100 が個片化される。

【0042】

次に、図 2N に示す工程において、例えばダイスピッカーなどの装置によって、個片化された半導体装置 100 を前記ダイシングテープ 110 より剥離する。このようにして、本実施例による半導体装置 100 を形成することができる。

【0043】

本実施例による半導体装置の製造方法によれば、従来のダイシングによる個片化で問題になっていたチッピングの発生を抑制することが可能となり、チッピングが起点となって起こる半導体装置の割れや破損の発生を抑制することが可能となる。このため、信頼性の良好な半導体装置を製造することができる。

【0044】

特に、異なる材料からなる基板が接合された構造においては、従来の個片化の方法では、異なるブレードを用いる必要が生じる場合があるため、チッピングがさらに生じやすくなり、半導体装置の信頼性が低下してしまう場合があった。

【0045】

例えば、本実施例による半導体装置のように、光機能素子よりなる半導体素子を封止する場合には、例えばガラスなどの光透過性の材料よりなる基板を用いることが好ましい。また、光透過性の材料よりなる基板と接合される、当該半導体素子が実装される基板は、

10

20

30

40

50

例えば S i などの実装に好適な材料が用いられることが好ましい。

#### 【0046】

このように、本実施例による半導体装置は、異なる材料よりなる基板が接合された構造とされることが好ましく、このような構造を個片化する必要が生じていた。そこで、本実施例では、異なる材料よりなる第1の基板（基板101）と第2の基板（基板106）が接合された構造を個片化する場合、まず、前記第1の基板に第1の溝部（溝部101D）を、前記第2の基板に第2の溝部（溝部106A）を形成している。次に、前記第1の溝部と前記第2の溝部の間（接続部111）をへき開することにより、第1の基板と第2の基板の個片化を行っている。

#### 【0047】

このため、個片化された切断面に、ダイシングのブレード（例えばブレードの幅）を変更したことによる段差が生じることがない。また、へき開による切断面は突起や凹凸などが形成されることが少なく、切断面の形状が良好であって、チッピングの発生が起こりにくい。このため、欠けや破損などの発生が抑制され、信頼性の良好な半導体装置を製造することができる。

#### 【0048】

また、本実施例では、実装される半導体素子105を封止する場合に、S i よりなる前記基板101と、ガラスよりなる前記基板106を用いているため、該基板101と該基板106の接合を陽極接合により行うことが可能になっている。このため、例えば樹脂などの接着剤により基板が接合される場合に比べて前記半導体素子105が封止される空間が清浄に保持され、前記半導体素子（光機能素子）105の特性を良好に保持することができるようになっている。

#### 【0049】

また、本実施例では、前記半導体素子105を実装する前に、該半導体素子105と接続される、前記基板101を貫通するビアプラグ102を形成しているため、当該導体素子105と接続対象（ボードなど）との接続が容易となる半導体装置を製造することが可能となっている。

#### 【0050】

また、本実施例による半導体装置100を構成する材料は、上記に示した場合に限定されず、様々な材料を用いて形成することが可能である。

#### 【0051】

以上、本発明を好ましい実施例について説明したが、本発明は上記の特定の実施例に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

#### 【産業上の利用可能性】

#### 【0052】

本発明によれば、基板を個片化する場合のチッピングの発生を抑制し、信頼性の良好な半導体装置を製造する半導体装置の製造方法を提供することが可能となる。

#### 【図面の簡単な説明】

#### 【0053】

【図1A】従来の基板の個片化の方法を示す図（その1）である。

【図1B】従来の基板の個片化の方法を示す図（その2）である。

【図2A】実施例1による半導体装置の製造方法を示す図（その1）である。

【図2B】実施例1による半導体装置の製造方法を示す図（その2）である。

【図2C】実施例1による半導体装置の製造方法を示す図（その3）である。

【図2D】実施例1による半導体装置の製造方法を示す図（その4）である。

【図2E】実施例1による半導体装置の製造方法を示す図（その5）である。

【図2F】実施例1による半導体装置の製造方法を示す図（その6）である。

【図2G】実施例1による半導体装置の製造方法を示す図（その7）である。

【図2H】実施例1による半導体装置の製造方法を示す図（その8）である。

10

20

30

40

50

【図2I】実施例1による半導体装置の製造方法を示す図(その9)である。

【図2J】実施例1による半導体装置の製造方法を示す図(その10)である。

【図2K】実施例1による半導体装置の製造方法を示す図(その11)である。

【図2L】実施例1による半導体装置の製造方法を示す図(その12)である。

【図2M】実施例1による半導体装置の製造方法を示す図(その13)である。

【図2N】実施例1による半導体装置の製造方法を示す図(その14)である。

【符号の説明】

【0054】

100 半導体装置

101 基板

10

101A 絶縁膜

101B 凹部

101C ビアホール

101D 溝部

102 ビアプラグ

102A 接続層

103 パターン配線

103A 接続層

20

104 バンプ

105 半導体素子

106 基板

106A 溝部

107 ソルダーレジスト層

108 半田ボール

109, 110 ダイシングテープ

111 接続部

【図 1 A】

従来の基板の個片化の方法を示す図(その1)

【図 2 A】

実施例1による半導体装置の製造方法を示す図(その1)

【図 1 B】

従来の基板の個片化の方法を示す図(その2)

【図 2 B】

実施例1による半導体装置の製造方法を示す図(その2)

【図 2 C】

実施例1による半導体装置の製造方法を示す図(その3)

【図2D】

実施例1による半導体装置の製造方法を示す図(その4)

【図2E】

実施例1による半導体装置の製造方法を示す図(その5)

【図2F】

実施例1による半導体装置の製造方法を示す図(その6)

【図2G】

実施例1による半導体装置の製造方法を示す図(その7)

【図2H】

実施例1による半導体装置の製造方法を示す図(その8)

【図2I】

実施例1による半導体装置の製造方法を示す図(その9)

【図2J】

実施例1による半導体装置の製造方法を示す図(その10)

【図2K】

実施例1による半導体装置の製造方法を示す図(その11)

【図2L】

実施例1による半導体装置の製造方法を示す図(その12)

【図2M】

実施例1による半導体装置の製造方法を示す図(その13)

【図2N】

実施例1による半導体装置の製造方法を示す図(その14)

---

フロントページの続き

(72)発明者 小泉 直幸

長野県長野市小島田町 80 番地 新光電気工業株式会社内

(72)発明者 村山 啓

長野県長野市小島田町 80 番地 新光電気工業株式会社内

(72)発明者 坂口 秀明

長野県長野市小島田町 80 番地 新光電気工業株式会社内

(72)発明者 東 光敏

長野県長野市小島田町 80 番地 新光電気工業株式会社内

F ターム(参考) 5F041 DA03 DA09 DA13 DA20 DA61