등록특허 10-1988405

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2019년09월30일

(11) 등록번호 10-1988405

(24) 등록일자 2019년06월05일

- (51) 국제특허분류(Int. Cl.)

*H01L 33/44* (2010.01) *H01L 33/36* (2010.01)

(21) 출원번호 10-2013-0010618

(22) 출원일자 2013년01월30일

심사청구일자 2018년01월23일

(65) 공개번호 10-2014-0097898

(43) 공개일자 2014년08월07일

(56) 선행기술조사문현

US06242761 B1

US20110156077 A1

- (73) 특허권자

엘지이노텍 주식회사

서울특별시 중구 후암로 98 (남대문로5가)

(72) 발명자

박병두

서울특별시 중구 한강대로 416 서울스퀘어

김태진

서울특별시 중구 한강대로 416 서울스퀘어

황선교

서울특별시 중구 한강대로 416 서울스퀘어

(74) 대리인

박병창

전체 청구항 수 : 총 22 항

심사관 : 배성주

(54) 발명의 명칭 **발광소자**

**(57) 요 약**

실시 예에 따른 발광소자는, 도전성 기판, 상기 도전성 기판 상에 배치되는 제1전극층, 상기 제1전극층 상에 배치되는 제1 반도체층, 제2 반도체층, 및 상기 제1 반도체층과 상기 제2 반도체층 사이에 위치하는 활성층을 구비하는 발광 구조물, 상기 제2 반도체층과 전기적으로 연결된 제2전극 및 상기 발광 구조물이 칩(chip)단위로 절단될 때 상기 칩들의 경계에 배치되어 크랙을 방지하는 크랙방지층을 포함하고, 상기 크랙방지층은 상기 발광구조물의 아래에 배치되고, 상기 발광구조물과 오믹접촉을 이루는 금속재질인 것을 특징으로 한다.

**대 표 도** - 도1

## 명세서

### 청구범위

#### 청구항 1

도전성 기판;

상기 도전성 기판 상에 배치되는 제1전극층;

상기 제1전극층 상에 배치되는 제1 반도체층, 제2 반도체층, 및 상기 제1 반도체층과 상기 제2 반도체층 사이에 위치하는 활성층을 구비하는 발광 구조물;

상기 제2 반도체층과 전기적으로 연결된 제2전극층; 및

상기 발광 구조물의 둘레에 배치되는 크랙방지층을 포함하고,

상기 제1전극층과 상기 제1반도체층 사이에는 반사 인덱스 차이를 줄이는 윈도우층이 더 포함되고,

상기 크랙방지층은,

상기 제1전극층과 동일평면 상에 배치되고,

상기 발광구조물과 오믹접촉을 이루는 금속재질을 포함하고,

상기 크랙방지층은 상기 윈도우층의 하부와 접하는 발광소자.

#### 청구항 2

제1항에 있어서,

상기 크랙방지층은 닫힌 공간을 형성하는 발광소자.

#### 청구항 3

제1항에 있어서,

상기 크랙방지층은, 상기 발광 구조물의 둘레에 배치되는 발광소자.

#### 청구항 4

제1항에 있어서,

상기 크랙방지층의 폭은  $30\mu\text{m}$  내지  $70\mu\text{m}$  인 발광소자.

#### 청구항 5

제1항에 있어서,

상기 크랙방지층은,

Au, Be 및 Au합금 중 적어도 하나 이상을 포함하는 발광소자.

#### 청구항 6

제1항에 있어서,

상기 크랙방지층은 다층 구조를 가지는 발광소자.

#### 청구항 7

삭제

#### 청구항 8

삭제

**청구항 9**

제1항에 있어서,

상기 원도우층은 GaP, GaAsP 및 AlGaAs 중 어느 하나를 포함하는 발광소자.

**청구항 10**

제1항에 있어서,

상기 원도우층에서 상기 크랙방지층과 접하는 영역은 상기 제1반도체층의 극성과 같은 극성의 도편트로 도핑되는 발광소자.

**청구항 11**

제10항에 있어서,

상기 원도우층에서 상기 크랙방지층과 접하는 영역은 p형 도편트에 의해 도핑되는 발광소자.

**청구항 12**

제10항에 있어서,

상기 원도우층에서 상기 크랙방지층과 접하는 영역이 Mg에 의해 도핑되는 경우, 도핑농도는  $5e^{18}/cm^3$  내지  $1e^{18}/cm^3$  인 발광소자.

**청구항 13**

제10항에 있어서,

상기 원도우층에서 상기 크랙방지층과 접하는 영역이 C에 의해 도핑되는 경우, 도핑농도는  $5e^{19}/cm^3$  내지  $1e^{19}/cm^3$  인 발광소자.

**청구항 14**

제1항에 있어서,

상기 제1전극층은,

상기 도전성 기판과 상기 제1반도체층 사이에 배치되는 투명 전극층과, 상기 투명 전극층을 상하로 관통하는 다수개의 금속 컨택부를 구비하는 오믹층을 포함하고,

상기 금속 컨택부는 AuBe를 포함하는 발광소자.

**청구항 15**

제14항에 있어서,

상기 투명전극층의 평면상 면적은 상기 금속 컨택부의 평면상 면적보다 큰 발광소자.

**청구항 16**

제14항에 있어서,

상기 금속 컨택부의 평면상 면적은 상기 투명 전극층의 평면상 면적 대비 10% 내지 25%인 발광소자.

**청구항 17**

제14항에 있어서,

상기 금속 컨택부의 일면은 상기 제1 반도체층과 접하는 발광소자.

### 청구항 18

제14항에 있어서,

서로 인접한 상기 금속 컨택부들 사이의 이격거리는  $3.5 \mu\text{m}$  내지  $5.0 \mu\text{m}$ 인 발광소자.

### 청구항 19

제1항에 있어서,

상기 발광 구조물은

AIGInP 또는 GaInP을 포함하는 발광소자.

### 청구항 20

제1항에 있어서,

상기 발광구조물의 아래에 상기 제2 전극층과 수직 방향으로 적어도 일 영역이 중첩되게 배치되며, 상기 제1 전극층 보다 전기 전도율이 낮은 전류차단층을 더 포함하는 발광소자.

### 청구항 21

제20항에 있어서,

상기 전류차단층은,

산화알루미늄( $\text{Al}_2\text{O}_3$ ), 산화실리콘( $\text{SiO}_2$ ), 질화실리콘( $\text{Si}_3\text{N}_4$ ), 산화티탄( $\text{TiO}_x$ ), 알루미늄산화아연(AZO, aluminum zinc oxide) 및 인듐 아연 산화물(IZO, Indium Zinc Oxide) 중 적어도 하나를 포함하는 발광소자.

### 청구항 22

제1항 내지 제6항 및 제 9항 내지 제21항 중 어느 한 항의 발광소자를 포함하는 발광소자 패키지.

### 청구항 23

제1항 내지 제6항 및 제 9항 내지 제21항 중 어느 한 항의 발광소자를 포함하는 조명 장치.

### 청구항 24

제1항 내지 제6항 및 제 9항 내지 제21항 중 어느 한 항의 발광소자를 포함하는 표시 장치.

## 발명의 설명

### 기술 분야

[0001] 실시 예는 발광소자에 관한 것이다.

### 배경 기술

[0002] 발광소자의 대표적인 예로, LED(Light Emitting Diode; 발광 다이오드)는 화합물 반도체의 특성을 이용해 전기 신호를 적외선, 가시광선 또는 빛의 형태로 변환시키는 소자로, 가정용 가전제품, 리모콘, 전광판, 표시기, 각종 자동화 기기 등에 사용되고, 점등 LED의 사용 영역이 넓어지고 있는 추세이다.

[0003] 보통, 소형화된 LED는 PCB(Printed Circuit Board) 기판에 직접 장착하기 위해서 표면설장소자(Surface Mount Device)형으로 만들어지고 있고, 이에 따라 표시소자로 사용되고 있는 LED 램프도 표면설장소자 형으로 개발되고 있다. 이러한 표면설장소자는 기존의 단순한 점등 램프를 대체할 수 있으며, 이것은 다양한 칼라를 내는 점등표시기용, 문자표시기 및 영상표시기 등으로 사용된다.

[0004] 이와 같이 LED의 사용 영역이 넓어지면서, 생활에 사용되는 전등, 구조 신호용 전등 등에 요구되는 휘도가 높아

지는 바, LED의 발광휘도를 증가시키는 것이 중요하다.

[0005] 또한 발광소자의 전극은 접착력이 우수하고, 전기적 특성이 우수해야 한다.

[0006] 또한, 발광소자의 휘도를 높이고, 사용전압을 줄이기 위한 연구가 진행 중이다. 또한, 웨이퍼를 발광소자 단위로 절단하는 경우, 크랙이 발생되는 문제점이 있다.

### 발명의 내용

#### 해결하려는 과제

[0007] 실시 예는 발광소자의 VF를 낮추고 발광효율을 향상시키며, 발광소자 단위로 절단 시에 크랙을 방지하는 발광소자를 제공한다.

#### 과제의 해결 수단

[0008] 실시 예에 따른 발광소자는, 도전성 기판, 상기 도전성 기판 상에 배치되는 제1전극층, 상기 제1전극층 상에 배치되는 제1 반도체층, 제2 반도체층, 및 상기 제1 반도체층과 상기 제2 반도체층 사이에 위치하는 활성층을 구비하는 발광 구조물, 상기 제2 반도체층과 전기적으로 연결된 제2전극 및 상기 발광 구조물이 칩(chip)단위로 절단될 때 상기 칩들의 경계에 배치되어 크랙을 방지하는 크랙방지층을 포함하고, 상기 크랙방지층은 상기 발광 구조물의 아래에 배치되고, 상기 발광구조물과 오믹접촉을 이루는 금속재질인 것을 특징으로 한다.

### 발명의 효과

[0009] 실시예에 따른 발광소자는 크랙방지층이 발광구조물의 둘레의 하부와 오믹접촉을 이루므로, 발광구조물이 칩단위로 절단될 때, 발광구조물과 제1전극층 및/또는 도전성 기판과의 박리(peeling)를 방지할 수 있는 이점이 있다.

[0010] 또한, 크랙방지층이 칩 단위의 발광구조물의 경계에 위치하여, 발광구조물의 절단 시에 같이 절단되기 때문에, 절단으로 인해 발생되는 크랙(crack)을 방지할 수 있다.

[0011] 또한, 크랙방지층은 발광구조물의 절단 시에 크랙과 박리를 방지하면서도, 발광구조물에 전원을 공급하는 역할을 수행므로, 발광소자의 발광효율을 저하시키지 않는 이점을 가진다.

[0012] 또한, 금속 컨택부가 투명 전극층을 관통하여 배치되어서, 발광구조물과의 오믹접합이 쉽게 되는 이점이 있다.

[0013] 또한, 금속 컨택부가 투명 전극층을 관통하고 있으므로, 발광구조물에 발생하는 열이 도전성 기판으로 쉽게 배출되는 이점이 있다.

[0014] 또한, 금속 컨택부가 발광구조물과 직접 접촉되므로, VF(Voltage Forward)가 감소되는 이점이 있다.

[0015] 금속 컨택부의 면적이 투명 전극층의 면적보다 작아서 금속 반사층에서 반사되는 광의 진행을 방해하는 확률이 줄어들어서 발광효율이 향상되는 이점이 있다.

### 도면의 간단한 설명

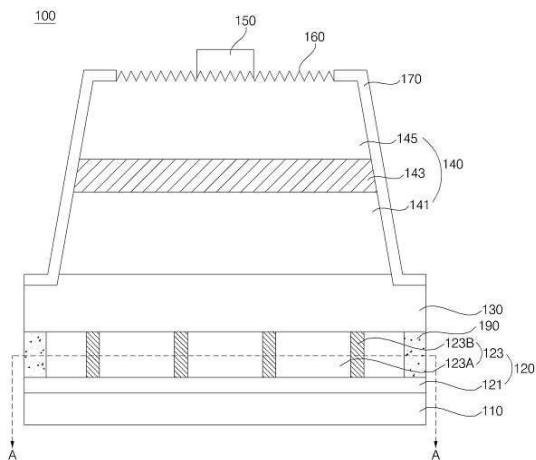

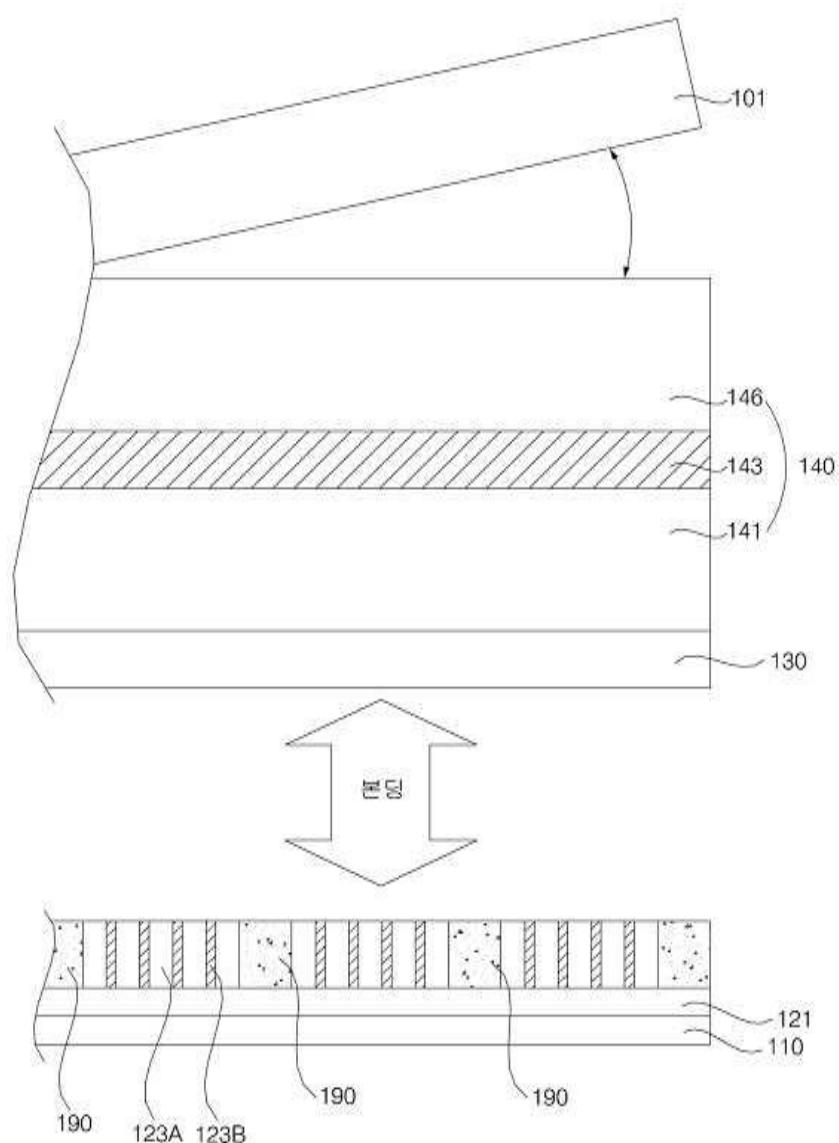

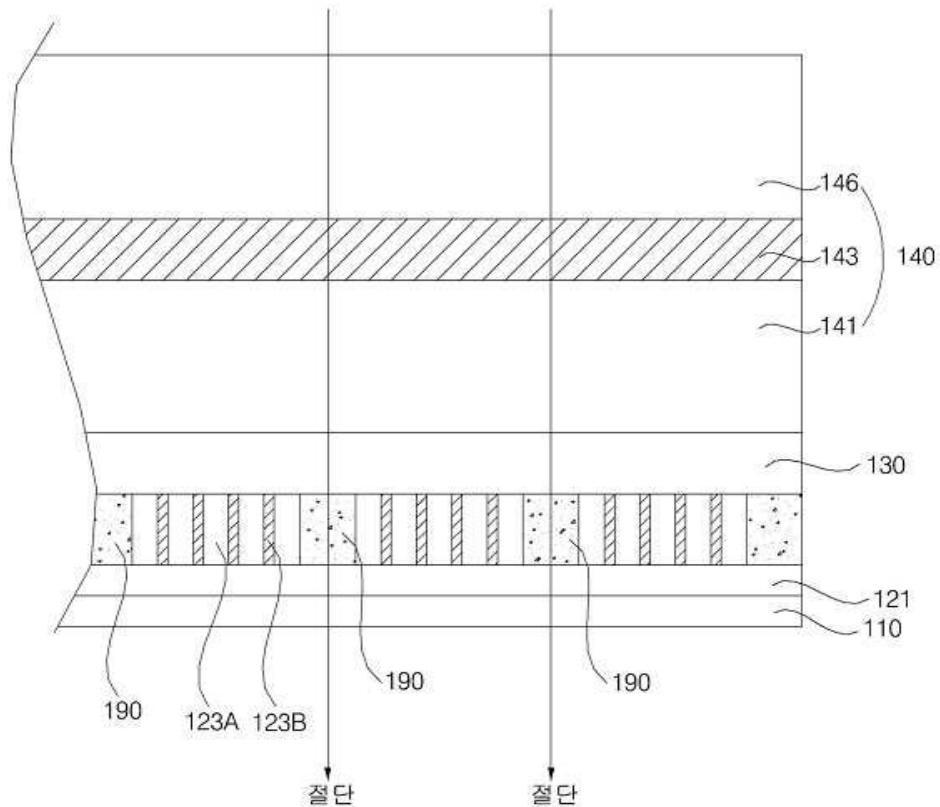

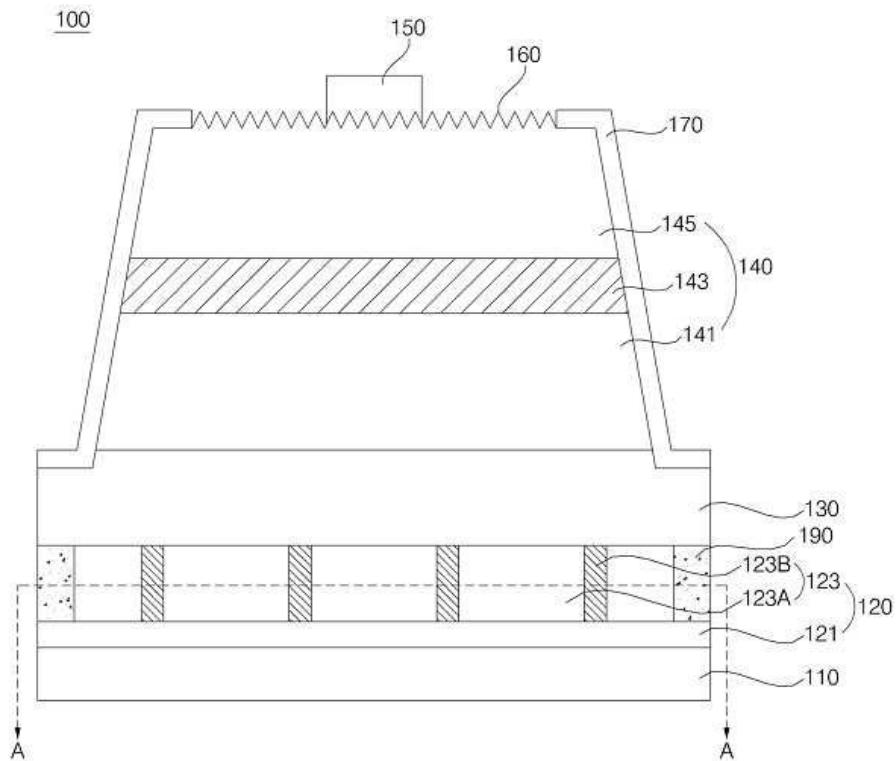

[0016] 도 1은 본 발명의 일 실시예에 따른 발광소자를 나타낸 단면도,

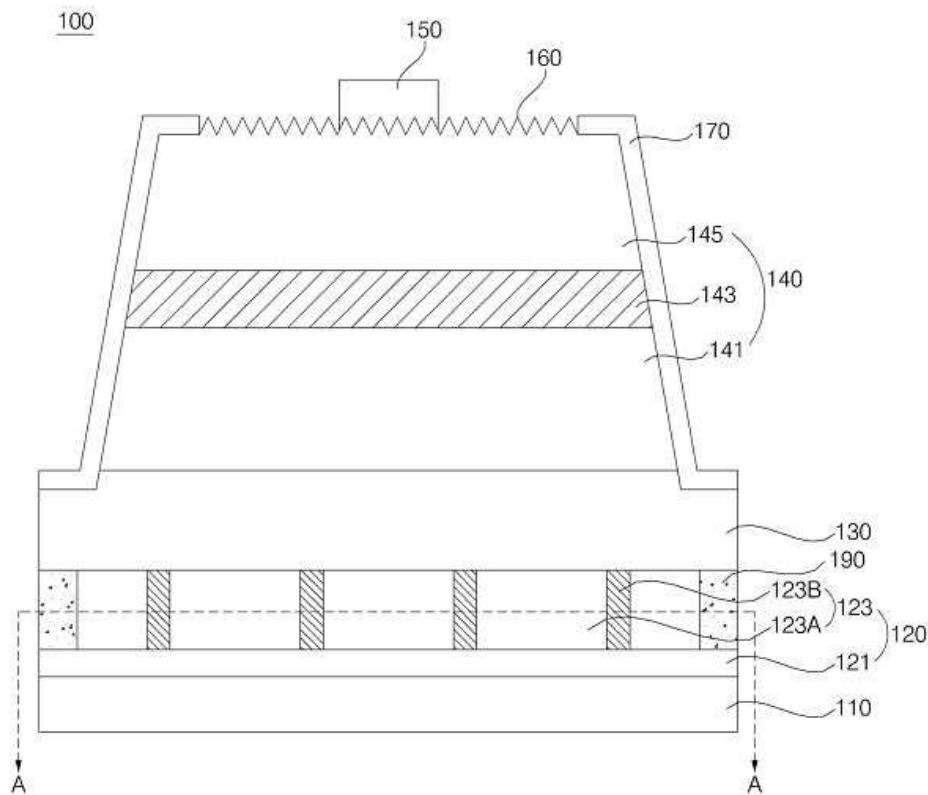

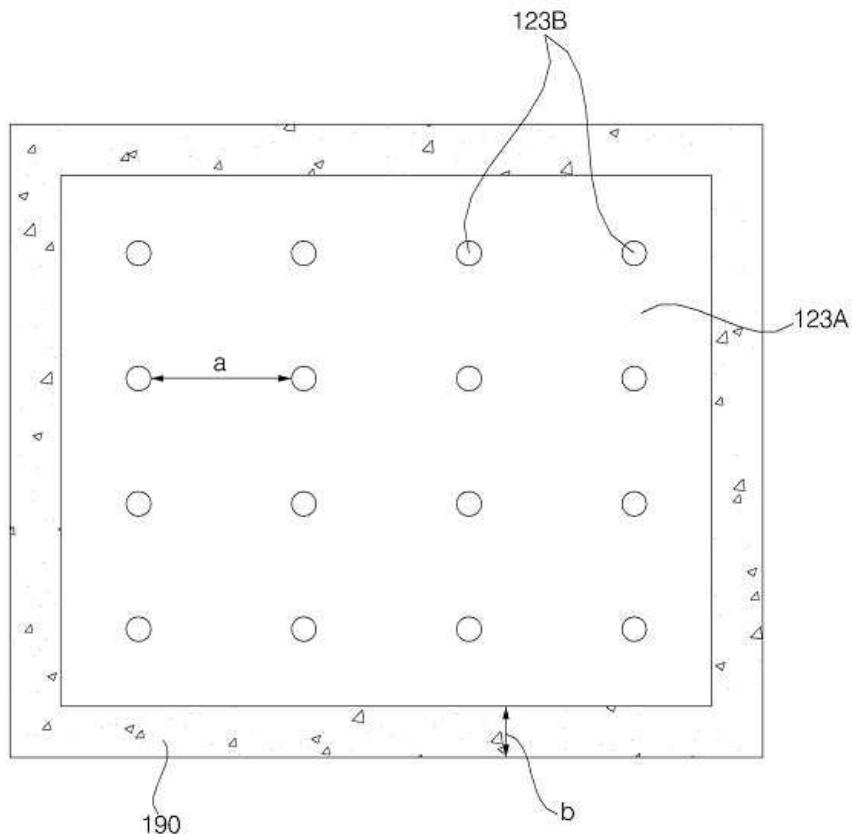

도 2는 도 1의 A-A선을 취한 평면단면도,

도 3은 본 발명의 다른 실시예에 따른 A-A선을 취한 평면단면도,

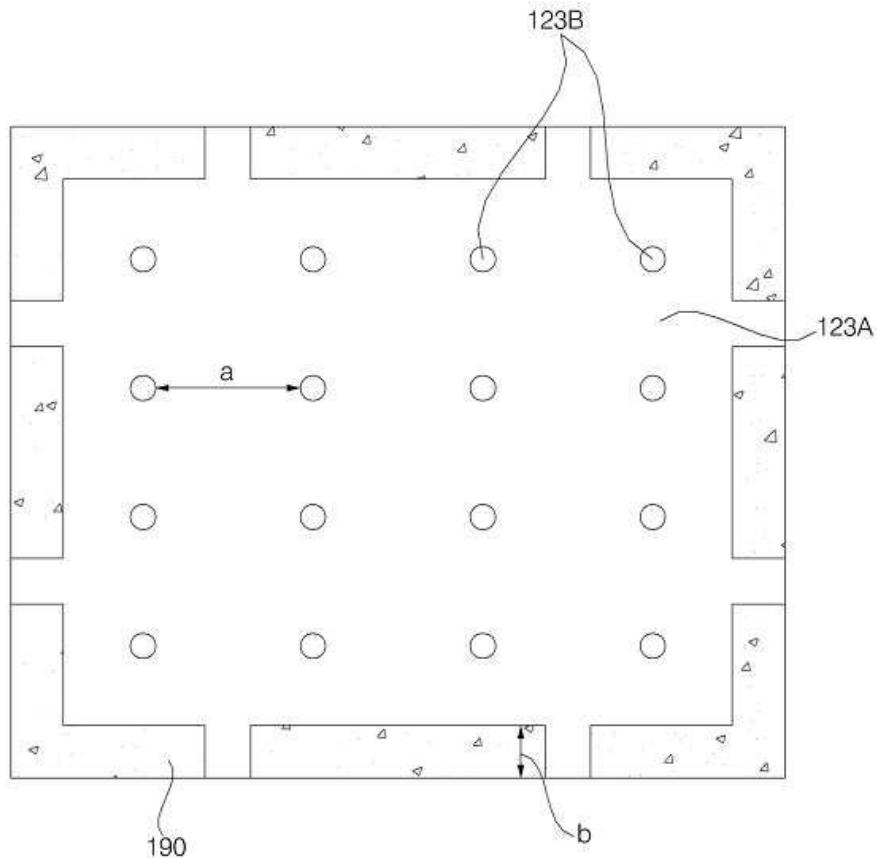

도 4는 본 발명의 또 다른 실시예에 따른 발광소자를 나타낸 단면도,

도 5은 본 발명의 또 다른 실시예에 따른 발광소자를 나타낸 단면도,

도 6 내지 도 10은 실시예에 따른 발광소자를 제조하는 방법을 나타낸 설명도,

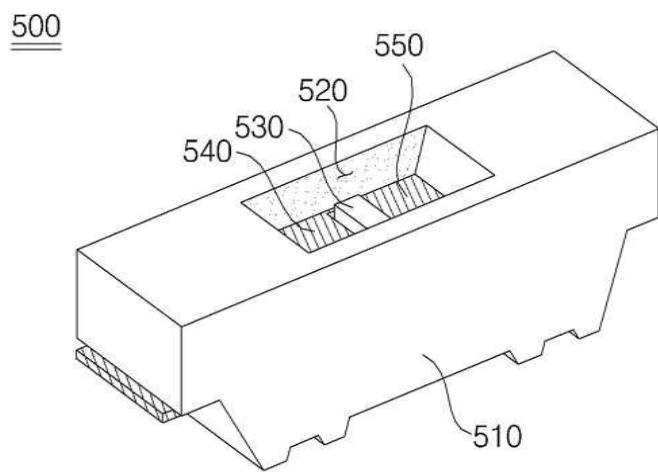

도 11은 실시예에 따른 발광소자를 포함한 발광소자 패키지의 사시도,

도 12은 실시예에 따른 발광소자를 포함한 발광소자 패키지의 단면도,

도 13는 실시예에 따른 발광소자를 포함하는 표시장치의 분해 사시도,

도 14은 도 13의 표시장치의 단면도,

도 15은 실시예에 따른 발광소자를 포함하는 조명 장치의 분해 사시도이다.

### 발명을 실시하기 위한 구체적인 내용

[0017]

본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 수 있으며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하고, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

[0018]

공간적으로 상대적인 용어인 "아래(below)", "아래(beneath)", "하부(lower)", "위(above)", "상부(upper)" 등은 도면에 도시되어 있는 바와 같이 하나의 소자 또는 구성 요소들과 다른 소자 또는 구성 요소들과의 상관관계를 용이하게 기술하기 위해 사용될 수 있다. 공간적으로 상대적인 용어는 도면에 도시되어 있는 방향에 더하여 사용시 또는 동작 시 소자의 서로 다른 방향을 포함하는 용어로 이해되어야 한다. 예를 들면, 도면에 도시되어 있는 소자를 뒤집을 경우, 다른 소자의 "아래(below)" 또는 "아래(beneath)"로 기술된 소자는 다른 소자의 "위(above)"에 놓여질 수 있다. 따라서, 예시적인 용어인 "아래"는 아래와 위의 방향을 모두 포함할 수 있다. 소자는 다른 방향으로도 배향될 수 있고, 이에 따라 공간적으로 상대적인 용어들은 배향에 따라 해석될 수 있다.

[0019]

본 명세서에서 사용된 용어는 실시예들을 설명하기 위한 것이며 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서, 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 명세서에서 사용되는 "포함한다(comprises)" 및/또는 "포함하는(comprising)"은 언급된 구성요소, 단계, 동작 및/또는 소자는 하나 이상의 다른 구성요소, 단계, 동작 및/또는 소자의 존재 또는 추가를 배제하지 않는다.

[0020]

다른 정의가 없다면, 본 명세서에서 사용되는 모든 용어(기술 및 과학적 용어를 포함)는 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 공통적으로 이해될 수 있는 의미로 사용될 수 있을 것이다. 또 일반적으로 사용되는 사전에 정의되어 있는 용어들은 명백하게 특별히 정의되어 있지 않은 한 이상적으로 또는 과도하게 해석되지 않는다.

[0021]

도면에서 각종의 두께나 크기는 설명의 편의 및 명확성을 위하여 과장되거나 생략되거나 또는 개략적으로 도시되었다. 또한 각 구성요소의 크기와 면적은 실제크기나 면적을 전적으로 반영하는 것은 아니다.

[0022]

또한, 실시예에서 발광소자의 구조를 설명하는 과정에서 언급하는 각도와 방향은 도면에 기재된 것을 기준으로 한다. 명세서에서 발광소자를 이루는 구조에 대한 설명에서, 각도에 대한 기준점과 위치관계를 명확히 언급하지 않은 경우, 관련 도면을 참조하도록 한다.

[0023]

도 1은 실시예에 따른 발광소자를 나타낸 단면도, 도 2는 도 1의 A-A선을 취한 평단면도이다.

[0024]

도 1을 참조하면, 실시예의 따른 발광소자(100)은 도전성 기판(110), 도전성 기판(110) 상에 배치되는 제1전극 층(120), 제1전극층(120) 상에 배치되는 제1 반도체층(141), 제2 반도체층(145), 및 제1 반도체층(141)과 제2 반도체층(145) 사이에 위치하는 활성층(143)을 구비하는 발광구조물(140), 제2 반도체층(145)과 전기적으로 연결된 제2전극층(150), 및 발광구조물(140)의 아래에 배치되는 크랙방지층(190)을 포함한다.

[0025]

도전성 기판(110)은 발광구조물(140)을 지지하며, 제2전극층(150)과 함께 발광구조물(140)에 전원을 제공할 수 있다. 도전성 기판(110)은 열전도성이 우수한 물질 또는 전도성 물질로 형성될 수 있으며, 예를 들어, 금(Au), 니켈(Ni), 텉스텐(W), 몰리브덴(Mo), 구리(Cu), 알루미늄(Al), 탄탈(Ta), 은(Ag), 백금(Pt), 크롬(Cr), Si, Ge, GaAs, ZnO, GaN, Ga<sub>2</sub>O<sub>3</sub> 또는 SiC, SiGe, CuW 중에서 선택된 어느 하나로 형성하거나 둘 이상의 합금으로 형성할 수 있으며, 서로 다른 둘 이상의 물질을 적층하여 형성할 수 있다. 즉 도전성 기판(110)은 캐리어 웨이퍼로 구현될 수도 있다.

[0026]

이와 같은 도전성 기판(110)은 발광소자(100)에서 발생하는 열의 방출을 용이하게 하여 발광소자(100)의 열적 안정성을 향상시킬 수 있다.

[0027]

실시 예에서, 도전성 기판(110)은 전도성을 갖는 것으로 설명하나, 전도성을 갖지 않을 수도 있으며, 이에 한정

을 두지 않는다.

[0028] 도전성 기판(110) 상에는 발광구조물(140)에 전원을 공급하는 제1전극층(120)을 포함한다. 제1전극층(120)에 대한 자세한 설명은 후술한다.

[0029] 제1전극층(120) 상에는 제1전극층(120)과 발광구조물(140) 사이의 반사를 차이를 줄이는 원도우층(130)이 더 포함될 수 있다.

[0030] 원도우층(130)은 발광구조물(140)과 제1전극층(120)의 반사를 차이를 줄이므로써, 광추출 효율을 증가시킨다.

[0031] 원도우층(130)은 GaP, GaAsP 및 AlGaAs 중 어느 하나를 포함할 수 있다.

[0032] 발광구조물(140)은 제1 반도체층(141)과, 제2 반도체층(145)과, 제1 반도체층(141)과 제2 반도체층(145) 사이의 활성층(143)으로 이루어진다.

[0033] 제2 반도체층(145)은 n형 반도체층으로 구현될 수 있으며, n형 반도체층은 예컨대,  $In_xAl_yGa_{1-x-y}N$  ( $0 \leq x \leq 1$ ,  $0 \leq y \leq 1$ ,  $0 \leq x+y \leq 1$ )의 조성식을 갖는 반도체 재료, 예를 들어 GaN, AlN, AlGaN, InGaN, InN, InAlGaN, AlInN 등에서 선택될 수 있으며, 예를 들어, Si, Ge, Sn, Se, Te와 같은 n형 도편트가 도핑될 수 있다. 또한, 제2 반도체층(145)은  $(Al_xGa_{1-x})_{0.5}In_{0.5}P$ 의 조성식을 갖는 반도체 재료에서 선택될 수도 있다.

[0034] 한편, 제2 반도체층(145)상에는 제2 반도체층(145)과 전기적으로 연결된 제2전극층(150)이 배치될 수 있으며, 제2전극층(150)은 적어도 하나의 패드 또는/및 소정 패턴을 갖는 전극을 포함할 수 있다. 제2전극층(150)은 제2 반도체층(145)의 상면 중 센터 영역, 외측 영역 또는 모서리 영역에 배치될 수 있으며, 이에 대해 한정하지는 않는다. 제2전극층(150)은 제2 반도체층(145)의 위가 아닌 다른 영역에 배치될 수 있으며, 이에 대해 한정하지는 않는다.

[0035] 제2전극층(150)은 전도성 물질, 예를 들어 In, Co, Si, Ge, Au, Pd, Pt, Ru, Re, Mg, Zn, Hf, Ta, Rh, Ir, W, Ti, Ag, Cr, Mo, Nb, Al, Ni, Cu, 및 WTi 중에서 선택된 금속 또는 합금을 이용하여 단층 또는 다층으로 형성될 수 있다.

[0036] 제2전극층(150)이 형성되지 않은 제2 반도체층(145)의 표면 일부 영역 또는 전체 영역에 대해 소정의 식각 방법으로 광 추출효율을 향상시키기 위한 요철 패턴(160)을 형성해 줄 수 있다.

[0037] 여기서, 제2전극층(150)은 요철 패턴(160)이 형성되지 않는 평坦한 면에 형성된 것으로 설명하나, 요철 패턴(160)이 형성된 상부면에 형성될 수 있으며 이에 한정을 두지 않는다.

[0038] 요철 패턴(160)은 제2 반도체층(145)의 상면의 적어도 일 영역에 대해 에칭을 수행함으로써 형성될 수 있으며 이에 대해 한정하지 않는다. 에칭 과정은 습식 또는/및 건식 에칭 공정을 포함하며, 에칭 과정을 거칠에 따라서, 제2 반도체층(145)의 상면은 요철 패턴(160)을 포함할 수 있다. 요철 패턴(160)은 랜덤한 크기로 불규칙하게 형성될 수 있으며, 이에 대해 한정하지는 않는다. 요철 패턴(160)은 평탄하지 않는 상면으로서, 텍스처(texture) 패턴, 요철 패턴, 평탄하지 않는 패턴(uneven pattern) 중 적어도 하나를 포함할 수 있다.

[0039] 요철 패턴(160)은 측 단면이 원기둥, 다각기둥, 원뿔, 다각뿔, 원뿔대, 다각뿔대 등 다양한 형상을 갖도록 형성될 수 있으며, 뾰 형상을 포함한다.

[0040] 한편, 요철 패턴(160)은 PEC(photo electro chemical) 등의 방법으로 형성될 수 있으며, 이에 한정하지 아니한다. 요철 패턴(160)은 제2 반도체층(145)의 상부면에 형성됨에 따라서 활성층(143)으로부터 생성된 빛이 제2 반도체층(145)의 상부면으로부터 전반사되어 재흡수되거나 산란되는 것이 방지될 수 있으므로, 발광소자(100)의 광 추출 효율의 향상에 기여할 수 있다.

[0041] 제2 반도체층(145)의 아래에는 활성층(143)이 형성될 수 있다. 활성층(143)은 전자와 정공이 재결합되는 영역으로, 전자와 정공이 재결합함에 따라 낮은 에너지 준위로 천이하며, 그에 상응하는 파장을 가지는 빛을 생성할 수 있다.

[0042] 활성층(143)은 예를 들어,  $In_xAl_yGa_{1-x-y}N$  ( $0 \leq x \leq 1$ ,  $0 \leq y \leq 1$ ,  $0 \leq x+y \leq 1$ )의 조성식을 가지는 반도체 재료를 포함하여 형성할 수 있으며, 단일 양자 우물 구조 또는 다중 양자 우물 구조(MQW: Multi Quantum Well)로 형성될 수 있다. 또한, 활성층(143)은  $(Al_xGa_{1-x})_{0.5}In_{0.5}P$ 의 조성식을 갖는 반도체 재료에서 선택될 수도 있다.

[0043] 따라서, 더 많은 전자가 양자우물층의 낮은 에너지 준위로 모이게 되며, 그 결과 전자와 정공의 재결합 확률이

증가되어 발광효과가 향상될 수 있다. 또한, 양자선(Quantum wire)구조 또는 양자점(Quantum dot)구조를 포함할 수도 있다.

[0044] 활성층(143) 아래에는 제1 반도체층(141)이 형성될 수 있다. 제1 반도체층(141)은 p형 반도체층으로 구현되어, 활성층(143)에 정공을 주입할 수 있다. 예를 들어 p형 반도체층은  $In_xAl_yGa_{1-x-y}N$  ( $0 \leq x \leq 1$ ,  $0 \leq y \leq 1$ ,  $0 \leq x+y \leq 1$ )의 조성식을 갖는 반도체 재료, 예를 들어 GaN, AlN, AlGaN, InGaN, InN, InAlGaN, AlInN 등에서 선택될 수 있으며, Mg, Zn, Ca, Sr, Ba 등의 p형 도편트가 도핑될 수 있다. 또한, 제1 반도체층(141)은  $(Al_xGa_{1-x})_{0.5}In_{0.5}P$ 의 조성식을 갖는 반도체 재료에서 선택될 수도 있다.

[0045] 또한 제1 반도체층(141)의 아래에는 제3 반도체층(미도시)을 형성할 수도 있다. 여기서 제3 반도체층은 제2 반도체층과 극성이 반대인 반도체층으로 구현될 수 있다.

[0046] 한편, 상술한 제2 반도체층(145), 활성층(143) 및 제1 반도체층(141)은 유기금속 화학 증착법(MOCVD; Metal Organic Chemical Vapor Deposition), 화학 증착법(CVD; Chemical Vapor Deposition), 플라즈마 화학 증착법(PECVD; Plasma-Enhanced Chemical Vapor Deposition), 분자선 성장법(MBE; Molecular Beam Epitaxy), 수소화물 기상 성장법(HVPE; Hydride Vapor Phase Epitaxy), 스퍼터링(Sputtering) 등의 방법을 이용하여 형성될 수 있으며, 이에 대해 한정하지는 않는다.

[0047] 또한, 상술한 바와는 달리 실시예에서 제2 반도체층(145)이 p형 반도체층으로 구현되고, 제1 반도체층(141)이 n형 반도체층으로 구현될 수 있으며, 이에 한정하지 않는다. 이에 따라 발광구조물(140)은 N-P 접합, P-N 접합, N-P-N 접합 및 P-N-P 접합 구조 중 적어도 하나를 포함할 수 있다.

[0048] 또한, 발광구조물(140)의 외주면 중 일부 영역 또는 전체 영역은 외부의 충격 등으로부터 보호하고, 전기적 쇼트를 방지할 수 있도록 패시베이션(170)이 형성 될 수도 있다.

[0049] 도 1 및 도 2를 참고하면, 제1전극층(120)은 금속과 투광성 전도층을 선택적으로 사용할 수 있으며, 발광구조물(140)에 전원을 제공한다. 제1전극층(120)은 전도성 재질을 포함하여 형성될 수 있다. 예를 들면, 니켈(Ni), 백금(Pt), 루테늄(Ru), 아리듐(Ir), 로듐(Rh), 탄탈(Ta), 몰리브덴(Mo), 티탄(Ti), 은(Ag), 텉스텐(W), 구리(Cu), 크롬(Cr), 팔라듐(Pd), 바나듐(V), 코발트(Co), 니오브(Nb), 지르코늄(Zr), 산화인듐주석(ITO, Indium Tin Oxide), 알루미늄산화아연(AZO, aluminum zinc oxide), 인듐 아연 산화물(IZO, Indium Zinc Oxide), IZTO(indium zinc tin oxide), IAZO(indium aluminum zinc oxide), IGZO(indium gallium zinc oxide), IGTO(indium gallium tin oxide),ATO(antimony tin oxide), GZO(gallium zinc oxide), IrO<sub>x</sub>, RuO<sub>x</sub>, RuO<sub>x</sub>/ITO, Ni/IrO<sub>x</sub>/Au, 또는 Ni/IrO<sub>x</sub>/Au/ITO 중 적어도 하나로 형성될 수 있다. 다만 이에 한정되는 것은 아니다.

[0050] 제1전극층(120)은 오믹층(123)(ohmic layer) 및 금속 반사층(125)(reflective layer) 중 적어도 한 층을 포함할 수 있다. 또한, 제1전극층(120)은 오믹층(123)(ohmic layer), 금속 반사층(125)(reflective layer) 및 금속 접착층(121) 중 적어도 한 층을 포함할 수 있다.

[0051] 예컨대, 제1전극층(120)은 금속 접착층(121) 상에 금속 반사층(125) 및 오믹층(123)이 순차로 적층된 형태일 수 있다. 도 1에서는 금속 접착층(121) 상에 오믹층(123)이 적층된 형태를 도시하고 있다.

[0052] 오믹층(123)은 도전성 기판(110)과 발광구조물(140) 사이에 배치되는 투명 전극층(123A)과, 투명 전극층(123A)을 상하로 관통하는 다수개의 금속 컨택부(123B)를 구비할 수 있다.

[0053] 투명 전극층(123A)은 도전성 기판(110) 또는 금속 반사층(125)에서 반사되는 빛이 투과되면서 도전성을 가지는 재질일 수 있다. 예를 들면, 투명 전극층(123A)은  $In_2O_3$ ,  $SnO_2$ ,  $ZnO$ , ITO, CTO,  $CuAlO_2$ ,  $CuGaO_2$  및  $SrCu_2O_2$  중 적어도 하나를 포함할 수 있다.

[0054] 금속 컨택부(123B)는 투명 전극층(123A)을 상하로 관통하여 다수 개가 배치된다. 다수개의 금속 컨택부(123B)들은 서로 규칙적으로 이격되어 배치된다. 금속 컨택부(123B)는 발광구조물(140)과 오믹컨택이 되게 한다.

[0055] 또한, 금속 컨택부(123B)의 적어도 일면은 발광구조물(140)의 제1 반도체층(141)에 접하고, 다른 일면은 도전성 기판(110)과 접할 수 있다.

- [0056] 금속 컨택부(123B)는 AuBe를 포함한다.

- [0057] 금속 컨택부(123B)가 투명 전극층(123A)을 관통하여 배치되는 경우, 발광구조물(140)과의 오믹접합이 쉽게 되는 이점이 있다. 또한, 금속 컨택부(123B)가 투명 전극층(123A)을 관통하고 있으므로, 발광구조물(140)에 발생하는 열이 도전성 기판(110)으로 쉽게 배출되는 이점이 있다.

- [0058] 또한, 금속 컨택부(123B)가 발광구조물(140)과 직접 접촉되므로, VF(Voltage Forward)가 감소되는 이점이 있다. 특히, 금속 컨택부(123B)가 투명 전극층(123A)을 관통하지 않는 경우와 비교하면 대략 10% 정도의 사용전압이 내려가는 효과를 가진다. 이는 투명 전극층(123A)은 금속 컨택부(123B) 보다 전도성이 떨어지기 때문이다.

- [0059] 특히, 도 2를 참고하면, 투명 전극층(123A)의 평면상 면적은 금속 컨택부(123B)의 평면상 면적보다 큰 것이 바람직하다. 더욱 바람직하게는 금속 컨택부(123B)의 평면상 면적은 투명 전극층(123A)의 평면상 면적 대비 10% 내지 25%일 수 있다. 금속 컨택부(123B)의 평면상 면적은 투명 전극층(123A)의 평면상 면적 대비 10% 보다 작은 경우, 발광구조물(140)과 제1전극층(120)의 오믹접촉이 어렵고, 금속 컨택부(123B)의 평면상 면적은 투명 전극층(123A)의 평면상 면적 대비 25%보다 큰 경우, 광투과율이 떨어지는 금속 컨택부(123B) 때문에 발광소자(100)의 광효율이 저하되는 문제점이 있다.

- [0060] 금속 컨택부(123B)의 평면상 면적이 투명 전극층(123A)의 평면상 면적 대비 10% 내지 25%일려면, 예를 들면, 서로 인접한 금속 컨택부(123B) 사이의 이격거리는  $35\mu\text{m}$  내지  $50\mu\text{m}$ 이고, 금속 컨택부(123B)의 폭은  $10\mu\text{m}$  내지  $20\mu\text{m}$ 인 것이 바람직하다.

- [0061] 금속 컨택부(123B)은 형상은 제한이 없지만, 막대형상을 가질 수 있다, 바람직하게는 원기둥 또는 다각기둥의 형상을 가진다.

- [0062] 제1전극층(120)은 도 1에서 도시된 바와 같이 평평할 수 있지만, 이에 한정되지 않고 단차를 가질 수 있다.

- [0063] 제1전극층(120)은 금속 접합층(121)을 더 포함할 수 있다.

- [0064] 금속 접합층(121)은 오믹층(123)의 아래에 형성되어, 층들간의 접착력을 강화시켜 줄 수 있다. 금속 접합층(121)은 하부 물질과의 접착력이 우수한 물질을 이용하여 형성될 수 있다. 예를 들어, PbSn 합금, AuGe 합금, AuBe 합금, AuSn 합금, Sn, In 및 PdIn 합금 중 어느 하나를 포함할 수 있다. 또한,

- [0065] 금속 접합층(121) 상부에 확산 방지막(미도시)을 더 형성할 수 있다. 확산 방지막은 도전성 기판(110) 및 금속 접합층(121)을 이루는 물질이 발광구조물(140)로 확산되는 것을 방지할 수 있다. 확산 방지막은 금속의 확산을 방지하는 물질로 형성될 수 있으며, 예를 들어, 백금(Pt), 팔라듐(Pd), 텅스텐(W), 니켈(Ni), 루테늄(Ru), 몰리브덴(Mo), 이리듐(Ir), 로듐(Rh), 탄탈(Ta), 하프늄(Hf), 지르코늄(Zr), 니오브(Nb), 바나듐(V) 중 적어도 하나 또는 둘 이상의 합금을 이용할 수 있다. 다만 이에 한정되는 것은 아니다. 그리고, 금속 접합층(121)은 단층 또는 다층 구조로 형성될 수 있다.

- [0066] 크랙방지층(190)은, 발광구조물(140)이 칩(chip)단위로 절단될 때 칩들의 경계에 배치되어 크랙을 방지한다. 여기서, 칩은 발광구조물(140)이 적층된 웨이퍼(미도시)가 각각의 발광소자로 분리된 것을 의미한다. 이에 대한 자세한 설명은 제조방법에서 후술한다.

- [0067] 크랙방지층(190)은 발광구조물(140)의 일 영역과 접하게 배치되고, 바람직하게는 발광구조물(140)의 하부 둘레에 배치된다. 크랙방지층(190)의 평면 형상은 닫힌 공간을 형성하는 링 형상, 루프 형상, 프레임 형상, 메시(mesh) 형상 등으로 형성될 수 있으며, 그 닫힌 공간의 크기는 발광소자의 크기에 대응된다. 여기서, 닫힌 공간이란, 도 2의 평면에서 닫힌 공간을 의미한다.

- [0068] 크랙방지층(190)의 폭(b)은 제한이 없지만, 너무 좁으면, 발광구조물(140)과의 박리를 방지하기 어렵고, 너무 넓으면, 발광소자의 광효율을 저하시키므로,  $30\mu\text{m}$  내지  $70\mu\text{m}$  인 것이 바람직하다.

- [0069] 또한, 크랙방지층(190)은 발광구조물(140)의 하부와 접촉하며 제1전극층(120)과 동일평면 상에 배치될 수 있다. 즉, 발광구조물(140)에 전원을 공급하는 역할과, 발광구조물(140)의 절단 시에 크랙을 방지하는 역할을 수행한다. 여기서, 동일평면은 수학적 의미의 완전한 동일평면을 의미하는 것은 아니고, 어느 정도 오차를 포함하는 범위에서 일견하기에 동일평면으로 보이는 정도를 의미한다. 즉, 크랙방지층(190)은 제1전극층(120)의 외측에 배치된다.

- [0070] 크랙방지층(190)은 발광구조물(140)의 하부와 오믹접촉을 이를 수 있다. 예를 들면, 발광구조물(140)의 하부가 제1 반도체층(141)인 경우, 크랙방지층(190)은 제1 반도체층(141)과 오믹접촉을 하고, 발광구조물(140)의 하부

가 윈도우층(130)인 경우, 크랙방지층(190)은 윈도우층(130)이 하부와 오믹접촉을 하게 된다.

[0071] 크랙방지층(190)이 발광구조물(140)의 둘레의 하부와 오믹접촉을 이루면, 발광구조물(140)이 침단위로 절단될 때, 발광구조물(140)과 제1전극층(120) 및/또는 도전성 기판(110)과의 박리(peeling)를 방지할 수 있다. 또한, 크랙방지층(190)이 침 단위의 발광구조물(140)의 경계에 위치하여, 발광구조물(140)의 절단 시에 같이 절단되기 때문에, 절단으로 인해 발생되는 크랙(crack)을 방지할 수 있다.

[0072] 크랙방지층(190)은 도전성을 가지는 금속재질을 포함할 수 있고, 예를 들면, Au, AuBe 및 Au합금 중 적어도 하나 이상을 포함할 수 있다.

[0073] 또한, 크랙방지층(190)은 단층 또는 다층구조를 가질 수 있다. 예를 들면, 크랙방지층(190)은 Au, Au/AuBe, Au/AuBe/ Au 의 구조를 가질 수 있다. 다만, 이에 한정되는 것은 아니다.

[0074] 크랙방지층(190)이 Au 또는 Au합금으로 이루어지는 경우, 발광구조물(140)의 절단 시에 크랙과 박리를 방지하면서도, 발광구조물(140)에 전원을 공급하는 역할을 수행하므로, 발광소자의 발광효율을 저하시키지 않는 이점을 가진다.

[0075] 한편, 발광구조물(140)이 윈도우층(130)을 더 포함하는 경우, 윈도우층(130)에서 크랙방지층(190)과 접하는 영역은 제1 반도체층(141)의 극성과 같은 극성의 도편트로 도핑된다. 여기서는 제1 반도체층(141)은 p형 도편트에 의해 도핑되는 것을 전제로 하므로, 윈도우층(130)에서 크랙방지층(190)과 접하는 영역은 p형 도편트에 의해 도핑되는 것을 기준으로 설명한다.

[0076] 윈도우층(130)이 도핑되면, 광의 투과도는 감소하지만, 크랙방지층(190)과의 오믹접합을 이루는 능력은 상승되게 된다. 따라서, 윈도우층(130)에서 크랙방지층(190)과 접하는 영역이 윈도우층(130) 내에서 크랙방지층(190)과 접하는 영역에만 형성되므로, 윈도우층(130)과 크랙방지층(190)은 오믹접촉되게 된다. 또한, 윈도우층(130)에서 크랙방지층(190)과 접하는 영역이 줄어들어서, 광투과성은 크게 떨어지지 않게 된다. 결과적으로, 윈도우층(130)의 광투과률을 크게 저하시키지 않으면서도 윈도우층(130)과 크랙방지층(190)의 오믹접촉을 이를 수 있게 해준다.

[0077] 또한, 윈도우층(130)과 크랙방지층(190)이 오믹접촉되어서 발광소자(100)의 사용전압은 낮아지고, 윈도우층(130)의 광투과성이 많이 저하되지 않아서 발광효율은 크게 저하되지 않고, 발광구조물(140)의 크랙은 방지하는 이점이 있다.

[0078] 윈도우층(130)에서 크랙방지층(190)과 접하는 영역에 도핑되는 p형 도편트는, Mg, Zn, Ca, Sr, Ba 및 C 중 어느 하나를 포함할 수 있다.

[0079] 윈도우층(130)에서 크랙방지층(190)과 접하는 영역이 너무 높은 농도로 도핑되면, 광투과율이 현저하게 저하되고 너무 낮은 농도로 도핑되면 윈도우층(130)과 크랙방지층(190)의 오믹접촉이 어려울 수 있다. 따라서, 윈도우층(130)에서 크랙방지층(190)과 접하는 영역이 Mg에 의해 도핑되는 경우, 도핑농도는  $5e^{18}/cm^3$  내지  $1e^{18}/cm^3$  이고, C에 의해 도핑되는 경우, 도핑농도는  $5e^{19}/cm^3$  내지  $1e^{19}/cm^3$  인 것이 바람직하다.

[0080] 도 3은 본 발명의 다른 실시예에 따른 A-A선을 취한 평단면도이다.

[0081] 실시예에 따른 발광소자(100)는 도 2의 실시예와 크랙방지층(190)의 배치에 차이점이 존재한다.

[0082] 도 3을 참조하면, 크랙방지층(190)은 침들의 경계에 연속적 또는 불연속적으로 배치될 수 있다. 도 3에는 크랙방지층(190)이 침들의 경계인 발광구조물(140)의 둘레에 불연속적으로 배치될 수 있다.

[0083] 불연속적으로 배치된 크랙방지층(190)은 발광소자의 크랙을 방지하면서, 제조비용을 절감할 수 있다.

[0084] 도 4는 본 발명의 다른 일 실시예에 따른 발광소자를 나타낸 단면도이다.

[0085] 도 5를 참조하면, 실시예에 따른 발광소자(100A)는 도 1의 실시예와 비교하면, 금속 반사층(125), 및 전류차단층(180)을 더 포함한다.

[0086] 제1전극층(120)은 금속 반사층(125)을 더 포함한다. 금속 반사층(125)은 오믹층(123)의 아래에 형성되어 활성층(143)에서 반사되는 광 중 도전성 기판(110)으로 향하는 광을 발광구조물(140)의 상부로 반사시킨다.

[0087] 금속 반사층(125)은 반사특성이 우수한 물질, 예를 들어 Ag, Ni, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt, Au, Hf 및 이들의 선택적인 조합으로 구성된 물질 중에서 형성되거나, 금속 물질과 IZO, IZTO, IAZO, IGZO, IGTO, AZO,

ATO 등의 투광성 전도성 물질을 이용하여 다층으로 형성할 수 있다. 또한 반사층(미도시)은 IZO/Ni, AZO/Ag, IZO/Ag/Ni, AZO/Ag/Ni 등으로 적층할 수 있다.

[0088] 전류차단층(180)은 발광구조물(140)의 아래에 제2전극층(150)과 수직 방향으로 적어도 일영역이 중첩되게 배치되며, 오믹층(123) 및 금속 반사층(125) 보다 전기 전도율이 낮을 수 있다. 전류차단층(180)은 예를 들면, 산화알루미늄( $Al_2O_3$ ), 산화실리콘( $SiO_2$ ), 질화실리콘( $Si_3N_4$ ), 산화티탄( $TiO_x$ ), 산화인듐주석(ITO, Indium Tin Oxide), 알루미늄산화아연(AZO, aluminum zinc oxide) 및 인듐 아연 산화물(IZO, Indium Zinc Oxide) 중 적어도 하나를 포함할 수 있다. 다만, 이에 한정되는 것은 아니다.

[0089] 전류차단층(180)은 고 전류 인가 시 제2 반도체층(145)으로부터 활성층(143)으로 주입되는 전자가 활성층(143)에서 재결합되지 않고, 제1전극층(120)으로 흐르는 현상을 방지하는 전자 차단층(Electron blocking layer)일 수 있다. 전류차단층(180)은 활성층(143) 보다 상대적으로 큰 밴드갭을 가짐으로써, 제2 반도체층(145)으로부터 주입된 전자가 활성층(143)에서 재결합되지 않고 제1 반도체층(141)으로 주입되는 현상을 방지할 수 있다. 이에 따라 활성층(143)에서 전자와 정공의 재결합 확률을 높이고 누설전류를 방지할 수 있다.

[0090] 도 5는 본 발명의 또 다른 실시예에 따른 발광소자를 나타낸 단면도이다.

[0091] 실시예에 따른 발광소자(100B)는 도 1의 실시예와 원도우층(130)의 존재여부에 존재한다.

[0092] 도 5를 참조하면, 실시예에 따른 발광소자(100B)는 원도우층(130)이 생략되고, 크랙방지층(190)이 발광구조물(140)의 제1반도체층(141)과 접하게 배치될 수 있다.

[0093] 도 6 내지 도 10은 도 1의 발광소자의 제조공정을 나타낸 순서도이다.

[0094] 실시예에 따른 발광소자 제조방법은 다음과 같다.

[0095] 도 6을 참조하면, 성장기판(101) 상에 순차적으로 제2 반도체층(145), 활성층(143) 및 제1 반도체층(141)을 포함하는 발광구조물(140)이 적층된다.

[0096] 발광구조물(140) 상에는 원도우층(130)이 적층될 수 있다.

[0097] 성장기판(101)은 사파이어 기판( $Al_2O_3$ ), GaN, SiC, ZnO, Si, GaP, InP, 그리고 GaAs 등으로 이루어진 군에서 선택될 수 있으며, 도면에 나타내지는 않았으나 성장기판(101)과 발광구조물(140) 사이에는 벼퍼층(미도시)이 형성될 수 있다.

[0098] 벼퍼층(미도시)은 3족과 5족 원소가 결합된 형태이거나 GaN, InN, AlN, InGaN, AlGaN, InAlGaN, AlInN 중에서 어느 하나로 이루어질 수 있으며, 도편트가 도핑될 수도 있다.

[0099] 이러한 성장기판(101) 또는 벼퍼층(미도시) 위에는 언도프드 반도체(미도시)층이 형성될 수 있으며, 벼퍼층(미도시)과 언도프드 반도체층(미도시) 중 어느 한 층 또는 두 층 모두 형성하거나 형성하지 않을 수도 있으며, 이러한 구조에 대해 한정되지는 않는다.

[0100] 도 7를 참조하면, 도전성 기판(110)을 준비하고, 도전성 기판(110) 상에 제1전극층(120)을 본딩한다.

[0101] 제1전극층(120)이 형성되는 방법에는 제한이 없지만, 예를 들면, 투명 전극층(123A) 상에는 일정 패턴을 가지는 PR(Photo Resist)(미도시)이 배치될 수 있다. 이때 PR은 전류확산 및 광추출 효율을 고려한 금속 컨택부(123B)에 대응하여 일정한 패턴으로 배치될 수 있다.

[0102] 이후, 투명 전극층(123A) 중 PR이 배치된 영역과 수직적으로 중첩된 영역 이외의 영역이 제거된다. 이때, 제거되는 단면은 직사각형을 이를 수고 있고, 곡률을 가질 수도 있으며 단차를 가질 수도 있다. 이에 대해 한정하지는 않는다. 제거방법은 습식식각(wet etching), 건식식각(dry etching) 또는 LLO(laser lift off) 방법이 사용될 수 있으나, 이에 한정되지는 않는다.

[0103] 이후, 식각된 영역에 금속 컨택부(123B)가 형성될 수 있다.

[0104] 또한, 제1전극층(120)에는 1침단위의 발광소자의 경계에 대응되게 크랙방지층(190)이 형성된다. 크랙방지층(190)의 형성방법은 금속 컨택부(123B)의 형성방법과 동일하다.

[0105] 도 8을 참고하면, 제2 반도체층(145) 상에 배치된 성장기판(101)을 분리시킬 수 있다.

[0106] 이때, 성장기판(101)은 물리적 또는/및 화학적 방법으로 제거할 수 있으며, 물리적 방법은 일 예로 LLO(laser

lift off) 방식으로 제거할 수 있다.

[0107] 또한, 도전성 기판(110)과 제1전극층(120)이 결합된 것과 발광구조물(140)을 본딩한다.

[0108] 도 9을 참고하면, 발광구조물(140)과 도전성 기판(110)의 결합체를 1침단위로 절단한다. 절단방법에는 제한이 없고, 레이저 도는 블레이드를 사용할 수 있다.

[0109] 도 10을 참조하면, 발광구조물(140)의 외주면 일부 또는 전체 영역에 패시베이션(170)이 형성될 수 있다.

[0110] 그리고, 발광구조물(140)의 제2 반도체층(145)의 표면 일부 영역 또는 전체 영역에 대해 소정의 식각 방법으로 요철 패턴(160)을 형성해 줄 수 있으며, 이러한 제2 반도체층(145)의 표면에 제2전극층(150)을 형성해 준다.

[0111] 또한, 도 6 내지 도 10에 나타낸 공정 순서에서 적어도 하나의 공정은 순서가 바뀔 수 있으며 이에 한정을 두지 않는다.

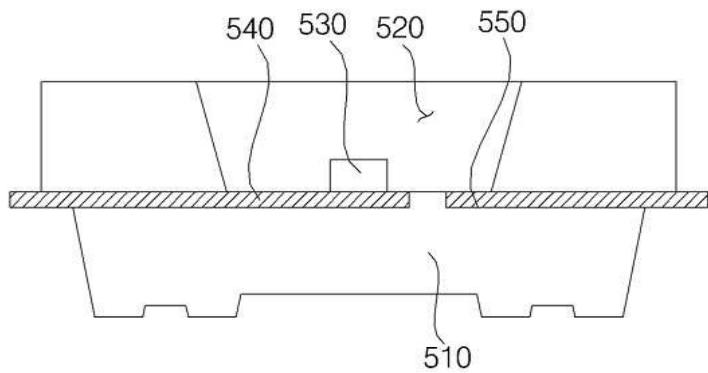

[0112] 도 11은 실시예에 따른 발광소자를 포함하는 발광소자 패키지를 나타낸 사시도이고, 도 12는 실시예에 따른 발광소자를 포함하는 발광소자 패키지를 나타낸 단면도이다.

[0113] 도 11 및 도 12를 참조하면, 발광소자 패키지(500)는 캐비티(520)가 형성된 몸체(510), 몸체(510)에 실장되는 제1 및 제2 리드 프레임(540, 550)과, 제1 및 제2 리드 프레임(540, 550)과 전기적으로 연결되는 발광소자(530), 및 발광소자(530)를 덮도록 캐비티(520)에 충진되는 봉지재(미도시)를 포함할 수 있다.

[0114] 몸체(510)는 폴리프탈아미드(PPA:Polyphthalamide)와 같은 수지 재질, 실리콘(Si), 알루미늄(Al), 알루미늄 나이트라이드(AlN), 액정폴리머(PSG, photo sensitive glass), 폴리아미드9T(PA9T), 신지오텍틱폴리스티렌(SPS), 금속 재질, 사파이어(Al<sub>2</sub>O<sub>3</sub>), 베릴륨 옥사이드(BeO), 인쇄회로기판(PCB, Printed Circuit Board) 중 적어도 하나로 형성될 수 있다. 몸체(510)는 사출 성형, 예칭 공정 등에 의해 형성될 수 있으나 이에 대해 한정하지는 않는다.

[0115] 몸체(510)의 내면은 경사면이 형성될 수 있다. 이러한 경사면의 각도에 따라 발광소자(530)에서 방출되는 광의 반사각이 달라질 수 있으며, 이에 따라 외부로 방출되는 광의 지향각을 조절할 수 있다.

[0116] 광의 지향각이 줄어들수록 발광소자(530)에서 외부로 방출되는 광의 집중성은 증가하고, 반대로 광의 지향각이 클수록 발광소자(530)에서 외부로 방출되는 광의 집중성은 감소한다.

[0117] 한편, 몸체(510)에 형성되는 캐비티(520)를 위에서 바라본 형상은 원형, 사각형, 다각형, 타원형 등의 형상일 수 있으며, 모서리가 곡선인 형상일 수도 있으나 이에 한정되는 것은 아니다.

[0118] 발광소자(530)는 제1 리드 프레임(540) 상에 실장되며, 예를 들어, 적색, 녹색, 청색, 백색 등의 빛을 방출하는 발광소자 또는 자외선을 방출하는 UV(Ultra Violet) 발광소자일 수 있으나, 이에 대해 한정하지는 않는다. 또한, 발광소자(530)는 한 개 이상 실장될 수 있다.

[0119] 또한, 발광소자(530)는 그 전기 단자들이 모두 상부 면에 형성된 수평형 타입(Horizontal type)이거나, 또는 상, 하부 면에 형성된 수직형 타입(Vertical type), 또는 플립 칩(flip chip) 모두에 적용 가능하다.

[0120] 봉지재(미도시)는 발광소자(530)를 덮도록 캐비티(520)에 충진될 수 있다.

[0121] 봉지재(미도시)는 실리콘, 에폭시, 및 기타 수지 재질로 형성될 수 있으며, 캐비티(520) 내에 충진한 후, 이를 자외선 또는 열 경화하는 방식으로 형성될 수 있다.

[0122] 또한 봉지재(미도시)는 형광체를 포함할 수 있으며, 형광체는 발광소자(530)에서 방출되는 광의 파장에 종류가 선택되어 발광소자 패키지(500)가 백색광을 구현하도록 할 수 있다.

[0123] 이러한 형광체는 발광소자(530)에서 방출되는 광의 파장에 따라 청색 발광 형광체, 청록색 발광 형광체, 녹색 발광 형광체, 황녹색 발광 형광체, 황색 발광 형광체, 황적색 발광 형광체, 오렌지색 발광 형광체, 및 적색 발광 형광체 중 하나가 적용될 수 있다.

[0124] 즉, 형광체는 발광소자(530)에서 방출되는 제1 빛을 가지는 광에 의해 여기 되어 제2 빛을 생성할 수 있다. 예를 들어, 발광소자(530)가 청색 발광 다이오드이고 형광체가 황색 형광체인 경우, 황색 형광체는 청색 빛에 의해 여기되어 황색 빛을 방출할 수 있으며, 청색 발광 다이오드에서 발생한 청색 빛 및 청색 빛에 의해 여기 되

어 발생한 황색 빛이 혼색됨에 따라 발광소자 패키지(500)는 백색 빛을 제공할 수 있다.

[0125] 이와 유사하게, 발광소자(530)가 녹색 발광 다이오드인 경우는 magenta 형광체 또는 청색과 적색의 형광체를 혼용하는 경우, 발광소자(530)가 적색 발광 다이오드인 경우는 Cyan형광체 또는 청색과 녹색 형광체를 혼용하는 경우를 예로 들 수 있다.

[0126] 이러한 형광체는 YAG계, TAG계, 황화물계, 실리케이트계, 알루미네이트계, 질화물계, 카바이드계, 니트리도실리케이트계, 봉산염계, 불화물계, 인산염계 등의 공지된 형광체일 수 있다.

[0127] 제1 및 제2 리드 프레임(540, 550)은 금속 재질, 예를 들어, 티타늄(Ti), 구리(Cu), 니켈(Ni), 금(Au), 크롬(Cr), 탄탈늄(Ta), 백금(Pt), 주석(Sn), 은(Ag), 인(P), 알루미늄(Al), 인듐(In), 팔라듐(Pd), 코발트(Co), 실리콘(Si), 게르마늄(Ge), 하프늄(Hf), 루테늄(Ru), 철(Fe) 중에서 하나 이상의 물질 또는 합금을 포함할 수 있다. 또한, 제1 및 제2 리드 프레임(540, 550)은 단층 또는 다층 구조를 가지도록 형성될 수 있으며, 이에 대해 한정하지는 않는다.

[0128] 제1 제2 리드 프레임(540, 550)은 서로 이격되어 서로 전기적으로 분리된다. 발광소자(530)는 제1 및 제2 리드 프레임(540, 550)상에 실장되며, 제1 및 제2 리드 프레임(540, 550)은 발광소자(530)와 직접 접촉하거나 또는 솔더링 부재(미도시)와 같은 전도성을 갖는 재료를 통해서 전기적으로 연결될 수 있다. 또한, 발광소자(530)는 와이어 본딩을 통해 제1 및 제2 리드 프레임(540, 550)과 전기적으로 연결될 수 있으며, 이에 한정하지 아니한다. 따라서 제1 및 제2 리드 프레임(540, 550)에 전원이 연결되면 발광소자(530)에 전원이 인가될 수 있다. 한편, 수개의 리드 프레임(미도시)이 몸체(510)내에 실장되고 각각의 리드 프레임(미도시)이 발광소자(530)와 전기적으로 연결될 수 있으며, 이에 한정하지 아니한다.

[0129] 실시예에 따른 발광 소자는 조명 시스템에 적용될 수 있다. 상기 조명 시스템은 복수의 발광 소자가 어레이된 구조를 포함하며, 도 13 및 도 14에 도시된 표시 장치, 도 15에 도시된 조명 장치를 포함하고, 조명등, 신호등, 차량 전조등, 전광판 등이 포함될 수 있다.

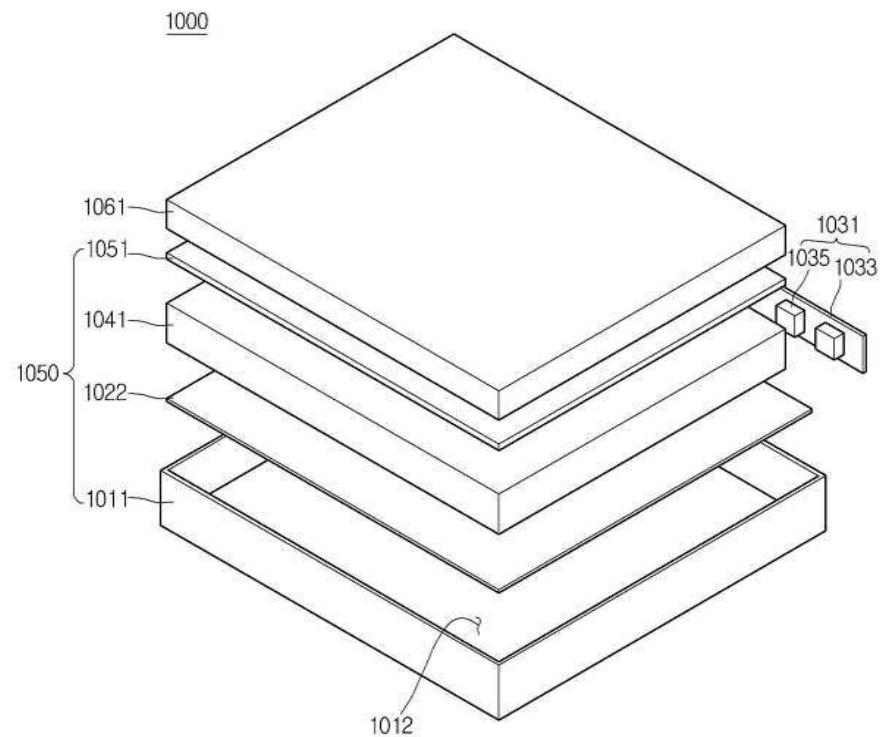

[0130] 도 13는 실시 예에 따른 발광 소자를 갖는 표시 장치의 분해 사시도이다.

[0131] 도 13를 참조하면, 실시예에 따른 표시 장치(1000)는 도광판(1041)과, 상기 도광판(1041)에 빛을 제공하는 광원 모듈(1031)와, 상기 도광판(1041) 아래에 반사 부재(1022)와, 상기 도광판(1041) 위에 광학 시트(1051)와, 상기 광학 시트(1051) 위에 표시 패널(1061)과, 상기 도광판(1041), 광원 모듈(1031) 및 반사 부재(1022)를 수납하는 바텀 커버(1011)를 포함할 수 있으나, 이에 한정되지 않는다.

[0132] 상기 바텀 커버(1011), 반사시트(1022), 도광판(1041), 광학 시트(1051)는 라이트유닛(1050)으로 정의될 수 있다.

[0133] 상기 도광판(1041)은 빛을 확산시켜 면광원화 시키는 역할을 한다. 상기 도광판(1041)은 투명한 재질로 이루어지며, 예를 들어, PMMA(polymethylmethacrylate)와 같은 아크릴 수지 계열, PET(polyethylene terephthalate), PC(poly carbonate), COC(cycloolefin copolymer) 및 PEN(polyethylene naphthalate) 수지 중 하나를 포함할 수 있다.

[0134] 상기 광원 모듈(1031)은 상기 도광판(1041)의 적어도 일 측면에 빛을 제공하며, 궁극적으로는 표시 장치의 광원으로써 작용하게 된다.

[0135] 상기 광원 모듈(1031)은 적어도 하나를 포함하며, 상기 도광판(1041)의 일 측면에서 직접 또는 간접적으로 광을 제공할 수 있다. 상기 광원 모듈(1031)은 기판(1033)과 상기에 개시된 실시 예에 따른 발광 발광 소자(1035)를 포함하며, 상기 발광 소자(1035)는 상기 기판(1033) 상에 소정 간격으로 어레이될 수 있다.

[0136] 상기 기판(1033)은 회로패턴(미도시)을 포함하는 인쇄회로기판(PCB, Printed Circuit Board)일 수 있다. 다만, 상기 기판(1033)은 일반 PCB 뿐 아니라, 메탈 코어 PCB(MCPCB, Metal Core PCB), 연성 PCB(FPCB, Flexible PCB) 등을 포함할 수도 있으며, 이에 대해 한정하지는 않는다. 상기 발광 소자(1035)는 상기 바텀 커버(1011)의 측면 또는 방열 플레이트 상에 탑재될 경우, 상기 기판(1033)은 제거될 수 있다. 여기서, 상기 방열 플레이트의 일부는 상기 바텀 커버(1011)의 상면에 접촉될 수 있다.

[0137] 그리고, 상기 복수의 발광 소자(1035)는 상기 기판(1033) 상에 빛이 방출되는 출사면이 상기 도광판(1041)과 소정 거리 이격되도록 탑재될 수 있으며, 이에 대해 한정하지는 않는다. 상기 발광 소자(1035)는 상기 도광판(1041)의 일측 면인 입광부에 광을 직접 또는 간접적으로 제공할 수 있으며, 이에 대해 한정하지는 않는다.

- [0138] 상기 도광판(1041) 아래에는 상기 반사 부재(1022)가 배치될 수 있다. 상기 반사 부재(1022)는 상기 도광판(1041)의 하면으로 입사된 빛을 반사시켜 위로 향하게 함으로써, 상기 라이트유닛(1050)의 휘도를 향상시킬 수 있다. 상기 반사 부재(1022)는 예를 들어, PET, PC, PVC 레진 등으로 형성될 수 있으나, 이에 대해 한정하지는 않는다. 상기 반사 부재(1022)는 상기 바텀 커버(1011)의 상면일 수 있으며, 이에 대해 한정하지는 않는다.

- [0139] 상기 바텀 커버(1011)는 상기 도광판(1041), 광원 모듈(1031) 및 반사 부재(1022) 등을 수납할 수 있다. 이를 위해, 상기 바텀 커버(1011)는 상면이 개구된 박스(box) 형상을 갖는 수납부(1012)가 구비될 수 있으며, 이에 대해 한정하지는 않는다. 상기 바텀 커버(1011)는 탑 커버와 결합될 수 있으며, 이에 대해 한정하지는 않는다.

- [0140] 상기 바텀 커버(1011)는 금속 재질 또는 수지 재질로 형성될 수 있으며, 프레스 성형 또는 압출 성형 등의 공정을 이용하여 제조될 수 있다. 또한 상기 바텀 커버(1011)는 열 전도성이 좋은 금속 또는 비 금속 재료를 포함할 수 있으며, 이에 대해 한정하지는 않는다.

- [0141] 상기 표시 패널(1061)은 예컨대, LCD 패널로서, 서로 대향되는 투명한 재질의 제 1 및 제 2기판, 그리고 제 1 및 제 2기판 사이에 개재된 액정층을 포함한다. 상기 표시 패널(1061)의 적어도 일면에는 편광판이 부착될 수 있으며, 이러한 편광판의 부착 구조로 한정하지는 않는다. 상기 표시 패널(1061)은 광학 시트(1051)를 통과한 광에 의해 정보를 표시하게 된다. 이러한 표시 장치(1000)는 각 종 휴대 단말기, 노트북 컴퓨터의 모니터, 랩탑 컴퓨터의 모니터, 텔레비전 등에 적용될 수 있다.

- [0142] 상기 광학 시트(1051)는 상기 표시 패널(1061)과 상기 도광판(1041) 사이에 배치되며, 적어도 한 장의 투광성 시트를 포함한다. 상기 광학 시트(1051)는 예컨대 확산 시트, 수평 및 수직 프리즘 시트, 및 휘도 강화 시트 등과 같은 시트 중에서 적어도 하나를 포함할 수 있다. 상기 확산 시트는 입사되는 광을 확산시켜 주고, 상기 수평 또는/및 수직 프리즘 시트는 입사되는 광을 표시 영역으로 집광시켜 주며, 상기 휘도 강화 시트는 손실되는 광을 재사용하여 휘도를 향상시켜 준다. 또한 상기 표시 패널(1061) 위에는 보호 시트가 배치될 수 있으며, 이에 대해 한정하지는 않는다.

- [0143] 여기서, 상기 광원 모듈(1031)의 광 경로 상에는 광학 부재로서, 상기 도광판(1041), 및 광학 시트(1051)를 포함할 수 있으며, 이에 대해 한정하지는 않는다.

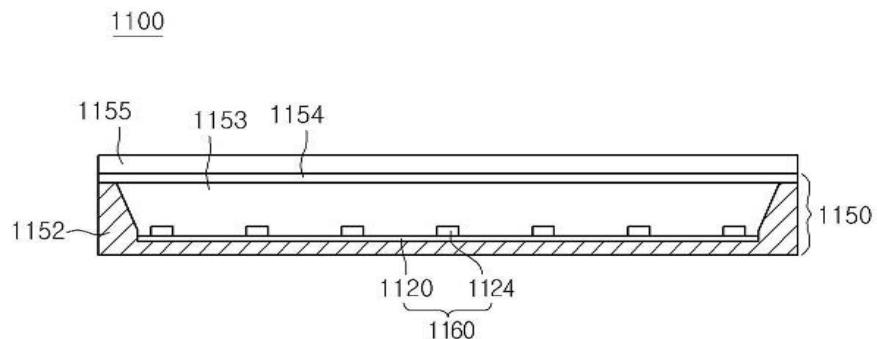

- [0144] 도 14는 실시 예에 따른 발광 소자를 갖는 표시 장치를 나타낸 도면이다.

- [0145] 도 14를 참조하면, 표시 장치(1100)는 바텀 커버(1152), 상기에 개시된 발광 소자(1124)가 어레이된 기판(1120), 광학 부재(1154), 및 표시 패널(1155)을 포함한다.

- [0146] 상기 기판(1120)과 상기 발광 소자(1124)는 광원 모듈(1160)로 정의될 수 있다. 상기 바텀 커버(1152), 적어도 하나의 광원 모듈(1160), 광학 부재(1154)는 라이트유닛(1150)으로 정의될 수 있다. 상기 바텀 커버(1152)에는 수납부(1153)를 구비할 수 있으며, 이에 대해 한정하지는 않는다. 상기의 광원 모듈(1160)은 기판(1120) 및 상기 기판(1120) 위에 배열된 복수의 발광 소자(1124)를 포함한다.

- [0147] 여기서, 상기 광학 부재(1154)는 렌즈, 도광판, 확산 시트, 수평 및 수직 프리즘 시트, 및 휘도 강화 시트 등에서 적어도 하나를 포함할 수 있다. 상기 도광판은 PC 재질 또는 PMMA(polymethyl methacrylate) 재질로 이루어 질 수 있으며, 이러한 도광판은 제거될 수 있다. 상기 확산 시트는 입사되는 광을 확산시켜 주고, 상기 수평 및 수직 프리즘 시트는 입사되는 광을 표시 영역으로 집광시켜 주며, 상기 휘도 강화 시트는 손실되는 광을 재사용하여 휘도를 향상시켜 준다.

- [0148] 상기 광학 부재(1154)는 상기 광원 모듈(1160) 위에 배치되며, 상기 광원 모듈(1160)로부터 방출된 광을 면 광원하거나, 확산, 집광 등을 수행하게 된다.

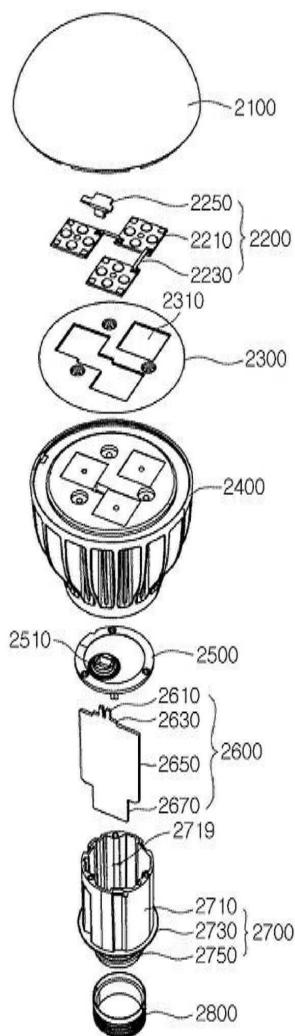

- [0149] 도 15은 실시 예에 따른 발광소자를 갖는 조명장치의 분해 사시도이다.

- [0150] 도 15을 참조하면, 실시 예에 따른 조명 장치는 커버(2100), 광원 모듈(2200), 방열체(2400), 전원 제공부(2600), 내부 케이스(2700), 소켓(2800)을 포함할 수 있다. 또한, 실시 예에 따른 조명 장치는 부재(2300)와 홀더(2500) 중 어느 하나 이상을 더 포함할 수 있다. 상기 광원 모듈(2200)은 실시 예에 따른 발광소자를 포함할 수 있다.

- [0151] 예컨대, 상기 커버(2100)는 벌브(bulb) 또는 반구의 형상을 가지며, 속이 비어 있고, 일 부분이 개구된 형상으로 제공될 수 있다. 상기 커버(2100)는 상기 광원 모듈(2200)과 광학적으로 결합될 수 있다. 예를 들어, 상기

커버(2100)는 상기 광원 모듈(2200)로부터 제공되는 빛을 확산, 산란 또는 여기 시킬 수 있다. 상기 커버(2100)는 일종의 광학 부재일 수 있다. 상기 커버(2100)는 상기 방열체(2400)와 결합될 수 있다. 상기 커버(2100)는 상기 방열체(2400)와 결합하는 결합부를 가질 수 있다.

[0152] 상기 커버(2100)의 내면에는 유백색 도료가 코팅될 수 있다. 유백색의 도료는 빛을 확산시키는 확산재를 포함할 수 있다. 상기 커버(2100)의 내면의 표면 거칠기는 상기 커버(2100)의 외면의 표면 거칠기보다 크게 형성될 수 있다. 이는 상기 광원 모듈(2200)로부터의 빛이 충분히 산란 및 확산되어 외부로 방출시키기 위함이다.

[0153] 상기 커버(2100)의 재질은 유리(glass), 플라스틱, 폴리프로필렌(PP), 폴리에틸렌(PE), 폴리카보네이트(PC) 등 일 수 있다. 여기서, 폴리카보네이트는 내광성, 내열성, 강도가 뛰어나다. 상기 커버(2100)는 외부에서 상기 광원 모듈(2200)이 보이도록 투명할 수 있고, 불투명할 수 있다. 상기 커버(2100)는 블로우(blow) 성형을 통해 형성될 수 있다.

[0154] 상기 광원 모듈(2200)은 상기 방열체(2400)의 일 면에 배치될 수 있다. 따라서, 상기 광원 모듈(2200)로부터의 열은 상기 방열체(2400)로 전도된다. 상기 광원 모듈(2200)은 발광소자(2210), 연결 플레이트(2230), 커넥터(2250)를 포함할 수 있다.

[0155] 상기 부재(2300)는 상기 방열체(2400)의 상면 위에 배치되고, 복수의 발광소자(2210)들과 커넥터(2250)이 삽입되는 가이드홈(2310)들을 갖는다. 상기 가이드홈(2310)은 상기 발광소자(2210)의 기판 및 커넥터(2250)와 대응된다.

[0156] 상기 부재(2300)의 표면은 빛 반사 물질로 도포 또는 코팅된 것일 수 있다. 예를 들면, 상기 부재(2300)의 표면은 백색의 도료로 도포 또는 코팅된 것일 수 있다. 이러한 상기 부재(2300)는 상기 커버(2100)의 내면에 반사되어 상기 광원 모듈(2200)측 방향으로 되돌아오는 빛을 다시 상기 커버(2100) 방향으로 반사한다. 따라서, 실시 예에 따른 조명 장치의 광 효율을 향상시킬 수 있다.

[0157] 상기 부재(2300)는 예로서 절연 물질로 이루어질 수 있다. 상기 광원 모듈(2200)의 연결 플레이트(2230)는 전기 전도성의 물질을 포함할 수 있다. 따라서, 상기 방열체(2400)와 상기 연결 플레이트(2230) 사이에 전기적인 접촉이 이루어질 수 있다. 상기 부재(2300)는 절연 물질로 구성되어 상기 연결 플레이트(2230)와 상기 방열체(2400)의 전기적 단락을 차단할 수 있다. 상기 방열체(2400)는 상기 광원 모듈(2200)로부터의 열과 상기 전원 제공부(2600)로부터의 열을 전달받아 방열한다.

[0158] 상기 홀더(2500)는 내부 케이스(2700)의 절연부(2710)의 수납홈(2719)을 막는다. 따라서, 상기 내부 케이스(2700)의 상기 절연부(2710)에 수납되는 상기 전원 제공부(2600)는 밀폐된다. 상기 홀더(2500)는 가이드 돌출부(2510)를 갖는다. 상기 가이드 돌출부(2510)는 상기 전원 제공부(2600)의 돌출부(2610)가 관통하는 훌을 구비할 수 있다.

[0159] 상기 전원 제공부(2600)는 외부로부터 제공받은 전기적 신호를 처리 또는 변환하여 상기 광원 모듈(2200)로 제공한다. 상기 전원 제공부(2600)는 상기 내부 케이스(2700)의 수납홈(2719)에 수납되고, 상기 홀더(2500)에 의해 상기 내부 케이스(2700)의 내부에 밀폐된다.

[0160] 상기 전원 제공부(2600)는 돌출부(2610), 가이드부(2630), 베이스(2650), 돌출부(2670)를 포함할 수 있다.

[0161] 상기 가이드부(2630)는 상기 베이스(2650)의 일 측에서 외부로 돌출된 형상을 갖는다. 상기 가이드부(2630)는 상기 홀더(2500)에 삽입될 수 있다. 상기 베이스(2650)의 일 면 위에 다수의 부품이 배치될 수 있다. 다수의 부품은 예를 들어, 외부 전원으로부터 제공되는 교류 전원을 직류 전원으로 변환하는 직류변환장치, 상기 광원 모듈(2200)의 구동을 제어하는 구동칩, 상기 광원 모듈(2200)을 보호하기 위한 ESD(ElectroStatic discharge) 보호 소자 등을 포함할 수 있으나 이에 대해 한정하지는 않는다.

[0162] 상기 돌출부(2670)는 상기 베이스(2650)의 다른 일 측에서 외부로 돌출된 형상을 갖는다. 상기 돌출부(2670)는 상기 내부 케이스(2700)의 연결부(2750) 내부에 삽입되고, 외부로부터의 전기적 신호를 제공받는다. 예컨대, 상기 돌출부(2670)는 상기 내부 케이스(2700)의 연결부(2750)의 폭과 같거나 작게 제공될 수 있다. 상기 돌출부(2670)에는 "+ 전선"과 "- 전선"의 각 일 단이 전기적으로 연결되고, "+ 전선"과 "- 전선"의 다른 일 단은 소켓(2800)에 전기적으로 연결될 수 있다.

[0163] 상기 내부 케이스(2700)는 내부에 상기 전원 제공부(2600)와 함께 물당부를 포함할 수 있다. 물당부는 물당 액체가 굳어진 부분으로서, 상기 전원 제공부(2600)가 상기 내부 케이스(2700) 내부에 고정될 수 있도록 한다.

[0164]

또한, 이상에서 실시예를 중심으로 설명하였으나 이는 단지 예시일 뿐 본 발명을 한정하는 것이 아니며, 본 발명이 속하는 분야의 통상의 지식을 가진 자라면 본 실시예의 본질적인 특성을 벗어나지 않는 범위에서 이상에 예시되지 않은 여러 지의 변형과 응용이 가능함을 알 수 있을 것이다. 예를 들어, 실시예에 구체적으로 나타난 각 구성 요소는 변형하여 실시할 수 있는 것이다. 그리고 이러한 변형과 응용에 관계된 차이점들은 첨부된 청구 범위에서 규정하는 본 발명의 범위에 포함되는 것으로 해석되어야 할 것이다.

## 도면

### 도면1

도면2

도면3

## 도면4

100A

## 도면5

100B

도면6

도면7

도면8

도면9

도면10

도면11

도면12

500

도면13

## 도면14

## 도면15

【심사관 직권보정사항】

【직권보정 1】

【보정항목】 청구범위

【보정세부항목】 청구항 22

【변경전】

제1항 내지 제21항 중 어느 한 항의

【변경후】

제1항 내지 제6항 및 제 9항 내지 제21항 중 어느 한 항의

【직권보정 2】

【보정항목】 청구범위

【보정세부항목】 청구항 24

【변경전】

제1항 내지 제21항 중 어느 한 항의

【변경후】

제1항 내지 제6항 및 제 9항 내지 제21항 중 어느 한 항의

【직권보정 3】

【보정항목】 청구범위

【보정세부항목】 청구항 23

【변경전】

제1항 내지 제21항 중 어느 한 항의

【변경후】

제1항 내지 제6항 및 제 9항 내지 제21항 중 어느 한 항의