(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6791735号

(P6791735)

(45) 発行日 令和2年11月25日(2020.11.25)

(24) 登録日 令和2年11月9日(2020.11.9)

(51) Int.Cl.

F 1

|             |              |                  |        |       |   |

|-------------|--------------|------------------|--------|-------|---|

| <b>HO4B</b> | <b>1/16</b>  | <b>(2006.01)</b> | HO 4 B | 1/16  | R |

| <b>HO4L</b> | <b>27/10</b> | <b>(2006.01)</b> | HO 4 L | 27/10 | Z |

| <b>HO4L</b> | <b>27/22</b> | <b>(2006.01)</b> | HO 4 L | 27/22 | Z |

| <b>HO4B</b> | <b>1/26</b>  | <b>(2006.01)</b> | HO 4 B | 1/26  | B |

請求項の数 14 外国語出願 (全 13 頁)

|                    |                               |           |                                                                                                                            |

|--------------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号          | 特願2016-231531 (P2016-231531)  | (73) 特許権者 | 508223789<br>スティヒティング・イメック・ネーデルラント<br>S t i c h t i n g I M E C N e d e r l a n d<br>オランダ5656アーエー・エイントホーフェン、ハイ・テク・キャンパス31番 |

| (22) 出願日           | 平成28年11月29日(2016.11.29)       | (74) 代理人  | 100101454<br>弁理士 山田 卓二                                                                                                     |

| (65) 公開番号          | 特開2017-112606 (P2017-112606A) | (74) 代理人  | 100081422<br>弁理士 田中 光雄                                                                                                     |

| (43) 公開日           | 平成29年6月22日(2017.6.22)         | (72) 発明者  | ビジャイ・クマール・ブルショタマン<br>ベルギー3001ルーヴァン、カペルドリーフ75番 アイメック・ヴェーゼットウエー内                                                             |

| 審査請求日              | 令和1年5月10日(2019.5.10)          |           |                                                                                                                            |

| (31) 優先権主張番号       | 15201303.3                    |           |                                                                                                                            |

| (32) 優先日           | 平成27年12月18日(2015.12.18)       |           |                                                                                                                            |

| (33) 優先権主張国・地域又は機関 | 歐州特許庁(EP)                     |           |                                                                                                                            |

最終頁に続く

(54) 【発明の名称】位相追跡受信機

## (57) 【特許請求の範囲】

## 【請求項 1】

第1及び第2の入力を有する位相検出器であって、前記第1の入力が変調された入力信号を受信するように適合された位相検出器と、

前記位相検出器の出力に結合された入力を有する比較器と、

前記比較器の出力に結合された入力を含む周波数オフセットキャンセルブロックと、

デジタル制御発振器とを備える受信機であって、

前記デジタル制御発振器は、

前記比較器の出力と前記周波数オフセットキャンセルブロックの出力とに結合された制御入力と、

前記位相検出器の第2の入力に結合された出力を有する受信機。

## 【請求項 2】

前記比較器の入力はローパスフィルタを介して位相検出器の出力に結合される請求項1に記載の受信機。

## 【請求項 3】

前記周波数オフセットキャンセルブロックは、積分器を備える請求項1又は2に記載の受信機。

## 【請求項 4】

前記周波数オフセットキャンセルブロックは、低域通過で調整可能な有限インパルス応答フィルタを備える請求項1～3のうちのいずれか1つに記載の受信機。

**【請求項 5】**

前記周波数オフセットキャンセルブロックは、可変利得増幅器を備える請求項1～4のうちのいずれか1つに記載の受信機。

**【請求項 6】**

前記周波数オフセットキャンセルブロックは、デルタシグマ変調器を備える請求項1～5のうちのいずれか1つに記載の受信機。

**【請求項 7】**

前記周波数オフセットキャンセルブロックは、積分器、調整可能な有限インパルス応答フィルタ、可変利得増幅器、及びデルタシグマ変調器を備え、

前記積分器、調整可能な有限インパルス応答フィルタ、可変利得増幅器、及びデルタシグマ変調器は順次に接続される請求項1又は2に記載の受信機。 10

**【請求項 8】**

前記周波数オフセットキャンセルブロックは、デジタル領域で実装される請求項1～7のうちのいずれか1つに記載の受信機。

**【請求項 9】**

前記比較器は、前記デジタル制御発振器の前記制御入力にデジタル信号を供給するよう構成され、

前記デジタル制御発振器は、前記デジタル信号に基づき、前記デジタル制御発振器の出力に第1又は第2の周波数の信号を供給するように適合される請求項1～8のうちのいずれか1つに記載の受信機。 20

**【請求項 10】**

前記デジタル制御発振器の制御入力は、加算点を介して、前記比較器の出力、もしくは、前記周波数オフセットキャンセルブロックの出力に結合される請求項1～9のうちのいずれか1つに記載の受信機。

**【請求項 11】**

前記比較器の入力における信号は第1の周波数を有し、

前記比較器は、より高い第2の周波数で前記信号をサンプリングするように適合される請求項1～10のうちのいずれか1つに記載の受信機。

**【請求項 12】**

前記比較器は、復調された出力信号を提供するように適合される請求項1～11のうちのいずれか1つに記載の受信機。 30

**【請求項 13】**

前記入力信号は、周波数シフトキーイング変調信号又は位相シフトキーイング変調信号である請求項1～12のうちのいずれか1つに記載の受信機。

**【請求項 14】**

受信された変調信号を復調する方法であって、前記方法は、

第1及び第2の入力を有する位相検出器の入力で変調信号を受信し、前記位相検出器からの出力を比較器の入力に供給することと、

前記比較器の入力をしきい値と比較することと、

前記比較器の出力をデジタル制御発振器の制御入力と周波数キャンセルブロックの入力とに提供することと、 40

前記周波数キャンセルブロックの出力を前記デジタル制御発振器の前記制御入力に供給することと、

前記デジタル制御発振器の出力を前記位相検出器に供給することを含む方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、一般に、無線受信機に関し、特に、自動周波数オフセットキャンセルを提供するデジタル制御発振器(DCO)をベースとする位相追跡受信機に関する。

**【背景技術】**

10

20

30

40

50

**【0002】**

定包絡線 FSK / PSK 変調は、ハードウェアの複雑さが低く、干渉に対する耐性が優れているために、例えば Zigbee (登録商標) や Bluetooth (登録商標) low energy のような無線規格において広く採用されている。従来の I / Q ベースの FSK / GFSK 受信機は、例えば差分及び乗算、ゼロクロス検出、及び直交相関のような周波数復調技術を用いる。

**【0003】**

これらの受信機は消費電力が高く、いくつかのアナログブロックを使用し、その性能はテクノロジのスケーリングによって低下する。電力消費を部分的に削減するスライディング I/F ベースの受信機はイメージ除去の問題が発生しやすい。位相領域受信機は、超低電力及び低電圧無線のためのより良い選択肢になりつつある。10

**【0004】**

位相同期ループ (PLL) はそのロック状態において、発振器、通常は電圧制御発振器 (VCO) の出力と、基準信号との間に一定の位相差を保持する。言い換えると、PLL の発振器は基準信号の周波数を追跡する。PLL のこの位相 / 周波数追跡動作は、周波数復調に使用することができ、発振器への制御信号を直接にその後の処理のための復調周波数信号として使用することができる。

**【0005】**

VCO をベースとする位相トラッキング FSK / GFSK 受信機は、アナログ・デジタル変換器 (ADC) が信号をデジタル領域に変換する前に PLL 变調器を受信機チェーンの終端におけるある別のブロックとして使用し、もしくは、ミキサ、ローパスフィルタ、可変ゲインアンプなどの他の受信機ブロックと集積化することができる。これらのアプローチでは、RF 入力信号は一般に、適切な中間周波数に低域周波数変換 (ダウンコンバート) され、復調のために PLL に渡す前に振幅が制限される。次に、PLL 内の発振器の制御信号は、デジタルベースバンド (DBB) 処理のためにデジタル化される。20

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

VCO をベースとする位相追跡受信機は、アーキテクチャの問題がほとんどない。まず第 1 に、PLL 復調器はフリーランニング発振器を使用して入力 RF 信号に同期し、無線規格は、RF 入力信号がデータ伝送中に一定量の動的周波数オフセットを有することを可能にする。フリーランニング発振器の周波数不安定性に起因する低周波ドリフトに伴うこれらの入力周波数偏差は、復調時の搬送波回復に大きく影響し、高いビット誤り率が生じる。従って、位相追跡 FSK 受信機は周波数偏差の公差が不十分である。30

**【0007】**

第 2 に、強力な干渉源は発振器を所望の搬送波周波数から引き離し、復調性能を低下させる。このことは高次のチャネル選択フィルタを用いて干渉源を抑圧することにより、部分的に対処することができる。しかしながら、高次フィルタによってもたらされる長い遅延は、復調性能及びループ安定性を低下させる。

**【0008】**

最後に、FSK データを識別するために、高分解能 ADC 又は高精度しきい値検出器が必要である。40

**【0009】**

上記に鑑み、本発明の目的は、低減された電力消費、改良された周波数許容度及び干渉除去を有する受信機を提供することにある。

**【課題を解決するための手段】****【0010】**

本発明の第 1 の態様によれば、受信機が提供される。前記受信機は、第 1 及び第 2 の入力を有する位相検出器を備え、第 1 の入力は、変調された入力信号を受信するように適合される。受信機は、位相検出器の出力に結合された入力を有する比較器を含む。受信機は50

、比較器の出力に結合された入力を含む周波数オフセットキャンセルブロックを含む。前記受信機は、前記比較器の出力及び前記周波数オフセットキャンセルブロックの出力に結合された制御入力と、前記位相検出器の第2の入力に結合された出力とを備えるデジタル制御発振器を含む。

#### 【0011】

このように、本発明は、比較器と自動周波数オフセットキャンセル( AFC )ループとを含む復調ループを有する受信機を提供するという考えに基づいており、ここで、前記比較器と前記自動周波数オフセットキャンセル( AFC )ループの両方のユニットは DCO を制御することで電力消費を低減し、DCO をベースとする位相追跡受信機の周波数許容誤差及び干渉除去を改善する。以下に説明する受信機の異なる部分(とて代わって「ユニット」、「デバイス」、「回路」及び／又は「構成要素(素子)」と呼ばれる)はハードウェア、ソフトウェア、又はその両方の組み合わせで実施することができる。さらに、詳細説明全体を通じて使用される用語「集積された」は、半導体材料(通常はシリコン)の1つ以上の小プレート(「チップ」)上に集積された電子回路、もしくは、プロセッサ上で実行されるときに開示された各受信機部分の機能を提供する制御プログラムの形式で集積されるソフトウェアコード部分で実装される。10

#### 【0012】

用語「位相検出器」は、少なくとも2つの入力信号間の位相差を表す出力信号を生成することができる、任意のユニット、デバイス、回路及び／又は構成要素を意味する。位相検出器は、アナログ信号又は方形波デジタル信号を受信し、信号間の差周波数を表す出力信号を生成するように適合されてもよい。位相検出器は、受信された入力信号のエッジの相対的なタイミングにのみに感度を有し、両方の信号が同じ周波数にあるときに入力信号間の位相差を表す出力信号を生成する。20

#### 【0013】

用語「比較器」は、ここでは、アナログ又はデジタルの入力信号の値をアナログ又はデジタルの基準値と比較し、入力信号の値が基準値より大きいか又は等しいかを示す出力信号を提供することができる、任意のユニット、デバイス、回路、及び／又は構成要素を意味する。基準値は、比較器の内部で提供されてもよいし、もしくは、比較器の入力において外部ソースから供給されてもよい。周波数オフセットキャンセルは、好ましくは、動作中の周波数オフセットキャンセルブロックが、例えば受信機のユーザによる介入なしにその機能を実行することができるように自動である。簡単にするために、以下では、周波数オフセットキャンセルブロックは、自動周波数オフセットキャンセルブロック( AFC )と呼ばれる。用語「デジタル制御発振器」は、ここでは、デジタル調整ワードを受信するための入力を備え、その出力に信号を提供するように適合された発振器を意味し、前記信号はデジタル調整ワードによって少なくとも部分的に決定される周波数を有する。一般化された例として、デジタル調整ワードは論理「1」又は論理「0」であってもよく、ここで、デジタル制御発振器の出力における周波数は、デジタル調整ワードが「1」のときは第1の周波数とし、デジタル調整ワードが「0」のときは第2の周波数とするように仮定する。受信機の各構成要素は、受信機の他の1つ以上の構成要素で集積化されてもよいし、もしくは別個の回路、ソフトウェア又は両方の組み合わせによって実施されてもよい。30

#### 【0014】

DCOは、好ましくは、比較器の出力に基づいて特定の周波数で発振して、DCOゲインの非直線性の影響を除去する。比較器は捕捉効果を提供し、受信信号における干渉を抑制する。干渉は、より高い周波数で強い信号に由来することがあり、例えば、隣接チャネル及び代替チャネルから、又は信号が伝搬する回路(例えば、位相検出器に先行する低雑音增幅器( LNA )、位相検出器自体、及び／又はDCO)内の非理想的な特性に由来することがある。このような非線形特性は、入力信号の高調波を生成し、所望の信号に対する干渉源として作用する。負帰還構成のAFCループは、入力周波数オフセットと発振器周波数の不安定性のために周波数偏差を推定し、それに応じてDCOの中心周波数を変更することによってそれを打ち消す。この構成により、複雑さが低減され、低減された電力40

消費、改善された周波数許容度及び改善された干渉除去を有する受信機が提供され得る。

**【0015】**

比較器の入力は、ローパスフィルタ（L P F）を介して位相検出器の出力に結合することができる。

**【0016】**

ローパスフィルタは、アナログ又はデジタルフィルタであってもよい。デジタルフィルタは、アナログ - デジタル変換器（A D C）を備えているか、又は当該デジタルフィルタに先行している。当該フィルタは、多くの異なる方法で実装することができる。例として、ローパスフィルタは、受動的又は能動的な第1又はより高次のR C、R L又はL Cフィルタ、スイッチトキャパシタフィルタ、F I Rフィルタ又はI I Rフィルタとすることが可能である。10

**【0017】**

ローパスフィルタはその帯域幅の外にある任意の信号を抑圧することができ、ここで、ローパスフィルタの帯域幅は、好ましくは、入力変調信号の帯域幅と等しくなるように設定される。この配置により、比較器に供給される信号の干渉が低減されるので、変調信号の状態 / 値の正確な検出が容易になるために、入力データのより信頼性の高い検出器を有する受信機が達成される。ローパスフィルタは、受信機の他の1つ以上の構成要素を用いて集積化されてもよく、もしくは、別個の回路、ソフトウェア又は両方の組み合わせによって実施されてもよい。20

**【0018】**

周波数オフセットキャンセルブロックは積分器を備えてよい。

**【0019】**

一般に、用語「積分器」は、ここでは、その入力信号の時間積分を表す出力信号を提供することができる、任意のユニット、デバイス、回路、及び / 又は構成要素を意味する。積分器は、第1又はより高次のI I R又はF I R積分器であってもよい。一例として、積分器は、順方向矩形積分器、逆方向矩形積分器、台形積分器又はシンプソン積分器であってもよい。積分器は、受信機の他の1つ以上の構成要素で集積化されてもよく、もしくは、別個の回路、ソフトウェア又は両方の組み合わせによって実施されてもよい。30

**【0020】**

積分器は、ループ内の残留周波数誤差 / 偏差を決定するために使用される、比較器出力からの望ましくない低周波成分の抽出を容易にする。30

**【0021】**

周波数オフセットキャンセルブロックは、低域通過で調整可能な有限インパルス応答（F I R）フィルタを備えてよい。

**【0022】**

一般に、用語「調整可能なF I Rフィルタ」は、制御可能なスペクトル特性を有するフィルタとして作用する任意のユニット、デバイス、回路及び / 又は構成要素を意味し、すなわち、可変カットオフ周波数応答を有するフィルタを意味する。前記フィルタは、任意の適切な設計方法を用いて設計することができ、例えば、変換又はスペクトルパラメータ近似によって行うことができる。前記フィルタは、好ましくは長さMの低域F I Rフィルタであり、ここで、Mは、適切な周波数応答を提供するように選択される。前記フィルタは、受信機の他の1つ以上の構成要素で集積化されてもよく、もしくは、別個の回路、ソフトウェア又は両方の組み合わせによって実施されてもよい。40

**【0023】**

調整可能なF I Rフィルタは、比較器の出力からの望ましくない低周波成分の抽出を容易にし、当該出力は、ループ内の残留周波数誤差 / 偏差を決定するために使用される。調整可能なF I Rフィルタは、A F Cブロックをプログラマブルにし、無線規格によって設定された受信機周波数許容誤差を満たすために使用することができる。

**【0024】**

周波数オフセットキャンセルブロックは、可変利得増幅器を備えてよい。50

**【 0 0 2 5 】**

一般に、用語「可変利得増幅器」は、ここでは、その入力に供給された信号を増幅、通過又は減衰させ、その出力で処理された信号を提供するように設計される、任意のユニット、デバイス、回路及び／又は構成要素を意味する。可変利得増幅器は、受信機の他の1つ以上の構成要素で集積化されてもよく、もしくは別個の回路、ソフトウェア又は両方の組み合わせによって実施されてもよい。

**【 0 0 2 6 】**

可変利得増幅器の提供により、A F C ループの帯域幅を調整し、A F C ブロックのステップ応答を制御することが可能である。可変利得増幅器は、A F C ブロックをプログラム可能にし、無線規格によって設定された受信機周波数許容誤差を満たすために使用することができる。10

**【 0 0 2 7 】**

周波数オフセットキャンセルブロックは、デルタシグマ変調器を備えてもよい。

**【 0 0 2 8 】**

デルタシグマ変調器は、フィルタリングされ増幅されたデジタルデータを、D C O に直接供給することができる離散的なステップに量子化するために使用されてもよい。デルタシグマ変調器は、時間平均による離散ステップの分解能を改善するために使用される。デルタシグマ変調器は、受信機の他の1つ以上の構成要素で集積化されてもよく、もしくは、別個の回路、ソフトウェア又は両方の組み合わせによって実施されてもよい。

**【 0 0 2 9 】**

この配置により、デルタシグマ変調器によって提供されるD C O の周波数分解能が向上するため、より良好な周波数トラッキング特性を有する受信機を達成することができる。

**【 0 0 3 0 】**

積分器、調整可能な有限インパルス応答フィルタ、可変利得増幅器及びデルタシグマ変調器は、順次に（シーケンシャルで、逐次に、連続して、又は縦続で）接続されてもよい。

**【 0 0 3 1 】**

用語「順次に接続される」は、積分器、調整可能な有限インパルス応答フィルタ、可変利得増幅器及びデルタシグマ変調器が、信号伝搬の観点から見て任意の順序で接続されてもよいことを理解されたい。30

**【 0 0 3 2 】**

この提供により、受信機を実現する際の柔軟性を高めることができる。

**【 0 0 3 3 】**

周波数オフセットキャンセルブロックは、デジタル領域で実装又は実施してもよい。

**【 0 0 3 4 】**

用語「デジタル領域」は、ここでは、周波数オフセットキャンセルブロックが、デジタル信号に作用してデジタル信号を提供するデジタル回路に実装又は実施されることを意味する。デジタル回路は、単一のチップ上に集積されてもよく、又は複数の集積回路の中に分散されてもよい。单一チップは、集積回路として提供されてもよい。周波数キャンセルブロックを形成するデジタル回路は、受信機の他の1つ以上の構成要素に関連する回路を含むより大きなチップの一部であってもよい。周波数キャンセルブロック及び／又は受信器を形成する集積回路は、プリント回路基板などの基板上に組み立てられてもよい。あるいは、周波数オフセットキャンセルブロックは、プロセッサ上で動作するときに周波数オフセットキャンセルブロックの機能を提供するソフトウェアで実装又は実施されてもよい。

**【 0 0 3 5 】**

この配置により、従来のF S K 受信機に比べてアナログブロックの数が少ない受信機を提供することができる。従って、受信機は、より少ない電力を消費し、チップ／基板の面積を最小限にして実装することができる。

**【 0 0 3 6 】**

10

20

30

40

50

比較器は、デジタル制御発振器の制御入力にデジタル信号を供給し、デジタル制御発振器は、前記デジタル信号に基づいてその出力に第1又は第2の周波数の信号を提供するよう適合されてもよい。

#### 【0037】

発振器は、好ましくは、受信機が動作する特定の通信規格に準拠する第1及び第2の周波数の出力信号を適合される。一例として、受信機がBlueooth(登録商標)通信のために使用される場合、受信機は、特定のチャネルを介して送信された信号を受信してもよく、前記第1及び第2の周波数は、前記Blueooth(登録商標)規格内の前記特定のチャネルに基づいて選択され、すなわち、チャネル周波数は全て2.4GHzのISM帯域内に位置し、チャネル内の搬送波の周波数は変調信号を搬送するようにシフトされる。二値の「1」は正の周波数偏差によって表され、二値の「0」は負の周波数偏差によって表される。典型的には、変調指数は、搬送波から0.140MHzと0.175MHzとの間の周波数偏差を与える0:28と0:35との間で変化し得る。

10

#### 【0038】

発振器は、比較器によって提供される信号に基づいて第1又は第2の周波数の出力信号を提供するよう適合されるので、DCO利得における任意の非線形性の影響、ひいては発振器周波数の回避が回避される。

#### 【0039】

デジタル制御発振器の制御入力は、加算器を介して比較器の出力と自動周波数オフセットキャセルブロックの出力とに結合することができる。

20

#### 【0040】

一般に、ここで、用語「加算点」は、2つ以上の信号源(ソース)から入力データを受信し、2つ以上の入力データストリームの合計を表す出力データを提供するように設計される、任意のユニット、デバイス、回路及び/又は構成要素を意味する。特に、加算点は、その入力で受信された2つ以上の直列又は並列データストリームの合計を提供することができる。加算点は、受信機の他の1つ以上の構成要素で集積化されてもよく、もしくは、別個の回路、ソフトウェア又は両方の組み合わせによって実施されてもよい。

#### 【0041】

加算点を設けることにより、AFCループ、復調ループ、及びRFフロントエンドは、受信機の多くのコンポーネントを共有する場合がある。従って、消費電力を低減したコンパクトな受信機を提供することができる。

30

#### 【0042】

比較器の入力における信号は第1の周波数を有し、比較器は、第2のより高い周波数で前記信号をサンプリングするよう適合される。

#### 【0043】

比較器は、変調信号のピットレートよりも高い周波数でLPFの出力をサンプリングするよう適合される。すなわち、比較器は、ナイキスト周波数よりもかなり高いサンプリング周波数でLPF信号のオーバーサンプリングを使用する。

#### 【0044】

オーバーサンプリングは、LPFの性能要求を緩和することで、分解能を向上させ、雑音を低減し、エイリアシング及び位相歪みを回避することを達成する。

40

#### 【0045】

比較器は、復調された出力信号を提供するよう適合される。

#### 【0046】

ここで、用語「出力信号」は、比較器の出力はデジタル領域での更なるデータ処理に使用されることを意味する。追加の回路及び/又はソフトウェアは、比較器からの出力信号を後続の回路に供給する前に、パルス整形(すなわち、出力信号の波形を変化させる)を提供し、及び/又は、適応処理(例えば、増幅、フィルタリングなど)を提供してもよい。

#### 【0047】

50

比較器からの復調信号を供給することにより、それほど複雑ではなく、コンパクトで効率的な受信機を提供することができる。

#### 【0048】

入力信号は、周波数シフトキーイング変調（F S K）信号又は位相シフトキーイング変調（P S K）信号であってもよい。

#### 【0049】

一般に、受信機は、任意のF S K / P S K信号を受信し復調するように適合されてもよい。特に、受信機は、一定の包絡線及び2進周波数変調で任意の信号を復調するように構成されてもよい。そのような信号は、ガウス周波数シフトキーイング（G F S K）、バイナリ周波数シフトキーイング（B F S K）、オフセット直交位相シフトキーイング（H S - O Q P S K）及びガウス最小シフトキーイング（G M S K）を含む。10

#### 【0050】

現代の通信におけるF S K / P S Kの普及のために、この提供により、広範囲の用途に使用するのに適した受信機を提供することができる。

#### 【0051】

本発明の第2の態様によれば、受信された変調信号を復調する方法が提供される。当該方法は、位相検出器で前記変調信号を受信し、前記位相検出器からの出力を比較器の入力に供給することを備える。前記方法は、比較器の入力をしきい値と比較することと、比較器の出力をデジタル制御発振器の制御入力と周波数キャンセルブロックの入力とに供給することを備える。前記方法は、前記周波数キャンセルブロックの出力を前記デジタル制御発振器の前記制御入力に供給し、デジタル制御発振器の出力を位相比較器に供給することを備える。20

#### 【発明の効果】

#### 【0052】

本発明の方法の利点は上述した受信機の利点に類似している。

#### 【0053】

本発明の他の目的、特徴及び利点は、以下の詳細な開示から明らかとなり、添付の請求項及び図面から明らかになるであろう。

#### 【0054】

一般的に、特許請求の範囲において使用される全ての用語は、明示的に定義される場合を除き、技術分野におけるそれらの通常の意味に従って解釈されるべきである。「1つ又はその〔構成要素、デバイス、手段、手段、ステップなど〕」に対するすべての参照は、特に明記しない限り、構成要素、装置、構成要素、手段、ステップなどの少なくとも1つのインスタンスを指すものとして、公然と解釈されるべきである。本明細書で開示される任意の方法のステップは、明示的に述べられていない限り、開示された正確な順序で実施される必要はない。30

#### 【0055】

上記及び本発明の追加の目的、特徴及び利点は、本発明の好ましい実施形態の以下の例示的かつ非限定的な詳細な説明を通して、また添付の図面を参照して、よりよく理解されるであろう。ここで、同様の構成要素には同じ参照番号が使用される。40

#### 【図面の簡単な説明】

#### 【0056】

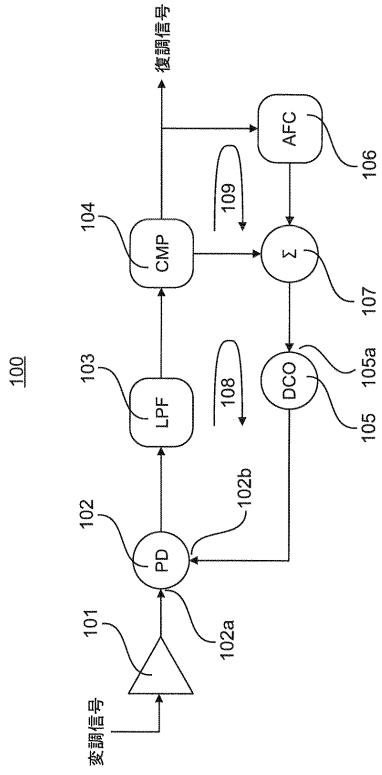

【図1】本発明の一実施形態にかかるPLLをベースとする位相追跡受信機を図式的に示す。

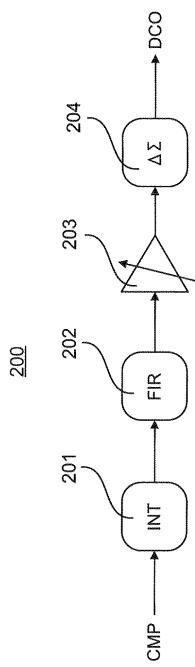

【図2】本発明の一実施形態にかかる周波数オフセット補正ブロックを図式的に示す。

#### 【発明を実施するための形態】

#### 【0057】

図1は、本発明の一実施形態にかかるPLLをベースとする位相追跡受信機100を示す。F S K / P S K変調信号は、受信機の入力で受信される。受信された変調信号は、受信機100の後続の機能ブロックに十分な振幅の信号を提供するために、低雑音増幅器150

0 1 により増幅される。低雑音増幅器 1 0 1 の帯域幅は関心のある帯域幅において十分な増幅を提供するようにを設定され、ここで、当該帯域幅は、好ましい実施形態によれば、2 4 0 0 M H z から 2 4 8 3 . 5 M H z に及ぶ 2 . 4 G H z の I S M 帯域を含む。

#### 【 0 0 5 8 】

位相検出器 ( P D ) 1 0 2 は第 1 の入力 1 0 2 a 及び第 2 の入力 1 0 2 b を含み、その第 1 の入力 1 0 2 a においてオプションの低雑音増幅器 1 0 1 の出力を受信する。好ましい実施形態によれば、ミキサは、アナログ位相検出器 1 0 2 として使用され、その入力 1 0 2 a 、 1 0 2 b における信号間の位相差に比例する信号を出力する。代替の実施形態によれば、アナログ乗算器又は論理回路を位相検出器 1 0 2 として使用することができる。

#### 【 0 0 5 9 】

位相検出器 1 0 2 の出力はローパスフィルタ L P F 1 0 3 に送られる。L P F 1 0 3 は、入力信号中の干渉信号を抑圧する。L P F 1 0 3 の入力における干渉信号は、通常、以下の 2 つのソース ( 信号源 ) を有する。

( 1 ) 受信機の入力からのより高い周波数で強い信号であって、通常は隣接チャネル及び代替チャネルからの信号が所望の信号と干渉する。

( 2 ) 受信機の回路における非理想的な特性であって、例えば、低雑音増幅器 1 0 1 、位相検出器 1 0 2 及び / 又は受信機 1 0 0 の他の部分は、入力信号の高調波を生成する可能性があり、それは所望の信号に対する干渉源として作用する。

L P F 1 0 3 はその帯域幅の外にある信号を抑圧し、ここで、L P F 1 0 3 の帯域幅は、好ましくは、入力変調信号の帯域幅と等しくなるように設定される。

#### 【 0 0 6 0 】

L P F 1 0 3 からの出力は、比較器 C M P 1 0 4 に転送され、当該出力信号は変調信号のビットレートよりも高い周波数で L P F 1 0 3 の出力をサンプリングすることが好ましい。比較器 1 0 4 によって示される捕捉効果は、余分な干渉抑制を提供し、すなわち、比較器 1 0 4 は、入力信号の瞬時振幅に応答する。もし所望の信号に対する干渉信号の比が一定の係数未満である場合、比較器 1 0 4 の入力の瞬時振幅は、所望の信号によって支配されるであろう。比較器 1 0 4 は、L P F 1 0 3 の出力信号の極性にのみ応答し、その出力信号は振幅依存性を緩和し、受信機 1 0 0 の利得制御を緩和し、復調ループ 1 0 8 を振幅変動 ( 例えば、アナログゲイン変動又はチャネルフェーディング ) に対して無感応にする。比較器 1 0 4 からの出力は復調された信号を表し、デジタル領域でのさらなるデータ処理に使用される。比較器 1 0 4 は、ビットレートより高い周波数でクロック同期されることで、しきい値検出を提供するために追加の A D C を必要とすることなしに、1 ビットオーバサンプリングデジタル出力を生成する。

#### 【 0 0 6 1 】

比較器 1 0 4 からの出力は、デジタル制御発振器 ( D C O ) 1 0 5 に転送される。D C O 1 0 5 は、比較器 1 0 4 の出力に基づいて特定の周波数でのみ発振し、D C O 1 0 5 の利得における非線形性の影響を除去する。例えば、B F S K アプリケーションに対して、発振器 1 0 5 の出力は、B F S K 方式でのマーク周波数及びスペース周波数に対応する 2 つの予め決められた周波数のうちの 1 つである。1 ビット比較器 1 0 4 の出力は、D C O 1 0 5 の入力 1 0 5 a にデジタル調整ワードを提供することによって、次のサンプリング期間における発振器周波数を決定する。デジタル調整ワードのフォーマットは、D C O 1 0 5 の実装に基づいて変化してもよい。

#### 【 0 0 6 2 】

一例として、デジタル調整ワードは、最も単純な形式では、論理「 1 」又は論理「 0 」であってもよく、ここで、デジタル調整ワードが「 1 」である場合、D C O 1 0 5 の出力における周波数は第 1 の周波数をとり、デジタル調整ワードが「 0 」のときは第 2 の周波数となる。あるいは、D C O 1 0 5 は、動的に公称値の周りの D C O 1 0 5 の周波数の動的な引き込みを可能にする、フレームフォーマットのデジタル調整ワードを受信する。D C O 1 0 5 の入力 1 0 5 a は、D C O 1 0 5 に 1 つ又は複数のレジスタ ( 図示せず ) を書き込むためのデータフレームを受信するシリアルインタフェースであってもよい。レジス

10

20

30

40

50

タに書き込まれた値は、公称周波数からの周波数引き込み量を制御する。

**【0063】**

D C O 1 0 5 の出力は、位相検出器 1 0 2 の第 2 の入力 1 0 2 b に供給される。

**【0064】**

D C O 1 0 5 は、好ましくは、異なる値の多数のキャパシタを含む L C タンク（図示せず）を備える。D C O 1 0 5 は、デジタル調整ワードに基づいて、L C タンク内の 1 つ以上のキャパシタを接続するように適合化され、ここで、L C タンク内のキャパシタの数は、D C O 1 0 5 に必要な分解能に応じて変化し得る。

**【0065】**

代替実施形態では、1 ビット比較器の代わりにマルチビット A D C を使用することができる。本実施形態では、マルチビット A D C の出力は、受信機がまた M - arry の周波数シフトキーイング（M - F S K）変調方式を復調することができるよう、2 つ以上の周波数で発振するように D C O 1 0 5 を制御する。10

**【0066】**

望ましくない周波数偏差（例えば、D C O 1 0 5 の周波数ドリフト）は、比較器 1 0 4 の出力のスペクトルにおいて主に低周波数領域を占有する。自動周波数オフセットキャンセル（A F C）ブロック 1 0 6 を介した負帰還ループ 1 0 9 は、比較器 1 0 4 の出力の低周波成分を打ち消す。負帰還構成の A F C ループ 1 0 9 は、入力周波数オフセットと発振器の周波数不安定性に起因する周波数偏差を推定し、それに応じて D C O 1 0 5 の中心周波数を変更することによってそれを打ち消す。20

**【0067】**

好ましい実施形態では、比較器 1 0 4 及び A F C ブロック 1 0 6 からの出力は加算点 1 0 7 でマージされる。すなわち、比較器 1 0 4 及び A F C ブロック 1 0 6 によって供給されたデジタルデータは、D C O 1 0 5 を制御するのに適したフォーマットにマージされる。通常は、比較器 1 0 4 は、D C O 1 0 5 が例えば B F S K 方式のマーク周波数及びスペース周波数に従うように、より大きなステップで D C O 1 0 5 がその周波数を増減させる。A F C ブロック 1 0 6 は、通常、入力信号に存在する任意の周波数オフセットを補償するために、D C O 1 0 5 に対して、はるかに小さなステップで周波数を増減させる。加算点は、D C O 1 0 5 は、比較器 1 0 4 及び A F C ブロック 1 0 6 からの信号を受信するための 2 つの入力を有するか、もしくは、又は D C O 1 0 5 が 1 つの入力を有し、比較器 1 0 4 及び A F C ブロック 1 0 6 からのデータを順次受信するように（すなわち、その貢献を D C O 1 0 5 内で内部的に組み合わせ、例えば、D C O 1 0 5 の周波数を制御する 1 つ又は複数のレジスタ内のデジタル調整ワードを調整することによって）D C O 1 0 5 に実装されてもよい。30

**【0068】**

A F C ループ 1 0 9 は、主復調ループ 1 0 8 と P D 1 0 2 、 L P F 1 0 3 、比較器 1 0 4 、 D C O 1 0 5 を共有する。A F C ループ 1 0 9 内の追加の A F C ブロック 1 0 6 は、好ましくは、A F C ループ 1 0 9 の実装を容易にし、電力効率を向上させるために、デジタル領域で実装又は実施される。

**【0069】**

図 2 は、本発明の一実施形態にかかる自動周波数オフセット補正ブロック A F C 2 0 0 を示す。A F C ブロック 2 0 0 は、積分器 2 0 1 、調整可能な F I R フィルタ 2 0 2 、可変利得增幅器 2 0 3 、及びデルタシグマ変調器 2 0 4 を備える。40

**【0070】**

積分器 2 0 1 及び調整可能な F I R フィルタ 2 0 2 は、比較器 1 0 4 の出力から低周波の望ましくない成分を抽出し、ループ 1 0 9 内の残留周波数誤差 / 偏差を決定するために使用される。

**【0071】**

可変利得增幅器 2 0 3 は、A F C ループ 1 0 9 の帯域幅を調整するために使用され、従って、A F C ブロック 2 0 0 のステップ応答を決定する。すなわち、可変 F I R フィルタ50

202 及び可変利得増幅器 203 は、AFC ブロック 200 をプログラム可能にし、無線規格（例えば、Blueooth（登録商標））によって設定された受信機周波数許容誤差を満たすために使用することができる。

#### 【0072】

デルタシグマ変調器 204 は、フィルタリングされて増幅されたデジタルデータを離散的なステップに量子化するために使用され、前記デジタルデータは DC0105 に直接供給することができる。デルタシグマ変調器 204 は、時間平均によるこれらの離散ステップの分解能を改善する。すなわち、機能的な観点から、デルタシグマ変調器は、以下の 2 つの動作を実行する。

(1) 時間平均 / ディザリング：通常、最小の DC0105 周波数ステップは、LC タンク内の最小キャパシタによって制限される。デルタシグマ変調器 204 を使用して、この最小の周波数ステップをさらに減らすことができる。言い換えれば、それは DC 周波数分解能を増加させることができる。10

(2) AFC 200 で生成された量子化雑音をより高い周波数にプッシュし、復調ループ 108 によって抑圧される。

#### 【0073】

上述したように、FSK / PSK 変調入力信号に応答して復調された出力信号を提供するように適合された受信機が開示される。前記受信機は、変調された入力信号を復調された出力信号を提供するデジタル制御発振器を備える位相同期ループを含む。前記受信機はさらにデジタル調整ワード（又は信号）をデジタル制御発振器に供給するように適合された周波数オフセットキャンセルブロックを備え、ここで、デジタル制御発振器は、デジタル調整ワード（信号）に応答し、デジタル調整ワードに基づいてその周波数を変更するよう<sup>20</sup>に適合され、ここで、前記周波数キャンセルブロックは、復調された出力信号に基づいてデジタル調整ワードを提供する。

#### 【0074】

本発明は、主として、いくつかの実施形態を参照して上述される。しかしながら、当業者には容易に理解されるように、上述したもの以外の他の実施形態も、本発明の範囲内で等しく可能であり、添付の特許請求の範囲によって提供される。

【図1】

【図2】

---

フロントページの続き

(72)発明者 リウ・ヤオ - ホン

ベルギー 3001ルーヴァン、カペルドリーフ75番 アイメック・ヴェーゼットウェー内

(72)発明者 ロバート・ボグダン・スタシェフスキ

ベルギー 3001ルーヴァン、カペルドリーフ75番 アイメック・ヴェーゼットウェー内

審査官 大野 友輝

(56)参考文献 特開2003-087117(JP,A)

特許第2766267(JP,B2)

米国特許第04682118(US,A)

米国特許出願公開第2014/0091842(US,A1)

(58)調査した分野(Int.Cl., DB名)

H04B 1/16

H04B 1/26

H04L 27/10

H04L 27/22