(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2011-522301

(P2011-522301A)

(43) 公表日 平成23年7月28日(2011.7.28)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>G06F 12/16</b> (2006.01) | G06F 12/16 | 320A 5B018  |

| <b>G11C 16/06</b> (2006.01) | G11C 17/00 | 639C 5B060  |

| <b>G11C 29/42</b> (2006.01) | G11C 29/00 | 631D 5B125  |

| <b>G11C 16/02</b> (2006.01) | G11C 17/00 | 601E 5L106  |

| <b>G06F 12/00</b> (2006.01) | G11C 17/00 | 641         |

審査請求 未請求 予備審査請求 未請求 (全 29 頁) 最終頁に続く

|               |                              |          |                                                                                               |

|---------------|------------------------------|----------|-----------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2010-550838 (P2010-550838) | (71) 出願人 | 500587067<br>アギア システムズ インコーポレーテッド<br>アメリカ合衆国, 18109 ペンシルヴァニア, アレンタウン, アメリカン パークウェイ エヌイー 11110 |

| (86) (22) 出願日 | 平成21年3月11日 (2009.3.11)       | (74) 代理人 | 100094112<br>弁理士 岡部 譲                                                                         |

| (85) 翻訳文提出日   | 平成22年11月8日 (2010.11.8)       | (74) 代理人 | 100064447<br>弁理士 岡部 正夫                                                                        |

| (86) 國際出願番号   | PCT/US2009/036810            | (74) 代理人 | 100085176<br>弁理士 加藤 伸晃                                                                        |

| (87) 國際公開番号   | W02009/114618                | (74) 代理人 | 100104352<br>弁理士 朝日 伸光                                                                        |

| (87) 國際公開日    | 平成21年9月17日 (2009.9.17)       |          |                                                                                               |

| (31) 優先権主張番号  | 61/068,934                   |          |                                                                                               |

| (32) 優先日      | 平成20年3月11日 (2008.3.11)       |          |                                                                                               |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                               |

最終頁に続く

(54) 【発明の名称】クロス・ページ・セクタ、マルチ・ページ符号化およびパー・ページ符号化を使用して多重レベル・セル・フラッシュ・メモリ・デバイスにデータを記憶するための方法および装置

## (57) 【要約】

クロス・ページ・セクタ、マルチ・ページ符号化およびパー・ページ符号化を使用して多重レベル・セル・フラッシュ・メモリ・デバイスにデータを記憶するための方法および装置が提供される。フラッシュ・メモリ・デバイス内の複数のページにわたって単一セクタを記憶することができる。個々のページにおけるセクタの数、ならびに所与のページを符号化および復号化するために使用される符号および/または符号レート、および所与のページを復号化するために使用される復号器または復号化アルゴリズムのパー・ページ制御が提供される。また、マルチ・ページ・アクセス・スキームおよび語線レベル・アクセス・スキームが提供される。

FIG. 1

**【特許請求の範囲】****【請求項 1】**

複数のセルを有する多重レベル・セル・フラッシュ・メモリ・デバイスにデータを記憶するための方法であって、前記多重レベル・セル・フラッシュ・メモリ・デバイスの個々のセルが複数のビットを記憶することができ、前記複数のビットの各々が異なるページからのビットであり、前記方法が、

複数の前記ページを蓄積することと、

前記複数のページを單一のブロックとして符号化することと、

前記單一のブロックを前記多重レベル・セル・フラッシュ・メモリ・デバイスに記憶することと

10

を含む方法。

**【請求項 2】**

前記記憶された單一のブロックを復号化するステップをさらに含む、請求項 1 に記載の方法。

**【請求項 3】**

前記記憶された單一のブロックを復号化する前記ステップが、前記複数の前記ページを提供し、また、前記方法が、要求されたセクタを前記複合化された複数のページから獲得するステップをさらに含む、請求項 2 に記載の方法。

**【請求項 4】**

前記複数のページが前記多重レベル・セル・フラッシュ・メモリ内の單一の語線に対応する、請求項 1 に記載の方法。

20

**【請求項 5】**

前記複数のページが、前記多重レベル・セル・フラッシュ・メモリ・デバイスからの読み出しあり前記多重レベル・セル・フラッシュ・メモリ・デバイスへの書き込みのためのものであってもよい最小データ単位である、請求項 1 に記載の方法。

**【請求項 6】**

少なくとも 1 つのセクタが複数のページにまたがる、請求項 1 に記載の方法。

**【請求項 7】**

前記複数のページを單一のブロックとして符号化するステップが、單一の符号および單一の符号レートを使用して前記複数のページを符号化する、請求項 1 に記載の方法。

30

**【請求項 8】**

前記複数のページを單一のブロックとして符号化するステップが、複数の符号および複数の符号レートのうちの 1 つまたは複数を使用して前記複数のページを符号化する、請求項 1 に記載の方法。

**【請求項 9】**

前記複数のページを單一のブロックとして符号化するステップが、独自の符号および独自の符号レートのうちの 1 つまたは複数を使用して前記複数のページの各々を符号化する、請求項 1 に記載の方法。

**【請求項 10】**

前記複数の前記ページを蓄積する前記ステップが、j が前記多重レベル・セル・フラッシュ・メモリ・デバイス内の語線当たりのページ数であり、また、k がページ当たりの前記セクタの数である j × k 個のセクタを蓄積するステップをさらに含む、請求項 1 に記載の方法。

40

**【請求項 11】**

前記符号化された單一のブロックを複数のページに分割するステップをさらに含み、また、前記記憶するステップが、前記複数のページの各々を前記多重レベル・セル・フラッシュ・メモリ・デバイスに記憶するステップを含む、請求項 1 に記載の方法。

**【請求項 12】**

複数のセルを有する多重レベル・セル・フラッシュ・メモリ・デバイスにデータを記憶するための方法であって、前記多重レベル・セル・フラッシュ・メモリ・デバイスの個々

50

のセルが複数のビットを記憶することができ、前記複数のビットの各々が異なるページからのビットであり、前記方法が、

前記多重レベル・セル・フラッシュ・メモリ・デバイスに書き込むべき現在のページのページ・タイプを決定することと、

前記決定されたページ・タイプに関連する符号および符号レートのうちの少なくとも1つを決定することと、

前記決定された少なくとも1つの符号および符号レートを使用して前記現在のページを符号化することと、

前記符号化された現在のページを前記多重レベル・セル・フラッシュ・メモリ・デバイスに記憶することと

10

を含む方法。

#### 【請求項13】

前記現在のページを符号化する前記ステップに先立って、前記決定されたページ・タイプに関連するページ当たりのセクタの数を決定するステップと、前記決定された数のセクタを蓄積するステップとをさらに含む、請求項12に記載の方法。

#### 【請求項14】

第2のページ・タイプより強力な符号および第2のページ・タイプより低い符号レートのうちの1つまたは複数を使用して、前記第2のページ・タイプより低い信頼性を有する第1のページ・タイプが符号化される、請求項12に記載の方法。

#### 【請求項15】

対応する符号レートを使用して、語線内の個々のページが実質的に同様の長さに符号化される、請求項12に記載の方法。

20

#### 【請求項16】

少なくとも1つのセクタを読み出す要求を受け取るステップと、前記要求されたセクタを有する前記多重レベル・セル・フラッシュ・メモリ・デバイス内のページを識別するステップと、前記識別されたページに関連する前記少なくとも1つの符号および符号レートを使用して、前記識別されたページを読み出し、かつ、前記読み出されたページを復号化するステップと、メモリ・マップを使用して前記要求されたセクタを前記復号化されたページから獲得するステップとをさらに含む、請求項12に記載の方法。

#### 【請求項17】

語線内の複数のページを復号化するために、複数の復号化段を備えた多段復号器を使用して1つまたは複数のページを復号化するステップをさらに含む、請求項12に記載の方法。

30

#### 【請求項18】

第1のページのための復号化段が他のページのための復号化段に決定を提供する、請求項17に記載の方法。

#### 【請求項19】

前記決定がハード決定およびソフト決定のうちの1つまたは複数である、請求項18に記載の方法。

#### 【請求項20】

第1のページが復号化され、前記方法が、前記第1のページに対する復号化誤りが検出されると少なくとも1つの追加ページを復号化するステップをさらに含む、請求項17に記載の方法。

40

#### 【請求項21】

複数のセルを有する多重レベル・セル・フラッシュ・メモリ・デバイスにデータを記憶するための方法であって、前記多重レベル・セル・フラッシュ・メモリ・デバイスの個々のセルが複数のビットを記憶することができ、前記複数のビットの各々が異なるページからのビットであり、前記方法が、

前記多重レベル・セル・フラッシュ・メモリ・デバイスに書き込むべき現在のページのページ・タイプを決定することと、

50

前記決定されたページ・タイプに関連するページ当たりのセクタの数を決定することと、

前記決定されたセクタの数を蓄積することと、

前記蓄積されたセクタを符号化することと、

前記蓄積されたセクタを前記多重レベル・セル・フラッシュ・メモリ・デバイスに記憶することと

を含む方法。

#### 【請求項 2 2】

少なくとも 1 つのセクタが複数のページにまたがり、前記記憶ステップの間、マルチ・ページ・アクセス・スキームおよび語線レベル・アクセス・スキームのうちの 1 つまたは複数が使用される、請求項 2 1 に記載の方法。10

#### 【請求項 2 3】

ページ当たりの前記セクタの数が非整数個であり、少なくとも 1 つのセクタが複数のページにまたがる、請求項 2 1 に記載の方法。

#### 【請求項 2 4】

後続するページのためにセクションの 1 つまたは複数のごく一部をバッファリングするステップをさらに含む、請求項 2 1 に記載の方法。

#### 【請求項 2 5】

前記蓄積されたセクタを記憶する前記ステップが、マルチ・ページ・アクセス・スキームおよび語線レベル・アクセス・スキームのうちの 1 つまたは複数を使用する、請求項 2 1 に記載の方法。20

#### 【請求項 2 6】

少なくとも 1 つのセクタを読み出す要求を受け取るステップと、前記要求されたセクタを有する前記多重レベル・セル・フラッシュ・メモリ・デバイス内の 1 つまたは複数のページを識別するステップと、ページ・レベル・アクセス・スキーム、マルチ・ページ・アクセス・スキームおよび語線レベル・アクセス・スキームを使用して前記識別された 1 つまたは複数のページを読み出すステップとをさらに含む、請求項 2 1 に記載の方法。

#### 【請求項 2 7】

前記読み出され、識別された 1 つまたは複数のページを前記識別された 1 つまたは複数のページに関連する符号および符号レートのうちの少なくとも 1 つを使用して復号化するステップと、メモリ・マップを使用して前記要求されたセクタを前記復号化された 1 つまたは複数のページから獲得するステップとをさらに含む、請求項 2 6 に記載の方法。30

#### 【請求項 2 8】

それぞれ複数の物理ページおよび複数のセルを備えた複数の語線を有する多重レベル・セル・フラッシュ・メモリ・デバイスにデータを記憶するための方法であって、前記多重レベル・セル・フラッシュ・メモリ・デバイスの個々のセルが複数のビットを記憶することができ、前記複数のビットの各々が異なる論理ページからのビットであり、前記論理ページの各々がユーザ・データの複数のセクタを備え、前記方法が、

第 1 のセットの論理ページを記憶することであって、前記第 1 のセットの論理ページ内の個々の論理ページの符号化サイズが前記複数の物理ページのサイズより小さいことと、40

第 2 のセットの論理ページを記憶することであって、前記第 2 のセットの論理ページ内の個々の論理ページの符号化サイズが前記複数の物理ページのサイズより大きく、かつ、前記第 2 のセットの論理ページの少なくとも一部がスピルオーバ領域に記憶されることとを含む方法。

#### 【請求項 2 9】

前記第 1 のセットの論理ページを記憶する前記ステップに引き続いて前記スピルオーバ領域がプログラムされる、請求項 2 8 に記載の方法。

#### 【請求項 3 0】

前記第 1 のセットの論理ページを記憶する前記ステップに先立って前記スピルオーバ領域がプログラムされる、請求項 2 8 に記載の方法。50

**【請求項 3 1】**

前記多重レベル・セル・フラッシュ・メモリ・デバイスが、それぞれ複数の前記ページを備えた複数の語線をさらに備え、前記複数のページの各々が、前記複数のページの各々の非符号化長が実質的に同様の長さになり、また、前記複数のページの各々の符号化長が異なるように関連する符号レートを有する、請求項 2 8 に記載の方法。

**【請求項 3 2】**

前記多重レベル・セル・フラッシュ・メモリ・デバイスが、それぞれ複数の前記ページを備えた複数の語線をさらに備え、前記複数のページの各々が、前記複数のページの各々の非符号化長が異なり、また、前記複数のページの各々の符号化長が実質的に同様の長さになるように関連する符号レートを有する、請求項 2 8 に記載の方法。

10

**【請求項 3 3】**

多重レベル・セル・フラッシュ・メモリ・デバイスであって、

複数のセルであって、前記多重レベル・セル・フラッシュ・メモリ・デバイスの個々のセルが複数のビットを記憶することができ、前記複数のビットの各々が異なるページからのビットである複数のセルと、

それぞれ複数の前記ページを備えた複数の語線であって、前記複数のページの各々が、前記複数のページの各々の非符号化長が実質的に同様の長さになり、また、前記複数のページの各々の符号化長が異なるように関連する符号レートを有する複数の語線と

を備えた多重レベル・セル・フラッシュ・メモリ・デバイス。

20

**【請求項 3 4】**

多重レベル・セル・フラッシュ・メモリ・デバイスであって、

複数のセルであって、前記多重レベル・セル・フラッシュ・メモリ・デバイスの個々のセルが複数のビットを記憶することができ、前記複数のビットの各々が異なるページからのビットである複数のセルと、

それぞれ複数の前記ページを備えた複数の語線であって、前記複数のページの各々が、前記複数のページの各々の非符号化長が異なり、また、前記複数のページの各々の符号化長が実質的に同様の長さになるように関連する符号レートを有する複数の語線と

を備えた多重レベル・セル・フラッシュ・メモリ・デバイス。

30

**【請求項 3 5】**

多重レベル・セル・フラッシュ・メモリ・デバイスであって、

複数のセルであって、前記多重レベル・セル・フラッシュ・メモリ・デバイスの個々のセルが複数のビットを記憶することができ、前記複数のビットの各々が異なるページからのビットである複数のセルと、

それぞれ複数の前記ページを備えた複数の語線であって、少なくとも 1 つのセクタが前記複数のページにまたがっている複数の語線と

を備えた多重レベル・セル・フラッシュ・メモリ・デバイス。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

関連出願の相互参照

40

本出願は、参照により本明細書に組み込まれている、2008年3月11日に出願した米国仮出願第 61 / 068934 号の利益を主張するものである。

**【0 0 0 2】**

本発明は一般に多重レベル・セル・フラッシュ・メモリ・デバイスに関し、より詳細には、このような多重レベル・セル・デバイスを符号化し、かつ、このような多重レベル・セル・デバイスにアクセスするための技法に関する。

**【背景技術】****【0 0 0 3】**

フラッシュ・メモリ・デバイスなどの多くのメモリ・デバイスには、データを記憶するためのアナログ・メモリ・セルが使用されている。個々のメモリ・セルは、記憶値とも呼

50

ばれている、電荷または電圧などのアナログ値を記憶する。この記憶値は、セル内に記憶された情報を表す。フラッシュ・メモリ・デバイスの場合、例えば、個々のアナログ・メモリ・セルは、通常、特定の電圧を記憶する。個々のセルに対する可能アナログ値の範囲は、通常、複数の閾値領域に分割され、個々の領域は、1つまたは複数のデータ・ビット値に対応している。データは、所望の1つまたは複数のビットに対応する公称アナログ値を書き込むことによってアナログ・メモリ・セルに書き込まれる。

#### 【0004】

単一レベル・セル (SLC) フラッシュ・メモリ・デバイスは、例えば、1つのメモリ・セル毎に1つのビットを記憶する(つまり2つの可能メモリ状態)。一方、多重レベル・セル (MLC) フラッシュ・メモリ・デバイスは、1つのメモリ・セル毎に複数のビットを記憶する(つまり個々のセルは4つ以上のプログラム可能状態を有している)。多重レベル・セル・フラッシュ・メモリ・デバイスの場合、単に電流または電圧が存在しているか、あるいは存在していないかだけではなく、電流または電圧の量が検出される。多重レベル・セル・デバイスの場合、少なくとも3つの閾値レベルを使用して4つ以上の異なる閾値状態が定義される。したがって個々のセルの動作範囲は、多数の状態に分割されており、また、個々の状態の範囲は、单一レベル・セル・デバイスの場合より狭い。したがって、多重レベル・セル・デバイスにおける任意の单一のビットの信頼性は、单一レベル・セル・デバイスにおける信頼性より低い。多重レベル・セル (MLC) フラッシュ・メモリ・デバイスについてのより詳細な説明については、例えば、それぞれ参照により本明細書に組み込まれている、K. Takeuchiら、「A 56-nm CMOS 99 mm<sup>2</sup> 8-Gb Multi-Level NAND Flash Memory with 10-MB/s Program Throughput」、IEEE Journal of Solid-State Circuits, Vol. 42, No. 1, 219~232頁(2007)、およびK.-T. Parkら、「A Zeroing Cell-to-Cell Interference Page Architecture with Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE Journal of Solid-State Circuits, Vol. 43, No. 4, 919~928頁(2008)を参考されたい。

10

20

30

40

#### 【0005】

既存のフラッシュ・デバイスには、ページ・レベル・アクセス技法が使用されており、ページは、フラッシュ・メモリ・デバイスに書き込むことができ、あるいはフラッシュ・メモリ・デバイスから読み出すことができる最小単位である。ページは、通常、互いに独立して書き込まれ、かつ、読み出される。さらに、既存のフラッシュ・メモリには、通常、すべてのページを符号化(および復号化)するために同じ符号および符号レートが使用されている。オペレーティング・システムには、通常、例えば512バイトのユーザ情報からなるデータ・セクタが使用されている。通常、ユーザ・データ長は、セクタ・サイズの倍数である。ある典型的なフラッシュ・メモリ構成では、1つのページには、8個のセクタのユーザ情報が含まれている。したがって、フラッシュ・コントローラは、フラッシュ・メモリ・デバイスに個々のページを書き込むために、ページ・レベル・アクセス技法を使用して8個のセクタの情報を結合している。フラッシュ・メモリ・デバイスからセクタが読み出される毎に、所望のセクタを含んだすべてのページが読み出される。

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

【特許文献1】米国仮出願第61/068934号

【特許文献2】米国特許第6522580号

【非特許文献】

#### 【0007】

50

【非特許文献1】K. Takeuchiら、「A 56-nm CMOS 99-mm<sup>2</sup> 8-Gb Multi-Level NAND Flash Memory with 10-MB/s Program Throughput」、IEEE Journal of Solid-State Circuits、Vol. 42、No. 1、219~232頁(2007)

【非特許文献2】K.-T. Parkら、「A Zeroing Cell-to-Cell Interference Page Architecture with Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE Journal of Solid-State Circuits、Vol. 43、No. 4、919~928頁(2008) 10

【非特許文献3】U. Wachsmannら、「Multilevel Codes: Theoretical Concepts and Practical Design Rules」、IEEE Transaction Information Theory、Vol. 45、No. 5、1361~91頁(1999)

【非特許文献4】S. LinおよびD. Costello、「Error Control Coding: Fundamentals and Application, Second Edition」 Pearson Prentice Hall (2004) 20

### 【発明の概要】

### 【発明が解決しようとする課題】

### 【0008】

例えば、より低い誤り率を達成し、あるいは記憶容量を改善するためには、多重レベル・セル(MLC)フラッシュ・メモリ・デバイスのための改良型多重レベル符号化および読み出し/書き込みアクセス技法が必要である。さらに、フラッシュメモリ・デバイス内の複数のページにわたって単一のセクタを記憶することができる多重レベル・セル・フラッシュ・メモリ・デバイスのための改良型読み出し/書き込みアクセス技法が必要である。さらに、個々のページ内のセクタの数、ならびに符号化および復号化のために使用される符号および/または符号レートのパー・ページ制御を提供する改良型読み出し/書き込みアクセス技法が必要である。多重レベル符号についてのより詳細な説明については、例えば、参照により本明細書に組み込まれている、U. Wachsmannら、「Multilevel Codes: Theoretical Concepts and Practical Design Rules」、IEEE Transaction Information Theory、Vol. 45、No. 5、1361~91頁(1999)を参照されたい。 30

### 【課題を解決するための手段】

### 【0009】

一般に、クロス・ページ・セクタ、マルチ・ページ符号化およびパー・ページ符号化を使用して多重レベル・セル・フラッシュ・メモリ・デバイスにデータを記憶するための方法および装置が提供される。本発明の様々な態様によれば、複数のセルを有する多重レベル・セル・フラッシュ・メモリ・デバイスにデータが記憶され、多重レベル・セル・フラッシュ・メモリ・デバイスの個々のセルは、複数のビットを記憶することができ、複数のビットの各々は、異なるページからのビットである。開示されるデータ記憶方法の1つには、複数のページを蓄積するステップと、複数のページを单一のブロックとして符号化するステップと、单一のブロックを多重レベル・セル・フラッシュ・メモリ・デバイスに記憶するステップが含まれている。さらに、記憶された单一のブロックを復号化し、複数のページを提供することも可能である。 40

### 【0010】

他の記憶方法には、多重レベル・セル・フラッシュ・メモリ・デバイスに書き込むべき現在のページのページ・タイプを決定するステップと、決定されたページ・タイプに関連

する符号および符号レートのうちの少なくとも 1 つを決定するステップと、決定された少なくとも 1 つの符号および符号レートを使用して現在のページを符号化するステップと、符号化された現在のページを多重レベル・セル・フラッシュ・メモリ・デバイスに記憶するステップが含まれている。ページは、多重レベル・セル・フラッシュ・メモリ・デバイスの中に読み出すことができ、また、識別されたページに関連する少なくとも 1 つの符号、符号レート、復号器または復号化アルゴリズムを使用して復号化することができる。

#### 【0011】

さらに他の記憶方法には、多重レベル・セル・フラッシュ・メモリ・デバイスに書き込むべき現在のページのページ・タイプを決定するステップと、決定されたページ・タイプに関連するページ当たりのセクタの数を決定するステップと、決定されたセクタの数を蓄積するステップと、蓄積されたセクタを符号化するステップと、蓄積されたセクタを多重レベル・セル・フラッシュ・メモリ・デバイスに記憶するステップが含まれている。少なくとも 1 つのセクタを読み出す要求を受け取ると、要求されたセクタを有する多重レベル・セル・フラッシュ・メモリ・デバイス内の 1 つまたは複数のページを識別することができ、また、識別された 1 つまたは複数のページは、ページ・タイプ・アクセス・スキーム、マルチ・ページ・アクセス・スキームおよび語線レベル・アクセス・スキームのうちの 1 つまたは複数を使用して読み出すことができる。読み出された、識別された 1 つまたは複数のページは、識別された 1 つまたは複数のページに関連する符号、符号レート、復号器および復号化アルゴリズムのうちの少なくとも 1 つを使用して復号化することができ、また、メモリ・マップを使用して、復号化された 1 つまたは複数のページから、要求されたセクタを得ることができる。

10

20

30

40

50

#### 【0012】

他の記憶方法には、第 1 のセットの論理ページを記憶するステップであって、第 1 のセットの論理ページ内の個々の論理ページの符号化サイズが複数の物理ページのサイズより小さいステップと、第 2 のセットの論理ページを記憶するステップであって、第 2 のセットの論理ページ内の個々の論理ページの符号化サイズが複数の物理ページのサイズより大きく、かつ、第 2 のセットの論理ページの少なくとも一部が複数の物理ページのスピルオーバ領域に記憶されるステップが含まれている。

#### 【0013】

本発明の他の態様によれば、多重レベル・セル・フラッシュ・メモリ・デバイスが開示される。多重レベル・セル・フラッシュ・メモリ・デバイスは、複数のセルであって、多重レベル・セル・フラッシュ・メモリ・デバイスの個々のセルが複数のビットを記憶することができ、複数のビットの各々が異なるページからのビットである複数のセルと、それぞれ複数のページを備えた複数の語線であって、複数のページの各々が、複数のページの各々の非符号化長が実質的に同様の長さになり、また、複数のページの各々の符号化長が異なるように関連する符号レートを有することができる複数の語線とを備えている。

#### 【0014】

本発明の他の態様によれば、多重レベル・セル・フラッシュ・メモリ・デバイスが提供される。多重レベル・セル・フラッシュ・メモリ・デバイスは、複数のセルであって、多重レベル・セル・フラッシュ・メモリ・デバイスの個々のセルが複数のビットを記憶することができ、複数のビットの各々が異なるページからのビットである複数のセルと、それぞれ複数のページを備えた複数の語線であって、複数のページの各々が、複数のページの各々の非符号化長が異なり、また、複数のページの各々の符号化長が実質的に同様の長さになるように関連する符号レートを有することができる複数の語線とを備えている。

#### 【0015】

本発明のさらに他の態様によれば、多重レベル・セル・フラッシュ・メモリ・デバイスが提供される。多重レベル・セル・フラッシュ・メモリ・デバイスは、複数のセルであって、多重レベル・セル・フラッシュ・メモリ・デバイスの個々のセルが複数のビットを記憶することができ、複数のビットの各々が異なるページからのビットである複数のセルと、それぞれ複数のページを備えた複数の語線であって、少なくとも 1 つのセクタが複数の

ページにまたがることができる複数の語線とを備えている。

【0016】

本発明ならびに本発明の他の特徴および利点については、以下の詳細な説明および図面を参照することによってより完全に理解されよう。

【図面の簡単な説明】

【0017】

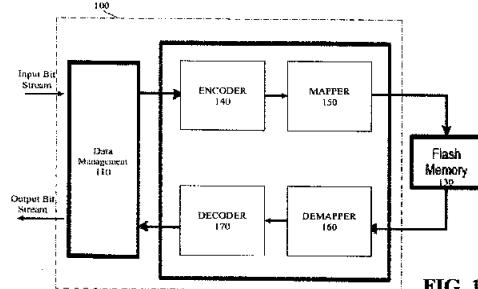

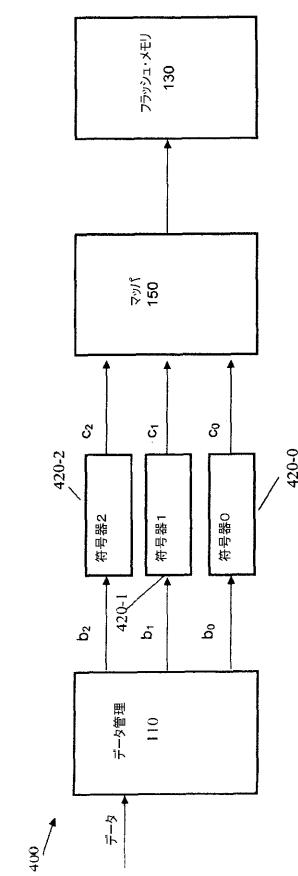

【図1】本発明によるフラッシュ・メモリ・コントローラとフラッシュ・メモリ・デバイスの間の相互作用を示す略ブロック図である。

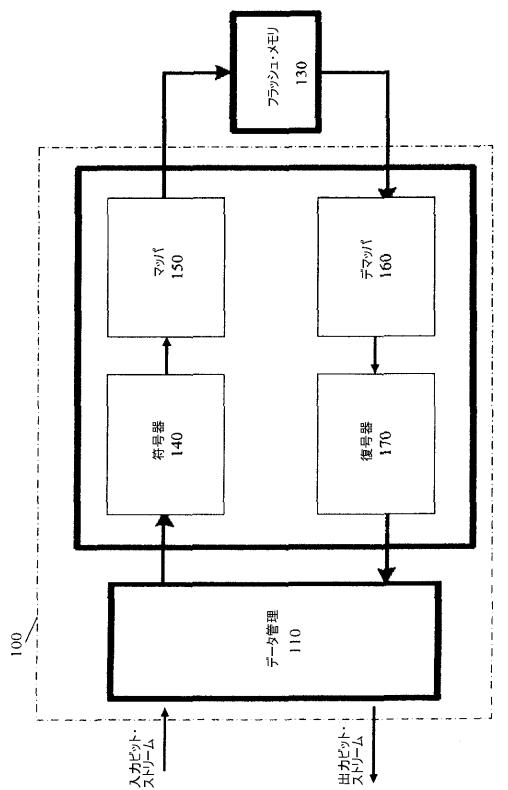

【図2】図1の例示的多重レベル・セル・フラッシュ・メモリのための一例示的閾値電圧分布を示す図である。

10

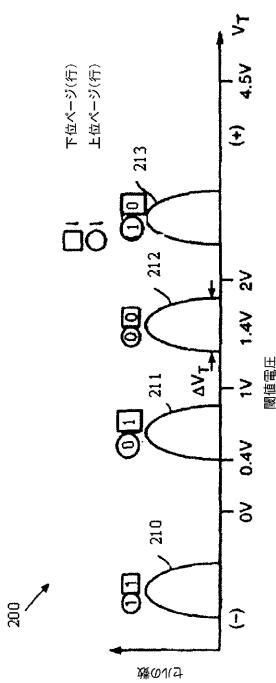

【図3】多重レベル・セル(MLC)フラッシュ・メモリ・デバイス内のフラッシュ・セル・アレイを示す図である。

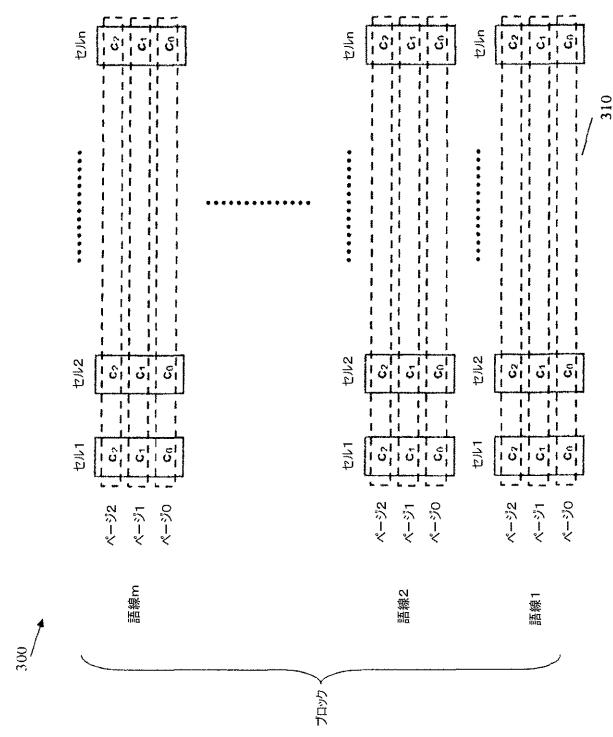

【図4】本発明の一態様による、図3のフラッシュ・セル・アレイのための一例示的符号器を示す図である。

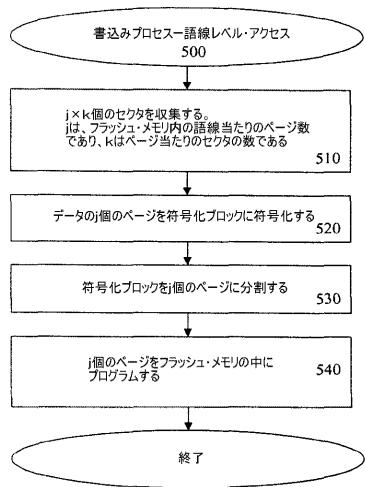

【図5】本発明の特徴を組み込んだ語線レベル・アクセス・スキームのための書き込みプロセスの一例示的実施態様を記述した流れ図である。

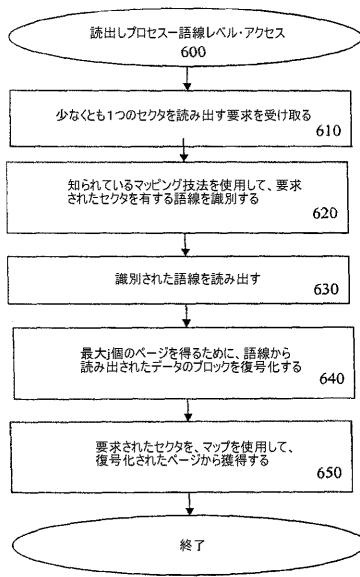

【図6】本発明の特徴を組み込んだ語線レベル・アクセス・スキームのための読み出しプロセスの一例示的実施態様を記述した流れ図である。

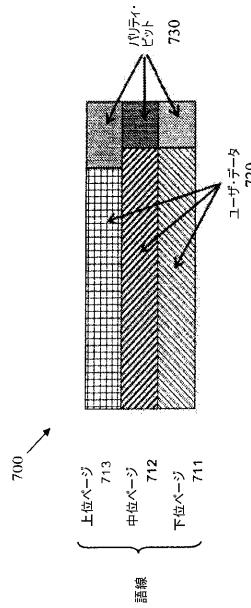

【図7】語線内の個々のページが異なる符号レートで同じ長さに符号化される、本発明の特徴を組み込んだ可変符号レート符号化スキームを示す図である。

20

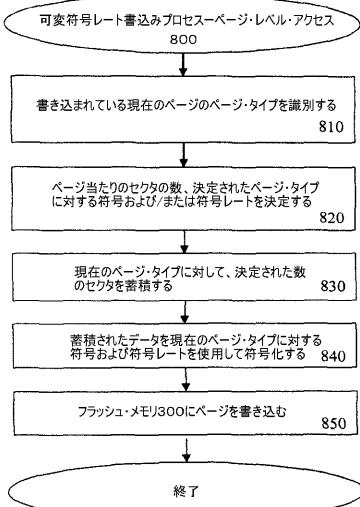

【図8】個々のページが整数個のセクタを備えている場合における、フラッシュ・メモリ130に書き込むための可変符号レート書き込みプロセスの一例示的実施態様を記述した流れ図である。

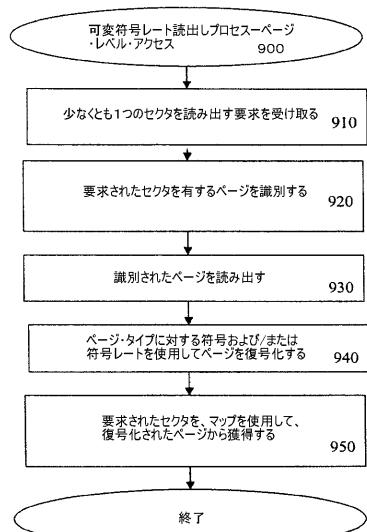

【図9】個々のページが整数個のセクタを備えている場合における、フラッシュ・メモリ130から読み出すための可変符号レート読み出しプロセスの一例示的実施態様を記述した流れ図である。

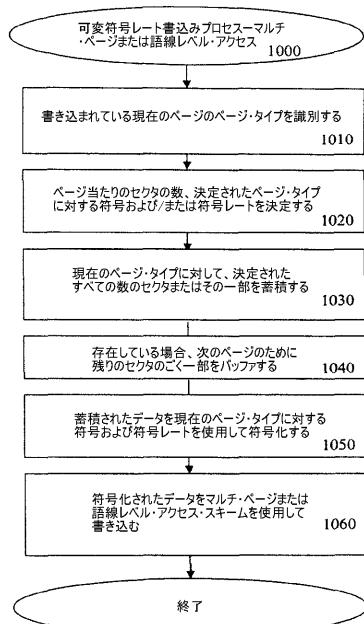

【図10】個々のページが非整数個のセクタを備え、また、所与のセクタが複数のページにまたがることができる場合における、フラッシュ・メモリに書き込むための可変符号レート書き込みプロセスの一例示的実施態様を記述した流れ図である。

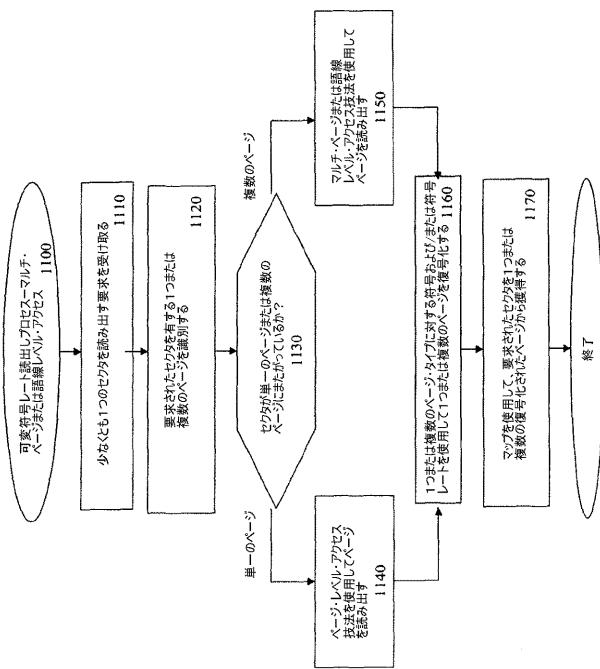

【図11】1つまたは複数のページが非整数個のセクタを備えることができ、また、所与のセクタが複数のページにまたがることができる場合における、フラッシュ・メモリから読み出すための可変符号レート・プロセスの一例示的実施態様を記述した流れ図である。

30

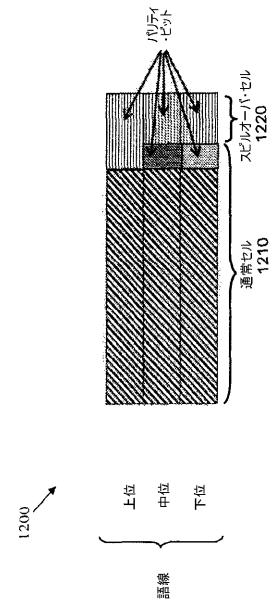

【図12】通常のセルおよびスピルオーバ・セルを備えたマルチ・ページセル語線を示す図である。

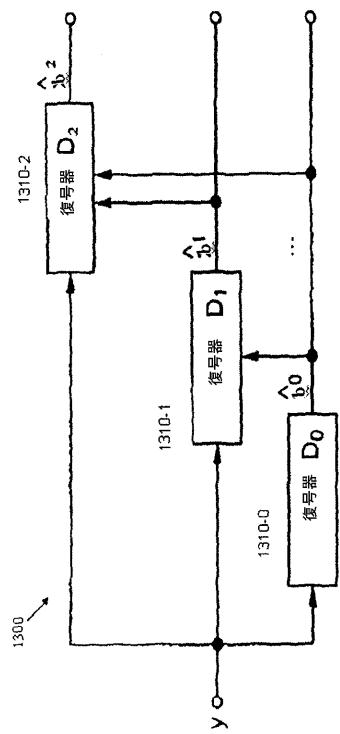

【図13】本発明の特徴を組み込んだ多段復号器の略ブロック図である。

【発明を実施するための形態】

【0018】

本発明によれば、多重レベル・セル(MLC)フラッシュ・メモリ・デバイスのための多重レベル符号化および読み出し/書き込みアクセス技法が提供される。本明細書において使用されているように、多重レベル・セル・フラッシュ・メモリは、個々のメモリ・セルが複数のビットを記憶するメモリを備えている。通常、1つのフラッシュ・セル内に記憶されている複数のビットは、異なるページに属している。図1は、本発明によるフラッシュ・メモリ・コントローラ100とフラッシュ・メモリ・デバイス120の間の相互作用を示す略ブロック図である。図1に示されているように、ユーザ・データは、以下で説明する本発明の態様によるフラッシュ・メモリ130に書き込むことができ、かつ、フラッシュ・メモリ130から読み出すことができる。図1に示されているように、入力ビット・ストリームは、データ蓄積、集約、蓄積、収集、分割、またはインタリービングなどの潜在的に他のタスクを実行するデータ管理ブロック110によって処理される。次に、集約され、あるいは分割されたデータが符号器140によって符号化され、例えば冗長ビットが追加される。本発明のすべての実施形態では、系統的符号および非系統的符号の両方を

40

使用することができる。

#### 【0019】

次に、符号化されたデータがマッパ150によって処理され、マッパ150は、符号化された1つまたは複数のビット・ストリームをフラッシュ・メモリ130をプログラムするためのプログラム済み電圧レベルにマップする。フラッシュ・メモリ130からデータが読み出され、読み出された電圧レベルを1つまたは複数のビット・ストリームにデマップするデマッパ160によって処理され、この1つまたは複数のビット・ストリームが復号器170によって復号化される。通常、符号器140およびマッパ150は、ユーザ・データのストリームを、フラッシュ・メモリ130のセルの中にプログラムしなければならない状態または電圧レベルのストリームに変換する。同様に、デマッパ160および復号器170は、フラッシュ・メモリ130から読み出されたセル状態または電圧レベルのストリームを、フラッシュ・メモリ130に記憶されていたユーザ・データのストリームに変換する。データ管理ブロック110は、符号器140の出力部分またはデマッパ160の出力部分で、符号化されたデータ・ストリームに追加データ集約、蓄積、収集、分割、インタリービングまたは他のタスクを適用することができる。10

#### 【0020】

以下、図4および図13に関連して、データを符号化し、かつ、復号化するための本発明による技法についてさらに説明する。以下、例えば図5および6に関連して、フラッシュ・コントローラ100のための適切な技法についてさらに説明する。フラッシュ・メモリ130は、多重レベルNANDフラッシュ・メモリまたは多重レベル位相変化メモリなどの多重レベル・セル・フラッシュ・メモリとして具体化することができる。通常、図2および3に関連して以下でさらに説明するように、フラッシュ・メモリ130には、少なくとも1つのフラッシュ・セル・アレイ、ならびに読み出しおよび書き込み回路が含まれている。20

#### 【0021】

##### 多重レベル・セル・フラッシュ・メモリ

多重レベル・セル・フラッシュ・メモリの場合、通常、閾値検出器を使用して、特定のセルに関連する電圧値が定義済みメモリ状態に変換される。図2は、参照により本明細書に組み込まれている米国特許第6522580号の教示に基づく、図1の例示的多重レベル・セル・フラッシュ・メモリ130のための一例示的閾値電圧分布を示したものである。図2に示されている例示的実施形態では、個々の記憶素子には、2つのビットのデータを個々のメモリ・セルに記憶するために4つの可能データ状態が使用されている。図2には、個々のピークが1つの状態に対応している4つのピーク210～213が示されている。多重レベル・セル・フラッシュ・デバイスの場合、セルに2つのビットを記憶するために、閾値電圧分布グラフ200の異なるピーク210～213が使用される。30

#### 【0022】

閾値電圧分布グラフ200のピーク210～213には、それぞれ2進値11、01、00および10のラベルが振られている。したがってセルが第1の状態210にある場合、それは、下位ビットが「1」であり、また、上位ビットが「1」であることを表している（これは、通常、セルのプログラムされていない初期状態または消去状態である）。同様に、セルが第2の状態211にある場合、それは、下位ビットが「1」であり、また、上位ビットが「0」であることを表している。セルが第3の状態212にある場合、それは、下位ビットが「0」であり、また、上位ビットが「0」であることを表している。最後に、セルが第4の状態213にある場合、それは、下位ビットが「0」であり、また、上位ビットが「1」であることを表している。40

#### 【0023】

閾値電圧分布210は、0ボルト未満の負の閾値電圧レベルを有する消去状態（「11」データ状態）にあるアレイ内のセルの閾値レベル $V_T$ の分布を表している。それぞれ「01」および「00」ユーザ・データを記憶しているメモリ・セルの閾値電圧分布211および212は、それぞれ0ボルトと1ボルトの間、および1ボルトと2ボルトの間にな50

るよう示されている。閾値電圧分布 213 は、閾値電圧レベルがリード・バス電圧の 2 ボルトと 4.5 ボルトの間に設定された「10」データ状態にプログラムされているセルの分布を示している。

#### 【0024】

以下でさらに説明するように、単一のメモリ・セルに記憶されている 2 つのビットの各々は、異なるページからのビットである。言い換えると、個々のメモリ・セルに記憶されている 2 つのビットの個々のビットは、異なるページ・アドレスを担っている。図 2 に示されている右側のビットは、下位ページ・アドレスが入力されるとアクセスされる。左側のビットは、上位ページ・アドレスが入力されるとアクセスされる。

#### 【0025】

フラッシュ・メモリは、通常、複数のブロックで構成されており、個々のブロックは、フラッシュ・セル・アレイとして実施されている。図 3 は、多重レベル・セル (MLC) フラッシュ・メモリ・デバイス 130 内のフラッシュ・セル・アレイ 300 を示したものである。図 3 に示されているように、フラッシュ・セル・アレイ 300 は、フラッシュ・セル c<sub>i</sub> 当たり複数のビットを記憶している。図 3 には、1 つのブロックに対するフラッシュ・セル・アレイ・アーキテクチャが示されており、個々の例示的セルは、通常、3 つのビットを記憶する浮遊ゲート・トランジスタに対応している。例示的セル・アレイ 300 は、m 本の語線および n 本のビット線からなっている。通常、マルチ・ページ・セル・フラッシュ・メモリの場合、個々のページはセクタ・サイズの倍数であり、また、单一セル内のビットは、異なるページに属している。図 3 の例では、個々のセルの 3 つのビットは、3 つの異なるページに対応しており、また、個々の語線は、3 つのページを記憶している。以下の説明では、ページ 0、1 および 2 は、下位ページ・レベル、中位ページ・レベルおよび上位ページ・レベルと呼ばれている。さらに、フラッシュ・セル・アレイ 300 内のページ 310 などの個々のページは、通常、8 個のセクタなどの固定数のセクタを備えている。本発明の一態様によれば、個々のページは、セクタ・サイズの非整数倍であってもよい。

#### 【0026】

フラッシュ・セル・アレイは、さらに、偶数ページおよび奇数ページに分割することができ、例えば偶数番号のセル（図 3 のセル 2 および 4 など）は偶数ページに対応しており、また、奇数番号のセル（図 3 のセル 1 および 3 など）は奇数ページに対応している。この場合、ページ（ページ 0 など）は、偶数ページ（偶数ページ 0）および奇数ページ（奇数ページ 0）を含むことになる。偶数ページおよび奇数ページの詳細な説明については、例えば、参照により本明細書に組み込まれている、K.-T. Park ら、「A Zeroing Cell-to-Cell Interference Page Architecture with Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE Journal of Solid-State Circuits、Vol. 43、No. 4、919～928 頁（2008）を参照されたい。本発明のすべての態様は、偶数 / 奇数ページ分割または他のフラッシュ・セル・アレイ分割を有するフラッシュ・セル・アレイに適用することができる。以下では、ページは、図 3 に示されているページもしくは偶数ページまたは奇数ページのいずれかを表している。

#### 【0027】

##### ジョイント符号化またはパー・ページ符号化

本発明の一態様によれば、語線内の個々のページは、任意選択で、異なる符号レートまたは異なるタイプの符号（または両方）を使用して符号化することができる。例えば、Low Density Parity Check Codes (LDPC)、Bose-Chaudhuri-Hocquenghem (BCH) および Reed Solomon (RS) 符号を使用することができる。一実施形態では、より高い信頼性を必要とするページには、より強力な符号またはより低い符号レートを使用することができる。例え

10

20

30

30

40

50

ば、より大きいページ番号は、場合によっては誤りを生じる可能性がより高い。したがってこれらのページは、これらのページの性能を改善する符号または符号レート（または両方）を使用して符号化することができる。誤り率がより高い上位ページには、より強力な誤り修正符号（より低いレートの符号およびLDPC符号など）を使用することができ、また、誤り率がより低い下位ページには、微力な誤り修正符号（より高いレートの符号および代数符号など）を使用することができる。

#### 【0028】

したがって、本発明によれば、多重レベル・フラッシュ・セル・アレイ300の語線内の個々のページの符号化パラメータを独自に確立することができる。例えば、本発明の一実施形態によれば、(i)ページ当たりのセクタの数、(ii)符号、(iii)ページを分割および/または符号化するために使用される符号レート、および/または(iv)ページを復号化するために使用される復号器または復号器アルゴリズムのパート・ページ制御が可能である。10

#### 【0029】

図4に関連して以下でさらに説明するように、個々の語線内のデータのj個のページ（jはフラッシュ・セル・アレイ300内の語線当たりのページ数である）は、任意選択で、最大j個の固有符号および/または符号レートを有する独立した符号化スキームを使用した符号器140によって符号化することができる。例えば、図4に示されている実施形態では、個々のページは、任意選択で、固有の符号および符号レートを使用することができる。ページは、例えば、図3に示されている語線内の3つのページを参照することができる。あるいは偶数ページおよび奇数ページを有する3ビット/セル・フラッシュ・セル・アレイ内の6個のページ（3つは偶数ページであり、また、3つは奇数ページである）を参照することができる。20

#### 【0030】

図1および5に関連して以下で説明する本発明の他の態様は、ジョイント符号化スキームをサポートしており、単一の符号および符号レートを有する符号器140によって、個々の語線内のデータのj個のページを符号化することができる。

#### 【0031】

#### ページ・アクセス・スキーム、マルチ・ページ・アクセス・スキームおよび語線レベル・アクセス・スキーム

本発明の他の態様によれば、ページ・レベル、マルチ・ページ・レベルまたは語線レベルに基づいてマルチ・ページ・セル・フラッシュ・メモリ130にアクセスすることができる。上で既に示したように、既存のフラッシュ・デバイスには、ページ・レベル・アクセス技法が使用されており、ページは、フラッシュ・メモリ・デバイスに書き込むことができ、あるいはフラッシュ・メモリ・デバイスから読み出すことができる最小単位である。さらに、本発明によれば、(i)フラッシュ・メモリ・デバイスを符号化し、フラッシュ・メモリ・デバイスに書き込み、あるいはフラッシュ・メモリ・デバイスから読み出すための最小単位として複数のページを使用することができるマルチ・ページ・レベル・アクセス技法、および(ii)語線が、データを符号化し、読み出し、あるいは書き込むための最小データ単位である語線レベル・アクセス技法が可能である。本発明は、この方法で、ページの境界を越えた符号語の符号化を可能にし、あるいは語線内における異なるページのための可変符号レートを可能にすることによって、より優れた柔軟性および有効性を提供している。さらに、本発明によれば、複数のページをまとめて符号化するLDPC符号化技法などの改良型符号化スキームおよび復号化スキームを使用することができる。30

#### 【0032】

以下でさらに説明するように、データ管理ブロック110は、ページ・レベル・アクセス・スキーム、マルチ・ページ・アクセス・スキームまたは語線レベル・アクセス・スキームが使用されているかどうかに基づいて、入力ビット・ストリームからデータを蓄積している。マルチ・ページ・アクセス・スキームまたは語線レベル・アクセス・スキームの場合、データ管理および符号化は、複数のページまたはすべての語線に対して実施するこ40

とができるが、これらの複数のページまたは語線は、知られている技法を使用してページを逐次フラッシュ・メモリに書き込むことによって物理的に書き込むことができる。

### 【0033】

#### 語線内のページの符号化 / 復号化

図4は、本発明の一態様による、図3のマルチ・ページ・セル・フラッシュ・アレイ300のための一例示的符号器400を示したものである。上で既に示したように、例示的フラッシュ・メモリ130内の個々のページは、独立して符号化することができる。図4に示されているように、例示的語線内の3つの例示的ページに対して、3つの全く異なる符号器420-1ないし420-3が使用されている。これらの3つの符号器420-1ないし420-3は、符号化のタイプ（例えばLDPC、BCHおよびRS）または符号レートあるいはその両方の点で異なっていてもよい。上で示したように、下位ページ・レベルは、中位ページ・レベルおよび上位ページ・レベルより高い符号レートで符号化することができる（その逆についても同様である）。一変形形態では、十分な信頼性を有するいくつかのページ・レベルは、全く符号化することができない。図4に示されているように、以下でさらに説明するデータ管理ユニット110内でのデータ分割の後、フラッシュ・セル・アレイ300の適切なセルに記憶される前に、1つのセル内の個々のビットが個別の符号器420-1ないし420-3によって符号化される。

10

### 【0034】

本発明の他の態様によれば、語線内の個々のページは、LDPC、BCH、RS、ハード・デシジョン復号器またはソフト・デシジョン復号器などの異なるタイプの復号器を使用して復号化することができる。例えば、語線内の誤り率がより低いページは、ハード・デシジョン復号器を使用して復号化することができ、一方、誤り率がより高いページは、ソフト・デシジョン復号器を使用して復号化することができる。ハード・デシジョン復号器は、通常、フラッシュ・セル・アレイ300から読み出される、符号化されたビットを使用することになる。ソフト・デシジョン復号器は、ソフト情報、例えばフラッシュ・セル・アレイ300内のセルから読み出される電圧値を使用することになる。

20

### 【0035】

他の変形形態では、復号器が反復復号化を実施すると、個々のページの復号器は、異なる反復回数を実施することができる。例えば、語線内の誤り率がより高いページは、より多くの反復回数を使用して復号化することができ、一方、誤り率がより低いページは、誤り率がより高いページより少ない反復回数を使用して復号化することができる。さらに、図13に関連して以下でさらに説明するように、本発明の他の態様は、語線内の複数のページを復号化しており、例えば、総合誤り率を改善するために、1つのページの復号器は、他のページの復号器に決定を供給している。ハード・デシジョン復号器およびソフト・デシジョン復号器、反復復号化、LDPC符号化および他の符号化技法の説明については、例えば、参照により本明細書に組み込まれている、S. LinおよびD. Costello、「Error Control Coding: Fundamentals and Applications, Second Edition」 Pearson Prentice Hall (2004)を参照されたい。

30

### 【0036】

図5は、本発明の特徴を組み込んだ語線レベル・アクセス・スキームのための書き込みプロセス500の一例示的実施態様を記述した流れ図である。図5に示されているように、例示的語線レベル書き込みプロセス500は、最初に、ステップ510の間、 $j \times k$  個のセクタを収集する。 $j$  は、フラッシュ・セル・アレイ300内の語線当たりのページ数であり、 $k$  はページ当たりのセクタの数である。ステップ510の間、1つまたは複数のページには、場合によっては、データの3つのすべてのページが有効になるまでの間、例えばデータ管理ブロック110内のメモリ回路を使用したバッファリングが必要であることに留意されたい（図3の例示的3-ビット-パー-セル実施形態の場合）。次に、語線レベル書き込みプロセス500は、ステップ520の間、データの $j$  個のページを符号化ブロックに符号化する。符号化ブロックは、任意選択で、ステップ530の間、 $j$  個のページに

40

50

分割される。次に、ステップ 540 の間、 $j$  個のページがフラッシュ・セル・アレイ 300 の中にプログラムされる。

#### 【0037】

本発明の様々な実施形態では、図 1 に示されている符号器 140 を使用することにより、単一の符号および符号レートを使用して、データの  $j$  個のページをまとめて符号化することができ、あるいは図 4 に示されている符号器 420 を使用することにより、(個々のページ毎に独自の符号および符号レートを有する) 最大  $j$  個の符号および符号レートを使用して独立して符号化することができることに留意されたい。さらに、ジョイント符号化スキームの場合、ステップ 530 の間の分割は、通常、図 5 に示されているように、ステップ 520 の符号化の後に実施され、一方、独立符号化スキームの場合、データは、通常、ステップ 520 の符号化に先立って複数のページに分割されることに留意されたい。10

#### 【0038】

図 6 は、本発明の特徴を組み込んだ語線レベル・アクセス・スキームのための読み出しプロセス 600 の一例示的実施態様を記述した流れ図である。図 6 に示されているように、例示的語線レベル読み出しプロセス 600 は、最初に、ステップ 610 の間、少なくとも 1 つのセクタを読み出す要求を受け取る。次に、語線レベル読み出しプロセス 600 は、ステップ 620 の間、知られているマッピング技法を使用して、要求されたセクタを有する語線を識別する。語線レベル読み出しプロセス 600 は、ステップ 630 の間、例えば語線に記憶されているすべてのページを連続的に読み出すことによって、識別された語線を読み出し、また、ステップ 640 の間、最大  $j$  個のページを得るために、語線から読み出されたデータのブロックを復号化する。本発明の他の代替実施形態では、ステップ 630 の間、語線内のセルに対する電圧値などのソフト情報が、語線レベル読み出しのための語線から読み出され、読み出されたソフト情報に基づいて、ステップ 640 の間、最大  $j$  個のページを復号化することができる。十分なソフト情報を有することにより、語線内のすべてのページを復号化することができる。本発明の様々な実施形態では、語線から読み出されたデータのブロックは、ステップ 520 の間に如何にしてデータがフラッシュ・メモリに書き込まれたかに基づいて、単一の符号および符号レートを使用して復号化することができ、あるいは(個々のページ毎に独自の符号および符号レートを有する) 最大  $j$  個の符号および符号レートを使用して独立して復号化することができることに留意されたい。最後に、語線レベル読み出しプロセス 600 は、ステップ 650 の間、書込みプロセス 500 の間に生成されたメモリ・マップを使用して、要求されたセクタを復号化されたページから獲得する。20

#### 【0039】

##### 可変符号レート多重レベル・セル

上で既に示したように、本発明の一態様によれば、個々のページ毎に異なる符号および / または符号レートを使用して語線内の個々のページを独立して符号化および復号化することができる。一変形形態では、語線内の個々のページは、異なる符号レートを使用して符号化することができる。図 7 は、語線内の個々のページが異なる符号レートで同じ長さに符号化される、本発明の特徴を組み込んだ可変符号レート符号化スキーム 700 を示したものである。図 7 の例示的実施態様に示されているように、下位ページおよび中位ページ 711、712 は、同じ符号レートを使用して符号化され、また、同じ量のユーザ・データ 720 およびパリティ・ビット 730 を備えている。上位ページ 713 は、ページ 711、712 と比較すると、より低い符号レートを使用して符号化され、したがってより少ないユーザ・データ 720 を符号化し、利用可能なより多くの数のパリティ・ビット 730 を有している。例えば、符号化された下位ページおよび中位ページ 711、712 は、7 個のセクタを備えることができ、一方、符号化された上位ページ 713 は、6 個のセクタを備えることができる。以下、図 8 ないし 11 に関連して、図 7 の可変符号レート符号化スキーム 700 をサポートするための適切な書込みプロセスおよび読み出しプロセスについてさらに説明する。40

#### 【0040】

10

20

30

40

50

したがって、本発明によれば、語線内のページが同じ符号化長を有し、かつ、異なる非符号化長を有するように符号レートを選択することができる。以下で説明するように、コントローラ100は、受け取ったデータ・ストリームをページのユーザ・データ・サイズに基づいて、また、プログラミングのために利用することができるフラッシュ・メモリ内の1つまたは複数のページ・タイプ(つまり符号レートおよびページ当たりのセクタの数)に基づいて分割することができる。ページ位置は、フォーマット効率、読み出し速度および書き込み速度の点でシステム性能が最大化されるように選択することができる。

#### 【0041】

図8および9は、それぞれ、個々のページが整数個のセクタを備えている場合における、フラッシュ・メモリ130に書き込むための可変符号レート・プロセスおよびフラッシュ・メモリ130から読み出すための可変符号レート・プロセスを示したものである。図10および11は、それぞれ、1つまたは複数のページが非整数個のセクタを備えることができ、また、所与のセクタが複数のページにまたがることができる場合における、フラッシュ・メモリ130に書き込むための可変符号レート・プロセスおよびフラッシュ・メモリ130から読み出すための可変符号レート・プロセスを示したものである。

10

#### 【0042】

図8は、個々のページが整数個のセクタを備えている場合における、フラッシュ・メモリ130に書き込むための可変符号レート書込みプロセス800の一例示的実施態様を記述した流れ図である。通常、書き込みプロセス800には、符号化されているページ・タイプ(つまりページ・レベル)に基づいてユーザ・データを分割するためのページ・レベル・アクセス・スキームおよび新規な技法が使用されている。さらに、書き込みプロセス800には、同じく、識別されたページ・タイプに関連する適切な符号レートが使用されている。例えば、一例示的実施態様では、語線の下位ページおよび中位ページは、ユーザ・データの8個のセクタを備えることができ、一方、上位ページは、ユーザ・データの7個のセクタを備えることができる。したがって、下位ページまたは中位ページがプログラムされている場合、ユーザ・データの8個のセクタを蓄積しなければならず、一方、上位ページがプログラムされている場合、ユーザ・データの7個のセクタを蓄積しなければならない。

20

#### 【0043】

図8に示されているように、書き込みプロセス800は、最初に、ステップ810の間、書き込まれている現在のページのページ・タイプ(つまりページ・レベルおよび/または偶数ページまたは奇数ページ)を決定し、また、ステップ820の間、ページ当たりのセクタの数、および決定されたページ・タイプに対する符号および/または符号レートを決定する。書き込みプロセス800は、ステップ830の間、現在のページ・タイプに対して、決定された数のセクタを蓄積する。ステップ840の間、蓄積されたデータが現在のページに対する符号および符号レートを使用して符号化され、また、ステップ850の間、フラッシュ・セル・アレイ300にページが書き込まれる。

30

#### 【0044】

図9は、個々のページが整数個のセクタを備えている場合における、フラッシュ・メモリ130から読み出すための可変符号レート読み出しプロセス900の一例示的実施態様を記述した流れ図である。通常、読み出しプロセス900にはページ・レベル・アクセス・スキームが使用されている。図9に示されているように、例示的可変符号レート・ページ・レベル読み出しプロセス900は、最初に、ステップ910の間、少なくとも1つのセクタを読み出す要求を受け取る。次に、可変符号レート・ページ・レベル読み出しプロセス900は、ステップ920の間、要求されたセクタを有するページを識別する。可変符号レート・ページ・レベル読み出しプロセス900は、ステップ930の間、識別されたページを読み出し、次に、ステップ940の間、現在のページ・タイプに対する適切な符号および/または符号レートを使用してページを復号化する。ステップ950の間、要求されたセクタが、メモリ・マップを使用して、復号化されたページから獲得される。

40

#### 【0045】

50

上で既に示したように、図10および11は、それぞれ、1つまたは複数のページが非整数個のセクタを備えることができ、また、所与のセクタが複数のページにまたがることができる場合における、フラッシュ・メモリ130に書き込むための可変符号レート・プロセスおよびフラッシュ・メモリ130から読み出すための可変符号レート・プロセスを示したものである。

#### 【0046】

セクタが複数のページにまたがることができる（例えば個々のページが非整数個のセクタを有する）一実施態様では、可変符号レート・スキームを実施するためには、マルチ・ページ・アクセス技法または語線レベル・アクセス技法を使用しなければならない。図10は、個々のページが非整数個のセクタを備え、また、所与のセクタが複数のページにまたがることができるとする場合における、フラッシュ・メモリ130に書き込むための可変符号レート書込みプロセス1000の一例示的実施態様を記述した流れ図である。通常、書き込みプロセス1000には、符号化されているページ・タイプ（つまり下位ページ、中位ページまたは上位ページ、あるいは偶数ページまたは奇数ページなどのページ・レベル）に基づいてユーザ・データを分割するためのマルチ・ページ・アクセス・スキームまたは語線レベル・アクセス・スキームおよび新規な技法が使用されている。さらに、書き込みプロセス1000には、同じく、識別されたページ・タイプに関連する適切な符号レートが使用されている。図10に示されているように、書き込みプロセス1000は、最初に、ステップ1010の間、書き込まれている現在のページのページ・タイプを識別し、また、ステップ1020の間、ページ当たりのセクタの数、および決定されたページ・タイプに対する符号および/または符号レートを決定する。この場合も、ページ当たりのセクタの数は非整数個であってもよいことに留意されたい。書き込みプロセス1000は、ステップ1030の間、現在のページ・タイプに対して、決定されたすべての数のセクタまたはその一部を蓄積する。書き込みプロセス1000は、次に、ステップ1040の間、存在していれば、次のページのために残りのセクタのごく一部をバッファする。このバッファリングは、例えば、データ管理ブロック110内のメモリ回路内で実施することができる。ステップ1050の間、蓄積されたデータが現在のページ・タイプに対する符号レートを使用して符号化され、また、ステップ1060の間、マルチ・ページ・アクセス・スキームまたは語線レベル・アクセス・スキームを使用することが適切である場合、それを使用して、符号化されたデータがフラッシュ・セル・アレイ300に書き込まれる。通常、マルチ・ページ・アクセス・スキームの場合、複数のページが符号化されるまでの間、ステップ1060に先立ってステップ1010ないし1050が繰り返される。次に、知られている技法を使用して、符号化されたこれらのページが例えば逐次フラッシュ・メモリに書き込まれる。語線レベル・アクセス・スキームの場合、語線内のすべてのページが符号化されるまでの間、ステップ1060に先立ってステップ1010ないし1050が繰り返される。次に、例えば知られている技法を使用して語線内のすべてのページを逐次書き込むことにより、すべての語線がフラッシュ・メモリに書き込まれる。

#### 【0047】

図11は、1つまたは複数のページが非整数個のセクタを備えることができ、また、所与のセクタが複数のページにまたがることができるとする場合における、フラッシュ・メモリ130から読み出すための可変符号レート・プロセス1100の一例示的実施態様を記述した流れ図である。通常、読み出しプロセス1100にはマルチ・ページ・アクセス・スキームまたは語線レベル・アクセス・スキームが使用されている。図11に示されているように、例示的可変符号レート読み出しプロセス1100は、最初に、ステップ1110の間、少なくとも1つのセクタを読み出す要求を受け取る。次に、可変符号レート読み出しプロセス1100は、ステップ1120の間、要求されたセクタを有する1つまたは複数のページを識別する。

#### 【0048】

ステップ1130の間、セクタが单一のページまたは複数のページにまたがっているかどうかを決定するための試験が実施される。ステップ1130の間に、セクタが单一のペ

10

20

30

40

50

ージにまたがっていることが決定されると、ステップ 1140 の間、ページ・レベル・アクセス技法を使用してそのページが読み出される。しかしながら、ステップ 1130 の間に、セクタが複数のページにまたがっていることが決定されると、ステップ 1150 の間、マルチ・ページ・アクセス技法または語線レベル・アクセス技法を使用してそれらのページが読み出される。通常、マルチ・ページ・アクセス・スキームの場合、複数のページが読み出され、また、語線レベル・アクセス・スキームの場合、すべての語線が読み出される。フラッシュ・メモリからページを逐次読み出すことにより、複数のページまたはすべての語線を読み出すことができる。語線レベル読み出しの他の代替実施形態では、語線内のセルの電圧値などのソフト情報が語線から読み出され、読み出されたソフト情報に基づいてページを復号化することができる。十分なソフト情報を有することにより、語線内のすべてのページを復号化することができる。

10

## 【0049】

次に、可変符号レート読み出しプロセス 1100 は、ステップ 1160 の間、1つまたは複数のこれらのページ・タイプ（つまり 1 つまたは複数のレベルおよび / または偶数ページあるいは奇数ページ）に対する適切な符号および / または符号レートを使用して、読み出された 1 つまたは複数のページを復号化する。最後に、可変符号レート読み出しプロセス 1100 は、ステップ 1170 の間、メモリ・マップを使用して、要求されたセクタを 1 つまたは複数の復号化されたページから獲得する。

## 【0050】

多重レベル・セルにおけるクロス・ページ記憶

本発明の他の実施形態では、ページは、物理ページの境界を越えてあふれ出ることができる。その場合、図 3 に示されているように、データを分割し、かつ、符号化するために使用される論理ページと、語線中に記憶される物理ページとを区別することができる。論理ページは、例えば図 4 に示されている符号化スキームを使用して符号化することができる。通常、語線中の論理ページは、同じ非符号化長（つまり同じ量のユーザ・データ）を有することができるが、符号化長は異なっている。例えば、同じユーザ・データ長を有する論理ページのための可変符号レート実施態様は、長さが異なる符号化論理ページに導くことができ、その場合、論理ページの一部が語線内の 1 つのページからその語線内の他のページへスピルオーバーすることになる。本発明は、この方法で、語線内のセル（スピルオーバー・セルと呼ばれている）の一部を使用して、物理ページ境界を越える論理データ部分を記憶することを企図している。この場合、スピルオーバー・セルは、通常のセルとは異なり、同じ論理ページに属する少なくとも 2 つのビットを記憶することができる。以下で説明するように、スピルオーバー・セルは、語線内の他のセルと同時にプログラムすることができ、あるいは物理ページ中にシフトする他の論理ページがプログラムされた後にプログラムすることも可能である。一例示的実施態様では、スピルオーバー・セル 1220 を使用して、上位ページ 2 のための追加パリティ・ビットを記憶することができる。

20

## 【0051】

図 12 は、通常のセル 1210 およびスピルオーバー・セル 1220 を備えたマルチ・ページ・セル語線 1200 を示したものである。図 12 の例示的実施形態では、下位論理ページ 0 および中位論理ページ 1 は、同じ符号化長を有しており、また、上位論理ページ 2 は、物理ページ 0 および 1 の中へスピルオーバーしている。一実施態様では、スピルオーバー・セル 1220 をプログラミングすることなく、最初に論理ページ 0 および 1 を語線 1200 の通常のセル 1210 の中にプログラムすることができる。次に、論理ページ 2 が通常のセル 1210 の上位ページの中、およびスピルオーバー・セル 1220 のすべてのページの中にプログラムされる。例えば、下位ページ、中位ページおよび上位ページ 0、1、2 は、従来のフラッシュ・メモリと同様の方法で通常のセル 1210 の中にプログラムすることができる。上位ページがプログラムされると、スピルオーバー・セル 1220 の下位ビット、中位ビットおよび上位ビットが同じくプログラムされる（例えば通常のセルの上位ページ・プログラミングの直後に実施される）。

30

## 【0052】

40

50

他の実施態様では、マルチ・ページ・アクセス技法または語線レベル・アクセス技法を使用して、通常部分およびスピルオーバ部分を含むすべての物理ページが、上で説明した図5と同様の方法で同時にプログラムされる。例えば、データ管理ユニット110は、複数のセクタを収集し、かつ、集合体化されたデータをj個の論理ページに分割することができる。次に、最大j個の符号器を使用してこのj個の論理ページを符号化することができる。データ管理ユニット110は、次に、符号化されたデータをj個の物理ページに分割し、次に、分割されたこれらの物理ページがディスクに書き込まれる。ディスクには、物理ページの通常のセクションおよびスピルオーバ・セクションの両方を同時に書き込むことができる。j個の物理ページは、知られている技法を使用してフラッシュ・セル・アレイに逐次書き込むことができる。本発明の他の実施形態では、論理ページおよび物理ページの数は異なっていてもよく、データ管理ユニットは、データを収集した後にセクタをj個の論理ページに分割することができ、また、プログラミングのための符号化の後に、符号化されたデータをj'個の物理ページに分割することができる。

10

#### 【0053】

スピルオーバしない論理ページは、例えばページ・レベル・アクセス技法を使用して互いに独立してプログラムし、かつ、読み出すことができる。スピルオーバする論理ページがプログラムされ、あるいは読み出されると、図5、6、10、11に関連して上で説明したように、マルチ・ページ・アクセス技法または語線レベル・アクセス技法を使用して少なくとも2つの物理ページをアクセスしなければならない。

20

#### 【0054】

他の変形形態では、最初に、スピルオーバ・セルのない物理ページ（つまり図12の例における物理ページ2）のみを読み出すことによってスピルオーバ・ページを読み出すことができる。例えば巡回冗長検査（CRC）符号またはパリティ・チェック符号によって決定される復号化誤りが生じると、同じくスピルオーバ・セル1220を読み出すことができる。復号化誤りの場合における他のオプションは、復号化のためのスピルオーバ・セルを備えたすべての論理ページを得るために、同じく他の物理ページ（つまり図12の物理ページ0および1）を読み出すことである。別法としては、他の物理ページ（つまり図12の物理ページ0および1）が既に読み出され、かつ、バッファに記憶されている場合、スピルオーバ・セルに記憶されているデータを得るために、バッファからこれらのページを読み出すことも可能である。復号化誤りの場合における他のオプションは、スピルオーバ・セル1220を備えたすべての論理ページを得るために、すべての語線1200を読み出すことである。

30

#### 【0055】

##### 多段復号化

図13は、本発明の特徴を組み込んだ多段復号器1300の略ブロック図である。図13に示されているように、多段復号器1300では、対応する復号器1310-0ないし1310-2によってコンポーネント符号が連続的に復号化される。一例示的多段復号器1300についてのより詳細な説明については、例えば、参照により本明細書に組み込まれている、U.Wachsmannら、「Multilevel Codes: Theoretical Concepts and Practical Design Rules」、IEEE Transaction Information Theory、Vol.45、No.5、1361~91頁（1999）を参照されたい。

40

#### 【0056】

本発明によれば、多段復号器1300は、語線内の複数のページを復号化し、例えば、復号器1310-0などの1つのページのための復号器は、総合誤り率を改善するために、復号器1310-1などの他のページの復号器に決定を供給している。図13では、yはデマッパからの出力であり、また、

#### 【0057】

【数1】

$\hat{b}^0, \hat{b}^1$

および

【0058】

【数2】

$\hat{b}^2$

は、それぞれページ0、1および2のための復号器の出力部分で復号化されたビットである。一代替実施態様では、1つのページのための復号器は、ログ尤度比(LLR)またはソフト情報を他のページのための復号器に供給することができる。図13には、一例示的復号化順序が示されており、決定は、最下位ページ0から最上位ページ1へ供給される。本発明の精神から逸脱することなく、他の復号化順序、例えばページ1から0へ、0から2への順序を実施することも可能である。

10

【0059】

本発明の他の態様では、最初に、他のページを復号化することなく1つのページを復号化することができ、あるいは他のページから独立して1つのページを復号化することができる。例えば誤りパリティ・チェックによって示される復号化誤りが生じると、図13に示されている多段復号化を実施するために、語線からの他のページを読み出すことができる。

20

【0060】

多段復号化を使用した多重レベル符号化は、個々のビット・レベルにおける符号器レートが個々のビット・レベル・チャネルの容量と整合する場合、シャノン容量に近づくことができることが分る。上で既に示したように、本発明によれば、より高い信頼性を必要とするページには、より強力な符号またはより低い符号レートを使用することができる。したがって、選択された符号レートが実質的にビット・レベル・チャネルの容量と整合する場合、記憶容量をシャノン容量に近づけることができる。

【0061】

#### 製造のプロセス、システムおよび物品詳細

本明細書における多くの流れ図は、複数のステップの一例示的シーケンスを記述したものであるが、シーケンスの変更が可能であることも同じく本発明の一実施形態である。アルゴリズムの様々な置換は、本発明の代替実施形態として企図されている。以上、本発明の例示的実施形態について、ソフトウェア・プログラムにおける処理ステップに関連して説明したが、当業者には明らかであるように、ソフトウェア・プログラムにおける処理ステップとしてのデジタル領域の中で、回路エレメントまたは状態マシンによるハードウェアの中で、あるいはソフトウェアとハードウェアの両方の組合せの中で様々な機能を実施することができる。このようなソフトウェアは、例えばデジタル信号プロセッサ、専用集積回路、マイクロ・コントローラあるいは汎用コンピュータに使用することができる。このようなハードウェアおよびソフトウェアは、集積回路内で実施される回路の中で具体化することができる。

30

【0062】

したがって本発明の機能は、これらの方針を実践するための方法および装置の形態で具体化することができる。本発明の1つまたは複数の態様は、例えば、記憶媒体に記憶され、マシンにロードされ、および/またはマシンによって実行されるものであれ、あるいは何らかの伝送媒体を介して伝送されるものであれ、プログラム・コードの形態で具体化することができ、このプログラム・コードがコンピュータなどのマシンにロードされ、かつ、マシンによって実行されると、そのマシンは、本発明を実践するための装置になる。汎用プロセッサ上で実施されると、プログラム・コード・セグメントは、プロセッサと相俟って、特定の論理回路と同様に動作するデバイスを提供する。また、本発明は、集積回路、デジタル信号プロセッサ、マイクロプロセッサおよびマイクロ・コントローラのうち

40

50

の1つまたは複数の中で実施することも可能である。

【0063】

当分野で知られているように、本明細書において説明されている方法および装置は、コンピュータ可読コード手段がその上に具体化されたコンピュータ可読媒体をそれ自体が備えた製造物品として分散させることができる。コンピュータ可読プログラム・コード手段は、本明細書において説明されている方法を実行し、あるいは本明細書において説明されている装置を生成するために、すべてのステップまたはステップの一部を実行するべくコンピュータ・システムと連携して動作することができる。コンピュータ可読媒体は、記録可能媒体（例えばフロッピー・ディスク、ハード・ドライブ、コンパクト・ディスク、メモリ・カード、半導体デバイス、チップ、専用集積回路（ASIC））であっても、あるいは伝送媒体（例えば光ファイバ、ワールド・ワイド・ウェブ、ケーブル、または時分割多重アクセス、符号分割多重アクセスを使用した無線チャネル、または他の無線周波チャネルを備えたネットワーク）であってもよい。コンピュータ・システムとの使用に適した情報を記憶することができる、知られている、あるいは開発されている任意の媒体を使用することができる。コンピュータ可読コード手段は、コンピュータによる、磁気媒体上の磁気の変化あるいはコンパクト・ディスクの表面の高さの変化などの命令およびデータの読み出しを可能にするための任意の機構である。

10

【0064】

本明細書において説明されているコンピュータ・システムおよびサーバの各々には、本明細書において開示されている方法、ステップおよび機能を実施するように関連するプロセッサを構成することができるメモリが含まれている。メモリは、分散させることができ、つまり局部メモリにすることができる、また、プロセッサは、分散させることも、あるいは単独のプロセッサにすることも可能である。メモリは、電気メモリ、磁気メモリもしくは光学メモリ、またはこれらのタイプあるいは他のタイプの記憶装置の任意の組合せとして実施することができる。さらに、「メモリ」という用語は、関連するプロセッサによってアクセスされるアドレス指定可能空間におけるアドレスから読み出すことができ、あるいはこのアドレスに書き込むことができるあらゆる情報を包含するべく十分広義に解釈されたい。この定義によれば、関連するプロセッサは、ネットワークからの情報を検索することができるため、ネットワーク上の情報は、依然としてメモリ内に存在している。

20

【0065】

本明細書において示され、かつ、説明されている実施形態および変形形態は、単に本発明の原理を示したものにすぎないこと、また、当業者によって、本発明の範囲および精神から逸脱することなく、様々な修正を実施することができることを理解されたい。

30

【 叁 1 】

【 図 2 】

【 図 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図 1 3】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2009/036810

A. CLASSIFICATION OF SUBJECT MATTER

INV. G06F11/10 G11C11/56

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G06F G11C

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                   | Relevant to claim No. |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X        | US 2007/089034 A1 (LITSYN SIMON [IL] ET AL) 19 April 2007 (2007-04-19)<br>paragraph [0010]<br>paragraph [0017]<br>paragraph [0021] – paragraph [0022]<br>paragraph [0049] – paragraph [0053]<br>claims 1,2; figure 2 | 1-5, 7-11             |

| A        | US 2007/300130 A1 (GOROBETS SERGEY ANATOLIEVICH [GB])<br>27 December 2007 (2007-12-27)<br>paragraph [0018] – paragraph [0023]<br>paragraph [0059] – paragraph [0060]<br>paragraph [0072]                             | 1-5, 7-11             |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the International filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the International filing date but later than the priority date claimed

\*T\* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

\*&\* document member of the same patent family

Date of the actual completion of the International search

22 June 2009

Date of mailing of the International search report

05/10/2009

## Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

## Authorized officer

Harms, Juergen

**INTERNATIONAL SEARCH REPORT**

International application No.

PCT/US2009/036810

**Box No. II Observations where certain claims were found unsearchable (Continuation of item 2 of first sheet)**

This International search report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.: because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.: because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful International search can be carried out, specifically:

3.  Claims Nos.: because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

**Box No. III Observations where unity of invention is lacking (Continuation of item 3 of first sheet)**

This International Searching Authority found multiple Inventions in this International application, as follows:

see additional sheet

1.  As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fees, this Authority did not invite payment of additional fees.

3.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:

4.  No required additional search fees were timely paid by the applicant. Consequently, this International search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:

see annex

**Remark on Protest**

- The additional search fees were accompanied by the applicant's protest and, where applicable, the payment of a protest fee.

- The additional search fees were accompanied by the applicant's protest but the applicable protest fee was not paid within the time limit specified in the invitation.

- No protest accompanied the payment of additional search fees.

International Application No. PCT/US2009 /036810

**FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210**

This International Searching Authority found multiple (groups of) inventions in this international application, as follows:

1. claims: 1-5, 7-11

Plural pages coded/decoded as a block

2. claims: 12-20, 33 and 34

Code or code rate associated with page

3. claims: 21-27

Number of sectors is function of page type

4. claims: 6, 28-32 and 35

Mixed storage of encoded logical pages having different lengths

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2009/036810

| Patent document cited in search report | Publication date | Patent family member(s)                                                                      | Publication date                                                   |

|----------------------------------------|------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| US 2007089034                          | A1 19-04-2007    | EP 1934854 A2<br>WO 2007043042 A2<br>JP 2009512055 T<br>KR 20080076902 A<br>US 2009070657 A1 | 25-06-2008<br>19-04-2007<br>19-03-2009<br>20-08-2008<br>12-03-2009 |

| US 2007300130                          | A1 27-12-2007    | NONE                                                                                         |                                                                    |

## フロントページの続き

| (51) Int.Cl.                   | F I                   | テーマコード(参考) |

|--------------------------------|-----------------------|------------|

| <b>G 0 6 F 12/02 (2006.01)</b> | G 0 6 F 12/00 5 9 7 U |            |

|                                | G 0 6 F 12/02 5 7 0 A |            |

|                                | G 0 6 F 12/16 3 1 0 A |            |

|                                | G 0 6 F 12/16 3 4 0 F |            |

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,SE,SI,S K,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BR,BW, BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,K E,KG,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL ,PT,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(特許庁注:以下のものは登録商標)

### 1. フロッピー

|           |                                                                                                                                 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| (74)代理人   | 100128657<br>弁理士 三山 勝巳                                                                                                          |

| (74)代理人   | 100160967<br>弁理士 濱 口 岳久                                                                                                         |

| (72)発明者   | バーガー,ハーレイ,エフ.,ジュニア<br>アメリカ合衆国 9 5 1 2 0 カリフォルニア,サンホセ,マックアビー エステイツ ピーアイ. 1 2 9 1                                                 |

| (72)発明者   | ハラッシュ,エリッチ,エフ.<br>アメリカ合衆国 1 8 0 1 7 ペンシルヴァニア,ペスレヘム,バーバリー ストリート 5 1 0 5                                                          |

| (72)発明者   | イヴコヴィック,ミロズ<br>アメリカ合衆国 1 8 1 0 4 ペンシルヴァニア,アレンタウン,スプリングハウス ロード 6 0 7 - アパートメント ケー                                                |

| (72)発明者   | クラッチコブスキー,ヴィクター<br>アメリカ合衆国 1 8 1 0 3 ペンシルヴァニア,アレンタウン,ルヤン ドライヴ 6 6 3                                                             |

| (72)発明者   | ヴィットヤイヴ,アンドレイ<br>アメリカ合衆国 9 5 1 3 5 カリフォルニア,サンホセ,ジョージ ブラウア ピーアイ. 2 7 8 3                                                         |

| (72)発明者   | ウィルアムソン,クリフトン<br>アメリカ合衆国 9 5 0 7 0 カリフォルニア,サラトガ,クロストブルック ドライヴ 1 9 6 9 4                                                         |

| (72)発明者   | イエン,ジョンソン<br>アメリカ合衆国 9 4 5 3 9 カリフォルニア,フレモント,ローレル グレン テラス 6 0 0                                                                 |

| F ターム(参考) | 5B018 GA04 HA21 HA35 NA06 QA16 RA11<br>5B060 AB26<br>5B125 BA01 BA19 CA11 DE08 EA05 EA10 FA01<br>5L106 AA10 BB02 FF04 FF05 GG05 |