(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4955935号

(P4955935)

(45) 発行日 平成24年6月20日(2012.6.20)

(24) 登録日 平成24年3月23日(2012.3.23)

(51) Int.Cl.

F 1

H01L 21/3205 (2006.01)

H01L 21/88

J

H01L 23/522 (2006.01)

H01L 21/768 (2006.01)

請求項の数 2 (全 13 頁)

(21) 出願番号 特願2005-141086 (P2005-141086)

(22) 出願日 平成17年5月13日 (2005.5.13)

(65) 公開番号 特開2006-13454 (P2006-13454A)

(43) 公開日 平成18年1月12日 (2006.1.12)

審査請求日 平成20年5月13日 (2008.5.13)

(31) 優先権主張番号 特願2004-154836 (P2004-154836)

(32) 優先日 平成16年5月25日 (2004.5.25)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 森本 弘之

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

審査官 須賀 亮介

最終頁に続く

(54) 【発明の名称】貫通孔形成方法および半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

表面の結晶方位が {100} 結晶面のシリコン基板の表面に、保護膜を形成し、前記 {100} 結晶面のシリコン基板の表面の {111} 結晶面の境界線に沿って、前記シリコン基板の表面から前記保護膜を除去して前記シリコン基板を露出させた四角形状の開口部を形成し、

前記開口部にレーザを照射して前記シリコン基板を貫通する貫通孔を形成し、前記貫通孔を、TMAH水溶液を用いたウェットエッチングによって、前記貫通孔の断面形状が四角形状となるように拡大し、

前記貫通孔の断面形状の対角線が、前記開口部の四角形状の一辺の長さと等しくなる前に前記エッチングを終了することを特徴とする貫通孔形成方法。

## 【請求項 2】

貫通孔により表裏面が電気的に接続されている半導体装置の製造方法において、表面の結晶方位が {100} 結晶面のシリコン基板の表面に、保護膜を形成し、

前記 {100} 結晶面のシリコン基板の表面の {111} 結晶面の境界線に沿って、前記シリコン基板の表面から前記保護膜を除去して前記シリコン基板を露出させた四角形状の開口部を形成し、

前記開口部にレーザを照射して前記シリコン基板を貫通する貫通孔を形成し、前記貫通孔を、TMAH水溶液を用いたウェットエッチングによって、前記貫通孔の断面形状が四角形状となるように拡大し、

10

20

前記貫通孔の断面形状の対角線が、前記開口部の四角形状の一辺の長さと等しくなる前に前記エッティングを終了し、

前記貫通孔の内側表面に絶縁層を形成し、前記絶縁層の内側表面に導電層を形成することで、前記シリコン基板の表裏面を電気的に接続することを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体基板に貫通孔を形成する貫通形成方法に関するものであり、更に、半導体基板に貫通孔を形成する事で半導体基板の表裏面を電気的に接続する半導体装置およびその製造方法に関するものである。

【背景技術】

【0002】

従来から、電子撮像装置や、光記録装置や、インクジェットプリンタヘッドのような半導体プロセスで形成される半導体装置は、半導体基板の表面に複数の能動素子が形成されている。そしてそれらの能動素子をお互いに電気的に接続することで様々な機能を、コンパクトに形成することを実現している。近年電子機器の小型化に伴い、半導体装置は更なる小型化、高密度化が要求されている。そこで半導体基板の裏面も配線領域として活用するため、半導体基板に貫通孔を形成しその表裏面を電気的に接続することが検討されている。

【0003】

半導体基板に貫通孔を形成する方法の一つにレーザによる加工を挙げることができる。レーザ加工により形成した貫通孔を利用して、半導体基板の表裏面を電気的に接続する方法は、特開2000-246474号（特許文献1）や、特開2000-246475号（特許文献2）に記載されている。これらの特許文献においては、まず表面の結晶方位が{100}や{110}結晶面であるシリコン基板にレーザを用いて貫通孔を形成する。その後、ウェット異方性エッティングにより貫通孔の内径の拡大を行う。次に貫通孔内部に化学気相堆積（CVD）や物理気相堆積（PVD）等により貫通孔の内側表面に絶縁膜を形成する。その後、絶縁膜の表面にスパッタ、メッキ、パターニング、エッティング等により導電膜を形成する。このようにして、表面と裏面を貫通孔内部の導電膜を介して電気的に接続した半導体基板を製造している。

【特許文献1】特開2000-246474号

【特許文献2】特開2000-246475号

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、前述の特許文献1、2に示したようなレーザ加工により貫通孔を形成し、その後エッティングにより内径を拡大する方法にはいくつかの課題がある。これは半導体基板をウェット異方性エッティングする場合、各結晶方位に対するエッチングレートは大きく異なることに起因する。表1にシリコン基板に対する結晶方位が{100}、{110}、{111}結晶面のエッティングレートを示す。

【0005】

10

20

30

40

## 【表1】

| シリコン基板のエッティングレート |      |

|------------------|------|

| {100}            | 0.60 |

| {110}            | 1.11 |

| {111}            | 0.02 |

| エッティング条件：        |      |

| TMAH 20パーセント水溶液  |      |

| 温度：80°C          |      |

10

## 【0006】

まず表面の結晶方位が{110}結晶面であるシリコン基板にレーザを用いて貫通孔を形成した後、ウェット異方性エッティングにより貫通孔の内径の拡大を行う場合について説明する。表面の結晶方位が{110}結晶面であるシリコン基板を使用した場合、レーザ加工により形成した貫通孔の内径を拡大する方向は、結晶方位が{111}結晶面である。表1からわかるように、結晶方位が{111}結晶面のシリコン基板のエッティングレートは、結晶方位が{100}面、{110}結晶面のシリコン基板に比べて極端に遅い。従って一旦形成した貫通孔をエッティングにより内径の拡大する方式においては、表面の結晶方位が{110}面のシリコン基板を使用する事は、産業上好ましいとは言えない。

20

## 【0007】

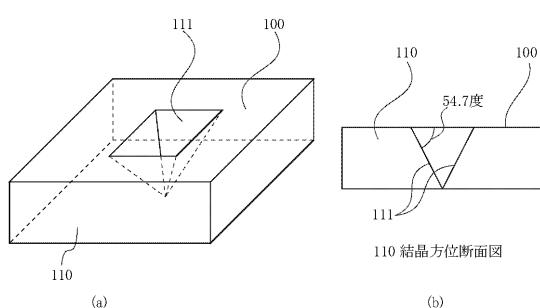

次に表面の結晶方位が{100}結晶面であるシリコン基板を用いた場合について説明する。図8に表面の結晶方位が{100}結晶面であるシリコン基板における、{111}結晶面、{100}結晶面、{110}結晶面のそれぞれの位置関係を示す。図8(a)は{100}シリコン基板における各結晶面の位置関係を示した斜視図で、図8(b)は{110}結晶方位方向に沿った断面図である。図8からわかるように、{100}結晶面と{110}結晶面はそれぞれ90度の位置関係を有し、{111}結晶面は{100}結晶面に対して約54.7度の位置関係を有している。

30

## 【0008】

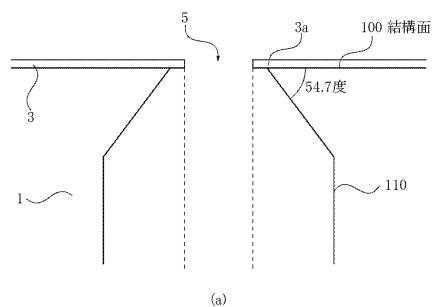

図9は表面の結晶方位が{100}結晶面であるシリコン基板にレーザを用いて貫通孔を形成した後、ウェット異方性エッティングにより貫通孔の内径の拡大を行った時の貫通孔の状態を示す模式図である。図9(a)は半導体基板の断面図であり、図9(b)はその上面図である。尚、図9(a)は、半導体基板の表面側の貫通孔近傍のみを示したものであり、半導体基板の裏面側も同様な状態となっている。図9(a)において点線で示しているのは、エッティングによる貫通孔の内径を拡大する前にレーザ加工により形成された貫通孔である。

40

## 【0009】

図9において1はシリコンからなる半導体基板、3は熱酸化膜からなり絶縁性を有する保護膜、5は貫通孔である。レーザ加工は半導体基板1の表面に絶縁保護膜3を形成した後に行うため、レーザ加工により形成される貫通孔の内径(点線で示す)と保護膜3の開口部の内径は一致している。表面の結晶方位が{100}結晶面であるシリコン基板の場合、レーザ加工により形成した貫通孔の内径を拡大する方向の結晶方位は{100}結晶面と{110}結晶面である。すなわちエッティングレートは早く容易にエッティングを行うことができる。

## 【0010】

50

しかしながら、結晶方位が { 1 1 1 } 結晶面である方向へはほとんどエッチングされない。前述したように、結晶方位が { 1 1 1 } 結晶面は、シリコン基板の表面の結晶方位が { 1 0 0 } 結晶面である面と約 54.7 度の角度をなしている。そのため、異方性エッチングにより内径を拡大するに従って、貫通孔 5 の開口部近傍の形状は、図 9 に示すように、約 54.7 度の角度を有するエッジ形状（逆テープ形状）となってしまう。また異方性エッチングを行えば行うほど、この逆テープ形状は大きくなっていく。

#### 【 0 0 1 1 】

図 9 に示した貫通孔の場合、半導体基板 1 の表面および裏面の開口部よりも、貫通孔内径が大きくなる。そのため、貫通孔 5 の内側表面に CVD や PVD 等により絶縁膜や導電膜を成膜する場合、均一な膜を形成することは困難であった。すなわち、貫通孔の開口部の内径が小さく、貫通孔の奥に行くほど内径が大きくなる逆テープ形状であると、CVD 等の場合、貫通孔内部の気体循環が阻害されて成膜効率が低下してしまう。また、スパッタ等の PVD の場合、貫通孔の入口から貫通孔内に直線的に進行する金属原子が、貫通孔内面には幾何学的に到達できない場合もある。その結果、絶縁膜や導電膜の膜厚を確保できず、絶縁不良や導通不良が発生していた。また、メッキにより導電膜を形成する場合も、貫通孔 5 の内部でメッキ液が滞留し貫通孔の外部とのメッキ液循環が阻害されるため、貫通孔内側表面のメッキ速度が低下する。そのため、導電膜の膜厚を確保できないため、導通不良となってしまう。

#### 【 0 0 1 2 】

また、CVD や PVD、メッキ処理において、鋭角形状先端部への成膜やメッキ膜の形成は困難であり、膜厚が低下し、絶縁不良および導通不良の起点となりやすい。また、貫通孔内部の封止工程や、その後の取り扱いにおいても鋭角形状先端部に局所的に圧力がかかりやすく、絶縁膜や導電膜が破損し、絶縁不良および導通不良の起点となりやすい。

#### 【 0 0 1 3 】

また、半導体基板 1 は、貫通孔 5 を形成後に半導体パターンを形成している。その際スピニコート等によってレジスト材の塗布を行うため、貫通孔 5 の内部は封止材により完全に封止する事が望ましい。封止手段としては、印刷法やディスペンサー、気圧差を利用した等による注入方式が考えられる。しかしながら、貫通孔 5 の開口部に逆テ - パがあると貫通孔 5 の内部へ封止材を完全注入する事が難しく、貫通孔 5 の内部に気泡残りが発生する可能性が高い。

#### 【 0 0 1 4 】

また、図 9 ( a ) に示すように半導体基板 1 には、厚さ 1  $\mu$ m 程度の熱酸化膜 3 はエッチングストップ層としての機能も有している。エッチングストップ層この熱酸化膜 3 は、半導体基板 1 の貫通孔 5 がエッチングによって内径の拡大されるため、ひさし部 3a が形成される。このひさし部 3a はわずかな圧力で容易に破損するため、工程の信頼性には大きな問題を生じていた。

#### 【 0 0 1 5 】

そこで本発明の目的は、半導体基板にレーザにより貫通孔を形成し、その後貫通孔の内径を拡大する場合であっても、貫通孔の開口部近傍に逆テープ形状を形成することなく、効率よく半導体基板に垂直な貫通孔を形成することにある。

#### 【課題を解決するための手段】

#### 【 0 0 1 6 】

前述の課題を解決するために本発明の貫通孔形成方法においては、表面の結晶方位が { 1 0 0 } 結晶面のシリコン基板の表面に、保護膜を形成し、前記 { 1 0 0 } 結晶面のシリコン基板の表面の { 1 1 1 } 結晶面の境界線に沿って、前記シリコン基板の表面から前記保護膜を除去して前記シリコン基板を露出させた四角形状の開口部を形成し、前記開口部にレーザを照射して前記シリコン基板を貫通する貫通孔を形成し、前記貫通孔を、TMAH 水溶液を用いたウェットエッチングによって、前記貫通孔の断面形状が四角形状となるように拡大し、前記貫通孔の断面形状の対角線が、前記開口部の四角形状の一辺の長さと等しくなる前に前記エッチングを終了することを特徴とする。

10

20

30

40

50

## 【0017】

本発明の半導体装置の製造方法においては、貫通孔により表裏面が電気的に接続されている半導体装置の製造方法において、表面の結晶方位が $\{100\}$ 結晶面のシリコン基板の表面に、保護膜を形成し、前記 $\{100\}$ 結晶面のシリコン基板の表面の $\{111\}$ 結晶面の境界線に沿って、前記シリコン基板の表面から前記保護膜を除去して前記シリコン基板を露出させた四角形状の開口部を形成し、前記開口部にレーザを照射して前記シリコン基板を貫通する貫通孔を形成し、前記貫通孔を、TMAH水溶液を用いたウェットエッチングによって、前記貫通孔の断面形状が四角形状となるように拡大し、前記貫通孔の断面形状の対角線が、前記開口部の四角形状の一辺の長さと等しくなる前に前記エッチングを終了し、前記貫通孔の内側表面に絶縁層を形成し、前記絶縁層の内側表面に導電層を形成することで、前記シリコン基板の表裏面を電気的に接続することを特徴とする。

10

## 【発明の効果】

## 【0019】

本発明によれば、表面の結晶方位が $\{100\}$ 結晶面の半導体基板に、ほぼ垂直な貫通孔を、迅速に形成することが可能となる。これによりCVDやPVD等による成膜性、メッキ性、孔封止性が良好であり、工程の信頼性を確保する事ができる。

## 【0020】

またレーザ加工に一旦貫通孔を形成したが、その内径を異方性エッチングにより拡大しているため、レーザ加工孔の周囲および内部に発生するドロスやデブリス等を消滅させ、かつ貫通孔内面が非常に滑らかな結晶面で形成された、高品位の貫通孔を形成する事が可能である。

20

## 【0021】

また本発明によれば、半導体基板表面および裏面の開口部に熱酸化膜などのエッチングストップ膜によるひさしが存在しないため、ひさしを除去する工程を省略する事が可能である。

## 【発明を実施するための最良の形態】

## 【0022】

次に、本発明の好適な実施の形態を図面を参照して説明する。

## 【実施例1】

## 【0023】

30

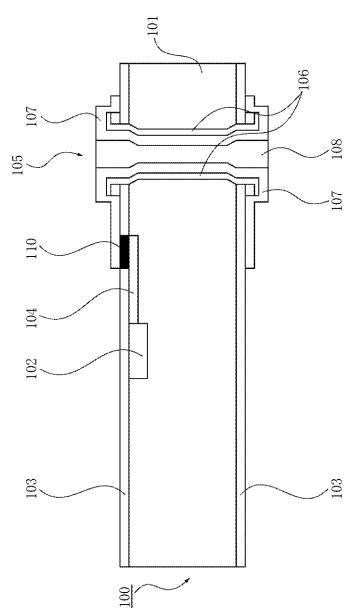

図1は本発明の実施例1に関わる半導体装置の断面図である。図中100は半導体装置であり、101は表面の結晶方位が $\{100\}$ 結晶面であるシリコン基板（以下、 $\{100\}$ シリコン基板）である。102は $\{100\}$ シリコン基板101上に形成された能動素子である。能動素子102は、 $\{100\}$ シリコン基板101に半導体プロセスにより作りこまれている。能動素子102としてはトランジスターや、インクジェットプリンタヘッド駆動素子、電子撮像素子、光記録素子等の機能性素子を適用することができる。尚、図1において能動素子102は $\{100\}$ シリコン基板101の片面にしか形成されていないが、両面に形成してもかまわない。103は、 $\{100\}$ シリコン基板101の表面に形成された熱酸化膜であり絶縁性を有する保護膜である。104は能動素子102から伸びている導電性の配線部である。配線部104の能動素子102と逆の端部には、外部接続電極110が形成されている。105は $\{100\}$ シリコン基板101の表裏面を貫通している貫通孔である。106は貫通孔105の内側表面と $\{100\}$ シリコン基板101表面の貫通孔105の開口部近傍を覆う絶縁層である。107は保護膜103の表面および絶縁層106の更に内側表面に形成された導電層である。108は貫通孔内部を充填する封止材である。導電層107は、外部接続電極110と電気的に接続されている。これにより、能動素子102は配線部104、外部接続電極110、導電層107を介して、 $\{100\}$ シリコン基板101の裏面と電気的に接続する事ができる。

40

## 【0024】

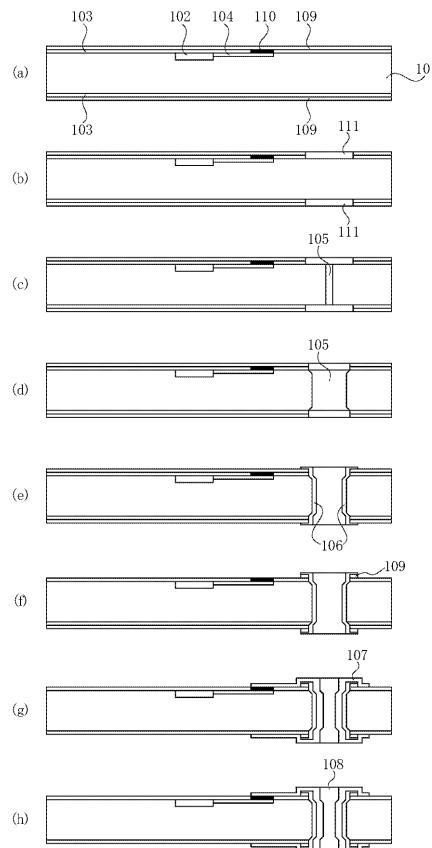

次に図1に示した半導体装置100の製造プロセスを図2(a)乃至図2(h)を使って説明する。図2(a)乃至図2(h)において、図1と同じ部材には同じ符号が付して

50

ある。

【0025】

まず図2(a)において、あらかじめ能動素子102が形成された{100}シリコン101基板を準備する。109は、能動素子102および配線部104を、後述するレーザ加工やエッティング、メッキ等による汚染から保護する保護層である。配線部104は、通常の半導体プロセスにより、あらかじめ{100}シリコン基板101上に形成されている。半導体基板としては、シリコン以外にゲルマニウム、セレン等の単一元素や、酸化物、硫化物、セレン化物、テルル化物、アンチモン化合物、ヒ素化合物、リン化合物等の化合物や有機半導体材料等を主成分としたものを用いることができる。

【0026】

{100}シリコン基板101の厚さは625μmであり、その形状としては、ウエハ状、四角形、多角形のものや、マイクロマシーン等で多用されている複雑に加工された形状とことができる。保護膜103は、電気的絶縁性を有し、かつ後述のTMAH(tetramethyl ammonium hydroxide, (CH<sub>3</sub>)<sub>4</sub>NOH)水溶液に対して、{100}シリコン基板101と比較して耐エッティング性を有する膜である。例えばSiO<sub>2</sub>、SiN、SiO等の絶縁性材料を、0.6μmから2μm程度成膜する事によって形成されている。保護層109は、例えば高分子ポリマー等の絶縁性材料を用いた膜であり、スピンドル塗布等により形成される。保護層109の膜厚は、1μm～3μmが好ましいがこの範囲に限定されるものではない。保護層109は、保護膜103、能動素子102、および配線部104を、後述するレーザ加工やエッティング、電着等による汚染、および電気的なダメージから保護することができるのであれば良い。外部接続電極110は金、銀、アルミ、銅、ケイ素などを主成分としている。また外部接続電極110の表面は保護膜103から露出して形成されている。

【0027】

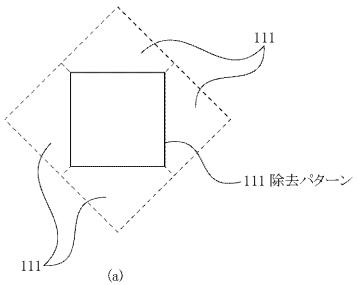

次に図2(b)において、{100}シリコン基板101の表面の、貫通孔形成する個所の保護膜103および保護層109を除去し、開口部111を形成する。保護膜103及び保護層109の除去方法としては、レジスト塗布、レジストパターニング、エッティングといった、典型的なリソグラフィープロセスや、レーザ加工で直接保護膜103を剥離する直接加工方法を使用することができる。

【0028】

開口部111は、{100}シリコン基板101をTMAH水溶液でエッティングする際に析出する{111}結晶面と{100}シリコン基板表面の境界線に沿った四角形状としている。これは後述の異方性エッティング工程で、開口部外郭より111結晶面を析出させるためである。また開口部111の大きさは、形成する貫通孔の3倍から5倍が好ましい。たとえば直径が30μmである時、100×100μm程度が好ましい。これは、開口部111の形状が大きいと、異方性エッティング終了時にエッティング速度の速い{110}結晶面が残ってしまうためであり、小さいと貫通孔形成に必要なエッティング時間が過剰にかかるてしまうからである。

【0029】

次に図2(c)において、開口部111の中央部に貫通孔105aが形成される。この貫通孔105aの形成方法としてはレーザ加工法が用いられる。レーザ加工法は、{100}シリコン基板101、保護膜103、および保護層109を除去できる波長、出力を備えたものである。例えばYAG、YLF、YVO<sub>4</sub>、ガラス、チサンサファイア等の固体レーザや、CO<sub>2</sub>、銅蒸気、エキシマ等のガスレーザ、もしくは色素レーザ等を使用する事ができる。レーザ加工法は{100}シリコン基板101の表面に対して、垂直な貫通孔105aを容易に形成できる。貫通孔105aの内径は、30μmである。

【0030】

次に図2(d)において、{100}シリコン基板101をTMAH水溶液などによりエッティング処理する。シリコン材料をTMAH水溶液でエッティングする場合、シリコンの結晶方位によってエッティング速度が異なる。そのため、エッティングの進行とともにエッチ

10

20

30

40

50

ング速度の早い面は消失し、最後にはエッティング速度の遅い面で形成された異方性の形状となる。このエッティング方法を、異方性エッティングという。その結果、貫通孔 105a は異方性エッティングにより内径を拡大され貫通孔 105b となる。貫通孔 105b の形状は、開口部 111 に対して 45 度回転した四角形状となる。この時、貫通孔 105b の内径の最大値が、長方形の頂点が開口部 111 よりも外側にはみ出さない位置で、エッティングによる内径の拡大は終了する。開口部 111 が  $100 \times 100 \mu\text{m}$  の正方形である場合、貫通孔 105b の孔径の最大値(対角線の距離)は、 $100 \mu\text{m}$  以下とする。尚、図 2 (d) に示す異方性エッティングの工程の詳細は後述する。

#### 【0031】

次に図 2 (e) において、貫通孔 105 の内部に絶縁層 106 を形成する。絶縁層 106 を形成する方法としては液相法が用いられる。液相法には、ディッピング、ディスペンス、印刷、電着、陽極酸化等が含まれる。液相法は、基板を高温にする必要がないため、あらかじめ能動素子 102 が形成された基板であっても使用する事が可能である。なお、絶縁層 106 は、本プロセス以降の半導体プロセスにおける温度等の雰囲気や、各プロセスで使用する薬品に耐えうる材料を選定する。絶縁層 106 の膜厚としては、 $1 \mu\text{m} \sim 30 \mu\text{m}$  程度が好ましいがこの範囲に限定されるものではない。後述の導電層 107 と {100} シリコン基板 101 の電気的な絶縁関係において、所定の抵抗値を上回る性能であれば良い。

#### 【0032】

次に図 2 (f) において、{100} シリコン基板 101 表面に形成されている保護層 109 を除去する。除去の方法としては、酸素プラズマ等により、全面一括除去される。このとき貫通孔 105b の端部に形成された絶縁層 106 も一部除去されるが、厚さの違いにより完全に除去されない。従って、貫通孔 105b の端部、絶縁層 106、および絶縁層 106 の下層にのみ保護層 109 が残る事になる。

#### 【0033】

次に図 2 (g) において、貫通孔 105b の内側表面に形成された絶縁層 106 の内側表面、および保護膜 103 上に、導電層 107 を形成する。導電層 107 は貫通孔 105b の内側表面、{100} シリコン基板 101 全体に形成される。貫通孔 105b の内側表面を経由して、{100} シリコン基板 101 の表裏面が電気的に接続される。導電層 107 は銅、ニッケル、パラジウム、金、銀、等の材料を使用する事ができる。導電層 107 の膜厚としては、 $0.5 \mu\text{m} \sim 1.0 \mu\text{m}$  が好ましいがこの範囲に限定されるものではない。外部接続電極 110 から貫通孔 105b の内部を経由して、{100} シリコン基板 101 の表裏面まで確実に接続し、回路抵抗値が所定の抵抗値を下回る性能であれば良い。

#### 【0034】

導電層 107 の製法としては、処理温度が 1000 を超える PVD や CVD を使用する事はできない。そこで、ドライメッキ、ウェットメッキ、ジェットプリントティング法、導電ペーストや溶融金属の成膜法等を、貫通孔 105 の形状やアスペクト比に応じて適宜選択することができる。

#### 【0035】

最後に図 2 (h) において、貫通孔 105 の内部は、封止材 108 によって完全に充填される。封止材 108 の材料としては、樹脂、溶融金属等が挙げられる。充填の方法としては、印刷、注入、貫通孔内部と外部の空気圧の差を利用する方法、等を利用する事ができる。

#### 【0036】

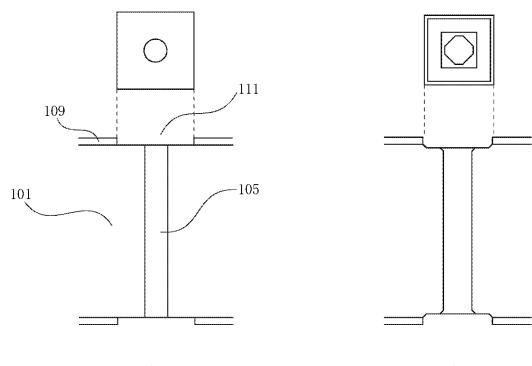

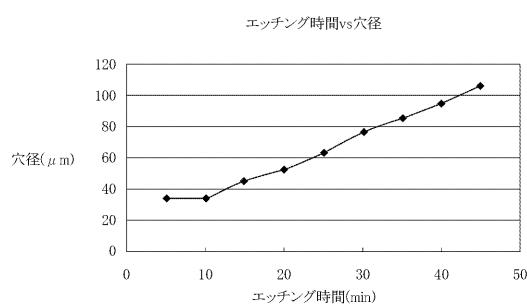

次に前述の図 2 (d) に示した異方性エッティングの工程を、図 3 を使って詳細を説明する。図 3 (a) 乃至図 3 (d) は、前述の図 2 (c) において形成した内径  $30 \mu\text{m}$  の貫通孔 105a を異方性エッティングする際の様子を示した模式断面図である。加工時間を 0 分 ~ 70 分まで順に変化させ、そのた時の貫通孔形状の変化を示している。エッティング条件は、TMAH・20 パーセント水溶液、エッティング液温度 : 80 である。

10

20

30

40

50

## 【0037】

図3(a)はエッティング直後(0分)の時の $\{100\}$ シリコン基板101の上面図と断面図である。図3(a)において $\{100\}$ シリコン基板101の表面には、保護膜103および保護層109が成膜されており、開口部111が形成されている。開口部111は、 $\{100\}$ シリコン基板101をTMAH水溶液でエッティングする際に析出する、 $\{111\}$ 結晶面と $\{100\}$ シリコン基板表面の境界線に沿った四角形状としておく。開口部111の中心には、レーザ加工により内径 $30\mu\text{m}$ の貫通孔105aが形成されている。この時貫通孔105は $\{100\}$ シリコン基板101に垂直に形成されている。

## 【0038】

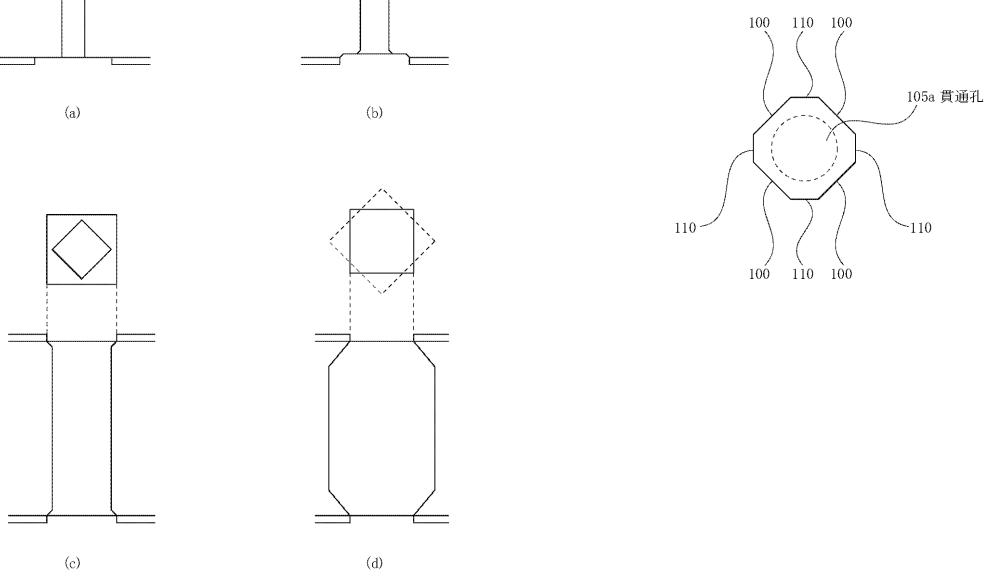

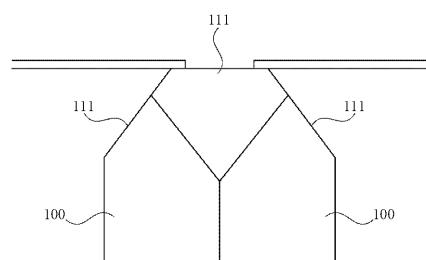

次に、図3(b)はエッティング経過(20分)の時の $\{100\}$ シリコン基板101の上面図と断面図である。このとき貫通孔105bは、 $\{100\}$ および $\{110\}$ 結晶面で形成された8角形の形状となっている。図4はこの時の貫通孔105aの横断面を示した模式図であり、貫通孔105aの内面における $\{100\}$ 結晶面と $\{110\}$ 結晶面の関係を示している。8角形の大きさは、対辺の距離が $50\mu\text{m}$ である。この8角形は、異方性エッティングによって貫通孔内部のSiが融解し、 $\{100\}$ および $\{110\}$ 結晶面が交互に析出するように形成される。

## 【0039】

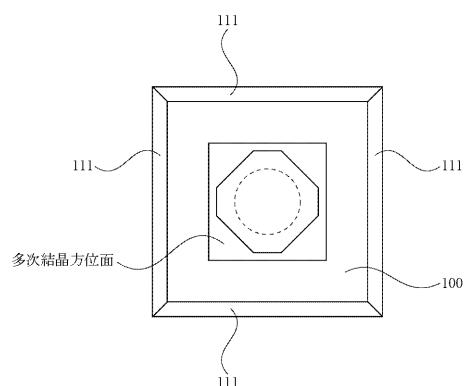

またこの時、開口部111の下面に位置する $\{100\}$ シリコン基板101の表面には、 $\{100\}$ 結晶面、 $\{111\}$ 結晶面、および貫通孔105bと $\{100\}$ シリコン基板101の表面との境界部には、複数の多次結晶方位の結晶面が析出している。図5は、この時の貫通孔105bの開口部近傍の様子を示した模式図である。図5(a)は貫通孔上面における結晶面を示した上面図で、図5(b)はその断面図である。

## 【0040】

図5(a)、(b)においてレーザ加工によって形成された貫通孔105aの内側表面は、図4に示す異方性エッティングの開始によって、ただちに融解し、 $\{100\}$ 結晶面、 $\{110\}$ 結晶面が析出する。この時、貫通孔105bの周辺に形成された開口部111内の $\{100\}$ シリコン基板101の表面は、 $\{100\}$ 結晶面が露出している。そのため、開口部111内のエッティングは、 $\{100\}$ シリコン基板101の板厚方向に進行する。また、貫通孔105bと $\{100\}$ シリコン基板101の表面の境界付近では、常に $\{100\}$ 、 $\{110\}$ 、 $\{111\}$ 結晶面よりもエッティング速度の速い多次結晶面が析出している。従って、エッティングによる内径の拡大を開始した直後の貫通孔105bの形状は、図9に示したような逆テープ方向に $\{111\}$ 結晶面が析出する事はない。

## 【0041】

次に、図3(c)はエッティング経過(40分)の時の $\{100\}$ シリコン基板101の上面図と断面図である。このとき貫通孔105bは、 $\{100\}$ 結晶面で囲まれ、開口部111とは45度傾いた位置関係にある4角形状となる。貫通孔105bの大きさは対辺が約 $75\mu\text{m}$ である。シリコン基板のエッティング条件において、 $\{110\}$ 結晶方位は $\{100\}$ 結晶方位に対して前述の表1に示すように2倍程度エッティング速度が速い。そのため、図3(b)の8角形状の貫通孔105bは、時間の経過とともに貫通孔の内面の $\{110\}$ 結晶面が消滅し、 $\{100\}$ 結晶面のみが残った4角形状となる。この時の貫通孔105bは $\{100\}$ シリコン基板101に対して垂直な形状をなしている。また、4角形状の貫通孔105bの対角線の長さと、4角形状の開口部111の一片の長さがほぼ等しい関係が最も好ましい。このとき貫通孔105bは逆テープ形状とならない最も径の大きい貫通孔とすることができます。

## 【0042】

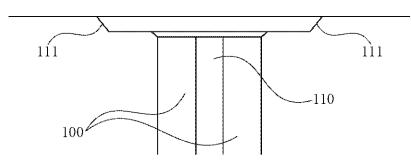

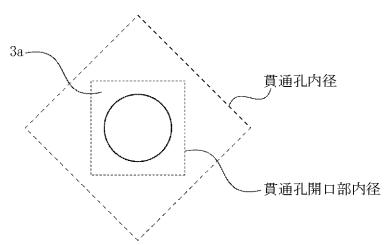

次に、図3(d)はエッティング経過(70分)の時の $\{100\}$ シリコン基板101の上面図と断面図である。このとき貫通孔105bは、その内径が開口部111よりも部分的に大きい逆テープ形状となっている。図6はこの逆テープ形状の概念を示す模式図である。図6は、図3(d)に示した状態からさらにエッティングを行い、貫通孔105bの内径が開口部111よりも完全に大きくなった状態を示している。

10

20

30

40

50

## 【0043】

図6(a)は貫通孔105bの上面図であり、その時の結晶面の状態を示している。図6(b)はその時の断面図である。図6(a)、(b)では、エッティングによる貫通孔105bの内径の拡大により、内径が開口部111の大きさを超えて、{100}シリコン基板101の表面の{100}結晶面が全て消失している。そのため、貫通孔105bの周辺には多次結晶面は析出せず、{100}シリコン基板101の板厚方向へのエッティング速度はほぼ0となる。それにより、貫通孔105bの表面付近より逆テーパ方向に{111}結晶面が析出する。従ってこの貫通孔形状は、前記課題で述べたように工程信頼性を低下させる形状であり、エッティング時間が最適条件から超過した状態である。

## 【0044】

10

図7は図3において説明したエッティング時間と貫通孔の孔径(頂点間の距離)との関係を示すグラフである。エッティング時間40~45分の時に、図3(c)の形状が得られた。このエッティング時間は、工程信頼性を低下させる逆テーパ形状の{111}結晶面は析出せず、かつ最大孔径が得られる条件である。更に、レーザ加工に伴って発生するドロス、デブリス等の加工残存物等の半導体溶融物、クラック、結晶欠陥等はエッティングにより全て消失することができる。また、貫通孔壁面は全て{100}結晶面が析出した非常に平滑な壁面が得られるため、後述する絶縁層や導電層の形成に最適な貫通孔状態となる。

## 【0045】

以上のような製造プロセスにより、外部接続電極110から貫通孔105を経由して{100}シリコン基板101の裏面側まで回路パターンを形成でき、能動素子102の信号を、{100}シリコン基板101の裏面に取り出すことが可能な電極構造を形成することが可能となる。

20

## 【図面の簡単な説明】

## 【0046】

【図1】本発明の実施形態における半導体装置の断面図

【図2】実施例1における半導体装置の製造プロセスを示す断面図

【図3】異方性エッティングの進行に伴う貫通孔の形状の変化を示す断面図

【図4】貫通孔内面における{100}結晶面と{110}結晶面の関係を示す図

【図5】貫通孔内面における{100}結晶面と{110}結晶面の多次結晶方位の関係を示す図

30

【図6】開口部および貫通孔上面における結晶面を示した図

【図7】異方性エッティングにおけるエッティングレートグラフ

【図8】{100}シリコン基板における各結晶面の位置関係を示す図

【図9】従来の貫通孔が形成された半導体基盤の断面図

## 【符号の説明】

## 【0047】

100 半導体装置

101 {100}シリコン基板

102 能動素子

103 絶縁膜

104 配線部

105 貫通孔

106 絶縁層

107 導電層

108 封止材

109 保護層

110 外部接続電極

111 開口部

40

【図1】

【図2】

【図3】

【図4】

【図5】

(a)

(b)

【図6】

(a)

(b)

【図7】

【図8】

(a)

(b)

【図9】

---

フロントページの続き

(56)参考文献 特開平04-299872(JP, A)

特開2000-246474(JP, A)

特開平05-243207(JP, A)

特開平03-253025(JP, A)

国際公開第00/050198(WO, A1)

特開2002-094082(JP, A)

特開2001-135785(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3205

H01L 21/3213

H01L 21/768

H01L 23/52-23/522

H01L 23/10

H01L 21/60

H01L 25/04-25/18

H01L 23/12

H01L 21/306-21/308