(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5111191号

(P5111191)

(45) 発行日 平成24年12月26日(2012.12.26)

(24) 登録日 平成24年10月19日(2012.10.19)

(51) Int.Cl.

G06F 9/50 (2006.01)

F 1

G06F 9/46 465Z

請求項の数 20 (全 16 頁)

(21) 出願番号 特願2008-83112 (P2008-83112)

(22) 出願日 平成20年3月27日 (2008.3.27)

(65) 公開番号 特開2009-237888 (P2009-237888A)

(43) 公開日 平成21年10月15日 (2009.10.15)

審査請求日 平成23年3月11日 (2011.3.11)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100089071

弁理士 玉村 静世

(72) 発明者 植田 浩司

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 岩田 肇一

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 望月 誠二

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】データ処理装置、画像符号化復号装置、データ処理システム及び画像処理装置

## (57) 【特許請求の範囲】

## 【請求項1】

初期設定情報に基づいて初期設定されたプログラムとデータに基づいたデータ処理を並列的に行なう複数のプロセッサユニットと、

前記複数のプロセッサユニットを初期設定するための初期設定情報及び前記初期設定情報の設定先である設定先情報が格納される外部記憶装置と、

前記外部記憶装置内の前記初期設定情報及び前記設定先情報の格納場所を含む制御情報が外部から設定される第1回路と、

前記第1回路に設定された前記制御情報を用いて前記初期設定情報と前記設定先情報を前記外部記憶装置から読み込み、読み込んだ前記設定先情報に従って前記複数のプロセッサユニットへ前記初期設定情報を転送する第2回路とを有する、データ処理装置。 10

## 【請求項2】

初期設定情報に基づいて初期設定された内容に従って画像データの符号化及び復号処理が可能にされる複数の画像処理モジュールと、

前記複数の画像処理モジュールを初期設定するための初期設定情報及び前記初期設定情報の設定先である設定先情報が格納される外部記憶装置と、

前記外部記憶装置内の前記初期設定情報及び前記設定先情報の格納場所を含む制御情報が外部から設定される第1回路と、

前記第1回路に設定された前記制御情報を用いて前記初期設定情報と前記設定先情報を前記外部記憶装置から読み込み、読み込んだ前記設定先情報に従って前記複数の画像処 20

理モジュールへ前記初期設定情報を転送する第2回路とを有する、データ処理装置。

**【請求項3】**

前記制御情報は前記初期設定情報及び前記設定先情報の格納場所の先頭を示すアドレス情報を有し、前記第2回路は前記先頭を示すアドレス情報を順次インクリメントして前記初期設定情報及び前記設定先情報の読み込み先を順次生成する、請求項2記載の画像符号化復号装置。

**【請求項4】**

前記設定先情報はどの画像処理モジュールであるかを示す情報、及び画像モジュール内の記憶領域のアドレスを示す情報である、請求項2記載の画像符号化復号装置。

**【請求項5】**

前記初期設定情報と前記設定先情報は設定先情報毎に固定長のパケットを構成し、それぞれのパケットはフラグを有し、前記フラグの第1状態は当該フラグに前記初期設定情報が後続することを意味し、前記フラグの第2状態は当該パケットが終端パケットであることを意味する、請求項3記載の画像符号化復号装置。

**【請求項6】**

前記第2の回路は前記終端パケットの前記フラグに応答して、前記初期設定情報と前記設定先情報との読み込みと読み込んだ情報に従った初期設定情報の転送処理を終了する、請求項5記載の画像符号化復号装置。

**【請求項7】**

前記第2の回路は前記終端パケットの前記フラグに後続するアドレス情報を従ってコード情報を第1の回路に転送し、第1の回路は転送された前記コードに応答して前記複数の画像処理モジュールに画像符号化及び復号処理の開始を指示する、請求項5記載の画像符号化復号装置。

**【請求項8】**

前記複数の画像処理モジュールとして、符号化処理のための複数の演算処理を並列に行なう複数のプロセッサユニットと、復号処理のための複数の演算処理を並列に行なう複数のプロセッサユニットとを有する、請求項2記載の画像符号化復号装置。

**【請求項9】**

前記複数のプロセッサユニットの動作プログラムとデータの格納に利用されるRAMが、前記複数のプロセッサユニット各々に設けられ、前記RAMに前記初期設定情報が初期設定される、請求項8記載の画像符号化復号装置。

**【請求項10】**

請求項7記載の画像符号化復号装置と、前記画像符号化復号装置の第1回路に前記制御情報を設定するCPUと、前記画像符号化復号装置の第2回路が読み込む前記初期設定情報と前記設定先情報とが格納される記憶装置とを有するデータ処理システム。

**【請求項11】**

前記CPUは複数の異なる符号化復号処理アルゴリズムのなかから一つを選択するため必要な制御情報を前記画像符号化復号装置の第1回路に設定する、請求項10記載のデータ処理システム。

**【請求項12】**

携帯電話器に搭載された請求項11記載のデータ処理システム。

**【請求項13】**

初期設定情報に基づいて初期設定された内容に従って画像データの符号化または復号処理が可能にされる複数の画像処理モジュールと、

前記複数の画像処理モジュールを初期設定するための初期設定情報及び前記初期設定情報の設定先である設定先情報が格納される外部記憶装置と、

前記外部記憶装置内の前記初期設定情報及び前記設定先情報の格納場所を含む制御情報が外部から設定される第1回路と、

前記第1回路に設定された前記制御情報を用いて前記初期設定情報と前記設定先情報とを前記外部記憶装置から読み込み、読み込んだ前記設定先情報に従って画像処理モジュー

10

20

30

40

50

ルへ初期設定情報を転送する第2回路とを有する、画像処理装置。

**【請求項14】**

前記制御情報は前記初期設定情報及び前記設定先情報の格納場所の先頭を示すアドレス情報を有し、前記第2回路は前記先頭を示すアドレス情報を順次インクリメントして前記初期設定情報及び前記設定先情報の読み込み先を順次生成する、請求項13記載の画像処理装置。

**【請求項15】**

前記設定先情報はどの画像処理モジュールであるかを示す情報、及び画像モジュール内の記憶領域のアドレスを示す情報である、請求項13記載の画像処理装置。

**【請求項16】**

前記初期設定情報と前記設定先情報は設定先情報毎に固定長のパケットを構成し、それぞれのパケットはフラグを有し、前記フラグの第1状態は当該フラグに前記初期設定情報が後続することを意味し、前記フラグの第2状態は当該パケットが終端パケットであることを意味する、請求項14記載の画像処理装置。

**【請求項17】**

前記第2の回路は前記終端パケットの前記フラグに応答して、前記初期設定情報と前記設定先情報との読み込みと読み込んだ情報に従った初期設定情報の転送処理を終了する、請求項16記載の画像処理装置。

**【請求項18】**

前記第2の回路は前記終端パケットの前記フラグに後続するアドレス情報を従ってコード情報を第1の回路に転送し、第1の回路は転送された前記コードに応答して前記複数の画像処理モジュールに画像符号化または復号処理の開始を指示する、請求項16記載の画像処理装置。

**【請求項19】**

前記複数の画像処理モジュールとして、符号化処理のための複数の演算処理を並列に行なう複数のプロセッサユニットと、復号処理のための複数の演算処理を並列に行なう複数のプロセッサユニットの両方、あるいはそのいずれかを有する、請求項13記載の画像処理装置。

**【請求項20】**

前記複数のプロセッサユニットの動作プログラムとデータの格納に利用されるRAMが前記複数のプロセッサユニット各自に設けられ、前記RAMに前記初期設定情報が初期設定される、請求項19記載の画像処理装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、データ処理装置、画像符号化復号装置及びそれを適用したデータ処理システムに關し、例えば画像圧縮伸張ハードウェアであるDVD/HDDレコーダ、デジタルビデオカメラ、デジタルカメラ、携帯電話、ナビゲーションシステム、デジタルテレビほか動画像再生並びに記録装置全般に適用して有効な技術に関する。

**【背景技術】**

**【0002】**

近年、画像符号化復号装置はMPEG2とMPEG4のように複数種類の画像符号化復号アルゴリズムに対応可能なマルチコーデック処理に対応するなど、機能が複雑化し、初期設定を行うレジスタ数やプログラムファイルの容量等が増加している。従来技術では、CPUからバスのスレーブアクセスを利用して画像符号化復号装置内の大量のレジスタを一つずつ設定していたため、初期設定動作に時間がかかる。また、レジスタ等の増加に伴い設定するデータ量が大量になり、CPUの負荷が増大するといった問題もある。

**【0003】**

特許文献1には、レジスタを2面設け、1面を現在の動作に使用して、もう1面を次の動作設定や、レジスタの初期値保持に使用することで、設定時間を隠蔽する技術が記載さ

10

20

30

40

50

れる。特許文献 2 には、圧縮したデータを転送し、回路内部で解凍してレジスタに設定することで設定量と時間の短縮を図る技術が記載される。

【0004】

【特許文献 1】特開 2005 - 56033 号公報

【特許文献 2】特開 2006 - 178689 号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、画像符号化又は復号を行う際には、フレーム毎に符号化と復号処理を切り替えて使用する場合や、フレーム毎にコーデックの種類（アルゴリズムの種類）を切り替えて使用する場合などもあり、そのような場合にはフレーム単位でレジスタ設定やプログラムファイルの入れ替えを行わなければならないという特有の事情がある。これを考慮すると、上記特許文献 1 及び 2 に記載の技術では充分に対応できない。また、DMA 転送を採用すれば確かに CPU の負荷を軽減することはできるが、頻繁に且つ大量のデータを初期設定する場合には、単なる DMA 転送では CPU の負荷軽減にも限界のあることが本発明者によって見出された。上記事情は、初期設定されたプログラムとデータに基づいたデータ処理を並列的に行なう複数のプロセッサユニットを有するデータ処理装置についても同じである。

【0006】

本発明の目的は、画像符号化復号装置に代表されるデータ処理装置に頻繁に且つ大量のデータを初期設定する場合に外部の CPU の処理負担を軽減することにある。

【0007】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0008】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0009】

すなわち、画像符号化復号装置（データ処理装置）は複数の画像処理モジュール（プロセッサユニット）を初期設定するために第 1 回路と第 2 回路を有し、複数の画像処理モジュールに初期設定される情報を直接外部の CPU から受けず、第 1 回路に CPU から初期設定のための制御情報が設定され、第 2 回路が第 1 回路に設定された制御情報を用いて初期設定情報と当該初期設定情報の設定先情報を外部から読み込み、読み込んだ設定先情報を従って画像処理モジュールへ初期設定情報を転送する。

【0010】

これにより、CPU は複数の画像処理モジュールに初期設定される全ての情報を直接画像符号化復号装置にセットすることを要せず、しかも、DMA 転送を利用する場合のように転送元アドレスと転送先アドレスの双方を CPU が設定することも必要ない。また、CPU や DMA 転送を用いる場合には初期設定される記憶回路は CPU のアドレス空間にマッピングされることが必要になり、CPU のアドレス空間の多くを占有することになるが、上記手段ではそれを要さず、個々の画像処理モジュールで初期設定される記憶回路はオーバルなアドレスにマッピングされていればよい。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0012】

すなわち、画像符号化復号装置に頻繁に且つ大量のデータを初期設定する場合にも外部の CPU の処理負担を軽減することができる。

10

20

30

40

50

**【発明を実施するための最良の形態】****【0013】****1. 実施の形態の概要**

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものと例示するに過ぎない。

**【0014】**

[1] 本発明に係るデータ処理装置は、初期設定されたプログラムとデータに基づいたデータ処理を並列的に行なう複数のプロセッサユニットと、外部から初期設定のための制御情報が設定される第1回路と、第1回路に設定された制御情報を用いて初期設定情報と当該初期設定情報の設定先情報を外部から読み込み、読み込んだ設定先情報を従って前記プロセッサユニットへ初期設定情報を転送する第2回路とを有する。10

**【0015】**

[2] 本発明に係る画像符号化復号装置は、初期設定された内容に従って画像データの符号化及び復号処理が可能にされる複数の画像処理モジュールと、外部から初期設定のための制御情報が設定される第1回路と、第1回路に設定された制御情報を用いて初期設定情報と当該初期設定情報の設定先情報を外部から読み込み、読み込んだ設定先情報を従って画像処理モジュールへ初期設定情報を転送する第2回路とを有する。

**【0016】**

[3] 項2の画像符号化復号装置において、前記制御情報は例えば初期設定情報及び設定先情報の格納場所を示すアドレス情報を有する。20

**【0017】**

[4] 項3の画像符号化復号装置において、前記制御情報は例えば初期設定情報及び設定先情報の格納場所の先頭を示すアドレス情報を有し、前記第2回路は前記先頭を示すアドレス情報を順次インクリメントして初期設定情報及び設定先情報の読み込み先を順次生成する。

**【0018】**

[5] 項2の画像符号化復号装置において、前記設定先情報は例えば、どの画像処理モジュールであるかを示す情報、及び画像モジュール内の記憶領域のアドレスを示す情報である。30

**【0019】**

[6] 項4の画像符号化復号装置において、前記初期設定情報と設定先情報は例えば設定先情報毎に固定長のパケットを構成し、それぞれのパケットはフラグ(E)を有し、前記フラグの第1状態は当該フラグに初期設定情報が後続することを意味し、前記フラグの第2状態は当該パケットが終端パケットであることを意味する。

**【0020】**

[7] 項6の画像符号化復号装置において、例えば、前記第2の回路は前記終端パケットの前記フラグに応答して、前記初期設定情報と設定先情報との読み込みと読み込んだ情報に従った初期設定情報の転送処理を終了する。

**【0021】**

[8] 項6の画像符号化復号装置において、例えば前記第2の回路は前記終端パケットの前記フラグに後続するアドレス情報を従ってコード情報を第1の回路に転送し、第1の回路は転送された前記コードに応答して前記複数の画像処理モジュールに画像符号化及び復号処理の開始を指示する。40

**【0022】**

[9] 項2の画像符号化復号装置において、前記複数の画像処理モジュールとして、符号化処理のための複数の演算処理を並列に行なう複数のプロセッサユニットと、復号処理のための複数の演算処理を並列に行なう複数のプロセッサユニットとを有する。

**【0023】**

[10] 項9の画像符号化復号装置において、前記プロセッサユニットの動作プログラ50

ムとデータの格納に利用されるRAMがそれぞれのデータプロセッサ毎に設けられ、前記RAMに前記初期設定情報が初期設定される。

**【0024】**

[11] 本発明に係るデータ処理システムは、項7の画像符号化復号装置と、前記画像符号化復号装置の第1回路に制御情報を設定するCPUと、前記画像符号化復号装置の第2回路が読み込む前記初期設定情報と設定先情報とが格納される記憶装置とを有する。

**【0025】**

[12] 項11のデータ処理システムにおいて、前記CPUは複数の異なる符号化復号処理アルゴリズムのなかから一つを選択するために必要な制御情報を前記画像符号化復号装置の第1回路に設定する。 10

**【0026】**

[13] 項11のデータ処理システムは例えば携帯電話器に搭載される。

**【0027】**

2. 実施の形態の詳細

実施の形態について更に詳述する。以下、本発明を実施するための形態を図面に基づいて詳細に説明する。なお、発明を実施するための形態を説明するための全図において、同一の機能を有する要素には同一の符号を付して、その繰り返しの説明を省略する。

**【0028】**

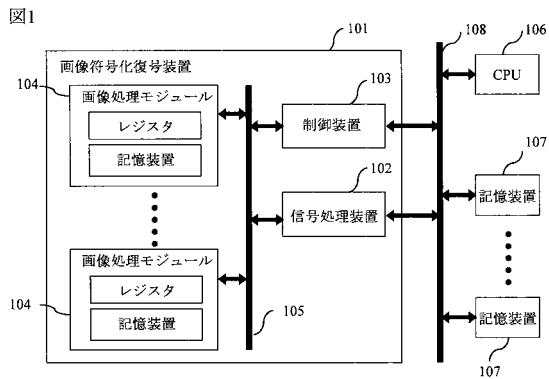

図1には本発明に係る画像符号化復号装置の一例が示される。画像符号化復号装置101はバス108に共通接続されたCPU(中央処理装置)106及び記憶装置107を備えたデータ処理システムに設けられたアクセラレータ若しくは周辺回路モジュールとして位置付けられる。前記バス108は、特に制限されないが、スプリットトランザクションバスとルータにより構成され、イニシエータからのリクエストパケットがターゲットに転送され、ターゲットは必要に応じてレスポンスパケットを転送元のイニシエータに返すという、データ転送プロトコルによるバス制御を行う。ここではCPU106と制御装置103がイニシエータ、即ちバスマスターとなり得る。 20

**【0029】**

画像符号化複合装置101は複数の画像処理モジュール104、制御装置103および信号処理装置102を備え、それらは内部バス105に共通接続される。信号処理装置102は画像処理モジュール104のレジスタや記憶装置にデータやプログラムの初期設定を行う。制御装置103はCPU106からの指示に従って画像符号化復号装置を全体的に制御し、例えば、信号処理装置102による前記初期設定に必要な情報をCPU106から受取って前記初期設定動作を信号処理装置102にさせ、また、初期設定が終った画像処理モジュール104に対する起動制御等を行う。 30

**【0030】**

記憶装置107は初期設定データ、画像データ及び符号化データ等の格納に利用される。複数の画像処理モジュール104は、例えば画像データを符号化するための直交変換処理(DCT)、量子化および可変長符号化等の処理をそれぞれ担う複数の回路モジュールと、符号化データを復号するための可変長復号、逆量子化、及び逆DCT等の処理をそれぞれ担う複数の回路モジュールとされる。また、それら画像処理モジュールは初期設定されるプログラムや制御データに応じて、MPEG2、MPEG4.H.264等の規格に準拠した処理が選択可能にされる。したがって、デジタルスチルカメラ用処理、ビデオカメラ用処理、及びテレビ電話用画像処理のそれぞれに選択的に対応するという、例えば携帯電話器用途等を想定する場合には、複数の画像処理モジュール104に対する比較的設定データ量の多い初期設定を頻繁に行なうことが予想される。画像符号化復号装置101においては画像処理モジュール104に対する初期設定の効率化について考慮されている。以下、その点について詳述する。 40

**【0031】**

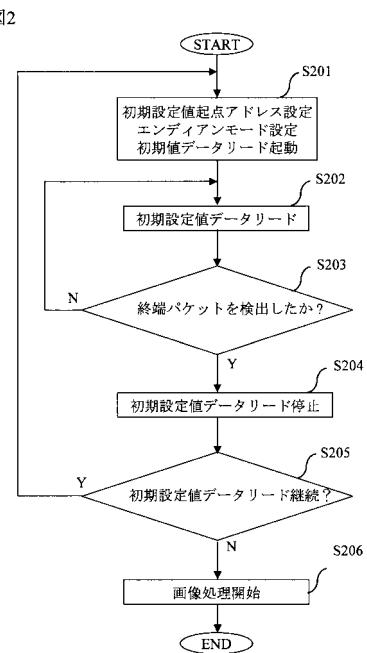

図2は画像符号化復号装置101を使用して画像符号化、もしくは復号処理を行う際の起動処理(初期設定と初期設定後の画像処理モジュールの起動)のフローチャートである 50

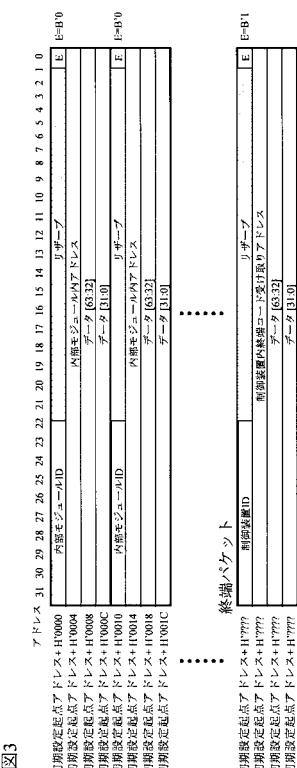

。まずステップ S 201において初期設定に必要なデータやプログラム等の所在を特定するための初期設定値起點アドレス、及びエンディアンモードの初期設定値等の初期設定値リードに必要な初期値データが C P U 1 0 6 によって制御装置 1 0 3 にセットされ、セット後に、信号処理装置 1 0 2 に、セットされた初期値データに従った画像処理モジュール 1 0 4 への初期設定データのリード動作が起動される。これによって、ステップ S 202 では、信号処理装置 1 0 2 による記憶装置 1 0 7 からの初期値データのリード動作が行われる。例えば初期値データは、図 3 に例示されるように、内部モジュール I D ( 画像処理モジュールに I D ) 、フラグ E 、内部モジュール内アドレス及びデータを有するパケットとして構成される。フラグ E が “ 0 ” であればデータは初期設定データで在って、後続のパケットがすることを意味する。フラグ E が “ 1 ” であれば其れが終端パケットであることを意味し、そのデータ部には制御装置内の終端コード受取りアドレス等が格納されている。ステップ S 202 のリード動作は終端パケット ( E = 1 ) が検出されるまで繰り返し行われ、終端パケットを検出するとステップ S 204 で初期設定値データのリード動作が停止される。リードされた初期設定値データは信号処理装置 1 0 2 の制御により、パケットの内部モジュール I D とモジュール内アドレスで示される画像処理モジュール 1 0 4 のレジスタ及び記憶装置に内部転送されて初期設定される。ステップ S 205 では更に別の格納アドレスから初期設定値データのリードを行う必要があるかを制御装置 1 0 3 が判定し、継続する場合には制御装置 1 0 3 は信号処理装置 1 0 2 にステップ S 201 からステップ S 205 までの処理を繰り返えさせる。すべての初期設定値データのリードが完了した後、ステップ S 206 で制御装置 1 0 3 により画像処理モジュール 1 0 4 に対する画像処理の開始が指示される。尚、エンディアンモードとはバス 1 0 8 における転送形態がビッグエンディアンであるのかリトルエンディアンであるかを示す。

10

20

#### 【 0 0 3 2 】

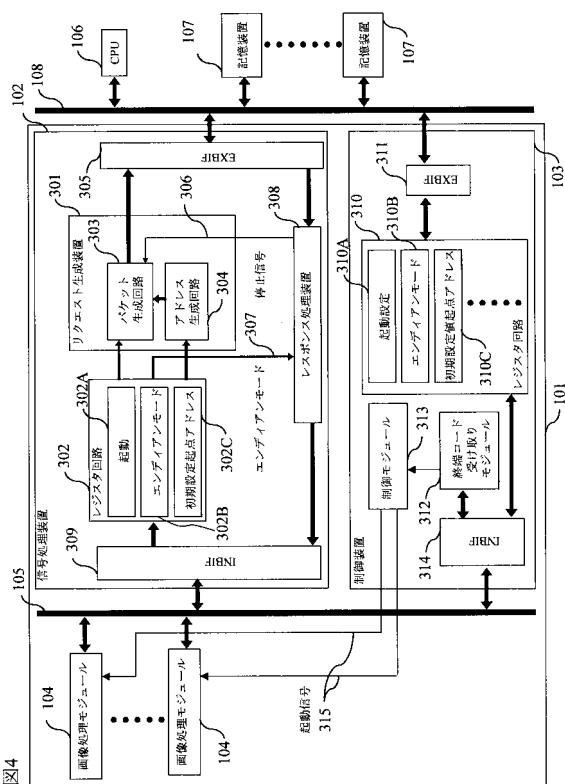

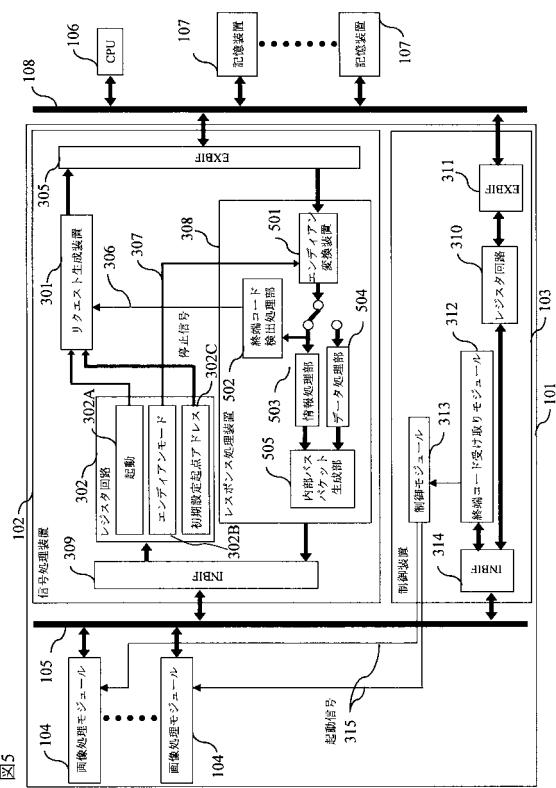

図 4 および図 5 には信号処理装置 1 0 2 と制御装置 1 0 3 の具体例が示され、特に図 4 には制御装置 1 0 3 の詳細が示され、図 5 には信号処理装置 1 0 2 の詳細が示される。

#### 【 0 0 3 3 】

図 4 において制御装置 1 0 3 はレジスタ回路 3 1 0 、外部バスインターフェース ( E X B I F ) 3 1 1 、終端コード受取りモジュール 3 1 2 、制御モジュール 3 1 3 、及び内部バスインターフェース ( I N B I F ) 3 1 4 を有する。レジスタ回路 3 1 0 は、起動設定、エンディアンモード、複数の初期設定値基点アドレスの各レジスタ 3 1 0 A , 3 1 0 B , 3 1 0 C ... を有する。

30

#### 【 0 0 3 4 】

図 4 において信号処理装置 1 0 2 はリクエスト生成装置 3 0 1 、レジスタ回路 3 0 2 、レスポンス処理装置 3 0 8 、外部バスインターフェース ( E X B I F ) 3 0 5 、及び内部バスインターフェース ( I N B I F ) 3 0 9 を備える。レジスタ回路 3 0 2 は、起動、エンディアンモード、初期設定値基点アドレスの各レジスタ 3 0 2 A , 3 0 2 B , 3 0 2 C を有する。リクエスト生成装置 3 0 1 はアドレス生成回路 3 0 4 とパケット生成回路 3 0 3 を有する。

#### 【 0 0 3 5 】

図 4 を参照しながら、初期設定値データのリード機能について説明する。初期設定値リードを行う信号処理装置 1 0 2 は制御装置 1 0 3 によりその動作が起動される。初期設定値リードを行う場合、まず C P U 1 0 6 から外部バス 1 0 8 、外部バスインターフェース 3 1 1 を経由して制御装置 1 0 3 内のレジスタ回路 3 1 0 にデータ設定が行われる。C P U 1 0 6 がレジスタ回路 3 1 0 に設定するデータは、初期設定値データが格納されている記憶装置 1 0 7 上の初期設定値起點アドレス、外部バス 1 0 8 のエンディアンモード、および起動設定である。起動設定は、初期設定値起點アドレス及びエンディアンモード等の設定が完了した後に設定される。この起動設定により制御装置 1 0 3 に初期設定値リード動作が起動される。初期設定値リード動作の完了後に、制御モジュール 3 1 3 が画像処理モジュール 1 0 4 を続けて起動する。または初期設定値リードが既に終了している状態で画像処理モジュール 1 0 4 のみを起動するというような、起動単位を選択して起動すること

40

50

も可能とされる。

**【0036】**

起動設定により初期設定値リード動作の起動が指示されると、制御装置103は内部バス105を経由して初期設定値データリードの動作を行なう信号処理装置102内のレジスタ回路302に設定データを転送する。転送される設定データはCPU106によりレジスタ回路310にセットされたエンディアンモードと一つの初期設定値基点アドレスを含む。信号処理装置102内のレジスタ回路302に初期設定値起点アドレス、エンディアンモードなどの初期設定値リードに必要なレジスタデータが転送された後に、制御装置103が起動レジスタにイネーブルデータをセットすることにより信号処理装置102による初期設定値リード動作が起動される。10 初期設定値リード動作の起動が指示されると、リクエスト生成装置301は初期設定値起点アドレスをレジスタから読み出し、アドレス生成回路304でその初期設定値起点アドレスに対応する外部バス108上のアドレス計算を行う。パケット生成回路303はバスコマンドを生成する。アドレス生成回路304で生成されたアドレスと、パケット生成回路303で生成したバスコマンドなどは外部バスインターフェース回路305で外部バスプロトコルに変換されて外部バス108へ出力される。このバスコマンドに従って記憶装置107から初期設定値データが読み出され、読み出された初期設定値データがレスポンスとして外部バスインターフェース回路305からレスポンス処理装置308に供給される。20 リクエスト生成回路301はレスポンス処理装置308から停止信号306が入力されるまでリクエストパケットを生成し続け、停止信号306が入力されるとリクエストの生成を停止して次の起動を待つ。リクエストの生成停止は図2のステップS204に相当する。リクエストの生成停止は図3の前記E=1によって示される終端コードによって検出される。

**【0037】**

ここで図3に基づいて外部の記憶装置107に格納される初期設定データの例を更に詳述する。外部の記憶装置107に格納される初期設定データは、扱うデータ量やデータの種類、内部モジュール数（内部モジュールのIDのビット数）や内部モジュールのアドレスのビット数などにより、1パケットを何ビットで構成するかは自由に選択可能である。30 ここでは、128ビットのデータを1パケットとして扱う場合について説明を行う。最初の32ビットは内部モジュール（画像処理モジュール104）のIDと終端パケットを示すビットEを格納する。次の32ビットは内部モジュール内のアドレスを格納するビット列として使用される。次の64ビットには内部モジュールへ転送するデータを格納するビット列として使用される。この128ビットを1パケットとして扱う。終端パケットについては、終端パケットを示すビットEはイネーブルにされ（E=1）、内部モジュールIDは制御装置103のID、内部モジュール内アドレスは制御装置103内の終端コードを受け取る専用のアドレス（終端コード受け付けモジュール312の内部）を格納する。初期設定データの最初のパケットから終端パケットまでのデータは、初期設定起点アドレスから連続した領域に格納される。

**【0038】**

次に、図5を参照しながらレスポンス処理装置による初期設定値データの内部転送機能について説明する。リクエスト生成装置301から外部バス108に対して出力されたリクエストに対するレスポンスは外部バスインターフェース305を経由してレスポンス処理装置308に入力される。40 レスポンス処理装置308では、入力されたレスポンスに対し、まずエンディアン変換装置501で、レジスタ302Bに設定されたエンディアンモードによりエンディアン変換を行う。次にレスポンスデータが情報部分（図3の設定データ例の場合は内部モジュールID、終端パケットを示すビットE、内部モジュール内アドレス部分）であるか、データ部分（図3の設定データ例の場合はデータ部分）であるかを判定し、情報部分である場合は情報処理部503へ、データ部分である場合はデータ処理部504へデータを送る。情報処理部503では内部モジュールID及び内部モジュール内アドレスを解析し、内部バス105のアドレス信号やモジュールID信号等を生成し、各信号を内部バスパケット生成部505に送る。データ処理部504では内部バスのデータ50

信号を生成し、内部バスパケット生成部 505 に送る。また、終端コード検出処理部 502 では、情報部分データの終端パケットコード E を監視し、終端コード ( E = 1 ) を検出した場合にはリクエスト生成装置 301 ヘリクエスト停止信号 306 を出力し、リクエストの生成を停止させる。内部バスパケット生成部 505 では、情報処理部 503 及びデータ処理部 504 から入力された信号から内部バスパケットを生成し、内部バスインターフェース 309 を経由して内部バス 105 へパケットを送出する。画像処理モジュール 104 は、自分宛のパケットを受け取ると、内部モジュール内アドレスに従って初期設定データを内部のレジスタや記憶装置に格納する。終端パケットは制御装置 103 の終端コード受け取りモジュール 312 宛に転送される。終端コード受け取りモジュール 312 は内部バスインターフェース 314 を経由して終端パケットを受け取ると、一連のパケット転送で初期設定値が所要の画像処理モジュール 104 に設定されたと判断する。終端コード受け取りモジュール 312 は、終端パケットを受け取ると、画像処理モジュール 104 へ起動信号 315 を送信し、画像処理を開始させる。図 2 のステップ S205 に例示されるように、初期設定値データリードを継続する必要がある場合には、全ての初期設定値データリードを完了してから画像処理を起動する。初期設定値データリードを継続する必要があるか否かは、CPU106 によってレジスタ 310C に設定された全ての初期設定値基点アドレスに基づく初期設定動作を完了したか否かによって判別することができる。例えば CPU106 によるレジスタ 310C の書き込み個数と、制御装置 103 によるレジスタ 310C の読み出す個数とが一致するか否かによって判定すればよい。

## 【0039】

10

制御装置の初期設定データリード起動のレジスタ 310A と画像処理起動のレジスタ ( 終端コード受け付けモジュール 312 内 ) とを分けることにより、初期設定データリードの開始と画像処理の開始を別々に起動することも可能である。また、初期設定起点アドレスを更新し、再度初期データリードを起動することにより、初期設定データを外部記憶装置の複数箇所に配置することも可能である。

## 【0040】

20

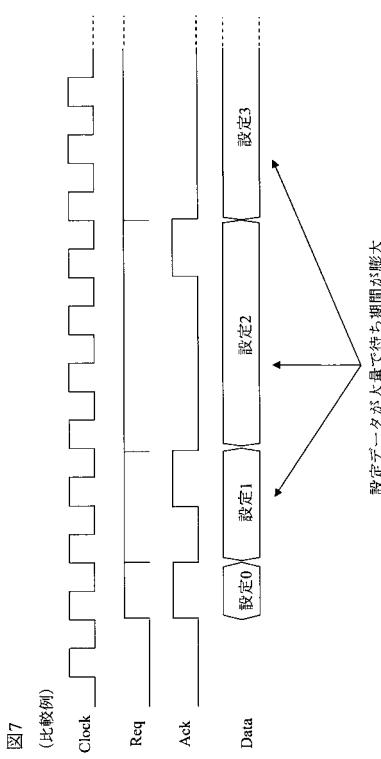

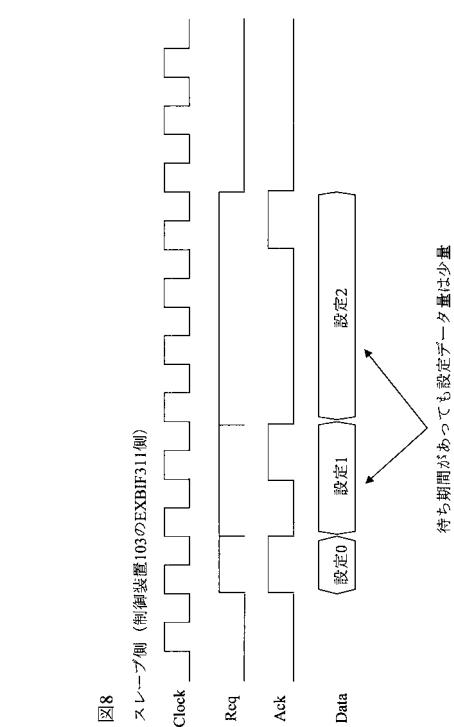

以上説明した信号処理装置 102 と制御装置 103 によれば、CPU106 からは制御装置 103 へ初期設定起点アドレス、エンディアンモード等の最低限の設定だけを行うことによって、その設定に基づいて信号処理装置 102 が自動的に初期設定値データを外部の記憶装置 107 から読み出して、内部の画像処理モジュール 104 にデータやプログラム等の初期設定を行って、画像処理を開始することができる。これにより、CPU が全ての初期設定値データをセットして初期設定を行う場合に比べて大量のレジスタ設定を行う必要がない。このため、CPU 負荷を大幅に削減することができる。例えば CPU が全てのレジスタ設定を直接行う場合には図 7 のように、設定される側の状態やバスの状態に応じて CPU はバスアクセスのリクエストに対してアクノリッジが返されるまで待たなければならず (Ack のローレベル期間) 、設定データが大量の場合には、CPU の動作時間だけでなく待ち時間も長くなり、CPU の負荷が大幅に増大する。これに対して本実施の形態のように CPU106 による設定がレジスタ回路 310A だけで良い場合には、図 8 に例示されるようにアクノリッジが返されるまでの待ち時間 (Ack のローレベル期間) は発生するが、設定データ量が格段に少ないから、図 7 の場合に比べて CPU106 の負荷は大幅に軽減される。

30

## 【0041】

40

初期設定データのみの起動も可能であるため、バスの負荷が軽い期間に初期設定データを転送しておくこともできるため、バス負荷を低減することができる。

## 【0042】

50

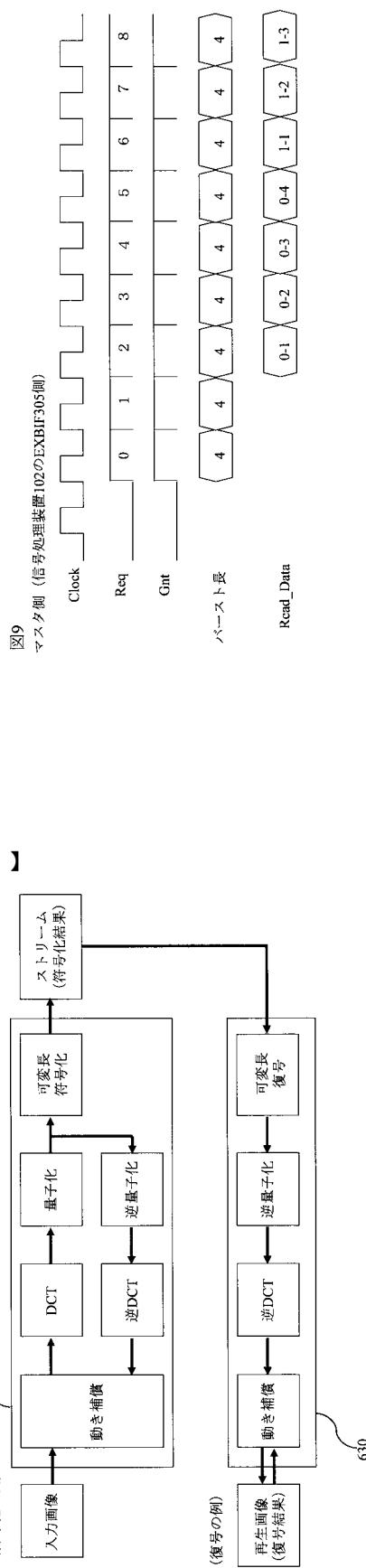

また、制御装置 103 の外部バスインターフェース回路 311 側はスレーブポートであるが、信号処理装置 102 の外部バスインターフェース 305 側はマスターポートとして機能される。従って、このマスターportを使用して初期設定を行うため、外部バスの仕様によつては、スレーブポートからレジスタ設定する場合よりも高速化を図ることができる。例えば図 9 に例示されるように、バースト転送等を利用して連続的にデータを読み込むことも

可能である。

**【0043】**

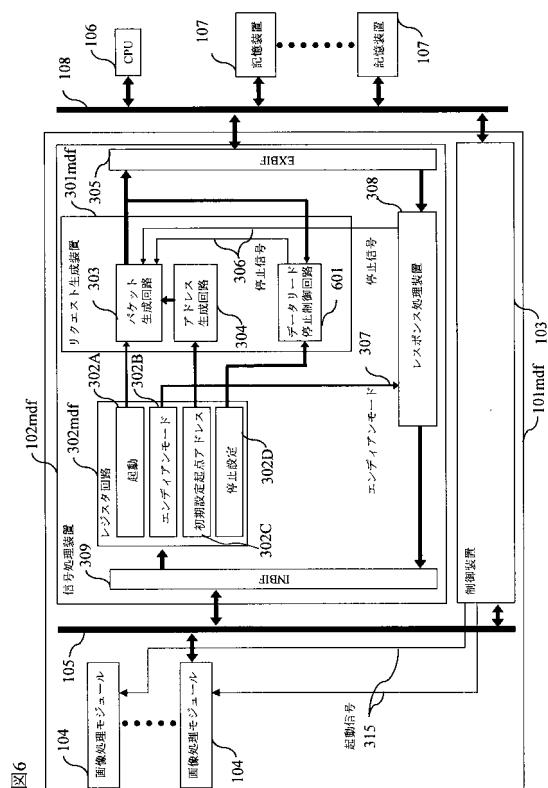

図6には本発明に係る別の画像符号化復号装置101m d fが例示される。図4,5の画像符号化復号装置101とは、信号処理装置102m d fにおけるデータリードの停止制御形態が相違される。例えば、信号処理装置102m d fは終端コードを検出せず、リクエスト生成装置301m d fにデータリード停止制御回路601が設けられ、レジスタ回路302m d fには停止設定のレジスタ302Dが追加される。停止設定レジスタ302DはCPU106からの指示値が制御装置103によってセットされる。停止設定レジスタ302Dには、例えばリクエスト発行回数、リードデータ量、外部記憶装置のリード終了アドレスなどリクエスト発行を停止するための条件が設定される。リクエスト生成装置301m d fはレジスタ302Dから停止設定を受け取り、停止する条件に達したらパケット生成回路303へリクエスト発行の停止を指示する。

10

**【0044】**

図4,5の画像符号化復号装置101では外部バス108からのレスポンスを確認し、終端パケットである場合にリクエスト停止処理を行う。このため、終端パケットを読み出すまでに既に発行されたリクエストは無駄読みとなる。図6の例では予め停止条件が設定されるので、無駄読みを無くすことができる。

**【0045】**

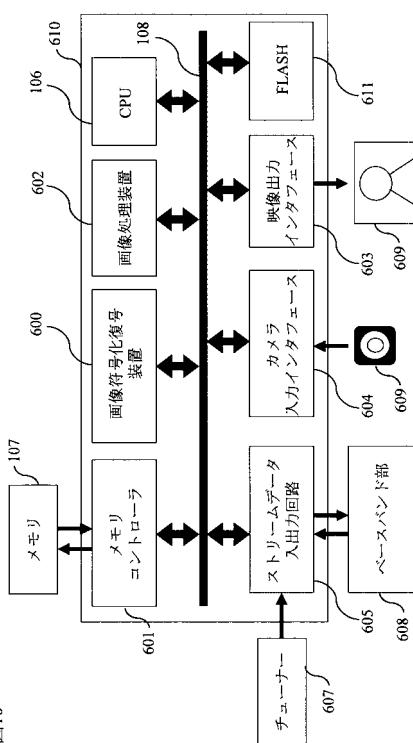

図10には画像符号化復号装置を携帯電話システムに適用した例が示される。ベースバンド部608には図示を省略するアナログフロントエンドを介して高周波部が接続され、携帯電話の送受信が可能にされる。610はアプリケーションプロセッサである。アプリケーションプロセッサ610は、本発明に係る画像符号化復号装置600、書換え可能な不揮発性メモリとしてのフラッシュメモリ(FLASH)611、CPU106、メモリコントローラ601、画像処理装置602、映像出力インターフェース603、カメラ入力インターフェース604、及びストリームデータ入出力回路605を備え、それらはバス108に共通接続される。ストリームデータ入出力回路605にはベースバンド部608とチューナ607が接続され、携帯電話ネットワークからダウンロードしたストリームデータやチューナ607で受信したストリームデータを入力可能にされる。画像符号化復号装置600は図4,5又は図6で説明した回路構成を備える。フラッシュメモリ611は、特に制限されないが、CPU106の動作プログラムと共に画像符号化復号装置600の画像処理モジュール104に初期設定されるプログラムやデータが初期的に格納されている。それら初期設定用のプログラムやデータはアプリケーションプロセッサ610のパワーオンリセット処理でメモリ107の所定の領域に転送され、あるいは適宜ネットワークを介してダウンロードされてメモリ107の所定の領域に格納される。そのようにしてメモリ107に予め格納される初期設定用のプログラムおよびデータは例えばMPRG2、MPEG4、又はH.264の符号化復号処理アルゴリズムを実現するものである。CPU106は、動作プログラムに従って、MPRG2、MPEG4、又はH.264の符号化復号処理アルゴリズムのなかから一つを選択するために必要な制御情報(初期設定値基点アドレス、エンディアンモード)を前記画像符号化復号装置のレジスタ回路310に設定する。これによって画像符号化復号装置101はMPRG2、MPEG4、又はH.264に準拠した符号化復号処理を選択的に実行することができる。

20

30

40

**【0046】**

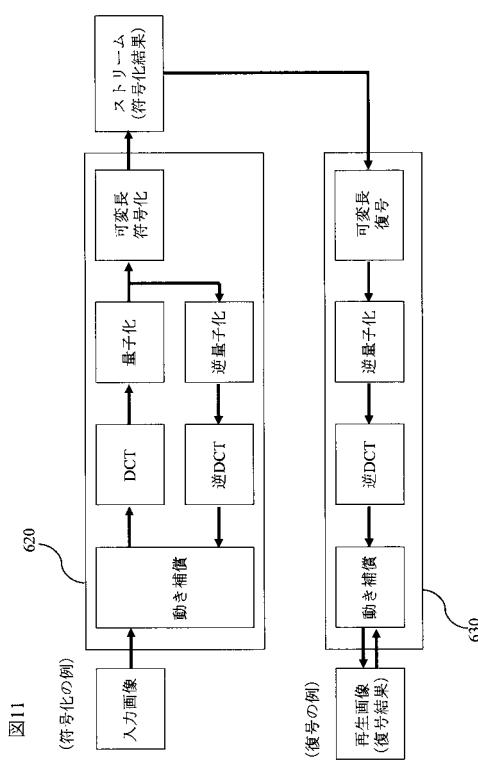

図11には画像符号化復号装置600における動画像に対する符号化工エレメント620と復号エレメント630の基本的な機能ブロックダイヤグラムが例示される。符号化工エレメント620は、入力画像に対して、動き補償、DCT、量子化、可変長符号化、逆量子化、逆DCTの各機能を備える。復号エレメント630は符号化データに対する可変長復号、逆量子化、逆DCT、及び動き補償の各機能を備える。前記符号化工エレメント620及び復号エレメント630は複数の画像処理モジュール104によって実現される。

**【0047】**

図12には図11の符号化工エレメント620と復号エレメント630の機能をパイプラ

50

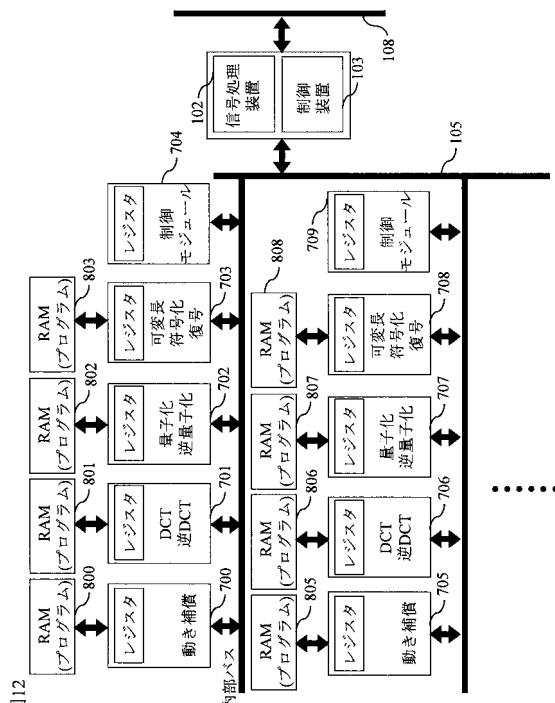

インで処理する場合に好適な画像処理モジュールの例が示される。図12ではマルチプロセッサシステムが採用され、複数のプロセッサユニット700～709が設けられ、プロセッサユニット700～703にはRAM800～803が接続され、プロセッサユニット705～708にはRAM805～808が接続される。プロセッサユニット700は動き補償、プロセッサユニット701はDCT及び逆DCT、プロセッサユニット702は量子化及び逆量子化、プロセッサユニット703は可変長符号化及び復号に割当てられ、プロセッサユニット704はプロセッサユニット700～703の制御機能を執する。RAM800～803にはそれぞれ対応するプロセッサユニットの機能を実現するためのプログラムやデータの保持に利用される。もう一組のプロセッサユニット705～709及びRAM805～808についても同様である。

10

#### 【0048】

図12の画像処理モジュール構成においては複数のプロセッサユニット700～703、705～708で並列処理が行なわれるから、その並列処理数分だけプロセッサユニットのレジスタに対する初期設定やRAMに対するプログラムやデータの初期設定量が増加する。したがって、並列数の多い符号化復号処理を行なう画像処理モジュールが採用される場合に図4、5や図6の構成を採用すれば、CPUの負担軽減、初期設定動作の高速化という効果が更に顕在化される。

#### 【0049】

以上説明した画像符号化復号装置によれば、CPU106が制御装置103に設定値や設定先の場所を示す情報を格納した外部の記憶装置107の先頭格納アドレス情報を設定し起動をかけると、信号処理装置102が自動的に設定されたアドレス位置から設定値と設定先の場所を示す情報を読み出し、設定先の場所を示す情報に従って複数の画像処理モジュール104に対する初期設定が行われる。すなわち、CPU106が外部の記憶装置107に初期設定データを格納し、格納場所の先頭位置のアドレス情報を制御装置103に設定し起動すると、信号処理装置102が初期設定データを自動的に読み出して画像処理モジュール104に対する初期設定が行なわれる。

20

#### 【0050】

記憶装置107が保持する初期設定用情報の中に画像処理モジュールを特定する情報を埋め込むことにより、CPU106は画像処理モジュールのアドレスを制御装置103にセットすることを要しない。

30

#### 【0051】

初期設定データの終端を示すデータパケットを初期設定データの最後に配置することにより、自動的に信号処理装置による外部の記憶装置107に対するリードリクエストの発行を停止させることができる。信号処理装置にその停止条件を設定する場合には、外部記憶装置から読み出されたレスポンスデータのパケットフラグ(E)を解析することなく前記リードリクエストの停止を制御することができる。

#### 【0052】

信号処理装置102は1コマンドで複数のデータをリードするバーストアクセス等によって連続アクセスが可能であるから、従来の初期設定などを行っていたスレーブアクセスと比較して、高速に処理を行うことが可能である。

40

#### 【0053】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。本発明は画像符号化復号装置だけでなく並列動作される複数のプロセッサユニットを有するデータ処理装置にも広く適用することができる。画像処理モジュールに代えてプロセッサユニットが初期設定の対象にされる。

#### 【図面の簡単な説明】

#### 【0054】

【図1】図1は本発明に係る画像符号化復号装置の一例を示すブロックダイヤグラムである。

50

【図2】図2は画像符号化復号装置を使用して画像符号化、もしくは復号処理を行う際の起動処理を示すフローチャートである。

【図3】図3は初期設定に用いられ初期値データのパケット構成を例示するデータフォーマット図である。

【図4】図4は制御装置の詳細と共に信号処理装置の具体例を示すブロックダイヤグラムである。

【図5】図5は信号処理装置の詳細と共に制御装置の具体例を示すブロックダイヤグラムである。

【図6】図6は本発明に係る別の画像符号化復号装置を例示するブロックダイヤグラムである。

【図7】図7はCPUが全てのレジスタ設定を直接行う場合のデータ転送動作を比較例として示すタイミングチャートである。

【図8】図8はCPUが制御装置のスレーブポートを介して内部レジスタを設定する動作を図7との比較用に示したタイミングチャートである。

【図9】図9は信号処理装置のマスターportを使用して初期設定値データをリードする動作を例示するタイミングチャートである。

【図10】図10は画像符号化復号装置を携帯電話システムに適用した例を示すブロックダイヤグラムである。

【図11】図11は画像符号化復号装置における動画像に対する符号化工エレメントと復号エレメントの基本的な機能ブロックダイヤグラムである。

【図12】図12は図11の符号化工エレメントと復号エレメントの機能をパイプラインで処理する場合に好適な複数の画像処理モジュールのブロックダイヤグラムである。

#### 【符号の説明】

##### 【0055】

101 画像符号化復号装置

108 バス

106 CPU(中央処理装置)

107 記憶装置

104 画像処理モジュール

103 制御装置

102 信号処理装置

310 レジスタ回路

311 外部バスインターフェース(EXBIF)

312 終端コード受取りモジュール

313 制御モジュール

314 内部バスインターフェース(INBIF)

301 リクエスト生成装置

302 レジスタ回路

308 レスポンス処理装置

305 外部バスインターフェース(EXBIF)

309 内部バスインターフェース(INBIF)

101 m d f 画像符号化復号装置

102 m f d 信号処理装置

301 m f d リクエスト生成装置

302 m d f レジスタ回路

600 画像符号化復号装置

620 符号化工エレメント

630 復号エレメント

700 ~ 709 プロセッサユニット

10

20

30

40

【図1】

【 四 2 】

【 四 3 】

【 义 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【 図 1 2 】

---

フロントページの続き

審査官 鈴木 修治

(56)参考文献 特開2005-122759(JP,A)

特開2008-048130(JP,A)

特開平11-252549(JP,A)

特開平09-128323(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 50

H 04 N 7 / 26