(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5498304号

(P5498304)

(45) 発行日 平成26年5月21日(2014.5.21)

(24) 登録日 平成26年3月14日(2014.3.14)

(51) Int.Cl.

H04N 5/3745 (2011.01)

F 1

H04N 5/335 745

請求項の数 9 (全 16 頁)

(21) 出願番号 特願2010-171177 (P2010-171177)

(22) 出願日 平成22年7月29日 (2010.7.29)

(65) 公開番号 特開2011-166733 (P2011-166733A)

(43) 公開日 平成23年8月25日 (2011.8.25)

審査請求日 平成25年7月22日 (2013.7.22)

(31) 優先権主張番号 特願2010-5153 (P2010-5153)

(32) 優先日 平成22年1月13日 (2010.1.13)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像システム及び撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が入射光に応じて画素信号を出力する、行列状に配列された複数の画素と、前記複数の画素の列に対応して設けられた複数のA/D変換回路と、を備える撮像システムであつて、

前記A/D変換回路は、

前記画素信号を電圧レベルとして保持する保持部と、

前記保持部に保持された電圧レベルと基準レベルとの比較を行う比較器と、

前記保持部に保持された電圧レベルが第1の割合と前記第1の割合よりも小さい第2の割合とで前記基準レベルに近づくように前記保持部に保持された電圧レベルを変化させる手段と、を備え、

前記保持部に保持された前記画素信号の電圧レベルを前記第1の割合で変化させ、前記保持部に保持された電圧レベルと前記基準レベルとの関係が逆転したことに応じて上位ビットを決定し、その後、前記保持部に保持された電圧レベルを前記第2の割合で変化させ、前記保持部に保持された電圧レベルと前記基準レベルとの関係が逆転したことに応じて下位ビットを決定し、

前記撮像システムはさらに、

前記上位ビットの決定の後の前記保持部に保持された電圧レベルが取り得る範囲に渡つて前記保持部に保持された電圧レベルと前記下位ビットとの関係が線形となるように、前記上位ビットの決定の後、前記第2の割合で前記保持部に保持された電圧レベルを変化さ

10

20

せるまでの期間に、前記保持部に保持された電圧レベルを調整する調整部を備えることを特徴とする撮像システム。

【請求項 2】

撮像装置と、前記撮像装置を調整するための調整装置と、を有する撮像システムにおいて、

前記撮像装置は、複数の光電変換素子が二次元アレイ状に配置された画素領域を含む撮像部と、前記撮像部の出力を上位ビットおよび下位ビットからなるディジタル信号に変換するA / D変換回路と、調整データを記憶するメモリとを有し、

前記A / D変換回路は、

電圧レベルを保持する保持部と、

10

前記撮像部から出力された信号の電圧レベルを初期レベルとして前記保持部に保持させる書き込み部と、を備え、

前記A / D変換回路は、前記保持部によって保持された電圧レベルを前記初期レベルから第1の傾きで基準レベルに向けて変化させながら、その変化を開始した時刻から前記電圧レベルが前記基準レベルと交差する時刻までの時間をカウントするカウンタによるカウント値を前記上位ビットとし、前記電圧レベルが前記基準レベルと交差し、前記電圧レベルと前記基準レベルとの間に差分が生じた後に前記電圧レベルを第2の傾きで前記基準レベルに向けて変化させながら、前記第2の傾きで変化を開始した時刻から前記電圧レベルが前記基準レベルと再び交差する時刻までの時間をカウントする前記カウンタによるカウント値を前記下位ビットとするように構成され、前記差分の発生量は前記メモリに格納された前記調整データに従って調整され、

20

前記調整装置は、

前記A / D変換回路に複数の電圧レベルを順に提供して、前記A / D変換回路に前記複数の電圧レベルをディジタル信号に変換させる提供部と、

前記複数の電圧レベルとそれらが前記A / D変換回路に提供されたときに前記A / D変換回路から出力されるディジタル信号の値とが前記電圧レベルのとり得る範囲の全域にわたって線形になるように前記差分の発生量を調整するための前記調整データを前記メモリに格納する処理部と、

を具備することを特徴とする撮像システム。

【請求項 3】

30

複数の光電変換素子が二次元アレイ状に配置された画素領域を含む撮像部と、前記撮像部の出力を上位ビットおよび下位ビットからなるディジタル信号に変換するA / D変換回路と、調整データを記憶するメモリと、調整回路とを備える撮像装置であって、前記A / D変換回路は、

電圧レベルを保持する保持部と、

前記光電変換素子から出力された信号の電圧レベルを初期レベルとして前記保持部に保持させる書き込み部とを備え、

前記A / D変換回路は、前記保持部によって保持された電圧レベルを前記初期レベルから第1の傾きで基準レベルに向けて変化させながら、その変化を開始した時刻から前記電圧レベルが前記基準レベルと交差する時刻までの時間をカウントするカウンタによるカウント値を前記上位ビットとし、前記電圧レベルが前記基準レベルと交差し、前記電圧レベルと前記基準レベルとの間に差分が生じた後に前記電圧レベルを第2の傾きで前記基準レベルに向けて変化させながら、前記第2の傾きで変化を開始した時刻から前記電圧レベルが前記基準レベルと再び交差する時刻までの時間をカウントする前記カウンタによるカウント値を前記下位ビットとするように構成され、前記差分の発生量は前記メモリに格納された前記調整データに従って調整され、

40

前記調整データは、

前記A / D変換回路に複数の電圧レベルを供給したときに前記A / D変換回路から出力されるディジタル信号の値と前記複数の電圧レベルとの関係が前記A / D変換回路の入力の値がとり得る範囲の全域にわたって線形となるように前記差分の発生量を制御するデー

50

タであり、

前記調整回路は、前記調整データを前記メモリから読み出して前記差分の発生量を制御する差分制御回路を備えることを特徴とする撮像装置。

**【請求項 4】**

前記A / D変換回路は、前記保持部にそれぞれ互いに電流値の異なる第1および第2の電流を供給する第1および第2の電流源を更に備え、前記第1および第2の電流を前記保持部に供給することによって前記第1及び第2の傾きで前記電圧レベルを変化させることを特徴とする請求項3に記載の撮像装置。

**【請求項 5】**

前記差分制御回路は、前記A / D変換回路を駆動するクロック信号の位相を制御することを特徴とする請求項3に記載の撮像装置。 10

**【請求項 6】**

前記差分制御回路は、前記電圧レベルに対して前記第2の傾きで変化を開始した時刻から前記カウンタによるカウントの開始までの時間を制御することを特徴とする請求項3に記載の撮像装置。

**【請求項 7】**

前記A / D変換回路は、前記保持部によって保持された電圧レベルを前記初期レベルから前記第1の傾きで前記基準レベルに向けて変化させたときに前記電圧レベルが前記基準レベルと交差した後であって、前記電圧レベルを前記第2の傾きで前記基準レベルに向けて変化させる前に電流を前記保持部に供給することによって前記電圧レベルを変化させる第3の電流源を更に備え、前記差分制御回路は前記第3の電流源で前記電圧レベルを変化させる時間を制御することによって前記差分の発生量を制御することを特徴とする請求項4に記載の撮像装置。 20

**【請求項 8】**

前記A / D変換回路は、前記保持部によって保持された電圧レベルを前記初期レベルから前記第1の傾きで前記基準レベルに向けて変化させたときに前記電圧レベルが前記基準レベルと交差した後であって、前記電圧レベルを前記第2の傾きで前記基準レベルに向けて変化させる前に電流を前記保持部に供給することによって前記電圧レベルを変化させる電流源を更に備え、前記差分制御回路は前記電流源が前記保持部に供給する電流の値を制御することによって前記差分の発生量を制御することを特徴とする請求項3に記載の撮像装置。 30

**【請求項 9】**

前記A / D変換回路は前記下位ビットのビット数を変更可能に構成されていることを特徴とする請求項3に記載の撮像装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は撮像システム及び撮像装置に関する。

**【背景技術】**

**【0002】**

近年の撮像装置に用いられるA / D (Analog to Digital)変換方法として、イメージセンサの画素の一列ごとにA / D変換器を設置するカラムA / Dと呼ばれる方法がある。カラムA / Dに用いられるA / D変換器として積分型A / D変換方式が挙げられる。中でも上位のビットと下位のビットの2段階、もしくはそれ以上に分けてA / D変換を行うマルチステップ方式が特許文献1に開示されている。 40

**【先行技術文献】**

**【特許文献】**

**【0003】**

【特許文献1】特開2005-348325号公報

**【発明の概要】**

## 【発明が解決しようとする課題】

## 【0004】

特許文献1によると、二次元アレイ状にセンシング素子がならべられ、センシング素子の列ごとにA/D変換器が設けられている撮像装置が開示されている。この撮像装置において、A/D変換器は、アナログ信号となるセンシング素子の信号に対応した電気信号を初期値として記憶部に保持する。そののちに入力される第1の固定信号により記憶部の充電もしくは放電を行う。放電もしくは充電の開始時間から記憶部の電気信号が基準信号に達するまで時間を離散的に計測する。その後入力される第2の固定信号により記憶部の放電もしくは充電を行い、計測後の記憶部の基準信号を超えた電気信号が基準信号に達するまでの時間を離散的に計測してデジタル値とする。より具体的には、積分器の出力を画素信号電圧にセットした後、負の傾きで積分を開始する。ある時刻に積分器の出力は基準電圧を下回り上位NビットのA/D変換が終了する。終了した時点で積分が一度中断されるが、スイッチは離散時間で制御されているために積分器の出力と基準電圧の差は0にならぬ、両者の間には電位差（残差信号）が存在する。次のステップで、一回目の電位差を再度積分することで下位Mビットの変換を行う。その後のある時刻に再度比較器の基準電圧と積分器出力が交わり、下位MビットのA/D変換が終了する。

10

## 【0005】

しかしながら、上記従来例では上位変換後の積分器出力と基準電圧の差である残差信号にリークや遅延などによってオフセットが乗ると、下位カウント期間終了までに判定を終えないと、又は逆に下位変換カウント前に比較器が反転する場合がある。このような場合、変換の線形性を悪化させる。

20

## 【0006】

本発明の目的はA/D変換回路に入力される電圧レベルとA/D変換回路から出力されるデジタル信号との線形性を調整することができる撮像システム及び撮像装置を提供することである。

## 【課題を解決するための手段】

## 【0007】

本発明の1つの側面は、各々が入射光に応じて画素信号を出力する、行列状に配列された複数の画素と、前記複数の画素の列に対応して設けられた複数のA/D変換回路と、を備える撮像システムであって、前記A/D変換回路は、前記画素信号を電圧レベルとして保持する保持部と、前記保持部に保持された電圧レベルと基準レベルとの比較を行う比較器と、前記保持部に保持された電圧レベルが第1の割合と前記第1の割合よりも小さい第2の割合とで前記基準レベルに近づくように前記保持部に保持された電圧レベルを変化させる手段と、を備え、前記保持部に保持された前記画素信号の電圧レベルを前記第1の割合で変化させ、前記保持部に保持された電圧レベルと前記基準レベルとの関係が逆転したことに応じて上位ビットを決定し、その後、前記保持部に保持された電圧レベルを前記第2の割合で変化させ、前記保持部に保持された電圧レベルと前記基準レベルとの関係が逆転したことに応じて下位ビットを決定し、

30

前記撮像システムはさらに、前記上位ビットの決定の後の前記保持部に保持された電圧レベルが取り得る範囲に渡って前記保持部に保持された電圧レベルと前記下位ビットとの関係が線形となるように、前記上位ビットの決定の後、前記第2の割合で前記保持部に保持された電圧レベルを変化させるまでの期間に、前記保持部に保持された電圧レベルを調整する調整部を備えることを特徴とする。

40

## 【発明の効果】

## 【0008】

本発明によれば、A/D変換回路に入力される電圧レベルとA/D変換回路から出力されるデジタル信号との線形性を調整することができる。

## 【図面の簡単な説明】

## 【0009】

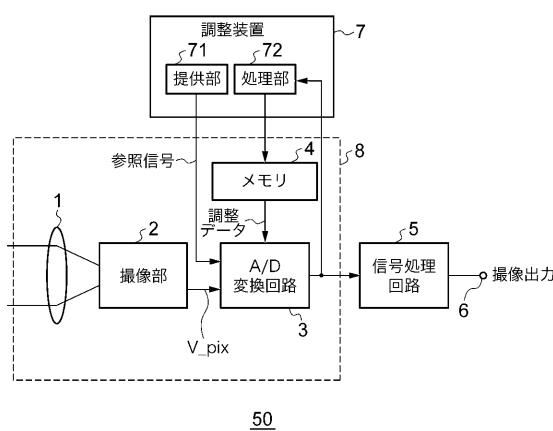

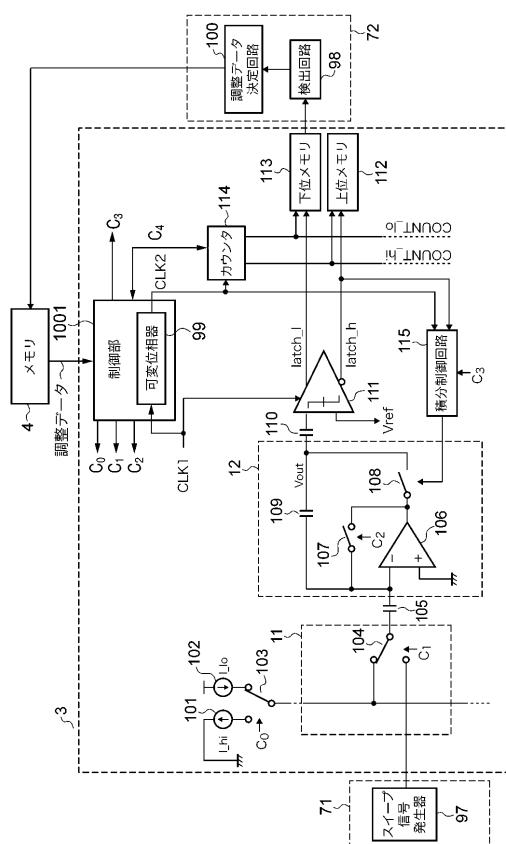

【図1】本発明が適用される撮像システムを示す図である。

50

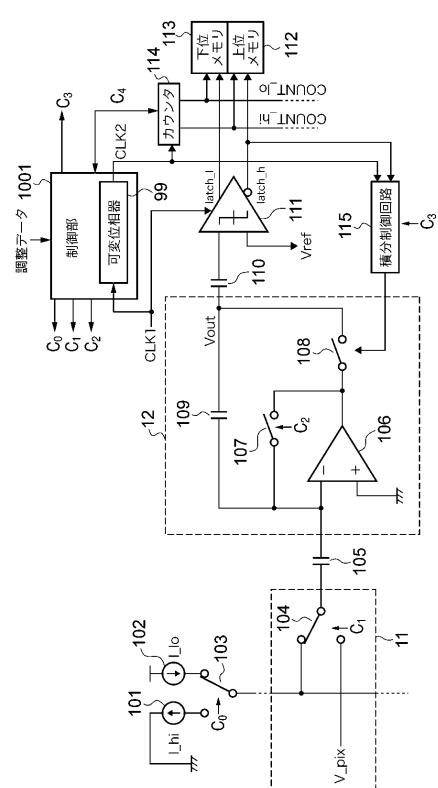

【図2】実施例1を説明する回路図である。

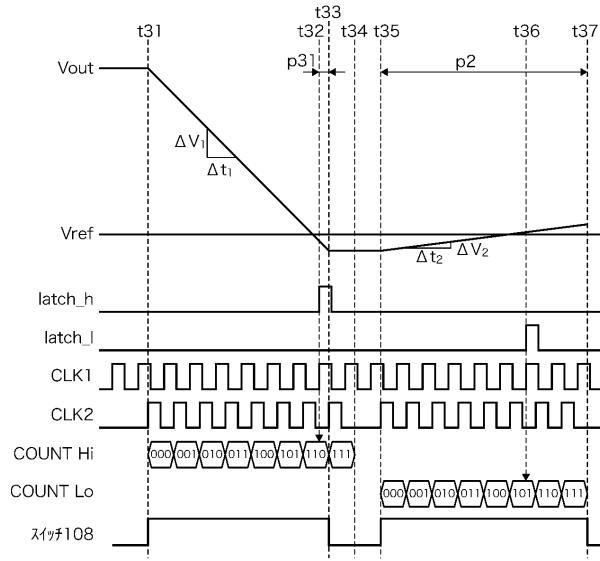

【図3】図1の駆動タイミング図、及び動作波形である。

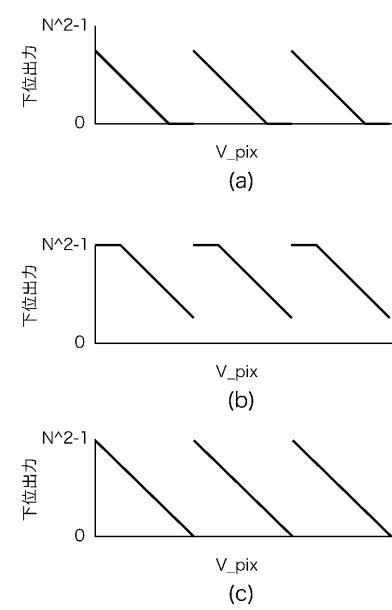

【図4】オーバーレンジの状態を説明する図である。

【図5】本発明による差分を調整する方法を説明する図である。

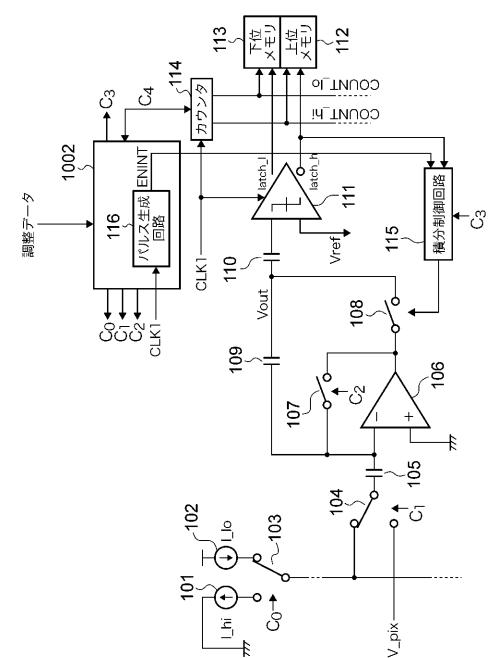

【図6】実施例2を説明する回路図である。

【図7】図5の駆動タイミング図、及び動作波形である。

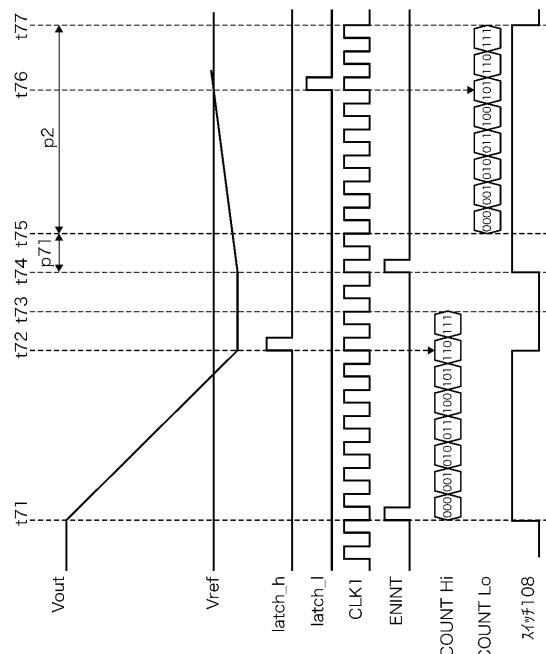

【図8】実施例3を説明する回路図である。

【図9】図7の駆動タイミング図、及び動作波形である。

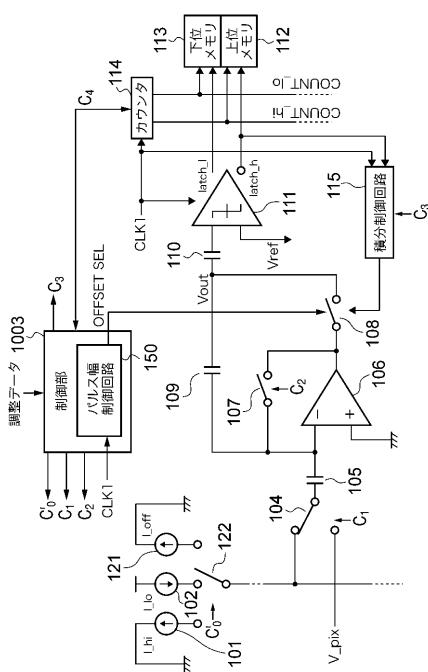

【図10】実施例4を説明する回路図である。

【図11】図9の駆動タイミング図、及び動作波形である。

【図12】実施例5の駆動タイミング図である。

【発明を実施するための形態】

【0010】

図1に本発明の実施形態の撮像システムを示す。図1において、撮像システム50は、光学系1と、撮像装置8と、調整部を構成する調整装置7と、信号処理回路5とを含む。撮像装置8は撮像部2と、A/D変換回路3と、メモリ4とを備える。光学系1は、撮像部2の撮像面に被写体の像を形成する。撮像部2は、例えばCMOSイメージセンサまたはCCDイメージセンサ等の固体撮像素子である。撮像部2の撮像面には、入射光に応じて画素信号を発生する光電変換素子を含む画素が複数行および複数列を構成するように二次元アレイ状、すなわち行列状に配列されている。撮像部2で撮像された画像の信号は、アナログ画素信号Vpixとして撮像部2から出力される。A/D変換回路3は、撮像部2から出力されたアナログ画素信号Vpixをデジタル信号に変換して出力する。信号処理回路5は、A/D変換回路3から出力されたデジタル信号を処理して出力端子6から出力する。

【0011】

撮像部2とA/D変換回路3とは、1つの半導体チップ上に形成されてもよいし、別々の半導体チップ上に形成されてもよい。ただ、少なくとも撮像部2の画素アレイとA/D変換回路は同一の半導体チップ上に形成される。また、メモリ4も撮像部2と同一の半導体チップ上に設けられてもよい。撮像部2とA/D変換回路3とが1つの半導体チップ上に形成される場合において、画素の1又は複数の列ごとにA/D変換回路が設けられてもよいし、画素信号の出力数と同数のA/D変換回路が設けられてもよいし、他の形態が採用されてもよい。

【0012】

調整装置7はA/D変換回路3に複数の参照信号を提供する提供部71と調整データをメモリ4に記憶する処理部72を具備する。なお、ここでメモリ4には例えばバッテリーでバックアップされた揮発性のメモリや、不揮発性のメモリが用いられる。

【0013】

図2は、上位変換と下位変換の2段階でA/D変換を行うA/D変換回路3の実施例1の構成を示す図である。第1の電流源である上位電流源回路101、第2の電流源である下位電流源回路102はそれぞれ図3に示される第1および第2の傾きV1/t1, V2/t2で保持部を構成する積分回路12によって保持された電圧レベルを変化させる上位電流源回路、下位電流源回路である。それぞれ電流I\_hi及びI\_loを積分回路12に供給している。これらの電流の値によって前記第1の割合とこれよりも小さい第2の割合が決定される。ここで電流を供給するという表現は、積分回路12に電流を流す動作だけではなく、積分回路から電流を引き出す動作の両方を含む。下位変換をMビットで行う場合、 $I_{hi} = -I_{lo} \times 2^M$ である。上位電流源回路101と下位電流源回路102は制御部1001からの制御信号C0によって制御されるスイッチ103で選択される。また選択された電流源と画素出力Vpixは制御部1001からの制御信号C1によって制御されるスイッチ104で選択される。選択された信号は入力容量105を介し、演算増幅器106、制御部1001からの制御信号C2によって制御されるリセットスイッチ107、積

10

20

30

40

50

分制御回路 115 によって制御される積分制御スイッチ 108、積分容量 109 からなる保持部を構成する積分回路 12 に供給される。

【0014】

ノード  $V_{out}$  の積分回路 12 の出力は接続容量 110 を介して比較器 111 に入力される。比較器 111 はクロック信号  $CLK_1$  の立ち上がりのタイミングで比較判定を行い、積分回路 12 の出力が基準電圧を下回ったときに  $latch_h$  を、積分回路 12 の出力が上回ったときに  $latch_l$  を出力する。出力  $latch_h$  及び  $latch_l$  はそれぞれ上位メモリ 112 と下位メモリ 113 に入力される。114 は可変位相器 99 によって位相を調整されたクロック信号  $CLK_2$  及び制御部 1001 からの制御信号  $C4$  で制御されるカウンタで、上位のカウンタ値  $COUNT_hi$  が上位メモリ 112、下位のカウンタ値  $COUNT_l$  が下位メモリ 113 に入力される。上位メモリ 112、下位メモリ 113 はそれぞれ  $latch_h$ 、 $latch_l$  が入力された時のカウンタ値を保持する。最終的な A/D 変換のデジタル信号出力は上位メモリ 112 の値である上位ビットと下位メモリ 113 の値である下位ビットを結合した値である。 10

【0015】

115 は積分制御回路で積分制御スイッチ 108 の ON/OFF を行う。積分制御回路 115 は  $CLK_2$  及び制御部 1001 からの制御信号  $C3$  に応じて動作し、 $latch_h$  が入力された後の  $CLK_2$  の立ち上がりタイミングで積分制御スイッチ 108 を OFF する。また、積分制御回路 115 は、当該制御信号  $C3$  がハイレベルとなった後に可変位相器 99 から入力される  $CLK_2$  の立ち上がりで、積分制御スイッチ 108 を ON する。 20

【0016】

ここで、図 2 において 11 はスイッチ 104 によって保持部を構成する積分回路 12 に画素出力  $V_{pix}$  を初期値として設定するための書き込み部である。

【0017】

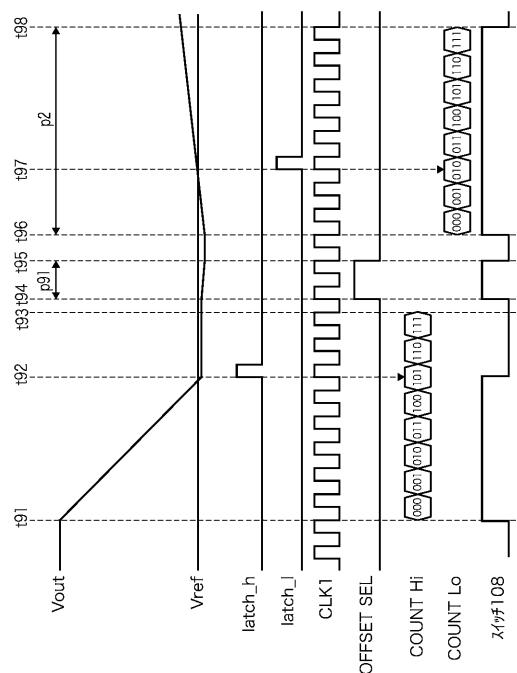

図 3 は図 2 の駆動状態を示す駆動タイミング図、及び動作波形である。図 3 において  $V_{out}$  は、図 2 におけるノード  $V_{out}$  の電位を表している。

【0018】

まず、通常の撮像動作時、撮像部 2 から出力されるアナログ画素信号  $V_{pix}$  を A/D 変換回路 3 で A/D 変換する動作を説明する。書き込み部 11 を構成するスイッチ 104 が画素信号  $V_{pix}$  を選択することによって、この画素信号  $V_{pix}$  が積分回路 12 に供給され、 $V_{out}$  のノードは画素信号  $V_{pix}$  によって充電される。時刻  $t_{31}$  において、 $CLK_2$  の立ち上がりに同期して、積分制御回路 115 が積分制御スイッチ 108 を ON にし、上位ビットに係る積分動作が始まる。この時、スイッチ 103 及び 104 によって入力には上位電流源回路 101 が選択されおり、上位電流  $I_{hi}$  によって積分回路 12 が放電されることでノード  $V_{out}$  の電位が低下する。これによって積分回路 12 の電圧レベルを、画素出力  $V_{pix}$  に設定された初期レベルから第 1 の傾き（第 1 の割合）-  $V_1 / t_1$  によって変化させる動作が行われる。比較部を構成する比較器 111 の判定は  $CLK_1$  の立ち上がりのタイミングで行われている。そのためノード  $V_{out}$  の電位が基準電圧を下回った後、すなわち両者の関係が逆転した後に  $CLK_1$  が初めて立ち上がるタイミングである時刻  $t_{32}$  に比較器 111 の出力が反転し、ハイレベルの  $latch_h$  が出力される。ハイレベルの  $latch_h$  を受けた上位メモリ 112 はこの時点でのカウント値を保持する。このカウント値が上位ビットとなり上位ビットが決定される。一方、積分制御回路 115 はハイレベルの  $latch_h$  が入力された後の  $CLK_2$  の立ち上がりで積分制御スイッチ 108 を OFF にするため、時刻  $t_{33}$  で積分動作が停止する。時刻  $t_{34}$  はカウンタ 114 の上位ビットが "111" となったタイミングで上位変換の終了時刻である。上位ビット決定の後、時刻  $t_{35}$  でスイッチ 103 を下位電流源回路 102 に切り替えるとともに再び積分制御スイッチ 108 を ON にし、下位ビットに係る積分を開始する。これによって積分回路 12 の電圧レベルを基準電圧と交差し、基準電圧との間に差分が生じた電圧レベルを第 2 の傾き（第 2 の割合）+  $V_2 / t_2$  で変化させる動作が行われる。時刻  $t_{36}$  で積分回路 12 の電圧レベルが基準電圧を上回る、すなわち両者の関係が再度逆転するた 40

めに、比較器 111 の出力が再び反転し、ハイレベルの  $l\ a\ t\ c\ h\_1$  を出力する。ハイレベルの  $l\ a\ t\ c\ h\_1$  を受けた下位メモリ 113 はこの時点でのカウンタ値を保持する。時刻  $t37$  はカウンタ 114 の下位ビットが "111" となったタイミングで下位変換の終了時刻である。

#### 【 0 0 1 9 】

本実施例では比較器 111 と積分制御スイッチ 108 をそれぞれ  $C\ L\ K\ 1$  と  $C\ L\ K\ 2$  に応じて動作させることで、比較判定時刻  $t32$  から積分停止時刻  $t33$  間での期間  $p\ 31$  の間、差分の発生量に対してオフセットを与えている。期間  $p\ 31$  は可変位相器 99 によって  $C\ L\ K\ 1$  と  $C\ L\ K\ 2$  のタイミングを変更することで調整可能である。可変位相器 99 は例えば  $D\ L\ L$  回路を含んで構成される。期間  $p\ 31$  の長さによって積分出力  $V\ o\ u\ t$  と基準レベルとなる基準電圧  $V\ r\ e\ f$  との差分にあたる残差信号に付与されるオフセット量を調整できる。これにより、下位の判定が下位変換期間  $p\ 2$  内に終えるように調整ができ、結果として線形性の悪化を抑制することができる。10

#### 【 0 0 2 0 】

この例では  $C\ L\ K\ 1$  と  $C\ L\ K\ 2$  とで制御しているが、一つのクロック信号を遅延させることで 2 つのクロック信号を生成したり、又は一つのクロック信号の立ち上がりと立下りを用いて期間  $p\ 31$  を作ったりしても良い。

#### 【 0 0 2 1 】

残差信号の調整量を決める方法として入力をスイープさせたときの下位出力から判定する方法がある。図 4 にオーバーレンジしている場合と、適切な範囲である場合の下位出力を示す。図 4 (a) の場合最小出力が連続して出力されている。これは残差信号が理想より小さいためオーバーレンジしている（図 3 で下位の判定が下位変換期間  $p\ 2$  の前半のみ）場合である。同様に図 4 (b) では最大の出力が連続して出力されており、残差信号が理想より大きいためオーバーレンジしている（図 3 で下位の判定が下位変換期間  $p\ 2$  の後半のみ）場合である。すなわち、光電変換素子の出力の変化範囲で下位ビットが非線形に変化していることがわかる。それに対して図 4 (c) は適切な範囲で動作している場合であり最小出力や最大出力は連続して出力されていない。すなわち前記光電変換素子の出力の値と前記ディジタル信号の下位信号の値との関係が前記光電変換素子の出力の値がとり得る範囲の全域にわたって線形となるように変化している（図 3 で下位の判定が下位変換期間  $p\ 2$  の全体に広がる）ことがわかる。このような状態を理想の状態として想定している。よって最小出力が連続して出力される場合残差信号を増やす方向に調整を行う。逆に最大出力が連続する場合は残差信号を減らす方向に調整を行い、最小出力や最大出力が連続して出力されていない状態まで続けることで適切な調整量を得ることができる。20

#### 【 0 0 2 2 】

実施例 1 では入力をスイープさせ、最小出力が連続して出力される場合に、期間  $p\ 31$  を徐々に増やしていく、最小出力が連続して出力されなくなった時の期間  $p\ 31$  が調整量として適している。

#### 【 0 0 2 3 】

次に図 5 を参照してキャリブレーション時に、この期間  $p\ 31$  を調整する方法について説明する。例えば工場出荷時に、図 1 の調整装置 7 に設けられたスイープ信号発生器 97 から連続的に変化するスイープ信号が積分回路 12 (図 2) に供給される。すなわち、複数の電圧レベルがこのスイープ信号発生器 97 によって積分回路 12 に順に提供され、上位及び下位の A/D 変換が行われる。ここで、下位メモリ 113 からの信号を検出回路 98 に供給して、この検出回路 98 で下位信号が最大値、または最小値をどの程度連続して出力しているかを検出する。そしてこの検出回路 98 の出力を例えば LUT (ルックアップテーブル) を有する調整データ決定回路 100 で検出回路 98 の出力に従って調整データを決定する。この調整データをメモリ 4 に格納する。なお、この検出回路 98 及び調整データ決定回路 100 は図 1 の調整装置 7 の処理部 72 に設けられている。調整データ決定回路 100 の出力によって差分制御回路を構成する可変位相器 99 を制御する。それにより、 $C\ L\ K\ 1$  と  $C\ L\ K\ 2$  の位相差を制御し期間  $p\ 31$  を残差信号が理想となるよう変更す40

る。また、上述したように最小出力が連続した場合には期間 p31 を徐々に増加させる。逆に最大値が連続した場合には期間 p31 を徐々に減少させる。そして最小出力または最大出力が連続しないように、ある程度時間をかけて制御するようにしてもよい。この調整装置 7 によって複数の電圧レベルが順に提供されたときに、A / D 変換回路 3 から出力されるディジタル信号とこの電圧レベルとの関係が、この電圧レベルのとり得る範囲の全域にわたって線形になるように期間 p31 が制御される。これにより第 4 図 (c) に示されるような関係が実現される。このようにして得られた期間 p31 のデータが図 1 のメモリ 4 に格納される。撮像装置 8 の通常動作時はこのメモリ 4 に格納された期間 p31 のデータが調整データとして用いられる。なお、このメモリ 4 に格納される調整データは画素領域の列ごとに発生させて、それぞれ異なるアドレスに格納してもよい。また、全列共通の調整データを格納してもよい。上記した調整方法は実施例 1 以外の他の実施例にも適用できる。

#### 【0024】

図 6 は A / D 変換回路 3 の実施例 2 の構成を示した図である。図 2 との違いを説明する。図 6 では比較器 111 とカウンタ 114 は共通の CLK1 で制御されている。一方、実施例 2 の制御部 1002 はパルス生成回路 116 を有し、積分制御回路 115 は積分開始をパルス生成回路 116 によって生成されるパルス E N I N T の立ち上がりで、停止を 1 a t c h \_h での立ち上がりでコントロールされている。なお、実施例 2 では、下位変換時のカウンタ 114 のカウント開始は制御信号 C4 によって上位変換時のカウンタ 114 のカウント終了から遅延を有するよう制御され、その間でパルス E N I N T の出力を制御する。他の構成は、図 2 と同様である。

#### 【0025】

図 7 は図 6 の駆動状態を示す駆動タイミング図、及び動作波形である。

#### 【0026】

まず、ノード Vout は画素出力によってあらかじめ充電されているものとする。時刻 t71において、ハイレベルのパルス E N I N T が積分制御回路 115 に入力されて積分制御スイッチ 108 が ON になることで、上位ビットに係る積分動作が始まる。また、同時にカウンタ 114 によるカウント動作を開始している。

この時、スイッチ 103 及び 104 によって入力には上位電流源回路 101 が入力容量 105 に電流を供給するように選択されており、上位電流 I\_hi によって積分回路が放電されることでノード Vout の電位が低下する。比較の判定は CLK1 の立ち上がりのタイミングで行われるため、ノード Vout の電位が Vref を下回った後に CLK1 が初めて立ち上がる時刻 t72において比較器の反転動作が行われ、ハイレベルの 1 a t c h \_h が输出される。ハイレベルの 1 a t c h \_h を受けた上位メモリ 112 はその時点でのカウント値を保持する。同時にハイレベルの 1 a t c h \_h を受けた積分制御回路 115 は積分制御スイッチ 108 を OFF にして積分を停止する。時刻 t73 はカウンタ 114 の上位ビットが "111" となつたタイミングで上位変換の終了時刻である。

#### 【0027】

その後、スイッチ 103 を下位電流源回路 102 に切り替え、時刻 t74 でパルス E N I N T が立ち上がり再び積分制御スイッチ 108 を ON にして下位積分を開始する。この時、積分制御スイッチ 108 が ON してもそれに同期してカウンタ 114 は動作せず、時刻 t74 から期間 p71 経過した後の時刻 t75 でカウント動作を開始する。かかる期間 p71 は、パルス E N I N T の発生する時刻 t74 ( 前のパルス E N I N T の発生した時刻 t71 からの CLK1 の数 ) により決まる。

#### 【0028】

時刻 t76 で再び比較器が反転しハイレベルの 1 a t c h \_l を出力し、ハイレベルの 1 a t c h \_l を受けた下位メモリ 113 はカウンタ値を保持する。時刻 t77 はカウンタ 114 の下位ビットが "111" となつたタイミングで下位変換の終了時刻である。

#### 【0029】

本実施例では下位ビットに係る積分開始時刻 t74 からカウント開始時刻 t75 までの期間 p

10

20

30

40

50

71の長さによって残差信号のオフセット量を調整することができる。p71を残差信号の理想値との差に応じた値にすることで、下位変換期間p2内で変換が行われるように調整することが可能であり、結果として線形性の悪化を抑制することができる。調整量の決定の仕方は、実施例1において説明したものと同様である。すなわち、実施例1と同様にスイープ信号発生器97、検出回路98、調整データ決定回路100を設ける。積分回路の入力V<sub>pix</sub>を提供部71に設けられたスイープ信号発生器97から供給されるスイープ信号によってスイープして連続的に変化させたときに、下位メモリ113の出力を検出回路98によって検出する。この検出回路98で下位信号が最大値、または最小値をどの程度連続して出力しているかを検出する。また、この検出回路98の出力によって調整データ決定回路100で調整データを決定する。なお、この検出回路98及び調整データ決定回路100は図1の調整装置7の処理部72に設けられる。その調整データをパルス生成回路116に供給して、パルスENTのタイミングを制御することでp71の期間を調整することができる。このようにして得られた期間p71のデータが図1のメモリ4に格納される。撮像装置8の通常動作時はこのメモリ4に格納された期間p71のデータがパルスENTのタイミングを制御するための調整データとして用いられる。なお、実施例2では、制御信号C4による下位変換時のカウンタ114のカウント開始時期t75の調整や、あるいはパルスENTのタイミングt74とカウント開始時期t75を共に調整してもよい。

### 【0030】

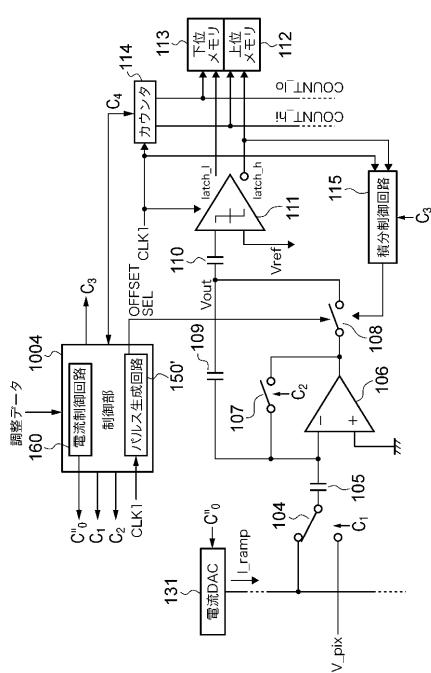

図8は実施例3に係るA/D変換回路3の構成例を示す回路図である。

10

### 【0031】

図2との違いを説明する。図8では上位電流源回路101、下位電流源回路102の他にオフセット電流源回路121が設けられる。オフセット電流源回路121により供給される電流I<sub>off</sub>は任意の値である。電流源回路101、102、121は制御部1003からの制御信号C0'によってスイッチ122によって選択される。また、積分制御スイッチ108はCLK1とlatch<sub>h</sub>によって駆動される積分制御回路115からの信号の他に制御部1003が有するパルス幅制御回路150からの信号でもスイッチングする。なお、図8の積分制御スイッチ108は、積分制御回路115からの信号とパルス幅制御回路150からの信号のいずれかがハイであれば、接続される。また、実施例3では、下位変換時のカウンタ114のカウント開始は制御信号C4によって上位変換時のカウンタ114のカウント終了から遅延を有するよう制御され、その間でパルス幅制御回路150からの信号の出力を制御する。他の構成は、図2と同様である。

20

### 【0032】

図9は図8の駆動状態を示す駆動タイミング図、及び動作波形である。

まず、V<sub>out</sub>は画素出力によってあらかじめ充電されているものとする。時刻t91において、CLK1に同期して積分制御回路115が積分制御スイッチ108をONにすることで、上位ビットに係る積分動作が開始される。また、同時にカウンタ114によるカウント動作を開始している。この時、スイッチ122及び104によって、上位電流源回路101からの電流が入力容量106に供給されるように選択されており、上位電流I<sub>hi</sub>によって積分回路が放電されることでノードV<sub>out</sub>の電位が低下する。比較器111の判定はCLK1の立ち上がりのタイミングで行われるため、ノードV<sub>out</sub>の電位がV<sub>ref</sub>を下回った後にCLK1が初めて立ち上がる時刻t92において比較器111の出力が反転し、ハイレベルのlatch<sub>h</sub>が出力される。ハイレベルのlatch<sub>h</sub>を受けた上位メモリ112はその時点のカウント値を保持する。同時にハイレベルのlatch<sub>h</sub>を受けた積分制御回路115は積分制御スイッチ108をOFFにして積分を停止する。時刻t93はカウンタ114の上位ビットが"111"となったタイミングで上位変換の終了時刻である。

30

### 【0033】

その後、スイッチ122をオフセット電流源回路121に切り替え、時刻t94でパルス制御回路150から出力される信号OFFSETSELが立ち下がり、積分制御スイッチ

40

50

をONする。信号OFFSETSELがハイの期間p91の後、時刻t95でオフセット積分を停止する。その後、スイッチ122を下位電流源回路102に切り替え、時刻t96で下位ビットに係る積分と下位カウントを開始する。

【0034】

時刻t97で再び比較器が反転しハイレベルのlatch\_1を出力し、ハイレベルのlatch\_1を受けた下位メモリ113はカウント値を保持する。時刻t98はカウンタ114のs下位ビットが"111"となったタイミングで下位変換の終了時刻である。

【0035】

本実施例では上位変換と下位変換の間に第3の電流源であるオフセット電流源回路121が供給するオフセット電流注入期間を設け任意の電流I\_offで期間p91の間積分している。よって、期間p91を変えることで、下位残差量を調整することができる。期間p91を下位残差信号の理想値との差に応じた値にすることで、下位の判定が下位変換期間p2内に終えるように調整ができる、結果として線形性の悪化を抑制することができる。具体的な調整方法としては上述と同様に、積分回路の入力Vpixをスイープして連続的に変化させる。すなわち複数の電圧レベルを順にA/D変換回路を構成する積分回路に提供する。そのとき下位メモリ113の出力を検出回路98によって検出し、この検出回路98で下位信号が最大値、または最小値をどの程度連続して出力しているかを検出する。また、この検出回路98の出力によって調整データ決定回路100で調整データを決定する。なお、この検出回路98及び調整データ決定回路100は図1の調整装置7の処理部72に設けられる。その調整データを信号OFFSETSELのパルス幅を制御するパルス幅制御回路150に供給して、その出力で積分スイッチ108を制御してオフセット電流I\_offによる積分期間p1を制御することができる。このようにして得られた期間p91のデータが図1のメモリ4に格納される。撮像装置8の通常動作時はこのメモリ4に格納された期間p91のデータが調整データとして用いられる。

【0036】

図10はA/D変換回路3の実施例4に係る回路図である。

【0037】

図8との違いを説明する。図10では電流源回路として電流DAC131を用いて任意の電流を供給している。電流DAC131は、例えば外部からのデジタル制御信号C0"に応じた電流を供給するものが考えられる。実施例4では、制御部1004にパルス幅が固定のパルス生成回路150'と電流DAC131の電流を調整データに従って調整する制御信号C0"を生成する電流制御回路160が設けられている。他の構成は図8と同様である。

【0038】

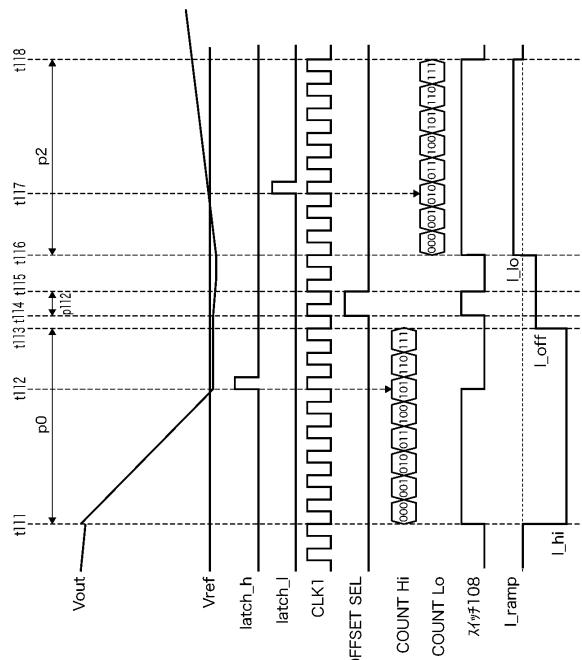

図11は図10の駆動状態を示す駆動タイミング図、及び動作波形である。

【0039】

まず、ノードVoutは画素出力によってあらかじめ充電されているものとする。時刻t111において、CLK1に同期して積分制御回路115が積分制御スイッチ108をONにし、上位ビットに係る積分動作が始まる。電流DAC131は期間p0の間、上位電流I\_hiを供給している。時刻t112で上位の判定が行われた後、時刻t113でカウンタ114の上位ビットが"111"となったタイミングで上位変換が終了する。次に、時刻t114でハイレベルの信号OFFSETSELによって積分制御スイッチ108がONし、期間p112の間、積分動作をする。期間p112は固定でよい。期間p112では電流DACは制御信号C0"により決定される任意の電流I\_offを供給している。

【0040】

時刻t115でオフセット電流による積分動作を停止した後、時刻t116で下位ビットに係る積分動作を開始し、時刻t117で下位の判定が行われる。期間p2では、電流DACは下位電流I\_loを供給している。下位変換をMbitで変換する場合、I\_hi = -I\_lo × 2Mである。電流DAC131を用いることで期間p112で供給される電流I\_offを任意の値にし、残差量を調整することが可能である。電流I\_offを下位残差信号の理想値との差に応じた

10

20

30

40

50

値にすることで、下位の判定が下位変換の期間  $p_2$  内に終わるようにすることができ、結果として線形性の悪化を抑制することが可能である。具体的な調整方法としては上述と同様積分回路の入力  $V_{pix}$  をスイープして連続的に変化させる。すなわち、複数電圧レベルを順に A / D 変換回路を構成する積分回路に提供する。そのとき、下位メモリ 113 の出力を検出回路 98 によって検出し、この検出回路 98 で下位信号が最大値、または最小値をどの程度連続して出力しているかを検出する。また、この検出回路 98 の出力によって調整データ決定回路 100 で調整データを決定する。なお、この検出回路 98 及び調整データ決定回路 100 は図 1 の調整装置 7 の処理部 72 に設けられる。その調整データを電流源 D A C 131 に供給し電流値  $I_{off}$  を制御することによって調整が可能である。このようにして得られた電流値  $I_{off}$  のデータが図 1 のメモリ 4 に格納される。撮像装置 8 の通常動作時はこのメモリ 4 に格納された  $I_{off}$  のデータが調整データとして用いられる。

10

#### 【0041】

次に、A / D 変換回路 3 の実施例 5 を示す。実施例 5 は下位変換に冗長 bit を持たせた例である。すなわち下位ビットのビット数を変更可能とした例である。

#### 【0042】

本実施例の説明に用いる回路図は図 2 と同様である。ただし、カウンタ 114 による下位のカウントは、上位のカウントの Mbit 精度に対して 1bit 冗長 bit を持たせて  $(M+1)$  bit で行う。よって下位出力は  $(M+1)$  bit である。上位出力の LSB ( 最下位ビット ) は下位出力の MSB ( 最上位ビット ) に相当する。また、電流源回路から供給される電流は  $I_{hi} = -I_{lo} \times 2M$  である。

20

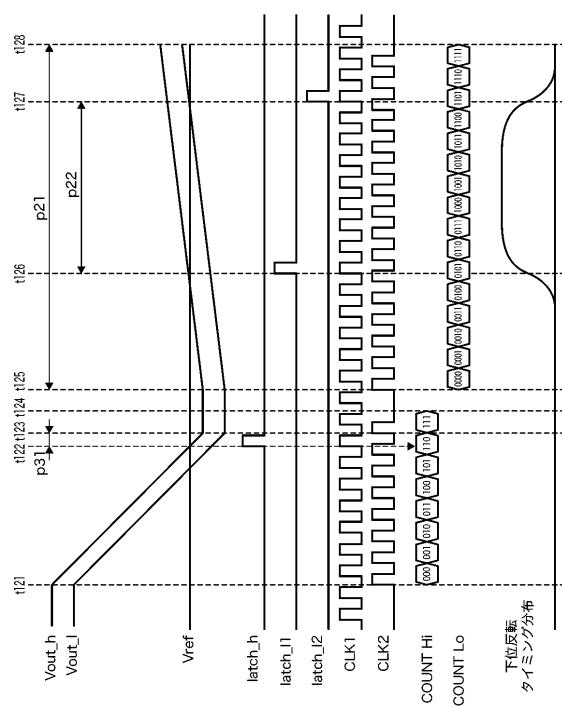

#### 【0043】

図 12 は本実施例の駆動状態を示す駆動タイミング図、及び動作波形である。  $V_{out\_h}$ ,  $V_{out\_l}$  はそれぞれ積分出力  $V_{out}$  の最大信号と最小信号である。時刻  $t_{121}$  で上位変換が開始し、積分出力  $V_{out}$  は時刻  $t_{122}$  で比較器の反転動作が行われて上位のカウントが上位メモリ 112 に記憶される。その後、CLK1 と CLK2 の位相差の期間  $p_{31}$  を経て時刻  $t_{123}$  で積分動作が停止する。そして、時刻  $t_{124}$  でカウンタ 114 の上位ビットが "111" となったタイミングで上位変換が終了する。その後、時刻  $t_{125}$  で下位の積分及びカウントが始まり、入力が  $V_{out\_h}$  の場合に時刻  $t_{126}$  で、入力が  $V_{out\_l}$  の場合に時刻  $t_{127}$  で比較器の反転し、それぞれ  $latch\_l1$  と  $latch\_l2$  を出力する。信号  $latch\_l1$  は  $V_{out\_h}$  が変換に供された場合に比較器 111 から出力される  $latch\_l$  の信号、信号  $latch\_l2$  は  $V_{out\_l}$  が変換に供された場合に比較器 111 から出力される  $latch\_l$  の信号である。時刻  $t_{128}$  はカウンタ 114 の下位ビットが "1111" となったタイミングで下位変換の終了時刻である。

30

#### 【0044】

ここで、理想的には下位変換は時刻  $t_{126}$  から時刻  $t_{127}$  までの期間  $p_{22}$  の幅を持って行われるが、ランダムノイズや ADC 間のばらつきなどにより実際には積分器の反転タイミング分布は図 12 の下位反転タイミング分布のようになる。下位 bit が冗長化されている場合、この分布が下位変換期間  $p_{21}$  内にあるように、期間  $p_{31}$  を調整することでリニアリティの悪化を抑制することができる。

40

#### 【0045】

本実施例では残差信号の調整機能と下位 bit の冗長化をあわせることで、下位出力がばらついた場合でもリニアリティの悪化を抑制する。また残差信号の調整精度が低くても許容される。

#### 【0046】

以上の各実施例においては、画素アレイの 1 列に対応する読み出し回路のみを示した。2 次元に画素が配置された画素アレイに対しては同じ構成の読み出し回路が並列に設けられており、図 2、6、8、10において、上位電流源回路 101、下位電流源回路 102、およびカウンタ 114 は、複数の読み出し回路に共通の構成となる。なお、実施例では積分回路に電流を供給しているが、電圧を用いたマルチステップ方式 A/D 変換回路構成に

50

も適用可能である。

### 【符号の説明】

【 0 0 4 7 】

101 上位電流源回路、102 下位電流源回路、12 積分回路、111 比較器

、112 上位メモリ、113 下位メモリ、114 カウンタ、115 積分制御回路

【 义 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

---

フロントページの続き

(72)発明者 池田 泰二

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 橋山 拓己

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 山崎 和男

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 松永 隆志

(56)参考文献 特開2005-347932(JP, A)

特開2005-348325(JP, A)

特開2008-211774(JP, A)

特開平05-199118(JP, A)

特開2006-128752(JP, A)

特開2006-033352(JP, A)

特開2009-239694(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/3745