(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6151681号

(P6151681)

(45) 発行日 平成29年6月21日(2017.6.21)

(24) 登録日 平成29年6月2日(2017.6.2)

(51) Int.CI.

F 1

|      |       |           |      |      |         |

|------|-------|-----------|------|------|---------|

| G09G | 3/30  | (2006.01) | G09G | 3/30 | K       |

| G09G | 3/20  | (2006.01) | G09G | 3/20 | 6 1 1 H |

| H01L | 51/50 | (2006.01) | G09G | 3/20 | 6 2 4 B |

|      |       |           | G09G | 3/20 | 6 4 1 E |

|      |       |           | G09G | 3/20 | 6 4 1 P |

請求項の数 5 (全 31 頁) 最終頁に続く

(21) 出願番号

特願2014-266955 (P2014-266955)

(22) 出願日

平成26年12月29日(2014.12.29)

(62) 分割の表示

特願2012-148099 (P2012-148099)

の分割

原出願日 平成14年9月6日(2002.9.6)

(65) 公開番号

特開2015-99372 (P2015-99372A)

(43) 公開日

平成27年5月28日(2015.5.28)

審査請求日 平成27年1月27日(2015.1.27)

審判番号 不服2016-16127 (P2016-16127/J1)

審判請求日 平成28年10月28日(2016.10.28)

(31) 優先権主張番号

特願2001-271424 (P2001-271424)

(32) 優先日

平成13年9月7日(2001.9.7)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

合議体

審判長 酒井 伸芳

審判官 中塚 直樹

審判官 関根 洋之

(56) 参考文献 特開平11-219146 (JP, A)

(58) 調査した分野(Int.CI., DB名)

G09G 3/30

(54) 【発明の名称】発光装置、表示モジュール、電子機器

## (57) 【特許請求の範囲】

## 【請求項1】

補正回路と、画素と、を有する発光装置であつて、

前記画素は、発光素子と、容量素子と、トランジスタと、を有し、

前記トランジスタは、前記容量素子の電圧に応じて、前記発光素子の輝度の大きさを制御することができる機能を有し、

前記トランジスタのドレインは、前記発光素子と電気的に接続され、

前記補正回路は、第1のデータと、第2のデータと、を用いて、前記画素に入力されるビデオ信号の大きさを、前記トランジスタの電流特性のばらつきの影響が小さくなるように補正することができる機能を有し、

第3のデータは、前記容量素子に第1の電圧値を有する電圧が入力された際に、前記トランジスタから得られた電流値に基づいたデータであり、

第4のデータは、前記容量素子に第2の電圧値を有する電圧が入力された際に、前記トランジスタから得られた電流値に基づいたデータであり、

前記第1のデータは、下記の式(1)のP1に前記第1の電圧値が入力され、下記の式(1)のQ1に前記第3のデータが入力された式と、下記の式(2)のP2に前記第2の電圧値が入力され、下記の式(2)のQ2に前記第4のデータが入力された式と、を用いて導出されたAに基づいたデータであり、

前記第2のデータは、下記の式(1)のP1に前記第1の電圧値が入力され、下記の式(1)のQ1に前記第3のデータが入力された式と、下記の式(2)のP2に前

10

20

記第2の電圧値が入力され、下記の式(2)のQ2に前記第4のデータが入力された式と、を用いて導出されたBに基づいたデータであることを特徴とする発光装置。

$$[ \text{式1} ] Q_1 = A \times (P_1 - B)^2$$

$$[ \text{式2} ] Q_2 = A \times (P_2 - B)^2$$

#### 【請求項2】

請求項1において、

前記トランジスタは、Nチャネル型であることを特徴とする発光装置。

#### 【請求項3】

請求項1において、

前記トランジスタは、Pチャネル型であることを特徴とする発光装置。 10

#### 【請求項4】

請求項1乃至請求項3のいずれか一に記載の発光装置と、

FPCと、

を有する表示モジュール。

#### 【請求項5】

発光装置、または、表示モジュールのいずれか一を有する電子機器であって、

操作キー、スピーカ、アンテナ、音声入力部、バッテリ、または、受像部と、

を有し、

前記発光装置は、請求項1乃至請求項3のいずれか一に記載の発光装置であり、

前記表示モジュールは、請求項4に記載の表示モジュールであることを特徴とする電子 20 機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体基板上又は絶縁表面上に発光素子と、該発光素子を制御するトランジスタとが設けられた発光装置及びその駆動方法に関する。より詳細には、発光素子を制御するトランジスタの特性バラツキの影響を防止した発光装置及びその駆動方法に関する。また本発明は、トランジスタ等の半導体素子を用いた発光装置に係る技術分野に属する。

##### 【背景技術】

##### 【0002】

近年、発光素子が用いられた発光装置(画像表示装置)の開発が進められている。発光装置は、大別してパッシブ型とアクティブ型に分類される。アクティブ型の発光装置は、絶縁表面上に発光素子と、該発光素子を制御するトランジスタとが設けられる。 30

##### 【0003】

ポリシリコン膜を用いたトランジスタは、従来のアモルファスシリコン膜を用いたトランジスタよりも電界効果移動度(モビリティともいう)が高く、高速動作が可能である。そのため、従来基板外の駆動回路で行っていた画素の制御を、画素と同一の絶縁表面上に形成した駆動回路で行うことが可能である。このようなアクティブ型の発光装置は、同一の絶縁表面上に様々な回路や素子を作り込むことで製造コストの低減、小型化、歩留まりの上昇及びスループットの低減などの様々な利点が得られる。 40

##### 【0004】

アクティブ型の発光装置の主な駆動方法としては、アナログ方式とデジタル方式が挙げられる。前者のアナログ方式は、発光素子に流れる電流を制御することにより、輝度を制御して階調を得る方式である。一方、後者のデジタル方式は、発光素子がオン状態(その輝度がほぼ100%である状態)と、オフ状態(その輝度がほぼ0%である状態)の2つの状態のみによって駆動される。しかしながら、デジタル方式の場合は、このままでは2階調しか表示できないため、時間階調方式や面積階調方式などと組み合わせて多階調化を実現する技術が提案されている(例えば特許文献1参照)。

##### 【先行技術文献】

##### 【特許文献】

## 【0005】

【特許文献1】特開2001-159878号公報(第6、7頁)

## 【0006】

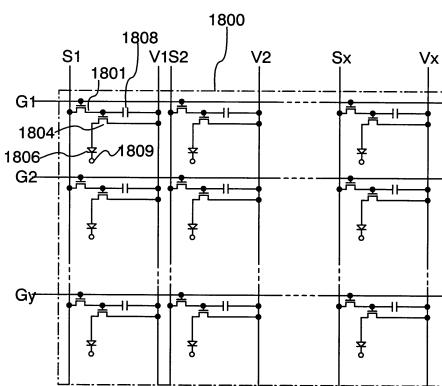

ここで、発光装置の駆動方法について、図14及び図15を用いて詳しく説明する。まず発光装置の構成について、図14を用いて説明する。図14には、発光装置が有する画素部1800の回路図の一例を示す。ゲート信号線駆動回路から供給されるゲート信号を画素に伝えるゲート信号線(G1～Gyのいずれか一つ)は、各画素が有するスイッチング用トランジスタ1801のゲート電極に接続されている。また各画素が有するスイッチング用トランジスタ1801のソース領域とドレイン領域は、一方はビデオ信号を入力するソース信号線(S1～Sxのいずれか一つ)に、もう一方は各画素が有する駆動用トランジスタ1804のゲート電極及び各画素が有するコンデンサ1808にそれぞれ接続されている。10

## 【0007】

各画素が有する駆動用トランジスタ1804のソース領域は電源供給線(V1～Vxのいずれか一つ)に接続されており、ドレイン領域は発光素子1806に接続されている。なお、電源供給線(V1～Vxのいずれか一つ)の電位は電源電位と呼ぶ。また電源供給線(V1～Vxのいずれか一つ)は、各画素が有するコンデンサ1808に接続されている。

## 【0008】

発光素子1806は、陽極及び陰極、並びに前記陽極と前記陰極の間に設けられた有機化合物層を有する。発光素子1806の陽極が駆動用トランジスタ1804のドレイン領域と接続している場合、発光素子1806の陽極が画素電極、陰極が対向電極となる。逆に発光素子1806の陰極が駆動用トランジスタ1804のドレイン領域と接続している場合、発光素子1806の陽極が対向電極、陰極が画素電極となる。20

## 【0009】

なお対向電極の電位を対向電位と呼び、対向電極に対向電位を与える電源を対向電源と呼ぶ。画素電極の電位と対向電極の電位の電位差が駆動電圧であり、この駆動電圧が有機化合物層にかかる。

## 【0010】

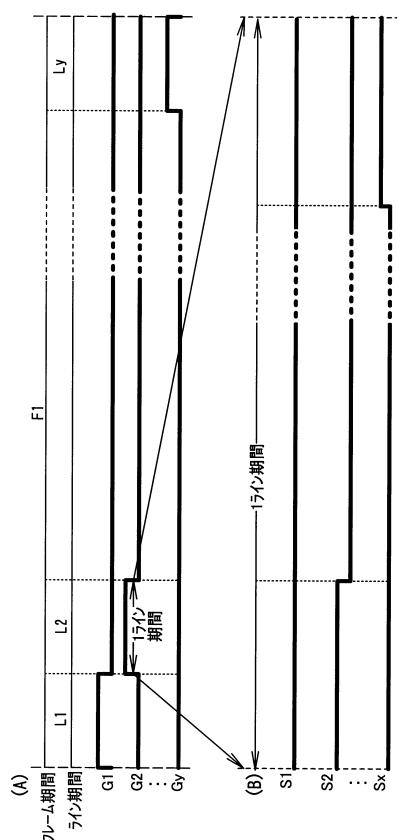

図14で示した発光装置を、アナログ方式で駆動させた場合のタイミングチャートを図15に示す。図15において、1つのゲート信号線が選択されてから、その次のゲート信号線が選択されるまでの期間を1ライン期間(L)と呼ぶ。また、1つの画像が表示されてから次の画像が表示されるまでの期間を1フレーム期間(F)と呼ぶ。図14の発光装置の場合、ゲート信号線はy本あるので、1フレーム期間中にy個のライン期間(L1～Ly)が設けられている。30

## 【0011】

電源供給線(V1～Vx)は、一定の電源電位に保たれている。また対向電極の電位である対向電位も一定の電位に保たれている。対向電位は、発光素子が発光する程度に電源電位との間に電位差を有している。

## 【0012】

第1のライン期間(L1)において、ゲート信号線駆動回路から供給されるゲート信号によって、ゲート信号線(G1)が選択される。なおゲート信号線が選択されるとは、該ゲート信号線にゲート電極が接続されたトランジスタがオンの状態になることを意味する。

## 【0013】

そして、ソース信号線(S1～Sx)に順にアナログのビデオ信号が入力される。ゲート信号線(G1)に接続された全てのスイッチング用トランジスタ1801はオン状態になっているので、ソース信号線(S1～Sx)に入力されたビデオ信号は、スイッチング用トランジスタ1801を介して駆動用トランジスタ1804のゲート電極に入力される。4050

## 【0014】

駆動用トランジスタ1804のチャネル形成領域を流れる電流の量は、駆動用トランジスタ1804のゲート電極に入力される信号の電位の高さ(電圧)によって制御される。よって、発光素子1806の画素電極にかかる電位は、駆動用トランジスタ1804のゲート電極に入力されたビデオ信号の電位の高さによって決まる。つまり発光素子1806はビデオ信号の電位の高さに応じて、発光素子1806に電流が流れ、その電流量に応じて発光を行う。

## 【0015】

上述した動作を繰り返し、ソース信号線(S1～Sx)にビデオ信号の入力が終了すると、第1のライン期間(L1)が終了する。次いで第2のライン期間(L2)となり、ゲート信号によってゲート信号線(G2)が選択される。そして第1のライン期間(L1)と同様にソース信号線(S1～Sx)に順にビデオ信号が入力される。

10

## 【0016】

上述した動作を繰り返し、全てのゲート信号線(G1～Gy)にゲート信号が入力されると、1フレーム期間が終了する。1フレーム期間において全ての画素が表示を行い、1つの画像が形成される。

## 【0017】

このように、ビデオ信号によって発光素子に流れる電流量が制御され、その電流量に応じて階調表示がなされる方式が、アナログ方式と呼ばれる駆動方式である。つまり、アナログ方式では、画素に入力されるビデオ信号の電位に応じて階調表示が行われる。

20

## 【0018】

一方、デジタル方式は、上述したように時間階調方式などと組み合わせて多階調化を実現する。詳しいタイミングチャートの図示は省略するが、時間階調方式と組み合わせたデジタル方式では、発光素子の両電極間に電流が流れている時間の長さに応じて階調表示が行われる。

## 【0019】

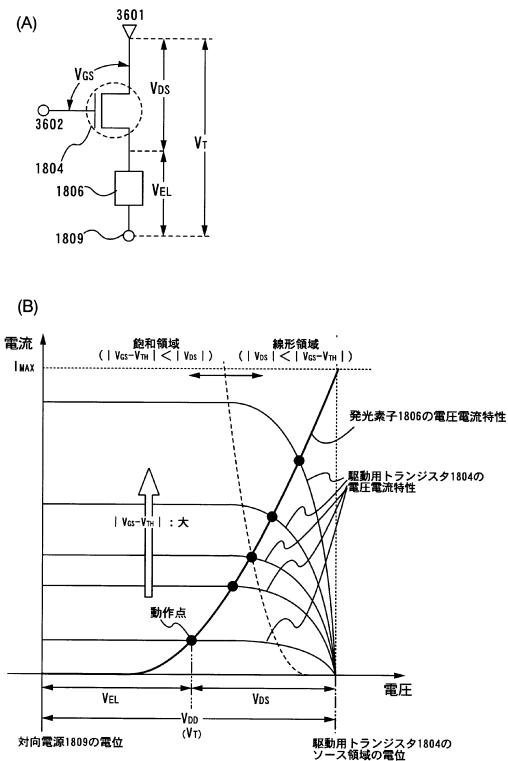

続いて、駆動用トランジスタ1804と発光素子1806の電圧電流特性について、図11～図13を用いて説明する。図11(A)は、図14に示した画素において、駆動用トランジスタ1804および発光素子1806の構成部分のみを示す。図11(B)は、図11(A)で示した駆動用トランジスタ1804および発光素子1806の電圧電流特性を示す。なお図11(B)に示す駆動用トランジスタ1804の電圧電流特性のグラフは、ソース領域とドレイン領域の間の電圧である $V_{DS}$ に対する、駆動用トランジスタ1804のドレイン領域に流れる電流の大きさを示す。図12は、駆動用トランジスタ1804のソース領域とゲート電極の間の電圧である $V_{GS}$ の値が異なる複数のグラフを示す。

30

## 【0020】

図11(A)に示したように、発光素子1806の画素電極と対向電極の間にかかる電圧を $V_{EL}$ 、電源供給線に接続される端子3601と発光素子1806の対向電極の間にかかる電圧を $V_T$ とする。なお $V_T$ は電源供給線( $V_1$ ～ $V_x$ )の電位によってその値が固定される。また駆動用トランジスタ1804のソース領域・ドレイン領域間の電圧を $V_{DS}$ 、駆動用トランジスタ1804のゲート電極に接続される配線3602とソース領域との間の電圧、つまり駆動用トランジスタ1804のゲート電極とソース領域の間の電圧を $V_{GS}$ とする。

40

## 【0021】

駆動用トランジスタ1804と発光素子1806とは直列に接続されている。よって、両素子(駆動用トランジスタ1804と発光素子1806)を流れる電流量は同じである。従って、図11(A)に示した駆動用トランジスタ1804と発光素子1806とは、両素子の電圧電流特性を示すグラフの交点(動作点)において駆動する。図11(B)において、 $V_{EL}$ は、対向電極1809の電位と動作点での電位との間の電圧に相当する。 $V_{DS}$ は、駆動用トランジスタ1804の端子3601での電位と動作点での電位との間の電圧に相当する。つまり、 $V_T$ は、 $V_{EL}$ と $V_{DS}$ の和に等

50

しい。

#### 【0022】

ここで、 $V_{GS}$ を変化させた場合について考える。図11(B)から分かるように、駆動用トランジスタ1804の $|V_{GS} - V_{TH}|$ が大きくなるにつれて、言い換えると $|V_{GS}|$ が大きくなるにつれて、駆動用トランジスタ1804に流れる電流量が大きくなる。なお、 $V_{TH}$ は駆動用トランジスタ1804のしきい値電圧である。よって図11(B)から分かるように、 $|V_{GS}|$ が大きくなると、動作点において発光素子1806を流れる電流量も当然大きくなる。発光素子1806の輝度は、発光素子1806を流れる電流量に比例して高くなる。

#### 【0023】

$|V_{GS}|$ が大きくなることによって発光素子1806を流れる電流量が大きくなると、電流量に応じて $V_{EL}$ の値も大きくなる。そして $V_T$ の大きさは電源供給線( $V_1 \sim V_x$ )の電位によって定まっているので、 $V_{EL}$ が大きくなると、その分 $V_{DS}$ が小さくなる。

#### 【0024】

また図11(B)に示したように、駆動用トランジスタ1804の電圧電流特性は、 $V_{GS}$ と $V_{DS}$ の値によって2つの領域に分けられる。 $|V_{GS} - V_{TH}| < |V_{DS}|$ である領域が飽和領域、 $|V_{GS} - V_{TH}| > |V_{DS}|$ である領域が線形領域である。

#### 【0025】

飽和領域においては以下の式(1)が成り立つ。なお $I_{DS}$ は駆動用トランジスタ1804のチャネル形成領域を流れる電流量である。また $= \mu C_0 W / L$ であり、 $\mu$ は駆動用トランジスタ1804の移動度、 $C_0$ は単位面積あたりのゲート容量、 $W / L$ はチャネル形成領域のチャネル幅 $W$ とチャネル長 $L$ の比である。

#### 【0026】

#### 【数1】

$$I_{DS} = \beta (V_{GS} - V_{TH})^2 \dots (1)$$

#### 【0027】

また線形領域においては以下の式(2)が成り立つ。

#### 【0028】

#### 【数2】

$$I_{DS} = \beta \{ (V_{GS} - V_{TH}) V_{DS} - V_{DS}^2 \} \dots (2)$$

#### 【0029】

式(1)からわかるように、飽和領域において電流量は $V_{DS}$ によってほとんど変化せず、 $V_{GS}$ のみによって電流量が定まる。

#### 【0030】

また、式(2)からわかるように、線形領域においては、 $V_{DS}$ と $V_{GS}$ とにより電流量が定まる。 $|V_{GS}|$ を大きくしていくと、駆動用トランジスタ1804は線形領域で動作するようになる。そして、 $V_{EL}$ も徐々に大きくなっていく。よって、 $V_{EL}$ が大きくなつた分だけ、 $V_{DS}$ が小さくなっていく。線形領域においては、 $V_{DS}$ が小さくなると電流量も小さくなる。そのため、 $|V_{GS}|$ を大きくしていくと、電流量は増加しにくくなってくる。 $|V_{GS}| =$  になった時、電流量 =  $I_{MAX}$ となる。つまり、 $|V_{GS}|$ をいくら大きくしても、 $I_{MAX}$ 以上の電流は流れない。ここで、 $I_{MAX}$ は、 $V_{EL} = V_T$ の時に、発光素子1806を流れる電流量である。

#### 【0031】

このように $|V_{GS}|$ の大きさを制御することによって、動作点を飽和領域にしたり、線形領域にしたりすることができます。

#### 【0032】

ところで、全ての駆動用トランジスタ1804の特性は理想的には全て同じであることが望ましいが、実際には個々の駆動用トランジスタ1804でしきい値 $V_{TH}$ と移動度 $\mu$ と

10

20

30

40

50

が異なっていることが多い。そして個々の駆動用トランジスタ 1804 のしきい値  $V_{TH}$  と移動度  $\mu$  とが互いに異なると、式(1)及び式(2)からわかるように、 $V_{GS}$  の値が同じでも駆動用トランジスタ 1804 のチャネル形成領域を流れる電流量が異なってしまう。

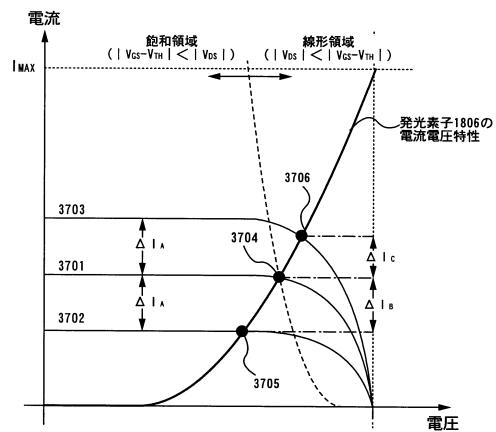

#### 【0033】

図 12 にしきい値  $V_{TH}$  と移動度  $\mu$  がずれた駆動用トランジスタ 1804 の電流電圧特性を示す。実線 3701 が理想の電流電圧特性のグラフであり、3702、3703 がそれぞれしきい値  $V_{TH}$  と移動度  $\mu$  とが理想とする値と異なってしまった場合の駆動用トランジスタ 1804 の電流電圧特性である。

#### 【0034】

電流電圧特性のグラフ 3702、3703 は飽和領域においては同じ電流量  $I_1$  だけ、理想の特性を有する電流電圧特性のグラフ 3701 からずれていて、電流電圧特性のグラフ 3702 の動作点 3705 は飽和領域にあり、電流電圧特性のグラフ 3703 の動作点 3706 は線形領域にあったとする。その場合、理想の特性を有する電流電圧特性のグラフ 3701 の動作点 3704 における電流量と、動作点 3705 及び動作点 3706 における電流量のずれをそれぞれ  $I_2$ 、 $I_3$  とすると、飽和領域における動作点 3705 におけるずれ  $I_2$  よりも線形領域における動作点 3706 におけるずれ  $I_3$  の方が小さくなっている。

#### 【0035】

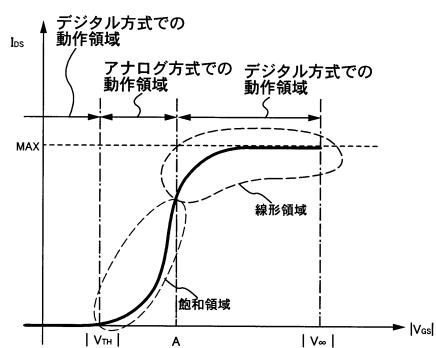

以上の動作分析のまとめとして、駆動用トランジスタ 1804 のゲート電圧  $|V_{GS}|$  に対する電流量のグラフを図 13 に示す。 $|V_{GS}|$  を大きくしていくと、駆動用トランジスタ 1804 が導通状態となり、電流が流れ始める。そして、さらに  $|V_{GS}|$  を大きくしていくと、 $|V_{GS}|$  が  $|V_{GS} - V_{TH}| = |V_{DS}|$  を満たすような値（ここでは仮に A とする）となり、飽和領域から線形領域になる。

さらに  $|V_{GS}|$  を大きくしていくと、電流量が大きくなり、遂には、電流量が飽和してくる。その時  $|V_{GS}| = A$  となる。

#### 【0036】

図 13 から分かる通り、 $|V_{GS}| < |V_{TH}|$  の領域では、電流がほとんど流れない。 $|V_{TH}| < |V_{GS}| < A$  の領域は飽和領域とよばれる領域であり、 $|V_{GS}|$  によって電流量が変化する。これは、飽和領域において、発光素子 1806 に印加される電圧が少しでも変化すると、それに対して発光素子 1806 を流れる電流が指数関数的に大きく変化するということである。そして、発光素子 1806 の輝度は、発光素子 1806 に流れる電流にほぼ正比例して大きくなる。つまり、 $|V_{GS}|$  の値に応じて発光素子に流れる電流を制御することにより、輝度を制御して階調を得る方式であるアナログ方式は、主に飽和領域で動作される。

#### 【0037】

一方、図 13において、 $A < |V_{GS}|$  の領域は線形領域であり、発光素子に流れる電流量は  $|V_{GS}|$  及び  $|V_{DS}|$  よって電流量が変化する。線形領域においては、発光素子 1806 に印加される電圧の大きさを変化させても、発光素子 1806 を流れる電流量は大きく変化しない。デジタル方式は、発光素子がオン状態（その輝度がほぼ 100% である状態）、又はオフ状態（その輝度がほぼ 0% である状態）の 2 つの状態のみによって駆動されるが、発光素子をオン状態にするには、 $A < |V_{GS}|$  で動作させると、いつでも電流値は  $I_{MAX}$  に近くなるため、その輝度はほぼ 100% の状態となる。また発光素子をオフ状態にするには、 $|V_{TH}| < |V_{GS}|$  で動作させると、電流値はほぼゼロとなり、発光素子の輝度はほぼ 0% となる。つまり、デジタル方式で駆動させる発光装置は、主に  $|V_{TH}| < |V_{GS}|$ 、 $A < |V_{GS}|$  の領域で動作される。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0038】

10

20

30

40

50

アナログ方式で駆動させた発光装置において、スイッチング用トランジスタがオンになると、画素に入力されたアナログのビデオ信号は、駆動用トランジスタのゲート電圧となる。このとき、駆動用トランジスタのゲート電極に入力されるアナログのビデオ信号の電圧に対応して、ドレイン領域の電位が定まり、所定のドレイン電流が発光素子に流れ、その電流量に対応した発光量（輝度）で前記発光素子が発光する。以上のように、ビデオ信号によって発光素子の発光量が制御され、その発光量の制御によって階調表示がなされる。

#### 【0039】

しかし、上記アナログ方式は駆動用トランジスタの特性バラツキに非常に弱いという欠点がある。仮に各画素の駆動用トランジスタに等しいゲート電圧がかかったとしても、駆動用トランジスタに特性バラツキが生じていれば、同じドレイン電流を供給することはできない。つまり、僅かな駆動用トランジスタの特性バラツキによって、同じ電圧のビデオ信号を入力しても発光素子の発光量が大きく異なってしまう。

#### 【0040】

このように、アナログ方式は駆動用トランジスタの特性バラツキに対して敏感であり、その点が従来のアクティブ型の発光装置の階調表示における障害となっていた。

#### 【0041】

また駆動用トランジスタの特性バラツキに対処するために、デジタル方式で発光装置を駆動させると、発光素子の有機化合物層が劣化したときに、有機化合物層に流れる電流量が変化してしまう。

#### 【0042】

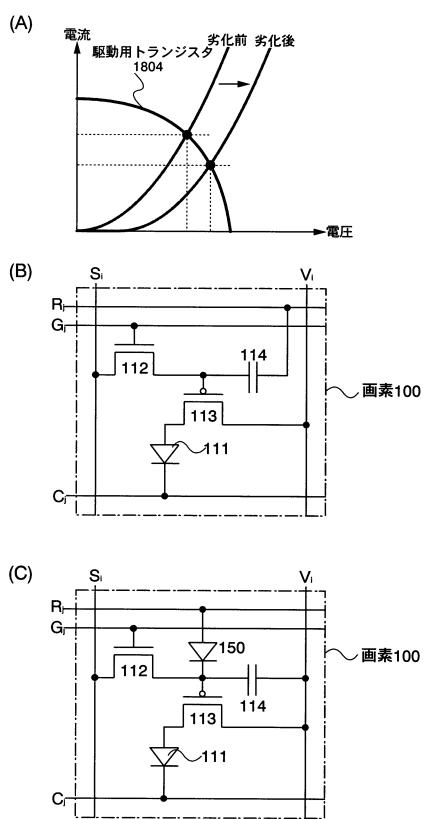

これは、発光素子が経時変化により劣化する性質を有することに起因する。図18(A)には、発光素子の劣化前と劣化後の電圧電流特性のグラフを示す。上述したように、デジタル方式では線形領域で動作する。従って、図18(A)に示すように、発光素子が劣化すると、その電圧電流特性のグラフが変化するため、その動作点がずれてしまう。そうすると、発光素子の両電極間に流れる電流量は変化してしまう。

#### 【0043】

本発明は上記問題点を鑑みてなされたものであり、アナログ方式で駆動させた発光装置において、トランジスタの特性バラツキによる影響を防止し、鮮明な多階調の表示が可能な発光装置及びその駆動方法を提供することを課題とする。また本発明は、前記発光装置を表示用の装置として具備した電子機器を提供することを課題とする。

#### 【0044】

さらに本発明は、経時変化により発光素子の両電極間に流れる電流量の変化を抑制し、鮮明な多階調表示が可能な発光装置及びその駆動方法を提供することを課題とする。また本発明は、前記発光装置を表示用の装置として具備した電子機器を提供することを課題とする。

#### 【課題を解決するための手段】

#### 【0045】

本発明は、上述の実情を鑑み、画素に設けられた駆動用トランジスタの特性を特定し、その結果に基づいて画素に入力するビデオ信号を補正することにより、駆動用トランジスタの特性バラツキによる影響を防止した発光装置およびその駆動方法を提供する。

#### 【0046】

また本発明は、発光素子の発光量（輝度）が、発光素子に流れる電流量に制御されることを利用する。つまり発光素子に所望の電流量が流れるようにすれば、発光素子により所望の発光量を得ることが出来る。そのため、各画素の駆動用トランジスタの特性に応じたビデオ信号を各画素に入力し、発光素子に所望の電流量が流れるようにする。そうすれば駆動用トランジスタの特性バラツキに影響されることなく、発光素子により所望の発光を得ることが出来る。

#### 【0047】

本発明の基幹である駆動用トランジスタの特性を特定する方法について以下に説明する

10

20

30

40

50

。まず、発光素子に電流を供給している配線上に電流計を接続して、該発光素子に流れる電流値を測定する。例えば、電源供給線や対向電源線などの発光素子に電流を供給している配線上に電流計を接続し、該発光素子に流れる電流値を測定する。このとき、ソース信号線駆動回路からある特定の画素（好ましくは一画素、複数の画素でもよい）のみにビデオ信号が入力されるようにして、それ以外の画素の発光素子には電流が流れないようにする。そうすると電流計によって、ある特定の画素のみに流れる電流値を測定することが出来る。また大きさ（電圧値）の異なるビデオ信号を入力すれば、画素ごとに大きさ（電圧値）の異なるビデオ信号に対応した複数の電流値を測定することが出来る。

## 【0048】

本発明は、ビデオ信号を  $P$  ( $P_1, P_2, \dots, P_n$ ,  $n$  は少なくとも 2 以上の自然数) とする。前記ビデオ信号  $P$  ( $P_1, P_2, \dots, P_n$ ) に対応した電流値  $Q$  ( $Q_1, Q_2, \dots, Q_n$ ) は、表示パネルの全ての画素が非点灯時の電流値  $I_0$  と表示パネルの画素が 1 つだけ点灯しているときの電流値  $I_1, I_2, \dots, I_n$  の差を計算することにより得られる。 $P$  と  $Q$  を画素ごとに測定したら、補間法を用いて画素の特性を求める。補間法とは、関数の二つ以上の点における関数値を用いて、関数値の間の点の近似値を求める計算法、或いはその間の点における関数値を与えて（補間して）関数を拡張する方法である。その近似値を与える式は、補間式とよばれ、式(3)に示す。

## 【0049】

## 【数3】

$$Q = F(P) \dots \quad (3)$$

## 【0050】

画素ごとに測定されたビデオ信号  $P$  ( $P_1, P_2, \dots, P_n$ ) と、該ビデオ信号に対応した電流値  $Q$  ( $Q_1, Q_2, \dots, Q_n$ ) の値を式(3)に代入すれば補間関数  $F$  が求められる。そして求められた補間関数  $F$  は、発光装置に設けられた半導体メモリや磁気メモリなどの記憶媒体に記憶される。

## 【0051】

そして発光装置に画像を表示するときには、記憶媒体に記憶された補間関数  $F$  を用いて、各画素の駆動用トランジスタの特性に応じたビデオ信号 ( $P$ ) を計算して求める。そして求められたビデオ信号 ( $P$ ) を各画素に入力すれば、発光素子に所望の電流量を流すことが出来るので、所望の輝度を得ることができる。

## 【0052】

なお本発明における発光装置とは、発光素子を有する画素部及び駆動回路を基板とカバー材との間に封入した表示パネル（発光パネル）、前記表示パネルに I C 等を実装した発光モジュール、表示装置として用いられる発光ディスプレイなどを範疇に含む。つまり発光装置は、発光パネル、発光モジュール及び発光ディスプレイなどの総称に相当する。なお本発明の必須の構成要素に発光素子は含まれないが、該発光素子を含まない場合においてもここでは発光装置と称する。

## 【0053】

本発明は、発光素子を含む画素が設けられた表示パネルを有する発光装置であって、前記画素の電流値を測定する電流測定手段、前記電流測定手段の出力を用いて前記画素に対応した補間関数を計算する計算手段、前記補間関数を記憶する記憶手段、及び前記記憶手段に記憶された前記補間関数を用いてビデオ信号を補正する信号補正手段を有することを特徴とする。

## 【0054】

前記電流測定手段は、発光素子の両電極間に流れる電流値を測定する手段を有するものであり、例えば電流計や、抵抗素子及び容量素子で構成され抵抗分割を利用して測定を行う回路などに相当する。前記計算手段及び前記信号補正手段は、計算を行う手段を有するものであり、例えばマイクロコンピュータや C P U などに相当する。前記記憶手段は、半導体メモリや磁気メモリなどの公知の記憶媒体に相当する。また、画素が非点灯の状態と

10

20

30

40

50

は、該画素が有する発光素子が非発光の状態、“黒”の画像信号が入力された画素の状態に相当する。画素が点灯の状態とは、該画素が有する発光素子が発光の状態、“白”の画像信号が入力された画素の状態に相当する。

#### 【0055】

本発明は、表示パネルを有する発光装置の駆動方法であって、前記表示パネルの全ての画素が非点灯の状態における電流値  $I_0$  を測定し、前記表示パネルの各画素にビデオ信号  $P_1, P_2, \dots, P_n$  ( $n$  は自然数) を入力したときの電流値  $I_1, I_2, \dots, I_n$  を測定し、前記電流値  $I_0$  と前記電流値  $I_n$  の差  $Q_1, Q_2, \dots, Q_n$  及び前記ビデオ信号  $P_1, P_2, \dots, P_n$  及び補間式  $Q = F(P)$  を用いて補間関数  $F$  を計算し、前記補間関数  $F$  を用いて前記表示パネルの各画素に入力するビデオ信号を補正することを特徴とする。10

#### 【0056】

本発明における前記画素の代表的な構成としては、前記発光素子の両電極間に流れる電流を制御する第1半導体素子及び前記画素に対するビデオ信号の入力を制御する第2半導体素子、並びに前記ビデオ信号を保持する容量素子とを有する構成が挙げられる。なお、前記半導体素子とは、トランジスタなどのスイッチング機能を有する素子に相当する。容量素子とは、電荷を保持する機能を有し、構成する材料は特に限定されない。

#### 【0057】

上記の構成を有する本発明はアナログ方式で駆動させた発光装置において、トランジスタの特性バラツキによる影響を防止し、鮮明な多階調の表示が可能な発光装置及びその駆動方法を提供することができる。さらに本発明は、経時変化により発光素子の両電極間に流れる電流量の変化を抑制し、鮮明な多階調表示が可能な発光装置及びその駆動方法を提供することが出来る。20

#### 【発明の効果】

#### 【0058】

本発明は、画素の構成を変更することなく、各画素の駆動用トランジスタの特性に応じたビデオ信号を計算して求める。そして求められたビデオ信号を各画素に入力すれば、発光素子に所望の電流量を流すことが出来るので、所望の発光を得ることができる。その結果、発光素子を制御するトランジスタの特性バラツキの影響を防止した発光装置及びその駆動方法を提供することが出来る。30

#### 【0059】

また上記の構成を有する本発明は、アナログ方式で駆動させた発光装置において、トランジスタの特性バラツキによる影響を防止し、鮮明な多階調の表示が可能な発光装置及びその駆動方法を提供することができる。さらに本発明は、経時変化により発光素子の両電極間に流れる電流量の変化を抑制し、鮮明な多階調表示が可能な発光装置及びその駆動方法を提供することが出来る。

#### 【図面の簡単な説明】

#### 【0060】

【図1】本発明の発光装置の回路図。

【図2】本発明の発光装置の回路図。

【図3】本発明の発光装置の駆動方法を説明する図。

【図4】本発明の発光装置に入力される信号のタイミングチャートを示す図。

【図5】ビデオ信号と電流値との関係を示す図。

【図6】本発明の発光装置の画素の回路図を示す図。

【図7】本発明の発光装置の断面構造(下面出射)を示す図。

【図8】本発明の発光装置の外観を示す図。

【図9】本発明の発光装置の外観を示す図。

【図10】本発明の発光装置が具備された電子機器の一例を示す図。

【図11】発光素子と駆動用トランジスタの接続の構成を示す図と、発光素子と駆動用トランジスタの電圧電流特性を示す図。50

【図12】発光素子と駆動用トランジスタの電圧電流特性を示す図。

【図13】駆動用トランジスタのゲート電圧とドレイン電流の関係を示す図。

【図14】発光装置の画素部の回路図を示す図。

【図15】発光装置に入力される信号のタイミングチャートを示す図。

【図16】ビデオ信号と電流値との関係を示す図。

【図17】本発明の発光装置の断面構造(上面出射)を示す図。

【図18】発光素子と駆動用トランジスタの電圧電流特性を示す図と画素の回路図。

【発明を実施するための形態】

【0061】

(実施の形態)

10

本発明の実施の形態について、図1～図5を用いて説明する。

【0062】

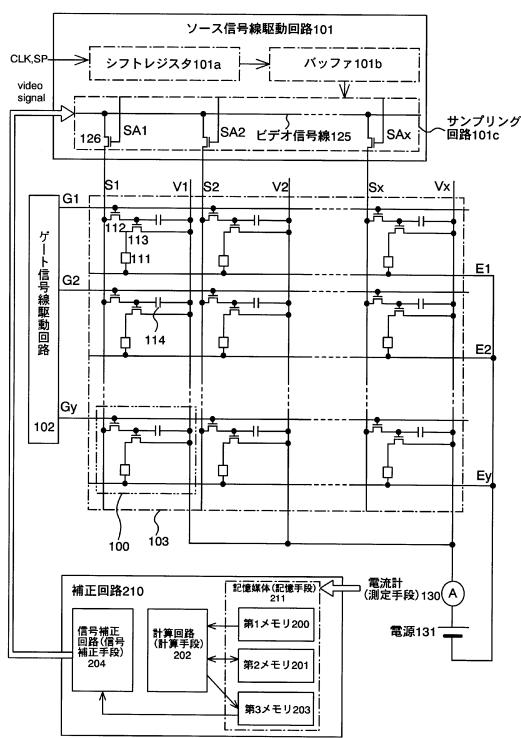

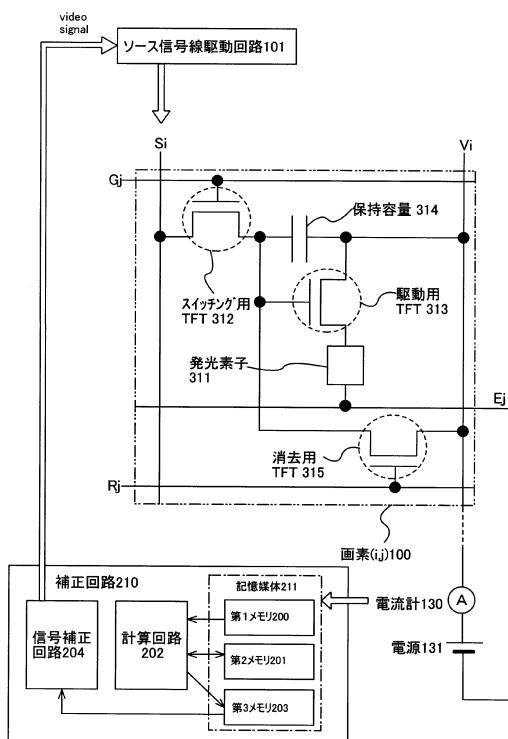

図1に発光装置の回路図の一例を示す。図1において、発光装置は、画素部103、画素部103の周辺に配置されたソース信号線駆動回路101及びゲート信号線駆動回路102を有している。なお、図1において発光装置はソース信号線駆動回路101と、ゲート信号線駆動回路102とをそれぞれ1つずつ有しているが、本発明はこれに限定されない。画素100の構成に応じて、ソース信号線駆動回路101とゲート信号線駆動回路102の数は任意に定めることができる。

【0063】

またソース信号線駆動回路101は、シフトレジスタ101a、バッファ101b、サンプリング回路101cを有している。しかしながら本発明はこれに限定されず、保持回路などを有していてもよい。

20

【0064】

シフトレジスタ101aにはクロック信号(CLK)及びスタートパルス(SP)が入力される。シフトレジスタ101aは、クロック信号(CLK)及びスタートパルス(SP)に基づき、タイミング信号を順に発生させ、バッファ101bを介してサンプリング回路101cに順次入力される。

【0065】

シフトレジスタ101aから供給されるタイミング信号は、バッファ101bによって緩衝増幅される。タイミング信号が入力される配線には、多くの回路あるいは素子が接続されているために負荷容量が大きくなってしまう。そのためバッファ101bは、該負荷容量が大きいために生ずるタイミング信号の立ち上がりまたは立ち下がりの鈍りを防ぐために設けられている。

30

【0066】

サンプリング回路101cは、バッファ101bから入力されたタイミング信号に基づいて、ビデオ信号を順に画素100に出力していく。サンプリング回路101cは、ビデオ信号線125とサンプリング線(SA1～SAx)とを有している。なお本発明はこの構成に限定されず、アナログスイッチなどの半導体素子を有していてもよい。

【0067】

画素部103は、ソース信号線(S1～Sx)と、ゲート信号線(G1～Gy)と、電源供給線(V1～Vx)と、対向電源線(E1～Ey)が設けられている。また画素部103には、複数の画素100がマトリクス状に設けられている。

40

【0068】

電源供給線(V1～Vx)は、電流計130を介して電源131に接続されている。なお電流計130と電源131は、画素部103が形成されている基板とは異なる基板上に形成され、コネクター等を介して画素部103と接続されていてもよいし、作製が可能であれば画素部103と同じ基板上に形成してもよい。

なお電流計130と電源131の数は特に限定されず、任意に定めることができる。また電流計130は、発光素子111に電流を供給する配線上に設ければよく、例えば対向電源線(E1～Ey)に電流計130を接続してもよい。つまり、電流計130を設ける場

50

所は特に限定されない。電流計 130 は、測定手段に相当する。

**【0069】**

そして電流計 130 により測定された電流値は、データとして補正回路 210 に送られる。補正回路 210 は、記憶媒体（記憶手段）211、計算回路（計算手段）202 及び信号補正回路（信号補正手段）204 を有している。なお補正回路 210 の構成は、図 1 に示す構成に限定されず、增幅回路、変換回路などを設けてもよい。また必要に応じて、記憶媒体 211 のみを設けてもよく、前記補正回路 210 の構成は、任意に定めることができる。

**【0070】**

記憶媒体 211 は、第 1 メモリ 200、第 2 メモリ 201 及び第 3 メモリ 203 を有している。10 しかし本発明はこれに限定されず、メモリの数は設計者が自由に設計することが出来る。また記憶媒体 211 としては、ROM、RAM、フラッシュメモリ、磁気テープなどの公知の記憶媒体を用いることが出来る。しかし画素部が設けられている基板上などに一体化して記憶媒体 211 を設ける場合には、半導体メモリを用いることが好ましく、特に ROM を用いることが好ましい。またコンピュータの表示装置として、本発明の発光装置を用いる場合には、該コンピュータ内に記憶媒体 211 を設けてもよい。

**【0071】**

計算回路 202 は、計算を行う手段を有する。より詳しくは、画素 100 にビデオ信号 P1、P2、…、Pn が入力されたときの電流値 I1、I2、…、In から、画素部 103 が非発光の状態における電流値 I0 を減算し、電流値 Q1、Q2、…、Qn を算出する手段を有する。20 また上述した式（3）の補間関数の計算を行う手段を有する。なお計算回路 202 としては、公知の計算回路、マイクロコンピュータなどを用いることが出来る。コンピュータの表示装置として、本発明の発光装置を用いる場合には、該コンピュータ内に計算回路 202 を設けてもよい。

**【0072】**

信号補正回路 204 は、ビデオ信号を補正する手段を有する。より詳しくは記憶媒体 211 に記憶されている画素 100 の補間関数 F と、上述した式（3）から、画素 100 に入力されるビデオ信号を補正する手段を有する。30 なお信号補正回路 204 としては、公知の信号補正回路、マイクロコンピュータなどを用いることが出来る。コンピュータの表示装置として、本発明の発光装置を用いる場合には、該コンピュータ内に信号補正回路 204 を設けてもよい。

**【0073】**

ソース信号線（S1～Sx）は、サンプリング用トランジスタ 126 を介してビデオ信号線 125 に接続されている。サンプリング用トランジスタ 126 のソース領域とドレイン領域は、一方はソース信号線 S（S1～Sx のいずれか一つ）に接続され、もう一方はビデオ信号線 125 に接続されている。そしてサンプリング用トランジスタ 126 のゲート電極は、サンプリング線 SA（SA1～SAx のいずれか一つ）に接続されている。

**【0074】**

次いで、i 列目 j 行目に設けられた画素 100 の拡大図を図 2 に示す。画素（i, j）において、111 は発光素子、112 はスイッチング用トランジスタ、113 は駆動用トランジスタ、114 はコンデンサである。40

**【0075】**

スイッチング用トランジスタ 112 のゲート電極は、ゲート信号線（Gi）に接続されている。スイッチング用トランジスタ 112 のソース領域とドレイン領域は、一方はソース信号線（Si）、もう一方は駆動用トランジスタ 113 のゲート電極に接続されている。スイッチング用トランジスタ 112 は、画素 100 に信号を入力するときのスイッチング素子として機能するトランジスタである。

なおスイッチング用トランジスタ 112 が接続しているソース信号線（Si）は、図 1 に示すようにサンプリング用トランジスタ 126 を介してビデオ信号線 125 に接続されているが、図 2 では図示を省略している。50

## 【0076】

コンデンサ114は、スイッチング用トランジスタ112が非選択状態（オフ状態）にあるときに、駆動用トランジスタ113のゲート電圧を保持するために設けられている。なお本実施の形態では、コンデンサ114を設ける構成にしたが、本発明はこれに限定されず、コンデンサ114を設けない構成にしてもよい。

## 【0077】

駆動用トランジスタ113のソース領域は、電源供給線（Vi）に接続され、ドレイン領域は発光素子111に接続される。電源供給線（Vi）は、電流計130を介して電源131に接続されており、常に一定の電源電位が与えられている。また電源供給線Viはコンデンサ114に接続されている。駆動用トランジスタ113は、発光素子111に供給する電流を制御するための素子（電流制御素子）として機能するトランジスタである。10

## 【0078】

発光素子111は、陽極及び陰極、並びに前記陽極と前記陰極の間に設けられた有機化合物層とからなる。陽極が駆動用トランジスタ113のドレイン領域と接続している場合、陽極が画素電極、陰極が対向電極となる。逆に陰極が駆動用トランジスタ113のドレイン領域と接続している場合、陰極が画素電極、陽極が対向電極となる。

## 【0079】

なお、発光素子とは、一対の電極（陽極と陰極）間に有機化合物層が挟まれた構造とする。有機化合物層は、公知の発光材料を用いて作製することが出来る。20

また有機化合物層には、単層構造と積層構造の二つの構造があるが、どちらの構造を用いてもよい。有機化合物層におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光（蛍光）と、三重項励起状態から基底状態に戻る際の発光（リン光）とがあるが、どちらの発光を用いてもよい。

## 【0080】

発光素子の対向電極は、対向電源121に接続されている。なお、対向電源121の電位を対向電位と呼ぶ。画素電極の電位と対向電極の電位の差が駆動電圧であり、当該駆動電圧が有機化合物層にかかる。

## 【0081】

次いで、図1、図2で示した本発明の発光装置において、画素100に設けられた駆動用トランジスタ113の特性を特定し、その結果に基づいて画素100に入力するビデオ信号を補正する方法について、図3(A)を用いて説明する。30

なお説明を分かりやすくするために各段階をステップ1～ステップ5とする。また図3(B)には、補正回路210を示しているので、図3(A)、(B)をそれぞれ参照するとよい。

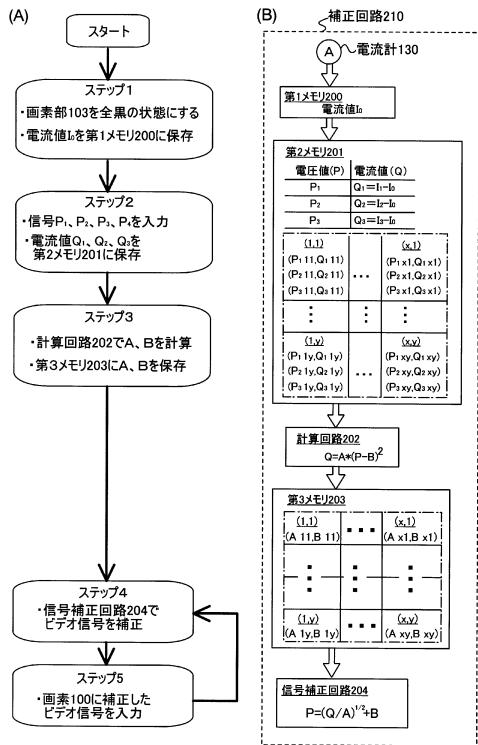

## 【0082】

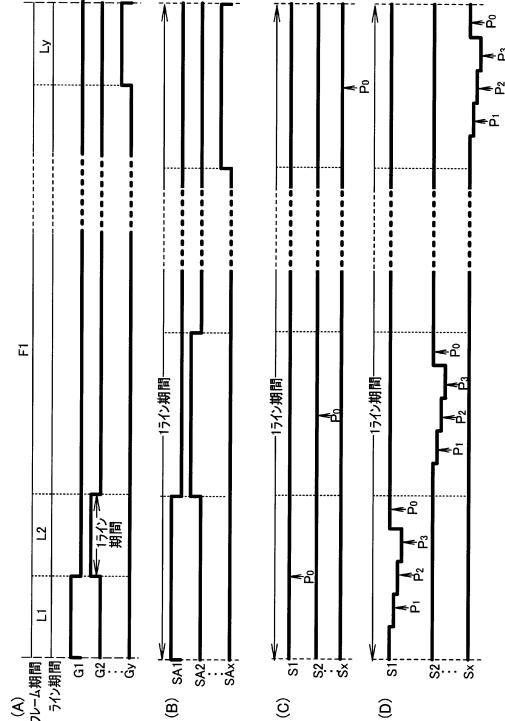

図4は発光装置に設けられた駆動回路（ソース信号線駆動回路101、ゲート信号線駆動回路102）から出力される信号のタイミングチャートを示している。画素部103には、ゲート信号線がy本設けられているので、1フレーム期間中にy個のライン期間（L1～Ly）が設けられている。

## 【0083】

図4(A)は、1ライン期間（L）において、1本のゲート信号線G(G1～Gyのいずれか一つ)が選択され、y本のゲート信号線(G1～Gy)が選択されると1フレーム期間が経過する様子を示している。図4(B)は、x本のサンプリング線SA(SA1～SAxのいずれか一つ)が順に選択され、全てのサンプリング線(SA1～SAx)が選択されると1ライン期間が経過する様子を示している。図4(C)は、ステップ1においてソース信号線(S1～Sx)にビデオ信号P0が入力される様子を示している。図4(D)は、ステップ2においてソース信号線(S1～Sx)にビデオ信号P1、P2、P3、P0が入力される様子を示している。40

## 【0084】

まずステップ1において、画素部103を全黒の状態にする。全黒の状態とは、全ての50

発光素子 111 を非発光の状態、全ての画素を非点灯の状態にするということである。図 4 (C) には、ステップ 1においてソース信号線 (S1 ~ Sx) にビデオ信号 P0 が入力される様子が示されている。なお図 4 (C) には、1 ライン期間において、ソース信号線 (S1 ~ Sx) にビデオ信号 P0 が入力される様子のみが図示されているが、実際は 1 フレーム期間 (F) に設けられた全てのライン期間 (L1 ~ Ly) において行われる。そして 1 フレーム期間において、全ての画素 100 に同じビデオ信号 P0 が入力されると、画素部 103 に設けられた全ての発光素子 111 は非発光の状態（全黒の状態）になる。

#### 【0085】

このような状態になったら、電流計 130 を用いて電源供給線 (V1 ~ Vx) に流れる電流値 I0 を測定する。このとき測定される電流値 I0 は、発光素子 111 が有する陽極と陰極間の一部がショートしていたり、画素 100 の一部がショートしていたり、画素部 103 に接続された FPC が正確に接続されていなかったりする場合に流れてしまった電流値に相当する。そして測定された電流値 I0 は、補正回路 210 に設けられた第 1 メモリ 200 に保存され、ステップ 1 が終了する。

#### 【0086】

次いでステップ 2において、画素部 103 に設けられた画素 100 にそれぞれ異なるビデオ信号 P1、P2、P3、P0 を入力する。

#### 【0087】

本実施の形態では、図 4 (D) に示すように、階段状に変化させた 4 つのビデオ信号 P1、P2、P3、P0 をソース信号線 (S1 ~ Sx) に入力している。

つまり 1 ライン期間 (L) で、1 つの画素 100 に 4 つのビデオ信号 P1、P2、P3、P0 を入力し、1 フレーム期間 (F) で画素部 103 に設けられた全ての画素 100 に 4 つのビデオ信号 P1、P2、P3、P0 を入力する。

#### 【0088】

そして、3 つのビデオ信号 P1、P2、P3 に対応した、駆動用トランジスタ 113 に流れた電流、つまり電源供給線 (V1 ~ Vx) に流れた電流値を電流計 130 により測定する。

#### 【0089】

なおここでは、1 ライン期間 (L) において、1 つの画素に階段状に変化させた 4 つのビデオ信号 P1、P2、P3、P0 を入力したが、本発明はこれに限定されない。例えば、1 ライン期間 (L) にビデオ信号 P1 のみを入力し、次の 1 ライン期間 (L) にビデオ信号 P2 を入力し、また次の 1 ライン期間 (L) にビデオ信号 P3 を入力してもよい。また本実施の形態では、階段状に変化させた 4 つのビデオ信号 P1、P2、P3、P0 を入力したが、本発明は大きさ（電圧値）の異なるビデオ信号を入力して、該大きさ（電圧値）の異なるビデオ信号に対応した電流値を測定すればよい。例えばランプ状（のこぎり刃状）に変化させたビデオ信号を入力して、ある一定の期間ごとに電流計 130 を用いて複数の電流値を測定するようにしてもよい。

#### 【0090】

ここで、1 例として、j 行目のゲート信号線 (Gj) がゲート信号線駆動回路 102 から供給されるゲート信号によって選択される場合について説明する。1 ライン期間 (Lj) には、一つの画素 100 に 4 つのビデオ信号 P1、P2、P3、P0 が入力されるので、ビデオ信号が入力された画素 100（ここでは (1, j) に設けられた画素 100 とする）以外は、全てオフ状態にある。そのため、電流計 130 で測定される電流値は、ある特定の画素（着目している画素）100 の駆動用トランジスタ 113 を流れる電流値とステップ 1 で測定された電流値 I0 を足した値となる。そして、(1, j) に設けられた画素 100 において、P1、P2、P3 の各々のビデオ信号に対応した電流値 I1、I2、I3 を測定して、該電流値 IA、IB、IC を第 2 メモリ 201 に保存する。

#### 【0091】

次いで、画素 (1, j) にビデオ信号 P0 を入力し、画素 100 の発光素子 111 を非発光の状態、画素 (1, j) を非点灯の状態にする。これは、次の画素 (2, j) を測定

10

20

30

40

50

するときに、電流が流れてしまうことを防ぐためである。

**【0092】**

そして次に、(2、j)に設けられた画素100に、4つのビデオ信号P1、P2、P3、P0を入力する。ビデオ信号P1、P2、P3に対応した電流値I1、I2、I3を取得して、第2メモリ201に保存する。

**【0093】**

このようにして上述した動作を繰り返し、j行目に設けられた1列目から×列目までの画素100にビデオ信号の入力が終了する。つまり、全てのソース信号線(S1～Sx)へのビデオ信号の入力が終了すると、1つのライン期間Ljが終了する。

**【0094】**

そして、次のライン期間Lj+1となり、ゲート信号線駆動回路102から供給されるゲート信号によってゲート信号線Gj+1が選択される。そして、全てのソース信号線(S1～Sx)に4つのビデオ信号P1、P2、P3、P0が入力される。

**【0095】**

このようにして上述した動作を繰り返し、全てのゲート信号線(G1～Gy)にゲート信号が入力されると、全てのライン期間(L1～Ly)が終了する。そして全てのライン期間(L1～Ly)が終了すると、1フレーム期間が終了する。

**【0096】**

こうして画素部103に設けられた画素100に入力された3つのビデオ信号P1、P2、P3に対応する電流値I1、I2、I3を測定することが出来る。

そして得られたデータは、第2メモリ201に保存される。

**【0097】**

そして、計算回路202において、画素部103に設けられた画素100ごとに電流値I1、I2、I3から、ステップ1において第1メモリ200に保存された電流値I0との差を求めて、電流値Q1 (= I1 - I0)、Q2 (= I2 - I0)、Q3 (= I3 - I0)を求める。そして電流値Q1、Q2、Q3は第2メモリ201に保存され、ステップ2は終了する。

**【0098】**

なお画素部103にショートしている画素がなく、また画素部103に接続されたFPCなどが正確に接続されている場合には、電流値I0はゼロ、又はほぼゼロである値が測定される場合がある。このような場合には、画素部103に設けられた画素100ごとに電流値I1、I2、I3から、電流値I0を引く動作や電流値I0を測定する動作を削除してもよく、これは任意に設定することが出来る。

**【0099】**

次いでステップ3においては、上述した式(1)を用いて、計算回路202において、各画素の駆動用トランジスタの電流電圧特性(I<sub>DS</sub>-V<sub>GS</sub>特性)を取得する。なお式(1)において、I<sub>DS</sub>=I、V<sub>GS</sub>=P、V<sub>TH</sub>=Bとし、Q=I-I0とすると、以下の式(4)が求められる。

**【0100】**

**【数4】**

$$Q = A * (P - B)^2 \dots \quad (4)$$

**【0101】**

式(4)において、AとBは定数である。定数Aと定数Bは少なくとも2組の(Pn、Qn)のデータがあれば求めることができる。つまり、ステップ2において求めた少なくとも2つの大きさ(電圧値)の異なるビデオ信号(Pn)と、そのビデオ信号(Pn)に対応した少なくとも2つの電流値(Qn)を式(3)

に代入すれば、定数Aと定数Bを求めることが出来る。そして、定数Aと定数Bは第3メモリ203に保存される。

**【0102】**

10

20

30

40

50

第3メモリ203に保存された定数Aと定数Bを用いることで、ある電流値(Qn)を流すために必要なビデオ信号(Pn)の値を求めることができる。その際には、以下の式(5)を用いる。

【0103】

【数5】

$$P = (Q/A)^{1/2} + B = \{ (I - I_0)/A \}^{1/2} + B \dots (5)$$

【0104】

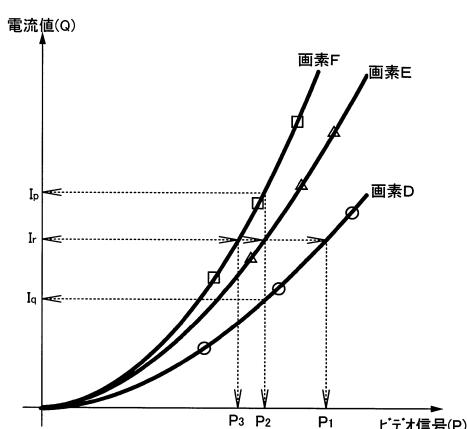

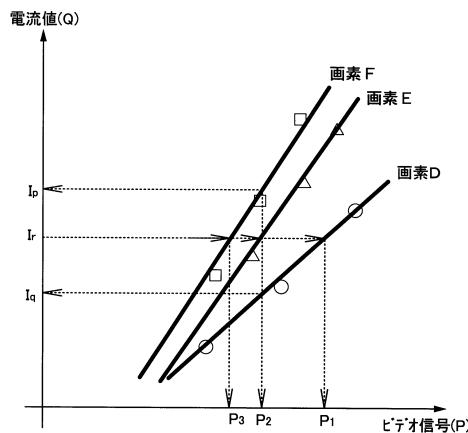

ここで、一例として式(4)、式(5)を用いて、画素D、画素E、画素Fの定数Aと定数Bの値を求め、それをグラフに示したものを図5に示す。図5に示すように、画素D、画素E、画素Fに同じビデオ信号(ここでは一例としてビデオ信号P2とする)を入力した場合、画素DではIqで示す電流が流れ、画素EではIrで示す電流が流れ、画素FではIpで示す電流が流れている。つまり同じビデオ信号(P2)を入力しても、画素D、E、Fに設けられたトランジスタの特性が異なるために、電流値が異なってしまっている。そこで本発明はこのような特性バラツキの影響を抑制するために、上述した式(4)を用いて、画素100の特性に応じたビデオ信号を画素100に入力する。

【0105】

なお図5では、画素D、画素E、画素Fの特性を式(4)、式(5)を用いて2次曲線で示したが、本発明はこれに限定されない。図16には、以下の式(6)を用いて画素D、画素E、画素Fに入力したビデオ信号(P)と、該ビデオ信号(P)に対応した電流値(Q)との関係を直線としたグラフを示す。

【0106】

【数6】

$$Q = a * P + b \dots (6)$$

【0107】

式(6)にステップ2で求めた画素ごとの電圧値(P)と電流値(Q)を代入することで、定数aと定数bを求める。そして、求められた定数aと定数bは、画素100ごとに第3メモリ203に保存されてステップ3は終了する。

【0108】

図16に示すグラフは、図5に示すグラ夫と同じように、画素D、画素E、画素Fに同じビデオ信号(ここでは一例としてビデオ信号P2とする)を入力した場合、画素DではIqで示す電流が流れ、画素EではIrで示す電流が流れ、画素FではIpで示す電流が流れている。つまり同じビデオ信号(P2)を入力しても、画素100に設けられたトランジスタの特性が異なるために、電流値が異なってしまっている。そこで本発明はこのような特性バラツキの影響を抑制するために、上述した式(6)を用いて、画素100の特性に応じたビデオ信号を画素100に入力する。

【0109】

なお、ビデオ信号の電圧値(P)と電流値(Q)との関係を特定する方法としては、図5に示すように2次曲線で示すことにより特定してもよいし、図16に示すように直線で示すことにより特定してもよい。またスプライン曲線(スプライン関数)やベジェ曲線(ベジェ関数)で特定してもよいし、また曲線上にうまく電流値がのらない場合には、最小自乗法を用いて曲線(1次関数)を最適化してもよく、その方法は特に限定されない。

【0110】

続いて、ステップ4において、信号補正回路204において、上述した式(5)(又は式(6))などを用いて各画素100の特性に応じたビデオ信号の値を計算する。そうするとステップ4は終了し、ステップ5において、計算されたビデオ信号を画素100に入力すれば、駆動用トランジスタの特性バラツキの影響を抑制して、発光素子に所望の電流を流すことが可能となり、その結果所望の発光量(輝度)を得ることが出来る。なお画素100ごとに求められた定数Aと定数B(又は定数aと定数b)の値が一旦第3メモリ2

10

20

30

40

50

03に保存されたら、後はステップ4とステップ5を交互に繰り返せばよい。

#### 【0111】

ここで再び図5を参照する。仮に、画素D、画素E、画素Fを同じ輝度で発光させたいときは、同じ電流値 $I_r$ を流すことが必要となる。そのためには、駆動用トランジスタの特性に応じたビデオ信号を入力することが必要であり、図5に示すように、画素Dにはビデオ信号P1を入力し、画素Eにはビデオ信号P2を入力し、画素Fにはビデオ信号P3を入力することが必要となる。そのためには、ステップ4において、各画素の特性に応じたビデオ信号を求め、その求められた信号を各画素に入力することが必須となる。

#### 【0112】

なお電流計130を用いて複数の異なるビデオ信号に対応した複数の電流値を測定する動作（ステップ1～ステップ3の動作）は、実際に画像を表示させる直前、又は直後に行ってもよいし、ある一定の期間ごとに行ってもよい。また記憶手段に所定の情報を記憶させる前に行ってもよい。さらに出荷前のみに行ってもよいが、その場合には計算回路202において計算された補間関数Fを一旦記憶媒体211に記憶させて、該記憶媒体211を画素部103と一体化形成すればよい。そうすれば、後は記憶媒体211に記憶された補間関数Fを参照して、画素の特性に応じたビデオ信号を計算することができるので、電流計130を発光装置に設ける必要がない。

10

#### 【0113】

なお本実施の形態においては、補間関数Fが記憶媒体211に記憶されたら、それをもとに画素100に入力するビデオ信号を計算回路202において随時計算して、その計算したビデオ信号を画素100に入力しているが、本発明はこれに限定されない。

20

#### 【0114】

例えば記憶媒体211に記憶された補間関数Fを基に、表示される画像の階調数に対応したビデオ信号を、あらかじめ画素100ごとに計算回路202において計算しておく、その計算されたビデオ信号を記憶媒体211に記憶させておいてもよい。例えば16階調で画像を表示するとしたら、該16階調分の16個のビデオ信号を画素100ごとにあらかじめ計算しておく。そして計算したビデオ信号は、記憶媒体211に記憶しておく。そうすれば、画素100ごとにある階調を表示するときに入力するビデオ信号の情報が記憶媒体211に記憶されているので、その情報をもとに、画像を表示することが出来る。つまり、計算回路202を発光装置に設けなくても、記憶媒体211に記憶させた情報をもとに画像を表示することが出来る。

30

#### 【0115】

また表示される画像の階調数に対応したビデオ信号を、あらかじめ画素100ごとに計算回路202において計算しておくときには、該ビデオ信号に、ガンマ値でガンマ補正をしたビデオ信号を記憶媒体211に記憶させておいてもよい。

なお用いるガンマ値は、画素部で共通であってもよいし、各画素で異なっていてもよい。そうすると、より鮮明な画像を表示することが出来る。

#### 【実施例1】

#### 【0116】

本発明は、図2とは異なる構成の画素の発光装置にも適用できる。本実施例ではその一例について図6、図18(B)(C)を用いて説明する。

40

#### 【0117】

図6に示す画素(i,j)は、発光素子311、スイッチング用トランジスタ312、駆動用トランジスタ313、消去用トランジスタ315及び保持容量314とを有する。また画素100は、ソース信号線(Si)、電源供給線(Vi)、ゲート信号線(Gj)、消去用ゲート信号線(Rj)に囲まれた領域に配置されている。

#### 【0118】

スイッチング用トランジスタ312のゲート電極は、ゲート信号線(Gj)に接続されている。スイッチング用トランジスタ312のソース領域とドレイン領域は、一方がソース信号線(Si)、もう一方が駆動用トランジスタ313のゲート電極に接続されている

50

。スイッチング用トランジスタ 312 は、画素 100 に信号を入力するときのスイッチング素子として機能するトランジスタである。

#### 【 0119 】

コンデンサ 314 は、スイッチング用トランジスタ 312 が非選択状態（オフ状態）にあるときに、駆動用トランジスタ 313 のゲート電圧を保持するために設けられている。なお本実施の形態では、コンデンサ 314 を設ける構成にしたが、本発明はこれに限定されず、コンデンサ 314 を設けない構成にしてもよい。

#### 【 0120 】

駆動用トランジスタ 313 のソース領域は電源供給線（V<sub>i</sub>）に接続され、ドレイン領域は発光素子 311 に接続される。電源供給線（V<sub>i</sub>）は、電流計 130 を介して電源 131 に接続されており、常に一定の電源電位が与えられている。また電源供給線（V<sub>i</sub>）はコンデンサ 314 に接続されている。駆動用トランジスタ 313 は、発光素子 311 に供給する電流を制御するための素子（電流制御素子）として機能するトランジスタである。

#### 【 0121 】

発光素子 311 は、陽極及び陰極、並びに前記陽極と前記陰極の間に設けられた有機化合物層とからなる。陽極が駆動用トランジスタ 313 のドレイン領域と接続している場合、陽極が画素電極、陰極が対向電極となる。逆に陰極が駆動用トランジスタ 313 のドレイン領域と接続している場合、陰極が画素電極、陽極が対向電極となる。

#### 【 0122 】

消去用トランジスタ 315 のゲート電極は、消去用ゲート信号線（R<sub>j</sub>）に接続されている。消去用トランジスタ 315 のソース領域とドレイン領域は、一方が電源供給線（V<sub>i</sub>）、もう一方が駆動用トランジスタ 313 のゲート電極に接続されている。消去用トランジスタ 315 は、画素 100 に書き込まれた信号を消去（リセット）するための素子として機能するトランジスタである。

#### 【 0123 】

消去用トランジスタ 315 をオン状態にすると、コンデンサ 314 に保持された容量は放電される。そうすると、画素 100 に書き込まれた信号は消去（リセット）されて、発光素子は非発光となる。つまり消去用トランジスタ 315 をオン状態にすることで、画素 100 は強制的に非発光となる。このように消去用トランジスタ 315 を設けることで、画素 100 を強制的に非発光とできることには様々な効果がある。例えば、デジタル方式の場合には、発光素子の点灯時間を任意に設定することができるため、高階調の画像を表示することができる。またアナログ方式の場合には、フレーム期間が切り替わるたびに画素を非発光状態にすることで、残像を残すことなく動画をきれいに表示することが出来る。

#### 【 0124 】

そして電源供給線（V<sub>i</sub>）は電流計 130 を介して電源 131 に接続されている。なお、電流計 130 と電源 131 は、画素部 103 が形成されている基板とは異なる基板上に形成され、コネクター等を介して画素部 103 と接続されていてもよいし、作製が可能であれば画素部 103 と同じ基板上に形成してもよい。

なお電流計 130 と電源 131 の数は特に限定されず、任意に設定することができる。

#### 【 0125 】

そして電流計 130 により測定された電流値は、データとして補正回路 210 に送られる。補正回路 210 は、記憶媒体 211、計算回路 202 及び信号補正回路 204 を有している。なお補正回路 210 の構成は、図 6 に示す構成に限定されず、增幅回路などを設けてもよい。補正回路 210 の構成は、設計者が自由に設計することができる。

#### 【 0126 】

そして画素部（図示せず）には、図 6 に示す画素（i、j）がマトリクス状に設けられている。また画素部には、ソース信号線（S<sub>1</sub>～S<sub>x</sub>）と、ゲート信号線（G<sub>1</sub>～G<sub>y</sub>）と、電源供給線（V<sub>1</sub>～V<sub>x</sub>）と、消去用ゲート信号線（R<sub>1</sub>～R<sub>y</sub>）とが設けられてい

10

20

30

40

50

る。

#### 【0127】

また図18(B)には、図2に示した画素にリセット線Rjを追加して配置した構成の画素を示し、コンデンサ114が電源供給線Viではなく、リセット線Rjに接続されている。この場合、このコンデンサ114は画素(i,j)をリセットする役目を担う。さらに図18(C)には、図2に示した画素にリセット線Rj及びダイオード150を追加した構成の画素を示し、該ダイオードが画素(i,j)をリセットする役目を担う。

#### 【0128】

なお本発明が適用される発光装置の画素の構成とは、発光素子とトランジスタを有する構成である。前記画素において発光素子とトランジスタとの接続関係は特に限定されず、10どのような接続関係でもよく、本実施例で示した画素の構成はその一例である。

#### 【0129】

ここで、図6に示した画素を例に挙げて、その動作について簡単に説明する。

前記画素には、デジタル方式、アナログ方式のいずれの方式も適用することができるが、ここでは時間階調方式と組み合わせたデジタル方式を適用したときの動作について説明する。なお時間階調方式とは、特開2001-343933号公報にて詳しく報告されているように、発光素子の点灯期間を制御することにより、階調表現を行う方式である。具体的には、1フレーム期間を長さの異なる複数のサブフレーム期間に分割し、各期間での発光素子の発光又は非発光を選択することで、1フレーム期間内における点灯期間の長さの差をもって階調を表現する。つまりビデオ信号により点灯期間の長さを制御することで、20階調を表現する。

#### 【0130】

なお、デジタル方式では、すでに述べたように、主に線形領域で動作させるが、飽和領域で動作させてもよい。線形領域で動作させる場合は、有機化合物層が劣化したときに、電流量が変化してしまう。一方、飽和領域で動作させる場合は、駆動用トランジスタの特性バラツキの影響を受けやすい。

#### 【0131】

なお本発明では、各画素に入力するビデオ信号を補正することで、各画素の特性バラツキの影響を抑制する。つまり、アナログ方式が適用された発光装置では、ビデオ信号の補正とは、該ビデオ信号の振幅値の補正に相当する。また、時間階調方式と組み合わせたデジタル方式が適用された発光装置では、ビデオ信号の補正とは、該ビデオ信号が入力された画素の点灯期間の長さの補正に相当する。30

#### 【0132】

時間階調方式と組み合わせたデジタル方式が適用された発光装置では、直線で示される式(6)を用いることが好ましい。但し、デジタル方式では、非発光の状態をわざわざ測定する必要がないため、式(6)における定数bの値をゼロとするとよい。そして各画素の特性の測定は一度だけ行って定数aの値を求めるといい。

#### 【0133】

上記の構成を有する本発明はアナログ方式で駆動させた発光装置において、トランジスタの特性バラツキによる影響を防止し、鮮明な多階調の表示が可能な発光装置及びその駆動方法を提供することができる。さらに本発明は、経時変化により発光素子の両電極間に流れる電流量の変化を抑制し、鮮明な多階調表示が可能な発光装置及びその駆動方法を提供することが出来る。40

#### 【0134】

なお本実施例は、実施の形態と自由に組み合わせることが可能である。

#### 【実施例2】

#### 【0135】

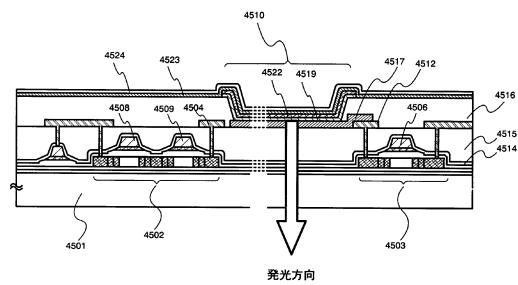

本実施例では、画素の断面構造の一例について図7を用いて説明する。

#### 【0136】

図7において、基板4501上に設けられたスイッチング用トランジスタ4502は公50

知の方法で形成されたnチャネル型トランジスタを用いる。なお、本実施例ではダブルゲート構造としているが、シングルゲート構造でも構わないし、トリプルゲート構造やそれ以上のゲート本数を持つマルチゲート構造でも構わない。また、公知の方法で形成されたpチャネル型トランジスタを用いて形成しても構わない。

#### 【0137】

駆動用トランジスタ4503は、公知の方法で形成されたnチャネル型トランジスタを用いる。スイッチング用トランジスタ4502のドレイン配線4504は配線（図示せず）によって駆動用トランジスタ4503のゲート電極4506に電気的に接続されている。

#### 【0138】

駆動用トランジスタ4503は発光素子4510を流れる電流量を制御するための素子であるため、多くの電流が流れ、熱による劣化やホットキャリアによる劣化の危険性が高い素子もある。そのため、駆動用トランジスタ4503のドレイン領域、あるいはソース領域とドレイン領域の両方に、ゲート絶縁膜を介してゲート電極に重なるようにLDD領域を設ける構造は極めて有効である。図7においては、一例として駆動用トランジスタ4503のソース領域とドレイン領域の両方にLDD領域を形成した例を示している。

#### 【0139】

また、本実施例では駆動用トランジスタ4503をシングルゲート構造で図示しているが、複数のトランジスタを直列に接続したマルチゲート構造としても良い。さらに、複数のトランジスタを並列につなげて実質的にチャネル形成領域を複数に分割し、熱の放射を高い効率で行えるようにした構造としても良い。このような構造は熱による劣化対策として有効である。

#### 【0140】

また、駆動用トランジスタ4503のゲート電極4506を含む配線（図示せず）は、駆動用トランジスタ4503のドレイン配線4512と絶縁膜を介して一部で重なり、その領域では保持容量が形成される。この保持容量は駆動用トランジスタ4503のゲート電極4506にかかる電圧を保持する機能を有する。

#### 【0141】

スイッチング用トランジスタ4502および駆動用トランジスタ4503の上には第1の層間絶縁膜4514が設けられ、その上に樹脂絶縁膜となる第2の層間絶縁膜4515が形成される。

#### 【0142】

4517は透光性の高い導電膜となる画素電極（発光素子の陽極）であり、駆動用トランジスタ4503のドレイン領域に一部が覆い被さるように形成され、電気的に接続される。画素電極4517としては酸化インジウムと酸化スズとの化合物（ITOと呼ばれる）、或いは酸化インジウムと酸化亜鉛の化合物を用いることが好ましい。もちろん、他の透光性の導電膜を用いてもよい。

#### 【0143】

次に有機樹脂膜4516を画素電極4517上に形成し、画素電極4517に面する部分をパターニングした後、有機化合物層4519が形成される。なおここでは図示していないが、R（赤）、G（緑）、B（青）の各色に対応した有機化合物層4519を作り分けても良い。有機化合物層4519とする発光材料としては、共役ポリマー系材料を用いる。代表的なポリマー系材料としては、ポリパラフェニレンビニレン（PPV）系、ポリビニルカルバゾール（PVK）系、ポリフルオレン系などが挙げられる。また、有機化合物層4519は、単層構造、積層構造の二つの構造があるが、本発明はどちらの構造を作製してもよい。公知の材料、及び構造を自由に組み合わせて有機化合物層4519（発光およびそのためのキャリアの移動を行わせるための層）を形成すれば良い。

#### 【0144】

例えば、本実施例ではポリマー系材料を有機化合物層4519として用いる例を示したが、低分子系有機発光材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪

10

20

30

40

50

素等の無機材料を用いることも可能である。これらの有機発光材料や無機材料は公知の材料を用いることができる。

【0145】

陰極4523まで形成されると、発光素子4510が完成する。なお、ここでいう発光素子4510とは、画素電極4517と、有機化合物層4519と、正孔注入層4522および陰極4523で形成された積層体を示す。

【0146】

ところで、本実施例では、陰極4523の上にパッシベーション膜4524を設けている。パッシベーション膜4524としては窒化珪素膜または窒化酸化珪素膜が好ましい。この目的は、外部と発光素子4510とを遮断することであり、発光材料の酸化による劣化を防ぐ意味と、有機発光材料からの脱ガスを抑える意味との両方を併せ持つ。これにより発光装置の信頼性が高められる。10

【0147】

以上のように本実施例において説明してきた発光装置は図7に示す構造の画素からなる画素部を有し、オフ電流値の十分に低い選択用トランジスタと、ホットキャリア注入に強い駆動用トランジスタとを有する。従って、高い信頼性を有し、且つ、良好な画像表示が可能な発光装置が得られる。

【0148】

本実施例において説明した構造を有する発光素子の場合、有機化合物層4519で発生した光は、矢印で示されるようにトランジスタが形成された基板4501の方向に向かって出射される。なお、発光素子4510から発せられる光が基板4501の方向に向かって出射することを下面出射とよぶ。20

【0149】

次いで、発光素子から発せられる光が、基板4510と反対の方向に向かって出射する（上面出射）発光装置の断面構造について図17を用いて説明する。

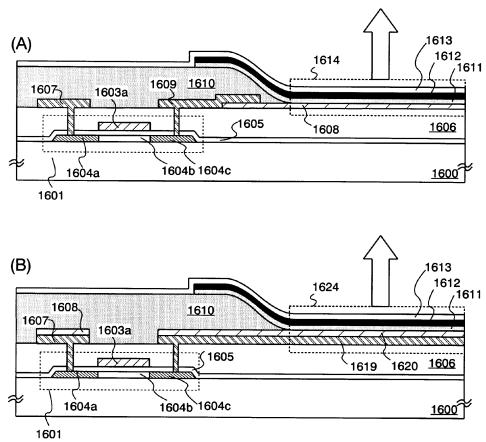

【0150】

図17(A)において、基板1600上には、駆動用トランジスタ1601が形成されている。駆動用トランジスタ1601は、ソース領域1604aとドレイン領域1604cと、チャネル形成領域1604bとを有する。またゲート絶縁膜1605を介して、チャネル形成領域1604b上に設けられたゲート電極1603aを有する。なお駆動用トランジスタ1601は、図17(A)に示した構成だけでなく、公知の構成のトランジスタを自由に用いることができる。30

【0151】

駆動用トランジスタ1601上には層間膜1606が形成されている。次いで、ITO等の透明導電膜を成膜して、所望の形状にパターニングして、画素電極1608を形成する。ここで画素電極1608は、発光素子1614の陽極として機能する。

【0152】

そして層間膜1606は、駆動用トランジスタ1601のソース領域1604a及びドレイン領域1604cに達するコンタクトホールを形成し、Ti、Tiを含むA1およびTiでなる積層膜を成膜して、所望の形状にパターニングする。そうすると、配線1607及び配線1609が形成される。40

【0153】

続いて、アクリル等の有機樹脂材料等でなる絶縁膜を形成し、発光素子1614の画素電極1608に対応する位置に開口部を形成して絶縁膜1610を形成する。ここで、開口部の側壁の段差に起因する有機化合物層の劣化、段切れ等の問題を回避するため、開口部は十分になだらかなテーパー形状の側壁を有するように形成する。

【0154】

そして有機化合物層1611を形成した後、発光素子1614の対向電極（陰極）1612を、2nm以下の厚さのセシウム(Cs)膜及び10nm以下の厚さの銀(Ag)膜を順に成膜した積層膜によって形成する。発光素子1614の対向電極1612の膜厚を極めて50

薄くすることにより、有機化合物層 1611 から発せられた光は対向電極 1612 を透過して、基板 1600 と反対の方向に出射される。そして、発光素子 1614 の保護を目的として、保護膜 1613 を成膜する。

#### 【0155】

図 17 (B) は、図 17 (A) と異なる構成の断面図である。なお図 17 (B) において、図 17 (A) と同じ部分は同じ符号を用いて説明する。また図 17 (B) において、駆動用トランジスタ 1601 と層間膜 1606 を形成するまでは、図 17 (A) で示した構成と同様であるので説明は省略する。

#### 【0156】

層間膜 1606 に、駆動用トランジスタ 1601 のソース領域 1604a 及びドレイン領域 1604c に達するコンタクトホールを形成する。その後、Ti、Ti を含む A1 および Ti でなる積層膜を成膜して、続いて、ITO 等を代表とする透明導電膜を成膜する。Ti、Ti を含む A1 および Ti でなる積層膜と、ITO 等を代表とする透明導電膜とを、所望の形状にパターニングして、配線 1607、配線 1608、配線 1609、画素電極 1620 を形成する。なお画素電極 1620 は、発光素子 1624 の陽極として機能する。

#### 【0157】

続いて、アクリル等の有機樹脂材料等でなる絶縁膜を形成し、発光素子 1624 の画素電極 1620 に対応する位置に開口部を形成して絶縁膜 1610 を形成する。ここで、開口部の側壁の段差に起因する有機化合物層の劣化、段切れ等の問題を回避するため、開口部は、十分になだらかなテーパー形状の側壁を有するように形成する。

#### 【0158】

次に、有機化合物層 1611 を形成した後、発光素子 1624 の対向電極（陰極）1612 を、2 nm 以下の厚さのセシウム (Cs) 膜及び 10 nm 以下の厚さの銀 (Ag) 膜を順に成膜した積層膜によって形成する。発光素子 1624 の対向電極 1612 の膜厚を極めて薄くすることにより、有機化合物層 1611 から発せられた光は対向電極 1612 を透過して、基板 1600 とは反対の方向に出射される。次いで、発光素子 1624 の保護を目的として、保護膜 1613 を成膜する。

#### 【0159】

このように、基板 1600 とは反対の方向に光を出射する発光装置は、基板 1600 上に形成された、駆動用トランジスタ 1601 等の素子を介して、発光素子 1614 の発光を視認する必要が無いために、開口率を大きくすることが出来る。

#### 【0160】

図 17 (B) で示した構成の画素は、図 17 (A) で示した構成の画素と比較すると、駆動用トランジスタのソース領域またはドレイン領域と接続される配線 1619 と、画素電極 1620 を、共通のフォトマスクを用いてパターニングして形成することができるため、作成工程において必要となるフォトマスクの削減及び工程の簡略化が可能となる。

#### 【0161】

なお、本実施例は、実施の形態及び実施例 1 と自由に組み合わせることが可能である。

#### 【実施例 3】

#### 【0162】

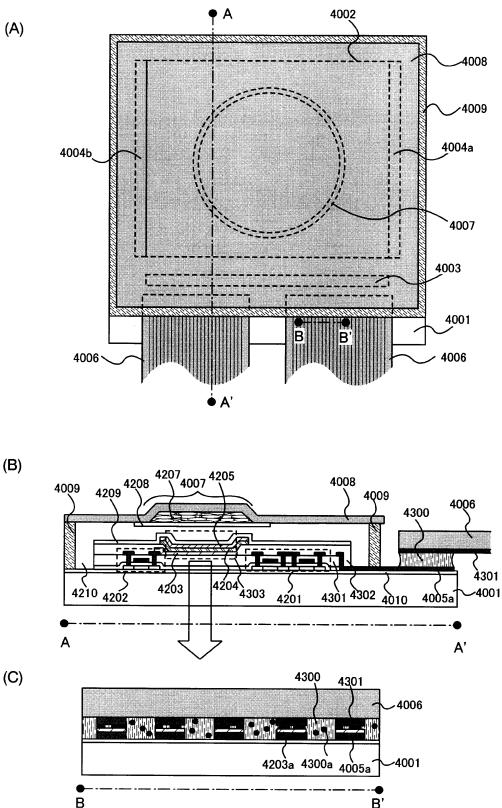

本実施例では、本発明の発光装置の外観について、図 8 を用いて説明する。

#### 【0163】

図 8 (A) は、発光装置の上面図であり、図 8 (B) は、図 8 (A) の A - A' における断面図、図 8 (C) は図 8 (A) の B - B' における断面図である。

#### 【0164】

基板 4001 上に設けられた画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、b とを囲むようにして、シール材 4009 が設けられている。また画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、b の上にシーリング材 4008 が設け

10

20

30

40

50

られている。画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、b とは、基板 4001 とシール材 4009 とシーリング材 4008 とによって、充填材 4210と共に密封されている。

#### 【0165】

なお本実施例において、1組(2つ)のゲート信号線駆動回路が設けられているが、本発明はこれに限定されず、ゲート信号線駆動回路とソース信号線駆動回路の数は設計者が任意に定めることができる。

#### 【0166】

また基板 4001 上に設けられた画素部 4002 と、ソース信号線駆動回路 4003 と、第 1 及び第 2 のゲート信号線駆動回路 4004a、b とは、複数のトランジスタを有している。図 8(B)では、下地膜 4010 上に形成されたソース信号線駆動回路 4003 に含まれる駆動回路用トランジスタ(但し、ここではnチャネル型トランジスタとpチャネル型トランジスタを図示する)4201 及び画素部 4002 に含まれる駆動用トランジスタ(発光素子への電流を制御するトランジスタ)4202 を図示した。

10

#### 【0167】

本実施例では、駆動回路用トランジスタ 4201 には公知の方法で作製されたpチャネル型トランジスタまたはnチャネル型トランジスタが用いられ、駆動用トランジスタ 4202 には公知の方法で作製されたpチャネル型トランジスタが用いられる。また、画素部 4002 には駆動用トランジスタ 4202 のゲート電極に接続された保持容量(図示せず)が設けられる。

20

#### 【0168】

駆動回路用トランジスタ 4201 及び駆動用トランジスタ 4202 上には層間絶縁膜(平坦化膜)4301 が形成され、その上に駆動用トランジスタ 4202 のドレインと電気的に接続する画素電極(陽極)4203 が形成される。画素電極 4203 としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガリウムを添加したものを用いても良い。

#### 【0169】

そして、画素電極 4203 の上には絶縁膜 4302 が形成され、絶縁膜 4302 は画素電極 4203 の上に開口部が形成されている。この開口部において、画素電極 4203 の上には有機化合物層 4204 が形成される。有機化合物層 4204 は公知の有機発光材料または無機発光材料を用いることができる。また、有機発光材料には低分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

30

#### 【0170】

有機化合物層 4204 の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。また、有機化合物層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。

#### 【0171】

有機化合物層 4204 の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極 4205 が形成される。また、陰極 4205 と有機化合物層 4204 の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、有機化合物層 4204 を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極 4205 を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスター・ツール方式)の成膜装置を用いることで上述のような成膜を可能とする。そして陰極 4205 は所定の電圧が与えられている。

40

#### 【0172】

以上のようにして、画素電極(陽極)4203、有機化合物層 4204 及び陰極 4205 からなる発光素子 4303 が形成される。そして発光素子 4303 を覆うように、絶縁

50

膜4302上に保護膜4209が形成されている。保護膜4209は、発光素子4303に酸素や水分等が入り込むのを防ぐのに効果的である。

#### 【0173】

4005aは電源線に接続された引き回し配線であり、駆動用トランジスタ4202のソース領域に電気的に接続されている。引き回し配線4005aはシール材4009と基板4001との間を通り、異方導電性フィルム4300を介してFPC4006が有するFPC用配線4301に電気的に接続される。

#### 【0174】

シーリング材4008としては、ガラス材、金属材（代表的にはステンレス材）、セラミックス材、プラスチック材（プラスチックフィルムも含む）を用いることができる。プラスチック材としては、FRP（Fiberglass-Reinforced Plastics）板、PVF（ポリビニルフルオライド）10

フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

#### 【0175】

但し、発光素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

#### 【0176】

また、充填材4103としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC（ポリビニルクロライド）、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB（ポリビニルブチラル）またはEVA（エチレンビニルアセテート）を用いることができる。本実施例では充填材として窒素を用いた。20

#### 【0177】

また充填材4103を吸湿性物質（好ましくは酸化バリウム）もしくは酸素を吸着しうる物質にさらしておくために、シーリング材4008の基板4001側の面に凹部4007を設けて吸湿性物質または酸素を吸着しうる物質4207を配置する。そして、吸湿性物質または酸素を吸着しうる物質4207が飛び散らないように、凹部カバー材4208によって吸湿性物質または酸素を吸着しうる物質4207は凹部4007に保持されている。なお凹部カバー材4208は目の細かいメッシュ状になっており、空気や水分は通し、吸湿性物質または酸素を吸着しうる物質4207は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質4207を設けることで、発光素子4303の劣化を抑制できる。30

#### 【0178】

図8(C)に示すように、画素電極4203が形成されると同時に、引き回し配線4005a上に接するように導電性膜4203aが形成される。

#### 【0179】

また、異方導電性フィルム4300は導電性フィラー4300aを有している。基板4001とFPC4006とを熱圧着することで、基板4001上の導電性膜4203aとFPC4006上のFPC用配線4301とが、導電性フィラー4300aによって電気的に接続される。40

#### 【0180】

本発明の発光装置が有する電流計及び補正回路は、基板4001とは異なる基板（図示せず）上に形成され、FPC4006を介して、基板4001上に形成された電源線及び陰極4205に電気的に接続されている。

#### 【0181】

なお本実施例は、実施の形態及び実施例1、2と自由に組み合わせて実施することが可能である。50

**【実施例 4】****【0182】**

本実施例では、実施例3とは異なる本発明の発光装置の外観について、図9を用いて説明する。より詳しくは、電流計及び補正回路を、画素部が形成されている基板とは異なる基板上に形成し、ワイヤボンディング法、COG(チップ・オン・グラス)法等の手段によって画素部が形成されている基板上の配線と接続した場合の発光装置の外観について、図9を用いて説明する。

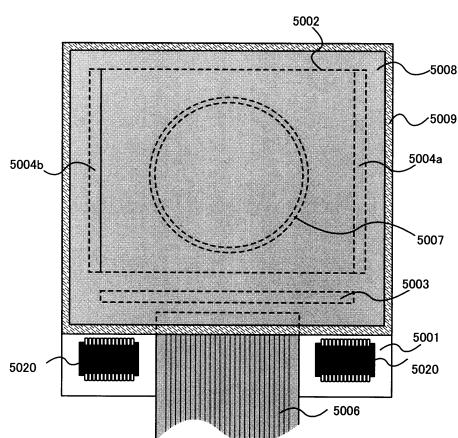

**【0183】**

図9に本実施例の発光装置の外観図を示す。基板5001上に設けられた画素部5002と、ソース信号線駆動回路5003と、第1及び第2のゲート信号線駆動回路5004a、bとを囲むようにして、シール材5009が設けられている。また画素部5002と、ソース信号線駆動回路5003と、第1及び第2のゲート信号線駆動回路5004a、bとの上にシーリング材5008が設けられている。よって画素部5002と、ソース信号線駆動回路5003と、第1及び第2のゲート信号線駆動回路5004a、bとは、基板5001とシール材5009とシーリング材5008とによって、充填材(図示せず)と共に密封されている。

**【0184】**

なお本実施例において、2つのゲート信号線駆動回路が設けられているが、これに限定されず、ゲート信号線駆動回路とソース信号線駆動回路の数は設計者が任意に定めることができる。

20

**【0185】**

シーリング材5008の基板5001側の面に凹部5007を設けて吸湿性物質または酸素を吸着しうる物質を配置する。

**【0186】**

基板5001上に引き回されている配線(引き回し配線)は、シール材5009と基板5001との間を通り、FPC5006を介して発光装置の外部の回路または素子に接続されている。

**【0187】**

電流計及び補正回路は、基板5001とは異なる基板(以下、チップと呼ぶ)5020に形成され、COG(チップ・オン・グラス)法等の手段によって基板5001上に取り付けられ、基板5001上に形成された電源線及び陰極(図示せず)に電気的に接続されている。

30

**【0188】**

本実施例では、チップ5020は、ワイヤボンディング法、COG法等により基板5001上に取り付けることで、発光装置を1枚の基板で構成することができ、装置自体がコンパクトになり、機械的強度も上がる。

**【0189】**

なお、基板上にチップを接続する方法に関しては、公知の方法を用いて行うことが可能である。また、電流計と、補正回路以外の回路及び素子を、基板5001上に取り付けても良い。

40

**【0190】**

本実施例は、実施の形態及び実施例1～3と自由に組み合わせて実施することが可能である。

**【実施例5】****【0191】**

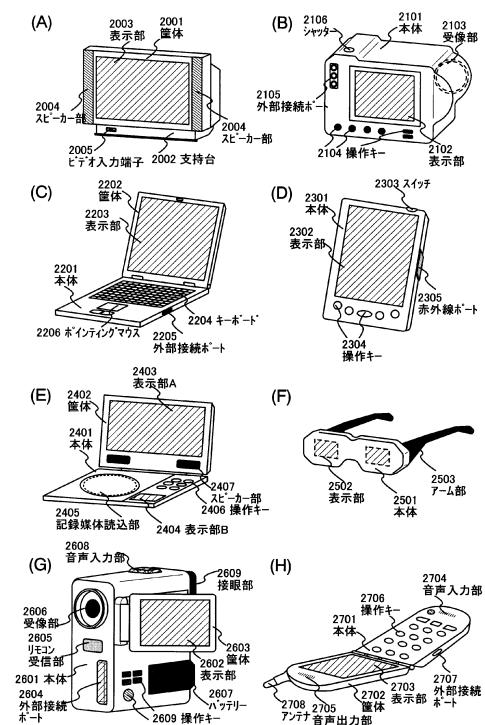

発光装置は自発光型であるため、液晶ディスプレイに比べ、明るい場所での視認性に優れ、視野角が広い。従って、様々な電子機器の表示部に用いることができる。

**【0192】**

本発明の発光装置を用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装

50

置（カーオーディオ、オーディオコンポ等）、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（具体的にはデジタルビデオディスク（DVD）等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。特に、斜め方向から画面を見る機会が多い携帯情報端末は、視野角の広さが重要視されるため、発光装置を用いることが望ましい。それら電子機器の具体例を図10に示す。

#### 【0193】

図10（A）は発光装置であり、筐体3001、支持台3002、表示部3003、スピーカー部3004、ビデオ入力端子3005等を含む。本発明の発光装置は表示部3003に用いることができる。発光装置は自発光型であるためバックライトが必要なく、液晶ディスプレイよりも薄い表示部とすることができます。なお、発光装置は、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。10

#### 【0194】

図10（B）はデジタルスチルカメラであり、本体3101、表示部3102、受像部3103、操作キー3104、外部接続ポート3105、シャッター3106等を含む。本発明の発光装置は表示部3102に用いることができる。

#### 【0195】

図10（C）はノート型パーソナルコンピュータであり、本体3201、筐体3202、表示部3203、キーボード3204、外部接続ポート3205、ポインティングマウス3206等を含む。本発明の発光装置は表示部3203に用いることができる。20

#### 【0196】

図10（D）はモバイルコンピュータであり、本体3301、表示部3302、スイッチ3303、操作キー3304、赤外線ポート3305等を含む。本発明の発光装置は表示部3302に用いることができる。

#### 【0197】

図10（E）は記録媒体を備えた携帯型の画像再生装置（具体的にはDVD再生装置）であり、本体3401、筐体3402、表示部A3403、表示部B3404、記録媒体（DVD等）読み込み部3405、操作キー3406、スピーカー部3407等を含む。表示部A3403は主として画像情報を表示し、表示部B3404は主として文字情報を表示するが、本発明の発光装置はこれら表示部A、B3403、3404に用いることができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。30

#### 【0198】

図10（F）はゴーグル型ディスプレイ（ヘッドマウントディスプレイ）であり、本体3501、表示部3502、アーム部3503を含む。本発明の発光装置は表示部3502に用いることができる。

#### 【0199】

図10（G）はビデオカメラであり、本体3601、表示部3602、筐体3603、外部接続ポート3604、リモコン受信部3605、受像部3606、バッテリー3607、音声入力部3608、操作キー3609等を含む。本発明の発光装置は表示部3602に用いることができる。40

#### 【0200】

ここで図10（H）は携帯電話であり、本体3701、筐体3702、表示部3703、音声入力部3704、音声出力部3705、操作キー3706、外部接続ポート3707、アンテナ3708等を含む。本発明の発光装置は表示部3703に用いることができる。なお、表示部3703は黒色の背景に白色の文字を表示することで携帯電話の消費電力を抑えることができる。

#### 【0201】

なお、将来的に有機発光材料の発光輝度が高くなれば、出力した画像情報を含む光をレンズ等で拡大投影してフロント型若しくはリア型のプロジェクターに用いることも可能となる。50

## 【0202】

また、上記電子機器はインターネットやCATV(ケーブルテレビ)などの電子通信回線を通じて配信された情報を表示することが多くなり、特に動画情報を表示する機会が増してきている。有機発光材料の応答速度は非常に高いため、発光装置は動画表示に好ましい。

## 【0203】

また、発光装置は発光している部分が電力を消費するため、発光部分が極力少なくなるように情報を表示することが望ましい。従って、携帯情報端末、特に携帯電話や音響再生装置のような文字情報を主とする表示部に発光装置を用いる場合には、非発光部分を背景として文字情報を発光部分で形成するように駆動することが望ましい。

10

## 【0204】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図16】

【図17】

【図18】

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 2 P |

| G 0 9 G | 3/20  | 6 7 0 J |

| H 0 5 B | 33/14 | A       |