(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3693504号

(P3693504)

(45) 発行日 平成17年9月7日(2005.9.7)

(24) 登録日 平成17年7月1日(2005.7.1)

(51) Int.C1.<sup>7</sup>

F 1

G 11 C 16/02

G 11 C 17/00 6 1 3

請求項の数 3 (全 10 頁)

(21) 出願番号 特願平10-217916

(22) 出願日 平成10年7月31日(1998.7.31)

(65) 公開番号 特開2000-48579(P2000-48579A)

(43) 公開日 平成12年2月18日(2000.2.18)

審査請求日 平成14年8月19日(2002.8.19)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100094525

弁理士 土井 健二

(74) 代理人 100094514

弁理士 林 恒徳

(72) 発明者 川又 潤弥

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 小松 正

最終頁に続く

(54) 【発明の名称】メモリデバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

フロー・ティングゲート型のメモリセルを複数有する不揮発性のメモリデバイスにおいて

前記メモリセルを有する複数の通常メモリブロックと、

前記メモリセルを有するブートメモリブロックと、

ブロック選択アドレスを供給され、前記複数の通常メモリブロック及びブートメモリブロックを選択するブロックデコーダと、

前記ブロックデコーダに供給するブロック選択アドレスを機能設定ビットに応じて反転または非反転するアドレス供給部と、

前記機能設定ビットを記憶する機能設定メモリとを有し、

前記機能設定メモリは、電源間に直列に接続され、電気的に書き込み及び消去される第1及び第2のフロー・ティングゲート型のMOSトランジスタと、前記第1及び第2のMOSトランジスタの接続点に接続される出力端子とを有し、前記第1のMOSトランジスタに書き込みを行い前記第2のMOSトランジスタに消去を行うことで第1のデータを記憶し、前記第1のMOSトランジスタに消去を行い前記第2のMOSトランジスタに書き込みを行うことで第2のデータを記憶することを特徴とするメモリデバイス。

## 【請求項 2】

請求項1において、

前記記憶データの読み出しにおいて、前記第1及び第2のMOSトランジスタのゲート

が、前記書き込み後の閾値電圧より低く前記消去後の閾値電圧より高い電圧に維持されることを特徴とするメモリデバイス。

【請求項 3】

請求項 1 または 2 において、

更に、前記第 1 の M O S トランジスタと共にフローティングゲートを有し、前記書き込み及び消去時に該フローティングゲートへの電子の注入及び引き抜きを行う第 3 の M O S トランジスタと、

前記第 2 の M O S トランジスタと共にフローティングゲートを有し、前記書き込み及び消去時に該フローティングゲートへの電子の注入及び引き抜きを行う第 4 の M O S トランジスタとを有することを特徴とするメモリデバイス。 10

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は、フローティングゲートを有する M O S トランジスタを利用した不揮発性メモリデバイスに関し、消費電流が小さく且つ読み出しを高速化できるメモリデバイスに関する。

【0 0 0 2】

【従来の技術】

フローティングゲートを有する M O S トランジスタをメモリセルとして利用する不揮発性メモリは、大容量で記憶したデータが不揮発性であることから、広く利用されている。特に、消去単位を比較的大きなブロックに限定して回路構成を簡略化したフラッシュメモリは、広く普及している。 20

【0 0 0 3】

かかるフラッシュメモリには、データを記憶する通常のメモリブロック以外に、それより容量が小さいブートブロックを有するデバイスがある。かかるブートブロックは、例えばフラッシュメモリが搭載されているシステムの起動時に、無条件にアクセスされる領域であり、システムの起動時に必要になる B I O S 等のシステム情報が記憶されている領域である。この様なブートブロックには、ブロックの上位アドレス側に配置されているトップブートブロックと、下位アドレス側に配置されているボトムブートブロックとが存在する。これらの違いは、最初にアクセスするブロック選択アドレスを、上位側のアドレスにするか下位側のアドレスにするかの違いだけであり、ブートブロック内のメモリデバイスは同じである。 30

【0 0 0 4】

上記の様なブートブロックを有するフラッシュメモリは、ユーザの要求に応じてトップブートブロック型か、ボトムブートブロック型かにする必要がある。したがって、同一のメモリデバイスを製造し、ユーザの要求に応じてどちらの型にすべきかの情報を機能設定メモリに記憶し、その機能設定ビットに応じてブロック選択アドレス A d d 1 を切り換えることが行われる。

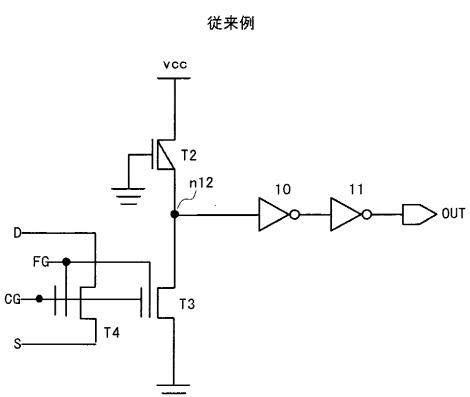

【0 0 0 5】

図 6 は、従来の機能設定メモリの構成例を示す図である。従来のメモリの構成は、通常のメモリセルと同様に、フローティングゲートを有しデータを記憶する M O S トランジスタ T 3 とその負荷トランジスタ T 2 とが、電源 V c c と G N D 間に直列接続される。負荷トランジスタ T 2 は、例えば N チャネル型のデプレッシジョン型トランジスタであり、そのゲートはグランド電位に維持され、所定のインピーダンスを有して常時導通状態である。また、 M O S トランジスタ T 3 は、フローティングゲート F G を有し、そのフローティングゲート F G に電子を注入する書き込み(プログラム)によりその閾値電圧が高くなり、フローティングゲート F G から電子を引き抜く消去によりその閾値電圧が低くなる。従って、コントロールゲート C G に、両閾値電圧の中間の電圧を印加することにより、 M O S トランジスタ T 3 は、記憶データに応じて導通または非導通となる。 40

【0 0 0 6】

また、MOSトランジスタT3のフローティングゲートFGへの電子の注入及び引き抜きの為には、そのソース、ドレインに所定の制御電圧を印加する必要がある。しかしながら、MOSトランジスタT3は負荷トランジスタT2と共に図示される回路構成をとるので、かかる制御電圧の印加が困難である。そこで、フローティングゲートFGを共通に有する書き込み、消去用のトランジスタT4が別途設けられる。そして、このトランジスタT4を介して、フローティングゲートFGへの電子の注入と引き抜き動作が行われる。

#### 【0007】

かかるメモリの読み出しは、コントロールゲートCGに上記の両閾値電圧の中間電圧を印加することで、トランジスタT3を導通又は非導通にし、トランジスタT2, T3の接続点n12の電圧を検出する。接続点n12の電圧がインバータ10, 11を介して出力OUTから読み出される。書き込みがなされている場合は、トランジスタT3が非導通となり、接続点n12はHレベルとなり、出力OUTもHレベルとなる。また、消去状態の場合は、トランジスタT3が導通し、接続点n12はLレベルとなり、出力OUTもLレベルとなる。

#### 【0008】

##### 【発明が解決しようとする課題】

図6に示されたメモリデバイス構成では、トランジスタT3が消去状態の場合、コントロールゲートCGに読み出し時の電圧を印加すると、トランジスタT3が導通し、電源VccからトランジスタT2, T3及びグランドに貫通電流が流れる。かかる電流は、消費電流の増大を招くので、読み出しを行わないパワーダウン状態では、コントロールゲートCGをグランド電位に維持して、トランジスタT3の消去状態か書き込み状態かにかかわらず貫通電流が流れないようにする必要がある。そして、アクティブ状態に遷移してデータを読み出す時のみ、コントロールゲートCGの電位をグランドから所定の読み出し電位まで上昇させる。

#### 【0009】

従って、図6に示したメモリデバイス構成の機能設定メモリを利用する場合、アクティブ状態になると、通常のメモリへのアクセスをする前に、その機能設定メモリのコントロールゲートCGを立ち上げて設定情報を読み出す必要があり、アクセス時間が長くなる。

#### 【0010】

大容量化されたフラッシュメモリの不良ビットを救済する為に冗長メモリセルアレイを設け、その不良ビットのアドレスを記憶する冗長ROMに、図6の如きメモリデバイスを利用する場合も、メモリへのアクセスのたびに、その冗長ROMの読み出しの為にメモリデバイスのコントロールゲートCGの立ち上げを行う必要がある。従って、かかる冗長ROMも広い概念では機能設定メモリの一種であり、図6の如きメモリデバイスでは、高速化の弊害となる。

#### 【0011】

そこで、本発明の目的は、上記従来の課題を解決し、低消費電流で読み出し速度が速いメモリデバイスを提供することにある。

#### 【0012】

更に、本発明の目的は、コントロールゲートの電位を一定に保っても貫通電流が流れないメモリデバイスを提供することにある。

#### 【0013】

##### 【課題を解決するための手段】

上記の目的を達成する為に、本発明は、不揮発性のメモリデバイスにおいて、電源間に直列に接続され、電気的に書き込み及び消去される第1及び第2のフローティングゲート型のMOSトランジスタと、

前記第1及び第2のMOSトランジスタの接続点に接続される出力端子とを有し、前記第1のMOSトランジスタに書き込みを行い前記第2のMOSトランジスタに消去を行うことで第1のデータを記憶し、前記第1のMOSトランジスタに消去を行い前記第2のMOSトランジスタに書き込みを行うことで第2のデータを記憶することを特徴とする

10

20

30

40

50

。

## 【0014】

上記のメモリデバイスによれば、両トランジスタのコントロールゲートに読み出し電圧を印加しても、一方のトランジスタのみしか導通しないので、電源間に貫通電流が流れることがない。従って、コントロールゲートを読み出し電圧レベルに維持することで、消費電流の増大を伴うことなく読み出し時間を短くすることができる。

## 【0015】

更に、上記の目的を達成する為に、本発明は、フローティングゲート型のメモリセルを複数有する不揮発性のメモリデバイスにおいて、

前記メモリセルを有する複数の通常メモリブロックと、

10

前記メモリセルを有するブートメモリブロックと、

ブロック選択アドレスを供給され、前記複数の通常メモリブロック及びブートメモリブロックを選択するブロックデコーダと、

前記ブロックデコーダに供給するブロック選択アドレスを機能設定ビットに応じて反転または非反転するアドレス供給部と、

前記機能設定ビットを記憶する機能設定メモリとを有し、

前記機能設定メモリは、電源間に直列に接続され、電気的に書き込み及び消去される第1及び第2のフローティングゲート型のMOSトランジスタと、前記第1及び第2のMOSトランジスタの接続点に接続される出力端子とを有し、前記第1のMOSトランジスタに書き込みを行い前記第2のMOSトランジスタに消去を行うことで第1のデータを記憶し、前記第1のMOSトランジスタに消去を行い前記第2のMOSトランジスタに書き込みを行うことで第2のデータを記憶することを特徴とする。

20

## 【0016】

上記の発明によれば、機能設定メモリのトランジスタのフローティングゲートを読み出し電圧に維持することで、消費電流の増大を伴うことなく、その記憶データを出力端に出力し続けることができ、読み出し速度を速くすることが可能になる。

## 【0017】

## 【発明の実施の形態】

以下、本発明の実施の形態について図面に従って説明する。しかしながら、本発明の技術的範囲がその実施の形態に限定されるものではない。

30

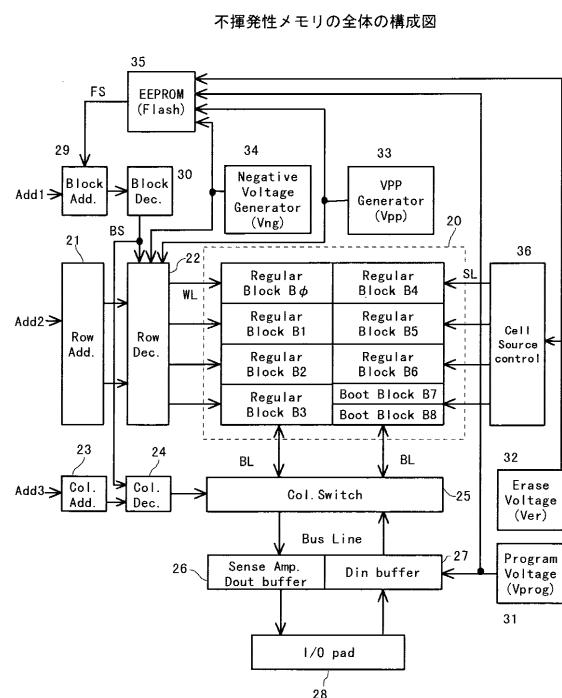

## 【0018】

図1は、フラッシュメモリ等の不揮発性メモリの全体構成図である。メモリセルアレイ20は、この例では、通常ブロックB0～B6と、ブートブロックB7, B8とを有する、ブートブロックB7, B8は、通常ブロックよりも小さい容量である。行アドレスAdd2が行アドレスバッファ21に供給され、その行アドレスが行デコーダ22でデコードされ、所定のワード線WLが選択される。また、列アドレスAdd3が列アドレスバッファ23に供給され、その列アドレスが列デコーダ24でデコードされ、コラムスイッチ回路25により所定のビット線BLが選択される。

## 【0019】

コラムスイッチ回路25により選択されたビット線は、読み出しままたは書き込みの為に、センスアンプ26や入力バッファ27に接続される。センスアンプ26及び入力バッファ27は、更に入出力バッド28に接続される。

40

## 【0020】

メモリセルアレイ20内のメモリセルへの書き込み(プログラム)、消去、読み出しの為に、高電圧Vpp発生回路33、プログラム電圧Vprog発生回路31、消去電圧Ver発生回路32、及び負電圧Vng発生回路34が設けられる。更に、メモリセルのソース線SLの状態を制御するセルソース制御回路36が設けられる。

## 【0021】

メモリセルアレイ20内のブロックを選択する為に、ブロック選択アドレスAdd1が供給されるブロックアドレスバッファ29と、そのブロック選択アドレスをデコードするブ

50

ロックデコーダ30とが設けられる。このブロックアドレスバッファは、単にブロック選択アドレスを入力してデコーダ30に供給するだけでなく、機能設定メモリ35からの機能設定ビットFSに応じて、ブロック選択アドレスを反転または非反転する機能を有するアドレス供給回路もある。

【0022】

ブートブロックB7, B8は、メモリセルアレイ20において、ブロック選択アドレスが下位側の位置に配置される。従って、ブロックデコーダ30に供給されるブロック選択アドレスが、B7, B8を選択するアドレスの場合に、ブートブロックの選択が行われる。即ち、ブロック選択信号BSに応答して、行デコーダ22は、対応するブートブロックB7, B8内のワード線WLを選択し、列デコーダ24は、対応するブートブロックB7, B8内のビット線BLを選択する。

10

【0023】

一方、ユーザの要求によりブロック選択アドレスが上位側に位置するトップブートブロックが指定される場合は、機能設定メモリ35内にそれを指定する機能設定ビットを記憶する。従って、その機能設定ビットFSに応答して、ブロックアドレス供給回路29内にて、供給されるアドレスAdd1を反転させることで、見かけ上はトップブートブロック対応のメモリデバイスとすることができる。また、ユーザの要求によりブロック選択アドレスが下位側に位置するボトムブートブロックが指定される場合は、同様に、機能設定メモリ35内にそれを指定する機能設定ビットを記憶する。従って、その機能設定ビットFSに応答して、ブロックアドレス供給回路29内にて、供給されるアドレスAdd1を非反転でブロックデコーダに供給する。その結果、ボトムブートブロック対応のメモリデバイスとすることができる。

20

【0024】

この様に、機能設定メモリ35内にその機能を設定する情報を記憶させることで、同じメモリセルアレイ構成のメモリデバイスでも、トップブートブロック形式とボトムブートブロック形式とに併用させることができ、生産効率を上げることができる。

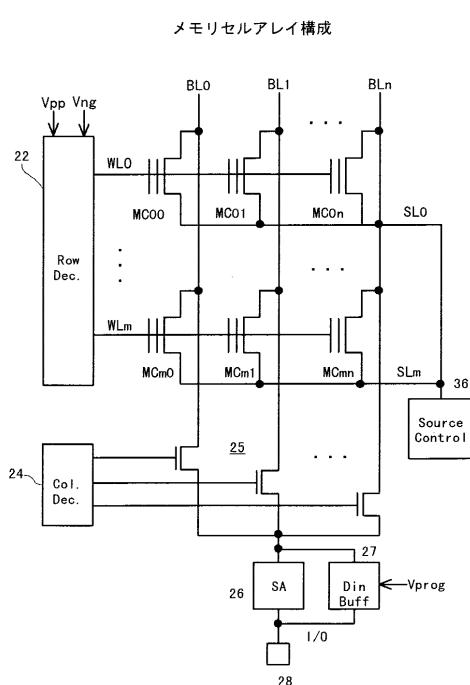

【0025】

図2は、メモリセルアレイの構成図である。ワード線WL<sub>0</sub> ~ WL<sub>m</sub>とビット線BL<sub>0</sub> ~ BL<sub>n</sub>の交差位置に、フローティングゲート型のNチャネルMOSトランジスタからなるメモリセルMC<sub>00</sub> ~ MC<sub>mn</sub>が設けられる。また、メモリセルのトランジスタのドレイン端子は、それぞれ対応するビット線BL<sub>0</sub> ~ BL<sub>n</sub>に接続され、コントロールゲートは、ワード線WL<sub>0</sub> ~ WL<sub>m</sub>に接続される。そして、メモリセルトランジスタのソース端子は、ソース線SL<sub>0</sub> ~ SL<sub>m</sub>を介してソース制御回路36に接続される。

30

【0026】

かかるメモリセルアレイ内のメモリセルへの書き込み(プログラム)、消去、読み出し動作は以下の通りである。先ず、書き込み(プログラム)は、ワード線WLに電源V<sub>cc</sub>よりも高い電圧V<sub>pp</sub>(例えば10V)を印加し、ビット線BLにプログラム電圧V<sub>prog</sub>(3 ~ 5V)を印加し、ソース線SLをグランド電位にする。その結果、フローティングゲート内に電子が注入され、メモリセルトランジスタの閾値電圧が上昇する。

【0027】

消去は、ワード線WLに負電圧V<sub>ng</sub>を印加し、ビット線BLをフローティングにし、ソース線SLに消去電圧V<sub>er</sub>(例えば5VまたはV<sub>cc</sub>)を印加する。その結果、フローティングゲート内の電子が引き抜かれ、メモリセルトランジスタの閾値電圧が低下する。

40

【0028】

読み出しがは、ワード線WLにプログラム時の閾値電圧と消去時の閾値電圧との中間の電圧を印加し、プログラム状態か消去状態かによりメモリセルトランジスタを非導通または導通させ、その状態をビット線BLを介してセンスアンプ26により検出する。

【0029】

以上の通り、メモリセルアレイ内のメモリセルへの書き込み(プログラム)、消去、読み出しがは、それぞれのワード線、ビット線、ソース線の電位或いは状態を制御することで行

50

われる。

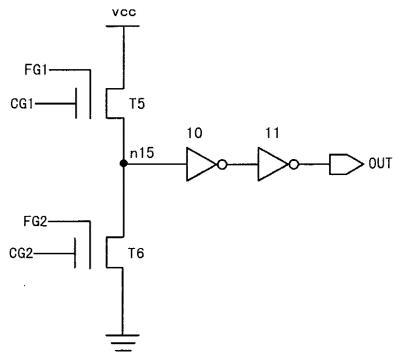

【0030】

図3は、機能設定メモリに利用されるメモリデバイスの回路図である。このメモリデバイスは、フローティングゲート型の第1のNチャネルMOSトランジスタT5と第2のNチャネルMOSトランジスタT6とを、グランドと電源Vccとの間に直列接続して構成される。そして、それらの接続点n15が、インバータ10, 11を介して出力OUTに接続される。第1、第2のトランジスタT5, T6は、それぞれフローティングゲートFG1, FG2とコントロールゲートCG1, CG2を有する。そして、情報の記憶方法については、第1のトランジスタT5に書き込み(プログラム)し、第2のトランジスタT6を消去することで、第1のデータが記憶され、第1のトランジスタT5を消去し、第2のトランジスタT6に書き込み(プログラム)することで、第1のデータの反転の第2のデータが記憶される。

【0031】

図3のメモリデバイスに第1のデータが記憶された場合は、第1のトランジスタの閾値電圧が高くなり、第2のトランジスタの閾値電圧が低くなる。従って、それらの閾値電圧の中間の読み出し用の電圧がそれぞれのコントロールゲートCG1, CG2に印加されると、トランジスタT5が非導通、トランジスタT6が導通して、ノードn15はLレベルとなる。その場合、トランジスタT5が非導通であるので、電源Vccからグランドへの貫通電流は発生しない。

【0032】

一方、第2のデータが記憶された場合は、上記の逆の動作となる。従って、トランジスタT5が導通し、トランジスタT6が非導通となり、ノードn15はHレベルとなる。その場合も貫通電流は発生しない。

【0033】

従って、図3のメモリデバイスを利用して、上記の通り第1または第2のデータを記憶させることで、コントロールゲートCG1, CG2を常に読み出し電圧に維持しても、貫通電流の発生はなく、消費電流の増大にはならない。従って、図3のメモリデバイスには、コントロールゲートをグランド電位に維持するパワーダウン制御をする必要がなく、常にコントロールゲートCG1, CG2を読み出し用の電圧に維持しても、消費電流を増大させることはない。即ち、消費電流を増大することなく、記憶された機能設定データを常にノードn15に読み出している状態に維持することができる。その結果、従来例のメモリデバイスの如く、パワーダウン状態からアクティブ状態になるたびに、読み出しのためにコントロールゲートの電圧を立ち上げる必要がなく、読み出し速度を上げることができる。

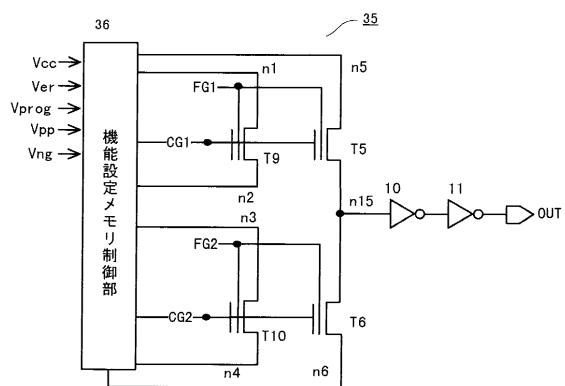

【0034】

図4は、機能設定メモリに利用されるメモリデバイスのより詳細な回路図である。この例は、図3の第1、第2のトランジスタT5, T6それぞれに、フローティングゲートFG1, FG2を共通にする書き込み・消去用のトランジスタT9, T10を追加した例である。書き込み・消去用のトランジスタT9, T10のコントロールゲートCG、ソース、ドレイン端子n1, n2, n3, n4は、機能設定メモリ制御部36によりそれぞれ独立に制御される。また、第1、第2のトランジスタT5, T6のドレイン端子n5, ソース端子n6も、機能設定メモリ制御部36によりそれぞれ制御されてもよい。

【0035】

書き込み・消去用のトランジスタT9, T10のレシオW/L(チャネル幅/チャネル長)は、読み出し用のトランジスタT5, T6のレシオW/Lよりも小さく設計される。即ち、読み出し用に利用される第1及び第2のトランジスタT5, T6は、インバータ10, 11を駆動する必要があり、ある程度の駆動能力が要求される。従って、それらのトランジスタのレシオW/Lはある程度大きく設計される。一方、書き込み・消去用のトランジスタT9, T10は、書き込みと消去時の駆動容量を小さくする為に、トランジスタのレシオW/Lは小さく設計される。これらのトランジスタT9, T10により駆動される

10

20

30

40

50

ことはないので、レシオが小さくても何ら問題はない。

【0036】

図5は、図4の機能設定メモリデバイスへの各動作に対するノードの電圧の関係を示す図表である。図4のメモリデバイスへの書き込み・消去は、書き込み・消去用トランジスタT9, T10を介して行われ、読み出しは第1、第2のトランジスタT5, T6により行われる。

【0037】

第1のトランジスタT5に書き込み（プログラム）を行う場合は、機能設定メモリ制御部36により、コントロールゲートCG1が高電圧Vppに、ノードn1がグランドに、ノードn2がプログラム電圧Vprogにそれぞれ制御される。その結果、フローティングゲートFG1内に電子が注入される。その場合、ノードn5, n6はグランド電位に制御される。第1のトランジスタT5を消去する場合は、機能設定メモリ制御部36により、コントロールゲートCG1が負電圧Vngに、ノードn1が消去電圧Ver（例えばVcc）に、ノードn2がフローティング状態にそれぞれ制御される。その結果、フローティングゲートFG1内から電子が引き抜かれる。この消去は、図5の消去1に示した制御動作である。

【0038】

第2のトランジスタT6への書き込み（プログラム）と消去も、トランジスタT10により、同様にノードn3, n4を制御することにより行われる。

【0039】

そして、読み出し動作では、ノードn1～n4を全てグランド電位にし、ノードn5を電源Vccにノードn6をグランド電位にし、コントロールゲートCG1, CG2に読み出し電圧Vread（例えば電源Vcc）を印加する。その結果、一方のトランジスタT5, T6が導通し、ノードn15がHレベル或いはLレベルとなる。より具体的には、コントロールゲートCG1, CG2は、通常は読み出し電圧に維持され、書き込みと消去の時に、上記の様に別の電圧Vpp, Vngに制御される。従って、ノードn15には、書き込みと消去時を除いて、常に記憶データに応じてHレベル或いはLレベルが出力されている。

【0040】

消去動作において、トランジスタT5, T6を利用することも可能である。その場合は、図5の消去2に示される通り、ノードn1～n4を全てグランドに維持し、コントロールゲートCG1, CG2を負電圧Vngにし、ノードn5, 6を消去電圧Verに制御する。その場合、ノードn15はフローティング状態となっている。その結果、フローティングゲートFG1, FG2から電子が引き出され、それらのトランジスタの閾値電圧が低下する。

【0041】

以上の通り、メモリデバイスのメモリセルアレイ内のメモリセルトランジスタと同じフローティングゲートを有するNチャネルMOSトランジスタを利用して機能設定メモリを構成する。しかも、第1、第2のフローティングゲート型のNチャネルMOSトランジスタを電源Vccとグランド間に直列接続する構成とし、一方のトランジスタに電子を注入し他方のトランジスタから電子を引き出すことで、データを記憶する。その結果、両トランジスタのコントロールゲートに読み出し電圧を印加しても、一方のトランジスタのみが導通し、貫通電流が流れることはない。従って、書き込みと消去以外は、常にコントロールゲートの電位を読み出し電圧に維持して、消費電流を増大することなく機能設定メモリへのアクセスタイムを限りなくゼロにすることができます。

【0042】

機能設定メモリは、ブートブロックの位置についての機能データに限られない。例えば、冗長アドレスを記憶するメモリとしても利用することができる。また、それ以外のメモリデバイスの機能を設定する為の初期値データのメモリとして利用することもできる。

【0043】

【発明の効果】

以上説明した通り、本発明によれば、消費電流を増大することなく、メモリデバイスへの

10

20

30

40

50

アクセスを高速化することができる。

【図面の簡単な説明】

【図1】フラッシュメモリ等の不揮発性メモリの全体構成図である。

【図2】メモリセルアレイの構成図である。

【図3】機能設定メモリに利用されるメモリデバイスの回路図である。

【図4】機能設定メモリに利用されるメモリデバイスのより詳細な回路図である。

【図5】図4の機能設定メモリデバイスへの各動作に対するノードの電圧の関係を示す図表である。

【図6】従来の機能設定メモリの構成例を示す図である。

【符号の説明】

T 5、T 6 第1、第2のフローティングゲート型MOSトランジスタ

C G コントロールゲート

F G フローティングゲート

2 0 メモリセルアレイ

B 0 ~ B 6 通常メモリブロック

B 7, B 8 ブートメモリブロック

2 9 ブロック選択アドレス供給回路

3 0 ブロックデコーダ

3 5 機能設定メモリ

F S 機能設定ビット

A d d 1 ブロック選択アドレス

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

各動作に対する各ノードの電圧の関係

| 動作    | FG1,2       | n1    | n2    | n3    | n4    | n5    | n6         |

|-------|-------------|-------|-------|-------|-------|-------|------------|

| ノーフ   | CG1,2 (GND) | (GND) | (GND) | (GND) | (GND) | Vcc   | GND        |

| 読み出し  | Vread       | (GND) | (GND) | (GND) | (GND) | Vcc   | GND        |

| プログラム | Vpp         | GND   | Vpp   | Vpp   | GND   | (GND) | (GND)      |

| 消去1   | Vng         | Vng   | Float | Float | Ver   | (GND) | (GND)      |

| 消去2   | Vng         | (GND) | (GND) | (GND) | (GND) | Ver   | Ver        |

|       |             |       |       |       |       |       | (n5はFloat) |

【図6】

---

フロントページの続き

(56)参考文献 特開平03-123118(JP, A)

米国特許第05740106(US, A)

特開平06-028872(JP, A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

G11C 16/00-16/34