| DOMANDA DI INVENZIONE NUMERO | 102021000020552 |

|------------------------------|-----------------|

| Data Deposito                | 30/07/2021      |

| Data Pubblicazione           | 30/01/2023      |

# Classifiche IPC

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| Н       | 01     | L           | 23     | 495         |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

| Н       | 01     | L           | 23     | 498         |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

| Н       | 01     | L           | 25     | 07          |

# Titolo

PROCEDIMENTO PER ASSEMBLARE DISPOSITIVI A SEMICONDUTTORE E DISPOSITIVO A SEMICONDUTTORE CORRISPONDENTE

DESCRIZIONE dell'invenzione industriale dal titolo:

"Procedimento per assemblare dispositivi a semiconduttore e dispositivo a semiconduttore corrispondente"

di: STMicroelectronics S.r.l., di nazionalità italiana, via C. Olivetti, 2 - 20864 Agrate Brianza (MB), Italia

Inventori designati: Matteo DE SANTA, Mirko ALESI

Depositata il: 30 luglio 2021

\* \* \* \*

#### TESTO DELLA DESCRIZIONE

### Campo tecnico

La descrizione è relativa ai dispositivi a semiconduttore.

Una o più forme di attuazione possono essere applicate vantaggiosamente ai dispositivi a semiconduttore di potenza.

#### Sfondo

In vari dispositivi a semiconduttore di potenza (compresi, per esempio, i dispositivi a semiconduttore di potenza in un package Quad-Flat No-leads o QFN) uno o più die o chip di potenza sono disposti a fianco di un die o un chip di pilotaggio ("driver") fabbricato, per esempio, usando la tecnologia BCD (Bipolar-CMOS-DMOS).

Questi chip (o die: i termini "chip" e "die" sono qui usati come sinonimi) possono essere montati su rispettivi die pad o paddle adiacenti in un leadframe.

Per fornire connessioni da die a die o da die a leadframe (per es., segnali, massa) si usa il wire bonding e per fornire percorsi o linee conduttive atte a trasportare correnti elevate si usano cosiddetti "ribbon" uniti con wedge-bonding ai lead del leadframe.

In un tale dispositivo, una quantità sostanziale di spazio del substrato (leadframe) è occupata da paddle o die pad distinti usati per montare i vari die o chip di pilotaggio e di potenza.

# Scopo e sintesi

Uno scopo di una o più forme di attuazione è di contribuire a trattare adeguatamente tale problema.

Secondo una o più forme di attuazione, tale scopo è raggiunto grazie a un procedimento avente le caratteristiche esposte nelle rivendicazioni che seguono.

Una o più forme di attuazione sono relative a un dispositivo a semiconduttore corrispondente. Un dispositivo a semiconduttore come un dispositivo di potenza comprendente più die o chip a semiconduttore accoppiati mutuamente può essere un esempio di un tale dispositivo.

Le rivendicazioni sono parte integrante dell'insegnamento tecnico qui fornito con riferimento alle forme di attuazione.

Una o più forme di attuazione comportano di impilare ("stacking") almeno un die (per esempio, un die di un controllore o di un dispositivo di pilotaggio) su un altro die (per esempio, un die di potenza) usando una o più sezioni di ribbon per l'attacco.

In tal modo, l'altezza complessiva del package è (leggermente) aumentata con tale aumento compensato in gran parte da una riduzione notevole dell'impronta ("footprint") del package. Questo può avere come risultato leadframe più piccoli, package più piccoli così come un ingombro ridotto sui substrati di montaggio finali, quale una scheda a circuito stampato (PCB, "Printed Circuit Board").

Una o più forme di attuazione si basano sul riconoscimento inaspettato del fatto che i ribbon, come

usati tradizionalmente per fornire percorsi o canali di corrente nei dispositivi a semiconduttore di potenza, sono abbastanza resistenti da sopportare adeguatamente uno o più chip a semiconduttore attaccati su di essi.

Una o più forme di attuazione offrono uno o più dei seguenti vantaggi:

compatibilità con macchine di wire bonding esistenti,

è fornito un processo plug & play, in cui il numero di fasi di assemblaggio rimane sostanzialmente invariato,

ampia applicabilità a vari package con leadframe, riduzione delle dimensioni dei package,

risparmi nei costi grazie alla riduzione delle dimensioni dei package,

selettività grazie alla capacità di customizzare i fili e i ribbon secondo specifiche desiderate.

Com'è il caso nei dispositivi tradizionali comprendenti chip impilati, un certo chip (per esempio, uno piccolo) può essere posto "sopra" almeno un altro chip usando come struttura di supporto un ribbon disposto tra essi.

Una o più forme di attuazione facilitano così una riduzione delle dimensioni X e Y complessive di un package di un chip a semiconduttore con la capacità di trarre vantaggio da una possibile combinazione sinergica di die bonding, wire bonding e ribbon bonding (più un impilamento di die o di chip) nella fabbricazione dei dispositivi a semiconduttore.

# Breve descrizione delle figure

Una o più forme di attuazione saranno descritte ora, a puro titolo di esempio, con riferimento alle figure annesse, nelle quali:

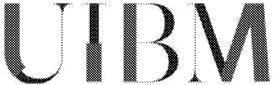

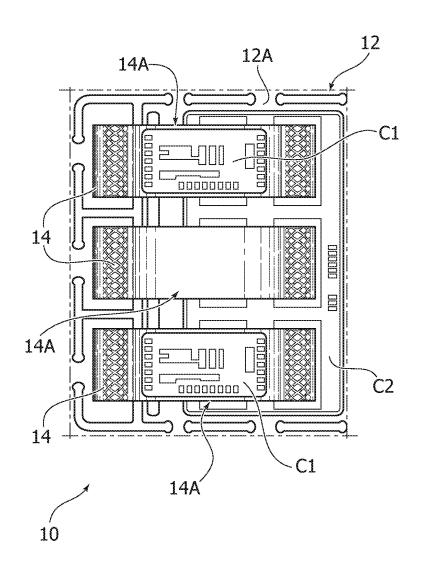

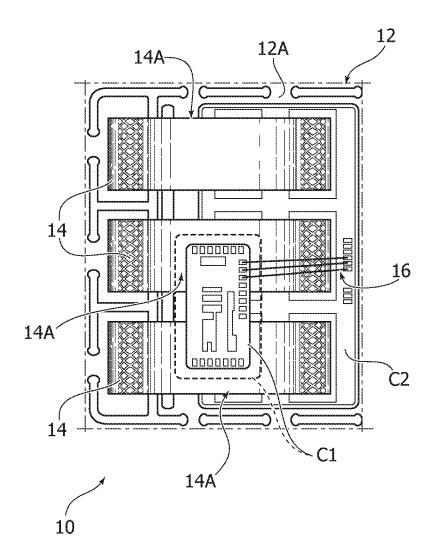

le Figure 1 e 2 sono viste in pianta di dispositivi a semiconduttore comprendenti più chip a semiconduttore disposti su un substrato con ribbon che forniscono percorsi o canali di connessione di potenza,

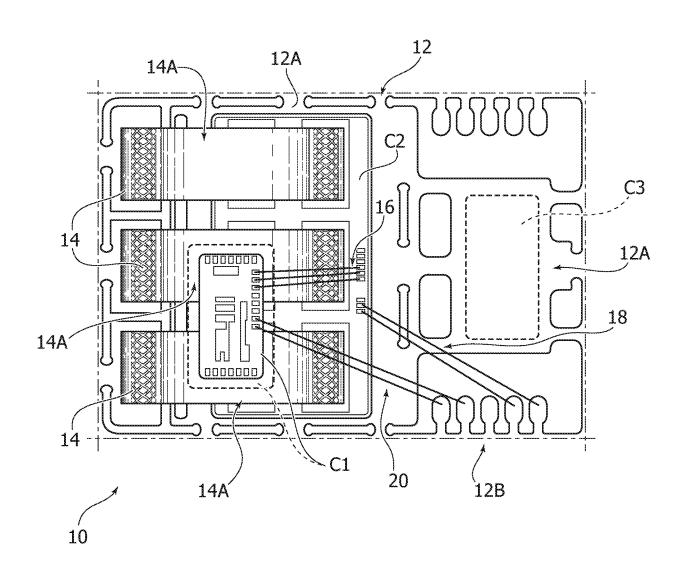

la Figura 3 è una vista in pianta di un dispositivo a semiconduttore secondo forme di attuazione della presente descrizione,

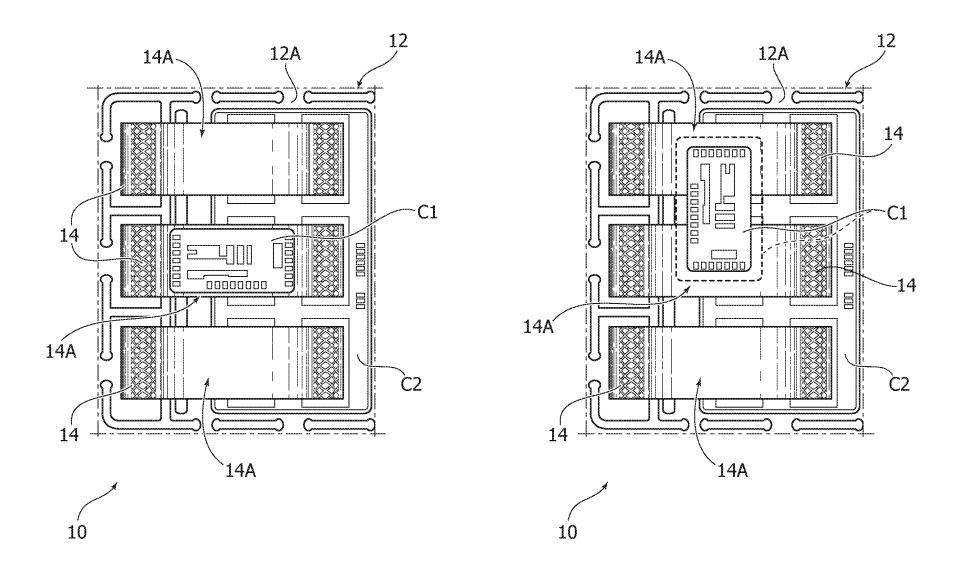

la Figura 4 è una vista in pianta di un altro dispositivo a semiconduttore secondo forme di attuazione della presente descrizione,

la Figura 5 è una vista in pianta di ancora un altro dispositivo a semiconduttore secondo forme di attuazione della presente descrizione,

la Figura 6 è una vista in pianta di un ulteriore dispositivo a semiconduttore secondo forme di attuazione della presente descrizione, e

la Figura 7 è un esempio di una vista in pianta di una possibile variante dell'esempio presentato nella Figura 6.

I simboli e numeri corrispondenti nelle differenti figure si riferiscono in generale a parti corrispondenti a meno che sia indicato altrimenti.

Le figure sono disegnate per illustrare chiaramente gli aspetti rilevanti delle forme di attuazione e non sono disegnate necessariamente in scala.

I bordi delle caratteristiche disegnate nelle figure non indicano necessariamente la fine dell'estensione della caratteristica.

# Descrizione dettagliata

Nella descrizione che segue sono illustrati vari dettagli specifici, allo scopo di fornire una comprensione approfondita di vari esempi di forme di attuazione secondo la descrizione. Le forme di attuazione possono essere ottenute senza uno o più dei dettagli specifici o con altri procedimenti, componenti, materiali, ecc. In altri casi, operazioni, materiali o strutture note non sono illustrate o descritte in dettaglio in modo tale da non rendere poco chiari vari aspetti delle forme di attuazione.

Un riferimento a "una forma di attuazione" nel quadro della presente descrizione intende indicare che particolare configurazione, struttura, o caratteristica descritta con riferimento alla forma di attuazione è compresa in almeno una forma di attuazione. Per cui, le frasi come "in una forma di attuazione" o simili che possono essere presenti in vari punti della presente descrizione non fanno necessariamente riferimento esattamente proprio alla stessa forma di attuazione. particolari configurazioni, Inoltre, strutture caratteristiche possono essere combinate in adequato qualsiasi in una o più forme di attuazione.

I riferimenti usati qui sono forniti semplicemente per comodità e quindi non definiscono l'ambito di protezione o l'ambito delle forme di attuazione.

Come rappresentato a titolo di esempio nelle Figure 1 e 2, dispositivi a semiconduttore 10 tradizionali possono comprendere più chip (o die) a semiconduttore C1, C2 disposti, qualunque sia il loro numero e siano le loro funzioni, in corrispondenza di rispettivi die pad o paddle 12A adiacenti in un substrato 12, come un leadframe.

La designazione "leadframe" (o "lead frame") è usata correntemente (si veda, per esempio, l'USPC Consolidated Glossary of the United States Patent and Trademark Office) per indicare un frame di metallo che fornisce supporto a un die o a un chip di un circuito integrato così come lead

elettrici per interconnettere il circuito integrato nel die o nel chip ad altri contatti o componenti elettrici.

Sostanzialmente, un leadframe comprende una schiera ("array") di formazioni elettricamente conduttive (lead) 12B che, da una posizione periferica, si estendono verso l'interno nella direzione di un die o un chip a semiconduttore, formando così una schiera di formazioni elettricamente conduttive da uno o più die pad o paddle 12A configurati per avere almeno un die o un chip a semiconduttore attaccato su di essi.

Questo può avvenire mediante mezzi tradizionali, come un adesivo per attacco di die (per esempio, una pellicola per attacco di die o DAF ("Die Attach Film").

Tradizionalmente, i leadframe sono creati usando tecnologie come una tecnologia di fotoincisione. Con questa tecnologia, un materiale di metallo (per es., rame) sotto forma di una lamina o un nastro è inciso sui lati superiore e inferiore per creare vari pad e lead.

I substrati, come i leadframe, sono forniti vantaggiosamente in una versione prestampata (pre-molded) in cui una resina isolante (una resina epossidica, per esempio) riempie gli spazi vuoti tra i die pad 12A e i lead 12B.

Un leadframe prestampato 12 è così un substrato laminare sostanzialmente piatto con il materiale prestampato (la resina) che riempie gli spazi nella struttura elettricamente conduttiva (di un materiale di metallo come rame, per esempio) del leadframe, a cui è stato conferito un aspetto scolpito che include spazi vuoti durante la formazione, mediante incisione, per esempio.

Lo spessore totale del leadframe prestampato è lo stesso spessore della struttura elettricamente conduttiva scolpita.

Figure 1 e 2, un Nelle riferimento 14 indica cosiddetti "ribbon" (vale a dire, una striscia stretta di materiale elettricamente conduttive - il rame può essere un esempio di tale materiale) che forniscono elettricamente conduttive estendentisi sopra i die potenza C2 e configurati per trasportare correnti dai die di potenza C2 a uno o più carichi elettrici (non visibili nelle figure).

Come illustrato nelle Figure 1 e 2, i ribbon 14 possono esibire una configurazione ondulata (a onde) che facilita la saldatura attraverso un bonding a ultrasuoni.

I package di potenza, come rappresentato a titolo di esempio nelle Figure 1 e 2, comprendono così almeno due chip o die.

Questi possono comprendere, per esempio, uno o più die di "potenza" C2 - che forniscono la sezione di potenza del dispositivo 10 - e almeno un die C1 più piccolo che agisce come un controllore e è connesso sia al die o ai die di potenza C2 sia ai lead esterni 12B nel substrato (leadframe) 12.

Come indicato, i ribbon come 14 sono usati principalmente per le linee "robuste" (heavy duty), mentre il die o i die di controllore C1 di solito sono uniti con wire bonding con un filo sottile.

Nei dispositivi tradizionali, come illustrato nelle Figure 1 e 2, ciascun die C1, C2 è disposto su un rispettivo die paddle 12A.

Di conseguenza, le dimensioni del package finale sono imposte dal numero e dalle dimensioni dei die paddle forniti per ospitare i die C1, C2.

Nella prospettiva di package, questo si traduce in dimensioni del package più grandi, poiché il numero dei die aumenta com'è attualmente il caso con le applicazioni di potenza comprendenti package multi-die.

In altre parole, nei dispositivi tradizionali come illustrati nelle Figure 1 e 2 - in cui i die C1, C2 sono disposti mutuamente adiacenti - un maggior numero di die C1, C2 porta a un maggiore spazio richiesto e a dimensioni X e Y più grandi del package del dispositivo, con le dimensioni del package finale inevitabilmente aumentate.

In maniera complementare, il numero di posizioni di montaggio di die disponibili in un leadframe è collegato direttamente alle dimensioni dei singoli die, e un numero più elevato di posizioni diventa disponibile in un leadframe soltanto in presenza di die di dimensione minore.

Se i die hanno una dimensione minore, le posizioni disponibili in un leadframe possono aumentare, ma sono ancora limitate dalla dimensione del package del dispositivo che è collegata al numero di die per ciascun dispositivo.

Il costo del package finale è collegato alla dimensione del package.

La possibilità di impilare i chip o i die (per es., impilando un die più piccolo "sopra" un die più grande) è ben nota nella tecnica.

D'altra parte, guardando le Figure 1 e 2, e pensando di impilare, per es., il die C1 su uno dei die C2, si sarebbe portati inevitabilmente a concludere che i ribbon

14 estendentisi sopra i die C2 ostacolano una tale soluzione.

Questo è particolarmente vero se si considera la generale configurazione ondulata conferita ai ribbon 14 al fine di facilitare la loro saldatura, per es., attraverso un bonding a ultrasuoni.

Contrariamente a tali attese, i ribbon 14 usati nella fabbricazione dei dispositivi a semiconduttore di potenza come illustrato nelle Figure 1 e 2 possono essere resi sufficientemente robusti (rigidi e resistenti) da essere usati come superfici di montaggio per die a semiconduttore, come un die di pilotaggio C1.

Questo può essere particolarmente vero se (come illustrato nelle figure dalla Figura 3 in poi) il ribbon o ciascuno dei ribbon 14 usati per montare un die C1 su di essi sono sagomati (in maniera peraltro nota agli esperti del settore del ribbon bonding) in modo tale da presentare una superficie planare come rappresentato a titolo di esempio con 14A nelle Figure da 3 a 7.

Si nota nuovamente che, in tutte queste figure, parti o elementi simili a parti o a elementi già discussi con riferimento alle Figure 1 e 2 sono indicati con gli stessi simboli di riferimento: per brevità una descrizione dettagliata corrispondente non sarà ripetuta.

La Figura 3 è illustrativa della possibilità di montare (attaccare) un die piccolo, come il die di controllo C1, su una tale superficie di ribbon planare 14A.

Questo può avvenire tramite un materiale per attacco (una "colla") tradizionale, come noto agli esperti del settore.

La Figura 3 è illustrativa di un die C1 di piccola dimensione atto a essere disposto completamente sopra una

superficie planare 14A fornita in uno singolo dei ribbon 14.

Confrontando la Figura 3 con la Figura 1 si può notare che, con il die C1 montato su uno dei ribbon 14 estendentesi a sua volta sopra il die o i die C2 - come illustrato nella Figura 3 - la porzione del substrato (lead frame) 12 che nella Figura 1 ospita il die C1 (comprendendo il die pad 12A sulla destra della figura) non è più usata per montare il die C1.

Tale porzione del substrato (lead frame) 12 può essere eliminata o usata per un altro scopo, come discusso con riferimento alla Figura 7.

La Figura 4 è un esempio del fatto che la dimensione del die C1 disposto (attaccato) sui ribbon 14 non è strettamente vincolante nella misura in cui un die (per es., più grande) come D1 illustrato in profilo tratteggiato può essere montato "a cavallo" o "a guisa di ponte" fra due ribbon 14 vicini (per es., tra due rispettive porzioni planari 14A).

I die come C1 possono essere montati sui ribbon 14 usando materiali per attacco, come una colla o un nastro adesivo, che possono essere conduttivi o non conduttivi, a seconda dell'applicazione desiderata.

Un montaggio a guisa di ponte, come rappresentato a titolo di esempio nella Figura 4, può essere sfruttato (per es., usando per attaccare il die C1 sui ribbon 14 un materiale elettricamente conduttivo) per creare un percorso elettricamente conduttivo che accoppia due ribbon 14 vicini. Una tale soluzione è descritta nella domanda di brevetto italiano 102021000017207 (Inventori: Villa e De Santa), assegnata in titolarità alla stessa titolare della

presente domanda e non ancora disponibile al pubblico alla data di deposito della presente domanda.

La Figura 5 è un esempio della possibilità di montare più die C1 su rispettive superfici di attacco 14A di due ribbon 14 (non necessariamente vicini).

Quale che sia la configurazione adottata per l'attacco, soluzioni come illustrate nelle Figure da 3 a 5 illustrano (per confronto diretto con le Figure 1 e 2) la possibilità di ridurre in modo apprezzabile le dimensioni X e Y complessive del package risultante.

Questa riduzione di dimensioni è vantaggiosa nell'aumentare il numero di posizioni di package disponibili su un certo leadframe 12, con la possibilità di ridurre il costo del package finale.

Questa possibilità è rappresentata a titolo di esempio dal confronto delle Figure 6 e 7.

La Figura 6 è illustrativa della possibilità (secondo i criteri, per es., della Figura 4) di attaccare un die C1 a cavallo o a guisa di ponte tra due ribbon 14 e di sfruttare il vantaggio di spazio ottenuto per mezzo dell'impilamento dei chip C1 e C2 ottenuto per fornire una riduzione complessiva del package del dispositivo.

La Figura 6 è illustrativa della possibilità di attaccare un die C1 a cavallo o a guisa di ponte tra due ribbon 14 (secondo i criteri, per es., della Figura 4) e di sfruttare il vantaggio dello spazio ottenuto per mezzo dell'impilamento dei chip C1 e C2 per fornire una riduzione complessiva del package del dispositivo, "eliminando" la porzione a destra del substrato (lead frame) 12 nella Figura 1.

La Figura 7 è un esempio della possibilità di sfruttare il vantaggio di spazio ottenuto per mezzo

dell'impilamento dei chip C1 e C2 al fine di conservare la porzione a destra del substrato (lead frame) 12 nella Figura 1 e sfruttare tale porzione del substrato 12 per montare uno o più die o chip aggiuntivi, come indicato con C3 in profilo tratteggiato.

Un approccio sostanzialmente simile può essere applicato al dispositivo della Figura 2, in cui il posto "lasciato libero" dal die C1 montato su uno o più dei ribbon 14 sul lato a sinistra della figura è usato eventualmente per montare un altro die.

Inoltre, la Figura 6 è un esempio della possibilità di accoppiare elettricamente il die di controllo C1 al die di potenza C2 tramite un wire bonding 16 tradizionale.

La Figura 7 illustra, in aggiunta a tale possibilità, la possibilità di:

accoppiare elettricamente il die di potenza C2 a lead esterni 12B nel leadframe per mezzo di ulteriori wire bond 18; e

accoppiare elettricamente il die di controllore C1 a lead esterni 12B nel leadframe per mezzo di ulteriori wire bond 20.

Si apprezzerà che un riferimento ai die C1 e C2 come die di potenza e di controllore è a puro titolo di esempio: una o più forme di attuazione possono in effetti applicarsi indipendentemente dalla natura e dal tipo dei chip o dei die coinvolti.

Sebbene siano stati rappresentati qui a titolo di esempio ribbon "funzionali" come 14 (cioè ribbon previsti per fornire percorsi o canali di flusso di corrente elevata per il dispositivo 10), certi esempi possono contemplare di fornire ribbon "fittizi" (vale a dire, ribbon che di per sé non sono richiesti per alcuna connessione elettrica) al

fine di facilitare la disposizione di un chip o di un die su di loro, eventualmente in una configurazione a guisa di ponte con un ribbon "funzionale".

Si è trovato che materiali di metallo tradizionali (per esempio, alluminio, rame o oro) come usati correntemente nel fornire i ribbon nei dispositivi a semiconduttore di potenza sono adeguati alle forme di attuazione, vale a dire, adeguati a produrre ribbon sufficientemente saldi da supportare un die a semiconduttore, come C1, montato su di essi, con la capacità di avere porzioni planari, come 14A, formate in essi.

I presenti esempi non hanno alcun impatto apprezzabile sul flusso di assemblaggio del dispositivo 10.

In effetti, dopo il die bonding su uno o più ribbon (come formati precedentemente per fornire linee di potenza come desiderato) un processo di wire bonding (come rappresentato a titolo di esempio dalle linee di wire bonding 16, 18 e 20 della Figura 7) può essere effettuato e continuato con le altre fasi di assemblaggio (stampaggio e incapsulamento, singolazione ("singulation"), e così via).

Fermi restando i principi di fondo, i dettagli e le forme di attuazione possono variare, anche in modo apprezzabile, rispetto a quanto è stato descritto, puramente a titolo di esempio, senza uscire dall'ambito delle forme di attuazione.

${\tt L'}$ ambito di protezione è definito dalle rivendicazioni annesse.

#### RIVENDICAZIONI

#### 1. Procedimento, comprendente:

disporre su un die pad (12A) in un substrato (12) almeno un primo die a semiconduttore (C2) con almeno un ribbon (14) elettricamente conduttivo che si estende sull'almeno un primo die a semiconduttore (C2), in cui l'almeno un primo die a semiconduttore (C2) è situato intermedio tra il substrato (12) e l'almeno un ribbon (14) elettricamente conduttivo, e

attaccare almeno un secondo die a semiconduttore (C1) sull'almeno un ribbon (14) elettricamente conduttivo per fornire su detto die pad (12A) un impilamento dell'almeno un secondo die a semiconduttore (C1) e dell'almeno un primo die a semiconduttore (C2), con l'almeno un ribbon (14) elettricamente conduttivo intermedio tra l'almeno un primo die a semiconduttore (C2) e l'almeno un secondo die a semiconduttore (C1).

# 2. Procedimento secondo la rivendicazione 1, comprendente:

disporre su detto substrato (12) una coppia di primi die a semiconduttore (C2) adiacenti con una coppia di ribbon (14) elettricamente conduttivi, ciascun ribbon (14) elettricamente conduttivo estendendosi su uno dei primi die a semiconduttore (C2), in cui ciascuno dei primi die a semiconduttore (C2) è situato intermedio tra il substrato (12) e un rispettivo ribbon (14) elettricamente conduttivo nella coppia di ribbon (14) elettricamente conduttivi, e

attaccare l'almeno un secondo die a semiconduttore (C1) a guisa di ponte tra detti ribbon (14) elettricamente conduttivi in detta coppia di ribbon (14) elettricamente

conduttivi per fornire un impilamento dell'almeno un secondo die a semiconduttore (C1), con ciascun ribbon (14) elettricamente conduttivo nella coppia di ribbon (14) elettricamente conduttivi intermedio tra uno rispettivo dei primi die a semiconduttore (C2) e una estremità del secondo die a semiconduttore (C1).

- 3. Procedimento secondo la rivendicazione 2, comprendente di attaccare l'almeno un secondo die a semiconduttore (C1) a guisa di ponte tra detti ribbon (14) elettricamente conduttivi in detta coppia di ribbon (14) elettricamente conduttivi per mezzo di un materiale per attacco elettricamente conduttivo, in cui detti ribbon (14) elettricamente conduttivi sono mutuamente elettricamente accoppiati.

- 4. Procedimento secondo una qualsiasi delle rivendicazioni precedenti, in cui l'almeno un ribbon (14) elettricamente conduttivo ha una configurazione ondulata e in cui il procedimento comprende fornire almeno una porzione planare (14A) nel ribbon (14) elettricamente conduttivo e attaccare l'almeno un secondo die a semiconduttore (C1) sull'almeno una porzione planare (14A) nel ribbon (14) elettricamente conduttivo.

- 5. Procedimento secondo una qualsiasi delle rivendicazioni precedenti, comprendente:

fornire in detto substrato (12) un ulteriore die pad (12A) adiacente a detto die pad (12A), e

attaccare su detto ulteriore die pad (12A) almeno un terzo die a semiconduttore (C3).

6. Procedimento secondo una qualsiasi delle rivendicazioni precedenti, comprendente almeno una tra:

una prima configurazione di wire-bond (16) che accoppia mutuamente l'almeno un primo die a semiconduttore (C2) e l'almeno un secondo die a semiconduttore (C1) in detto impilamento dell'almeno un secondo die a semiconduttore (C1) e dell'almeno un primo die a semiconduttore (C2), e/o

una seconda configurazione di wire-bond (18) che accoppia detto almeno un primo die a semiconduttore (C2) con formazioni elettricamente conduttive (12B) in una schiera di formazioni elettricamente conduttive fornite in detto substrato (12) intorno a detto die pad (12A), e/o

una terza configurazione di wire-bond (20) che accoppia detto almeno un secondo die a semiconduttore (C1) con formazioni elettricamente conduttive (12B) in una schiera di formazioni elettricamente conduttive fornite in detto substrato (12) intorno a detto die pad (12A).

#### 7. Dispositivo (10), comprendente:

un substrato (12) che comprende un die pad (12A) avente disposti su di esso almeno un primo die a semiconduttore (C2) con almeno un ribbon (14) elettricamente conduttivo che si estende sull'almeno un primo die a semiconduttore (C2), in cui l'almeno un primo die a semiconduttore (C2) è situato intermedio tra il substrato (12) e l'almeno un ribbon (14) elettricamente conduttivo, e

almeno un secondo die a semiconduttore (C1) sull'almeno un ribbon (14) elettricamente conduttivo per fornire su detto die pad (12A) un impilamento dell'almeno un secondo die a semiconduttore (C1) e dell'almeno un primo

die a semiconduttore (C2), con l'almeno un ribbon (14) elettricamente conduttivo intermedio tra l'almeno un primo die a semiconduttore (C2) e l'almeno un secondo die a semiconduttore (C1).

**8.** Dispositivo (10) secondo la rivendicazione 7, comprendente:

una coppia di primi die a semiconduttore (C2) adiacenti disposti su detto substrato (12) con una coppia di ribbon (14) elettricamente conduttivi, ciascun ribbon (14) elettricamente conduttivo estendendosi su uno dei primi die a semiconduttore (C2), in cui ciascuno dei primi die a semiconduttore (C2) è situato intermedio tra il substrato (12) e un rispettivo ribbon (14) elettricamente conduttivo nella coppia di ribbon (14) elettricamente conduttivi, e

almeno un secondo die a semiconduttore (C1) attaccato a guisa di ponte tra detti ribbon (14) elettricamente conduttivi in detta coppia di ribbon (14) elettricamente conduttivi per fornire un impilamento dell'almeno un secondo die a semiconduttore (C1), con ciascun ribbon (14) elettricamente conduttivo nella coppia di ribbon (14) elettricamente conduttivi intermedio tra uno rispettivo dei primi die a semiconduttore (C2) e una estremità del secondo die a semiconduttore (C1).

9. Dispositivo (10) secondo la rivendicazione 8, comprendente l'almeno un secondo die a semiconduttore (C1) attaccato a guisa di ponte tra detti ribbon (14) elettricamente conduttivi in detta coppia di ribbon (14) elettricamente conduttivi per mezzo di un materiale per attacco elettricamente conduttivo, in cui detti ribbon (14)

elettricamente conduttivi sono mutuamente accoppiati elettricamente.

- 10. Dispositivo (10) secondo una qualsiasi delle rivendicazioni da 7 a 9, in cui l'almeno un ribbon (14) elettricamente conduttivo ha una configurazione ondulata con almeno una porzione planare (14A) nel ribbon (14) elettricamente conduttivo, in cui l'almeno un secondo die a semiconduttore (C1) è attaccato all'almeno una porzione planare (14A) nel ribbon (14) elettricamente conduttivo.

- 11. Dispositivo (10) secondo una qualsiasi delle rivendicazioni da 7 a 10, comprendente:

un ulteriore die pad (12A) fornito in detto substrato (12) adiacente a detto die pad (12A), e

almeno un terzo die a semiconduttore (C3) che è attaccato su detto ulteriore die pad (12A).

12. Dispositivo (10) secondo una qualsiasi delle rivendicazioni da 7 a 11, comprendente almeno una tra:

una prima configurazione di wire-bond (16) che accoppia mutuamente l'almeno un primo die a semiconduttore (C2) e l'almeno un secondo die a semiconduttore (C1) in detto impilamento dell'almeno un secondo die a semiconduttore (C1) e dell'almeno un primo die a semiconduttore (C2), e/o

una seconda configurazione di wire-bond (18) che accoppia detto almeno un primo die a semiconduttore (C2) con formazioni elettricamente conduttive (12B) in una schiera di formazioni elettricamente conduttive fornite in detto substrato (12) intorno a detto die pad (12A), e/o

una terza configurazione di wire-bond (20) che accoppia detto almeno un secondo die a semiconduttore (C1) con formazioni elettricamente conduttive (12B) in una schiera di formazioni elettricamente conduttive fornite in detto substrato (12) intorno a detto die pad (12A).

FIG. 3 FIG. 4

FIG. 5 FIG. 6

FIG. 7