(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6184469号

(P6184469)

(45) 発行日 平成29年8月23日(2017.8.23)

(24) 登録日 平成29年8月4日(2017.8.4)

(51) Int.Cl.

H04N 5/3745 (2011.01)

F 1

H04N 5/3745 500

請求項の数 12 (全 17 頁)

(21) 出願番号 特願2015-254739 (P2015-254739)

(22) 出願日 平成27年12月25日 (2015.12.25)

(62) 分割の表示 特願2013-6147 (P2013-6147)

の分割

原出願日 平成25年1月17日 (2013.1.17)

(65) 公開番号 特開2016-76997 (P2016-76997A)

(43) 公開日 平成28年5月12日 (2016.5.12)

審査請求日 平成28年1月25日 (2016.1.25)

(31) 優先権主張番号 特願2012-82374 (P2012-82374)

(32) 優先日 平成24年3月30日 (2012.3.30)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 橋本 誠二

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 鈴木 建

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】光電変換装置および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

光に基づく画素信号を出力する画素と、A D 変換部と、補正部とを有し、

前記 A D 変換部は、対応する前記画素の出力する前記画素信号に基づく信号と、閾値との比較を行うことによって第1の比較結果信号を生成し、

前記第1の比較結果信号が、前記画素信号に基づく信号が前記閾値よりも大きいことを示す場合には、前記 A D 変換部は、前記画素信号に基づく信号と、時間に対して第1の変化率で第1の電位まで電位が変化する参照信号とを比較することによって、前記画素信号に基づく信号をデジタル信号に変換し、

前記第1の比較結果信号が、前記画素信号に基づく信号が前記閾値よりも小さいことを示す場合には、前記 A D 変換部は、前記画素信号に基づく信号と、時間に対して前記第1の変化率よりも小さい第2の変化率で、前記第1の電位よりも振幅が小さい第2の電位まで電位が変化する参照信号とを比較することによって、前記画素信号に基づく信号をデジタル信号に変換し、

前記閾値が、前記第2の電位よりも振幅が小さく、

前記補正部は、前記第1の変化率と前記第2の変化率との比を検出して、前記画素信号に基づくデジタル信号を補正することを特徴とする光電変換装置。

## 【請求項 2】

前記 A D 変換部は、ノイズと、時間に対して第3の変化率で第3の電位まで電位が変化する参照信号とを比較することによって、前記ノイズをデジタル信号に変換し、

10

20

前記閾値が、前記第3の電位よりも振幅が大きいことを特徴とする請求項1に記載の光電変換装置。

【請求項3】

前記第2の変化率と、前記第3の変化率とが同じ変化率であることを特徴とする請求項2に記載の光電変換装置。

【請求項4】

前記第2の変化率を前記第1の変化率で除した値を前記第1の電位に乗じた電位よりも、前記第2の電位が大きいことを特徴とする請求項1～3のいずれか1項に記載の光電変換装置。

【請求項5】

10

さらに選択回路を有し、

前記選択回路に、前記第1の変化率の参照信号と前記第2の変化率の参照信号とが入力され、

前記選択回路に前記第1の変化率の参照信号が入力される期間に、前記選択回路に前記第2の変化率の参照信号が入力され、

前記画素信号に基づく信号の前記デジタル信号への変換において、前記選択回路は、前記第1の比較結果信号に基づいて、前記第1の変化率の参照信号と、前記第2の変化率の参照信号との一方を前記A/D変換部に入力することを特徴とする請求項1～4のいずれか1項に記載の光電変換装置。

【請求項6】

20

さらに基準信号を生成する基準信号生成部を有し、

前記A/D変換部は、前記基準信号を、前記第1の変化率の参照信号と、前記第2の変化率の参照信号とのそれぞれを用いてデジタル信号に変換し、

前記基準信号を前記第1の変化率の参照信号と前記第2の変化率の参照信号とのそれぞれを用いて変換したデジタル信号によって、前記補正部が、前記前記第1の変化率と前記第2の変化率との比を検出することを特徴とする請求項1～5のいずれか1項に記載の光電変換装置。

【請求項7】

前記基準信号生成部は、前記基準信号とは振幅が異なる第2の基準信号を生成し、

前記A/D変換部は、前記第2の基準信号を、前記第1の変化率の参照信号と、前記第2の変化率の参照信号とのそれぞれを用いてデジタル信号に変換し、

前記基準信号を前記第1の変化率の参照信号と前記第2の変化率の参照信号とのそれぞれを用いて変換したデジタル信号と、前記第2の基準信号を前記第1の変化率の参照信号と前記第2の変化率の参照信号とのそれぞれを用いて変換したデジタル信号とによって、前記補正部が、前記前記第1の変化率と前記第2の変化率との比を検出することを特徴とする請求項6に記載の光電変換装置。

【請求項8】

請求項1～7のいずれか1項に記載の光電変換装置と、

前記光電変換装置から出力された信号を処理することで画像データを生成する信号処理部とを有することを特徴とする撮像システム。

40

【請求項9】

光に基づく画素信号を出力する画素を有する光電変換装置の駆動方法であって、

前記駆動方法は、

前記画素信号に基づく信号と、閾値との比較とによって第1の比較結果信号を生成するステップと、

前記第1の比較結果信号が、前記画素信号に基づく信号が前記閾値よりも大きいことを示す場合には、前記画素信号に基づく信号と、時間に対して第1の変化率で第1の電位まで電位が変化する参照信号とを比較することによって、前記画素信号に基づく信号をデジタル信号に変換し、

前記第1の比較結果信号が、前記画素信号に基づく信号が前記閾値よりも小さいことを

50

示す場合には、前記画素信号に基づく信号と、時間に対して前記第1の変化率よりも小さい第2の変化率で、前記第1の電位よりも振幅が小さい第2の電位まで電位が変化する参照信号とを比較することによって、前記画素信号に基づく信号をデジタル信号に変換するステップとを備え、

前記閾値が、前記第2の電位よりも振幅が小さく、

さらに前記駆動方法は、前記第1の変化率と前記第2の変化率との比を検出して、前記画素信号に基づくデジタル信号を補正するステップを備えることを特徴とする光電変換装置の駆動方法。

#### 【請求項10】

ノイズと、時間に対して第3の変化率で第3の電位まで電位が変化する参照信号とを比較することによって、前記ノイズをデジタル信号に変換するステップをさらに備え、

前記閾値が、前記第3の電位よりも振幅が大きいことを特徴とする請求項9に記載の光電変換装置の駆動方法。

#### 【請求項11】

前記第2の変化率と、前記第3の変化率とが同じ変化率であることを特徴とする請求項10に記載の光電変換装置の駆動方法。

#### 【請求項12】

前記第2の変化率を前記第1の変化率で除した値を前記第1の電位に乗じた電位よりも、前記第2の電位が大きいことを特徴とする請求項9～11のいずれか1項に記載の光電変換装置の駆動方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、光電変換装置および撮像システムに関し、特にA/D変換器を備えるものに関する。

##### 【背景技術】

##### 【0002】

A/D変換器を備えた撮像装置が知られている。その中で、特許文献1には、1個の画素からの画像信号を複数の比較器を用いて、時間に対する変化が異なる参照信号と比較することで、デジタル信号を得る固体撮像装置が記載されている。これにより、必要な範囲で高ビット精度の出力を得られるとしている。

##### 【先行技術文献】

##### 【特許文献】

##### 【0003】

【特許文献1】特開2007-281987号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

しかしながら、特許文献1に記載された技術では、アナログ信号に対して得られるデジタル信号との間の線形性についての検討が十分為されていなかった。特許文献1では、2つの比較器に与えられる参照信号RAMP1とRAMP2は、傾き（すなわち、時間に対する変化率）の違いが2の指數倍となるように設定しているが、例えば参照信号を生成するDACの特性ばらつきによって、正確に2の指數倍にならないおそれがある。

##### 【0005】

本発明は、上述の問題を解決し、アナログ信号とデジタル信号との間のリニアリティを向上させることを目的とする。

##### 【課題を解決するための手段】

##### 【0006】

本発明に係る光電変換装置は、光に基づく画素信号を出力する画素と、A/D変換部と、補正部とを有し、前記A/D変換部は、対応する前記画素の出力する前記画素信号に基づく

10

20

30

40

50

信号と、閾値との比較を行うことによって第1の比較結果信号を生成し、前記第1の比較結果信号が、前記画素信号に基づく信号が前記閾値よりも大きいことを示す場合には、前記A D変換部は、前記画素信号に基づく信号と、時間に対して第1の変化率で第1の電位まで電位が変化する参照信号とを比較することによって、前記画素信号に基づく信号をデジタル信号に変換し、前記第1の比較結果信号が、前記画素信号に基づく信号が前記閾値よりも小さいことを示す場合には、前記A D変換部は、前記画素信号に基づく信号と、時間に対して前記第1の変化率よりも小さい第2の変化率で、前記第1の電位よりも振幅が小さい第2の電位まで電位が変化する参照信号とを比較することによって、前記画素信号に基づく信号をデジタル信号に変換し、前記閾値が、前記第2の電位よりも振幅が小さく、前記補正部は、前記第1の変化率と前記第2の変化率との比を検出して、前記画素信号に基づくデジタル信号を補正することを特徴とする。

10

#### 【発明の効果】

#### 【0 0 0 7】

本発明によれば、アナログ信号とデジタル信号との間のリニアリティを向上させることができる。

#### 【図面の簡単な説明】

#### 【0 0 0 8】

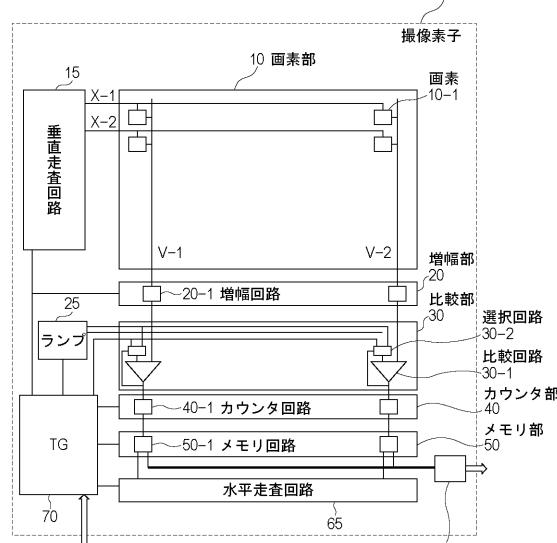

【図1】実施例1に係る撮像素子の構成図である。

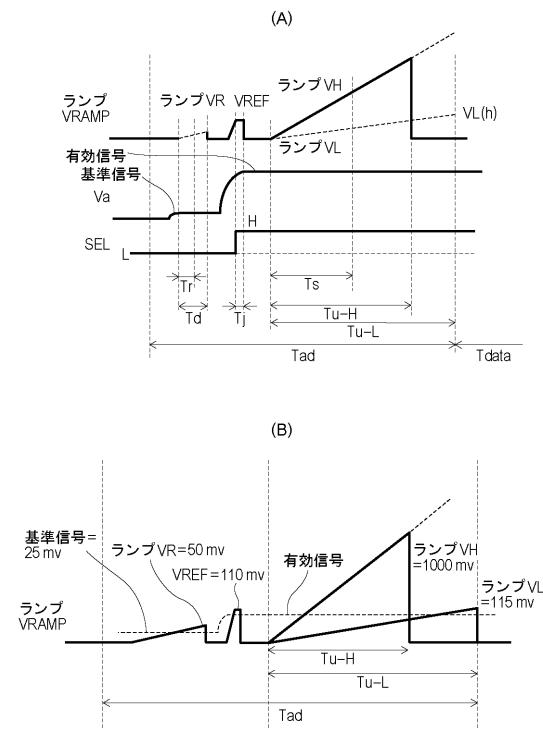

【図2】実施例1に係る動作を示すタイミング図である。

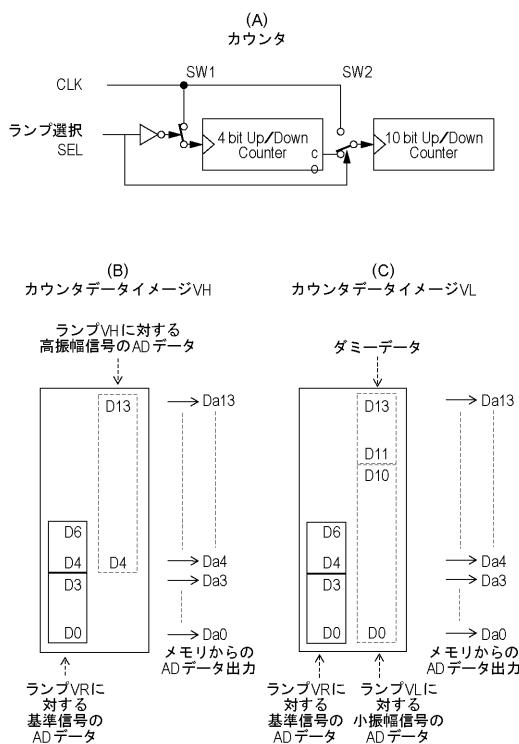

【図3】A D変換されたデータのビットシフトを説明する概念図である。

20

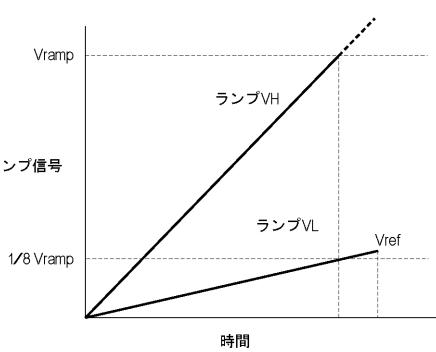

【図4】実施例1に係る参照信号を説明する図である。

【図5】本発明の原理を説明する図である。

【図6】実施例1に係る出力回路の構成図である。

【図7】傾き誤差を説明する図である。

【図8】実施例1に係る撮像素子の構成を示す図である。

【図9】実施例1に係る動作を説明する図である。

【図10】実施例2に係る撮像システムの構成を示す図である。

#### 【発明を実施するための形態】

#### 【0 0 0 9】

##### (実施例1)

30

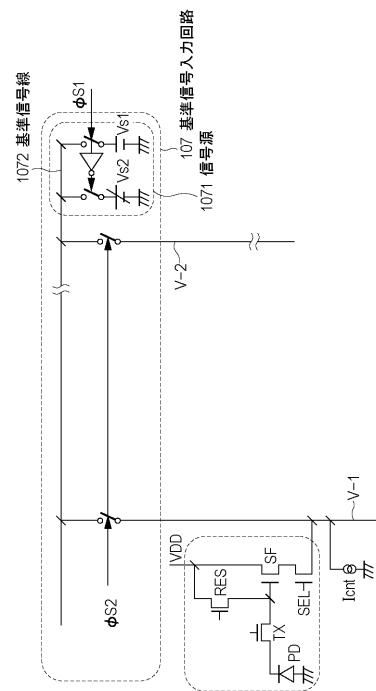

図1は、本発明の実施例に係る撮像素子100の概略構成図である。100は光電変換装置としての撮像素子であり、受光した被写体像を光電変換し、その電気信号をデジタル信号として出力する。撮像素子100は、画素部10、垂直走査回路15、増幅部20、ランプ信号発生回路(参照信号発生回路)25、比較部30、カウンタ部40、メモリ部50、出力回路60、水平走査回路65、タイミング発生回路(TG)70を有する。タイミング発生回路TGは、制御部としての機能を有する。A D変換部は、比較部30とカウンタ部40とを含んで構成される。画素部10は、2次元行列状に配置された複数の画素10-1を有する。画素10-1は、光電変換により画素信号を生成する。垂直走査回路15は、駆動パルスX-1,X-2,...を画素部10に出力する。増幅部20は、画素部10からの画素信号を増幅する。ランプ信号発生回路25は、画素信号との比較信号として、時間に対して変化するランプ信号(参照信号)を生成する。比較部30は、増幅部20により増幅された画素信号とランプ信号とを比較する。カウンタ部40は、比較部30が比較結果を出力するまでカウントする。メモリ部(補正部)50は、カウンタ部40のカウントデータを保持し、保持データのビットシフト及び演算を行う。水平走査回路65は、水平走査により、メモリ部50からのデータを出力回路60へ転送する。タイミング発生回路70は、上記回路ブロックをそれぞれタイミング制御する。

40

#### 【0 0 1 0】

画素部10は複数の画素10-1がエリア上に配置されているが、図1では簡略して4画素のみを図示している。各画素10-1の行は垂直走査回路15からの駆動パルスX-1,X-2により順次駆動される。各画素10-1のリセット状態における画素10-1

50

に基づく基準信号（リセット信号）と各画素 10 - 1 の非リセット状態における画素 10 - 1 に基づく有効信号（光電変換信号）は、垂直出力線 V - 1 ~ V - n を経て増幅部 20 へ導かれる。増幅部 20 からメモリ部 50 までは垂直出力線 V - 1 ~ V - n 毎に各回路が設けられている。増幅部 20 の各増幅回路 20 - 1 は画素 10 - 1 からの信号を単に増幅する機能のみであっても良いし、有効信号から基準信号の差分処理を行うことによりノイズを低減する CDS 処理機能を有しても良い。増幅部 20 で増幅することにより、比較部 30 で発生するノイズの影響を小さくすることができる。増幅器部 20 に CDS 処理機能を設けない場合は比較部 30 の入力部で CDS 処理を行うことができる。

#### 【0011】

比較部 30 は、増幅部 20 からの画素列に対応した比較回路 30 - 1 と、複数のランプ信号からの一つを選択する選択回路 30 - 2 を有する。比較部 30 は、増幅回路 20 - 1 からの基準信号と時間に対する変化率が小さいランプ信号とを比較した後、有効信号のレベルが比較レベルである比較電圧より大きいか、小さいかを判定し、その結果に応じて有効信号と比較するランプ信号を選択し、比較を行う。上記の比較電圧は、有効信号の S/N 比を考慮して設定される。カウンタ部 40 は、1 つの画素に対して 2 回の変換動作を行う。1 回目では、比較部 30 は基準信号と時間に対する変化率が小さいランプ信号とを比較し、カウンタ部 40 はランプ信号の立ち上がりから比較部 30 の出力信号が反転するまでダウンカウントする。基準信号とは、例えば増幅部 20 の入力をリセットした時に出力される信号や、増幅部 20 がない構成であれば画素 10 - 1 の出力をリセットした時に出力される信号である。2 回目では、有効信号のレベルが大きい場合は、比較部 30 は、有効信号と時間に対する変化率が大きいランプ信号とを比較し、カウンタ部 40 は、ランプ信号の時間に対する変化率が小と大の分解能比を補正してアップカウントを行う。その結果としての多ビット数の A/D 変換データは、メモリ部 50 のメモリ回路 50 - 1 に保持される。有効信号とは、光電変換によって得られる画素 10 - 1 からの信号を増幅部 20 で増幅したものや、増幅部 20 がない場合には画素 10 - 1 からの信号である。有効信号のレベルが小さい場合は、基準信号のダウンカウント結果に引き続き、比較部 30 は有効信号と時間に対する変化率が小さいランプ信号とを比較し、カウンタ部 40 はアップカウントを行う。その結果は、A/D 変換データとして、メモリ部 50 のメモリ回路 50 - 1 に保持される。メモリ回路 50 - 1 に保持された A/D 変換データは、水平走査回路 65 からの走査パルスにより出力回路 60 へ転送される。メモリ回路 50 - 1 は、フラグ信号を保持するフラグメモリを有しても良い。また、出力回路 60 は、メモリ回路から転送された信号に補正処理を施す機能を有しても良い。

#### 【0012】

以上述べたように、撮像素子 100 は、有効信号のレベルによらず、基準信号と時間に対する変化率が小さいランプ信号と比較するので、高分解能の基準信号の A/D 変換データを取得できる。有効信号の A/D 変換データから基準信号の A/D 変換データを補正処理するので、結果的に高精度、多ビット数の A/D 変換データが得られる。また、1 個の比較回路 30 - 1 が、有効信号のレベルに応じて、ランプ信号と比較するので、少ないビット数の A/D 変換処理を行い、高速化出来る。

#### 【0013】

図 2 (A) は、本実施例の撮像素子 100 の駆動方法を示すタイミング図である。

#### 【0014】

図 2 (A)において、期間 Tad は、比較回路に入力されるアナログ信号 Va の基準信号及び有効信号の A/D 変換期間である。期間 Tdat は、A/D 変換データを転送する転送期間である。期間 Tad の中に、期間 Td が画素からの基準信号の A/D 変換期間で、そのための比較信号が基準信号用ランプ信号（基準信号用参照信号）VR である。期間 Tj が有効信号の信号レベル判定期間であり、そのための比較信号が比較電圧 VREF である。また、期間 Tu が有効信号の A/D 変換期間で、そのための比較信号が有効信号用ランプ信号（有効信号用参照信号）VH 又は VL である。増幅回路 20 - 1 の出力信号 Va は、主に図示のような基準信号と有効信号を取り、比較回路 30 - 1 の入力端子へ導かれる

10

20

30

40

50

。比較回路 30 - 1 のもう一方の入力端子には信号  $V_a$  の比較信号であるランプ信号  $V_R$  A M P が入力される。ここで、基準信号とは、比較部 30 よりも前に C D S 回路を備える場合には、例えば增幅回路の入力をリセットしたことによって出力される信号である。一方、C D S 回路を持たない場合には、フローティングディフィュージョン部をリセットしたことに対応して垂直信号線に出力される信号に相当する。同様に、有効信号とは、例えば比較部 30 よりも前に C D S 回路を備える場合には、ノイズが低減された後の信号である。一方、C D S 回路を持たない場合には、フォトダイオードで発生した電荷をフローティングディフィュージョン部に転送したことによって垂直信号線に出力される信号に相当するランプ信号発生回路 25 は、タイミング発生回路 70 の制御信号 C N T 2 に制御されて、ランプ信号  $V_H$  / 比較電圧  $V_{REF}$  とランプ信号  $V_L$  / ランプ信号  $V_R$  を生成する。10 ランプ信号  $V_H$  は傾きが大きい上位ビット用のランプ信号であり、ランプ信号  $V_L$  は傾きが小さい下位ビット用のランプ信号である。また、比較電圧  $V_{REF}$  は有効信号のレベルを判定するための比較基準信号であり、基準信号用ランプ信号  $V_R$  は基準信号と比較するランプ信号である。これら 4 種のランプ信号は、タイミング発生回路 70 の制御信号 C N T 1 により制御される選択回路 30 - 2 により選択され、比較回路 30 - 1 へ入力される。また、タイミング発生回路 70 は、制御信号 C N T 2 によりランプ信号発生回路 25 を制御する。

#### 【 0015 】

次に、比較電圧  $V_{REF}$  について説明する。比較電圧  $V_{REF}$  は、別の電源回路から発生させても良いし、ランプ発生回路 25 で発生させても良い。ランプ発生回路 25 は、ランプ信号  $V_H$  の形成と同様に、発生途中（例えば  $60 \text{ mV}$  程度）で充電電流を停止することにより、比較電圧  $V_{REF}$  を生成することができる。比較電圧  $V_{REF}$  は、ランプ信号  $V_H$  に対して  $1/16$  の期間で発生させることができる。この期間をさらに短縮するには充電電流を大きくすれば良い。また、比較電圧  $V_{REF}$  は、ランプ信号  $V_L$  の最終到達電圧  $V_L(H)$  である  $67 \text{ mV}$  より低くする必要がある。このように低くすることで、有効信号は必ずランプ信号  $V_H$  又は  $V_L$  のどちらかで比較処理を行うことが出来る。20

#### 【 0016 】

比較回路 30 - 1 は、基準信号の A D 変換期間  $T_d$  で基準信号と基準信号用ランプ信号  $V_R$  とを比較し、基準信号用ランプ信号  $V_R$  が変化を開始してから基準信号との大小関係が逆転するまでの期間が  $T_r$  であるとする。カウンタ回路 40 - 1 は、その期間  $T_r$  にダウンカウントし、メモリ回路 50 - 1 はそのダウンカウント値（第 1 のカウント値）を基準信号デジタルデータとして保持する。基準信号用ランプ信号  $V_R$  は、ランプ信号  $V_L$  と同じ傾きである。同じ傾きにすることで、高分解能な基準信号デジタルデータを得ることが出来る。次に、信号振幅判定期間  $T_j$  では、比較回路 30 - 1 は、有効信号と比較電圧  $V_{REF}$  とを比較する。図示の例では、信号振幅判定期間  $T_j$  に、比較回路 30 - 1 は、有効信号が比較電圧  $V_{REF}$  より大きいことを表すハイレベルの選択信号  $S_{EL}$  を選択回路 30 - 2 に出力する。その結果、有効信号 A D 変換期間  $T_u$  では、選択回路 30 - 2 は、傾きが大きいランプ信号  $V_H$  を選択し、比較回路 30 - 1 へ出力する。比較回路 30 - 1 は、有効信号とランプ信号  $V_H$  とを比較し、両者の大小関係が逆転するまでの期間を  $T_s$  とする。カウンタ回路 40 - 1 は、その期間  $T_s$  において、上記の基準信号のダウンカウントに続きアップカウントを行う。メモリ回路 50 - 1 は、そのアップカウント値（第 2 のカウント値）を有効信号デジタルデータとして保持する。もし、信号レベル判定期間  $T_j$  に比較回路 30 - 1 の出力が逆転しなければ、選択信号  $S_{EL}$  はローレベルのままであり、有効信号のレベルは比較電圧  $V_{REF}$  よりも小さいということで、選択回路 30 - 2 は傾きが小さいランプ信号  $V_L$  を選択する。その場合、比較回路 30 - 1 は、有効信号とランプ信号  $V_L$  とを比較する。選択回路 30 - 2 は、増幅部 20 により増幅された有効信号のレベルに応じて異なる傾きのランプ信号  $V_H$  又は  $V_L$  を選択する。すなわち、選択回路 30 - 2 は、画素に基づく有効信号のレベルに応じて、ランプ信号の時間に対する変化率を設定する。比較回路 30 - 1 は、選択回路 30 - 2 により選択されたランプ信号と増幅部 20 により増幅された有効信号とを比較する。カウンタ回路 40 - 1 は、ランプ信304050

号の変化の開始から、比較回路 30 - 1 が、有効信号とランプ信号との大小関係が逆転したことを示す信号を出力するまでアップカウントする。

#### 【0017】

図 2 ( A )において、基準信号用ランプ信号  $V_R$  とランプ信号  $V_L$  は、先に述べたように同じ傾きである。基準信号用ランプ信号  $V_R$  は基準信号と比較されるが、基準信号は有効信号の基準信号でもあるので、高精度が必要であり、下位ビットを生成するランプ信号  $V_L$  と同じ傾きであるので、同一のランプ発生回路 25 を利用できるメリットがある。カウンタ回路 40 - 1 のダウンカウントモードとアップカウントモード機能は、図 3 ( A ) ~ ( C ) を参照しながら後述する。

#### 【0018】

増幅回路 20 - 1 のゲインは、撮影環境に応じて設定しうる。例えば、感度設定が 16 倍の場合は、信号レベル 62.5 mV を 1 V に増幅して比較回路 30 - 1 に入力することになる。この時、AD 変換に必要な SN 比は、大振幅信号をランプ信号  $V_H$  と比較する 10 ビット AD 変換の分解能で十分である。従って、感度設定が 16 倍以上であれば、選択回路 30 - 2 は、タイミング発生回路 70 からの制御信号 C O N T 1 によりランプ信号  $V_H$  を選択し、比較回路 30 - 1 に出力するように制御しても良い。画素部 10 の SN 比は画素部 10 の開口面積の影響が大きいので、開口面積によってランプ信号  $V_H$  とランプ信号  $V_L$  の傾き比や、上記のランプ信号  $V_H$  を選択するための感度設定が変わってくる。

#### 【0019】

次に、ランプ信号  $V_R$  の振幅や比較電圧  $V_{REF}$  の値をどのように決定するのかの一例を説明する。図 2 ( B ) は、図 2 ( A ) に示した期間  $T_{ad}$  におけるランプ信号  $V_{RAM}$  と増幅回路 20 - 1 の出力  $V_a$  とを重ねた図である。ランプ  $V_H$  の取り得る最大値、すなわち振幅を 1000 mV とする。この場合には、信号レベルが 1000 mV 以下のアナログ信号をデジタル値に変換することができる。

#### 【0020】

ランプ信号  $V_R$  の振幅は、比較器に入力される基準信号の最大振幅よりも大きな値に設定する必要がある。ここでは、ランプ信号  $V_R$  の振幅を 50 mV としている。

#### 【0021】

ランプ信号  $V_H$  はランプ信号  $V_L$  に対して 16 倍の傾きであるとすると、ランプ信号  $V_L$  は、期間  $T_{u-H}$  が終了する時刻において 62.5 mV となる。したがって、信号レベルが 62.5 mV 未満のアナログ信号はランプ信号  $V_L$  により変換するために、比較電圧  $V_{REF}$  は理想的には 62.5 mV に設定しうる。しかし、現実には、比較回路がオフセット性の特性誤差（ばらつき）を持つため、比較電圧  $V_{REF}$  を 62.5 mV に設定すると不都合が生じる恐れがある。たとえば、比較回路が 50 mV のオフセットを持つとすると、有効信号のレベルが 12.5 mV より大きい場合には、ランプ信号  $V_H$  を用いて AD 変換することになる。つまり、62.5 mV 未満の有効信号はランプ信号  $V_L$  で変換すべきであるにも関わらず、重畠された比較回路のオフセットのために、ランプ信号  $V_H$  を用いて AD 変換することになり、所望の精度が得られなくなる。

#### 【0022】

そこで、ランプ信号  $V_L$  で変換すべき最大信号振幅 62.5 mV に比較回路のオフセット 50 mV を加えた 112.5 mV を下回る信号が有効信号として比較回路に入力された場合には、ランプ信号  $V_L$  を用いて AD 変換するために、比較電圧  $V_{REF}$  を 112.5 mV 以下に設定する。図では、参照信号発生回路もばらつきを持つことを考慮して、比較電圧  $V_{REF}$  を 110 mV とした場合を示している。

#### 【0023】

ランプ信号  $V_L$  の振幅は、比較電圧  $V_{REF}$  以下のアナログ信号を AD 変換できるよう、比較電圧  $V_{REF}$  よりも大きい値に設定する。ここでは、比較電圧  $V_{REF}$  が 110 mV であるのに対して、ランプ信号  $V_L$  の振幅を 115 mV とした場合を図示している。115 mV は、ランプ信号  $V_H$  の振幅 1000 mV の 1 / 16 よりも大きいため、ランプ  $V_L$  を用いた場合の AD 変換期間  $T_{u-L}$  は、ランプ信号  $V_H$  を用いた場合の AD 変換期

10

20

30

40

50

間  $T_u - H$  よりも長くなる。このように、A/D 変換期間  $T_u - L$  を A/D 変換期間  $T_u - H$  よりも長く設定することで、比較器がオフセットを持っていたとしても、ランプ信号  $V_L$  を用いた A/D 変換を正確に実行することができる。

#### 【0024】

図 3 (A) ~ (C) は、カウンタ回路 (補正部) 40-1 の構成例を示す図である。カウンタ回路 40-1 は、基準信号と基準信号用ランプ信号  $V_R$  との比較、有効信号と有効信号用ランプ信号  $V_H$  又は  $V_L$  との比較における比較回路 30-1 の出力が逆転するまでをカウントする。比較回路 30-1 が基準信号の比較を行うときにはカウンタ回路 40-1 はダウンカウントする。これに対し、比較回路 30-1 が有効信号の比較を行うときにはカウンタ回路 40-1 はアップカウントする。そして、メモリ部 (補正部) 50 は、分解能比を補正するためのカウントデータのビットシフトを行う。

10

#### 【0025】

図 3 (A) は、カウンタ回路 40-1 の構成例を示す図である。図 3 (B) 及び (C) は、メモリ部 (補正部) 50 の処理を説明するための図である。図 3 (B) は、基準信号と基準信号用ランプ信号  $V_R$  とを比較した後、有効信号が比較電圧  $V_{REF}$  より大きい場合であり、有効信号とランプ信号  $V_H$  とを比較した時のカウントデータを示す図である。図 3 (C) は、基準信号と基準信号用ランプ信号  $V_R$  とを比較した後、有効信号が比較電圧  $V_{REF}$  より小さい場合であり、有効信号とランプ信号  $V_L$  とを比較した時のカウントデータを示す図である。

20

#### 【0026】

カウンタ回路 40-1 は、インバータ 601、4 ビットアップ / ダウンカウンタ 602、10 ビットアップ / ダウンカウンタ 603 及びスイッチ SW1, SW2 を有する。カウントクロック信号 CLK は、スイッチ SW1 及び SW2 に入力される。インバータ 601 は、選択信号 SEL の論理反転信号を出力する。スイッチ SW1 は、インバータ 601 の出力信号により制御される。スイッチ SW2 は、選択信号 SEL により制御される。カウンタクロック信号 CLK は、選択信号 SEL に応じて、4 ビットアップ / ダウンカウンタ 602 又は 10 ビットアップ / ダウンカウンタ 603 のクロック端子のいずれかに入力される。

20

#### 【0027】

図 3 (B) を参照しながら、有効信号が比較電圧  $V_{REF}$  より大きい場合であり、選択信号 SEL がハイレベルになり、比較回路 30-1 は有効信号とランプ信号  $V_H$  とを比較する場合を説明する。期間  $T_r$  では、選択信号 SEL がローレベルになる。すると、スイッチ SW1 により、カウンタクロック信号 CLK は、4 ビットアップ / ダウンカウンタ 602 のクロック端子に入力される。スイッチ SW2 により、4 ビットアップ / ダウンカウンタ 603 のクロック端子に出力される。4 ビットアップ / ダウンカウンタ 602 は、カウンタクロック信号 CLK に同期してダウンカウントを行い、データ  $D_0 \sim D_3$  を出力する。10 ビットアップ / ダウンカウンタ 603 は、4 ビットアップ / ダウンカウンタ 602 の桁上げ出力  $c_o$  に同期してダウンカウントを行い、データ  $D_4 \sim D_6$  を出力する。基準信号のダウンカウント値 (第 1 のカウント値) は、データ  $D_0 \sim D_6$  になる。次に、期間  $T_s$  では、選択信号 SEL がハイレベルになる。すると、スイッチ SW1 により、カウンタクロック信号 CLK は、4 ビットアップ / ダウンカウンタ 602 のクロック端子に入力されなくなる。スイッチ SW2 により、カウンタクロック信号 CLK は、10 ビットアップ / ダウンカウンタ 603 のクロック端子に出力される。10 ビットアップ / ダウンカウンタ 603 は、カウンタクロック信号 CLK に同期してアップカウントし、そのアップカウント値をメモリ部 50 に出力する。メモリ部 50 は、そのアップカウント値を 4 ビットシフトし、4 ビットシフトした 10 ビットデータ  $D_4 \sim D_{13}$  をデータ  $D_{a4} \sim D_{a13}$  として記憶する。また、メモリ部 50 は、4 ビットアップ / ダウンカウンタ 602 の出力 4 ビットデータ  $D_0 \sim D_3$  をデータ  $D_{a0} \sim D_{a3}$  として記憶する。結果的に、4 ビットアップ / ダウンカウンタ 602 及び 10 ビットアップ / ダウンカウンタ 603 において有効

30

40

50

信号と基準信号との差分が行われたデータが D a 0 ~ D a 1 3 になる。14ビットデータ D a 0 ~ D a 1 3 は、それぞれデータ D 0 ~ D 1 3 に対応し、メモリ回路 5 0 - 1 に記憶される。このように、有効信号とランプ信号 V H との比較による A D 変換データ D 4 ~ D 1 3 は、基準信号と基準信号用ランプ信号 V R との比較によるデータ D 0 ~ D 6 に対して、4ビットシフトされて差分処理される。これにより、高精度の14ビット A D 変換データ D a 0 ~ D a 1 3 が得られる。

#### 【 0 0 2 8 】

図 3 ( C ) を参照しながら、有効信号が比較電圧 V R E F より小さい場合であり、選択信号 S E L がローレベルになり、比較回路 3 0 - 1 は有効信号とランプ信号 V L とを比較する場合を説明する。期間 T r では、図 3 ( B ) と同様に、基準信号のダウンカウントが行われる。ダウンカウント値(第2のカウント値)は、データ D 0 ~ D 6 になる。次に、期間 T s では、選択信号 S E L がローレベルになる。すると、スイッチ S W 1 により、カウンタクロック信号 C L K は、4ビットアップ/ダウンカウンタ 6 0 2 のクロック端子に入力される。スイッチ S W 2 により、4ビットアップ/ダウンカウンタ 6 0 2 の桁上げ出力(キャリーアウト) c o は、10ビットアップ/ダウンカウンタ 6 0 3 のクロック端子に出力される。4ビットアップ/ダウンカウンタ 6 0 2 は、カウンタクロック信号 C L K に同期してアップカウントを行う。10ビットアップ/ダウンカウンタ 6 0 3 は、4ビットアップ/ダウンカウンタ 6 0 2 の桁上げ出力 c o に同期してアップカウントを行い、10ビットデータ D 0 ~ D 9 をメモリ部 5 0 に出力する。ダミーデータ D 1 1 ~ D 1 3 は、「0」である。データ D 0 ~ D 9 はそれぞれデータ D a 0 ~ D a 9 として、ダミーデータ D 1 1 ~ D 1 3 はデータ D a 1 1 ~ D a 1 3 として、14ビットデータ D a 0 ~ D a 1 3 がメモリ部 5 0 に記憶される。結果的に、4ビットアップ/ダウンカウンタ 6 0 2 及び10ビットアップ/ダウンカウンタ 6 0 3 において有効信号と基準信号との差分が行われたデータが D a 0 ~ D a 1 0 になる。ダミーデータ D 1 1 ~ D 1 3 は、データ D a 1 1 ~ D a 1 3 として追加される。14ビットデータ D a 0 ~ D a 1 3 は、メモリ回路 5 0 - 1 に記憶される。ダミーデータ D 1 0 ~ D 1 3 は、小振幅データであるので高位ビットがゼロであることを意味している。図 3 ( B ) の場合はデータ D 4 ~ D 1 3 の 10 ビットで合ったのに対して、図 3 ( C ) の場合にはデータ D 0 ~ D 1 0 の 11 ビットが、A D 変換によって得られるデータとなる。これは、図 2 ( B ) に示したように、A D 変換期間 T u - L の方が A D 変換期間 T u - H よりも長いため、A D 変換期間の差分が、1ビットのデータの差として現れているためである。

#### 【 0 0 2 9 】

以上のように、有効信号が大振幅信号か小振幅信号かによらず、有効信号と基準信号との差分処理する際に、基準信号は基準信号用ランプ信号 V R により高分解能で比較処理したカウントデータを利用する。これにより、量子化ノイズの影響を小さくした高精度の A D 変換データを得ることが出来る。また、図 3 ( B ) では、4ビットシフトさせた10ビットデータ D 4 ~ D 1 3 を用いることにより、14ビットの A D 変換データ D a 0 ~ D a 1 3 を取得することができる。

#### 【 0 0 3 0 】

比較回路 3 0 - 1 は、期間 T d で、画素に基づく基準信号と基準信号用ランプ信号 V R とを比較し、カウンタ回路 4 0 - 1 は、画素に基づく基準信号と基準信号用ランプ信号 V R との大小関係が逆転するまでの期間 T r に第1のカウント値のカウントを行う。その後、比較回路 3 0 - 1 は、期間 T u で、画素に基づく有効信号と有効信号用ランプ信号 V H 又は V L とを比較し、画素に基づく有効信号と有効信号用ランプ信号 V H 又は V L との大小関係が逆転するまでの期間 T s に第2のカウント値のカウントを行う。カウンタ回路 4 0 - 1 及びメモリ部 5 0 の補正部は、基準信号用ランプ信号 V R 及び有効信号用ランプ信号 V H 又は V L の時間に対する変化率の違いに対応する第1のカウント値及び第2のカウント値の分解能の違いを補正する。そして、メモリ部(補正部) 5 0 は、補正した第1のカウント値及び第2のカウント値の差分データ D a 0 ~ D a 1 3 を出力する。具体的には、メモリ部(補正部) 5 0 は、図 3 ( B ) の場合、第2のカウント値をビットシフトする

10

20

30

40

50

ことにより、分解能の違いを補正する。

#### 【0031】

上記では、期間  $T_r$  で第1のカウント値をダウンカウントし、期間  $T_s$  で第2のカウント値をアップカウントする例を説明したが、その逆でもよい。カウンタ回路 40 - 1 は、期間  $T_r$  で第1のカウント値をアップカウントし、期間  $T_s$  で第2のカウント値をダウンカウントすることにより、第1のカウント値及び第2のカウント値の差分データ  $D_a_0 \sim D_a_{13}$  を出力するようにしてもよい。すなわち、カウンタ回路 40 - 1 は、第1のカウント値をダウンカウント又はアップカウントし、第1のカウント値のアップダウン方向と逆方向になるように第2のカウント値をカウントする。これにより、メモリ部（補正部）50 は、補正した第1のカウント値及び第2のカウント値の差分データ  $D_a_0 \sim D_a_{13}$  を出力することができる。10

#### 【0032】

上述の差分処理は、ダウンカウントモードとアップカウントモードのカウント機能を有するカウンタ回路 40 - 1 により行う例を説明したが、これに限らない。有効信号と基準信号の差分処理は、基準信号と有効信号のカウンタ結果をメモリに記憶し、メモリ部 50 から出力回路 60 へ転送する時、出力回路 60 から撮像素子 100 の外部へ出力する時、又は外部回路（例えば図 8 の映像信号処理回路部 830）で行っても良い。この際、比較電圧  $V_{REF}$  に対する信号判定レベル（選択信号 SEL）を認識するフラグデータを AD 变換データに追加すれば、どのようなビットシフト方法にも対応が容易となる。カウンタ部 40 が出力する AD 变換データは、有効信号のレベルを示すフラグデータと共に出力される。20

#### 【0033】

次に、参照信号  $V_H$  および  $V_L$  について、より詳しく説明する。図 4 は図 2 の期間  $T_u$  におけるランプ信号  $V_L$  および  $V_H$  の遷移を示す。仮に、ランプ信号  $V_L$  で変換する場合とランプ信号  $V_H$  で変換する場合とで、3 ビット分の違いを持たせることを考える。そのため、ランプ信号  $V_H$  に対してランプ信号  $V_L$  の傾きは  $1 / (2^3) = 1 / 8$  に設定される。ランプ信号  $V_L$  を用いて変換するアナログ信号の振幅は小さいため、比較器の特性ばらつきの影響が相対的に大きくなる。そのため、信号レベル  $1 / 8 V_{ramp}$  付近の信号は、比較器のオフセット成分が重畠されて  $1 / 8 V_{ramp}$  を超えるおそれがある。そこで、図 4 に示すように、ランプ信号  $V_L$  はランプ信号  $V_H$  よりも長い期間、信号レベルを変化させることで、比較器のオフセット成分を考慮しても AD 变換できるようにすることができる。このときのランプ信号  $V_L$  が取り得る最大値は、例えば図 2 で示した比較電圧  $V_{REF}$  である。30

#### 【0034】

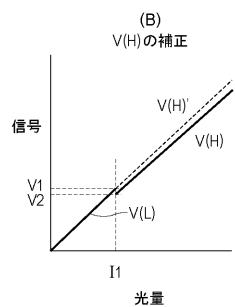

図 5 は横軸を入射光量、縦軸を AD 变換後のデジタルデータとして、両者の関係を示す図である。光量は、比較回路に与えられるアナログ信号  $V_a$  に対応する。 $V(H)$  はランプ信号  $V_H$  との比較処理から得た信号を表し、 $V(L)$  はランプ信号  $V_L$  との比較処理から得た信号を表している。また、実線  $V(H)$  と信号レベルゼロ間の破線は  $V(L)$  の理想的な傾きの場合の直線である。理想的には、入射光量に対して、デジタルデータは線形になる。図 5 (A) では、光量  $I_1$  未満の場合にはランプ信号  $V_L$  で変換し、光量  $I_1$  を超える場合にはランプ信号  $V_H$  で変換する場合を示している。光量  $I_1$  の時の信号電圧は、ランプ信号  $V_L$  で変換して得られたデータ  $V_1$  と、ランプ信号  $V_H$  で変換して得られたデータ  $V_2$  とで値が異なっている。40

#### 【0035】

これはランプ信号発生器でのランプ  $V_L$  とランプ  $V_H$  信号が、製造時のバラツキにより理想的な傾きからの傾き誤差や、ランプ信号  $V_L$  とランプ信号  $V_H$  とをそれぞれ利用する画素数が信号レベルにより変わり、信号を伝送する配線の寄生容量の合成値が異なり、結果的に傾きが変わることなどによる。さらに、ランプ  $V_L$  と  $V_H$  の傾きの比を変えた時も、信号電圧  $V_1$  と  $V_2$  が異なることが起こりうる。このように信号電圧  $V_1$  と  $V_2$  が異なると画素信号レベルの連続性が断たれ、微妙な輝度差がある画像上では輝度段差が発生す50

る。従ってV(L)あるいはV(H)の傾きを調整して、リニアリティを向上させる必要がある。

#### 【0036】

また、傾きの誤差とは別に、オフセット誤差も生じうる。図5(B)は、オフセット誤差を説明する図である。光量I1よりも光量が小さい領域では理想的な特性を示し、光量I1よりも光量が大きい領域では、点線で示す理想的な特性に対して、信号レベルが低くなるオフセットが生じている場合を図5(B)に示す。オフセット誤差が生じている場合も、オフセット量を調整することで、リニアリティを向上させることができる。

#### 【0037】

次に、リニアリティを補正する方法を説明する。

10

#### 【0038】

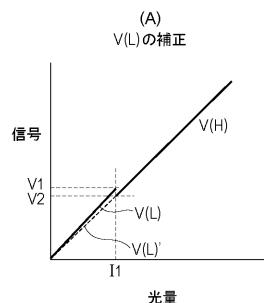

図6は本実施例に係る出力回路60の構成例を示す図である。出力部60は傾き比の調整、傾き比の誤差検出、傾き比の誤差補正、さらに有効信号データから基準信号データを減算する差分処理を行う機能を有する。

#### 【0039】

メモリ回路50は、メモリ(フラグ)、メモリ(S)、およびメモリ(N)を含む。メモリ(S)は、AD変換期間Tu-HもしくはTu-Lで得られたデジタルデータを保持し、メモリ(N)は、D変換期間Tdで得られたデジタルデータを保持する。メモリ(フラグ)は、ランプ信号VHとVLのうちのどちらを用いて有効信号のAD変換を行ったかを示すデータを保持するメモリである。

20

#### 【0040】

出力部60はランプ信号の傾き比を調整するレベルシフト回路60-2、ランプ信号の傾き誤差を検出する傾き誤差検出回路60-4、ADデータの傾き誤差を補正する傾き比補正回路60-6、傾き比及び傾き誤差を補正した有効信号のAD変換結果(S3-AD)から基準信号のAD変換結果(N-AD)を差分するS-N差分回路60-8からなる。レベルシフト回路60-2および傾き誤差補正回路60-6は、フラグデータFGによって処理を切り替えられる。

#### 【0041】

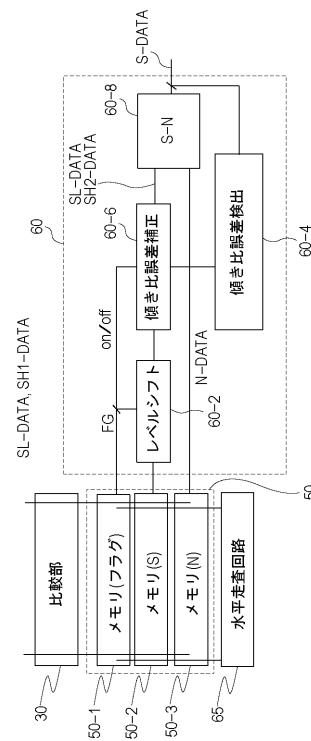

図7は傾き誤差を説明するランプ信号波形図である。

#### 【0042】

30

デジタルデータの傾き誤差について詳しく説明する。図7において、有効信号と比較するランプ信号VH(実線)が実際の信号であり、ランプ信号VH'(破線)が理想の信号を表している。ここで、基準信号と比較するランプ信号VLの傾きをk、ランプ信号VHとVLの傾き比をa、ランプ信号の傾き誤差を $\delta$ とすると、ランプ信号VH'の傾きは $a \cdot k$ であり、ランプ信号VHの傾きは $a \cdot \delta + k$ である。

#### 【0043】

ランプ信号VRAMPと一点鎖線で表した画素信号Vaの比較処理を行う。基準信号のAD期間はT1、有効信号のAD期間は、理想のランプ信号VH'では、基準信号のAD期間がT2'、有効信号のAD期間がT3'である。また、実際のランプ信号VHでは、それぞれのAD期間がT2、T3である。

40

#### 【0044】

理想のランプ信号VH'によるAD期間では、基準信号と有効信号の傾き比を調整するために、有効信号のAD期間をa倍すると、 $a \cdot (T2' + T3')$ となり、基準信号T1との差分処理により、 $a \cdot T2' = T1$ であるので、有効信号のAD期間は $a \cdot T3' = a \cdot (T2' + T3') - T1$  (1)となる。

#### 【0045】

実際のランプ信号VHによるAD期間では、実際のADデータの傾き比を調整後、傾き誤差 $\delta$ で除算し、基準信号T1を差分処理することで、正しい有効信号のADデータを得ることができ、

50

$$a \cdot (T_2 + T_3) / -T_1 = a \cdot T_3' \quad (2)$$

となる。

#### 【0046】

従って、精度良いA Dデータを取得するためには、傾き誤差を検出する必要がある。図8に、信号源としてのテスト用基準信号生成部の構成を示す。テスト用基準信号生成部107は、信号生成回路1071を含む。信号生成回路1071は信号S1に応じて電圧Vs1もしくはVs2を供給できるように構成されている。信号生成回路1071は、信号S2で駆動されるスイッチを介して、各垂直信号線接続される。

#### 【0047】

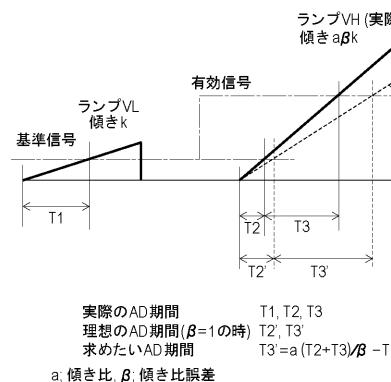

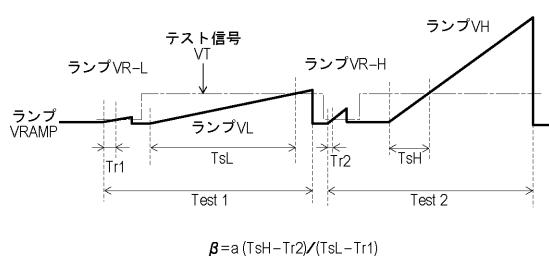

図9はランプ信号VLとランプ信号VHの傾きの比を検出するためのタイミング図である。

10

#### 【0048】

信号S2をHレベルにし、基準信号生成部107からの基準信号をテスト信号VTとして比較回路30-1に入力する。比較回路30-1ではテスト信号VTとランプ信号VRAMPを比較処理する。期間Ts-Lで、ランプ信号VLによりA D変換して得られたデータSLをメモリ回路50-1に保持させる。次に期間Ts-Hでランプ信号VHにより変換して得られたデータSHを、メモリ回路に保持させる。メモリ回路に保持させたデータSLおよびSHは、同時に外部に転送しても良いし、順次転送しても良い。

#### 【0049】

比較回路のオフセット電圧を除去するために、オフセット電圧を得るために図示のランプ信号VR-L、ランプ信号VR-Hを入力してもよい。ランプ信号VR-LとVLとは同じ傾きであり、ランプVR-HはランプVHと同じ傾きである。同じ傾きにすることにより、図3のアップダウンカウンタでオフセット電圧を差分処理することが可能となる。

20

#### 【0050】

ここでは、テスト信号VTを用いて分解能の補正を行う場合を例にとって簡単に説明する。傾き比が1/16の場合、ランプ信号VLでは、クロックCLKを4ビットアップダウンカウンタへ入力し、ランプ信号VHではクロックCLKを10ビットアップダウンカウンタへ入力することで分解能の補正が行われる。補正されたデータを、後段の映像信号処理回路830で、傾き誤差を演算し、その演算結果Kをメモリする。図5の信号レベルでは、K=V1/V2であり、信号V(L)この1/Kを乗算すれば、信号V(L)の傾きが補正され、信号V(H)と信号V(L)が直線的に連続するように、データSLを補正できる。この補正処理により、画像の輝度段差は検知減以下に低減出来る。補正是信号V(H)で補正処理を行っても良い。分解能の相違の補正是アップダウンカウンタに限らず、ランプ信号VLとランプ信号VHの比較処理からのデータを後段の回路で4ビット分レベルシフトさせても良い。ランプ信号VR-LやVR-Hを用いて変換した信号との差分を処理する、S-N処理も同様である。

30

#### 【0051】

また、基準信号生成部107を設けずに、撮像素子に一様光を照射することで、テスト信号VTとしても良い。

#### 【0052】

テスト信号生成部107からのテスト信号VTを、信号S2をHレベルにし、テスト信号線1072と垂直信号線V-1を接続し、增幅回路を経て比較回路30-1に入力する。テスト信号は信号S1をHレベルとすることで、画素信号の基準信号に相当する電圧を、S1をLレベルにすることで有効信号に相当する電圧を生成する。

40

#### 【0053】

図9の実施例ではTest1の期間に、テスト信号VTと傾き小のランプ信号VR-Lとランプ信号VLの比較処理の結果であるA Dデータの差分処理により、有効信号のA Dデータ1(TsL-Tr1)を取得し、傾き誤差検出回路60-4に保持する。次に、Test2の期間に、テスト信号VTと傾き大のランプ信号VR-Hとランプ信号VHの比較処理の結果であるA Dデータの差分処理により、有効信号のA Dデータ2(TsH-T

50

r<sub>2</sub>)を取得し、傾き誤差検出回路60-4に保持する。傾き誤差は、保持したA/Dデータ1とA/D2データ2から、式(3)で求めることが出来る。

$$= (T_{SH} - T_{r2}) / (T_{SL} - T_{r1}) \quad (3)$$

#### 【0054】

また、傾き誤差は基準信号生成部107を設けずに、撮像素子に一様光を照射することで、テスト信号V<sub>T</sub>としても良い。

#### 【0055】

傾き誤差は誤差検出回路60-4にメモリされ、撮像素子の実駆動で、傾き大のランプ信号V<sub>H</sub>で比較したA/DデータSH1-DATAに対し1/倍の処理を行う。

#### 【0056】

上記の操作は、例えば撮像素子を撮像システムに組み込む前に行って、補正用のデータを撮像システムが備えるメモリに記憶させておくことができる。また、撮像操作に先立つて行うことで、温度などの環境条件による影響を合わせて低減することもできる。

10

#### 【0057】

##### (実施例2)

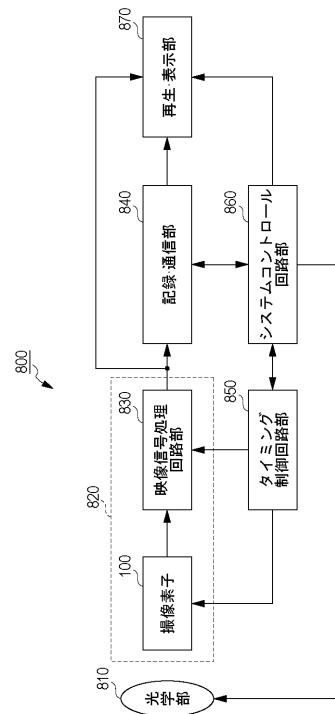

図10は、本発明の第3の実施例による撮像システムの構成例を示す図である。撮像システム800は、例えば、光学部810、撮像素子100、映像信号処理回路部830、記録・通信部840、タイミング制御回路部850、システムコントロール回路部860、及び再生・表示部870を含む。撮像装置820は、撮像素子100及び映像信号処理回路部830を有する。撮像素子100は、第1の実施例で説明した撮像素子100が用いられる。

20

#### 【0058】

レンズ等の光学系である光学部810は、被写体からの光を撮像素子100の、複数の画素が2次元状に配列された画素部10(図1)に結像させ、被写体の像を形成する。撮像素子100は、タイミング制御回路部850からの信号に基づくタイミングで、画素部10に結像された光に応じた信号を出力する。撮像素子100から出力された信号は、映像信号処理部である映像信号処理回路部830に入力され、映像信号処理回路部830が、プログラム等によって定められた方法に従って信号処理を行う。映像信号処理回路部830は、入力された信号に対して図3のビットシフト処理及び/差分処理等の信号処理を行ってもよい。映像信号処理回路部830での処理によって得られた信号は画像データとして記録・通信部840に送られる。記録・通信部840は、画像を形成するための信号を再生・表示部870に送り、再生・表示部870に動画や静止画像を再生・表示させる。記録・通信部840は、また、映像信号処理回路部830からの信号を受けて、システムコントロール回路部860と通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。

30

#### 【0059】

システムコントロール回路部860は、撮像システムの動作を統括的に制御するものであり、光学部810、タイミング制御回路部850、記録・通信部840、及び再生・表示部870の駆動を制御する。また、システムコントロール回路部860は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラム等が記録される。また、システムコントロール回路部860は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内に供給する。具体的な例としては、読み出す行やリセットする行の変更、電子ズームに伴う画角の変更や、電子防振に伴う画角のずらし等である。タイミング制御回路部850は、システムコントロール回路部860による制御に基づいて撮像素子100及び映像信号処理回路部830の駆動タイミングを制御する。

40

#### 【0060】

以上のように、第1及び第2の実施例によれば、画素の有効信号が大振幅信号か小振幅信号であるかにかかわらず、画素の基準信号は高分解能の基準信号用ランプ信号V<sub>R</sub>を利用して比較を行う。有効信号のレベルを判定後、その判定された信号に適したランプ信号

50

VH又はVLを選択し、有効信号と基準信号の分解能比を補正した差分処理によりA/D変換データを取得することにより、高精度・多ビット化を達成することができる。

#### 【0061】

暗い撮影環境では、露光条件によるが、画素信号は小振幅信号になり易く、画素信号を増幅して感度アップすることができる。第1の実施例では、増幅回路20-1で信号を増幅することにより感度をアップさせることができる。画素部10からの信号を増幅せずに比較回路30-1へ入力する場合は、ランプ信号の傾きを変えて結果的に感度アップを行うことができる。第1及び第2の実施例は、ランプ信号の傾きを一義的に決めるものではなく、求める感度アップに対応してランプ信号の傾きを変えることができ、例えば感度アップが2倍の場合は、ランプ信号の傾きを1/2に制御することができる。

10

#### 【0062】

上述の各実施例では参照信号として、時間に対して連続的に変化するランプ信号を例示したが、階段状に変化する参照信号など、他の形式でも良い。

#### 【0063】

上記の各実施例は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。例えば、参照信号として、ランプ信号は時間に対してレベルが直線的に変化するものを説明したが、階段状に変化するものを用いても良い。

20

#### 【符号の説明】

#### 【0064】

100 撮像素子

10 画素部

25 ランプ信号発生回路

30 比較部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 松野 靖司

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 武藤 隆

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 鈴木 明

(56)参考文献 特開2011-244249(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378